急峻なサブスレッショルド特性を持つ

“PN-body tied SOI-FET”の研究

森貴之

金沢工業大学大学院

工学研究科

電気電子工学専攻

指導教員

井田次郎教授

内容梗概

本 論 文 は, 新 規 考 案 し た ト ラ ン ジ ス タ で あ る “PN-body tied (PNBT) Silicon on Insulator Field -Effect Transistor (SOI-FET)” に 関 す る 研 究 結 果 を ま と め た も の で あ る. 本 論 文 の 目 的 は , 急 峻 な サ ブ ス レ ッ シ ョ ル ド 特 性 を 持 つ PNBT SOI-FET を 設 計 , メ カ ニ ズ ム の 解 析 を 行 い, 極 低 消 費 電 力 大 規 模 集 積 回 路( Large -Scale Integration circuit: LSI)及 び 極 低 電 力 用 レ ク テ ナ 整 流 デ バ イ ス へ の 応 用 可 能 性 を 追 求 す る こ と で あ る.

こ れ ま で LSI は , 構 成 デ バ イ ス で あ る 金 属 酸 化 膜 半 導 体 電 界 効 果 ト ラ ン ジ ス タ ( Metal-Oxide Semiconductor Field-Effect Transistor: MOSFET)の 微 細 化 に よ っ て 高 性 能 化 , 高 密 度 化 , 低 消 費 電 化 を し て き た が, そ の 性 能 改 善 は 限 界 を 迎 え つ つ あ る . 特 に 低 消 費 電 力 化 に 関 し て は, MOSFET の ス イ ッ チ ン グ 性 能 を 表 す サ ブ ス レ ッ シ ョ ル ド 係 数(Subthreshold Slope: SS)が 動 作 原 理 に 基 づ く 物 理 的 限 界 を 持 っ て い る た め, 電 源 電 圧 を 一 定 値 以 下 に す る こ と が 難 し く , 現 在 か ら の 劇 的 な 改 善 は 望 め な い. そ こ で 今 , 理 論 限 界 を 下 回 る 低 い 電 源 電 圧 で 急 峻 ス イ ッ チ ン グ が 可 能 な デ バ イ ス(steep slope devices)の 研 究 が 盛 ん に お こ な わ れ て い る. steep slope devices は 従 来 の MOSFET と は 異 な る 原 理 で 動 作 し, 例 え ば , ト ン ネ ル 現 象 を 利 用 し た ト ン ネ ル 電 界 効 果 ト ラ ン ジ ス タ や, 強 誘 電 体 キ ャ パ シ タ と 通 常 の キ ャ パ シ タ を 接 続 し た 際 に 発 生 す る と さ れ る 負 性 容 量 効 果 を 利 用 し た 負 性 容 量 電 界 効 果 ト ラ ン ジ ス タ が 主 と し て 研 究 さ れ て い る. こ れ ら の デ バ イ ス は, 理 論 的 に は 非 常 に 優 れ た 性 能 を 持 つ と 期 待 さ れ て い る が , 実 測 結 果 で は ま だ 十 分 な 特 性 が 得 ら れ て い な い. 本 研 究 で は 新 構 造 デ バ イ ス の PNBT SOI-FET を 提 案 し , 先 行 研 究 を 凌 ぐ 極 急 峻 な SS (< 1 mV/decade) を 実 証 し た . ま た , 応 用 と し て PNBT SOI-FET を RF 環 境 発 電 (Radio Frequency-Energy Harvesting: RF-EH) 用 の 整 流 デ バ イ ス に 活 用 す る 検 討 を 行 っ た. PNBT SOI-FET の 特 徴 は , こ れ ま で の 先 行 研 究 と 比 較 し て も 非 常 に 低 い ド レ イ ン 電 圧 で 動 作 す る 点 に あ る. PNBT SOI-FET は フ ロ ー テ ィ ン グ ボ デ ィ 効 果 と 呼 ば れ る 現 象 を 利 用 し て 極 急 峻 な SS を 達 成 し て い る. フ ロ ー テ ィ ン グ ボ デ ィ 効 果 は キ ャ リ ア の 蓄 積 を 利 用 す る 現 象 で, 従 来 型 の SOI MOSFET で も 現 れ る こ と が 知 ら れ て い る . し か し , 高 い ド レ イ ン 電 圧 が 必 要 な イ ン パ ク ト イ オ ン 化 現 象 を 用 い な け れ ば

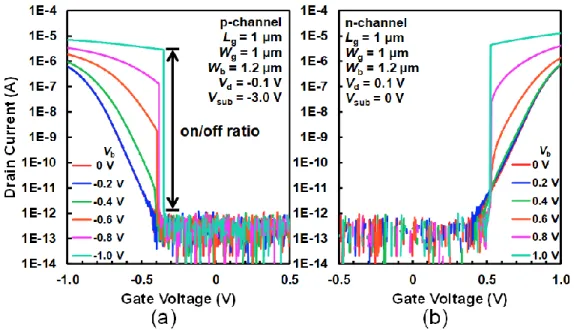

な ら ず, 低 消 費 電 力 用 デ バ イ ス に 使 用 す る こ と は 難 し い . 本 研 究 で は, SOI MOSFET に PN 接 合 を 持 つ ボ デ ィ 端 子 を 繋 げ た PNBT 構 造 を 考 案 し た. こ の 構 造 で は , ボ デ ィ 端 子 か ら キ ャ リ ア を 注 入 し , フ ロ ー テ ィ ン グ ボ デ ィ 効 果 を 引 き 起 こ す こ と が で き る. 考 案 方 式 で は イ ン パ ク ト イ オ ン 化 現 象 を 用 い る 必 要 が な い た め, ド レ イ ン 電 圧 を 0.1 V に す る こ と が 可 能 と な っ た . ま た , キ ャ リ ア の 動 き を 解 析 し , デ バ イ ス 中 に 形 成 さ れ た pnpn サ イ リ ス タ 構 造 に よ る フ ィ ー ド バ ッ ク 効 果 が 働 き, キ ャ リ ア が 注 入 さ れ る 動 作 メ カ ニ ズ ム を 提 案 し た . 極 急 峻 な SS は , n-channel 及 び p-channel 両 方 の タ イ プ で 確 認 す る こ と が で き た. す な わ ち , PNBT SOI-FET を 用 い た 相 補 型 MOS が 実 現 可 能 で あ る こ と を 示 唆 で き た. 更 に , 本 デ バ イ ス は 現 在 商 用 で 使 用 さ れ て い る SOI MOS FET と 同 じ 製 造 ラ イ ン で 作 製 さ れ た . steep slope devices は Si 以 外 の III-V 材 料 や , 通 常 の Si-LSI で は 使 用 さ れ な い 工 程 を 使 用 す る も の が 多 い 中, 通 常 Si プ ロ セ ス で 作 製 で き た こ と は コ ス ト の 面 で も 優 位 で あ る こ と を 意 味 し て い る. た だ し , PNBT SOI-FET は ゲ ー ト 長 を 縮 小 化 す る と on/off 比 が 減 少 す る と 分 か っ た . そ こ で, デ バ イ ス シ ミ ュ レ ー シ ョ ン に よ っ て 特 性 の 更 な る 改 善 検 討 を 行 っ た. 結 果 , ボ デ ィ 側 pn 接 合 部 の 幅 及 び 不 純 物 濃 度 を 最 適 化 す る こ と で, on/off 比 を 増 大 さ せ る こ と が で き た . こ れ は ゲ ー ト 長 縮 小 化 に よ る on/off 比 減 少 が , 他 の デ バ イ ス パ ラ メ ー タ の 最 適 化 に よ っ て 補 償 で き る こ と を 示 し て い る. さ ら に 応 用 と し て, PNBT SOI-FET を RF-EH 用 レ ク テ ナ 整 流 デ バ イ ス に 活 用 す る た め の 基 礎 検 討 を 行 っ た. RF-EH は 地 上 デ ジ タ ル テ レ ビ, 携 帯 電 話 , Wi-Fi 等 の 電 波 を 用 い る 環 境 発 電 方 式 で , 広 範 囲 に エ ネ ル ギ ー が 存 在 し, 非 接 触 で そ れ ら を 集 め る こ と が で き る た め , 有 望 な 環 境 発 電 方 式 の 一 つ で あ る. し か し , 得 ら れ る エ ネ ル ギ ー が 非 常 に 小 さ く, 極 低 入 力 電 圧 を 整 流 し , エ ネ ル ギ ー と し て 取 り 出 す 必 要 が あ る た め, レ ク テ ナ に 使 用 で き る 適 し た デ バ イ ス の 開 発 が 課 題 と な っ て い る. そ こ で , ダ イ オ ー ド 接 続 し た PNBT SOI-FET を 整 流 デ バ イ ス と し て 使 用 す る こ と で, 従 来 型 の ダ イ オ ー ド で は 困 難 だ っ た 極 低 入 力 電 圧 に お け る 整 流 特 性 を 実 証 し た. 静 特 性 で は 50 mV 以 下 の 入 力 で も 極 急 峻 な タ ー ン オ ン 特 性 を 確 認 し た. ま た , 動 特 性 で は 30 MHz 入 力 ま で の 半 波 整 流 特 性 及 び 交 流 電 圧 10 mV の 検 波 を 確 認 し た. 本 研 究 に よ っ て, PNBT SOI-FET を RF-EH 用 レ ク テ ナ の 整 流 デ バ イ ス と し て 使 用 し, そ の 集 め た エ ネ ル ギ ー に よ っ て PNBT SOI-FET を

用 い た 極 低 消 費 電 力 LSI を 駆 動 さ せ る , セ ン サ ー ネ ッ ト ワ ー ク シ ス テ ム へ の 展 望 を 得 る こ と が で き た と 言 え る.

Abstract

In this thesis, our newly proposed “PN-body-tied (PNBT) Silicon on Insulator FieldEffect Transistor (SOIFET)” for ultralow power large -scale integrations (LSIs) and high efficiency rectifiers is presented, and its performance demonstrated.

Ultralow power devices for micro and nanowatt el ectronics, such as those used in sensor network and medical applications, are one of the frontier research themes for LSI. To achieve ultralow power LSI, low power supply voltages and off currents are required. To that end, it is necessary to reduce the subthreshold slope (SS) of the metal -oxide semiconductor field -effect transistors (MOSFETs). Recently, steep SS devices to overcome the fundamental lower limit of the conventional MOSFET ’s SS (≈ 60 mV/decade (dec)) at room temperature have been studied. In p articular, tunnel field-effect transistors and negative capacitance field -effect transistors have been reported as mainstream research. These devices have achieved a steep SS (< 60 mV/dec) in the simulation results; however, actual fabricated devices have not yet achieved these ideal characteristics. In this thesis, we propose and demonstrate super -steep SS PNBT SOI-FET for ultralow power LSIs. Additionally, we investigate diode connected PNBT SOI-FET (hereinafter, termed as PNBT diode) for radio -frequency (RF) energy harvesting.

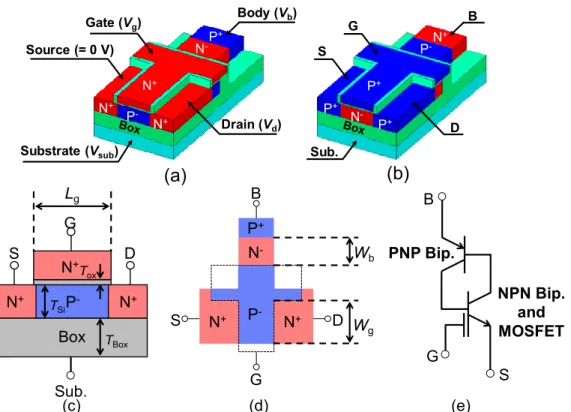

PNBT SOI-FET is a conventional body-tied SOI MOSFET with an n (or p)-region inserted between a p+ (or n+) contact region and a channel region. The purpose of adopting the PNBT approach is to induce floating -body effects (FBEs) usin g methods other than impact ionization. It is known that super-steep SS occurs in a floating body SOI MOSFET due to FBEs; however, unlike conventional FBEs, the PNBT approach does not use impact ionization. The aim is to realize injection of carriers from the body terminal. The measurement results show super -steep SS (< 1 mV/dec) characteristics while maintaining low off current and high on/off ratio with low drain voltage (± 0.1 V), good output characteristics, and threshold voltage controllability. The op erating mechanism of the PNBT SOI-FET is clarified through simulations, and it is found that an inherent thyristor on the PNBT structure plays a significant role. Both the p

-channel and n--channel PNBT SOI-FET characteristics are discussed, and it is indicated that an ultralow power complementary metal -oxide-semiconductor can be realized by the PNBT SOI -FET.

Additionally, the characteristics of PNBT diode are investigated to determine its suitability in RF energy harvesting, which is a promising power source for such systems because it is contactless and covers a wide area, when compared to other energy harvesting technologies. However, the expected power is very small and drops below the microwatt level when the coverage area is increased. Therefore, the mo st pressing problem with regard to RF energy harvesting is high -efficiency rectification, because conventional diodes do not function as rectifiers at such ultralow input powers. We presented the PNBT diode and demonstrated that the device possesses low le akage current and sharp turn -on characteristics, even in the ultralow voltage range (50 mV). In the half -wave rectification experiments, rectification up to 30 MHz and rectification of the ultralow voltage signal up to 10 mV were also confirmed. These results indicate that the PNBT diode can potentially be used in high -efficiency rectification for energy harvesting, particularly in situations of ultralow input power.

In this study, we designed a prospective technology for a sensor network system that uses PNBT SOI-FET as a rectifier device and ultralow power LSIs with PNBT SOI-FET.

i

目次

第

1 章 序論 ... 1

1.1 はじめに...1 1.2 研究背景...1 1.3 極低消費電力 LSI の実現へ向けた取り組みと課題 ...2 1.3.1 LSI の消費電力 ...2 1.3.2 サブスレッショルド特性 ...4 1.3.3 MOSFET のスケーリング則と短チャネル効果 ...5 1.3.4 完全空乏型 MOSFET... 10 1.3.5 従来型 MOSFET の理論限界 ... 11 1.3.6 SS < 60 mV/dec の steep SS デバイス ... 12 1.4 RF-EH 用整流デバイスの実現へ向けた取り組みと課題 ... 20 1.4.1 Hi-Z アンテナ ... 22 1.4.2 従来型ダイオードの理論限界 ... 23 1.4.3 ゼロバイアスダイオード ... 24 1.5 研究内容... 25 1.6 論文の構成 ... 25 1.7 参考文献... 27第

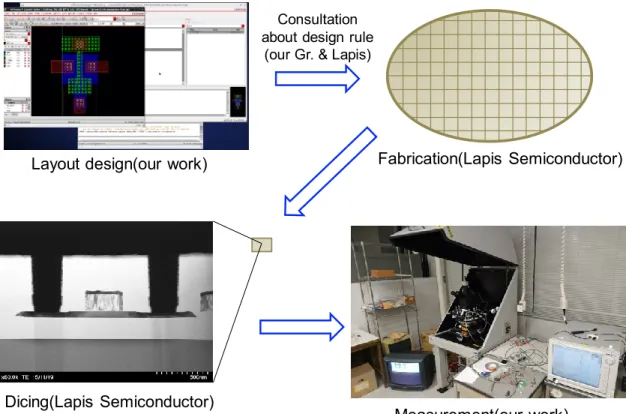

2 章 デバイス作製方法及びシミュレーション方法 ... 33

2.1 はじめに... 33 2.2 デバイス作製方法 ... 33 2.3 シミュレーション方法 ... 34 2.3.1 Shockley-Read-Hall (SRH) モデル ... 352.3.2 トラップ補助トンネル(Trap Assisted Tunneling : TAT)モデル ... 35

2.3.3 バンド間トンネル(Band To Band Tunneling : BTBT)モデル ... 36

2.3.4 Auger 再結合モデル ... 37

2.4 参考文献... 38

第

3 章 PN-body tied SOI-FET の構造と特性 ... 39

3.1 はじめに... 39

3.2 PN-body tied SOI-FET の構造 ... 39

3.3 従来型 SOI MOSFET による super-steep SS ... 39

ii

3.4.1 PN-body tied SOI-FET の基本アイデア ... 44

3.4.2 シミュレーションによるメカニズム検証 ... 44

3.5 実測における PN-body tied SOI-FET の特性 ... 48

3.6 まとめ... 60

3.7 参考文献... 61

第

4 章 シミュレーションによる PN-body tied SOI-FET 高性能化の

検討 ... 62

4.1 はじめに... 62 4.2 SRH モデルのキャリア寿命パラメータフィッティング ... 62 4.3 各種デバイスパラメータ依存性 ... 67 4.3.1 ベース幅 Wb依存性 ... 67 4.3.2 ベース不純物濃度 Nb依存性... 70 4.3.3 SOI 膜厚 TSi依存性 ... 72 4.3.4 チャネル不純物濃度 Nch依存性 ... 75 4.3.5 ゲート酸化膜厚 Tox依存性 ... 78 4.3.6 ゲート幅 Wg依存性 ... 81 4.4 まとめ... 84 4.5 参考文献... 85第

5 章 PN-body tied SOI-FET を用いた RF-EH 用整流デバイスの検

討 ... 86

5.1 はじめに... 86

5.2 従来型ダイオードの I–V 特性 ... 86

5.3 PN-body tied diode の構造と特性 ... 88

5.3.1 PN-body tied diode の構造 ... 88

5.3.2 PN-body tied diode の I–V 特性 ... 89

5.3.3 PN-body tied diode を用いた半波整流実験 ... 95

5.4 まとめ... 102

5.5 参考文献... 103

第

6 章 結論 ... 104

6.1 はじめに... 104

iii

6.3 全体のまとめ及び今後の展望 ... 105

付録

A シミュレーションにおける PN-body tied SOI-FET の各種物

理量分布 ... 107

謝辞

1

第

1 章 序論

1.1 はじめに

これまで, 大規模集積回路(Large-Scale Integration circuit: LSI)はその構成デバ イスである金属酸化膜半導体電界効果トランジスタ(Metal-Oxide Semiconductor Field-Effect Transistor: MOSFET)の微細化によって高性能, 高密度, 低消費電化 してきたが, 近年その性能改善は限界を迎えつつある. 本研究では新構造の “PN-body tied (PNBT) Silicon on Insulator Field-Effect Transistor (SOI-FET)” を提案 し, 従来型 MOSFET の理論限界を超えることで極低消費電力 LSI に使用するこ とを目的としている. また, 応用として PNBT SOI-FET を RF 環境発電(Radio Frequency-Energy Harvesting: RF-EH)用レクテナ整流デバイスに活用するための 検討を行う. 第1 章では研究背景として 2 つのテーマについて説明する. 1 つは極低消費電 力 LSI 用デバイスの必要性に関するもので, これまで行われてきた MOSFET の 微細化による高性能化と低消費電力化に関する取り組み及び急峻なサブスレッ ショルド特性を持つデバイスの先行研究と課題を示す. 2 つ目は RF-EH 用高効率 整流素子の必要性に関して, 従来型ダイオードの理論限界とゼロバイアスダイ オードの先行研究を示す. 最後に本研究の目的及び本論文の構成を述べる. 1.2 研究背景 現在, 社会の情報化はますます進み, 様々なデータがコンピュータによって 処理され, 我々の生活をより豊かにするために活用されている. コンピュータ は, LSI や記憶デバイス分野の目覚ましい進歩により, 計算スピードや扱えるデ ータ量がますます増加している. しかし, 我々が取り扱いたいデータも膨大な ものとなってきており, 際限のない容量, 処理速度の向上が求められている. そ して, これらの処理を行うために膨大な電力が消費されている. 世界でエネル ギー問題が叫ばれる中, 消費電力は大きな問題となっている. これは大型の演 算処理装置だけではなく, スマートフォンやタブレット端末等のポータブルデ バイスにも言える. ポータブルデバイスは小型化・高性能化とともに, バッテリ ー駆動のため, 低消費電力で長時間駆動できることが求められる. さらに近年, モノのインターネット(Internet of Thing: IoT)に代表されるような, センサーノ ードをばらまき, 情報を収集する分野や, インプラント医療分野が活況を見せ ている. IoT, インプラント医療で使用されるデバイスでは, 長期間メンテナンス フリーのバッテリーレスデバイス, すなわち, 太陽光や振動等の環境発電 (Energy Harvesting: EH)で電力を収集し, そこで得られるレベルの極低消費電

2

力で動作するものが求められている.

上述した装置において消費電力を下げるためには, 演算処理を行う LSI チッ プの低消費電力化が必要である. 図 1.1 に各デバイスにおける LSI チップの動作 時電力及びスタンバイ時リーク電流のまとめを示す. 極低消費電力分野では, micro, nano Watt レベルの電力, リーク電流の LSI チップが求められる. この領域 は現在の LSI 研究における最先端分野の一つとなっている[1]. また, EH は環境 中から微小な電力を集め, デバイスで使用できるよう変換する必要があり, そ の高効率化が求められる. 本研究では LSI の低消費電力化と EH の高効率化の 2 つを目的とする. 次節より上記 2 つの目的に関して, より詳細な説明を行う. 図1.1 各デバイスの動作時電力及び待機時リーク電流. 1.3 極低消費電力 LSI の実現へ向けた取り組みと課題 1.3 節では LSI の極低消費電力化へ向けたこれまでの取り組みと課題に関して 述べる. 1.3.1 LSI の消費電力

現在使用されるロジック用 LSI チップの大半は p-channel 及び n-channel の MOSFET を組み合わせた相補型 MOS(Complementary MOS: CMOS)回路で作ら れている. ここでは図 1.2 に示す CMOS インバータを例にその消費電力につい

3

て説明する.

通常, LSI の消費電力は以下の式で表される.

𝑃

active= 𝑛𝑎𝑓𝐶

load(𝑉

th+ 𝑉

OD)

2𝑃

standby= 𝑛𝐼

leak(𝑉

th+ 𝑉

OD)

Pactiveは動作時の消費電力, Pstandbyは待機時の消費電力, n は LSI 中の総トラン

ジスタ数, a は動作率(1 クロック中にトランジスタがスイッチングする平均回 数), f は動作周波数, Cloadは負荷容量(次段インバータ容量), Vthはしきい値電

圧, VODはオーバードライブ電圧, Ileakはリーク電流を表す. Pactiveはスイッチング,

すなわちCloadを充放電する際に消費される(図1.2(a)). 理想的な CMOS インバ

ータではこの時に貫通電流は流れない. なぜなら p-channel MOS(PMOS)がオ ン状態の時, n-channel MOS(NMOS)はオフ状態となり, 逆に NMOS がオン状態 の時, PMOS はオフ状態となるためである. これが相補型(Complementary)MOS と呼ばれる所以である. しかしながら, 完全に電流を遮断できるわけではなく, オフ時にもわずかな電流は流れてしまう. 待機時にはこの Ileak により Pstandbyが 消費される(図1.2(b)). 動作周波数, 負荷容量が決まっている場合, 消費電力は VthとVODを足しあわせた電源電圧VDD及びIleakに依存することが分かる. 図1.2 CMOS インバータの消費電力に関する説明図. (a) 動作時の消費電力, (b) 待機時の消費電力. 2 2 1 DD CV 2 2 1 DD CV charge discharge Active ON OFF OFF ON leak

I

Standby (b) (a) (1.1) (1.2)4

国 際 半 導 体 技 術 ロ ー ド マ ッ プ (International Technology Roadmap for Semiconductors: ITRS ) は ト ラ ン ジ ス タ を 用 途 に よ っ て 高 速 性 重 視 ( High Performance: HP), 一般用(Low Operating Power: LOP), 低待機電力重視(Low Standby Power: LSTP)の 3 種類に分けた[2]. これは, LSI に用いられているトラ ンジスタの af によってデバイスの最適な設計が変わるためである. 消費電力に 関してより詳細を検討するために, 式 1.3 で示されるスイッチングエネルギーu (1 回のスイッチングで消費されるエネルギー)を考える.

𝑢 =

𝑃

total𝑛𝑎𝑓

= 𝐶

load𝑉

DD 2+

𝐼

leak𝑉

DD𝑎𝑓

Ptotalは LSI 合計の消費電力を表す. ここで af が大きくなると, 待機時の消費電 力による影響は小さくなることが分かる. 例えば HP に分類されるような常時計 算し続けるサーバーではaf が大きい. すなわち, Pactiveが主な消費電力となり, 相 対的にPstandbyの影響が小さいため, Vthを低く設定し, Ileakを大きくしても低消費 電力化を実現できる. しかし, LSTP に分類される待機時間の長いポータブルデ バイスではaf が小さく, Ileakを抑える必要がある[3], [4]. VDDを低くすることでも 消費電力を抑えることが可能だが, それはすなわち, ドライブ電流を抑えるこ とになるため, 動作速度が劣化する. そのため, 極低消費電力用 LSI では低い IleakとVthを同時に実現することが理想である. 1.3.2 サブスレッショルド特性 MOSFET において IleakとVthはサブスレッショルド特性によって決まる. サブ スレッショルド特性は, MOSFET におけるスイッチング性能を表すパラメータ, サブスレッショルド係数 (Subthreshold slope: SS)で数値化される. SS はサブスレ ッショルド領域における, ドレイン電流 Idを 1 桁増加させるために必要なゲー ト電圧Vgによって定義され, 次式で表される[4].𝑆𝑆 = ln(10) 𝑚

𝑘

B𝑇

𝑞

𝑚 = (1 +

𝐶

dm𝐶

OX)

kBはボルツマン定数, T は格子温度, q は素電荷, Cdmは空乏層容量, COXはゲ ート酸化膜容量である. m はボディ効果係数と呼ばれる. 通常の MOSFET では, Vgによってコントロールできるサブスレッショルド電 (1.3) (1.4) (1.5)5 流は熱拡散機構に支配される. そのため式 1.4 によって SS が決まり, 室温にお いてγ を除いた部分の値は約 60 となる. m は 1 以下にはできないため, SS の理論 下限は約60 mV/decade (dec) である. LSI の低消費電力化, すなわち, 低い IleakとVDDには, SS を急峻化することが 必要である. 図1.3 MOSFET のサブスレッショルド特性. 1.3.3 MOSFET のスケーリング則と短チャネル効果 これまで LSI の高集積化, 高性能化, 低消費電力化は MOSFET の微細化によ って進められきた. 1.3.3 項では, MOSFET のスケーリング則と微細化によって顕 在化した問題点について述べる. <スケーリング則> MOSFET の高性能化・低消費電力化は, 主にデバイススケーリング(scaling)

V

DD

I

on

V

th

I

leak

Gate Voltage

lo

g

D

ra

in

C

u

rre

n

t

V

OD

Subthreshold

Slope (SS)

6 によって達成されてきた. スケーリング則は Dennard らによって提案され[5], 今 日においても MOSFET 微細化の重要な指導原理となっている. 以下に電界一定 スケーリングについて説明する. 電界一定スケーリングでは, 図 1.4 で示すように, デバイス電圧及びデバイス 寸法を同一の倍率 k だけ比例縮小することにより, 高集積化, 高速化, 低消費電 力化, 同一面積ウェハ上に作成できるチップ数の増加による低コスト化が同時 に達成できる. 表 1.1 に電界一定スケーリング則におけるパラメータの変化を示 す. 図1.4 スケーリングによる MOSFET の微細化. 表1.1 電界一定スケーリング則.

Parameter Scaling Ratio Gate Length Lg, Gate Width Wg 1/k

Gate Oxide Thickness TOX, Junction Deepness xj 1/k

Substrate Impurity Density NA k

Voltage V 1/k

Current I 1/k

Capacitance C 1/k

Delay Time t = CV / I 1/k Power Consumption P = VI 1/k2

Integration degree (Transistor per Chip) k2

Power Consumption per Chip 1 Gate Drain Source Oxide Gate Drain Source

1/k

7 <短チャネル効果> 上述のスケーリングによって低消費電力化を行ってきた LSI だが, 近年の 1 μm を切る短チャネル MOSFET ではデバイス内部が高電界化し, しきい値電圧 の変動, SS の劣化など, 長チャネル MOSFET では起こらなかった問題を引き起 こすようになった. このような微細化により発生する現象を短チャネル効果と 呼び, 以下のものが存在する.

・Drain Induced Barrier Lowering (DIBL)

短チャネルMOSFET ではドレイン電圧 Vdが高くなるとDrain Induced Barrier

Lowering (DIBL) と呼ばれる現象が起こる. 図 1.5 にシミュレーションから求め たゲート酸化膜/Si 界面における伝導帯のゲート長 Lg 依存性を示す. Vd が高く, Lgが短いと, ポテンシャルの上端が低くなることが分かる. これは, Lgが短くな ると, Vgによって制御できる空乏電荷が小さくなることから説明される. DIBL に よって短チャネルMOSFET は超チャネル MOSFET より SS が劣化し, Vthが低下 する. DIBL の低減には, ゲート酸化膜厚 Tox及びソース・ドレイン接合深さをス ケーリングすることが重要となる. 図1.5 ゲート酸化膜/Si 界面におけるポテンシャルの Lg依存性(DIBL). Nchは チャネルの不純物濃度を表す. 0.2 0.15 0.1 0.05 0 0 0.5 1 1.5 Energy (eV) Distance (μm) NMOS TOX=5nm Nch=1E16cm-3 Vg=0V Lg=1μm Vd=50mV 0.5μm 50mV 0.2μm 50mV 0.2μm 1.0V

Drain side

Source side

8 ・パンチスルー(Punch-Through) 高い Vdが印加されて DIBL が更に進行すると, Vgでコントロールされない大 きなIdが流れる. この状態をパンチスルー(Punch-Through)と呼ぶ. 図 1.6 に示 すように, パンチスルー状態ではチャネル下部で電流が流れてしまうため, Vgに よるコントロール性を失い, リーク電流が流れてしまう. 図1.6 パンチスルー状態の NMOS における電子濃度分布. ゲート界面から離れ た箇所で電流が流れてしまっていることが分かる.

・Gate Induced Drain Leakage (GIDL)

Toxを薄くする必要がある短チャネル MOSFET では, ゲートとドレインのオー

バーラップ領域が高電界化し, Gate Induced Drain Leakage (GIDL) と呼ばれる現 象が発生しやすくなる. 例えば, NMOS においてゲート電圧を負方向へ変化させ た場合, ゲートとドレインのオーバーラップ領域で, 図 1.7(a) に示すようにド レインで空乏層ができる. ゲートとドレイン間のバンド図で表すと図 1.7(b) の ようになり, 高電界化したゲート酸化膜とドレイン界面で価電子帯から伝導体 へのトンネル電流が流れる. これによりリーク電流が発生し , 短チャネル MOSFET では問題となる.

Drain

Source

Gate

9

図 1.7 GIDL の説明図. NMOS における GIDL 発生時の (a) 空乏層とキャリア の様子, (b) バンド図. 上述した短チャネル効果によって, 図 1.8 で示すように MOSFET の SS は劣化し, Ileakが増大するようになり, スケーリングによる低消費電力化が難しくなった. これを解決するために, 次項で示す完全空乏型 MOSFET が登場した. 図1.8 短チャネル効果による SS の劣化及び Vthの変動. N+ N+

Source

Drain

Vd> 0 VGate

Vg< 0 V Depletion Layer Hole Electron(a)

(b)

Ec Ev Ec Ev Gate DrainV

thI

leakGate Voltage

lo

g

D

ra

in

C

u

rre

n

t

Short Channel MOSFET Long Channel MOSFET SS Deterioration10 1.3.4 完全空乏型 MOSFET

ここまで説明してきたMOSFET は Bulk 基板上にプレーナー型 MOSFET を形 成した Bulk MOSFET であった. 本節では短チャネル効果による SS の劣化を改 善 す るた めに 開発 され た 完全 空乏型 MOSFET の Silicon on Insulator (SOI) MOSFET と FinFET 構造に関して説明する.

<SOI MOSFET>

SOI MOSFET は埋め込み酸化膜(Buried Oxide:Box)によって, デバイスを作 りこむSi 層(SOI 層)と, 基板側 Si 層を分離した構造を持つ MOSFET である. 図1.9 に SOI MOSFET の断面図を示す. SOI MOSFET はソース・ドレイン底面が Box 層に接触しているため, 底面の寄生容量が小さくなり, 高速化できるという 利点を持っている.

また, SOI MOSFET には部分空乏型(Partially Depleted : PD)SOI MOSFET(図 1.9(a))と完全空乏型(Fully Depleted : FD)SOI MOSFET(図 1.9(b))がある. PD SOI MOSFET は SOI 層の厚さが最大空乏層幅より厚いものを指し, ボディ下部 に中性領域が存在することになる. 対して FD SOI MOSFET は SOI 層の厚さが最 大空乏層幅より薄く, チャネル全体が空乏化している. これにより, FD における, 式1.5 の CdmはSOI 層の容量 CSOIとBox 層の容量 CBoxの直列結合容量に置き換

わる. Box 層が十分厚い場合, この容量は非常に小さくなり, m はほぼ 1 となるた め, SS は, 室温の理想的な値である約 60 mV/dec となり短チャネル効果が抑制さ れる.

図1.9 SOI MOSFET の断面図. (a) PD SOI MOSFET, (b) FD SOI MOSFET.

(a)

(b)

S

G

D

C

11 <FinFET> FinFET はマルチゲートデバイスのひとつで, 図 1.10(a) に示すような, ヒレ (Fin)型の Si 部分をゲートが覆う形になったデバイスである. 図 1.10(b) はゲ ート部分の断面図を示している. ゲートによるチャネル部分のポテンシャル制 御を左右から(ゲート上部酸化膜が薄い場合は上からも併せて)行うことができ るため, ゲートによるチャネル部ポテンシャルの支配力が高い. Fin が十分に薄 い場合, Si 部は完全空乏化するため, SS は約 60 mV/dec となり, 短チャネル効果 を抑制することができる. 図1.10 は SOI 基板を例として示しているが, Bulk 基板でも作成は可能である. Bulk 基板の場合は SOI 基板よりプロセスの工程数が増加する. どちらを使用す るかは基板コスト, プロセス難度, ばらつき, 自己加熱効果等の観点から選択さ れる[6]–[10]. 例えば, 商用デバイスとしては, Intel が 2012 年, 22 nm テクノロジ ーからBulk 基板を用い, tri-gate トランジスタ(ゲート上部含め 3 方向から制御) の名前でFinFET 技術を採用している. 図1.10 FinFET の構造図. (a) 鳥瞰図, (b) ゲート部断面図. 1.3.5 従来型 MOSFET の理論限界

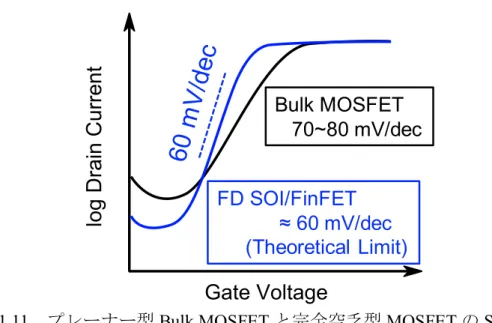

上述した完全空乏型 MOSFET の登場により, プレーナー型 Bulk MOSFET で は室温で70~80 mV/dec 程度だった SS は約 60 mV/dec まで急峻にすることがで きるようになった. しかし, 1.3.2 項で説明した通り, 60 mV/dec が SS の理論下限 であり, サブスレッショルド特性が熱拡散機構に従う従来型 MOSFET ではこれ 以上SS を急峻にして低消費電力化することができない. Gate Box Oxide Layer (a) (b)

12

図1.11 プレーナー型 Bulk MOSFET と完全空乏型 MOSFET の SS 比較

1.3.6 SS < 60 mV/dec の steep SS デバイス 上述の通り, 従来型 MOSFET はすでに SS ≈ 60 mV/dec へ到達している. しか し, 極低消費電力用 LSI では更に急峻な SS を持つデバイスが必要となる. そこ で現在, 理論下限を下回る SS を持つ, 新しい原理で動作する steep SS デバイス の研究が行われている. 図 1.12 で示すように, steep SS デバイスは, 低い Ileakを 保ったまま, 従来のものより更に低い VDD でトランジスタを駆動させることが できる. 以下に代表的な先行研究例を紹介する. 図1.12 Steep SS デバイスのサブスレッショルド特性.

FD SOI/FinFET

≈ 60 mV/dec

(Theoretical Limit)

Bulk MOSFET

70~80 mV/dec

13

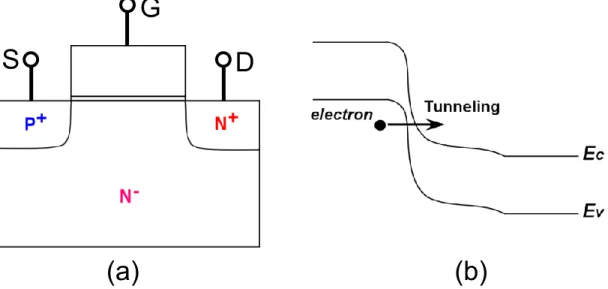

<Tunnel FET (TFET)>

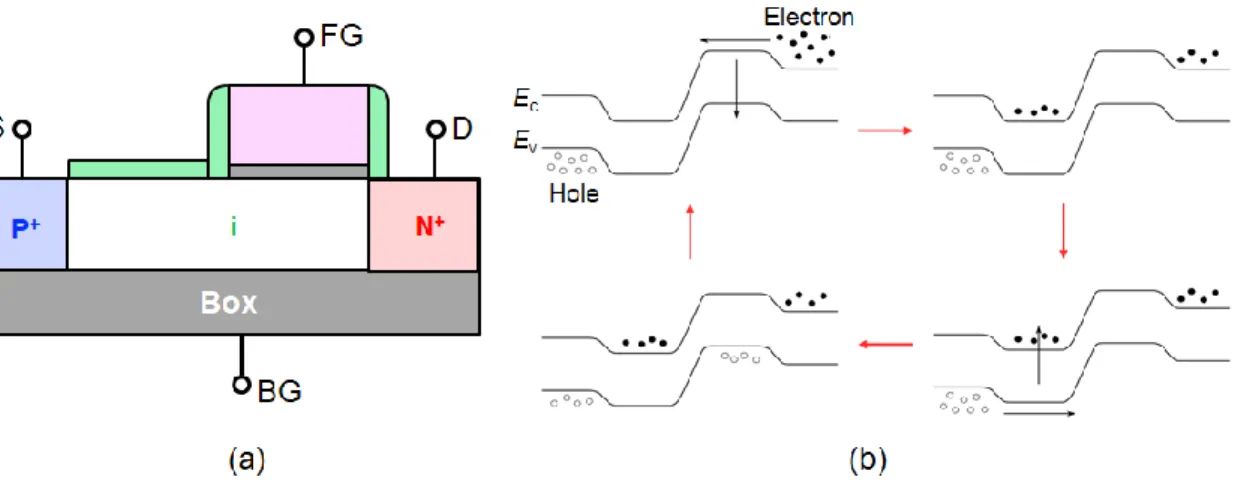

Tunnel FET (TFET) はトンネル現象を利用したスイッチングデバイスである. 図 1.13(a) に TFET の構造を示す. TFET は P–I (P−もしくはN−) –N 構造のソース/ド

レイン非対称構造を持ち, Vgによって, 図 1.13(b) で示すように, ソース–チャネ ル間のトンネル電流を制御することによりスイッチングを行う. サブスレッシ ョルド電流が熱拡散機構によらないため, 60 mV/dec を切る急峻な SS を実現で きるが, 基板材料が Si の場合, バンド間トンネルは間接遷移のため, トンネル抵 抗が高く, オン電流が低いという問題がある. 現在, 特性を改善するために, 接 合部で電界が強くなるようなデバイス構造の工夫[11], 直接遷移でトンネル現象 を起こす III-V 材料による TFET の開発[12]–[14], Si でもトラップを用いたトン ネル電流の増幅[15] などの研究が盛んに行われている.

図1.13 TFET の動作原理. (a) TFET の構造図, (b) TFET オン時のバンド図.

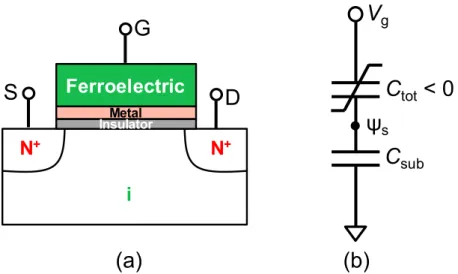

<Negative capacitance FET (NCFET)>

Negative Capacitance FET (NCFET) は強誘電体の負性容量効果を利用したデバ イスである. 強誘電体キャパシタは通常の絶縁体キャパシタと接続されたとき, 条件次第では負の容量として働くという主張がされている[16]. すなわち, 図 1.14(a) に示すような, 通常の MOSFET のゲートに強誘電体を積層した構造にす ることで, 式 1.4 の Coxが負となり, SS が 60 mV/dec より小さくなる. 実測でも SS < 60 mV/dec が観察されているが[17], [18], 高速動作において Steep SS が現れ ないといった報告もされている[19]. 詳細な動作メカニズムの追及や動作スピー ドに関して課題はあるが, TFET と合わせて steep SS デバイスのメインストリー ムとして研究されている.

S

G

D

(a)

(b)

14

図1.14 NCFET の動作原理. (a) NCFET の構造図, (b) ゲート容量と基板容量の 関係.

<Resistive-gate FET (ReFET)>

Resistive-gate FET (ReFET) は電圧による抵抗変化を利用した FET である. こ こでは図1.15(a)に示す Pt/TiN/TaOx/Poly-Si の組み合わせによる例で説明する[20].

遷移金属酸化物を金属で挟み込み電圧を印加すると, 図 1.15(b) で示すように酸 素空孔が発生し, 抵抗が変化する. これをゲート電極に使用することで, 非常に 急峻なスイッチングを引き起こすことが可能になる. 高い Vg が必要なことや,

オフ時は抵抗変化のリセットが必要なため, ヒステリシス特性を持つであろう ことが重大な課題として挙げられる.

図1.15 ReFET の動作原理. (a) ReFET の構造図, (b) 抵抗変化の原理.

N+ N+ Ferroelectric

S

G

D

i Metal Insulator(a)

(b)

V

gC

tot< 0

C

subψ

s N+ N+ Pt S G D i Poly-Si Insulator TaOx TiN Poly-Si TaOx TiN (a) (b) oxygen vacancy15

<Microelectromechanical (MEM) logic switch>

図1.16 に Microelectromechanical (MEM) logic switch の構造を示す. MEM logic switch は, ゲート電圧によって機械的にスイッチを動かし, ON/OFF の制御を行 うデバイスである[21], [22]. 図 1.16 は 3 端子構造のものだが, 4 端子構造のもの もあり, ソース/ドレイン対称構造にすることができる. 端子の接触/非接触のリ レーでスイッチングを行うため, 非常に急峻な SS と, 低いオフ電流を実現でき るが, 大きなヒステリシス幅を持つことと機械的強度の問題がある.

図1.16 MEM logic switch の構造図(3-terminal).

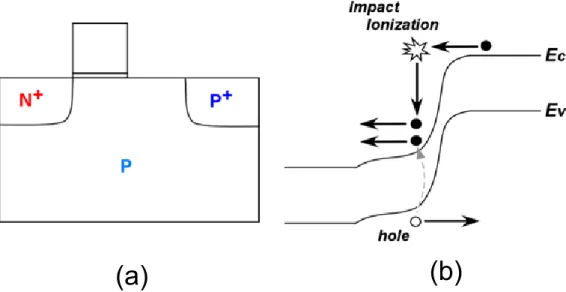

<Impact ionization MOS (I-MOS)>

Impact ionization MOS (I-MOS) はインパクトイオン化現象によるアバランシ ェ降伏を利用したスイッチングデバイスである. 図 1.17(a) にデバイス構造を示 す. I-MOS は P–I (P もしくは N) –N 構造で, 片側にオフセットがとられている. 図1.17(b) で示すように, オフセット領域を高電界にすることでアバランシェ降 伏を発生させ, 非常に急峻な SS (数 mV/dec) を得ることができる. しかし, 高い ドレイン(もしくはソース)電圧が必要[23], [24]で, Si I-MOS では 4.5 V 以下に 下げることができないとも言われている[25]. また, 生成されるキャリアが非常 に高いエネルギーを持つため, ホットキャリアによる性能の劣化も問題となる [26]. このため, より低い電圧でアバランシェ降伏を起こす材料を用いた I-MOS の開発が課題となっている.

Gate

D

S

F

elec

16

図1.17 I-MOS の動作原理. (a) I-MOS の構造図, (b) 動作時のバンド図.

<フローティングボディ効果を利用した Steep SS SOI MOSFET>

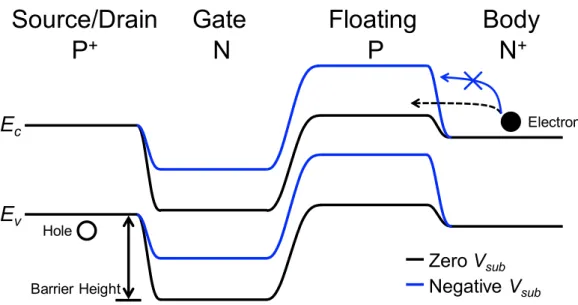

1.3.4 項で説明した SOI MOSFET のチャネル下部ボディ領域は Box 層で基板 と分離されているため, 電位が固定されていない. これにより, ボディの電位は 周囲の容量, pn 接合, インパクトイオン化電流や, 動作履歴によって変動する. NMOS を例にとると, 図 1.18 で示すように, ドレイン近傍でインパクトイオ ン化によって発生した正孔はボディ下部の中性領域へ蓄積する. 蓄積した正孔 は, ボディ領域の電位を正方向へ変動させる. これにより, ドレイン電流は増大 し, インパクトイオン化による正孔の蓄積もまた増大するといった正のフィー ドバックが発生する. この現象はフローティングボディ効果 (Floating Body Effect: FBE)と呼ばれ, キンク現象や, 寄生バイポーラトランジスタ (Parasitic Bipolar Transistor : PBT) によるブレークダウン電圧の低下を引き起こす. PBT によるブレークダウン電圧の低下は長らく SOI MOSFET を実用化する際 の問題となっていた. インパクトイオン化電流は MOSFET 中に存在する npn バ イポーラトランジスタのベース電流として働き, 式 1.6 において β(M − 1) = 1 の 条件で無限のフィードバックが発生し, Bulk MOSFET よりさらに低い電圧でブ レークダウンを迎える[27].

𝐼

d=

𝑀

1 − 𝛽(𝑀 − 1)

𝐼

ch Idは観測されるドレイン電流, M はインパクトイオン化係数, β は PBT の電流増(a)

(b)

(1.6)17 幅率, Ichはチャネル電流を示している. FBE によるボディ電位の変動や PBT は, 小さな Vgの変動で通常より大きくポ テンシャルを変動させ, 多くのドレイン電流を流すことに相当する. すなわち, 通常のBulk MOSFET より SS を急峻化させることができる[28]– [37]. ただし, Id– Vg特性にはヒステリシス幅が現れる. 従来これらの現象は抑制されるべき特性として, もしくは, 単トランジスタ DRAM (1-transistor DRAM: 1T-DRAM) の分野において研究されてきた[38]. しか し近年, 急峻な SS を活かした極低消費電力デバイスとしての検討がされている. 例えば, 非常に薄い SOI 膜厚と Box 膜厚を持つ SOI MOSFET を用いたデバイ ス[39], [40]や, Si ナノワイヤとマルチゲートを用いたものなどがある[41]. これらのデバイスはI-MOS より低いドレイン電圧で超急峻な(super-steep)SS を発生させることができる. しかし, それでも 1.0 V を切ることはできていない. これは Si を使用する以上, インパクトイオン化を引き起こすために 1.0 V 程度 の電圧が必要なためである. 今後, デバイスを実用化するに当たり, さらなる低 電圧化へ向けた材料開発やヒステリシス特性を抑える工夫が必要になっている. 図1.18 フローティングボディ効果. (a) 断面図及び (b) バンド図によるキャリ ア蓄積の模式図.

<Band Modulation Device>

ここでは, 以下に示すキャリアの注入と蓄積によってフィードバック現象を 引き起こし, 急峻な SS を引き起こすデバイスを Band Modulation Device[42]とし てまとめて報告する. N+ N+ S G Box Impact Ionization (a) (b)

Source Channel Drain

Electron

Ec

Ev

Hole

18

・Feedback FET (FB-FET)

Feedback FET (FB-FET) [43], [44]の構造を図 1.19(a) に示す. 実際のデバイスは 3D の FinFET 構造だが, ここでは 2D で示す. FB-FET ではまず, sidewall 領域にキ ャリアを蓄積させるプログラミング動作が必要になる. プログラム後の状態で, ゲート電圧を正方向に印加していくと, ソースからドレインに向かって電子が 注入される. ここで, 電子は sidewall 領域に存在するポテンシャルの溝に蓄積す ることになる. 蓄積した電子は sidewall 領域のポテンシャルを負方向へ変動させ, ドレインとsidewall 領域間のポテンシャル障壁を低下させる. これにより, ドレ インからソースに向かって正孔が注入され, これもまた, sidewall 領域に蓄積し, ポテンシャルを正方向へ変動させる. これらが繰り返されること, すなわち正 フィードバックが発生することで, ポテンシャル障壁が無くなり, ドレイン–ソ ース間に電流が流れる(図1.19(b)). FB-FET では super-Steep SS が得られるが, サイドウォールにキャリアが蓄積 されるため, オフ状態からオン状態へ移行する場合と, オン状態からオフ状態 へ移行する場合で, キャリアの蓄積状況が異なるため, ヒステリシス特性が発 生する.

図 1.19 FB-FET の動作原理. (a) FB-FET の構造図, (b) フィードバック発生の 原理. S G D i N+ P+ G Sidewall (a) (b) Ec Ev Ec Ev Electron Hole

19

・Z2-FET

Z2-FET[45]は FB-FET に似たフィードバックを用いる原理で super-steep SS を

引き起こすデバイスである. 図 1.20(a) に構造図を示す. デバイスは SOI 基板を 用いて作られ, ソースに対してゲートがオフセットを取る形で設けられている. また, Box 側をバックゲートとして使用することで, オフセット部分にポテンシ ャルの溝を作り出す. フィードバックの原理は FB-FET と似ており, 図 1.19(b) で示すように, ドレインから電子がオフセット領域に注入され, ポテンシャル が変動し, それによってソースからホールがゲート領域に注入される形でフィ ードバックが発生し, 急峻な SS が引き起こされる. Z2-FET もまたヒステリシス 特性を持ち, スイッチングデバイスとして使用する場合は問題点となるが, キ ャリアの蓄積を利用した 1T-DRAM での活用をメインとして検討されている [46]–[53].

図1.20 Z2-FET の動作原理. (a) Z2-FET の構造図, (b) 動作時のバンド図.

・その他のBand Modulation Device

その他にも, 類似のデバイス構造及び原理で動作する Field Effect Diode (FED) [54], Gated-thyristor[55], NAND String 上で同様のメカニズムによる super-steep SS を実現するデバイス[56]が報告されている. 一部デバイスは steep SS を活用した 低消費電力化より, 静電破壊対策用ダイオードや 1T-DRAM への応用を目的とし て研究されている.

<steep SS デバイスのまとめ>

20

SS デバイスの中でも精力的に研究されており, シミュレーションでは優れた特 性を示しているが, 実測ではまだ十分な特性に至っていない. TFET は steep SS と 高いオン電流の両立, NCFET は動作スピードの懸念がある点を解決しなければ ならない. ReFET と MEM logic switch はヒステリシス特性が無視できないと考え られる. I-MOS は非常に高い Vdが必要であることがネックである. FBE を利用し

たsteep SS SOI MOSFET は I-MOS よりは低い Vdでsuper-steep SS を引き起こせ

るのが魅力だが, 1.0 V を切るのは難しいと考えられる. FB-FET や Z2-FET は super-steep SS が得られるものの, やはり 1.0 V 以上の Vdとヒステリシス特性を 持っている. また, いくつかのデバイスは左右非対称構造をしている. これは, CMOS を構成する際に, 今までの MOSFET とは異なる回路で設計しなければな らず, 単純な置き換えができないないことを意味する. いずれのデバイスも 60 mV/dec を切る SS は確認できているものの, まだ解決すべき課題が残っている のが現状である. 表1.2 Steep SS デバイスの比較表. 1.4 RF-EH 用整流デバイスの実現へ向けた取り組みと課題 図1.1 で示したように, 極低消費電力 LSI は EH レベルのエネルギーで動かす ことが想定されている. EH の手法は様々なものが提案されているが[57], ここで はRF-EH に着目する. RF-EH は, 他の EH 技術と比較して, 広範囲にエネルギー 源が存在する上, 非接触で電力を集めることができるため, 有望な EH 手法の一

Tunnel FET Negative capacitance FET Resistive-gate FET MEM logic switch I-MOS SOI MOSFET

using FBE Feedback FET Z2-FET SSmin 21 mV/decgood 24 mV/decgood 8 mV/decexcellent < 0.1 mV/decexcellent 5.88 mV/decexcellent 0.058 mV/decexcellent 2 mV/decexcellent < 1 mV/decexcellent

Vd 0.1 Vlow 0.2 Vlow not enough1.0 V very low10 mV 5.76 V ※3 very high 1.3 V not enough 1.2 V not enough 1.5 V not enough Ion 1×10 -9 A/μm low 8×10–7 A/μm not enough 6×10–5 A/μm good 1×10–5 A※2 good 4×10–5 A/μm good 1×10-4 A/μm good 1×10-4 A/μm good 5×10-4 A/μm good Ioff < 1×10 -15 A/μm low 4×10–15 A/μm low 1×10–7 A/μm high < 1×10–14 A※2 low 1×10–9 A/μm high 1×10–12 A/μm low 5×10–12 A/μm low 1×10–11 A/μm low Hysteresis none 20 mV negligible significant※1 1.0 V significant none 2 mV negligible 0.18 V with with※4 S/D asymmetry symmetry symmetry symmetry asymmetry symmetry asymmetry asymmetry

Ref. [13] [18] [20] [21] [24] [39] [43] [45] Comment 高いIonと急峻 なSSを両立す るデバイスの 作成はまだで きていない 動作スピード に関する懸念 あり ゲートに適し たMIM層の材 料開発が課題 ヒステリシス 特性と機械的 強度の問題あ り アバランシェ 降伏を起こす ためにに高い 電圧が必要 I-MOSより低い Vdだが、Siで 1.0 Vを切るの は難しい ヒステリシス 特性とプログ ラミング動作 が必要な問題 あり 1T-DRAMへの 応用が主に検 討されている ※1: 論文中にヒステリシス特性の情報は載っていないが、set/reset特性から、大きなヒステリシス特性が発生すると予想される ※2: 総コンタクト面積は 8 μm2 ※3: Vs = –5.75 V, Vd = 0.1 V ※4:ヒステリシス特性の情報は載っていないが、Id–Vd特性がヒステリシス特性を持っていることから、Id–Vg特性も ヒステリシス特性を持っていると予想される

21 つである. しかし, 得られる電力は非常に小さいと予測される. 図 1.21 に Friis の伝達公式[58]から計算された受電電力の電波塔からの距離依存性を示す. 電波 塔から距離が離れると, 得られる電力は μW レベル以下に減少する. RF-EH はレ クテナと呼ばれるアンテナと整流回路を組み合わせたもの(図1.22)で行うこと が想定される. すなわち, RF-EH で最も重要な問題は極低入力電力を如何に高効 率で受電, 整流するかである. 図 1.21 Friis の伝達公式を用いて計算された各種 RF 電源(地上デジタル (DTTV), 携帯電話, Wi-Fi)における受電電力の距離依存性. 図1.22 レクテナの模式図. 1E-6 1E-4 1E-2 1E+0 1E+2 1E+4 1E+6 1E+8 1 10 100 1000 10000 R ec ei ve d Po w er (μ W ) Distance (m) DTTV Cellular phone Wi-Fi 1

Load

(e.g. LSI)

Antenna

Rectification Circuit

22 1.4.1 Hi-Z アンテナ 整流効率を上げるために, アンテナ部で昇圧を行い, ダイオードへの入力電 圧を増加させる研究がされている. 例えばアンテナのインダクタンスと整流器 の寄生容量との共振を使用する方法[59]や, 高インピーダンス(Hi-Z)アンテナ を備えたレクテナ[60]が提案されている. ここでは Hi-Z アンテナによる電圧増 幅に関して説明を行う. 図1.23 は, Hi-Z アンテナを用いて−30 dBm 及び−40 dBm を増幅した際の出力 電圧の計算結果を示している. 入力電圧は, 1 kΩ–10 kΩ のアンテナによって約 50 mV へ増幅できることが分かる. これは, 標準的な 50 Ω アンテナの場合の 10 mV よりも大幅に改善されている. 例えば先行研究では, 図 1.24 に示す MOS ダイオ ードと2 kΩ の Hi-Z アンテナを組み合わせて−30 dBm でおよそ 10 %の整流効率 を実現している[61]. しかし, 50 mV でも高効率化のためには依然として非常に 低い電圧である. 図1.23 Hi-Z アンテナによる受電電圧の増幅.

0.001

0.01

0.1

1

10

100

1000

10000

100000

In

pu

t

V

ol

ta

ge

t

o

di

od

e

(V

)

Antenna Impedance (Ω)

-30dBm

-40dBm

50mV

23 図1.24 Hi-Z アンテナを用いたレクテナ. 1.4.2 従来型ダイオードの理論限界 微小な電圧で整流を行うには, ダイオードの I–V 特性における非線形性が重 要にな る. 良く使 用さ れる ダイオ ードの 性能 指数の 一つ に曲 率 (curvature coefficient) γ が存在し, 以下の式 1.7 で表される[62], [63].

γ ≡

𝑑

2𝐼/𝑑𝑉

2𝑑𝐼/𝑑𝑉

γ はダイオードの応答性を示し, 大きいほど微小な電圧で非線形に電流が変化す る, すなわち, 整流効率が上がることを意味する. 図 1.25 に従来型ダイオードの I–V 特性を示す. 従来型の PN ダイオード及びショットキーバリアダイオード(Schottky Barrier Diode: SBD)は 0 V 付近の非線形領域における電流が熱拡散機構 によるため, γ が q/nkT で与えられる. 室温において理想的な pn 接合(n = 1) のと き, γ は 40 V-1となり, これが理論限界になってしまう.

Hi-Z Antenna

Rectifier

24 図1.25 従来型ダイオードの 0 V 付近における γ. 1.4.3 ゼロバイアスダイオード 高い整流効率を備えたレクテナを開発するには, ターンオン電圧がほぼゼロ の新しいダイオード機構が必要である. これはゼロバイアスダイオードと呼ば れ, トンネル現象を利用したデバイスが提案されている. 図 1.26(a) で示すよう に, pn 接合に逆方向バイアスを印加すると, 接合部が高電界化し, トンネル電流 が流れる. ここで適切なバンドエンジニアリングを行うことにより, I–V 特性は 図 1.26(b) で示すように, 逆方向バイアスで急峻にオン状態となり, 熱拡散機構 で動作するダイオードを超える γ を得ることができる. トンネル現象を利用し たダイオードとしては, トンネルダイオード[64]が有名だが, EH 用のゼロバイア スダイオードでも同様の現象を利用する試みがなされている, 例えば Backward Tunnel Diode は, III-V 材料を使用したヘテロ構造のダイオードで, 40 V-1を超え

るγ を得ている[65]. また, シミュレーションベースでは, Band-to-Band Tunneling

Diode の名前で, pn ダイオードの接合部を極急峻に作り, 濃度を厳密に調整する ことで, 低電圧範囲において高効率整流ができる可能性を示唆している[66]. さ らには, steep SS デバイスである TFET を用いた EH 用整流回路が検討されてい る[67], [68]. しかし, Backward Tunnel Diode は Si 以外の材料を使用することによ

I

V

Theoretical Limit25 る製造コストの問題, 残りのデバイスはまだシミュレーションでしか特性を確 認できていないという問題がある. また, それらの整流特性は極低入力電力に 対しては依然として不十分である. 図1.26 トンネル現象を利用したゼロバイアスダイオード. (a) バンド図, (b) 期 待されるI–V 特性. 1.5 研究内容 ここまで, 極低電力用 LSI 及び RF-EH に関するこれまでの取り組みと課題に 関して述べた. いずれにおいてもこれまで使用してきた従来型 MOSFET 及びダ イオードに理論限界が存在し, それを超えるべく, 電流伝導が熱拡散機構に依 らない新原理デバイスの開発が必要になっている. 本論文では先行研究におけ る問題点を解決すべく, 新しいデバイス候補として“PNBT SOI-FET”を提案, 作 製する. PNBT SOI-FET は左右対称形のデバイスで, 従来型の MOSFET と同じ Si CMOS プロセスで作製することが可能である. また, 物理現象の詳細な解明, 各 種パラメータ依存性の検討及び特性改善を目的として, シミュレーションによ る解析を行う. 加えて, PNBT SOI-FET を用いた RF-EH 用極低電圧整流ダイオー ドを検討する. 1.6 論文の構成 本論文は以下の内容で構成されている. Ec Ev Electron I V (a) (b) γ > 40 V-1

26

第1 章では序論として, 極低消費電力 LSI, RF-EH の必要性と, 従来型 MOSFET 及びダイオードの理論限界, それらを克服するための新原理デバイスを紹介し, 本研究の内容について述べた. 第 2 章では本論文中で使用するデバイスの作製方法とデバイスシミュレーシ ョン方法に関して説明する. 第3 章では PNBT SOI-FET の構造とその特性に関して説明する. まず, シミュ レーションによって PNBT SOI-FET はインパクトイオン化を用いることなくキ ャリアをチャネル下部へ注入してフローティングボディ効果を引き起こすこと が可能であることを示す. さらに, サイリスタ動作によるフィードバックがメ カニズムの主要因であることを提案する. また, 実デバイス上で p/n-channel と もにsteep SS が発生することを確認する. 第4 章では第 3 章の結果を受けたシミュレーションによる PNBT SOI-FET 特 性改善検討について述べる. シミュレーションでは, モデルパラメータのフィ ッティングによって, より実測に近いシミュレーションが可能であることを示 す. また, PNBT SOI-FET のスケーリング性及び, 不純物濃度のパラメータを最 適化することにより特性が改善可能であることを示す. 第5 章では PNBT SOI-FET を用いた RF-EH 用デバイスの検討について述べる. RF のような非常に小さいエネルギーを使用した EH においても優れた整流効率 を出せる整流器を目指し, ダイオード接続した PNBT SOI-FET を検討, 極低入力 電圧でも整流可能なデバイスを実証する. 第6 章では結果をまとめ, 今後の展望について述べる.

27 1.7 参考文献

[1] (2017). IRDS Report. [Online]. Available: http://irds.ieee.org/reports (アクセス 日: 2019/2/26)

[2] International Technology Roadmap for Semiconductors (ITRS) [Online].

Available: http://www.itrs2.net/itrs-reports.html (アクセス日: 2019/2/26) [3] K. Takeuchi, and T. Mogami, “A new multiple transistor parameter design

methodology for high speed low power SoC's,” IEDM tech. dig., Dec. 2001, pp. 515–518.

[4] 内田 建, 杉井信之, 竹内 潔, 集積ナノデバイス, 平本俊郎 (編), 丸善 出版株式会社, 東京, 2009, pp. 141–147.

[5] R. H. Dennard, F. H. Gaensslen, V. L. Rideout, E. Bassous, and A. R. LeBlanc, “Design of ion-implanted MOSFET's with very small physical dimensions,”

IEEE Journal of Solid-State Circuits, vol. SC-9, no. 5, pp. 256–268, Oct. 1974.

[6] T. Kanemura et al., “Improvement of Drive Current in Bulk-FinFET using Full 3D Process/Device Simulations,” 2006 International Conference on Simulation

of Semiconductor Processes and Devices, Monterey, CA, 2006, pp. 131–134.

[7] T. Chiarella, L. Witters, A. Mercha, C. Kerner, M. Rakowski, C. Ortolland, L.-Å. Ragnarsson, B. Parvais, A. De Keersgieter, S. Kubicek, A. Redolfi, C. Vrancken, S. Brus, A. Lauwers, P. Absil, S. Biesemans, and T. Hoffmann, “Benchmarking SOI and bulk FinFET alternatives for PLANAR CMOS scaling succession,” Solid-State Electronics, vol. 54, no. 9, pp. 855–860, May 2010. [8] T. Takahashi, N. Beppu, K. Chen, S. Oda, and K. Uchida, “Self-heating effects

and analog performance optimization of fin-type field-effect transistors,”

Japanese Journal of Applied Physics, vol. 52, no. 4S, pp. 04CC03-1–04CC03-6,

Feb. 2013.

[9] A. R. Brown, N. Daval, K. K. Bourdelle, B. Nguyen and A. Asenov, “Comparative Simulation Analysis of Process-Induced Variability in Nanoscale SOI and Bulk Trigate FinFETs,” IEEE Transactions on Electron Devices, vol. 60, no. 11, pp. 3611–3617, Nov. 2013.

[10] T. B. Hook et al., “SOI FinFET versus bulk FinFET for 10nm and below,” 2014

SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S),

Millbrae, CA, 2014, pp. 1–3.

[11] Y. Morita, T. Mori, S. Migita, W. Mizubayashi, A. Tanabe, K. Fukuda, T. Matsukawa, K. Endo, S. O’uchi, Y. X. Liu, M. Masahara, and H. Ota, “Performance enhancement of tunnel field-effect transistors by synthetic Electric field effect,” IEEE Electron Device Lett., vol. 35, no. 7, pp. 792–794, Jul. 2014.

28

[12] A. M. Ionescu, and H. Riel, “Tunnel field-effect transistors as energy-efficient electronic switches,” Nature, vol. 479, pp. 329–337, Nov. 2011.

[13] K. Tomioka, M. Yoshimura, and T. Fukui, “Steep-slope tunnel field-effect transistors using III–V nanowire/Si heterojunction,” in VLSI Tech. Dig., Jun. 2012. pp. 47–48.

[14] H. Lu, and A. Seabaugh, “Tunnel field-effect transistors: State-of the-art,” IEEE

J. Electron Devices Soc., vol. 2, no. 4, pp. 44–49, Jul. 2014.

[15] T. Mori, W. Mizubayashi, Y. Morita, S. Migita, K. Fukuda, N. Miyata, T. Yasuda, M. Masahara, and H. Ota, “Effect of hot implantation on ON-current enhancement utilizing isoelectronic trap in Si-based tunnel field-effect transistors,” Appl. Phys. Express, vol. 8, no. 3, pp. 036503-1–036503-3, Feb. 2015.

[16] S. Salahuddin, and S Datta, “Use of negative capacitance to provide voltage amplification for low power nanoscale devices,” Nano Lett., vol. 8, no. 2, pp. 405–410, Dec. 2007.

[17] K. S. Li, P.-G. Chen, T.-Y. Lai, C. H. Lin, C.-C. Cheng, C.-C. Chen, Y.-J. Wei, Y.-F. Hou, M.-H. Liao, M.-H. Lee, J.-M. Sheih, W.-K. Yeh, F.-L. Yang, S. Salahuddin, and C. Hu, “Sub-60mV-swing negative-capacitance FinFET without hysteresis,” in IEDM Tech. Dig., Dec. 2015, pp. 620–623.

[18] C.-C. Fan, C.-H. Cheng, Y.-R. Chen, C. Liu, and C.-Y. Chang, “Energy-efficient HfAlOx NCFET: Using gate strain and defect passivation to realize nearly

hysteresis-free sub-25mV/dec switch with ultralow leakage,” in IEDM Tech.

Dig., Dec. 2017, pp. 561–564.

[19] B. Obradovic, T. Rakshit, R. Hatcher, J. A. kittl, and M. S. Rodder, “Ferroelectric Switching Delay as Cause of Negative Capacitance and the Implications to NCFETs,” in Symp. on LVSI Tech. Dig., Jun. 2018, pp. 51–52.

[20] Q. Huang, R. Huang, Y. Pan, S. Tan, and Y. Wang, “Resistive-gate field-effect transistor: A novel steep-slope device based on a metal-insulator-metal-oxide gate stack,” IEEE Electron Device Lett., vol. 35, no. 8, pp. 877–879, Aug. 2014. [21] R. Nathanael, V. Pott, H. Kam, J. Jeon, and T.-J. K. Liu, “4-terminal relay technology for complementary logic,” in IEDM Tech. Dig., Dec. 2009, pp. 1–4. [22] T.-J. K. Liu, J. Jeon, R. Nathanael, H. Kam, V. Pott, and E. Alon, “Prospects for

MEM logic switch technology,” in IEDM Tech. Dig., Dec. 2010, pp. 424–427. [23] K. Gopalakrishnan, P. B. Griffin, and J. D. Plummer, “IMOS: A novel

semiconductor fevice with a subthreshold slope lower than kT/q,” in IEDM tech.

29

[24] E. Toh, G. H. Wang, L. Chan, G. Samudra and Y. Yeo, "A double-spacer I-MOS transistor with shallow source junction and lightly doped drain for reduced operating voltage and enhanced device performance," IEEE Electron Device

Letters, vol. 29, no. 2, pp. 189–191, Feb. 2008.

[25] A. Savio, S. Monfray, C. Charbuillet, and T. Skotnicki, “On the limitations of silicon for I-MOS integration,” IEEE Trans. Electron Devices, vol. 56, no. 5, pp. 1110–1117, May 2009.

[26] K. Gopalakrishnan, R. Woo, C. Jungemann, P. B. Griffin, and J. D. Plummer, “Impact ionization MOS (I-MOS)—Part II: Experimental results,” IEEE Trans.

Electron Devices, vol. 52, no. 1, pp. 77–84, Jan. 2005.

[27] 吉見 信, SOI デバイス技術 –実践的基礎と応用-, ED リサーチ社, 東京, 2005, pp. 24–31.

[28] J. R. Davis, A. E. Glaccum, K. Reeson, and P. L. F. Hemment, “Improved Subthreshold Characteristics of n-Channel SOI Transistors,” IEEE Electron

Device Lett., vol. EDL-7, no. 10, pp. 570–572, Oct. 1986.

[29] J. G. Fossum, R. Sundaresan, and M. Matloubian, “Anomalous Subthreshold Current-Voltage Characteristics of n-Channel SOI MOSFET’s,” IEEE Electron

Device Lett., vol. EDL-8, no. 11, pp. 544–546, Nov. 1987.

[30] B.-Y. Mao, R. Sundaresan, C.-E. D. Chen, M. Matloubian, and G. Pollack, “The Characteristics of CMOS Devices in Oxygen-Implanted Silicon-on-Insulator Structures,” IEEE Trans. Electron Devices, vol. 35, no. 5, pp. 629–633, May 1988.

[31] C.-E. D. Chen, M. Matloubian, R. Sundaresan, B.-Y. Mao, C. C. Wei, and G. P. Pollack, “Single-Transistor Latch in SOI MOSFET’s,” IEEE Electron Device

Lett., vol. 9, no. 12, pp. 636–638, Dec. 1988.

[32] J. R. Davis, G. A. Armstrong, N.J. Thomas, and A. Doyle, “Thin-film SOI CMOS transistors with p+-Poly silicon gates,” IEEE Trans. Electron Devices,

vol. 38, no. 1, pp. 32–38, Jan. 1991.

[33] J.-Y. Choi, and J. G. Fossum, “Analysis and control of floating-body bipolar effect in fully depleted submicrometer SOI MOSFET’s,” IEEE Trans. Electron

Devices, vol. 38, no. 6, pp. 1384–1391, Jun. 1991.

[34] J. Gautier, and A.-J. A.-Herve, “A Latch Phenomenon in Buried N-Body SOI NMOSFET’s,” IEEE Electron Device Lett., vol. 12, no. 7, pp. 372–374, Jul. 1991. [35] J. S. T. Huang, J.S. Kueng, and T. Fabian, “An Analytical Model for Snapback

in n-Channel SOI MOSFET's,” IEEE Trans. Electron Devices, vol. 38, no. 9, pp. 2082–2091, Sep. 1991.

30

[36] T.-D. Her, P. S. Liu, D. S. Quon, G. P. Li, R. Kjar, and J. White, “Parasitic bipolar transistor induced latch and degradation in SOI MOSFET’s,” in IEEE Int. SOI

Conf., pp. 124–125, Oct. 1991.

[37] M. A. Pavanello, J. A. Martino, and D. Flandre, “Graded-channel fully depleted Silicon-On-Insulator nMOSFET for reducing the parasitic bipolar effects,”

Solid-State Electron., vol. 44, no. 6, pp. 917–922, Jun. 2000.

[38] M. Jurczak, “Memories on SOI: Floating Body Cell Memory,” Training Course

EUROSOI, Granada, Jan. 2011.

[39] Z. Lu, N. Collaert, M. Aoulaiche, B. De Wachter, A. De Keersgieter, J. G. Fossum, L. Altimime, and M. Jurczak, “Realizing super-steep subthreshold slope with conventional FDSOI CMOS at low-bias voltages,” in IEDM Tech. Dig. Dec. 2010, pp. 16.6.1–16.6.3.

[40] J. G. Fossum, and Z. Lu, “Anomalous floating-body effects in SOI MOSFETs: low-voltage CMOS?,” in IEEE Int. SOI Conf., Oct. 2011, pp. 1–2.

[41] K. Nishiguchi, and A. Fujiwara, “Nanowire metal-oxide-semiconductor field-effect transistors with small subthreshold swing driven by body-bias field-effect,”

Appl. Phys. Express, vol. 5, no. 8, pp. 080052-1–080052-3, Aug. 2012.

[42] S. Cristoloveanu, J. Wan and A. Zaslavsky, "A Review of Sharp-Switching Devices for Ultra-Low Power Applications," in IEEE Journal of the Electron

Devices Society, vol. 4, no. 5, pp. 215-226, Sep. 2016.

[43] A. Padilla, C. W. Yeung, C. Shin, C. Hu, and T.-J. K. Liu, “Feedback FET: A novel transistor exhibiting steep switching behavior at low bias voltages,” in

IEDM Tech. Dig., Dec. 2008, pp. 171–174.

[44] C. W. Yeung, A. Padilla, T.-J. K. Liu, and C. Hu, “Programming characteristics of the steep turn-on/off feedback FET (FBFET),” in Symp. on LVSI Tech. Dig., Jun. 2009, pp. 176–177.

[45] J. Wan, S. Cristoloveanu, C. L. Royer, and A. Zaslavsky, “A feedback silicon-on-insulator steep switching device with gate-controlled carrier injection,” Solid

State Electron., vol. 76, pp. 109–111, Oct. 2012.

[46] J. Wan, C. L. Royer, A. Zaslavsky, and S. Cristoloveanu, “Progress in Z2-FET 1T-DRAM: Retention time, writing modes, selective array operation, and dual bit storage,” Solid State Electron., vol. 84, pp. 147–154, Jun. 2013.

[47] J. Wan, C. L. Royer, A. Zaslavsky, and S. Cristoloveanu, “A systematic study of the sharp-switching Z2-FET device: From mechanism to modeling and compact

memory applications,” Solid State Electron., vol. 90, pp. 2–11, Dec. 2013. [48] Y. Taur, J. Lacord, M. S. Parihar, J. Wan, S. Martinie, K. Lee, M. Bawedin, J.-C.