平成

30 年度 修士論文

スイッチング電源の

EMI ノイズ拡散と

それに伴う出力リプル増大対策における実装評価

指導教員 髙井 伸和 准教授

群馬大学大学院 理工学府理工学専攻

電子情報・数理教育プログラム

T171D081

三木 夏子

1

目次

第1 章 序論 ... 3 1.1 研究背景及び目的 ... 3 1.2 本論文の構成 ... 4 第2 章 スイッチング電源 ... 5 2.1 概要 ... 5 2.2 降圧形コンバータ ... 6 2.3 各種制御方式 ... 7 2.3.1 電圧モード制御 ... 8 2.3.2 電流モード制御 ... 9 2.3.3 リップル制御 ... 10 2.4 状態平均化法によるコンバータの解析 ... 11 2.4.1 状態平均化方程式の導出 ... 11 2.4.2 定常状態近傍での小信号解析... 16 2.4.3 周波数領域への変換 ... 16 2.4.4 一巡伝達関数の導出 ... 19 第3 章 EMI ノイズ及び低減手法 ... 25 3.1 電源回路性能とは ... 25 3.2 EMI ノイズ ... 28 3.3 EMI ノイズ低減手法 ... 28 3.3.1 M 系列回路を用いた擬似アナログ信号による方式 ... 29 3.3.2 クロック周波数スイープ方式(従来手法) ... 32 3.3.3 補正電流による出力リプル低減方式(提案手法) ... 35 第4 章 従来及び提案手法を用いたシミュレーション検証と基板実装評価 ... 39 4.1 シミュレーションにおける検証 ... 39 4.1.1 従来手法 ... 39 4.1.2 提案手法 ... 44 4.2 基板実装回路における検証 ... 48 4.2.1 従来手法 ... 51 4.2.2 提案手法 ... 53 4.3 まとめと今後の課題 ... 562

参考文献 ... 59 謝辞 ... 60 本研究に関する成果 ... 61

3

第1章 序論

1.1 研究背景と目的

一般に電源と呼ばれるものには家庭内コンセントや電池、バッテリーなど様々なものが 存在するが、それらの電源は直流や交流、高電圧や低電圧、安定や不安定などとその形態も 様々である。よって、これらの電源をすべての電子機器に直接用いることはできず、誤った 接続すると誤動作や故障の原因となってしまう。これより、電源から各電子機器が必要とす る電圧に変換して安定供給しなければいけない。その役割を果たすのが電源回路である。電 源回路は大別するとシリーズレギュレータとシャントレギュレータ、スイッチングレギュ レータの 3 つに分類することができる。シリーズレギュレータは負荷に対して直列に電力 制御素子を接続することで降圧動作が可能となり、リプルノイズが少ないという利点を持 つが、効率が非常に悪い。シャントレギュレータは負荷に対して並列に電力素子を接続した 場合であり、過電流保護回路が不要であるという利点を持つが、シリーズレギュレータと同 様に効率が悪い。スイッチングレギュレータは半導体素子をスイッチとして使用しており、 このON/OFF 動作によって最小の損失で電力の流れを制御することを基本としている。ま た、インダクタやコンデンサなどの受動素子が使われるが、周波数を高くすることによって 小型化が可能となる。これより、抵抗で熱として電力を消費させ目的の電圧を得るシリーズ レギュレータなどと比較し、高効率化が実現される。さらに、近年のMOS の微細化や集積 回路の発展等の影響を受け、電源回路にも高効率化・小型化が要求されていることから現在 ではスイッチングレギュレータが注目され、多く用いられている。しかし、スイッチングレ ギュレータも利点だけではない。シリーズレギュレータなどではノイズがほとんど発生し ないのに対して、スイッチングレギュレータではスイッチのON/OFF 切り替え時に電磁妨 害(Electro Magnetic Interference : EMI)ノイズが発生するという問題がある。この EMI ノ イズは周辺の電子機器に干渉し、誤動作や機器の損壊等の悪影響を及ぼす可能性がある。こ のためEMI ノイズの国際規格を作成する CISPR などの様々な規格が存在している3)。デ ィジタル家電や自動運転車などの普及によって通信機器が増えるのに従って、EMI ノイズ への規制が強くなるためEMI ノイズの対策方法に注目が集まっている。 EMI ノイズ対策の 1 つにスペクトラム拡散としてクロック周波数スイープ方式が挙げら れる。この方法を使うことで、通常はある周波数(クロック周波数)に集まっているエネル ギーを他の周波数帯にも分散させることでエネルギーの総量は変化しないものの、EMI ノ イズの最大値を低減させることができる。これによってEMI ノイズの規制規格をクリアす ることが期待できるとともに、この方式は使用する部品も少なく、リニア掃引であることか ら変化が定量的であるという利点を持つ。しかし、この方法では電源性能の重要な 1 つで ある出力電圧リプルが増大してしまうという、トレードオフの問題があった。そこでこの問4 題の原因を解明し、解決法として先ほどの方式に電流補正を行う簡単な回路を追加するこ とでEMI ノイズ低減と出力電圧リプル増大のトレードオフ問題解消を試みた。本研究では、 これらのEMI ノイズ低減手法において、シミュレーション解析及び基盤実装回路測定を行 い各手法の優位性等を確認する。

1.2 本論文の構成

まず第 2 章ではスイッチング電源の基本的な回路として降圧型 DC-DC コンバータを例 にとり、基本動作と各制御方式について述べる。第 3 章では電源回路を評価するための基 準となる電源性能について紹介し、さらにEMI ノイズについての概要と各低減手法につい て説明する。第4 章では第 3 章で述べた従来手法及び提案手法においてシミュレーション 及び基板実装測定を行った結果について述べる。5

第 2 章 スイッチング電源

2.1 概要

スイッチング電源(switched-mode power supply)は MOSFET やトランジスタなどとい った半導体素子をスイッチとして用い、その半導体スイッチのON/OFF による時比率(デュ ーティー)を制御することによって電力の流れを調整する電源方式である。この方式では、 半導体スイッチが飽和領域と遮断領域で動作しているため、能動領域で動作するシリーズ ドロッパ電源(series dropper power supply)に比べて半導体素子における損失が少なく、効 率が高い。また、平滑用のインダクタ、コンデンサなどの部品は、周波数を上昇させること によって小型化できるため、スイッチング電源は小型・軽量・高効率な電源として、従来の シリーズ電源の代わりに、あらゆる電子機器に使用されている。図2.1 にスイッチングレギ ュレータの基本構成をブロック図で示す。直流入力電圧𝑉𝑖𝑛が DC-DC コンバータに入力さ れ、任意の直流出力電圧𝑉𝑜に変換される。その出力電圧𝑉𝑜がエラーアンプに入力され基準電 圧𝑉𝑟𝑒𝑓と比較され、その誤差電圧を検出する。その誤差電圧と鋸歯状波(sawtooth)をコンパ レータによって比較することで、誤差電圧を抑えるように出力電圧を調整する。また、この ス イ ッ チ ング 電 源 の出力 電 圧 を 制御 す る 方式と し て 主 にパ ル ス 幅変調(Pulse Width Modulation:PWM)とパルス周波数変調(Pulse Frequency Modulation:PFM)の 2 種類が主 流となっている。PWM 方式はスイッチング周波数(周期)が一定であり、スイッチの ON/OFF 時間比を調整することで安定化を行っている。一方で、PFM 方式はスイッチの ON/OFF 時間比は一定であり、スイッチング周波数(周期)を変動させる方式である。一 般に、PWM 方式が多く用いられているが、低負荷時などには PFM 方式も利用されている。 なお、本研究においては前者のPWM 方式を用いていくものとする。さらに、PWM 方式は 電圧モード制御や電流モード制御、リップル制御などの制御方法が用いられる。 これより、本章では降圧型DC-DC コンバータの基本動作を例に、各種制御方式における 動作原理について説明していく。

6 図2.1 スイッチングレギュレータのブロック図

2.2 降圧形コンバータ

DC-DC コンバータのうちで最も基本的な回路はトランスを除く基本要素によって構成さ れているチョッパ方式の降圧型、昇圧型及び昇降圧型DC-DC コンバータである。降圧型は 入力電圧に対して低い電圧、つまり降圧した電圧を出力し、昇圧型では逆に入力電圧に対し て高い電圧、昇圧した電圧を出力する。これより、昇降圧型は入力電圧に対して降圧又は昇 圧した電圧を出力する回路となる。本節では、この中でも最も一般的に用いられる降圧形 DC-DC コンバータを例に動作原理を説明する。なお、ここでは簡単化の為、スイッチは理 想的な場合であるとし、その他すべての回路素子の内部抵抗等の寄生容量についても考慮 しないものとすると共にインダクタに流れる電流は連続的であると仮定する。 降圧型DC-DC コンバータの回路図を図 2.2 に示し、その動作波形を図 2.3 に示す。図 2.2 において、スイッチSW が ON の場合の電流の流れを実線で OFF の場合の電流の流れを破 線で示している。図2.3 の SW’は図 2.2 における SW の ON/OFF を制御する PWM 信号で あり、SW 直前の信号を示している。また、𝐼𝐿はインダクタに流れる電流、𝑉𝐿はインダクタ の両端電圧、𝑉𝑜は出力電圧を示している。ここで、PWM 信号が High=SW:ON、PWM 信号 Low=SW:OFF とする。図 2.2 の動作は次の通りである。まず、PWM 信号が High になる とSW:ON となり、入力電圧 𝑉𝑖よりインダクタL を介してコンデンサ C 及び負荷抵抗 R に電圧が供給される。インダクタに電圧がかかると、電気エネルギーが磁気エネルギーに変 換され、電流は時間に対して直線的に増加する。このとき、出力電圧 𝑉𝑜はインダクタL に 電圧がかかっていることから入力電圧 𝑉𝑖よりも低くなる。また、コンデンサC は出力電圧 𝑉𝑜により充電されるので、両端電圧は 𝑉𝑜となる。次に、PWM 信号が Low になると SW:OFF となるが、インダクタ L に流れる電流は急にゼロにはならないため、蓄積されて いた磁気エネルギーが電気エネルギーとして放電される。このとき、インダクタ L はコン デンサ C の両端電圧𝑉𝑜により磁気エネルギーを電気エネルギーである電流として変換し負7 荷抵抗R へと供給する。以上のように、インダクタ L とコンデンサ C の充放電を利用して 入力電圧𝑉𝑖より低い出力電圧𝑉𝑜得ている。さらにインダクタL に流れる電流が電流連続モー ドだと仮定すると、出力電圧𝑉𝑜は SW の ON/OFF の時間比だけで決定する。 次節では、このコンバータを制御する方式について説明していく。 図2.2 降圧型 DCDC コンバータ回路図 図2.3 降圧型 DCDC コンバータ動作波形

8

2.3 各種制御方式

前節の図2.2 に示した降圧型 DC-DC コンバータは出力電圧𝑉𝑜を一定に制御する機構を持 たず、そのため入出力の変化や部品定数のばらつきなどによる出力電圧𝑉𝑜の変動を是正でき ない。これより、実際のスイッチング電源では出力電圧𝑉𝑜が所望の電圧範囲に収まるよう、 出力電圧𝑉𝑜検出し帰還させるため、図2.1 のブロック図に示すような閉ループとして回路を 構成する必要がある。本節では帰還回路として電圧モード制御、電流モード制御、リップル 制御の3 つの制御方式について紹介する。2.3.1 電圧モード制御

まず、電圧モード制御方式はこの3 つの中で最も基本的な方式であり、図 2.4 に回路構成 を示す。この制御方式は帰還回路を介して出力電圧𝑉𝑜のみを帰還する方式である。帰還の流 れとしてはます、出力電圧𝑉𝑜がエラーアンプの反転入力端子に入力され、基準電圧𝑉𝑟𝑒𝑓と比 較し、その差分として誤差電圧𝑉𝑐が出力される。この誤差電圧𝑉𝑐と発振器より生成された鋸 歯状波 Sawtooth をコンパレータで比較することで PWM のパルス幅が決定され、パワー 段であるコンバータ部分へと帰還される。また、入力電圧𝑉𝑖や負荷電流𝐼𝑜の変動によって出 力電圧𝑉𝑜が変化した場合は、誤差電圧𝑉𝑐が変化し、これにより鋸歯状波Sawtooth と比較す るタイミングも変化するため、PWM の ON 時間が変化する。このためインダクタ L に流 れるリップル電流のON 時間と OFF 時間のバランスが崩れ、結果としてインダクタ電流𝐼𝐿 の平均値が変化することで出力電圧𝑉𝑜が規定の電圧値に収束する。 電圧モード制御方式の応答速度には限界があるが、その理由としてはエラーアンプの位 相補償が存在することによって生じる周波数特性の遅れや、半導体素子のスイッチング動 作 1 周期分に相当する無駄時間遅れなどが挙げられる。この対策として、スイッチング周 波数を高くすることで応答速度の改善が見込めるが、これによってスイッチング損失や EMI ノイズが増えるといった問題も存在する。9 図2.4 電圧モード制御降圧形コンバータ全体回路概略図

2.3.2 電流モード制御

電流モード制御方式は図2.5 に示す回路構成で表される。前項の電圧モード制御方式と比 較すると、回路構成はよく似ているが、電流モード制御方式の場合は制御ループで用いる鋸 歯状をパワー段(コンバータ部分)のスイッチング電流であるインダクタ電流に置き換えた 方式である。従って、帰還回路には電圧ループに加えて電流ループが存在し、コンパレータ の入力としてインダクタ電流と誤差電圧𝑉𝑐の両方を使用する。このインダクタ電流を検出す る方法には、平均電流モード制御、固定ON/OFF 時間制御、ピーク電流モード制御の 3 つ が挙げられ、一般にはピーク電流モード制御が用いられる場合が多い。インダクタ電流が制 御対象として加わる電流モード制御方式は、電流モード制御方式に比べて制御が複雑にな るが、パワー段のポールが1 次少なくなるため、位相補償回路の設計が大幅に簡単になる。10 図2.5 電流モード制御降圧形コンバータ全体回路概略図

2.3.3 リップル制御

リップル制御方式は図2.6 に示す回路構成によって表される。リップル制御方式では、 ヒステリシス特性を持つヒステリシスコンパレータを用いる。ヒステリシスコンパレータ 内には上下2 つの基準値𝑉𝑟𝑒𝑓+と𝑉𝑟𝑒𝑓−が存在する。出力電圧𝑉𝑜がコンパレータの下側基準値 𝑉𝑟𝑒𝑓−を下回るとPWM は High となり SW が ON となるため結果的に出力電圧𝑉𝑜は上昇す る。反対に、出力電圧Voがコンパレータの上側基準値𝑉𝑟𝑒𝑓+を上回るとPWM は Low とな りSW が OFF となるため、出力電圧𝑉𝑜は減少する。以上の動作によって出力電圧𝑉𝑜を監視 し、上下基準値を上回るもしくは下回ることでSW の ON/OFF を制御している。また、リ ップル制御方式では、出力電圧𝑉𝑜と基準値電圧𝑉𝑟𝑒𝑓を直接比較して帰還させるため、エラー アンプを必要としない。よって、回路構成が簡単であると共に、応答速度はパワー段出力部 のLC フィルタで決まるため、優れた応答速度で動作させることが出来る。しかし、この方 式では様々なパラメータの変化によってスイッチング周波数が変動してしまうという欠点 もある。この対策法として、PWM のオン時間を固定にすることで周波数を一定にする COT 方式という新たな方式も開発されている。11 図2.6 リップル制御降圧形コンバータ全体回路概略図

2.4 状態平均化法によるコンバータの解析

本節では状態平均化法を用いて降圧型コンバータの解析を行い、その結果を基に一巡伝 達関数を導出する。スイッチング方式のDC-DC コンバータは、直流電力を得るために低周 波フィルタを用いており、通常この低域通過フィルタの共振周波数に比べて十分高くなる ようスイッチング周波数を設定する。このため、スイッチングの各周期におけるインダクタ 電流及びコンデンサ電圧の変化を直線で近似することが出来る。この場合、1 スイッチング 周期における電流又は電圧の平均値を変数とすることで、非線形回路であるDC-DC コンバ ータを線形回路として取り扱うことができる。このような動作解析手法が状態平均化法で ある。 伝達関数の動作手順としては、スイッチのON 期間と OFF 期間それぞれの状態方程式を 求め、時比率(デューティ)𝐷で加重平均し、状態平均化方程式を求める。それを基に一般 の数学的手法により、定常解近傍における動特性を求め、パワー段の伝達関数を導出すると 共に最終的にコンバータ全体の一巡伝達関数を求める。2.4.1 状態平均化方程式の導出

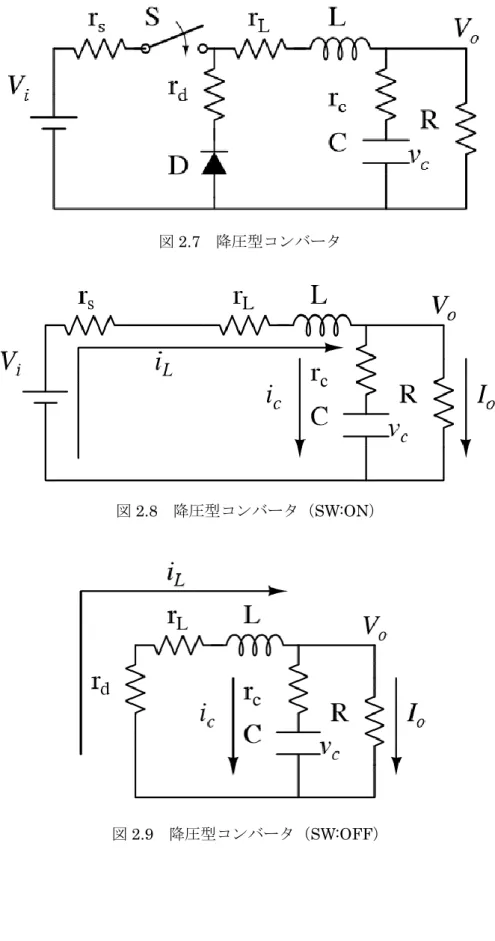

図2.7 に負荷抵抗 R を外部変数とした場合の降圧型コンバータ回路を示す。また、図 2.8 と図2.9 にスイッチ SW の ON 期間と OFF 期間の等価回路をそれぞれ示す。ただし、𝑉𝑖は 入力電圧、L は出力インダクタ、𝑖𝐿インダクタ電流、C は出力コンデンサ、𝑣𝐶はコンデンサ 両端電圧、𝑖𝐶はコンデンサに流れる電流、R は負荷、𝐼𝑜は負荷電流、𝑉𝑜は負荷電圧(コンバ ータの出力電圧)である。さらに、各素子の寄生する等価直列抵抗(ESR)やオン抵抗等とし て、𝑟𝑠, 𝑟𝑑, 𝑟𝐿, 𝑟𝐶を考慮し、計算するものとする。 状態平均化方程式の導出として、まず降圧型コンバータの状態方程式を立てる。導出する 微分方程式の形は式(2.1),(2.2)となる。12 𝑑𝑋 𝑑𝑡 = 𝐴𝑋 + 𝐵𝑉𝑖 (2.1) 𝑉𝑜= 𝐶𝑋 (2.2) 𝑋 = (𝑣𝑖𝐿 𝐶) (2.3) 𝐴 = (𝑎𝑎11 𝑎12 21 𝑎22) (2.4) 𝐵 = (𝑏11 𝑏21) (2.5) 𝐶 = (𝑐11 𝑐12) (2.6) なお、式(2.3)~(2.6)に示すように、インダクタ電流𝑖𝐿及びコンデンサ電圧𝑣𝐶を状態変数𝑋、 システム行列を𝐴、入力行列を𝐵、出力行列を𝐶として一階微分方程式を導出する。 [スイッチ ON 期間] スイッチSW が ON の場合、図 2.8 の等価回路から以下の 4 式が成り立つ。 𝑑𝑖𝐿 𝑑𝑡 = 𝑉𝑖− (𝑟𝑆+ 𝑟𝐿)𝑖𝐿− 𝑉𝑜 𝐿 (2.7) 𝑖𝐿 = 𝑖𝐶+ 𝐼𝑜 (2.8) 𝑖𝐶=𝐶 𝑑𝑣𝑐 𝑑𝑡 (2.9) 𝑉𝑜= 𝑖𝐶𝑟𝐶+ 𝑣𝐶 (2.10) 𝑑𝑣𝑐(𝑂𝑁)⁄ を導出する。(2.8),(2.10)式に(2.9)式を代入すると(2.8)’,(2.10)’式が得られる。 𝑑𝑡 𝑖𝐿 = 𝐶 𝑑𝑣𝑐 𝑑𝑡 + 𝑉𝑜 𝑅 (2.8)’ 𝑉𝑜= 𝑟𝐶𝐶 𝑑𝑣𝑐 𝑑𝑡 + 𝑣𝐶 (2.10)’ さらに、(2.8)’式の𝑉𝑜に(2.10)’式を代入し整理すると(2.11)のように求められる。

13 𝑑𝑣𝐶(𝑂𝑁) 𝑑𝑡 = 1 𝐶∙ 𝛼𝑖𝐿− 1 𝐶𝑅∙ 𝛼𝑣𝑐(ただし𝛼 = 𝑅 𝑅 + 𝑟𝐶 ) (2.11) 𝑉𝑜(𝑂𝑁)は(2.8)’,(2.10)’式より𝑑𝑣𝑐⁄ を消去すると(2.12)式のように導出できる。 𝑑𝑡 𝑉𝑜(𝑂𝑁)= 𝛼𝑟𝐶𝑖𝐿+ 𝛼𝑣𝑐 (2.12) 𝑑𝑖𝐿(𝑂𝑁)⁄ は(2.7)式に(2.12)式を代入し、求める。 𝑑𝑡 𝑑𝑖𝐿(𝑂𝑁) 𝑑𝑡 = −(𝑟𝑆+ 𝑟𝐿+ 𝛼𝑟𝐶) 𝐿 𝑖𝐿− 𝛼 𝐿∙ 𝑣𝑐+ 𝑉𝑖 𝐿 (2.13) これより、スイッチON 期間における状態方程式は(2.14)式、出力方程式は(2.15)式となる。 ( 𝑑𝑖𝐿(𝑂𝑁) 𝑑𝑡 𝑑𝑣𝐶(𝑂𝑁) 𝑑𝑡 ) = ( −𝑟𝑆+ 𝑟𝐿+ 𝛼𝑟𝐶 𝐿 − 𝛼 𝐿 𝛼 𝐶 − 𝛼 𝐶𝑅 ) (𝑣𝑖𝐿 𝐶) + ( 1 𝐿 0 ) 𝑉𝑖 (2.14) 𝑉𝑜(𝑂𝑁)= (𝛼𝑟𝐶 𝛼) (𝑖𝐿 𝑣𝐶) (2.15) [スイッチ OFF 期間] スイッチSW が OFF の場合、図 2.8 より𝑉𝑖 = 0となるので(2.8)~(2.10)式はそのままで、 (2.7)式のみに適応させると、(2.7)’式となる。 0 = 𝐿𝑑𝑖𝐿 𝑑𝑡 + (𝑟𝑆+ 𝑟𝐿)𝑖𝐿− 𝑉𝑜 (2.7)’ あとは、先ほどと同様の手順で行うと OFF 期間の状態方程式は(2.16)式、出力方程式は (2.17)式のように求められる。 ( 𝑑𝑖𝐿(𝑂𝐹𝐹) 𝑑𝑡 𝑑𝑣𝐶(𝑂𝐹𝐹) 𝑑𝑡 ) = ( −𝑟𝑑+ 𝑟𝐿+ 𝛼𝑟𝐶 𝐿 − 𝛼 𝐿 𝛼 𝐶 − 𝛼 𝐶𝑅 ) (𝑣𝑖𝐿 𝐶) + ( 0 0) 𝑉𝑖 (2.16) 𝑉𝑜(𝑂𝐹𝐹)= (𝛼𝑟𝐶 𝛼) ( 𝑖𝐿 𝑣𝐶) (2.17)

14 続いて、スイッチSW の ON 期間と OFF 期間の状態方程式と出力方程式を時比率𝐷で加重 平均すると、各係数行列は以下のようになる。なお、𝐷(𝑂𝐹𝐹)= (1 − 𝐷)とする。 𝐴 = 𝐷𝐴(𝑂𝑁)+ 𝐷(𝑂𝐹𝐹)𝐴(𝑂𝐹𝐹) = (− 𝐷𝑟𝑆+ (1 − 𝐷)𝑟𝑑+𝑟𝐿+ 𝛼𝑟𝐶 𝐿 − 𝛼 𝐿 𝛼 𝐶 − 𝛼 𝐶𝑅 ) (2.18) 𝐵 = 𝐷𝐵(𝑂𝑁)+ (1 − 𝐷)𝐵(𝑂𝐹𝐹) = ( 𝐷 𝐿 0 ) (2.19) 𝐶 = 𝐷𝐶(𝑂𝑁)+ (1 − 𝐷)𝐶(𝑂𝐹𝐹) = (𝛼𝑟𝐶 𝛼) (2.20) (2.18)~(2.20)式を(2.1),(2.2)式に代入すると、状態平均化方程式が求められる。 ( 𝑑𝑖𝐿 𝑑𝑡 𝑑𝑣𝑐 𝑑𝑡 ) = (− 𝐷𝑟𝑆+ (1 − 𝐷)𝑟𝑑+𝑟𝐿+ 𝛼𝑟𝐶 𝐿 − 𝛼 𝐿 𝛼 𝐶 − 𝛼 𝐶𝑅 ) (𝑣𝑖𝐿 𝐶) + ( 𝐷 𝐿 0 ) 𝑉𝑖 (2.21) 𝑉𝑜= (𝛼𝑟𝐶 𝛼) (𝑣𝑖𝐿 𝐶) (2.22) (2.24)式より、システム行列Aの𝑎11は変数𝐷を含んでおり、行列内に変数が入っていること でこの後の解析が複雑になるため、ここで𝑟𝑆 = 𝑟𝑑と仮定する。(これは、無理な仮定ではな く、現実的な仮定であるため、特に問題はない。)したがって、(2.21)式は(2.23)式のように 書き換えることが出来る。 ( 𝑑𝑖𝐿 𝑑𝑡 𝑑𝑣𝑐 𝑑𝑡 ) = ( −𝑟𝑑+𝑟𝐿+ 𝛼𝑟𝐶 𝐿 − 𝛼 𝐿 𝛼 𝐶 − 𝛼 𝐶𝑅 ) (𝑣𝑖𝐿 𝐶) + ( 𝐷 𝐿 0 ) 𝑉𝑖 (2.23)

15

図2.7 降圧型コンバータ

図2.8 降圧型コンバータ(SW:ON)

16

2.4.2

定常状態近傍での小信号解析

コンバータのパワーステージに対する外部変数(変動要因)は入力電圧𝑉𝑖𝑛、時比率𝐷、負 荷抵抗Rであり、これらが定常状態から微小変動が生じた場合の特性(動特性)を求める。 まず、以下の微小変動を(2.23),(2.22)式に適応させると、(2.25),(2.26)式が求められる。ただ し、微小項は無視するものとする。 𝑉𝑖 → 𝑉𝑖+ ∆𝑉𝑖(𝑡) 𝐷 → 𝐷 + ∆𝐷(𝑡) 𝑅 → 𝑅 + ∆𝑅(𝑡) (2.24) 𝑋(𝑡) → 𝑋 + ∆𝑋(𝑡) 𝑉𝑜(𝑡) → 𝑉𝑜+ ∆𝑉𝑜(𝑡) 𝑑(𝑋 + ∆𝑋) 𝑑𝑡 = (𝐴 + 𝑑𝐴 𝑑𝐷∙ 𝑑𝐷 + 𝑑𝐴 𝑑𝑅∙ 𝑑𝑅) (𝑋 + ∆𝑋) + (𝐵 + 𝑑𝐵 𝑑𝐷∙ 𝑑𝐷)(𝑉𝑖+ ∆𝑉𝑖) (2.25) 𝑉𝑜+ ∆𝑉𝑜= (𝐶 + 𝑑𝐶 𝑑𝐷∙ 𝑑𝐷 + 𝑑𝐶 𝑑𝑅∙ 𝑑𝑅) (𝑋 + ∆𝑋) (2.26) よって、時間領域における動特性の一般式が導出できた。次項では、この動特性の特性式を 用いて時間領域から周波数領域へと変換し、時比率𝐷の微小変動に対する状態変数𝑋(𝑠)の変 化を導出する。2.4.3

周波数領域への変換

前項までで解析してきた時間領域では、異常発振などに伴う過渡的な挙動は把握できる が、安定度を把握するためには周波数領域での解析が必要となる。時間領域から周波数領域 への変換には、ラプラス変換を用いる。以下のラプラス変換を(2.25),(2.26)式に適応させる と、(2.28),(2.29)式のように表せる。 ∆𝑉𝑖(𝑡) → ∆𝑉𝑖(𝑠) ∆𝐷(𝑠) → ∆𝐷(𝑠) ∆𝑅(𝑠) → ∆𝑅(𝑠) 𝑋(𝑡) → ∆𝑋(𝑠) (2.27) 𝑉𝑜(𝑡) → ∆𝑉𝑜(𝑠) 𝑑 𝑑𝑡∆𝑋(𝑡) = 𝑠∆𝑋(𝑠)17 𝑠∆𝑋(𝑠) = 𝐴∆𝑋 + (𝑑𝐴 𝑑𝐷∙ 𝑑𝐷 + 𝑑𝐴 𝑑𝑅∙ 𝑑𝑅) 𝑋 + 𝐵∆𝑉𝑖+ 𝑑𝐵 𝑑𝐷∙ 𝑑𝐷 ∙ ∆𝑉𝑖 (2.28) 𝑉𝑜+ ∆𝑉𝑜 = (𝐶 + 𝑑𝐶 𝑑𝐷∙ 𝑑𝐷 + 𝑑𝐶 𝑑𝑅∙ 𝑑𝑅) (𝑋 + ∆𝑋) (2.29) 続いて、(2.28)式を整理していくと(2.30)式となる。ここで、I は 2 行 2 列の単位行列であ る。 ∆𝑋(𝑠) = (𝑠𝐼 − 𝐴)−1(𝑑𝐴 𝑑𝐷∙ 𝑋 + 𝑑𝐵 𝑑𝐷∙ 𝑉𝑖) ∆𝐷 + 𝑑𝐴 𝑑𝑅∙ ∆𝑅 ∙ 𝑋 + 𝐵∆𝑉𝑖 (2.30) さらに、本節では時比率𝐷の微小変動に対する状態変数𝑋(𝑠)の変化を導出するため、(2.30) 式の2 項目以降は不要となり、(2.31)式で表される。 ∆𝑋(𝑠) = (𝑠𝐼 − 𝐴)−1(𝑑𝐴 𝑑𝐷∙ 𝑋 + 𝑑𝐵 𝑑𝐷∙ 𝑉𝑖) ∆𝐷 (2.31) これより𝑑𝐴 𝑑𝐷⁄ と𝑑𝐵 𝑑𝐷⁄ を求める。 𝑑𝐴 𝑑𝐷= 𝑑 𝑑𝐷{𝐷𝐴(𝑂𝑁)+ (1 − 𝐷)𝐴(𝑂𝐹𝐹)} = ( 𝑟𝑑− 𝑟𝑆 𝐿 0 0 0 ) (2.32) 𝑑𝐵 𝑑𝐷= 𝑑 𝑑𝐷{𝐷𝐵(𝑂𝑁)+ (1 − 𝐷)𝐵(𝑂𝐹𝐹)} = ( 1 𝐿 0 ) (2.33) (2.32),(2.33)式を(2.31)式に代入すると(2.34)式より周波数領域における動特性の一般式が 導出できた。 ∆𝑋(𝑠) = (𝑠𝐼 − 𝐴)−1[( 𝑟𝑑− 𝑟𝑆 𝐿 0 0 0 ) (𝑖𝐿 𝑣𝐶) + ( 1 𝐿 0 ) 𝑉𝑖] ∆𝐷 (2.34) 次に時比率𝐷の微小変動に対する状態変数𝑋(𝑠)の変化を求めることで、パワー段の伝達関数 𝐺𝑑𝑣(𝑠)を導出していく。ただし、以下では𝑟 = 𝑟𝑑+𝑟𝐿+ 𝛼𝑟𝐶とする。

18 ∆𝑋 ∆𝐷= [( 𝑠 0 0 𝑠) − ( −𝑟 𝐿 − 𝛼 𝐿 𝛼 𝐶 − 𝛼 𝐶𝑅 )] −1 [( 𝑟𝑑− 𝑟𝑆 𝐿 0 0 0 ) (𝑖𝐿 𝑣𝐶) + ( 1 𝐿 0 ) 𝑉𝑖] = 1 (𝑠 +𝑟𝐿) (𝑠 +𝐶𝑅) −𝛼 𝛼𝐿 (−𝛼𝐶)∙ ( 𝑠 + 𝛼 𝐶𝑅 − 𝛼 𝐿 𝛼 𝐶 𝑆 + 𝑟 𝐿 ) ( 𝑟𝑑− 𝑟𝑆 𝐿 𝑖𝐿+𝑉𝐿𝑖 0 ) = 1 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 1 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 𝑠2+ 𝑟 𝐿 + 𝛼 𝐶𝑅 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 𝑠 + 1 ∙ ( 𝑠 + 𝛼 𝐶𝑅 − 𝛼 𝐿 𝛼 𝐶 𝑆 + 𝑟 𝐿 ) ( 𝐷𝑟𝑑− 𝐷𝑟𝑆+ 𝑟𝑑+ 𝑟𝐿+ 𝛼𝑟𝐶 𝐷𝐿𝑅 0 ) 𝑉𝑜 ここで、式を見やすくするため 𝑃(𝑠) = 1 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 𝑠2+ 𝑟 𝐿 + 𝛼 𝐶𝑅 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 𝑠 + 1 と置くと ∆𝑋 ∆𝐷= 1 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 𝑃(𝑠) ∙ ( 𝑠 + 𝛼 𝐶𝑅 − 𝛼 𝐿 𝛼 𝐶 𝑆 + 𝑟 𝐿 ) ( 𝑟𝑑+ 𝑟𝐿+ 𝛼𝑟𝐶+ 𝑅𝛼 𝐷𝐿𝑅 0 ) 𝑉𝑜 = 1 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 1 𝑃(𝑠)∙ 𝑟𝑑+ 𝑟𝐿+ 𝑅 𝐷𝐿𝑅 ∙ ( 𝑠 +𝐶𝑅𝛼 𝛼 𝐶 ) 𝑉𝑜 (2.35) (2.35)式より以下の 2 式に分解できる。 ∆𝑖𝐿 ∆𝐷 = 1 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 1 𝑃(𝑠)∙ 𝑟𝑑+ 𝑟𝐿+ 𝑅 𝐷𝐿𝑅 ∙ (𝑠 + 𝛼 𝐶𝑅) 𝑉𝑜 (2.36) ∆𝑣𝐶 ∆𝐷 = 1 𝑟𝛼 𝑅𝐿𝐶+ 𝛼2 𝐶𝐿 ∙ 1 𝑃(𝑠)∙ 𝑟𝑑+ 𝑟𝐿+ 𝑅 𝐷𝐿𝑅 ∙ ( 𝛼 𝐶) 𝑉𝑜 (2.37)

19 (2.36),(2.37)式より(2.38)式が成り立ち、これを(2.22)式に代入すると(2.39)式が得られる。 (2.39)式を左辺が𝑣𝐶となるよう展開し、𝛼 = 𝑅/(𝑅 + 𝑣𝐶)を代入し直して整理すると(2.40)と なる。 𝑖𝐿= 𝐶 𝛼∙ (𝑠 + 𝛼 𝐶𝑅) 𝑣𝐶 (2.38) 𝑉𝑜= 𝛼𝑟𝐶𝑖𝐿+ 𝛼𝑣𝐶 = 𝑟𝐶C (𝑠 + 𝛼 𝐶𝑅) 𝑣𝐶+ 𝛼𝑣𝐶 (2.39) 𝑣𝐶= 𝑉𝑜 𝑟𝐶C (𝑠 +𝐶𝑅) + 𝛼𝛼 = 𝑉𝑜 𝑟𝐶C𝑠 + 1 (2.40) (2.37)式に(2.40)式を代入し、整理していくと(2.41)式が求められる。 ∆𝑉𝑜 ∆𝐷∙ 1 𝑟𝐶𝐶𝑠 + 1 = 𝐷 𝛼 +𝑅𝑟∙ 𝑉𝑖 1 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 1 𝑃(𝑠)∙ 𝑟𝑑+ 𝑟𝐿+ 𝑅 𝐷𝐿𝑅 ∙ ( 𝛼 𝐶) ∆𝑉𝑜 ∆𝐷 = 1 𝛼 +𝑅𝑟∙ 𝑉𝑖 1 𝛼 +𝑅𝑟∙ 1 𝑃(𝑠)∙ 𝑟𝑑+ 𝑟𝐿+ 𝑅 𝑅 ∙ (𝑟𝐶C𝑠 + 1) ∴ 𝐺𝑑𝑣(𝑠) ≡ ∆𝑉𝑜 ∆𝐷 = 𝑟𝑑+ 𝑟𝐿+ 𝑅 𝑅 (𝛼 +𝑅)𝑟 2 ∙ 𝑉𝑖 (𝑟𝐶C𝑠 + 1) 𝑃(𝑠) (2.41) 以上より、時比率𝐷の変動に対する出力電圧𝑉𝑜の応答を表す伝達関数𝐺𝑑𝑣(𝑠)を導出すること が出来た。

2.4.4

一巡伝達関数の導出

続いて電圧モード制御の帰還部分の各伝達関数を求め、コンバータ全体の一巡伝達関数 を導出する。図2.10 に一巡伝達関数を表すプロック図を示す。図の𝐺𝑐(𝑠)はエラーアンプ、 𝐹𝑚はFactor of Modulation の略称であり PWM を生成するコンパレータ、𝐺𝑑𝑣(𝑠)は前項で 導出したパワー段の伝達関数を表している。𝐺𝑐(𝑠)から順に導出していき、最終的に一巡伝 達関数𝑇(𝑠)を導出する。20 [エラーアンプ(位相補償器)𝐺𝑐(𝑠)] 本節で取り扱っている電圧モード制御は、パワー段における時比率𝐷の変動に対する出力 電圧𝑉𝑜の伝達関数𝐺𝑑𝑣(𝑠)は 2 次遅れ系であり、速い応答特性を得るには LC フィルタの共振 周波数𝐹𝐿𝐶よりも高い周波数にゼロクロス周波数𝐹0を設定する必要がある。この場合、図2.11 に示すTypeⅢの位相補償を一般的に用いる。また、図中に示すようにインピーダンス計算 の簡単化のため、C3, R3 のインピーダンスを Z、RbiasのインピーダンスをZ’、Z と Z’を掛 け合わせたものをZ1とし、C1,C2,R1 のインピーダンスを Z2とする。これより、Z,Z’,Z2を 求めると、(2.42)~(2.44)式のように表せる。 𝑍 = (𝑠𝐶1 3+ 𝑅3)𝑅1 𝑅1+𝑠𝐶1 3+ 𝑅3 = (1 + 𝑠𝐶3𝑅3)𝑅1 (𝑅1+ 𝑅3)𝑠𝐶3+ 1 (2.42) 𝑍′= 𝑅 𝑏𝑖𝑎𝑠 (2.43) 𝑍2= (𝑅2+𝑠𝐶1 1) 1 𝑠𝐶2 1 𝑠𝐶2+ 𝑅2+ 1 𝑠𝐶1 = 𝑠𝐶1𝑅2+ 1 𝑠2𝐶 1𝐶2𝑅2+ 𝑠(𝐶1+ 𝐶2) (2.44) 次に、(2.42),(2.43)式及び図 2.12 に示した、テブナンの定理を用いた等価変換を用いて Z1 と(𝑍′ 𝑍 + 𝑍′)𝑉 𝑂 ⁄ を導出する。 𝑍1= 𝑍 ∥ 𝑍′ = (1 + 𝑠𝐶3𝑅3)𝑅1𝑅𝑏𝑖𝑎𝑠 (1 + 𝑠𝐶3𝑅3)𝑅1+ {(𝑅1+ 𝑅3)𝑠𝐶3+ 1}𝑅𝑏𝑖𝑎𝑠 (2.45) 𝑍′ 𝑍 + 𝑍′∙ 𝑉𝑂= {(𝑅1+ 𝑅3)𝑠𝐶3+ 1}𝑅𝑏𝑖𝑎𝑠 (1 + 𝑠𝐶3𝑅3)𝑅1+ {(𝑅1+ 𝑅3)𝑠𝐶3+ 1}𝑅𝑏𝑖𝑎𝑠 ∙ 𝑉𝑂 (2.46) Z1及びZ2より、図2.11 は図 2.13 のように表せる。ここで、先ほど導出した(𝑍′⁄𝑍 + 𝑍′)𝑉𝑂 は𝑉𝑂′と置く。また、+端子と-端子は仮想短絡(イマジナリーショート)により同電位な ため、𝑉𝑖= 0と考えることが出来る。これより (2.47)式を求める。 𝐺𝑐(𝑠) = 𝑉𝐶 𝑉𝑂′ (2.47) 図2.13 より、入力インピーダンスが無限であるとすると、入力端子へ電流は流れ込まない ので(2.48)式が得られる。また、𝑉𝑖= 0より各電流は(2.49),(2.50)式で表せる。

21 𝐼1+ 𝐼2= 0 (2.48) 𝐼1= 𝑉𝑜′ 𝑍1 (2.49) 𝐼2= 𝑉𝑐 𝑍1 (2.50) (2.48)式に(2.49)式及び(2.50)式を代入すると(2.51)式となる。 𝐺𝑐(𝑠) = 𝑉𝑐 𝑉𝑜′ = 𝑍′𝑉𝐶 𝑍 + 𝑍′∙ 𝑉𝑂 = −𝑍2 𝑍1 (2.51) さらに、(2.51)式を変形させて(2.44)~(2.46)式((2.46)式は𝑉𝑂を除く)を代入すると、(2.52) 式が得られる。 𝐺𝐶(𝑠) = − 1 𝑠(𝐶1+ 𝐶2) ∙ 𝑠𝐶1𝑅2+ 1 (𝑠𝐶𝐶1𝐶2𝑅2 1+ 𝐶2+ 1) ∙(𝑅1+ 𝑅3)𝑠𝐶3+ 1 1 + 𝑠𝐶3𝑅3 (2.52) これより、エラーアンプの伝達関数𝐺𝐶(𝑠)が導出できた。また、(2.52)式より、𝑅𝑏𝑖𝑎𝑠は途中計 算で消去されるため、式の中には含まれず、𝑅𝑏𝑖𝑎𝑠の影響を受けないことが分かる。 図2.10 電圧モード制御の一巡伝達関数のブロック図

22

図2.11 エラーアンプ部の type3 位相補償

図2.12 テブナンの定理を用いた等価変換

23 [PWM コンパレータ𝐹𝑚] こではPWM を生成するコンパレータ部分の伝達関数を導出する。図 2.14 に PWM の原 理図を示す。図中の𝑉𝑟𝑎𝑚𝑝は内部の発振回路(図示せず)によって与えられた鋸歯状波(三 角波が用いられる場合もある)の振幅であり、エラーアンプが出力する電圧𝑉𝑐と比較し、鋸 歯状波よりも𝑉𝑐が高い場合を High、低い場合を Low として周期的なパルス信号を得てい る。鋸歯状波の周期に対するHigh 期間の比率が時比率𝐷である。𝑉𝑐が𝛥𝑉𝑐変化するとパルス 信号のHigh 期間は𝛥𝐷変化する。このように、外部信号(ここでは𝑉𝑐)によってパルスの幅

が変調される動作をPulse Width Modulation:PWM(パルス幅変調)という。エラーアン プ の 変 動 𝛥𝑉𝑐 に 対 す る 時 比 率 𝐷 の 変 動 𝛥𝐷 は 変 換 利 得 と 呼 ば れ 、 慣 例 的 に 𝐹𝑚(Factor of Modulation)が用いられるので PWM コンパレータの伝達関数は(2.53)式で示さ れる。 𝐹𝑚= 𝛥𝐷 𝛥𝑉𝑐 = 1 𝑉𝑟𝑎𝑚𝑝 (2.53) (2.53)式及び図 2.14 より、PWM コンパレータの伝達関数は一定の鋸歯状波とエラーアンプ の誤差電圧を比較しているだけなので周波数特性を持たないことが分かる。 また、PWM コンパレータで𝑉𝑐が比較され𝐷が決定されるのは 1 周期に 1 回のみであるため、 𝐷が決まった後に負荷電流𝐼𝑜に変動が生じ𝐷に変化を与えようとしても次の周期にしか反映 されない。そのため最大で 1 周期のむだ時間が生じる。このむだ時間は以下の式で表され る。 𝐻𝑑(𝑠) = 𝑒−𝑠𝑇 (2.54) むだ時間の利得は0dB で一定で位相はスイッチング周波数𝐹𝑆𝑊で360 度、𝐹𝑆𝑊⁄ で2 180 度 回転する。 図2.14 PWM の原理図

24 [一巡伝達関数𝑇(𝑠)] 以上で電圧モード制御の帰還部分の各伝達関数が導出できたので、前項で導出したパワ ー段の伝達関数𝐺𝑑𝑣(𝑠)よりコンバータ全体の一巡伝達関数を求める。ここで、一巡伝達関数 を𝑇(𝑠)とすると(2.55)式で表される。 𝑇(𝑠) = 𝐺𝑑𝑣(𝑠)𝐹𝑚𝐺𝑐(𝑠)𝐻𝑑(𝑠) (2.55) (2.55)式に(2.41),(2.52),(2.53),(2.54)式を代入すると、(2.56)式より一巡伝達関数が求められ る。 𝑇(𝑠) = 𝑟𝑑+ 𝑟𝐿+ 𝑅 𝑅 (𝛼 +𝑅)𝑟 2 ∙ 𝑉𝑖 (𝑟𝐶C𝑠 + 1) 𝑃(𝑠) ∙ 1 𝑉𝑟𝑎𝑚𝑝 ∙ 1 𝑠(𝐶1+ 𝐶2) ∙ 𝑠𝐶1𝑅2+ 1 (𝑠𝐶𝐶1𝐶2𝑅2 1+ 𝐶2+ 1) ∙(𝑅1+ 𝑅3)𝑠𝐶3+ 1 1 + 𝑠𝐶3𝑅3 (2.56) ただし、 𝑃(𝑠) = 1 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 𝑠2+ 𝑟 𝐿 + 𝛼 𝐶𝑅 𝑟𝛼 𝑅𝐿𝐶 + 𝛼2 𝐶𝐿 ∙ 𝑠 + 1 𝛼 = 𝑅 𝑅 + 𝑟𝐶 とする。

25

第 3 章 EMI ノイズ及び低減手法

3.1 電源回路性能について

電源回路を評価するための 1 つの指標として電源回路性能が用いられる。ここでは、 以下に示す9 項目において簡単に説明していく。なお、1~3 は DC 性能、4~6 は AC 性能、 6~9 は Transient 性能である。 1.効率 2.ラインレギュレーション 3.ロードレギュレーション 4.位相余裕/利得余裕 5.電源電圧変動除去比(PSRR) 6. EMC 7.入出力リップル電圧 8.負荷過渡応答(ロードステップレスポンス) 9.電源過渡応答(ラインステップレスポンス) まず1 つ目の効率は、入力電圧に対する出力電圧の比率[%]で定義される。単純には入力 が引き込んでいる電力(電流×電圧)と、出力から取れる電力を測定することで得られる値 である。電源性能の中で効率の重要性は言うまでもなく、損失を抑えることは発熱を下げる ことに繋がる。発熱は出力電力に制限を与えるばかりか、放熱や冷却の為のスペースやデバ イスを必要とし、電源回路や付加回路までもの信頼性を低下させる要因になるため、非常に 重要な性能項目である。 2 つ目のラインレギュレーションは入力の DC 電圧変動に対する出力電圧の変動であ り、%表示や決められた入力範囲における具体的な変動値 mV で表される。このラインレ ギュレーションは電源 IC や特にリニアレギュレータではほとんど場合に規格値が存在す る。入力範囲条件は、電源の入力として想定される電圧にベースを設定するがラインレギュ レーションはあくまで連続的な入力電圧の変動であり、つまりは過渡的ではない変動につ いての特性となる。 3 つ目のロードレギュレーションは負荷電流の変動に対する出力電圧の変動である。2 つ 目のラインレギュレーションと同様、%表示や決められた負荷変動間の変動値で表されると 共に、IC 自体にこの仕様があるが、電源としてみた場合は出力配線の抵抗成分により電源 出口と負荷入口では電圧降下あり、電圧が違う点に着目する必要がある。負荷の変動の1 つ として過渡的な変動があるが、ラインレギュレーションと同様にロードレギュレーション26 も過渡現象に対する特性ではなく、負荷過渡応答については別に Transient 性能として項 目の8 つ目で説明する。 4 つ目の位相余裕/利得余裕は電源回路のような負帰還回路の安定性を評価する尺度で ある。図3.1 に示すボード線図の概形を用いて説明する。図中の∅𝑀は位相余裕、𝑓𝑏𝑤はクロ スオーバー周波数、𝐺𝑀は利得余裕を示している。位相余裕∅𝑀はクロスオーバー周波数𝑓𝑏𝑤に おける位相を∅𝑓𝑏𝑤とすると、∅𝑓𝑏𝑤が-180°から何度余裕があるかを示しているため、 位相余裕: ∅𝑀= ∅𝑓𝑏𝑤+ 180 と表すことができる。一方で、利得余裕𝐺𝑀は位相が-180°における利得を𝐺180とすると、 𝐺180が0dB から何 dB 下がっているかを示しているため、 利得余裕: 𝐺𝑀= −𝐺180 と表すことができる。系が安定である場合は、∅𝑀, 𝐺𝑀共に正の値となる。スイッチング電 源のようなサーボ機構(追従制御)では、利得余裕𝐺𝑀が10dB から 20dB、位相余裕∅𝑀は 40°から 60°が安定余裕となる。 図3.1 ボード線図の概形

5 つ目の電源電圧変動除去比(PSRR:Power Supply Rejection Ratio)は、入力される電 源にリップルがある場合にそのリップルを取り除く能力のことである。通常の単位はdB で 表され、数値が高い程その能力が高いと言える。電源電圧変動除去比PSRR は AC 性能で あるため、周波数依存性を持ち、一般に周波数が高くなればなるほどPSRR は低くなる傾 向にあるため、比較的高いスイッチング周波数で動作させるスイッチング電源を採用する

27

場合は、組み合わせるレギュレータの周波数特性に注意する必要がある。

6 つ目の EMC は Electro Magnetic Compatibility の略称である。意味は「他の機器に電 磁妨害を与えず、他の機器から電磁妨害を受けても本来の性能を維持すること」であり、両 方の性能を両立させる必要性から電磁両立性や電磁適合性などと呼ばれる。図3.2 に EMC の分類を示す。これより、EMC は EMI と EMS の 2 つに分けることが出来る。まず、EMI はElectro Magnetic Interference の略称であり、電磁妨害や電磁障害を表す用語である。 意味はEMC の前半部分の「他の機器に電磁妨害を与えない」である。スイッチング電源に おいては、スイッチング動作により発生するスイッチングノイズに相当し、このEMI ノイ ズにおいては次節で詳しく述べる。続いて、EMS は Electro Magnetic Susceptibility の略 称であり電磁感受性を表す用語である。意味はEMC の後半部分の「他の機器から電磁妨害 を受けても」であり、EMI とは逆である。 図3.2 EMC の分類 7 つ目の入出力リップル電圧は、入力と出力の両方に発生する脈流のことであり、スイ ッチング電源では必ずスイッチングに起因したリップル電圧が存在する。リップルの特性 としては、脈の高さであるリップル電圧値と周波数が検討事項となる。入力リップルは、 スイッチング素子が大電流をスイッチングして、入力に引き込むことで発生する。また、 この電流のスイッチングと寄生インダクタンスによりスパイクが発生することもあり、設 計上で注意が必要となる。出力リップルは出力フィルタなどで低減することが可能だが、 PFM 制御のように周波数が変動する場合はさらなる検討が必要となる。 8 つ目の負荷過渡応答(ロードステップレスポンス)は、出力負荷電流が急激に増加ま たは減少などと変動した場合に、出力電圧が設定値である定常状態に戻るまでの応答速度 のことである。つまり、出力電圧が定常状態に戻るまでの時間が短い程負荷過渡応答に優 れていると言える。電流モード制御方式では位相特性の調整により最適化が可能であり、 ヒステリシス制御では非常に応用特性に優れている。 9 つ目の電源過渡応答(ラインステップレスポンス)は、入力ライン電圧が急激に増加ま たは減少などと変動した場合に、出力電圧が設定値である定常状態に戻るまでの応答速度 のことである。電源過渡応答は5 つ目の電源電圧変動除去比(PSRR)とは別物であり、 PSRR が DC 性能なのに対し、電源過渡応答はステップのフーリエ成分が含まれる

28 Transient 性能である。また、8 つ目の負荷過渡応答との違いは、負荷過渡応答では電源 の出力部分に外乱を注入するのに対し、電源過渡応答は入力に外乱が注入される。

3.2 EMI ノイズとは

近年のエレクトロニクスの進歩は著しく、身の回りにはスマートフォンやテレビなど 様々な電子機器が使われている。また、電子機器の発展とともにスイッチング電源も小型・ 軽量・高効率と高性能なものに発展してきた。しかし、スイッチング電源ではスイッチング 素子が数十~数百kHz の高周波で ON/OFF 動作を繰り返すため、これが EMI ノイズの発 生源となり、懸念されている。前節でも述べたが、EMI ノイズとは Electro Magnetic Interference の略称であり、日本語では電磁妨害という意味を持つ。また図 3.2 にも示し たように、EMI ノイズは伝導ノイズと放射ノイズの 2 つに分類でき、そのうち伝導ノイズ は伝導の仕方によってディファレンシャル(ノーマル)モードノイズとコモンモードノイズ に分けることができる。ディファレンシャルモードノイズは、ノイズ源が電源ラインに対し て直列に入り、電源電流と同方向にノイズ電流が流れ、電源ラインに発生する。コモンモー ドノイズは、浮遊容量などを介して漏れたノイズ電流が、GND を経由して電源ラインに戻 ってくるノイズである。電源のプラス側とマイナス側で流れるノイズ電流の向きが同じこ とからコモンモードと呼ばれる。これらのノイズは伝導ノイズだが、電源ラインにノイズ電 流が流れていることから、ノイズは放射されることになる。このように、EMI ノイズは空 間に放射されるため、クロストークといって周辺の回路や電子機器の通信を遮断したり誤 動作させてしまう恐れや、グランドノイズとしてグランドに流れることで自身の機器に影 響を与える恐れがある。よって、EMI ノイズは日本のみならず国際規格として世界各国で 規制されている。代表例としては、IEC(国際電気標準会議)規格や、その特別委員会であ る CISPR(国際無線障害特別委員会)規格などが挙げられ、日本国内規格としては VCCI が国際規格に準じた自主規制を行っている。また、昨今ではさらなる電源の高速化などに伴 いEMI ノイズの規制がより厳しいものになっており、規格をクリアできない製品は出荷が 出来ないといったことがある。そのため、スイッチング電源において EMI ノイズ対策は非 常に重要であり、必須項目となっている。次節ではこのEMI ノイズ対策法として 3 つの例 を説明する。3.3 EMI ノイズ低減手法

本節ではEMI ノイズ低減手法として、M 系列回路を用いた擬似アナログ信号による方 式、クロック周波数スイープ方式(従来手法)、補正電流による出力リプル低減方式(提案 手法)の3 つを説明する。さらに、従来手法と提案手法については次章においてシミュレー ション解析及び基板実装に用いる手法である。29

3.3.1

M 系列回路を用いた擬似アナログ信号による方式

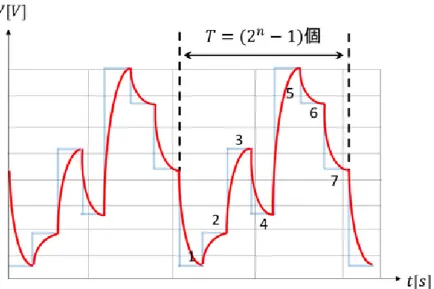

本項では M 系列回路を用いた擬似アナログ信号によって EMI ノイズを低減させる方 式を説明する。まず、M 系列回路の概略図を 3 ビットの場合を例として図 3.3 に示す。 M 系列(M-sequence) とはスペクトル拡散に用いられる拡散符号係数である PN 符号を 代表する擬似乱数系列である。n ビットのシフトレジスタと Ex-NOR 回路により構成さ れ、1 周期に𝑇 = (2𝑛− 1)個の擬似的な乱数信号を生成できる。これより、例として 3bit の 場合であれば 1 周期に 7 つのディジタル信号が出力され、その様子を図 3.4 に青線で示 す。赤線は M 系列回路の出力信号である 𝑉𝐷の先にローパスフィルタを追加するとこで、 ディジタル信号(青線)の波形を鈍らせることができ、擬似的にアナログな信号が得られる。 これを擬似アナログ信号と定義して取り扱う。 図 3.3 M 系列回路概略図(3bit)30

図 3.4 青線:ディジタル信号と赤線:擬似アナログ信号

続いて、図3.3 の M 系列回路が 3bit の場合を例にとり、動作原理を説明する。まず、 初期状態では𝑄1, 𝑄2, 𝑄3のすべてがLow なので、Ex-NOR の出力部分である𝐷1がHigh にな

る。、𝐹𝑐𝑙𝑘より最初にクロックclk が入力されると、𝑄1がHigh となる。続いてクロックが

入力されると、𝑄1はHigh のままで𝑄2がHigh となる。すると、Ex-NOR の 2 つの入力が

異なるのでEx-NOR の出力は Low となる。さらに次のクロックで𝐷1はLow のため、𝑄1は

Low になり、𝑄2と𝑄3がHigh となる。これより、Ex-NOR の 2 つの入力が同じなので𝐷1は

High になる。以上の動作を 7 回繰り返すことによって図 3.5 に示すようなタイムチャート が形成される。これらの信号を抵抗𝑅1~𝑅3に通し、オペアンプによって加算増幅すること で7 つの電圧レベルを持つディジタル信号が得られる。ディジタル信号Digitalの求め方 は抵抗𝑅1~𝑅3に流れる電流と𝑅0に流れる電流は同一なので、(3.1)式の様に示される。 𝐷𝑖𝑔𝑖𝑡𝑎𝑙 = (1 𝑅0 + 1 𝑅1 + 1 𝑅2 + 1 𝑅3 ) 𝑅0𝑉𝑜𝑓𝑓− ( 𝑄1 𝑅1 +𝑄2 𝑅2 +𝑄3 𝑅3 ) 𝑅0 (3.1) ここで、𝑅1: 𝑅2: 𝑅3= 1: 2: 4とすることで、1 レベルあたりの電圧の幅を揃えることがで き、𝑉𝑜𝑓𝑓を変えることでディジタル信号のDC 成分を、𝑅0変えることで電圧の最大値と最 小値の差を決めることが出来る。

31 図3.5 シフトレジスタのタイムチャート M 系列回路によってディジタル信号を生成することが出来たが、3bit のディジタル信 号が持つ電圧レベルは 7 通りであるため、PWM に適用し FFT にかけてもスペクトルは 7 本にしか拡散されない。シフトレジスタの bit 数を増やせば、さらなるスペクトル拡散 が見込まれるが、回路規模が大きくなってしまうという問題がある。これより、少ない bit 数のシフトレジスタであっても、アナログ信号であれば無限の電圧レベルを持ってい るため、PWM に適用し FFT をするとスペクトルがディジタル信号に比べて大幅に低減 させることが出来ると考えられる。ディジタル信号とアナログ信号の違いのイメージ図を 図 3.6 に示す。

32

図3.6 ディジタル信号とアナログ信号の違い

3.3.2

クロック周波数スイープ方式(従来手法)

クロック周波数スイープ方式は、スペクトラム拡散クロック発振器(Spread Spectrum Clock Generator:SSCG)の動作を簡易化したモデルを用いて EMI ノイズの低減を試みる方 式である。また次節においてこの方式の改善手法を説明するため、クロック周波数スイープ 方式は従来方式とする。 本研究で採用している電圧モード制御はクロック周波数が一定であることから、特定の 周波数成分にパワーが集中してしまう欠点があるが、SSCG はこのクロック周波数に僅か な変動を与えることで、線状に集中していたエネルギーを周辺周波数へと拡散することが 出 来 る 。SSCG の 簡 易 化 モ デ ル に は 、 電 圧 制 御 可 変 発 振 器 (Voltage Controlled Oscillator:VCO)を用いる。図 3.6 に VCO の動作原理図を示す。通常、VCO は入力された 信号の電圧値に応じて変換率 K=Hz/V で変換した矩形波を出力する。この特性を用いて、 従来方式ではVCO に変調信号として三角波を入力し、出力される周波数変調された矩形波 を用いることでEMI ノイズを低減させる。図 3.6 中の𝑉𝑏は三角波のベース電圧(オフセッ

ト電圧)、𝑉𝑚は変調電圧を示している。また、変調信号はベース電圧と変調電圧を用いて、

33 K=100kHz/1V ととした場合に、𝑉𝑏= 2[V],𝑉𝑚 = 100[mV]の三角波を VCO に入力すると出 力される矩形波は 200±10[kHz]となる。つまり、三角波の𝑉𝑏及び𝑉𝑚を設定することで、 PWM 信号の基本周波数 F1 を中心として±

F[Hz]の間を周波数変調できることになる。 この方式を適用した場合の PWM スペクトラム変化の様子として、図 3.9 にクロック周波 数スイープ方式を用いた場合のPWM スペクトラムを示し、比較特性として図 3.7 に EMI 拡散前のスペクトラム、図3.8 に前項で述べた M 系列回路方式を用いた場合の PWM スペ クトラムを示す。図3.8 及び図 3.9 より、各方式を適用することで図 3.7 と比較して基本周 波数のスペクトルのピーク値が1.5V 低減しており、ノイズ成分が周辺周波数へと拡散され ているのがわかる。さらに、図3.8 が M 系列回路を用いたランダム変調なのに対してクロ ック周波数スイープ方式はスペクトラムが一様に所定周波数幅で拡散されるため、図3.9 の ように頂上部がフラットな波形が得られる。これより、この方式ではスペクトラムが一様な 周波数幅で拡散されるため、頂上部がフラットな特性が得られ、低減量が定量的に分かり易 いことが利点であると言える。 図3.6 VCO の動作原理図 図3.7 EMI ノイズ拡散前の PWM スペクトラム34 図3.8 M 系列回路方式を用いた場合の PWM スペクトラム 図3.9 クロック周波数スイープ方式を用いた場合の PWM スペクトラム 続いて、クロック周波数スイープ方式の動作原理を説明するため、図3.10 に従来方式概 略回路図を示し、図3.11 に変調部の動作波形を示す。まず、変調信号である三角波が VCO に入力されると、VCO の出力波形𝑉𝐶𝑂𝑜𝑢𝑡は入力された変調信号に応じて周波数変調された 矩形波となる。この信号を内部の微分回路に通し、トリガとしてSW2 を ON/OFF するこ とで、鋸歯状波𝑆𝐴𝑊が生成される。この鋸歯状波𝑆𝐴𝑊と誤差電圧∆𝑉𝑜がコンパレータによっ て比較され、結果的に周波数変調されたPWM 信号が生成される。しかし、鋸歯状波𝑆𝐴𝑊 が生成されるにあたって、コンデンサ𝐶𝑆𝐴𝑊及び電流源𝐼𝑆𝐴𝑊の値は常に一定のため、周波数変 調ごとに振幅が異なる鋸歯状波𝑆𝐴𝑊が生成されることになり、この鋸歯状波𝑆𝐴𝑊と誤差電 圧∆𝑉𝑜が比較されて生成された PWM 信号は、周波数変調はされているものの、鋸歯状波 𝑆𝐴𝑊の影響で1周期ごとの ON 時間が一定の信号となってしまう。これより、周波数変調 ごとに差分のOFF 時間が変化することになり、この時比率𝐷変動によって出力電圧リプル が増大することが考えられる。以上より、クロック周波数スイープ方式ではVCO を用いた 周波数変調により、EMI ノイズの低減は見込める一方で出力電圧リプルが増大してしまう 欠点をもつ。次項ではこの問題を改善した提案手法である補正電流による出力リプル低減 方式について述べる。

35 図3.10 従来方式概略回路図 図3.11 変調部動作波形

3.3.3

補正電流による出力リプル低減方式(提案手法)

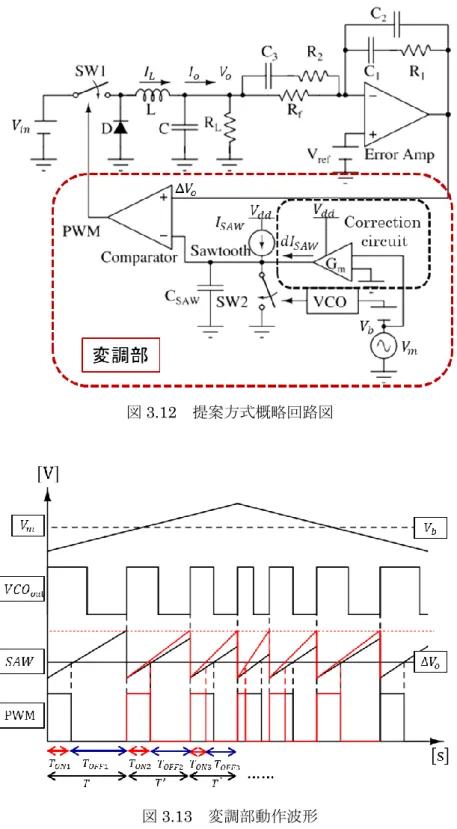

本項では、前項のクロック周波数スイープ方式の改良方式として、補正電流による出力リ プル低減方式を提案する。具体的には、従来方式においてEMI ノイズの低減は見込める一36 方で出力電圧リプルが増大してしまう問題を、提案方式では変調部の鋸歯状波生成部分に 補正電流を追加することで時比率𝐷変化を補正し、出力電圧リプル抑制を試みる。 図3.12 に提案方式概略回路図を示し、図 3.13 に変調部の動作波形を示す。図 3.10 と図 3.12 を比較すると、基本構造は従来方式と同じだが、提案方式では変調部の鋸歯状波生成 部分に補正回路が追加されていることが分かる。この補正回路により適切な補正電流𝑑𝐼𝑆𝐴𝑊 を生成し𝐼𝑆𝐴𝑊に加減することで鋸歯状波𝑆𝐴𝑊の傾きを変化させ、時比率𝐷を補正する。補正 電流𝑑𝐼𝑆𝐴𝑊の生成には電圧制御電流源を使用する。電圧制御電流源は入力された電圧値𝑉𝑖に 応じて出力電流𝐼𝑜が決まり、この関係性は(3.2)式のように相互コンダクタンス𝑔𝑚で表され る。 𝑔𝑚 =∆𝐼𝑜 ∆𝑉𝑖 (3.2) 相互コンダクタンス𝑔𝑚の単位は S(ジーメンス)である。この式の入力電圧を周波数変調 分である三角波の振幅𝑉𝑚、出力電流を補正電流𝑑𝐼𝑆𝐴𝑊とすると(3.3)式のように変換できる。 𝑑𝐼𝑆𝐴𝑊= 𝑔𝑚 ∗ 𝑉𝑚 (3.3) (3.3)式より、適切な補正電流𝑑𝐼𝑆𝐴𝑊を得るには適切な𝑔𝑚を設定する必要があると言える。 この適切な𝑔𝑚を最適電流補正量𝐺𝑚と定義して理論解析により𝐺𝑚を算出する。まず、クロッ ク周波数の変調部分から考える。クロック周波数を𝐹𝑐𝑙𝑘、VCO の変換率を K(kHz/V)、変調 信号ベース電圧を𝑉𝑏 、変調信号振幅を𝑉𝑚、(𝑉𝑚⁄𝑉𝑏 ) = 𝛼とすると、変調後のクロック周波数 𝐹𝑐𝑙𝑘′は(3.4)式で表される。 𝐹𝑐𝑙𝑘′ = 𝐾(𝑉𝑏± 𝑉𝑚) = 𝐾𝑉𝑏(1 ± 𝑉𝑚 𝑉𝑏 ) = 𝐾𝑉𝑏(1 ± 𝛼) (3.4) 𝛼は変調度と考え、仮に𝛼 = 0.1とすると、クロック周波数𝐹𝑐𝑙𝑘は10%変調していることにな る。変調信号によって𝛼分変調されるので、鋸歯状波を生成する電流源𝐼𝑆𝐴𝑊も同様に𝛼分補 正すればよいと考える。補正された電流源𝐼𝑆𝐴𝑊を𝐼𝑆𝐴𝑊′とすると、(3.5)式のようになる。 𝐼𝑆𝐴𝑊′ = 𝐼𝑆𝐴𝑊(1 ± 𝛼) = 𝐼𝑆𝐴𝑊+ 𝛼𝐼𝑆𝐴𝑊 (3.5) このとき𝛼𝐼𝑆𝐴𝑊は補正電流𝑑𝐼𝑆𝐴𝑊と考えられるので、最適電流補正量𝐺𝑚と共に(3.3)式に代入

37 すると次式が得られる。 𝛼𝐼𝑆𝐴𝑊= 𝐺𝑚∗ 𝑉𝑚 (3.6) さらに、(3.6)式の𝛼を元に戻すと(3.7)式のように最適電流補正量𝐺𝑚の理論式が導出できる。 𝑉𝑚 𝑉𝑏 𝐼𝑆𝐴𝑊= 𝐺𝑚∗ 𝑉𝑚 𝐺𝑚= 𝐼𝑆𝐴𝑊 𝑉𝑏 (3.7) この理論式より求められる𝐺𝑚値により、適切な補正電流𝑑𝐼𝑆𝐴𝑊を生成することが可能とな る。図3.13 に示す変調部の動作波形より、従来方式と動作の流れは同じだが赤線で記した 部分が提案方式によって変化した部分である。具体的には、補正回路より生成した補正電流 𝑑𝐼𝑆𝐴𝑊が電流源𝐼𝑆𝐴𝑊に加わることによって、鋸歯状波𝑆𝐴𝑊の傾きが補正され、1 周期ごとの 振幅が一定となる。これより、鋸歯状波𝑆𝐴𝑊とエラーアンプの誤差電圧∆𝑉𝑜によって生成さ れるPWM は周波数変調に応じて OFF 時間に加え ON 時間も変化することになる。すなわ ち、補正電流𝑑𝐼𝑆𝐴𝑊によって周波数変調は維持したまま本来の時比率𝐷が保たれるため、出 力電圧リプルは増大しない。以上より、補正電流による出力リプル低減方式(提案手法)を 採用することで、従来方式の問題点であったEMI ノイズ低減と出力電圧リプル増大のトレ ードオフを解決できる。

38

図3.12 提案方式概略回路図

39

第 4 章 従来及び提案手法を用いた

シミュレーション検証と基板実装評価

4.1 シミュレーションにおける検証

本節では前章の 3.3.2,3.3.3 項において説明した従来手法及び提案手法の動作をシミュ レーションにより確認する。またコンバータは電圧モード制御方式非同期降圧型DC-DC コ ンバータを用い、シミュレーションソフトにはSIMPLIS を用いた。 PWM スペクトラム(EMI ノイズ)は、50[Ω]負荷で 1[mW]を基準とする単位 [dBm]で示 し、実装評価に合わせている。よって、[dBm]の基準電圧𝑉0は以下のように計算できる。 𝑉0= √𝑃 ∗ 𝑅 = 1[mW] ∗ 50[Ω] = 0.224[V] (4.1) (4.1)式用いると、デシベル値 dB は(4.2)式で表せる。さらに(4.2)式を変形すると、デシベル 値dB から電圧値 V への変換は(4.3)式で求められる。 dB = 20𝑙𝑜𝑔10( V 0.224[V]) (4.2) V = 10( dB 20)∗ 0.224[V] (4.3) これより、各手法におけるPWM スペクトラム(EMI ノイズ)の低減率を求める際には、 (4.3)式より算出した電圧値を用いることとする。なお、以後簡単化のため[dBm]は[dB]表示 としている。4.1.1

従来手法

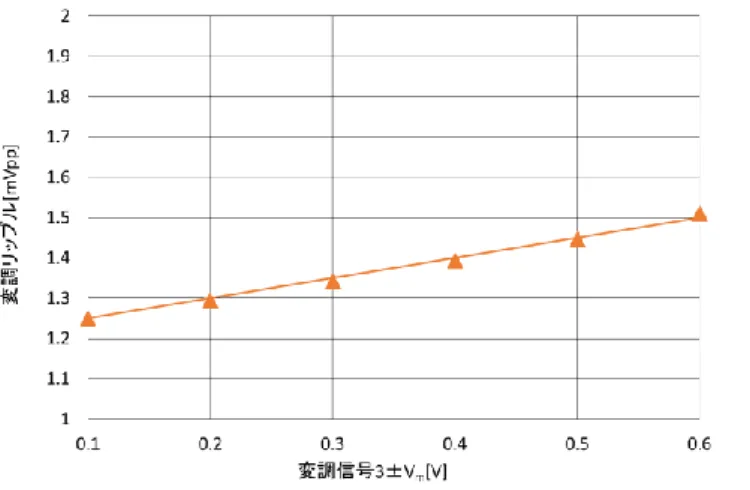

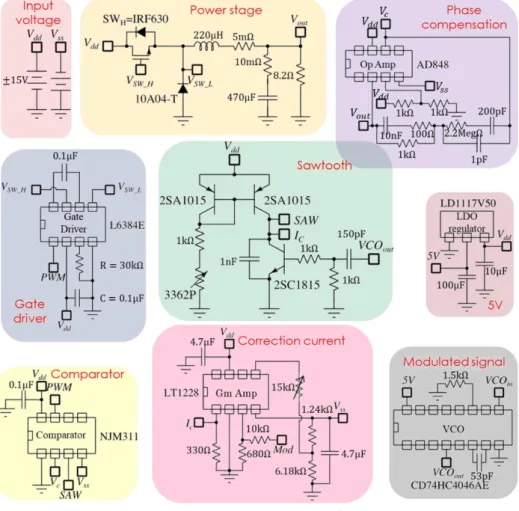

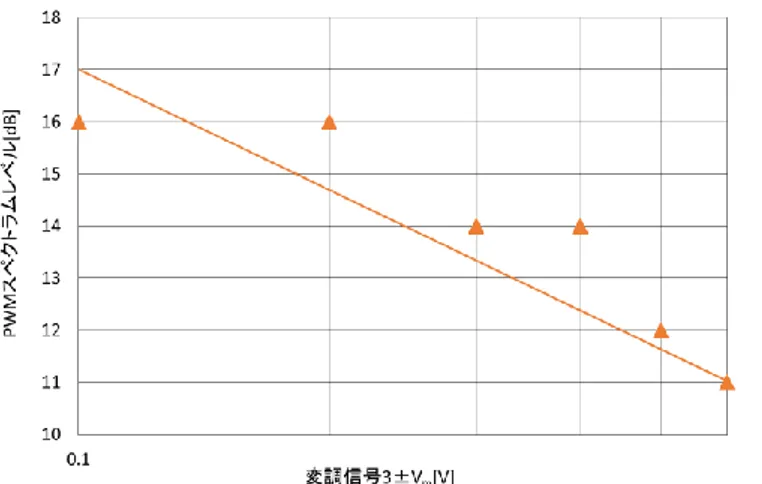

従来手法におけるシミュレーション回路を図4.1 に示し、各パラメータを表 4.1 に示す。 シミュレーション回路より、パワーステージの出力LC には等価直列抵抗等の寄生素子とし て𝑟𝐿及び𝑟𝐶を含むものとする。また、エラーアンプの位相補償回路は TypeⅢにおいて設計 した。40 図4.1 従来手法シミュレーション回路 表4.1 従来手法シミュレーション回路各パラメータ パワーステージ エラーアンプ(位相補償回路) 入力電圧𝑉𝑖 15[V] Rf 1[kΩ] 出力電圧𝑉𝑖 7.5[V] R1 2.08[MΩ] クロック周波数𝐹𝑐𝑙𝑘 150[kHz] R2 100[Ω] コイル L 220[uH] C1 0.206[nF] コイル寄生素子𝑟𝐿 5[mΩ] C2 1.02[pF] コンデンサ C 470[uF] C3 8.16[nF] コンデンサ寄生素子𝑟𝐶 10[mΩ] 出力負荷Ro 8.2[Ω] 変調信号+VCO+鋸歯状波生成 変調信号 ベース電圧𝑉𝑏 3[V] 変調信号 変調電圧𝑉𝑚 0.1~0.6[V] 変調信号波形の種類(時比率) 三角波(50[%]) VCO 変換率 K 50[kHz]/1[V] 鋸歯状波生成電流𝐼𝑆𝐴𝑊 2.6[mA] まず、変調信号振幅電圧𝑉𝑚を 0 とした変調を加えない状態で各状態を確認する。具体的 には、AC(周波数)解析により閉ループの一巡特性を出し、コンバータの安定性を確認す

41 ると共に、Transient(時間)解析により各動作波形を確認する。続いて、変調電圧𝑉𝑚を 0.1~0.6[V]と変化させていった場合の出力電圧リプル及び EMI ノイズの変化を Transient (時間)解析により確認していく。ここで、変調信号は三角波、EMI ノイズは PWM の FFT 特性の基本周波数部分に重畳しているものとして考える。 [変調無(𝑉𝑚= 0[V])] 図4.1 のシミュレーション回路における AC(周波数)解析の結果を図 4.2 に示す。図 4.2 より、周波数494[Hz]においてパワーステージの LC によるダブルポールを確認できる。こ れより利得は-40dB/dec で減衰するが、33.9[kHz]において C の寄生容量により C 分の位相 遅れがキャンセルされ、利得は-20dB/dec となる。また、利得が 0[dB]時における位相余裕 を確認すると60[°]であり、安定条件 45[°]以上を満たす結果が得られた。 続いてTransient(時間)解析により各動作波形を確認する。図 4.3 にシミュレーション 時間30[mS]中の 20.00~20.05[mS]の結果を示す。図中の上段から、変調信号𝑉𝑏± 𝑉𝑚、鋸歯 状波𝑆𝐴𝑊、PWM、コイル電流𝐼𝐿、出力電圧𝑉𝑜の結果となっている。変調信号𝑉𝑏± 𝑉𝑚におい ては、現在𝑉𝑚= 0[V]の状態を確認しているためベース電圧のみの 3[V]となっている。出力 電圧𝑉𝑜は鋸歯状波𝑆𝐴𝑊などを含む帰還回路より生成された PWM の ON/OFF によってリプ ルが発生する。これを出力電圧の定常リプルと呼び、変調をかけた場合に増加するリプルは 変調リプルと定義して取り扱う。また、図4.4 に PWM スペクトラムのシミュレーション解 析結果を示す。図より、基本周波数に重畳するEMI ノイズは 10[dB]であることが読み取れ る。 図4.2 AC(周波数)解析結果

42 図4.3 Transient(時間)解析結果(各波形) 図4.4 従来手法 無変調時 PWM スペクトラム [変調有(𝑉𝑚= 0.1~0.6[V])] 続いて、変調電圧𝑉𝑚を0.1~0.6[V]と変化させていった場合の出力電圧リプル及び EMI ノ イズの変化をTransient(時間)解析により確認する。変調電圧𝑉𝑚0.1~0.6[V]の範囲決定に は、帰還ループに支障をきたさない変調度として、クロック周波数𝐹𝑐𝑙𝑘に対し最大で20[%] となるよう設定した。 図 4.5 に変調信号と PWM スペクトラムの関係を示し、図 4.6 に𝑉𝑚= 0.6[V]における PWM スペクトラムと図 4.4 を比較した特性を示す。さらに、図 4.7 に変調信号と出力電圧

43 リプルの関係を示し、図4.8 に𝑉𝑚= 0.6[V]における出力電圧リプルと図 4.3 の定常リプルを 比較した特性を示す。図4.5 及び図 4.7 より、変調電圧𝑉𝑚を 0.1~0.6[V]と変化させていく と、EMI ノイズは比例的に減少するが、出力電圧リプル(変調リプル)は比例的に増大す るトレードオフの結果となった。変調信号変化による具体的なEMI ノイズの低減量と出力 電圧リプルの増大量は、図4.6 及び図 4.8 より、EMI ノイズ:-15[dB]、出力電圧リプル(変 調リプル):+3.239[mV]となる。以上より、3 章で述べた理論と同一の結果がシミュレーシ ョン解析によって得られた。次項では、提案手法においてシミュレーション解析を行う。 図4.5 変調信号と PWM スペクトラムの関係 図4.6 PWM スペクトラム比較(赤:変調無、緑:𝑉𝑚= 0.6[V])

44 図4.7 変調信号と出力電圧リプルの関係 図4.8 出力電圧リプル比較(赤:変調無、緑:𝑉𝑚= 0.6[V])

4.1.2

提案手法

提案手法におけるシミュレーション回路を図4.9 に示し、補正回路におけるパラメータを 表4.2 に示す。その他のパラメータは表 4.1 と同様である。まず (3.7)式に表 4.1 から、鋸 歯状波生成電流𝐼𝑆𝐴𝑊= 2.6[mA]と変調信号ベース電圧𝑉𝑏= 3[V]を代入すると、(4.4)式のよう に最適電流補正量𝐺𝑚の理論値が導出できる。 𝐺𝑚= 𝐼𝑆𝐴𝑊 𝑉𝑏 =2.6[mA] 3[V] = 0.87[mS] (4.4)45 続いて、補正回路の電圧制御電流源に(4.1)式より求めた𝐺𝑚= 0.87[mS]を設定することで、 出力電圧リプルが最小値となるかシミュレーションにより確認する。変化を分かり易くす るため、前項で得られた特性より出力電圧リプルが最大となる変調電圧𝑉𝑚= 0.6[V]の場合 を考える。この状態で、𝐺𝑚= 0.77,0.87,0.97,1.07,1.17[mS]と理論値 0.87[mS]前後を 0.1[mS] 刻みで変化させ、出力電圧リプルが最小値となる実測値を確認する。図4.10 にシミュレー ション結果を示す。図より、出力電圧リプルは𝐺𝑚= 1.07[mS]で最小値を示し、この値がシ ミュレーションにおける最適電流補正量𝐺𝑚′であることが分かる。よって、最適電流補正量 𝐺𝑚の理論値とシミュレーションによる実測値との誤差は 0.2[mS]となる。以後のシミュレ ーションには𝐺𝑚′ = 1.07[mS]を用いて解析を行う。 従来手法と同様に、変調電圧𝑉𝑚= 0[V]とした変調を加えない場合と𝑉𝑚= 0.1~0.6[V] と変 化させていった場合において、出力電圧リプル及びEMI ノイズの変化を Transient(時間) 解析する。なお、コンバータの安定性等については従来手法のAC(周波数)解析により確 認済みなので割愛する。 図4.9 提案手法シミュレーション回路 表4.2 補正回路パラメータ 補正回路(電圧制御電流源) 最適電流補正値𝐺𝑚 0.87[mS]

46 図4.10 シミュレーションにおける最適電流補正𝐺𝑚′の確認 [変調無(𝑉𝑚= 0[V])] 変調無𝑉𝑚= 0[V]の場合のシミュレーション解析結果として、図 4.11 に PWM スペクトラ ム、図4.12 に出力電圧リプルを示す。各図より、無変調時の PWM スペクトラム(EMI ノ イズ)は10[dB]、出力電圧リプル(定常リプル)は 0.001[mV]と従来手法と同様の結果に なった。 図4.11 提案手法 無変調時 PWM スペクトラム