101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com

コンパイラ・ユーザガイド

コンパイラ・バージョン : 3.4.1 ドキュメント・バージョン : 3.4.1 ドキュメント・デート : 2006 年 6 月 オペレーション・パート番号 この資料は英語版を翻訳したもので、内容に相違が生 じる場合には原文を優先します。こちらの日本語版は 参考用としてご利用ください。設計の際には、最新の 英語版で内容をご確認ください。performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the

このユーザガイドについて

改訂履歴 ... v アルテラへのお問い合わせ ... v 表記規則 ... viコンパイラの概要

はじめに ... vii デザインに最適なフローの選択 ... viii第1章 . このコンパイラについて

リリース情報 ... 1–1 サポートされるデバイス・ファミリ ... 1–1 バージョン 3.4.1 の新機能 ... 1–2 特長 ... 1–2 概要 ... 1–2 OpenCore Plus 評価機能 ... 1–4 性能 ... 1–5第2章 . 使用法

デザイン・フロー ... 2–1 SOPC Builder のデザイン・フロー ... 2–3 DDR & DDR2 SDRAM コントローラの実習 ... 2–3 トップレベル・デザインの作成 ... 2–14 SOPC Builder デザインのシミュレーション ... 2–15 SOPC Builder デザインのコンパイル ... 2–15 デバイスのプログラム ... 2–17 MegaWizard のデザイン・フロー ... 2–18 DDR & DDR2 SDRAM コントローラの実習 ... 2–18 デザイン例のシミュレーション ... 2–42 デザイン例のコンパイル ... 2–48 デバイスのプログラム ... 2–52 ユーザ・デザインの実装 ... 2–52 ライセンスの設定 ... 2–53第3章 . 仕様

機能の説明 ... 3–1 コントロール・ロジック ... 3–2 データパス ... 3–3 OpenCore Plus タイム・アウト動作 ... 3–4 デバイス・レベルでの説明 ... 3–5データパス ... 3–5 PLL コンフィギュレーション ... 3–15 DLL コンフィギュレーション ... 3–19 デザイン例 ... 3–20 制約 ... 3–22 インタフェースと信号 ... 3–23 インタフェースの説明 ... 3–23 信号 ... 3–35 パラメータ ... 3–40 メモリ ... 3–41 コントローラ ... 3–42 コントローラのタイミング ... 3–45 メモリ・タイミング ... 3–47 ボード・タイミング ... 3–48 プロジェクトの設定 ... 3–49 マニュアル・タイミング ... 3–50 MegaCore 検証 ... 3–50 シミュレーション・テスト ... 3–51 ハードウェア・テスト ... 3–51

付録 A. 手動タイミング設定

パラメータ ... A–1 再同期 ... A–4 DQS ポストアンブル ... A–11付録 B. Nios 開発ボード、Cyclone II エディション上の DDR SDRAM

付録 C. HardCopy II デザインの実習

付録 D. 性能の最大化

デバイスおよびボード設定 ... D–1 PLL 位相の調整 ... D–2 ピンの割り当て ... D–3 フィードバック PLL の配置 ... D–3 PLL 位相の更新 ... D–3改訂履歴

以下の表に、このユーザガイドの章の改定履歴を示します。アルテラへの

お問い合わせ

ア ル テ ラ 製 品 に 関 す る 最 新 情 報 は、ア ル テ ラ の ウ ェ ブ サ イ ト、 www.altera.co.jp をご覧ください。テクニカル・サポートについては、 www.altera.co.jp/mysupportにアクセスしてください。また、アルテラ の販売代理店にもお問い合わせいただけます。 章 日付 バージョン 変更内容 すべて June 2006 3.4.1 バースト長の定義を修正 すべて April 2006 3.4.0 ● 若干の体裁変更を実施 ● フィードバック・クロック・モードの付録を追加 ● IP Toolbench に PLL 出力オプションを追加 ● データパス信号の動作を追加 すべて December 2005 3.3.1 変更なし 1 October 2005 3.3.0 デバイスのサポート表を更新 April 2005 3.2.0 ● 機能一覧を更新 ● システム・レベルの図を修正 2 October 2005 3.3.0 ● ModelSim以外のシミュレータのシミュレーション命令を 追加 ● MegaWizard®フローの手順を改訂 April 2005 3.2.0 ● デザイン・フローを更新 ● PLL の編集の項を更新 ● トップレベル・デザイン例のコンパイルの項を更新 ● デザインの実装の項を更新 3 October 2005 3.3.0 ● DLL コンフィギュレーションの項を追加 ● reset信号の説明を更新 April 2005 3.2.0 ● Avalon™ バースト信号を追加 ● データパスの項を更新 ● PLL コンフィギュレーションの項を更新 ● 新しい移行可能なピン・パラメータを追加 A October 2005 3.3.0 変更なし April 2005 3.2.0 変更なし B October 2005 3.3.0 変更なし April 2005 3.2.0 新しい付録を追加 C October 2005 3.3.0 新しい付録を追加表記規則

本書では、以下の表記規則を使用しています。 書体 意味 太字かつ文頭が大文字 コマンド名、ダイアログ・ボックス・タイトル、チェックボックス・オプショ ン、およびダイアログ・ボックス・オプションは、太字かつ文頭が大文字で表 記されています。 例: Save As ダイアログ・ボックス 太字 外部タイミング・パラメータ、ディレクトリ名、プロジェクト名、ディスク・ ドライブ名、ファイル名、ファイルの拡張子、およびソフトウェア・ユーティ リティ名は、太字で表記されています。例: fMAX, \qdesigns ディレクトリ、d: ドライブ、chiptrip.gdf ファイル

斜体かつ文頭が大文字 資料のタイトルは、斜体かつ文頭が大文字で表記されています。 例: AN 75: High-Speed Board Design

斜体 内部タイミング・パラメータおよび変数は、斜体で表記されています。 例: tPIA, n + 1 変数は、山括弧 (< >) で囲み、斜体で表記されています。 例: <ファイル名>、<プロジェクト名>.pof ファイル 文頭が大文字 キーボード・キーおよびメニュー名は、文頭が大文字で表記されています。 例: Delete キー、Options メニュー 「小見出しタイトル」 資料内の小見出しおよびオンライン・ヘルプ・トピックのタイトルは、鉤括弧 で囲んでいます。 例: 「表記規則」 Courier フォント 信号およびポート名は、Courier フォントで表記されています。

例: data1、tdi、input。 アクティブ Low 信号は、サフィックスnで表示 されています ( 例:resetn)。 表示されているとおりに入力する必要があるものは、Courier フォントで表記 されています ( 例: c:\qdesigns\tutorial\chiptrip.gdf)。 また、 Report ファイルのような実際のファイル、ファイルの構成要素 ( 例:AHDL キーワードのSUBDESIGN)、ロジック・ファンクション名 ( 例:TRI) も Courier フォントで表記されています。 1.、2.、3. および a.、b.、c. など 手順など項目の順序が重要なものは、番号が付けられリスト形式で表記されて います。 ■ ● • 箇条書きの黒点などは、項目の順序が重要ではないものに付いています。 9 チェックマークは、1 ステップしかない手順を表します。 指差しマークは、要注意箇所を表しています。 CAUTION マークは、特別な配慮および理解が必要であり、手順またはプロセ スを始める前、または続ける際に確認すべき情報を示しています。 注意マークは、手順またはプロセスを始める前、または続ける際に確認すべき 情報を示しています。 矢印は、Enter キーを押すことを示しています。 足跡マークは、詳細情報の参照先を示しています。

はじめに

アルテラの DDR および DDR2 SDRAM コントローラ・コンパイラ、お よび Quartus®II ソフトウェアは、高性能の DDR および DDR2 SDRAM カスタム・デザインを作成するための多数のオプションを提供します。 DDR および DDR2 SDRAM コントローラ・コンパイラ、および Quartus II ソフトウェアには、以下の 2 つのデザイン・フロー・オプションがあり ます。 ■ DDRおよびDDR2 SDRAMコントローラ・コンパイラのSOPC Builder フロー ■ DDR および DDR2 SDRAM コントローラ・コンパイラの MegaWizard® フロー SOPC Builder フローでは、簡素化され、自動的に統合されたシステムが 生成されます。MegaWizard フローではユーザによるカスタマイズが必 要です。SOPC Builder フロー

DDR および DDR2 SDRAM コントローラ・コンパイラの SOPC Builder フロー・オプションを使用すると、完全な DDR または DDR2 SDRAM システムを構築できます。このオプションでは、DDR または DDR2 SDRAM コントローラをアルテラの Avalon™スイッチ・ファブリックに 接続することによって、Avalon ペリフェラルを 1 つまたは複数含むシス テムを簡単に作成できます。 システム・コンポーネントを指定して、豊富な機能セットからシステム のオプションを選択すれば、SOPC Builder が自動的に内部接続ロジック とシミュレーション環境を生成します。このため、手動で統合する場合 と比較して、システムを定義および生成するための時間が大幅に短縮さ れます。

DDR および DDR2 SDRAM コントローラ・コンパイラの SOPC Builder

フローのオプションについて詳しくは、2–3 ページの「DDR & DDR2

SDRAM コントローラの実習」を参照してください。

SOPC Builder の詳細については、「Quartus II ハンドブック Volume 3」 を参照してください。

MegaWizard フロー

DDR および DDR2 SDRAM コントローラ・コンパイラの MegaWizard フローのオプションを使用すると、DDR または DDR2 SDRAM コント ローラを完全に設定することができます。このフローでは低レベル・イ ンタフェースを利用します。 DDR および DDR2 SDRAM コントローラ・コンパイラの MegaWizard フローのオプションについて詳しくは、2–18 ページの「DDR & DDR2 SDRAM コントローラの実習」を参照してください。デザインに

最適なフロー

の選択

ここでは、デザインに最適なフローを選択するために役立つ情報を提供 します。SOPC Builder フロー

DDR および DDR2 SDRAM コントローラ・コンパイラの SOPC Builder フローが持つ利点および欠点は、以下のとおりです。 利点 ■ 最小限の DDR および DDR2 SDRAM デザイン専門知識が必要 ■ 完全な DDR または DDR2 SDRAM システムを数時間以内に作成でき るシンプルかつ柔軟な GUI ■ シミュレーション環境を自動的に生成 ■ カスタム・コンポーネントを作成し、コンポーネント・ウィザード でそれらを統合 ■ すべてのコンポーネントを Avalon スイッチ・ファブリックで自動的 に相互接続 欠点 ■ SOPC Builder システムの最大周波数で性能が制限される ■ インタフェースが 2 の累乗の幅に制限される

MegaWizard フロー

DDR および DDR2 SDRAM コントローラ・コンパイラの MegaWizard フローが持つ利点および欠点は、以下のとおりです。利点 ■ システム機能設定をより細かく制御可能 ■ DDR または DDR2 SDRAM インタフェースからペリフェラル・デバ イスにダイレクトに設計可能 ■ 高周波数動作を達成可能 欠点 ■ 設計時間が長い ■ 既存の SOPC Builder ペリフェラルを簡単に使用できない ■ インスタンス化ごとにレジスタ転送レベル(RTL)ファイルが必要

リリース情報

表 1–1に、このリリースの DDR および DDR2 SDRAM コントローラ・ コンパイラに関する情報を示します。サポートされる

デバイス・

ファミリ

下記で説明されているように、MegaCore®ファンクションは、ターゲッ トのアルテラ・デバイス・ファミリに対し、フル・サポートあるいは暫 定サポートを提供しています。 ■ フル・サポートとは、MegaCore ファンクションがデバイス・ファミ リの機能およびタイミング要件をすべて満たしており、製造デザイ ンで使用可能であることを意味します。 ■ 暫定サポートとは、MegaCore ファンクションがデバイス・ファミリ の機能要件はすべて満たしているが、タイミング要件については解 析中であることを意味します。注意しながら製造デザインで使用す ることは可能です。 表 1–2に、DDR および DDR2 SDRAM コントローラ・コンパイラがアル テラの各デバイス・ファミリに対して提供するサポート・レベルを示し ます。 表 1–1. DDR & DDR2 SDRAM コントローラのリリース情報 項目 説明 バージョン 3.4.1 リリース月 2006 年 6 月 製品コード IP-SDRAM/DDR (DDR SDRAM) IP-SDRAM/DDR2 (DDR2 SDRAM) プロダクト ID 0055 (DDR SDRAM) 00A7 (DDR2 SDRAM) 00A8(共通ライブラリ) ベンダ ID 6AF7 表 1–2. サポートされるデバイス・ファミリ (1 / 2) デバイス・ファミリ サポートの種類 DDR SDRAM DDR2 SDRAM Stratix® II フル・サポート フル・サポートバージョン

3.4.1 の新機能

■ Cyclone II デバイスをサポート特長

■ 業界標準のDDR & DDR2 SDRAMデバイスおよびモジュールをサポート ■ 1、2、4、または 8 つのチップ・セレクト信号 ■ 部分書き込み操作のためのデータ・マスク信号 ■ レイテンシを最小限に抑えるバンク管理アーキテクチャ ■ コンフィギュレーション可能なデータ幅 ■ DQS リード・ポストアンブル・コントロール・ロジック ■ カスタム・コントローラで使用するフリー・クリア・テキスト・デー タパス ■ 自動またはユーザ制御リフレッシュ ■ Registered DIMM(RDIMM)をサポート ■ Stratix および Stratix II サイド・バンクに対する非 DQS リード・モー ド(オプション) ■ IP Toolbench による制約スクリプトの生成 ■ デザイン例による迅速かつ容易な実装 ■ システム・タイミング解析 ■ OpenCore® Plus 評価版をサポート ■ SOPC Builder への対応 ■ アルテラでサポートしている VHDL、Verilog HDL シミュレータ上 で使用可能な IP ファンクション・シュミレーション・モデル概要

アルテラの DDR および DDR2 SDRAM コントローラ・コンパイラは、 DDR SDRAM コントローラ MegaCore ファンクションおよび DDR2 SDRAM コントローラ MegaCore ファンクションから構成されます。 Stratix II GX 暫定サポート 暫定サポート Stratix フル・サポート サポートなし Stratix GX フル・サポート サポートなし HardCopy® II 暫定サポート 暫定サポート Cyclone™ II フル・サポート フル・サポート Cyclone フル・サポート サポートなし その他のデバイス・ファミリ サポートなし サポートなし 表 1–2. サポートされるデバイス・ファミリ (2 / 2) デバイス・ファミリ サポートの種類 DDR SDRAM DDR2 SDRAMDDR および DDR2 SDRAM コントローラは、メモリ・デバイスの初期 化、SDRAM バンクの管理、および適切な間隔でのデバイスのリフレッ シュなど、DDR または DDR2 SDRAM を使用する際の複雑な処理を扱 います。DDR および DDR2 SDRAM コントローラは、ローカル・イン タフェースからのリードおよびライト要求を、必要なすべての SDRAM コマンド信号に変換します。

DDR SDRAM コントローラはアルテラの Stratix および Cyclone シリー ズに対して最適化されており、DDR2 SDRAM コントローラは Stratix II および Cyclone II デバイスに対してのみ最適化されています。これらの デバイスが持つ高度な機能により、DDR または DDR2 SDRAM デバイ スに直接インタフェースし、リードおよびライト方向で DQS 信号を使 用することができます。 図 1-1に、DDR または DDR2 SDRAM コントローラ MegaCore ファン クションで作成されるデザイン例を含む、システム・レベルの図を示し ます。 図 1-1. DDR & DDR2 SDRAM コントローラのシステム・レベルの図 図 1-1の注 : (1) Stratix シリーズおよび HardCopy II デバイスの場合のみ(オプション)。 DDR SDRAM Example Driver PLL DLL (1) DDR SDRAM Interface Pass or Fail Local Interface Example Design Control Logic (Encrypted) DDR SDRAM Controller Data Path (Clear Text)

IP Toolbench を SOPC Builder または Quartus II ソフトウェアのいずれで 使用する場合でも、デザイン例が生成され、PLL(Phase-Locked-Loop)、 サンプル・ドライバ、DDR または DDR2 SDRAM コントローラのカスタ ム・バリエーション、およびオプションの DLL(Stratix シリーズの場合 のみ)がインスタンス化されます。デザイン例は、ハードウェア上でシ ミュレーション、合成、および使用可能な完全に動作するデザインです。 サンプル・ドライバは、セルフ・テスト・モジュールでコントローラに リードとライトのコマンドを発行し、リード・データをチェックして、パ ス / フェイルおよびテスト完了の信号を出力します。 デザイン例にある、DDR または DDR2 SDRAM コントローラの暗号化 されたコントロール・ロジックは、独自のカスタム・ロジックに置き換 えることができ、これによってアルテラが提供するデータパスのソース を独自のコントロール・ロジックと共に使用できます。 DDR SDRAM コントローラと DDR2 SDRAM コントローラは、非常に よく似ています。相違点は以下のとおりです。 ■ 初期化タイミング(3–31 ページの「DDR SDRAM の初期化のタイミ ング」および3–33 ページの「DDR2 SDRAM の初期化タイミング」 を参照) ■ CAS レイテンシ・オプション : ● DDR SDRAM の場合、2.0、2.5、または 3.0 ● DDR2 SDRAM の場合、3、4、または 5 ■ バースト長 : ● DDR SDRAM の場合、2、4、または 8 ● DDR2 SDRAM の場合、4 ■ バンク : ● DDR SDRAM の場合、4 ● DDR2 SDRAM の場合、4 または 8 ■ DDR2 SDRAM における ODT のサポート

OpenCore Plus 評価機能

アルテラの無償 OpenCore Plus 評価版機能により、以下の処理を実行す ることができます。 ■ システム内でメガファンクションの動作のシミュレーション ■ デザインの機能を検証したり、サイズやスピードを素早く簡単に評 価可能 ■ MegaCore ファンクションを含むデザインに対し、実行時間に制限 のあるデバイス・プログラミング・ファイルを生成 ■ デバイスをプログラムしデザインをハードウェアで検証する。DDR および DDR2 SDRAM コントローラを使用したOpenCore Plus ハー

ドウェア評価について詳しくは、3–4 ページの「OpenCore Plus タイム・

アウト動作」および「Application Note 320: OpenCore Plus Evaluation

of Megafunctions」を参照してください。

性能

表 1–3に、Quartus® II ソフトウェアのバージョン 6.0 を使用した場合の DDR SDRAM コントローラの標準的な性能結果を示します。 デバイス性能の詳細については、関連するデバイス・ハンドブックを参 照してください。 表 1–4に、DDR SDRAM コントローラのロジック・エレメント(LE)の 標準的なサイズを示します。 表 1–3. 標準的な性能 デバイス システムの fMAX (MHz) DDR SDRAM DDR2 SDRAM Stratix II (EP2S60F1020C3) 200 267 (1)Stratix II GX (EP2SGX30CF780C3) 200 (2) 267 (1) & (2)

Stratix (EP1S25F780C5) 200 – Cyclone (EP1C20F400C6) 133 – Cyclone II (EP2C35F672C6) 167 167 表 1–3の注 : (1) 267 MHz(533 Mbps)を超えて最大 333 MHz(667 Mbps)の速度を達成 するソリューションについては、お問い合わせください。267 MHz を超え る速度を達成するには、新しいダイナミック自動キャリブレーション回路 が必要です。 (2) デバイス特性は未定です。 表 1–4. 標準的なサイズ (1 / 2) 注 (1) デバイス メモリ幅(ビット) LE 数またはALUT 数(2) ブロック数M4K RAM(3) Stratix II/ Stratix II GX 16 800 1 32 960 2 64 1,250 4 72 1,320 5

Stratix II GX 16 800 1 32 960 2 64 1,250 4 72 1,320 5 Stratix 16 750 1 32 830 2 64 1,000 4 72 1,040 5 Cyclone II 16 940 1 32 1,120 2 64 1,500 4 72 1,600 5 Cyclone 16 860 1 32 1,050 2 表 1–4の注 : (1) これらのサイズはあくまでも目安で、選択したパラメータによって異なり ます。これらの数値は各デバイス・ファミリのデフォルト設定で作成され、 インタフェースの幅のみが異なります。一般に、コントローラは約 700 個 の LE を使用しますが、データパスのサイズは、幅とパイプラインの段数お よび必要なクロッキング方式によって異なります。 (2) Stratix II デバイスは、アダプティブ・ルックアップ・テーブル(ALUT)を 使用しています。その他のデバイスは、ロジック・エレメント(LE)です。 (3) コントローラは、M4K RAM ブロックを使用してユーザ・ロジックからの ライト・データをバッファします。バースト長として 1(DDR SDRAM サ イドは 2)を選択した場合、このバッファは不要であり、データ幅に係わら ずユーザのバリエーションではメモリ・ブロックは使用されません。 表 1–4. 標準的なサイズ (2 / 2) 注 (1) デバイス メモリ幅(ビット) LE 数またはALUT 数(2) ブロック数M4K RAM(3)

デザイン・

フロー

OpenCore® Plus 機能を使用して、DDR または DDR2 SDRAM コントロー

ラ MegaCore ファンクションを評価するには、デザイン・フローに以下 のステップを含めます。 1. DDR および DDR2 SDRAM コントローラ・コンパイラを入手してイ ンストールします。 インストール方法について詳しくは、「DDR および DDR2 SDRAM コン トローラ・コンパイラ v3.4.1 リリース・ノート」を参照してください。 図 2-1に、DDR および DDR2 SDRAM コントローラをインストールした後 のディレクトリ構造を示します(<path> はインストール・ディレクトリ)。 図 2-1. ディレクトリ構造

SOPC Builder または MegaWizard®のデザイン・フローのいず

れかを使用できます。 <path>

common

Contains the common MegaCore function files.

ip_toolbench

Contains the common IP Toolbench files.

ddr_ddr2_sdram-v3.4.1

Contains the DDR and DDR2 SDRAM Controller Compiler files and documentation.

constraints

Contains scripts that generate an instance-specific Tcl script for each instance of the DDR or DDR2 SDRAM Controller in various Altera devices.

dat

Contains a data file for each Altera device combination

that is used by the Tcl script to generate the instance-specific Tcl script.

doc

Contains the documentation for the MegaCore functions.

lib

Contains encrypted lower-level design files and some clear-text example files that are used in the design flow. After installing the MegaCore function, you should set a user library in the Quartus II software that points to this directory.

This library allows you to access all the necessary MegaCore files.

system_timing

2. SOPC Builder のデザイン・フローでは、以下のステップを実行する 必要があります。

a. SOPC Builder では、IP Toolbench を使用して DDR または DDR2

SDRAM コントローラ MegaCore ファンクションのカスタム・ バリエーションを作成し、SOPC Builder システムの残りを実装 して生成します。 b. DDR または DDR2 SDRAM デザイン例に基づいてデザインを 作成します。 c. IP 機能シミュレーション・モデルを使用して機能シミュレー ションを実行します。 IP 機能シミュレーション・モデルについて詳しくは、「Quartus II ハンド ブック Volume 3」の「サードパーティ・シミュレーション・ツールに よるアルテラ IP のシミュレーション」の章を参照してください。 d. Quartus II ソフトウェアを使用して、PLL を編集し、制約を追 加し、コンパイルして、コンパイル後のタイミング解析を実行 します。 e. 適切な開発ボードがある場合は、OpenCore Plus 期限付きプロ グラミング・ファイルを生成できます。このファイルを使用す ると、デザインの動作をハードウェアで検証できます。 3. MegaWizard のデザイン・フローでは、以下のステップが含まれて います。

a. MegaWizard Plug-In Manager から IP Toolbench を使用して、 DDR または DDR2 SDRAM コントローラ MegaCore ファンク ションのカスタム・バリエーションを作成します。 b. IP Toolbench で生成された IP 機能シミュレーション・モデルを 使用して、デザイン例とサンプル・ドライバの動作を検証しま す。 IP 機能シミュレーション・モデルについて詳しくは、「Quartus II ハンド ブック Volume 3」の「サードパーティ・シミュレーション・ツールに よるアルテラ IP のシミュレーション」の章を参照してください。 c. Quartus II ソフトウェアを使用して、PLL を編集し、デザイン 例に制約を追加し、デザイン例をコンパイルして、コンパイル

d. ゲート・レベル・タイミング・シミュレーションを実行します。 あるいは、最適な開発ボードがある場合は、OpenCore Plus 期 限付きプログラミング・ファイルを生成できます。このファイ ルを使用すると、ハードウェアでデザイン例の動作を検証でき ます。 4. DDR または DDR2 SDRAM コントローラ MegaCore ファンクショ ンのライセンスを購入するか、暗号化された DDR または DDR2 SDRAM コントローラのコントロール・ロジックを独自のロジック に置き換えてクリアテキスト・データパスを使用します。 DDR または DDR2 SDRAM コントローラのライセンスを 購入する場合は、ライセンスを設定する必要があります。 5. ボード上のアルテラ・デバイス用のプログラミング・ファイルを生 成します。 6. 完成したデザインを使用してアルテラ・デバイスをプログラムします。 7. デザイン検証を実行します。

SOPC Builder

のデザイン・

フロー

SOPC Builder のデザイン・フローでは、以下のステップを実行する必要 があります。 1. 2–3 ページの「DDR & DDR2 SDRAM コントローラの実習」 2. 2–14 ページの「トップレベル・デザインの作成」 3. 2–15 ページの「SOPC Builder デザインのシミュレーション」 4. 2–15 ページの「SOPC Builder デザインのコンパイル」 5. 2–17 ページの「デバイスのプログラム」DDR & DDR2 SDRAM コントローラの実習

この実習では、アルテラの DDR SDRAM コントローラ IP Toolbench と Quartus II ソフトウェアを使用して、SOPC Builder システムで DDR ま たは DDR2 SDRAM コントローラの MegaCore ファンクションのカスタ ム・バリエーションを作成する方法について説明します。 ウィザードでの操作に沿って、各ステップについて詳しく説明します。 この SOPC Builder での実習で使用するフローにより、PLL は DDR また は DDR2 SDRAM コントローラに適切に接続され、ウィザードで生成し た制約が正しく適用されます。SOPC Builder について詳しくは、「Quartus II ハンドブック Volume 4」 を参照してください。

この実習では、以下のステップを実行します。

■ 2–4 ページの「新規 Quartus II プロジェクトの作成」

■ 2–6 ページの「SOPC Builder および IP Toolbench の起動」

■ 2–8 ページの「Step 1: Parameterize」

■ 2–10 ページの「Step 2: Constraints」

■ 2–12 ページの「Step 3: Add/Update Component」

新規 Quartus II プロジェクトの作成

New Project Wizard を使用して、Quartus II プロジェクトを新規作成す

る必要があります。このウィザードでは、プロジェクトの作業ディレク トリを指定し、プロジェクト名を割り当てて、トップレベル・デザイン・ エンティティを指定します。新規プロジェクトを作成するには、以下の ステップに従います。

1. Windows スタート・メニューからプログラム > Altera > Quartus II < バージョン > を選択して、Quartus II ソフトウェアを起動します。 Quartus II Web Edition ソフトウェアも同様に使用できます。

2. New Project Wizard(File メニュー)を選択します。

3. New Project Wizard Introduction の Next をクリックします(イン

トロダクションを以前にオフにしている場合は表示されません)。 4. New Project Wizard: Directory, Name, Top-Level Entity ページで、

以下の情報を入力します。 a. プロジェクトの作業ディレクトリを指定します。例えば、この 実習では c:\altera\temp\ddr_project ディレクトリを使用しま す。 b. プロジェクトの名前を指定します。この実習では、プロジェク ト名に project を使用します。 Quartus IIソフトウェアは、プロジェクトと同じ名前のトッ プレベル・デザイン・エンティティが自動的に指定されま す。これを変更しないでください。

指定したディレクトリが存在しない場合は、そのディレク トリを作成するかどうかを確認するメッセージが表示され ます。Yes をクリックして、ディレクトリを作成します。

6. Linux および Solaris オペレーティング・システムの場合は、New

Project Wizard: Add Files ページで以下のステップを実行してユー ザ・ライブラリを追加します。

a. User Library Pathnames をクリックします。

b. Library nameボックスに<path>\ddr_ddr2_sdram-v3.4.1\ lib\を入力します(<path>はDDRおよびDDR2 SDRAMコント ローラ・をインストールしたディレクトリ)。 c. Add をクリックして、Quartus II プロジェクトのパスを追加し ます。 d. OK をクリックして、プロジェクトにライブラリのパスを保存 します。

7. Next をクリックしてこのページを閉じ、New Project Wizard: Family

& Device Settings ページを表示します。

8. New Project Wizard: Family & Device Settings ページで、Family リストからサポートされているターゲット・デバイス・ファミリと し て、Cyclone™、Cyclone II、HardCopy II、Stratix®、Stratix GX、 Stratix II、または Stratix II GX デバイスを選択します。Do you want to assign a specific device? と表示されたら、Yes を選択します。

Do you want to assign a specific device? では必ず Yes を 選択して、特定のデバイスを選択してください。No を選 択すると、IP Toolbench が正しく機能しなくなります。 DDR2 SDRAM コントローラは、Cyclone II、HardCopy II、 Stratix II GX、および Stratix II デバイスのみをサポートし ます。

特定のアルテラ開発ボードをターゲットにする場合は、適 切なターゲット・デバイスとメモリ・タイプを選択します。

9. Available Devices リストでターゲット・デバイスを選択します。

10. New Project Wizard の残りのページはオプションです。Finish をク リックして、Quartus II プロジェクトを完了します。

SOPC Builder および IP Toolbench の起動

SOPC Builder を起動するには、以下のステップに従います。

1. SOPC Builder(Tools メニュー)を選択します。

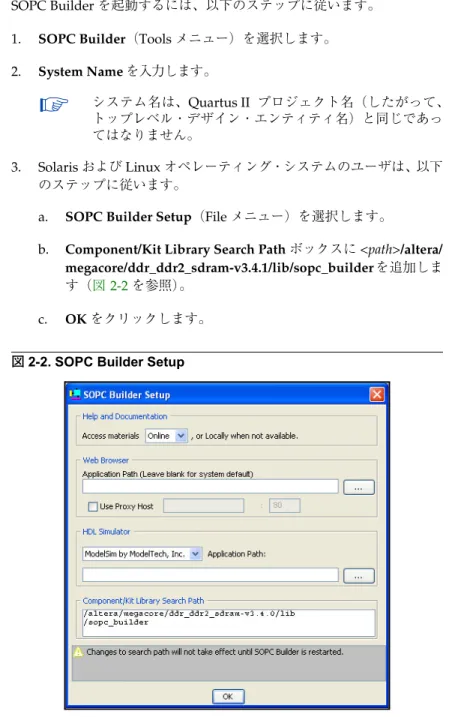

2. System Name を入力します。 システム名は、Quartus II プロジェクト名(したがって、 トップレベル・デザイン・エンティティ名)と同じであっ てはなりません。 3. Solaris および Linux オペレーティング・システムのユーザは、以下 のステップに従います。

a. SOPC Builder Setup(File メニュー)を選択します。

b. Component/Kit Library Search Path ボックスに<path>/altera/ megacore/ddr_ddr2_sdram-v3.4.1/lib/sopc_builder を追加しま

す(図 2-2を参照)。

c. OK をクリックします。

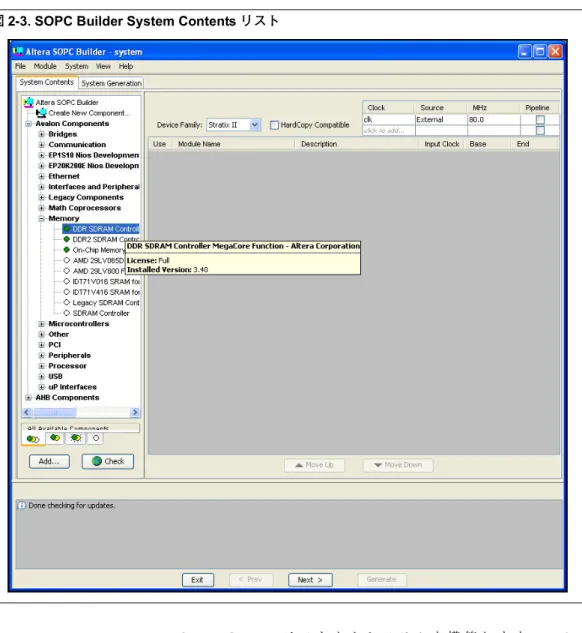

4. Clock (MHz) の値を入力します。例えば、80.0 を入力します

(図 2-3を参照)。

図 2-3. SOPC Builder System Contents リスト

5. System Contents リ ス ト か ら シ ス テ ム を 構 築 し ま す。Avalon Components > Memory ディレクトリで DDR SDRAM Controller または DDR2 SDRAM Controller を選択し、Add をクリックしま す。DDR SDRAM コントローラ IP Toolbench が開きます。

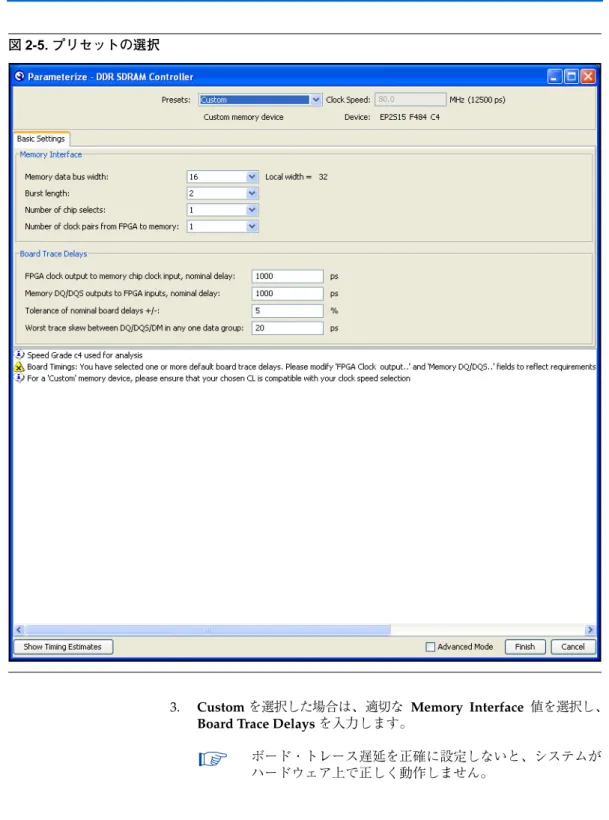

Step 1: Parameterize DDR または DDR2 SDRAM コントローラをパラメータ化するには、以 下のステップに従います。 1. Step 1: Parameterize をクリックして、カスタム・バリエーションを パラメータ化します(図 2-4を参照)。 図 2-4. Step 1: Parameterize 2. Presets リストで、特定のメモリ・デバイス、アルテラ開発ボード、 または Custom を選択します(2–9 ページの図 2-5を参照)。 アルテラのボードをターゲットにする場合、Basic Settings タブの設定および Advanced Mode の設定はすべてそのま まボードに適用できます。 IP Toolbench でクロック速度を変更することはできませ ん。システムのクロック速度を変更するには、IP Toolbench を閉じて2–7 ページのステップ4に戻ります。

図 2-5. プリセットの選択

3. Custom を選択した場合は、適切な Memory Interface 値を選択し、

Board Trace Delays を入力します。

ボード・トレース遅延を正確に設定しないと、システムが ハードウェア上で正しく動作しません。

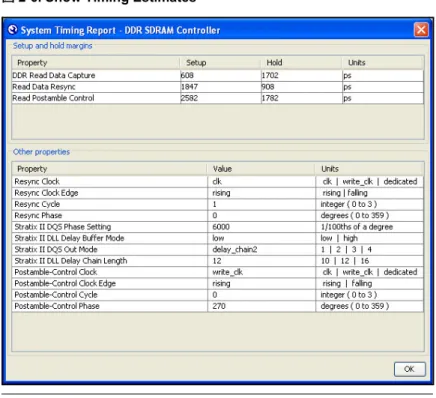

4. パラメータ化画面(図 2-6を参照)で Show Timing Estimates をク リックすると、システムのタイミング解析の結果をいつでも表示で きます。

図 2-6. Show Timing Estimates

5. Advanced Mode をオンにすると、DDR または DDR2 SDRAM コン

トローラで変更可能なすべての設定をいつでも表示できます。

Advanced Mode 設 定 に つ い て 詳 し く は、2–22 ペ ー ジ の「Step 1:

Parameterize」を参照してください。

Step 2: Constraints

デバイスの制約を選択するには、以下のステップに従います。

アルテラのボードをターゲットにすることを選択した場合、す べての制約の設定はそのボードに適合しています。

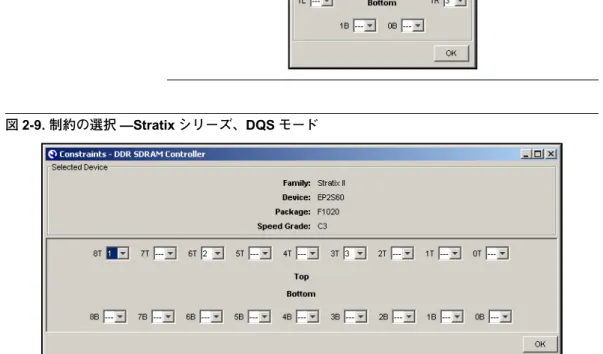

6. Step 2: Constraints をクリックします(図 2-7を参照)。 図 2-7. Step 2: Constraints 7. 各 DDR SDRAM バイト・グループのデバイス上での位置を選択し ます(2–12 ページの図 2-8および2–12 ページの図 2-9を参照)。バ イト・グループを配置するには、選択した位置にあるドロップダウ ン・ボックスでバイト・グループを選択します。 フロアプランは、Quartus II フロアプランナの方向と一致 しています。レイアウトは、上から見たダイで表されます。 バイト・グループは、4 本または 8 本の DQ ピン、1 本の DM ピン、および 1 本の DQS ピンで構成されます。 アル テラの ボード のプリ セッ トを使 用する 場合は、IP Toolbench で正しい位置が選択されます。

図 2-8. 制約の選択

図 2-9. 制約の選択 —Stratix シリーズ、DQS モード

Step 3: Add/Update Component

コンポーネントを追加または更新してシステムを生成するには、以下の ステップに従います。

8. Step 3: Add/Update Component をクリックして、SOPC Builder に

カスタム・バリエーションを追加します(図 2-10を参照)。

図 2-10. Step 3: Add/Update Component

9. SOPC Builder は、DDR または DDR2 SDRAM コントローラのバリ

エーション名にモジュール名(デフォルトでは ddr_sdram_0)を使 用します。この名前は必要に応じて変更できます。

10. SOPC Builder で、SOPC Builder システムの残りを作成します。 11. オプション。System Generation タブをクリックし、Simulation を

オンにします。Create Simulator Project Files をクリックして、プ ロジェクトのシミュレーション・ファイルを作成します。 これらのシミュレーション・モデル出力ファイルは、シミュレー ション目的にのみ使用し、特に合成やその他の目的には使用し ません。これらのモデルを合成に使用すると、機能しないデザ インが作成されます。 Nios II シミュレーション・フローについて詳しくは、「Quartus II ハン ドブック Volume 4」を参照してください。

12. System Generation タブをクリックし、Generate をクリックします。

Generate をクリックする前に、システムに少なくとも1 つ

SOPC Builder で SOPC Builder システム・ファイルが生成されます。 SOPC Builder プロジェクトを Quartus II ソフトウェアでコンパイルする 場合は、SOPC Builder システム、PLL、および DLL をインスタンス化

するトップレベル・デザインを事前に作成する必要があります(2–14

ページの「トップレベル・デザインの作成」を参照)。

SOPC Builder では SOPC Builder システム・ファイルに加えて、<variation name>_debug_design.v または .vhd が生成されます。デザイン例には、 DDR または DDR2 SDRAM コントローラ、PLL、およびサンプル・ドラ イバが含まれますが、SOPC Builder コンポーネントは含まれていません (1–3 ページの図 1-1を参照)。 デザイン例を使用してボードをテストおよびシミュレーションすると、 DDR または DDR2 SDRAM インタフェースを理解することができます。

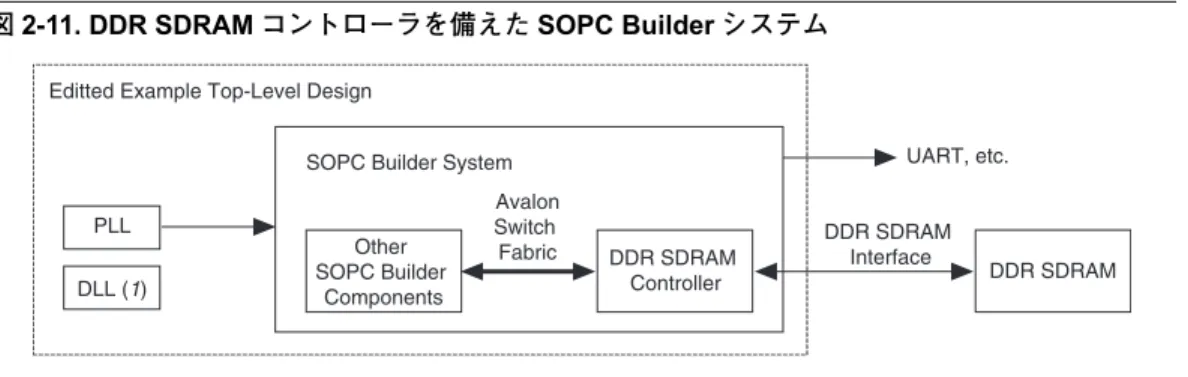

トップレベル・デザインの作成

PLL、オプションのフィードバック PLL、および DLL を SOPC Builder システムに接続してインスタンス化する際のガイドとして、デザイン例、 <variation name>_debug_design.v、または .vhd を使用します。サンプ ル・ドライバとコントローラを削除し、SOPC Builder で生成されたシス テムに置き換える必要があります(図 2-11を参照)。 ウィザードで生成した制約を正しく適用するには、制約スクリ プトで自動的に階層を検出できるようにするか、またはHierarchy タブの階層とピン名を HDL での名前と一致させます。 その他のデザイン例については、Nios II 開発キットの Cyclone II リファ レンス・デザインを参照してください。図 2-11. DDR SDRAM コントローラを備えた SOPC Builder システム

DDR SDRAM Other

SOPC Builder Components SOPC Builder System

DDR SDRAM Interface

UART, etc. Editted Example Top-Level Design

DDR SDRAM Controller Avalon Switch Fabric PLL DLL (1)

SOPC Builder デザインのシミュレーション

SOPC Builder デザインをシミュレートするには、Nios II シミュレーショ ン・フローを使用するか、または独自のテストベンチを作成して、トッ プレベル・デザインとメモリ・モデルをインスタンス化します。 Nios II シミュレーション・フローについて詳しくは、「Quartus II ハン ドブック Volume 4」を参照してください。

SOPC Builder デザインのコンパイル

ここで、PLL を編集し、Quartus II ソフトウェアを使用してデザイン例 をコンパイルし、コンパイル後のタイミング解析を実行できます。 PLL の編集 IP Toolbench で生成するデザイン例には PLL が含まれています。この PLL は、入力と出力のクロック比が 1:1 で、IP Toolbench で入力したク ロック周波数を持っています。また、IP Toolbench は、デザインのすべ ての関連クロック出力の位相オフセットもすべて正しく設定します。 PLL 入力クロックを編集して、システム要件に適合させることができま す。Automatically generate the PLL をオフにして IP Toolbench を再実 行すれば、この PLL は上書きされません。編集内容も失われません。Use fed-back clock for resynchronization をオンにすると、IP Toolbench は第 2 の PLL、つまりフィードバック PLL を生成し ます。フィードバック PLL を編集する必要はありません。

PLL について詳しくは、3–15 ページの「PLL コンフィギュレーション」

を参照してください。

サンプル PLL を編集するには、以下のステップに従います。

1. MegaWizard Plug-In Manager(Tools メニュー)を選択します。

2. Edit an existing custom megafunction variation を選択し、Next をクリックします。

3. Quartus II プロジェクト・ディレクトリで、VHDL の場合は

ddr_pll_<device name>.vhd を選択し、Verilog HDL の場合は ddr_pll_<device name>.v を選択します。

4. Next をクリックします。

altpll メガファンションについて詳しくは、Quartus II ヘルプを参照す

るか、またはaltpll MegaWizard Plug-In の Documentation をクリッ

クしてください。

タイミング解析のコンパイルと実行

Quartus II ソフトウェアでは SOPC Builder デザインをコンパイルする前 に、IP Toolbench で生成した Tcl 制約スクリプト auto_add_constraints.tcl が実行されます。

auto_add_constraints.tcl スクリプトは、デザイン内の各バリエーション の add_constraints_for_<variation name>.tcl スクリプトを呼び出します。 add_constraints_for_<variation name>.tcl スクリプトは、該当するバリ エーションにこれまでに追加された固有の制約をチェックし、それらを 削除し、そのバリエーションに制約を追加します。 制約スクリプトはデザインを解析し、綿密に調整して、ユーザのバリエー ションに自動的に階層を抽出します。制約スクリプトでデザインの解析 や綿 密な 調整 を行 わな いよ うに する には、ウ ィザ ード の Enable hierarchy control をオンにし、データパスに正しい階層パスを入力しま す(2–32 ページのステップ24を参照)。 制約スクリプトを実行すると、別のスクリプト remove_constraints_for_ <variation name>.tcl が作成されます。これを使用すると、デザインから 制約を削除できます。

9 Start Compilation(Processing メニュー)を選択します。これによっ

て、制約追加スクリプトが実行され、デザインがコンパイルされて、 タイミング解析が実行されます。

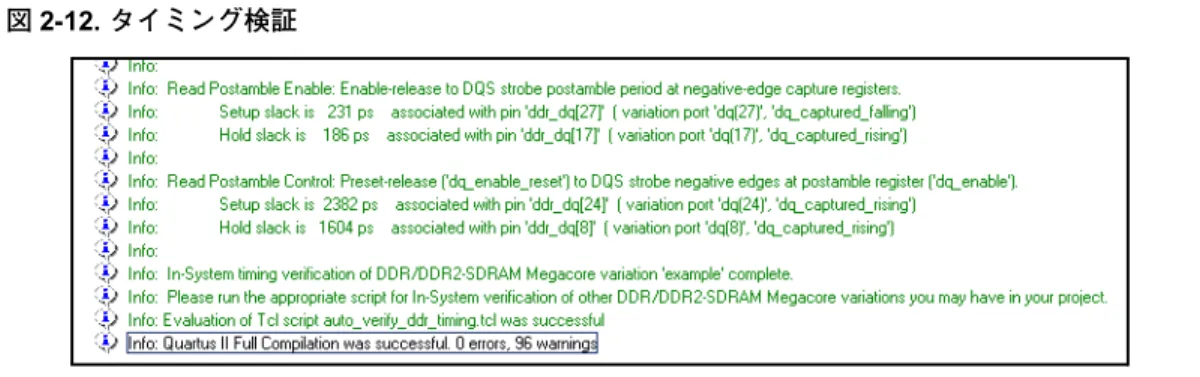

コンパイルが完了すると、Quartus II processing messages タブにコンパ イル後のタイミング解析結果が表示されます。この結果もプロジェクト・ ディレクトリの <variation name>_post_summary.txt ファイルに書き込ま れます。 この結果は、各種タイミング要求それぞれにどれだけのスラック(負の スラックはタイミングを満たしていないことを意味する)があるかを示 しています。Messages ウィンドウには、デザインの各種タイミング・ マージンが表示されます(図 2-12を参照)。

図 2-12. タイミング検証

タイミング検証スクリプトが、デザインがタイミングを満たしているこ とをレポートする場合、DDR または DDR2 SDRAM コントローラは正 常に生成されて実装されています。

タイ ミン グが 要件 に達 して いな い場合 は、IP Toolbench の Manual Timings タブで再同期およびポストアンブル・クロック位相を調整しま

す(A–1 ページの「手動タイミング設定」を参照)。

タイミングの達成方法について詳しくは、付録 B、Nios 開発ボード、

Cyclone II エディション上の DDR SDRAMを参照してください。

Quartus II Assignment Editorに制約を表示するには、Assignment Editor (Assignments メニュー)を選択します。

Quartus II Assignment Editor に “?” 文字が表示されている場合、 Quartus II ソフトウェアは、制約を適用すべきエンティティを検 出できていません。これは階層の不一致が原因として考えられま す。制約スクリプトを編集するか、または Hierarchy タブで正し い階層パスを入力します(2–32 ページのステップ24を参照)。 制約について詳しくは、3–22 ページの「制約」を参照してください。

デバイスのプログラム

SOPC Builder デザインをコンパイルした後は、ゲート・レベル・シミュ レーションを実行したり(2–15 ページの「SOPC Builder デザインのシ ミュレーション」を参照)、ターゲットのアルテラ・デバイスをプログラ ムしてハードウェアでの SOPC Builder デザインを検証することができ ます。アルテラの無償の OpenCore Plus 評価機能では、ライセンスを購入する 前に、DDR または DDR2 SDRAM コントローラ MegaCore ファンクショ ンを評価できます。OpenCore Plus 評価を使用すると、期限付きプログ ラミング・ファイルを生成できます。 DDR または DDR2 SDRAM コントローラ MegaCore ファンクションを 使用した OpenCore Plus ハードウェア評価について詳しくは、1–4 ペー

ジの「OpenCore Plus 評価機能」、3–4 ページの「OpenCore Plus タイ

ム・ア ウ ト 動 作」、お よ び「Application Note 320: OpenCore Plus

Evaluation of Megafunctions」を参照してください。

MegaWizard

のデザイン・

フロー

MegaWizard のデザイン・フローでは、以下のステップが含まれていま す。 ■ 2–18 ページの「DDR & DDR2 SDRAM コントローラの実習」 ■ 2–42 ページの「デザイン例のシミュレーション」 ■ 2–48 ページの「デザイン例のコンパイル」 ■ 2–52 ページの「デバイスのプログラム」 ■ 2–52 ページの「ユーザ・デザインの実装」DDR & DDR2 SDRAM コントローラの実習

SOPC Builder を使用しない場合、この実習ではアルテラ DDR および DDR2 SDRAM コントローラ IP Toolbench および Quartus II ソフトウェ アを使用して、DDR または DDR2 SDRAM コントローラ MegaCore ファ ンクションのカスタム・バリエーションを作成する方法について説明し ます。ウィザードでの操作に沿って、各ステップについて詳しく説明し ます。HardCopy IIデバイスの使用方法について詳しくは、付録 C、HardCopy II

デザインの実習を参照してください。

この実習では、以下のステップを実行します。

■ 2–19 ページの「新規 Quartus II プロジェクトの作成」

■ 2–20 ページの「MegaWizard Plug-In Manager からの IP Toolbench

の起動」

■ 2–22 ページの「Step 1: Parameterize」

■ 2–35 ページの「Step 2: Constraints」

■ 2–37 ページの「Step 3: Set Up Simulation」

新規 Quartus II プロジェクトの作成

New Project Wizard を使用して、Quartus II プロジェクトを新規作成す

る必要があります。このウィザードでは、プロジェクトの作業ディレク トリを指定し、プロジェクト名を割り当てて、トップレベル・デザイン・ エンティティを指定します。新規プロジェクトを作成するには、以下の ステップに従います。

1. Windows スタート・メニューからプログラム > Altera > Quartus II < バージョン > を選択して、Quartus II ソフトウェアを起動します。 Quartus II Web Edition ソフトウェアも同様に使用できます。

2. New Project Wizard(File メニュー)を選択します。

3. New Project Wizard Introduction の Next をクリックします(イン

トロダクションを以前にオフにしている場合は表示されません)。 4. New Project Wizard: Directory, Name, Top-Level Entity ページで、

以下の情報を入力します。 a. プロジェクトの作業ディレクトリを指定します。例えば、この 実習では c:\altera\temp\ddr_project ディレクトリを使用しま す。 b. プロジェクトの名前を指定します。この実習では、プロジェク ト名に project を使用します。 Quartus IIソフトウェアは、プロジェクトと同じ名前のトッ プレベル・デザイン・エンティティが自動的に指定されま す。これを変更しないでください。

5. Next をクリックしてこのページを閉じ、New Project Wizard: Add

Files ページを表示します。

指定したディレクトリが存在しない場合は、そのディレク トリを作成するかどうかを確認するメッセージが表示され ます。Yes をクリックして、ディレクトリを作成します。

6. Linux および Solaris オペレーティング・システムの場合は、New

Project Wizard: Add Files ページで以下のステップを実行してユー ザ・ライブラリを追加します。

a. User Library Pathnames をクリックします。

b. Library nameボックスに<path>\ddr_ddr2_sdram-v3.4.1\ lib\を入力します(<path>はDDRおよびDDR2 SDRAMコント ローラ・をインストールしたディレクトリ)。

c. Add をクリックして、Quartus II プロジェクトのパスを追加し ます。

d. OK をクリックして、プロジェクトにライブラリのパスを保存

します。

7. Next をクリックしてこのページを閉じ、New Project Wizard: Family

& Device Settings ページを表示します。

8. New Project Wizard: Family & Device Settings ページで、Family リ ス ト か らタ ー ゲ ッ ト・デ バ イ ス・フ ァ ミ リと し て、Cyclone、 Cyclone II、HardCopy II、Stratix、Stratix GX、Stratix II、ま た は Stratix II GXデバイスを選択します。Do you want to assign a specific device? と表示されたら、Yes を選択します。

Do you want to assign a specific device? では必ず Yes を 選択して、特定のデバイスを選択してください。No を選 択すると、IP Toolbench が正しく機能しなくなります。 DDR2 SDRAM コントローラは、Cyclone II、HardCopy II、 Stratix II GX、および Stratix II デバイスのみをサポートし ます。

特定のアルテラ開発ボードをターゲットにする場合は、適切 なターゲット・デバイスとメモリ・タイプを選択します。

9. Available Devices リストでターゲット・デバイスを選択します。

10. New Project Wizard の残りのページはオプションです。Finish をク リックして、Quartus II プロジェクトを完了します。

新しい Quartus II プロジェクトの作成が終了しました。

MegaWizard Plug-In Manager からの IP Toolbench の起動

Quartus II ソフトウェアのウィザードを起動するには、以下のステップ に従います。

1. MegaWizard Plug-In Manager コマンド(Tools メニュー)を選択

して、MegaWizard® Plug-In Manager を起動します。MegaWizard

Plug-In Manager ダイアログ・ボックスが表示されます。

MegaWizard Plug-In Manager の使用方法について詳しく は、Quartus II ヘルプを参照してください。

3. Interfaces > Memory Controllers ディレクトリを展開し、DDR SDRAMController v3.4.1 または DDR2 SDRAM Controller v3.4.1 をクリックします。

4. デザインの出力ファイル・タイプを選択します。ウィザードでは

VHDL と Verilog HDL をサポートしています。

5. MegaWizard Plug-In Manager に、New Project Wizard で指定した プロジェクト・パスが表示されます。MegaCore ファンクション出 力ファイル <project path>\<variation name>のバリエーション名を追

加します。2–21 ページの図 2-13に、これらの設定を行った後のウィ ザードを示します。 <variation name> の名前は、プロジェクト名およびトップ レベル・デザイン・エンティティ名と異なっていなければ なりません。 図 2-13. MegaCore ファンクションの選択 6. Next をクリックして、IP Toolbench を起動します。

Step 1: Parameterize

MegaCore ファンクションをパラメータ化するには、以下のステップに 従います。

パラメータについて詳しくは、3–40 ページの「パラメータ」を参照して

ください。

1. IP Toolbench の Step 1: Parameterize をクリックします(図 2-14を 参照)。 図 2-14. IP Toolbench—Parameterize 2. Presets リストで、特定のメモリ・デバイス、アルテラ開発ボード、 または Custom を選択します(2–23 ページの図 2-15を参照)。 \constraints ディレクトリ内の memory_types.dat ファイ ルを編集すると、このリストに独自のメモリ・デバイスを 追加できます。

図 2-15. メモリ・パラメータ

3. Clock Speed をMHz で入力します。例えば、200.0 を入力します。

制約スクリプト、タイミング解析、およびデータパスは、このクロッ ク速度を使用します。使用する値に設定する必要があります。DDR SDRAM コントローラ IP Toolbench を初めて使用する場合、または Automatically generate the PLL をオンにしている場合、この値は IP Toolbench で生成した PLL の入力および出力クロックに使用され

4. メモリ・パラメータを選択します(図 2-15を参照)。

a. メモリ・インタフェース・パラメータを選択します。

b. メモリ・プロパティを選択します。

c. Registered DIMM または Unbuffered memory を選択します。

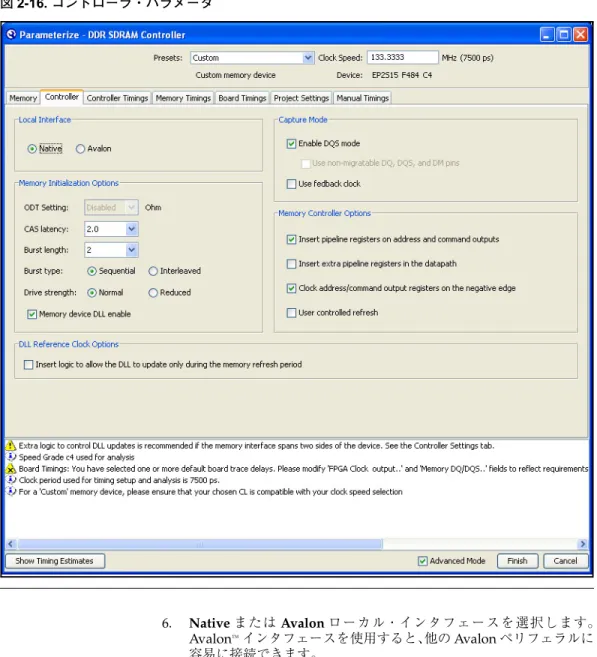

バッファなしのモジュールまたはデバイスを使用する場合 は、Unbuffered memory を選択します。 メモリ・パラメータについて詳しくは、3–41 ページの「メモリ」を参照 してください。 5. Controller タブをクリックします(2–25 ページの図 2-16を参照)。 コントローラ・パラメータについて詳しくは、3–42 ページの「コント ローラ」を参照してください。

図 2-16. コントローラ・パラメータ

6. Native または Avalon ローカル・インタフェースを選択します。

Avalon™インタフェースを使用すると、他の Avalon ペリフェラルに

容易に接続できます。

Avalon インタフェースについて詳しくは、「Avalon Bus Specification Reference Manual」を参照してください。

7. 関連するクロッキング・オプションをオンにします。

9. メモリ・コントローラ・オプションを選択します。 10. 関連する DLL 基準クロック・オプションをオンにします。 11. Controller Timings タブをクリックします(図 2-17を参照)。 コントローラのタイミングについて詳しくは、3–45 ページの「コント ローラのタイミング」を参照してください。 図 2-17. コントローラのタイミング

12. コントローラのタイミングがメモリのデータシートで規定される要 件を満たすように、Required カラムにメモリ・タイミング・パラ メータを入力します。ウィザードは、必要なコマンド間での適切な クロック・サイクル数を選択し、Actual カラムで遅延を計算します。

クロック・サイクル数を手動で入力するには、Manually

choose clock cycles をオンにし、Cycles カラムに値を入力

します。

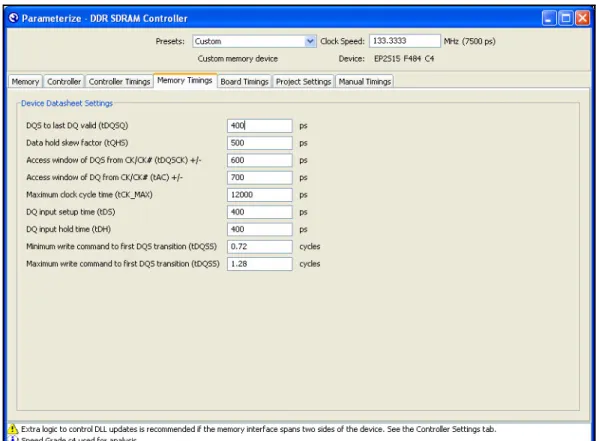

13. Memory Timings タブをクリックします(2–28 ページの図 2-18を

参照)。

メモリ・タイミングについて詳しくは、3–47 ページの「メモリ・タイミ

図 2-18. Memory Timings

14. Custom メモリ・デバイスを選択した場合、選択したメモリのデー タシートからデバイス設定を入力します。そうでない場合は、選択 したメモリ・タイプのデバイス設定が自動的に入力されます。

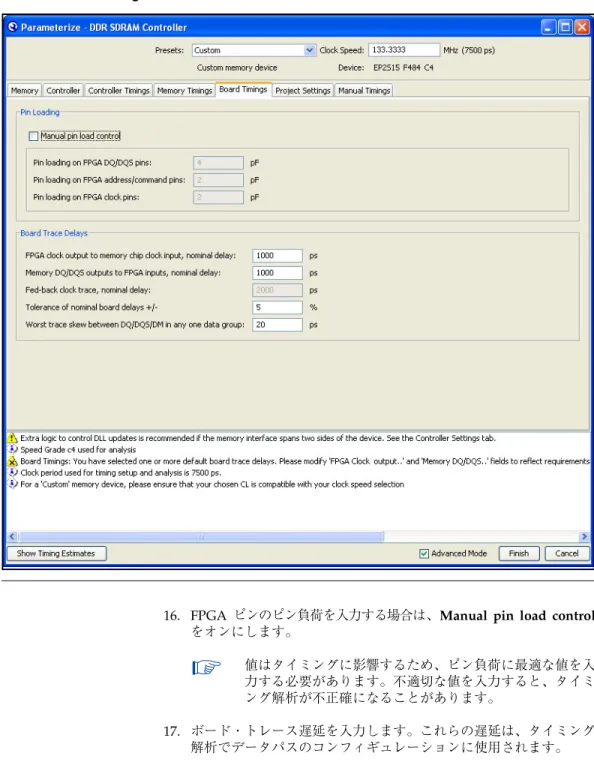

図 2-19. Board Timings

16. FPGA ピンのピン負荷を入力する場合は、Manual pin load control をオンにします。 値はタイミングに影響するため、ピン負荷に最適な値を入 力する必要があります。不適切な値を入力すると、タイミ ング解析が不正確になることがあります。 17. ボード・トレース遅延を入力します。これらの遅延は、タイミング 解析でデータパスのコンフィギュレーションに使用されます。

ボード・トレース遅延を正確に設定しないと、システムが ハードウェア上で正しく動作しません。

18. パラメータ化画面(図 2-20を参照)で Show Timing Estimates を

クリックすると、システムのタイミング解析の結果をいつでも表示 できます。 図 2-20. タイミングの表示 19. Project Settings タブをクリックします(図 2-21を参照)。 プロジェクト設定について詳しくは、3–49 ページの「プロジェクトの設 定」を参照してください。

図 2-21. Project Settings 20. メモリ (+) をドライブするクロックのピン名を入力します。メモリ (–) をドライブするクロックのピン名を入力します。フィードバッ ク・クロック入力の名前は IP Toolbench によって自動的に提案され ますが、必要に応じて編集できます(2–31 ページの図 2-21を参照)。 ピン名は、複数のクロック・ペアがある場合でも[0] で終 わる必要があります。

提案されたクロック・ピン名は、トップレベル・デザイン・ ファイルのクロック・ピン名を編集した場合にのみ変更し ます。クロック・ピン名を変更すると、トップレベル・デ ザイン例のクロック出力およびフィードバック・クロック の名前が変更されます。

21. Update the example design file that instantiates the controller variation がオンになっていることを確認します。これがオンになっ ていると、デザイン例とテストベンチは、IP Toolbench で自動的に 更新されます。

22. アルテラでは、Automatically apply datapath-specific contraints to the Quartus II project と Automatically verify datapath-specific timing in the Quartus II project をオンにすることを推奨していま す。これらをオンにすると、デザイン例のコンパイル時にこれらの スクリプトが Quartus II ソフトウェアで自動的に実行されます。 23. PLL を編集したが、バリエーションの再生成時に PLL をウィザード

で再生成したくない場合は、Update the example design PLLs をオ フにします。 24. 制約スクリプトはデザインを解析し、綿密に調整して、ユーザのバ リエーションに自動的に階層を抽出します。制約スクリプトでデザ インの解析および綿密な調整を実行しないようにするには、Enable hierarchy control をオンにし、バリエーションへの正しい階層パス を入力します。この階層パスは、DDR SDRAM コントローラのデー タパスへのパスからトップレベル名を除いたパスです。図 2-22に、 システム例を示します。 制約は、(コントローラではなく)データパスに適用されます。 そのため、コントローラ・ロジックを独自のコントローラに置 き換えても、制約追加スクリプトは有効のままです。したがっ て、エンティティおよびインスタンス名を維持している場合、 Quartus IIソフトウェアで制約がデザインに正しく追加されます。

図 2-22. システムの命名 25. IP Toolbench では、すべてのメモリ・インタフェース・ピンの名前 にプリフィックス(例えば、ddr_、ddr2_)を使用します。このカ スタム・バリエーションに関連付けるすべてのメモリ・インタフェー ス・ピンのプリフィックスを入力します。 26. 手動タイミング設定にアクセスする場合は、Manual Timing タブを クリックします(2–34 ページの図 2-23を参照)。そうでない場合は、

Finishをクリックして2–35ページの「Step 2: Constraints」に進みます。

手動タイミング設定について詳しくは、A–1 ページの「手動タイミング 設定」を参照してください。 DDR SDRAM Other Logic PLL DDR SDRAM Interface example_top

Example Top-Level Design

my_ddr_sdram DDR SDRAM Controller Data Path auk_ddr_sdram my_system System

図 2-23. 手動タイミング設定

27. Reclock resynchronized data to the positive edge リストで、 Automatic、Always、または Never を選択します。

28. Manual resynchronization control は、ウィザードで計算した値を 上書きする場合にのみオンにします。

再同期について詳しくは、A–1 ページの「手動タイミング設定」を参照 してください。

29. Manual postamble control は、ウィザードで計算した値を上書きす る場合にのみオンにします。 ほとんどの状況で、IP Toolbench はカスタム・バリエー ションの正しいポストアンブルを計算します。 ポストアンブルについて詳しくは、A–1 ページの「手動タイミング設定」 を参照してください。 30. タイミング解析オプションをオンにします。 31. Finish をクリックします。 Step 2: Constraints デバイスの制約を選択するには、以下のステップに従います。

1. IP Toolbench の Step 2: Constraints をクリックします(図 2-24を参 照)。

2. 各 DDR SDRAM バイト・グループのデバイス上での位置を選択し ます(2–36 ページの図 2-25および2–36 ページの図 2-26を参照)。 バイト・グループを配置するには、選択した位置にあるドロップダ ウン・ボックスでバイト・グループを選択します。 フロアプランは、Quartus II フロアプランナの方向と一致 します。レイアウトは、上から見たダイで表されます。バ イト・グループは、4 本または 8 本の DQ ピン、1 本の DM ピン、および 1 本の DQS ピンで構成されます。 アル テラの ボード のプリ セッ トを使 用する 場合は、IP Toolbench で正しい位置が選択されます。 図 2-25. 制約の選択 図 2-26. 制約の選択 —Stratix シリーズ、DQS モード

Step 3: Set Up Simulation IP 機能シミュレーション・モデルは、Quartus II ソフトウェアで生成さ れる、サイクルで正確な VHDL または Verilog HDL モデル・ファイル です。このモデルは、アルテラでサポートしている VHDL および Verilog HDL シミュレータで動作します。 これらのシミュレーション・モデル出力ファイルは、シミュレー ション目的にのみ使用し、特に合成やその他の目的には使用し ません。これらのモデルを合成に使用すると、機能しないデザ インが作成されます。 MegaCore ファンクション用の IP 機能シミュレーション・モデルを生成 するには、以下のステップに従います。

1. IP Toolbench の Step 3: Set Up Simulation をクリックします(図

2-27を参照)。

2. Generate Simulation Model をオンにします(図 2-28を参照)。 図 2-28. Generate Simulation Model

3. Language リストで、言語を選択します。 IP Toolbench が生成するテストベンチを使用するには、バ リエーション用に選択する言語と同じ言語を選択します。 4. OK をクリックします。 Step 4: Generate MegaCore ファンクションを生成するには、以下のステップに従います。

1. IP ToolbenchのStep 4: Generateをクリックします(図 2-29を参照)。 図 2-29. IP Toolbench—Generate

図 2-30. 生成レポート 表 2–1は、プロジェクト・ディレクトリに格納される可能性がある生成 されるファイルとその他のファイルを示しています。IP Toolbench レ ポートで指定されるファイルの名前とタイプは、デザインの作成に VHDL または Verilog HDL のいずれを使用したかによって異なります。 表 2–1. 生成されるファイル (1 / 3) 注 (1) & (2) ファイル名 説明

<variation name>.bsf MegaCore ファンクション・バリエーション用の

Quartus II シンボル・ファイルです。Quartus II ブ ロック図エディタでこのファイルを使用できます

<variation name>.html MegaCore ファンクション・レポート・ファイルで