ソフトウェア

•

デベロッパーズ

•

マニュアル

上巻:

基本アーキテクチャ

注記: 『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル』は、 次の 3 巻から構成されています。 上巻:基本アーキテクチャ (資料番号 245470J) 中巻:命令セット・リファレンス (資料番号 245471J) 下巻:システム・プログラミング・ガイド (資料番号 245472J) 設計する際は、これら 3 巻すべてを参照してください。2002

については、輸出または再輸出する場合、同法に基づく日本政府の輸出許可が必要です。また、米国産品である当社 製品は日本からの輸出または再輸出に際し、原則として米国政府の事前許可が必要です。 【資料内容に関する注意事項】 ・本ドキュメントの内容を予告なしに変更することがあります。 ・インテルでは、この資料に掲載された内容について、市販製品に使用した場合の保証あるいは特別な目的に合うこ との保証等は、いかなる場合についてもいたしかねます。また、このドキュメント内の誤りについても責任を負いか ねる場合があります。 ・インテルでは、インテル製品の内部回路以外の使用にて責任を負いません。また、外部回路の特許についても関知 いたしません。 ・本書の情報はインテル製品を使用できるようにする目的でのみ記載されています。 インテルは、製品について「取引条件」で提示されている場合を除き、インテル製品の販売や使用に関して、いかな る特許または著作権の侵害をも含み、あらゆる責任を負わないものとします。 ・いかなる形および方法によっても、インテルの文書による許可なく、この資料の一部またはすべてを複写すること は禁じられています。 インテル、Intel ロゴ、Intel386、Intel486、Celeron、MMX、Pentium、NetBurst、Xeonは、アメリカ合衆国およびその他の国における Intel Corporationまたはその子会社の商標、登録商標です。 © 1997-2003 Intel Corporation ※一般にブランド名または商品名は、各社の商標または登録商標です。

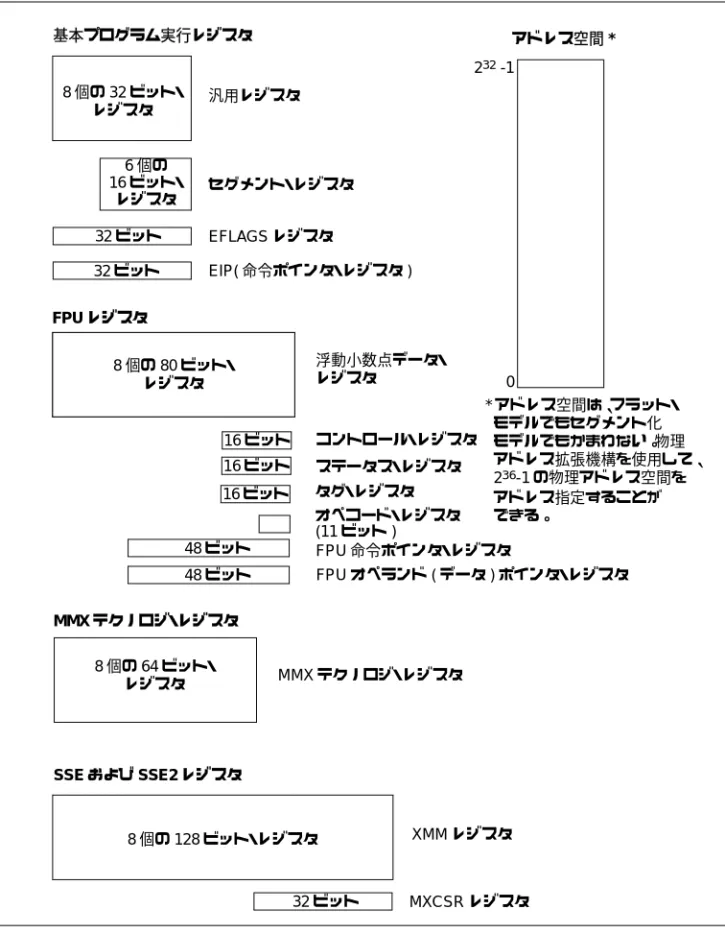

第 1章 本書について 1.1. 本書の対象となるIA-32プロセッサ . . . 1-1 1.2. 『IA-32インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・ マニュアル、上巻:基本アーキテクチャ』の概要 . . . 1-1 1.3. 『IA-32インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・ マニュアル、中巻:命令セット・リファレンス・マニュアル』の概要 . . . 1-3 1.4. 『IA-32インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・ マニュアル、下巻:システム・プログラミング・ガイド』の 概要 . . . 1-4 1.5. 表記法 . . . 1-6 1.5.1. ビット・オーダとバイト・オーダ . . . 1-6 1.5.2. 予約ビットとソフトウェア互換性 . . . 1-6 1.5.3. 命令オペランド . . . 1-7 1.5.4. 16進数と2進数 . . . 1-7 1.5.5. セグメント化アドレス指定 . . . 1-8 1.5.6. 例外 . . . 1-8 1.6. 参考文献 . . . 1-8 1.7. 参考URL . . . 1-9 第 2章 IA-32インテル®アーキテクチャの概説 2.1. IA-32アーキテクチャの変遷 . . . 2-1 2.2. インテル® Pentium® 4プロセッサ . . . 2-5 2.2.1. ストリーミングSIMD拡張命令2 (SSE2)テクノロジ . . . 2-5 2.3. Mooreの法則とIA-32プロセッサの各世代 . . . 2-7 2.4. P6ファミリ・マイクロアーキテクチャ . . . 2-8 2.5. インテル® NetBurst™マイクロアーキテクチャ . . . 2-10 2.5.1. フロント・エンド・パイプライン . . . 2-12 2.5.2. アウト・オブ・オーダー・コア . . . 2-13 2.5.3. リタイヤ . . . 2-13 第 3章 IA-32基本実行環境 3.1. 動作モード . . . 3-1 3.2. 基本実行環境の概要 . . . 3-2 3.3. メモリの構成 . . . 3-4 3.3.1. 動作モード対メモリ・モデル . . . 3-6 3.3.2. 32ビットと16ビットのアドレス・サイズとオペランド・サイズ . . . 3-7 3.3.3. 拡張された物理アドレス指定 . . . 3-7 3.4. 基本プログラム実行レジスタ . . . 3-8 3.4.1. 汎用レジスタ . . . 3-9 3.4.2. セグメント・レジスタ . . . 3-10 3.4.3. EFLAGSレジスタ . . . 3-12 3.4.3.1. ステータス・フラグ . . . 3-13 3.4.3.2. DFフラグ . . . 3-14 3.4.4. システム・フラグとIOPLフィールド . . . 3-14 3.5. 命令ポインタ . . . 3-15 3.6. オペランド・サイズ属性とアドレス・サイズ属性 . . . 3-16

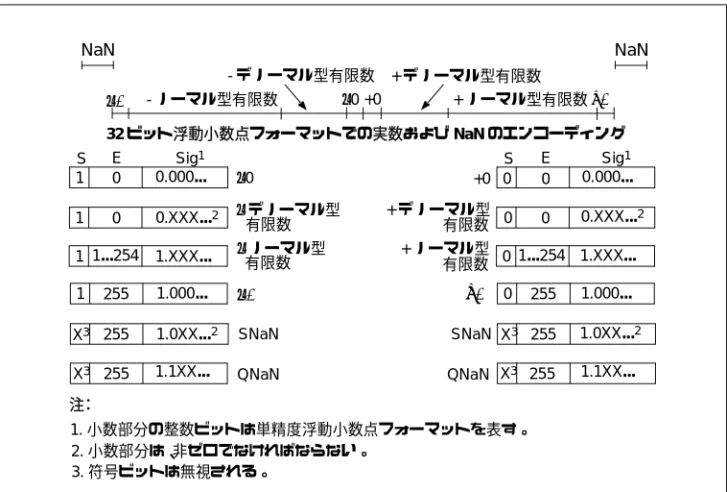

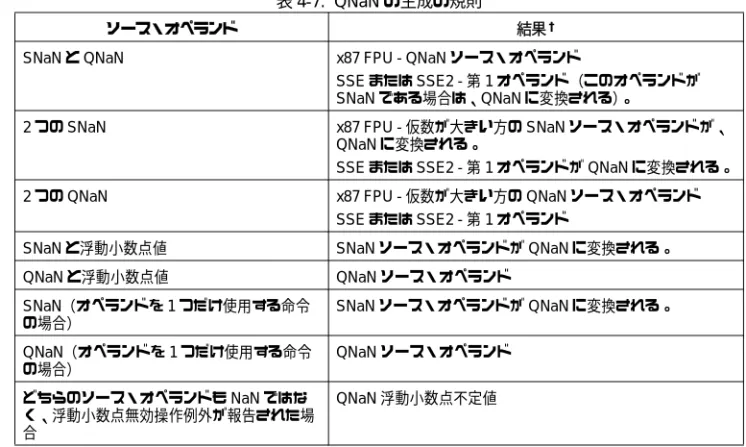

3.7. オペランドのアドレス指定 . . . 3-17 3.7.1. 即値オペランド . . . 3-17 3.7.2. レジスタ・オペランド . . . 3-17 3.7.3. メモリ・オペランド . . . 3-18 3.7.3.1. セグメント・セレクタの指定 . . . 3-18 3.7.3.2. オフセットの指定 . . . 3-19 3.7.3.3. アセンブラとコンパイラのアドレス指定モード . . . 3-21 3.7.4. I/Oポートのアドレス指定 . . . 3-21 第 4章 データ型 4.1. 基本データ型 . . . 4-1 4.1.1. ワード、ダブルワード、クワッドワード、ダブル・クワッドワードの アライメント . . . 4-2 4.2. 数値のデータ型 . . . 4-3 4.2.1. 整数 . . . 4-4 4.2.1.1. 符号なし整数 . . . 4-4 4.2.1.2. 符号付き整数 . . . 4-4 4.2.2. 浮動小数点データ型 . . . 4-5 4.3. ポインタ・データ型 . . . 4-7 4.4. ビット・フィールド・データ型 . . . 4-7 4.5. ストリング・データ型 . . . 4-8 4.6. パックドSIMDデータ型 . . . 4-8 4.6.1. 64ビット・パックドSIMDデータ型 . . . 4-8 4.6.2. 128ビット・パックドSIMDデータ型 . . . 4-9 4.7. BCDおよびパックドBCD整数 . . . 4-10 4.8. 実数フォーマットと浮動小数点フォーマット . . . 4-12 4.8.1. 実数体系 . . . 4-12 4.8.2. 浮動小数点フォーマット . . . 4-12 4.8.2.1. ノーマル型数 . . . 4-14 4.8.2.2. バイアス付き指数 . . . 4-14 4.8.3. 実数および非数のエンコーディング . . . 4-14 4.8.3.1. 符号付きゼロ . . . 4-15 4.8.3.2. ノーマル型有限数とデノーマル型有限数 . . . 4-16 4.8.3.3. 符号付き無限大 . . . 4-17 4.8.3.4. NaN (Not a Number) . . . 4-17 4.8.3.5. SNaNとQNaNの操作 . . . 4-17 4.8.3.6. アプリケーションでのSNANとQNANの使用 . . . 4-18 4.8.3.7. QNAN浮動小数点不定数 . . . 4-19 4.8.4. 丸め . . . 4-19 4.8.4.1. 丸め制御(RC)フィールド . . . 4-21 4.8.4.2. SSEおよびSSE2変換命令による切り捨て . . . 4-21 4.9. 浮動小数点例外の概要 . . . 4-21 4.9.1. 浮動小数点例外条件 . . . 4-23 4.9.1.1. 無効操作例外(#I) . . . 4-23 4.9.1.2. デノーマル・オペランド例外(#D) . . . 4-23 4.9.1.3. ゼロ除算例外(#Z) . . . 4-24 4.9.1.4. 数値オーバーフロー例外(#O) . . . 4-24 4.9.1.5. 数値アンダーフロー例外(#U) . . . 4-25 4.9.1.6. 不正確結果(精度)例外 (#P) . . . 4-26 4.9.2. 浮動小数点例外の優先順位 . . . 4-27 4.9.3. 浮動小数点例外ハンドラの一般的な動作 . . . 4-27

第 5章 命令セットの要約 5.1. 汎用命令 . . . 5-2 5.1.1. データ転送命令 . . . 5-2 5.1.2. 2進算術命令 . . . 5-3 5.1.3. 10進算術命令 . . . 5-4 5.1.4. 論理命令 . . . 5-4 5.1.5. シフト命令とローテート命令 . . . 5-4 5.1.6. ビット命令とバイト命令 . . . 5-5 5.1.7. 制御転送命令 . . . 5-6 5.1.8. ストリング命令 . . . 5-7 5.1.9. フラグ制御命令 . . . 5-8 5.1.10. セグメント・レジスタ命令 . . . 5-8 5.1.11. その他の命令 . . . 5-9 5.2. x87 FPU命令 . . . 5-9 5.2.1. データ転送命令 . . . 5-9 5.2.2. 基本算術命令 . . . 5-10 5.2.3. 比較命令 . . . 5-11 5.2.4. 超越関数命令 . . . 5-11 5.2.5. 定数ロード命令 . . . 5-12 5.2.6. x87 FPU制御命令 . . . 5-12 5.3. x87 FPUおよびSIMDステートの管理 . . . 5-13 5.4. SIMD命令 . . . 5-13 5.5. MMX®命令 . . . 5-15 5.5.1. データ転送命令 . . . 5-15 5.5.2. 変換命令 . . . 5-16 5.5.3. パックド算術命令 . . . 5-16 5.5.4. 比較命令 . . . 5-17 5.5.5. 論理演算命令 . . . 5-17 5.5.6. シフト命令とローテート命令 . . . 5-17 5.5.7. ステート管理 . . . 5-18 5.6. SSE . . . 5-18 5.6.1. SSE SIMD単精度浮動小数点命令 . . . 5-18 5.6.1.1. SSEデータ転送命令 . . . 5-18 5.6.1.2. SSEパックド算術命令 . . . 5-19 5.6.1.3. SSE比較命令 . . . 5-20 5.6.1.4. SSE論理演算命令 . . . 5-20 5.6.1.5. SSEシャッフル命令とアンパック命令 . . . 5-20 5.6.1.6. SSE変換命令 . . . 5-21 5.6.2. MXCSRステート管理命令 . . . 5-21 5.6.3. SSE 64ビットSIMD整数命令 . . . 5-21 5.6.4. SSEキャッシュ制御命令、プリフェッチ命令、および命令順序付け命令 . . . 5-22 5.7. SSE2 . . . 5-22 5.7.1. SSE2パックドおよびスカラ倍精度浮動小数点命令 . . . 5-23 5.7.1.1. SSE2データ転送命令 . . . 5-23 5.7.1.2. SSE2パックド算術命令 . . . 5-23 5.7.1.3. SSE2論理演算命令 . . . 5-24 5.7.1.4. SSE2比較命令 . . . 5-24 5.7.1.5. SSE2シャッフル命令とアンパック命令 . . . 5-25 5.7.1.6. SSE2変換命令 . . . 5-25 5.7.2. SSE2パックド単精度浮動小数点命令 . . . 5-26 5.7.3. SSE2 128ビットSIMD整数命令 . . . 5-26

5.7.4. SSE2キャッシュ制御命令と命令順序付け命令 . . . 5-27 5.8. システム命令 . . . 5-27 第 6章 プロシージャ・コール、割り込み、例外 6.1. プロシージャ・コールのタイプ . . . 6-1 6.2. スタック . . . 6-1 6.2.1. スタックのセットアップ . . . 6-2 6.2.2. スタックのアライメント . . . 6-3 6.2.3. スタック・アクセスにおけるアドレス・サイズ属性 . . . 6-3 6.2.4. プロシージャのリンクに関する情報 . . . 6-4 6.2.4.1. スタック・フレーム・ベース・ポインタ . . . 6-4 6.2.4.2. リターン命令ポインタ . . . 6-4 6.3. CALLとRETによるプロシージャのコール . . . 6-4 6.3.1. nearコール操作とnearリターン操作 . . . 6-5 6.3.2. farコール操作とfarリターン操作 . . . 6-5 6.3.3. パラメータの受け渡し . . . 6-6 6.3.3.1. 汎用レジスタによるパラメータの受け渡し . . . 6-6 6.3.3.2. スタックによるパラメータの受け渡し . . . 6-7 6.3.3.3. 引き数リストによるパラメータの受け渡し . . . 6-7 6.3.4. プロシージャのステート情報のセーブ . . . 6-7 6.3.5. 他の特権レベルに対するコール . . . 6-7 6.3.6. 特権レベル間のコール操作とリターン操作 . . . 6-9 6.4. 割り込みと例外 . . . 6-10 6.4.1. 割り込み/例外処理プロシージャのコール操作とリターン操作 . . . 6-11 6.4.2. 割り込み/例外ハンドラ・タスクのコール . . . 6-14 6.4.3. 実アドレス・モードでの割り込みと例外の処理 . . . 6-15 6.4.4. INT n、INTO、INT 3、およびBOUND命令 . . . 6-15 6.4.5. 浮動小数点例外の処理 . . . 6-16 6.5. ブロック構造言語でのプロシージャ・コール . . . 6-16 6.5.1. ENTER 命令 . . . 6-16 6.5.2. LEAVE命令 . . . 6-22 第 7章 汎用命令によるプログラミング 7.1. 汎用命令のプログラミング環境 . . . 7-1 7.2. 汎用命令の概要 . . . 7-2 7.2.1. データ転送命令 . . . 7-3 7.2.1.1. 汎用データ転送命令 . . . 7-3 7.2.1.2. 交換命令 . . . 7-4 7.2.1.3. スタック操作命令 . . . 7-6 7.2.1.4. 型変換命令 . . . 7-8 7.2.2. 2進算術命令 . . . 7-9 7.2.2.1. 加算命令と減算命令 . . . 7-9 7.2.2.2. インクリメント命令とデクリメント命令 . . . 7-9 7.2.2.3. 比較命令と符号変更命令 . . . 7-10 7.2.2.4. 乗算命令と除算命令 . . . 7-10 7.2.3. 10進算術命令 . . . 7-10 7.2.3.1. パックドBCD調整命令 . . . 7-11 7.2.3.2. アンパックBCD調整命令 . . . 7-11 7.2.4. 論理演算命令 . . . 7-12 7.2.5. シフト命令とローテート命令 . . . 7-12

7.2.5.1. シフト命令 . . . 7-12 7.2.5.2. ダブル・シフト命令 . . . 7-14 7.2.5.3. ローテート命令 . . . 7-14 7.2.6. ビット命令とバイト命令 . . . 7-15 7.2.6.1. ビット・テストおよび変更命令 . . . 7-16 7.2.6.2. ビット・スキャン命令 . . . 7-16 7.2.6.3. 条件付きバイト・セット命令 . . . 7-16 7.2.6.4. テスト命令 . . . 7-17 7.2.7. 制御転送命令 . . . 7-17 7.2.7.1. 無条件転送命令 . . . 7-17 7.2.7.2. 条件付き転送命令 . . . 7-18 7.2.7.3. ソフトウェア割り込み . . . 7-21 7.2.8. ストリングの操作 . . . 7-22 7.2.8.1. ストリング操作の反復 . . . 7-23 7.2.9. I/O命令 . . . 7-23 7.2.10. ENTER命令とLEAVE命令 . . . 7-24 7.2.11. EFLAGS命令 . . . 7-24 7.2.11.1. キャリー・フラグおよび方向フラグ命令 . . . 7-24 7.2.11.2. 割り込みフラグ命令 . . . 7-24 7.2.11.3. EFLAGS転送命令 . . . 7-24 7.2.11.4. 割り込みフラグ命令 . . . 7-25 7.2.12. セグメント・レジスタ命令 . . . 7-26 7.2.12.1. セグメント・レジスタ・ロードおよびストア命令 . . . 7-26 7.2.12.2. far制御転送命令 . . . 7-26 7.2.12.3. ソフトウェア割り込み命令 . . . 7-26 7.2.12.4. farポインタ・ロード命令 . . . 7-26 7.2.13. その他の命令 . . . 7-27 7.2.13.1. アドレス計算命令 . . . 7-27 7.2.13.2. テーブル・ルックアップ命令 . . . 7-27 7.2.13.3. プロセッサ識別命令 . . . 7-27 7.2.13.4. ノー・オペレーション命令と未定義命令 . . . 7-27 第 8章 x87 FPUによるプログラミング 8.1. x87 FPUの実行環境 . . . 8-1 8.1.1. x87 FPUデータ・レジスタ . . . 8-2 8.1.1.1. x87 FPUレジスタ・スタックとのパラメータの受け渡し . . . 8-4 8.1.2. x87 FPUステータス・レジスタ . . . 8-5 8.1.2.1. スタック・トップ(TOP)ポインタ . . . 8-5 8.1.2.2. 条件コード・フラグ . . . 8-5 8.1.2.3. x87 FPU浮動小数点例外フラグ . . . 8-6 8.1.2.4. スタック・フォルト・フラグ . . . 8-7 8.1.3. 条件コードに基づく分岐と条件付き移動 . . . 8-8 8.1.4. x87 FPU制御ワード . . . 8-9 8.1.4.1. x87 FPU浮動小数点例外フラグ・マスク . . . 8-10 8.1.4.2. 精度制御フィールド . . . 8-10 8.1.4.3. 丸め制御フィールド . . . 8-10 8.1.5. 無限大制御フラグ . . . 8-11 8.1.6. x87 FPUタグ・ワード . . . 8-11 8.1.7. x87 FPU命令とデータ(オペランド)ポインタ . . . 8-12 8.1.8. 最後の命令オペコード . . . 8-12 8.1.8.1. fopcode互換モード . . . 8-12

8.1.9. FSTENV/FNSTENV命令およびFSAVE/FNSAVE命令によるx87 FPUの ステートのセーブ . . . 8-13 8.1.10. FXSAVE命令によるx87 FPUステートの保存 . . . 8-15 8.2. x87 FPUデータ型 . . . 8-15 8.2.1. 不定値 . . . 8-16 8.2.2. サポートされない拡張倍精度浮動小数点のエンコーディング . . . 8-17 8.3. x87 FPU命令セット . . . 8-18 8.3.1. エスケープ(ESC)命令 . . . 8-19 8.3.2. x87 FPU命令のオペランド . . . 8-19 8.3.3. データ転送命令 . . . 8-19 8.3.4. 定数ロード命令 . . . 8-21 8.3.5. 基本算術命令 . . . 8-21 8.3.6. 比較命令と分類命令 . . . 8-23 8.3.6.1. x87 FPU条件コードに基づく分岐 . . . 8-24 8.3.7. 三角関数命令 . . . 8-25 8.3.8. π . . . 8-26 8.3.9. 対数、指数、およびスケーリング関数 . . . 8-27 8.3.10. 超越関数命令の精度 . . . 8-27 8.3.11. x87 FPU制御命令 . . . 8-28 8.3.12. 同期型命令と非同期型命令 . . . 8-29 8.3.13. サポートされていないx87 FPU命令 . . . 8-29 8.4. x87 FPU浮動小数点例外処理 . . . 8-29 8.4.1. 算術命令と非算術命令 . . . 8-30 8.5. x87 FPU浮動小数点例外条件 . . . 8-32 8.5.1. 無効操作例外 . . . 8-32 8.5.1.1. スタック・オーバーフロー例外またはスタック・アンダーフロー 例外 (#IS) . . . 8-32 8.5.1.2. 無効算術オペランド例外 (#IA) . . . 8-33 8.5.2. デノーマル・オペランド例外(#D) . . . 8-33 8.5.3. ゼロ除算例外 (#Z) . . . 8-35 8.5.4. 数値オーバーフロー例外 (#O) . . . 8-35 8.5.5. 数値アンダーフロー例外 (#U) . . . 8-36 8.5.6. 不正確結果(精度)例外 (#P) . . . 8-37 8.6. x87 FPU例外の同期 . . . 8-38 8.7. ソフトウェア内でのx87 FPU例外の処理 . . . 8-39 8.7.1. ネイティブ・モード . . . 8-40 8.7.2. MS-DOS*互換モード . . . 8-40 8.7.3. ソフトウェア内でのx87 FPU例外の処理 . . . 8-41 第 9章 インテル® MMX®テクノロジによるプログラミング 9.1. MMX®テクノロジのプログラミング環境の概要 . . . 9-1 9.2. MMX®テクノロジのプログラミング環境 . . . 9-2 9.2.1. MMX®テクノロジ・レジスタ . . . 9-2 9.2.2. MMX®テクノロジ・データ型 . . . 9-3 9.2.3. メモリ内のデータ・フォーマット . . . 9-4 9.2.4. SIMD (single-instruction, multiple-data) 実行モデル . . . 9-4 9.3. 飽和算術とラップアラウンド・モード . . . 9-5 9.4. MMX®命令 . . . 9-6 9.4.1. データ転送命令 . . . 9-7 9.4.2. 算術命令 . . . 9-8 9.4.3. 比較命令 . . . 9-8

9.4.4. 変換命令 . . . 9-9 9.4.5. アンパック命令 . . . 9-9 9.4.6. 論理命令 . . . 9-9 9.4.7. シフト命令 . . . 9-9 9.4.8. EMMS命令 . . . 9-9 9.5. x87 FPUアーキテクチャとの互換性 . . . 9-10 9.5.1. MMX®命令とx87 FPUタグ・ワードの関係 . . . 9-10 9.6. MMX®テクノロジ・コードによるアプリケーションの作成 . . . 9-10 9.6.1. MMX®テクノロジのサポートのチェック . . . 9-10 9.6.2. x87 FPUコードとMMX®テクノロジ・コードの間の移行 . . . 9-11 9.6.3. EMMS命令の使用法 . . . 9-12 9.6.4. MMX®命令とx87 FPU命令の混在 . . . 9-12 9.6.5. MMX®テクノロジ・コードのインターフェイス . . . 9-13 9.6.6. マルチタスク・オペレーティング・システム環境でのMMX®テクノロジ・ コードの使用 . . . 9-13 9.6.7. MMX®テクノロジ・コードでの例外処理 . . . 9-14 9.6.8. レジスタのマッピング . . . 9-14 9.6.9. MMX®命令に対する命令プリフィックスの影響 . . . 9-14 第 10章 ストリーミングSIMD拡張命令(SSE)によるプログラミング 10.1. SSEの概要 . . . 10-1 10.2. SSEのプログラミング環境 . . . 10-2 10.2.1. XMMレジスタ . . . 10-4 10.2.2. MXCSR制御およびステータス・レジスタ . . . 10-4 10.2.2.1. SIMD浮動小数点マスク・ビットおよびフラグ・ビット . . . 10-5 10.2.2.2. SIMD浮動小数点丸め制御フィールド . . . 10-6 10.2.2.3. ゼロ・フラッシュ . . . 10-6 10.2.2.4. デノーマル・ゼロ . . . 10-6 10.2.3. SSEとSSE2、MMX®テクノロジ、およびx87 FPUのプログラミング

環境の互換性 . . . 10-7 10.3. SSEのデータ型 . . . 10-7 10.4. SSEセット . . . 10-8 10.4.1. SSEパックドおよびスカラ浮動小数点命令 . . . 10-8 10.4.1.1. SSEデータ転送命令 . . . 10-10 10.4.1.2. SSE算術演算命令 . . . 10-10 10.4.2. SSE論理演算命令 . . . 10-12 10.4.2.1. SSE比較命令 . . . 10-12 10.4.2.2. SSEシャッフル命令とアンパック命令 . . . 10-13 10.4.3. SSE変換命令 . . . 10-14 10.4.4. SSE 64ビットSIMD整数命令 . . . 10-15 10.4.5. MXCSR ステート管理命令 . . . 10-16 10.4.6. キャッシュ制御命令、プリフェッチ命令、およびメモリ・アクセス 順序命令 . . . 10-16 10.4.6.1. キャッシュ制御命令 . . . 10-17 10.4.6.2. テンポラルなデータと非テンポラルなデータのキャッシュ処理 . . . 10-17 10.4.6.3. PREFETCHh命令 . . . 10-18 10.4.6.4. SFENCE命令 . . . 10-19 10.5. FXSAVE命令とFXRSTOR命令 . . . 10-19 10.6. SSEの例外の処理 . . . 10-20 10.7. SSEによるアプリケーションの作成 . . . 10-20

第 11章

ストリーミングSIMD拡張命令2 (SSE2)によるプログラミング

11.1. SSE2の概要 . . . 11-1 11.2. SSE2のプログラミング環境 . . . 11-3 11.2.1. SSE2とSSE、MMX®テクノロジ、およびx87 FPUのプログラミング

環境の互換性 . . . 11-4 11.2.2. デノーマル・ゼロ・フラグ . . . 11-4 11.3. SSE2のデータ型 . . . 11-4 11.4. SSE2命令 . . . 11-5 11.4.1. パックドおよびスカラ倍精度浮動小数点命令 . . . 11-6 11.4.1.1. データ転送命令 . . . 11-7 11.4.1.2. SSE2算術演算命令 . . . 11-8 11.4.1.3. SSE2論理演算命令 . . . 11-9 11.4.1.4. SSE2 比較命令 . . . 11-9 11.4.1.5. SSE2シャッフル命令とアンパック命令 . . . 11-10 11.4.1.6. SSE2変換命令 . . . 11-11 11.4.2. SSE2 64ビットおよび128ビットSIMD整数命令 . . . 11-14 11.4.3. 128ビットSIMD整数拡張命令 . . . 11-15 11.4.4. キャッシュ制御命令およびメモリ・アクセス順序命令 . . . 11-16 11.4.4.1. フラッシュのキャッシュ・ライン . . . 11-16 11.4.4.2. キャッシュ制御命令 . . . 11-16 11.4.4.3. メモリ・アクセス順序命令 . . . 11-16 11.4.4.4. PAUSE . . . 11-17 11.4.5. 分岐ヒント . . . 11-17 11.5. SSEとSSE2の例外 . . . 11-17 11.5.1. SIMD浮動小数点例外 . . . 11-18 11.5.2. SIMD浮動小数点例外条件 . . . 11-18 11.5.2.1. 無効操作例外(#I) . . . 11-19 11.5.2.2. デノーマル・オペランド例外(#D) . . . 11-20 11.5.2.3. ゼロ除算例外(#Z) . . . 11-20 11.5.2.4. 数値オーバーフロー例外(#O) . . . 11-20 11.5.2.5. 数値アンダーフロー例外(#U) . . . 11-21 11.5.2.6. 不正確結果(精度)例外(#P) . . . 11-21 11.5.3. SIMD浮動小数点例外の生成 . . . 11-22 11.5.3.1. マスクされている例外の処理 . . . 11-22 11.5.3.2. マスクされていない例外の処理 . . . 11-23 11.5.3.3. マスクされている例外とマスクされていない例外の組み合わせの処理 . . 11-24 11.5.4. ソフトウェアによるSIMD浮動小数点例外の処理 . . . 11-24 11.5.5. SIMD浮動小数点例外とx87 FPU浮動小数点例外の相互作用 . . . 11-24 11.6. SSEおよびSSE2によるアプリケーションの作成 . . . 11-25 11.6.1. SSEとSSE2の使用時の一般的なガイドライン . . . 11-26 11.6.2. SSEとSSE2のサポートのチェック . . . 11-26 11.6.3. MXCSRレジスタのDAZフラグのチェック . . . 11-27 11.6.4. SSEおよびSSE2の初期化 . . . 11-27 11.6.5. SSEとSSE2のステートのセーブとリストア . . . 11-28 11.6.6. MXCSRレジスタへの書き込みのガイドライン . . . 11-28 11.6.7. SSEおよびSSE2とx87 FPU命令およびMMX命令の相互作用 . . . 11-29 11.6.8. SIMD浮動小数点データ型とx87 FPU浮動小数点データ型の互換性 . . . 11-30 11.6.9. パックドおよびスカラ浮動小数点命令/データと128ビットSIMD

整数命令/データの組み合わせ . . . 11-30 11.6.10. SSEとSSE2のプロシージャと関数に対するインターフェイス . . . 11-32 11.6.10.1. XMMレジスタ内でのパラメータの受け渡し . . . 11-32

11.6.10.2. プロシージャ・コールまたは関数呼び出し時のXMMレジスタ・ ステートのセーブ . . . 11-32 11.6.10.3. プロシージャ・コールと関数呼び出しでの呼び出し元セーブの 必要条件 . . . 11-33 11.6.11. 128ビットSIMD整数命令の使用時の既存のMMX®テクノロジ・ ルーチンのアップデート . . . 11-33 11.6.12. 算術演算での分岐 . . . 11-34 11.6.13. キャッシュ・ヒント命令 . . . 11-34 11.6.14. SSEとSSE2に対する命令プリフィックスの影響 . . . 11-35 第 12章 入出力 12.1. I/O ポートのアドレス指定 . . . 12-1 12.2. ハードウェアからみたI/Oポート . . . 12-1 12.3. I/Oアドレス空間 . . . 12-2 12.3.1. メモリ・マップドI/O . . . 12-2 12.4. I/O命令 . . . 12-3 12.5. 保護モードI/O . . . 12-4 12.5.1. I/O特権レベル . . . 12-4 12.5.2. I/O許可ビット・マップ . . . 12-5 12.6. I/Oの順序 . . . 12-6 第 13章 プロセッサの識別と機能の判定 13.1. プロセッサの識別 . . . 13-1 13.2. 従来のインテル®アーキテクチャ・プロセッサの識別 . . . 13-6 付録A EFLAGSクロス・リファレンス 付録B EFLAGS条件コード 付録C 浮動小数点例外の要約 C.1. x87 FPU命令 . . . C-2 C.2. SSE . . . C-4 C.3. SSE2 . . . . C-6 付録D x87 FPU例外ハンドラを作成する際のガイドライン D.1. MS-DOS*互換モードのx87 FPU例外処理メカニズムの由来 . . . D-2 D.2. Intel486™プロセッサ、Pentium®プロセッサ、P6ファミリおよび Pentium® 4プロセッサにおけるMS-DOS互換モード . . . D-3 D.2.1. Intel486™プロセッサとPentium®プロセッサにおけるMS-DOS互換モード . D-3

D.2.1.1. FERR#信号発生時の基本規則 . . . D-4 D.2.1.2. MS-DOS互換モードをサポートするための推奨外部ハードウェア . . . D-5 D.2.1.3. 非同期型命令のウインドウ内のx87 FPU割り込み . . . D-7 D.2.2. P6ファミリおよびPentium® 4プロセッサにおけるMS-DOS互換モード . . . . D-9 D.3. MS-DOS互換モードのハンドラに対する推奨規則 . . . D-10 D.3.1. 浮動小数点例外とそのデフォルト動作 . . . D-10

D.3.2. 数値例外処理の2つのオプション . . . D-11 D.3.2.1. マスクによる自動例外処理 . . . D-11 D.3.2.2. ソフトウェアによる例外処理 . . . D-12 D.3.3. x87 FPU例外ハンドラの使用時に必要な同期 . . . D-14 D.3.3.1. 例外処理で同期の必要な対象、理由、タイミング . . . D-14 D.3.3.2. 例外処理の同期の例 . . . D-15 D.3.3.3. 例外処理の一般的な同期方法 . . . D-16 D.3.4. x87 FPU例外ハンドラの例 . . . D-16 D.3.5. x87 FPUとSMMを使用する場合のIGNNE#回路ステートのセーブ . . . D-20 D.3.6. タスク間でx87 FPUを共有する場合の注意事項 . . . D-21 D.3.6.1. x87 FPUステート保存の見込みによる据え置きの概要 . . . D-21 D.3.6.2. x87 FPU所有者の追跡 . . . D-22 D.3.6.3. x87 FPUステートのセーブと浮動小数点例外の関係 . . . D-23 D.3.6.4. カーネルからの割り込みルーチン . . . D-25 D.3.6.5. オペレーティング・システムがストリーミングSIMD拡張命令を サポートしている場合の考慮事項 . . . D-25 D.4. ネイティブ・モードのハンドラとの相違点 . . . D-26 D.4.1. Intel® 286プロセッサとIntel® 287プロセッサ、Intel386™プロセッサと

Intel® 387プロセッサの場合 . . . D-26

D.4.2. CR0.NE=1のIntel486™プロセッサ、Pentium®プロセッサ、

Pentium® Proプロセッサの場合 . . . D-27 D.4.3. ネイティブ・モードでタスク間でx87 FPUを共有する場合の注意事項 . . . . D-27 付録E SIMD浮動小数点例外ハンドラを作成する際のガイドライン E.1. 浮動小数点例外処理の2つのオプション . . . E-1 E.2. ソフトウェアによる例外処理 . . . E-1 E.3. 例外の同期 . . . E-3 E.4. 2進浮動小数点計算に関するIEEE-754規格とSIMD浮動小数点例外 . . . E-4 E.4.1. 浮動小数点エミュレーション . . . E-4 E.4.2. 浮動小数点例外に対するSSEおよびSSE2の応答 . . . E-6 E.4.2.1. 数値例外 . . . E-7 E.4.2.2. SSEおよびSSE2数値命令でNaNオペランドまたはNaN結果を含む

演算の結果 . . . E-7

E.4.2.3. マスクされた数値例外とマスクされていない数値例外に対する

条件コード、例外フラグ、および応答 . . . E-10 E.4.3. SIMD浮動小数点エミュレーションのコード例 . . . E-13

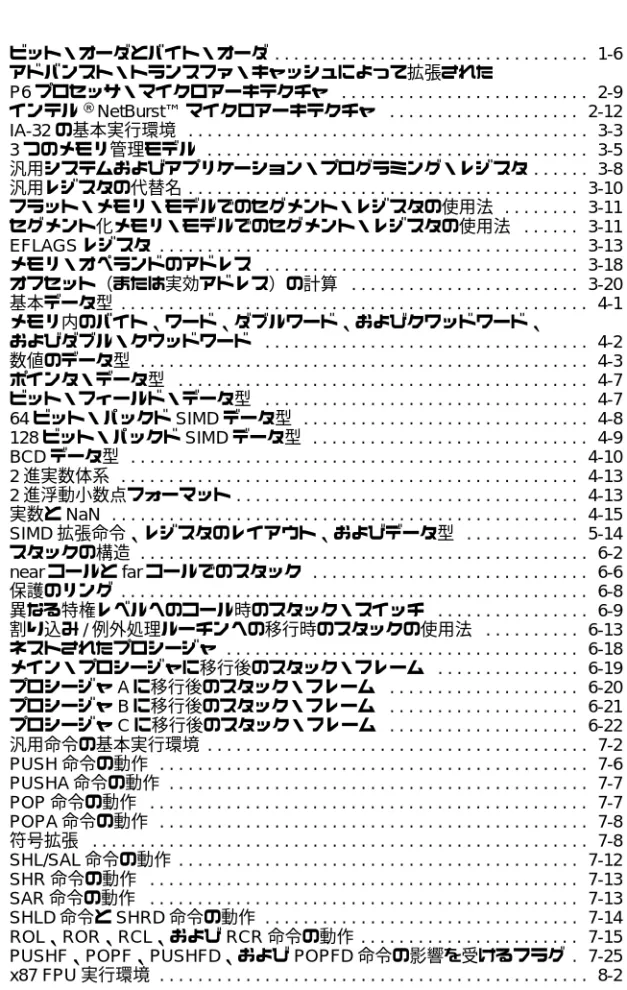

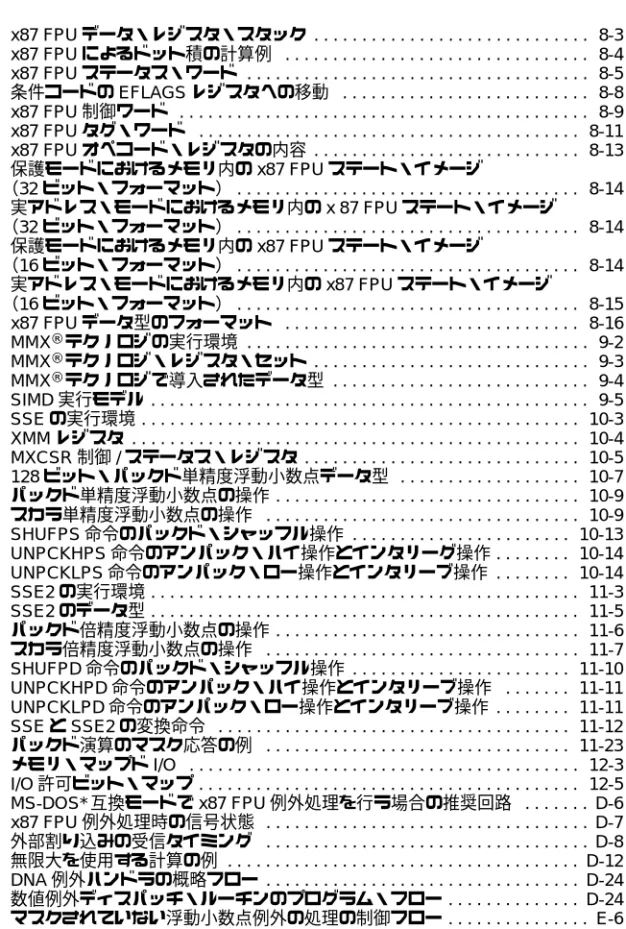

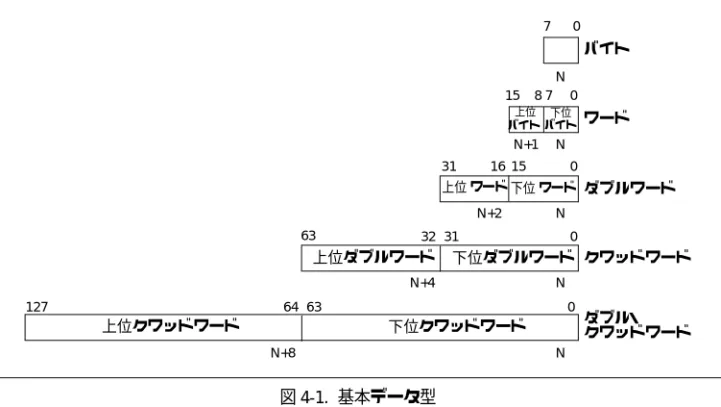

図1-1. ビット・オーダとバイト・オーダ . . . 1-6 図2-1. アドバンスト・トランスファ・キャッシュによって拡張された P6プロセッサ・マイクロアーキテクチャ . . . 2-9 図2-2. インテル® NetBurst™マイクロアーキテクチャ . . . 2-12 図3-1. IA-32の基本実行環境 . . . 3-3 図3-2. 3つのメモリ管理モデル . . . 3-5 図3-3. 汎用システムおよびアプリケーション・プログラミング・レジスタ . . . 3-8 図3-4. 汎用レジスタの代替名 . . . 3-10 図3-5. フラット・メモリ・モデルでのセグメント・レジスタの使用法 . . . 3-11 図3-6. セグメント化メモリ・モデルでのセグメント・レジスタの使用法 . . . 3-11 図3-7. EFLAGSレジスタ . . . 3-13 図3-8. メモリ・オペランドのアドレス . . . 3-18 図3-9. オフセット(または実効アドレス)の計算 . . . 3-20 図4-1. 基本データ型 . . . 4-1 図4-2. メモリ内のバイト、ワード、ダブルワード、およびクワッドワード、 およびダブル・クワッドワード . . . 4-2 図4-3. 数値のデータ型 . . . 4-3 図4-4. ポインタ・データ型 . . . 4-7 図4-5. ビット・フィールド・データ型 . . . 4-7 図4-6. 64ビット・パックドSIMDデータ型 . . . 4-8 図4-7. 128ビット・パックドSIMDデータ型 . . . 4-9 図4-8. BCDデータ型 . . . 4-10 図4-9. 2進実数体系 . . . 4-13 図4-10. 2進浮動小数点フォーマット . . . 4-13 図4-11. 実数とNaN . . . 4-15 図5-1. SIMD拡張命令、レジスタのレイアウト、およびデータ型 . . . 5-14 図6-1. スタックの構造 . . . 6-2 図6-2. nearコールとfarコールでのスタック . . . 6-6 図6-3. 保護のリング . . . 6-8 図6-4. 異なる特権レベルへのコール時のスタック・スイッチ . . . 6-9 図6-5. 割り込み/例外処理ルーチンへの移行時のスタックの使用法 . . . 6-13 図6-6. ネストされたプロシージャ . . . 6-18 図6-7. メイン・プロシージャに移行後のスタック・フレーム . . . 6-19 図6-8. プロシージャAに移行後のスタック・フレーム . . . 6-20 図6-9. プロシージャBに移行後のスタック・フレーム . . . 6-21 図6-10. プロシージャCに移行後のスタック・フレーム . . . 6-22 図7-1. 汎用命令の基本実行環境 . . . 7-2 図7-2. PUSH命令の動作 . . . 7-6 図7-3. PUSHA命令の動作 . . . 7-7 図7-4. POP命令の動作 . . . 7-7 図7-5. POPA命令の動作 . . . 7-8 図7-6. 符号拡張 . . . 7-8 図7-7. SHL/SAL命令の動作 . . . 7-12 図7-8. SHR命令の動作 . . . 7-13 図7-9. SAR命令の動作 . . . 7-13 図7-10. SHLD命令とSHRD命令の動作 . . . 7-14 図7-11. ROL、ROR、RCL、およびRCR命令の動作 . . . 7-15 図7-12. PUSHF、POPF、PUSHFD、およびPOPFD命令の影響を受けるフラグ . 7-25 図8-1. x87 FPU実行環境 . . . 8-2

図8-2. x87 FPUデータ・レジスタ・スタック . . . 8-3 図8-3. x87 FPUによるドット積の計算例 . . . 8-4 図8-4. x87 FPUステータス・ワード . . . 8-5 図8-5. 条件コードのEFLAGSレジスタへの移動 . . . 8-8 図8-6. x87 FPU制御ワード . . . 8-9 図8-7. x87 FPUタグ・ワード . . . 8-11 図8-8. x87 FPUオペコード・レジスタの内容 . . . 8-13 図8-9. 保護モードにおけるメモリ内のx87 FPUステート・イメージ (32ビット・フォーマット) . . . 8-14 図8-10. 実アドレス・モードにおけるメモリ内のx 87 FPUステート・イメージ (32ビット・フォーマット) . . . 8-14 図8-11. 保護モードにおけるメモリ内のx87 FPUステート・イメージ (16ビット・フォーマット) . . . 8-14 図8-12. 実アドレス・モードにおけるメモリ内のx87 FPUステート・イメージ (16ビット・フォーマット) . . . 8-15 図8-13. x87 FPUデータ型のフォーマット . . . 8-16 図9-1. MMX®テクノロジの実行環境 . . . 9-2 図9-2. MMX®テクノロジ・レジスタ・セット . . . 9-3 図9-3. MMX®テクノロジで導入されたデータ型 . . . 9-4 図9-4. SIMD実行モデル . . . 9-5 図10-1. SSEの実行環境 . . . 10-3 図10-2. XMMレジスタ . . . 10-4 図10-3. MXCSR制御/ステータス・レジスタ . . . 10-5 図10-4. 128ビット・パックド単精度浮動小数点データ型 . . . 10-7 図10-5. パックド単精度浮動小数点の操作 . . . 10-9 図10-6. スカラ単精度浮動小数点の操作 . . . 10-9 図10-7. SHUFPS命令のパックド・シャッフル操作 . . . 10-13 図10-8. UNPCKHPS命令のアンパック・ハイ操作とインタリーグ操作 . . . 10-14 図10-9. UNPCKLPS命令のアンパック・ロー操作とインタリーブ操作 . . . 10-14 図11-1. SSE2の実行環境 . . . 11-3 図11-2. SSE2のデータ型 . . . 11-5 図11-3. パックド倍精度浮動小数点の操作 . . . 11-6 図11-4. スカラ倍精度浮動小数点の操作 . . . 11-7 図11-5. SHUFPD命令のパックド・シャッフル操作 . . . 11-10 図11-6. UNPCKHPD命令のアンパック・ハイ操作とインタリーブ操作 . . . 11-11 図11-7. UNPCKLPD命令のアンパック・ロー操作とインタリーブ操作 . . . 11-11 図11-8. SSEとSSE2の変換命令 . . . 11-12 図11-9. パックド演算のマスク応答の例 . . . 11-23 図12-1. メモリ・マップドI/O . . . 12-3 図12-2. I/O許可ビット・マップ . . . 12-5 図D-1. MS-DOS*互換モードでx87 FPU例外処理を行う場合の推奨回路 . . . D-6 図D-2. x87 FPU例外処理時の信号状態 . . . D-7 図D-3. 外部割り込みの受信タイミング . . . D-8 図D-4. 無限大を使用する計算の例 . . . D-12 図D-5. DNA例外ハンドラの概略フロー . . . D-24 図D-6. 数値例外ディスパッチ・ルーチンのプログラム・フロー . . . D-24 図E-1. マスクされていない浮動小数点例外の処理の制御フロー . . . E-6

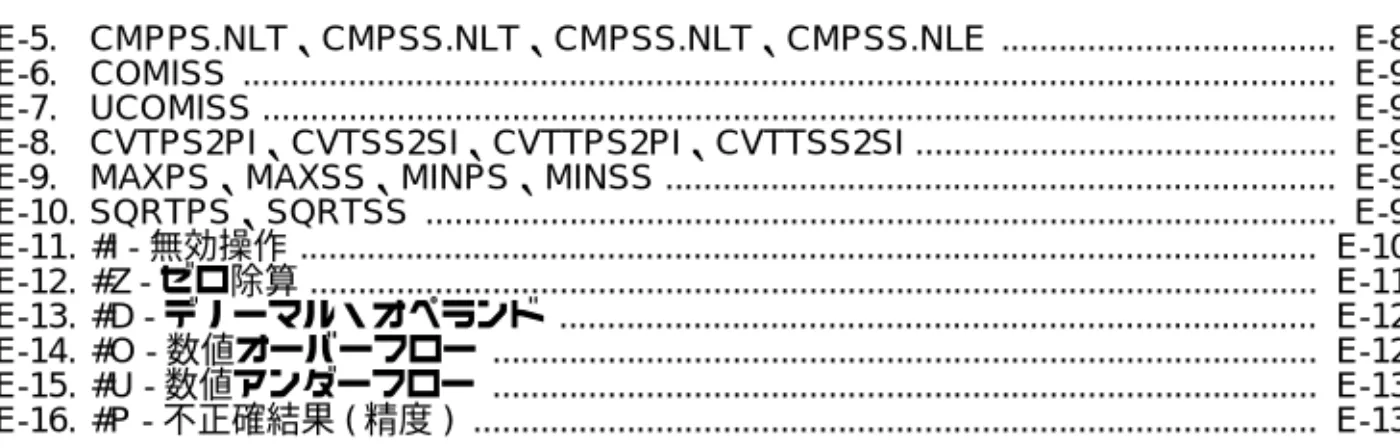

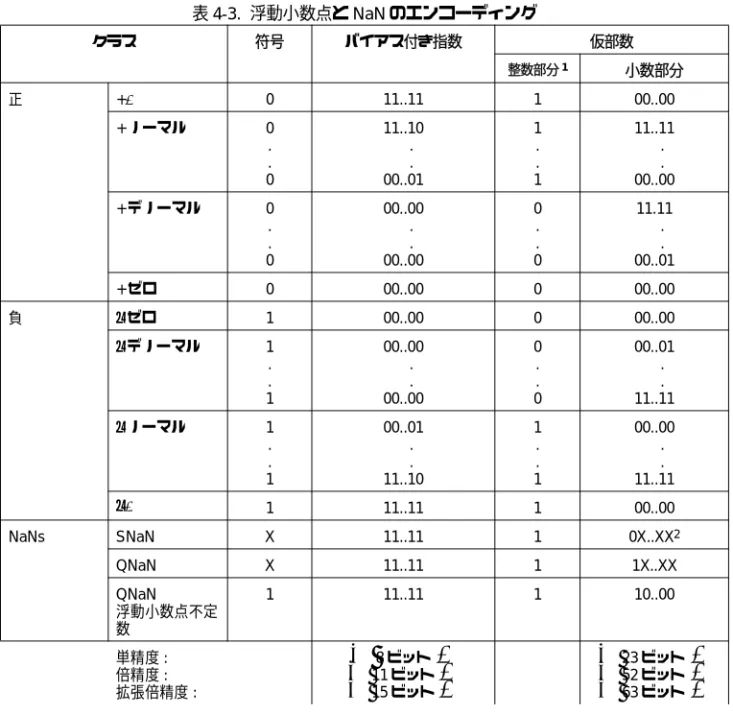

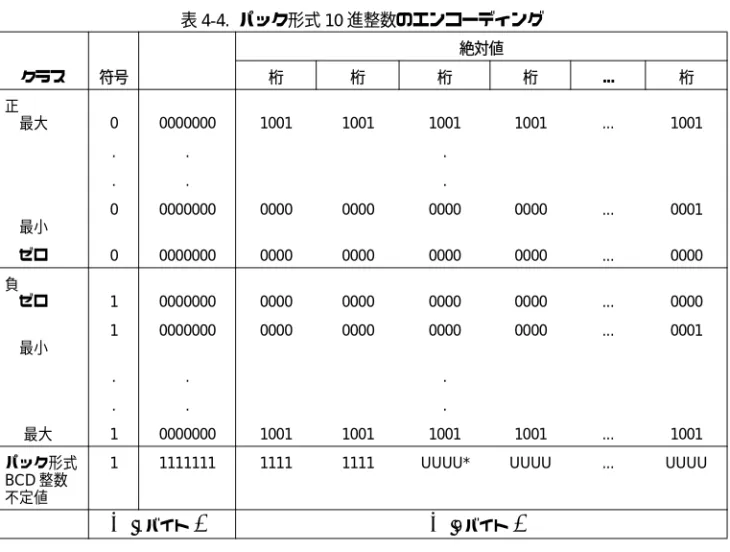

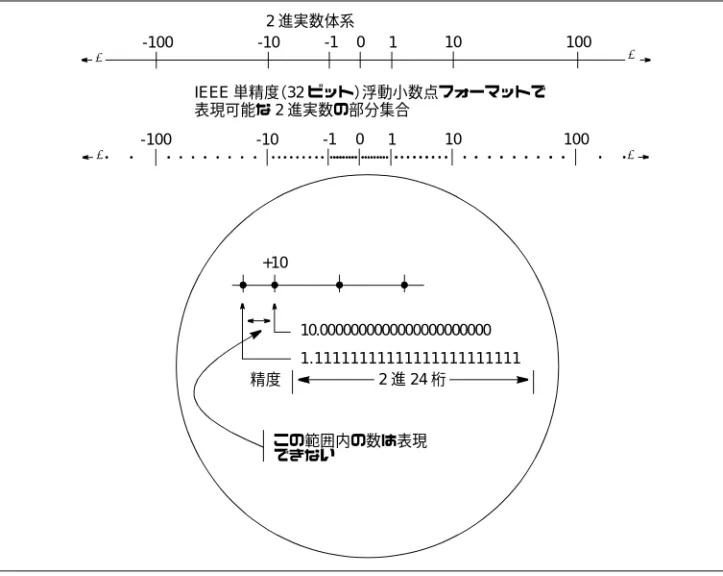

表2-1. 現在のIA-32プロセッサの主な特徴 ... 2-7 表2-2. IA-32プロセッサの過去の世代の主な特徴 ... 2-8 表3-1. 有効なオペランド・サイズ属性とアドレス・サイズ属性 ... 3-17 表3-2. デフォルトのセグメント選択規則 ... 3-19 表4-1. 符号付き整数のエンコーディング ... 4-4 表4-2. 浮動小数点データ型の長さ、精度、および範囲 ... 4-5 表4-3. 浮動小数点とNaNのエンコーディング ... 4-6 表4-4. パック形式10進整数のエンコーディング ... 4-11 表4-5. 実数および浮動小数点数表記法 ... 4-14 表4-6. デノーマライズ処理 ... 4-16 表4-7. QNaNの生成の規則 ... 4-18 表4-8. 丸めモードと丸め制御(RC)フィールドのエンコーディング ... 4-20 表4-9. 数値オーバーフローのスレッショルド範囲 ... 4-24 表4-10. 数値オーバーフローに対するマスク応答 ... 4-24 表4-11. 数値アンダーフローのスレッショルド範囲 ... 4-25 表5-1. 命令グループとIA-32プロセッサ ... 5-1 表6-1. 例外と割り込み ... 6-12 表7-1. 転送命令の動作 ... 7-3 表7-2. 条件付き転送命令 ... 7-5 表7-3. ビット・テストおよび変更命令 ... 7-16 表7-4. 条件付きジャンプ命令 ... 7-19 表8-1. 条件コードの解釈 ... 8-7 表8-2. 精度制御フィールド(PC) ... 8-10 表8-3. サポートされていない拡張倍精度浮動小数点のエンコーディング ... 8-18 表8-4. データ転送命令 ... 8-20 表8-5. 浮動小数点条件付き移動命令 ... 8-20 表8-6. 浮動小数点値比較におけるx87 FPU条件コード・フラグの設定 ... 8-23 表8-7. 浮動小数点値比較におけるEFLAGSステータス・フラグの設定 ... 8-24 表8-8. TEST命令の条件付き分岐用定数 ... 8-25 表8-9. 算術命令と非算術命令 ... 8-31 表8-10. 無効算術演算とそれらに対するマスク応答 ... 8-34 表8-11. ゼロ除算条件とそれらに対するマスク応答 ... 8-35 表9-1. 飽和算術演算でのデータ範囲の限界値 ... 9-6 表9-2. MMX®命令セットのまとめ ... 9-7 表9-3. MMX®テクノロジ命令に対するプリフィックスの影響 ... 9-14 表10-1. PREFETCHh命令のキャッシュ・ヒント ... 10-18 表11-1. 無効な算術演算に対するSSEとSSE2のマスク応答 ... 11-19 表11-2. 電源投入後/リセットまたはINITの実行後のSSEとSSE2のステート ... 11-28 表11-3. SSEおよびSSE2に対するプリフィックスの影響 ... 11-35 表12-1. I/O命令のシリアル化 ... 12-7 表13-1. 各IA-32プロセッサおよびプロセッサ・ファミリ向けのCPUID命令の ソース・オペランドの最大値 ... 13-2 表13-2. CPUID命令が返す情報 ... 13-2 表13-3. EDXレジスタに返される機能フラグ ... 13-3 表A-1. EFLAGSクロス・リファレンス ... A-1 表B-1. EFLAGS条件コード ... B-1 表C-1. x87 FPU浮動小数点例外とSIMD浮動小数点例外 ... C-1 表C-2. x87 FPU浮動小数点命令で生成される例外 ... C-2 表C-3. SSEで生成される例外 ... C-4 表C-4. SSE2で生成される例外 ... C-6 表E-1. ADDPS、ADDSS、SUBPS、SUBSS、MULPS、MULSS、DIVPS、DIVSS ... E-8 表E-2. CMPPS.EQ、CMPSS.EQ、CMPPS.ORD、CMPSS.ORD ... E-8 表E-3. CMPPS.NEQ、CMPSS.NEQ、CMPPS.UNORD、CMPSS.UNORD ... E-8 表E-4. CMPPS.LT、CMPSS.LT、CMPPS.LE、CMPSS.LE ... E-8

表E-5. CMPPS.NLT、CMPSS.NLT、CMPSS.NLT、CMPSS.NLE ... E-8 表E-6. COMISS ... E-9 表E-7. UCOMISS ... E-9 表E-8. CVTPS2PI、CVTSS2SI、CVTTPS2PI、CVTTSS2SI ... E-9 表E-9. MAXPS、MAXSS、MINPS、MINSS ... E-9 表E-10. SQRTPS、SQRTSS ... E-9 表E-11. #I - 無効操作 ... E-10 表E-12. #Z - ゼロ除算 ... E-11 表E-13. #D - デノーマル・オペランド ... E-12 表E-14. #O - 数値オーバーフロー ... E-12 表E-15. #U - 数値アンダーフロー ... E-13 表E-16. #P - 不正確結果(精度) ... E-13

1

本書について

『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、上巻:基本アー キテクチャ』(資料番号 245470J)は、IA-32 インテル ® プロセッサ全般のアーキテクチャとプログラ ミング環境を説明している全 3 巻のうちの1 巻である。他の2 巻を次に示す。•

『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、中巻:命令 セット・リファレンス・マニュアル』(資料番号 245471J)•

『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、下巻:シス テム・プログラミング・ガイド』(資料番号 245472J) 『IA-32 インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル』の「上巻:基本 アーキテクチャ」は、IA-32 プロセッサの基本的なアーキテクチャとプログラミング環境について説 明している。「中巻:命令セット・リファレンス・マニュアル」は、プロセッサの命令セットとオペ コードの構造について説明している。上巻と中巻は、既存のオペレーティング・システムやエグゼ クティブの下で実行するプログラムを開発しているアプリケーション・プログラマを対象としてい る。「下巻:システム・プログラミング・ガイド」は、IA-32 プロセッサのオペレーティング・シス テム・サポート環境について説明している。これには、メモリ管理、保護、タスク管理、割り込み / 例外処理、およびシステム管理モードの説明が含まれる。また、IA-32 プロセッサの互換性に関する 情報も掲載している。下巻が対象とするのは、オペレーティング・システムやBIOS の開発者ならび にプログラマである。1 .1 .

本書の対象となる

IA -3 2

プロセッサ

本書には、主に最近の IA-32 プロセッサに関する情報が記載されている。これには、Pentiumプロ セッサ、P6 ファミリ・プロセッサ、Pentium 4 プロセッサが含まれる。P6 ファミリ・プロセッサと は、P6 ファミリ・マイクロアーキテクチャに基づく IA-32 プロセッサである。P6 ファミリには、 Pentium Pro プロセッサ、Pentium II プロセッサ、Pentium III プロセッサが含まれる。Pentium 4 プロ セッサは、新しいインテル NetBurstマイクロアーキテクチャに基づく IA-32 プロセッサ・ファミ リの最初の製品である。1 .2 .

『

IA -3 2

インテル

®アーキテクチャ・ソフトウェア・デベロッパー

ズ・マニュアル、上巻:基本アーキテクチャ』の概要

本書は、次の内容で構成されている。 第1章 − 本書について。『IA-32 インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・マニュ アル』の全3 巻それぞれの内容を簡単に説明する。また、これらのマニュアルで使用されている表記 法について説明するとともに、インテルのマニュアルやドキュメンテーションのなかでプログラマ やハードウェア設計者に関係する関連資料を併記している。第2章 − IA-32 インテル® アーキテクチャの概説。IA-32 アーキテクチャと、このアーキテクチャ を基礎とするインテル・プロセッサのファミリについて概説する。また、これらのプロセッサに見 られる共通の特徴や、IA-32 アーキテクチャの変遷について簡単に説明する。 第3章 − IA-32 基本実行環境。メモリ構成のモデルを概説するとともに、アプリケーション上で使 用するレジスタ・セットについて説明する。 第4章 − データ型。プロセッサが認識するデータ型とアドレス指定モードについて説明する。実数、 浮動小数点形式、浮動小数点例外の概要も示す。 第5章 − 命令セットの要約。すべてのIA-32 アーキテクチャ命令の一覧を、テクノロジ・グループ

( 汎用命令、x87 FPU 命令、MMX®テクノロジ命令、ストリーミング SIMD 拡張命令(SSE)、ストリー

ミング SIMD 拡張命令2 (SSE2)、システム命令 ) ごとに分けて示す。各グループの命令は、機能的に 関連のあるグループごとに記載されている。 第6章 − プロシージャ・コール、割り込み、例外。プロシージャ・スタックと、プロシージャ・ コールの実行のメカニズム、割り込みと例外処理のメカニズムについて説明する。 第7章 − 汎用命令によるプログラミング。汎用レジスタおよびセグメント・レジスタ上で基本デー タ型を操作する、基本的なロード命令とストア命令、プログラム制御命令、算術命令、ストリング 命令について説明する。プロテクト・モードで実行されるシステム命令についても説明する。 第8章 − x87 FPU によるプログラミング。x87 の浮動小数点ユニット(FPU)について説明し、浮 動小数点レジスタとデータ型、浮動小数点命令セット、プロセッサの浮動小数点例外条件について 説明する。 第9章 − インテル® MMX®テクノロジ・レジスタによるプログラミング。インテル MMX テクノ ロジについて説明する。これには、MMX テクノロジ・レジスタとデータ型、MMX 命令セットの概 要についての説明が含まれる。

第10章 − ストリーミングSIMD拡張命令 (SSE) によるプログラミング。SSE について説明する。 これには、XMM レジスタ、MXCSR レジスタ、パックド単精度浮動小数点データ型についての説明 が含まれる。また、SSE 命令セットの概要と、SSE にアクセスするコードを作成する際のガイドライ ンについても説明する。

第11章 − ストリーミングSIMD拡張命令2 (SSE2) によるプログラミング。SSE2 について説明す る。これには、XMM レジスタ、パックド倍精度浮動小数点データ型についての説明が含まれる。ま た、SSE2 の命令セットの概要と、SSE2 にアクセスするコードを作成する際のガイドラインについて も説明する。この章では、SSE と SSE2 によって生成される SIMD 浮動小数点例外についても説明す る。また、オペレーティング・システムとアプリケーション・コードに SSE とSSE2 のサポート機能 を組み込むための一般的なガイドラインを示す。

第12章 − 入出力。I/O ポートのアドレス指定、I/O 命令、I/O 保護メカニズムなど、プロセッサの I/O アーキテクチャについて説明する。

第13章 − プロセッサの識別と機能の判定。プロセッサが備えている CPU タイプおよび機能を判定

する方法について説明する。

付録A− EFLAGS クロス・リファレンス。IA-32 の命令が EFLAGS レジスタの各フラグに及ぼす影

付録B− EFLAGS 条件コード。条件付きのジャンプ、移動、条件コード命令でのバイト・セットに おいて EFLAGS レジスタの条件コード・フラグ(OF、CF、ZF、SF、PF)がどのように使用される かを説明する。

付録C− 浮動小数点例外の要約。x87 FPU 浮動小数点、SSE およびSSE2 のSIMD 浮動小数点命令で 発生する例外を一覧で示す。

付録D− x87 FPU 例外ハンドラを作成する際のガイドライン。FPU 例外に対してMS-DOS* 互換の

例外処理機能を設計し開発する方法について説明する。これには、ソフトウェアとハードウェアの 要件、アセンブリ言語コードの例が含まれる。また、信頼性の高い FPU 例外ハンドラを開発するた めの一般的な技法について説明する。

付録E−SIMD浮動小数点例外ハンドラを作成する際のガイドライン。SSE および SSE2 の浮動小

数点命令で発生する例外と、これらの例外を処理する例外ハンドラを作成する際のガイドラインに ついて説明する。

1 .3 .

『

IA -3 2

インテル

®アーキテクチャ・ソフトウェア・デベロッパー

ズ・マニュアル、中巻:命令セット・リファレンス・マニュアル』

の概要

『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、中巻』は、次の 内容で構成されている。 第1章−本書について。『IA-32 インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・マニュ アル』の 3 巻それぞれの内容を簡単に説明する。また、これらのマニュアルで使用されている表記法 について説明するとともに、インテルのマニュアルやドキュメンテーションのなかでプログラマや ハードウェア設計者に関係する関連資料を併記している。 第2章−命令フォーマット。IA-32 の全命令が使用するマシン・レベル命令のフォーマットについ て説明し、許可されるプレフィックスのエンコーディング、オペランド識別子バイト(ModR/M バ イト)、アドレッシング・モード指示子バイト(SIB バイト)、ディスプレースメント・バイトと即値 バイトについても説明する。 第3章−命令セット・リファレンス。IA-32 各命令を詳細に説明している。これには、演算アルゴ リズムの説明、フラグの影響、オペランド・サイズとアドレス・サイズ属性の効果、および発生し うる例外などを詳細に説明する。命令は、アルファベット順に記載している。汎用命令、x87 FPU 命 令、MMX 命令、SSE、SSE2、システム命令の説明も本章に含まれる。 付録A −オペコード・マップ。IA-32 命令セットのオペコード・マップを示す。 付録B −命令フォーマットおよびエンコーディング。IA-32 命令の各フォームのバイナリ・エンコー ディングを示す。 付録C −機能的に同等のインテルC/C++コンパイラ組み込み関数。IA-32 MMX 命令、SSE、SSE2 のそれぞれと機能的に同等のインテル® C/C++ コンパイラ組み込み関数およびアセンブリ・コードを 示す。1 .4 .

『

IA -3 2

インテル

®アーキテクチャ・ソフトウェア・デベロッパー

ズ・マニュアル、下巻:システム・プログラミング・ガイド』の

概要

『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、下巻』は以下の 内容で構成されている。 第1章−本書について。『IA-32 インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・マニュ アル』の 3 巻それぞれの内容を簡単に説明する。また、これらのマニュアルで使用されている表記法 について説明するとともに、インテルのマニュアルやドキュメントのなかでプログラマやハード ウェア設計者に関係する関連資料を併記している。 第2章−システム・アーキテクチャの概要。IA-32 プロセッサの動作モード、オペレーティング・シ ステムやエグゼクティブをサポートするため IA-32 アーキテクチャに用意されているメカニズムに ついて説明する。これには、システム関連のレジスタとデータ構造の説明や、システム関連の命令 の説明が含まれる。また、実アドレス・モードと保護モード間の切り替えに必要なステップについ ても説明する。 第3章−保護モードにおけるメモリ管理。セグメンテーションとページングをサポートするデータ 構造、レジスタ、命令について説明し、それらを使用して「フラット」(セグメント化されていない) メモリ・モデルまたはセグメント化されたメモリ・モデルを使用する方法を説明する。 第4章−保護。IA-32 アーキテクチャのページ保護とセグメント保護のサポートについて説明する。 この章はまた、特権規則、スタックの切り替え、ポインタの検証、ユーザ・モードとスーパバイザ・ モードの使用方法を説明する。 第5章−割り込みと例外の処理。IA-32 アーキテクチャで定義されている基本的な割り込みメカニ ズムについて説明し、割り込みや例外と保護との関係を示し、アーキテクチャが各例外タイプをど のように処理するかについて説明する。章の最後には、それぞれの IA-32 の例外に対する参照情報を 掲載している。 第6章−タスク管理。マルチタスキングやタスク間保護を提供するため IA-32 アーキテクチャに用 意されているメカニズムについて説明する。 第7章−マルチ・プロセッサ管理。共有メモリ、メモリ・オーダリング、ハイパー・スレッディン グ・テクノロジを使用してマルチ・プロセッサをサポートする命令やフラグについて説明する。 第8章 - APIC(Advanced Programmable Interrupt Controller)。ローカル APIC のプログラミング・イ ンターフェイスについて説明し、ローカル APIC とI/O APIC 間のインターフェイスの概要を示す。第9章−プロセッサの管理と初期化。リセット初期化後の IA-32 プロセッサ、浮動小数点ユニット および SIMD 浮動小数点ユニットのステートを定義する。この章ではさらに、実アドレス・モード動 作や保護モード動作向けのセットアップ手順、両モード間の切り替え手順を説明する。 第10章−メモリ・キャッシュ制御。キャッシングの一般的な概念と、IA-32 アーキテクチャがサ ポートするキャッシュ・メカニズムについて説明する。この章ではさらに、メモリ・タイプ・レン ジ・レジスタ(MTRR)や、これらのレジスタを使用して物理メモリの各メモリ・タイプをマッピン グする方法についても説明する。また、Pentium IIIプロセッサ、Pentium 4 プロセッサ、インテル®

Xeon™ プロセッサで新たに導入されたキャッシュ制御命令とメモリ・ストリーミング命令の使用方 法についても説明する。

第11章−インテル® MMX®テクノロジ・システム・プログラミング。システム・プログラミング・ レベルで処理し、かつ配慮しなければならないインテル MMX テクノロジの各局面について説明す る。これには、タスク・スイッチング、例外処理、既存システム環境との互換性の説明が含まれる。 インテルMMX テクノロジは、Pentium プロセッサでIA-32 アーキテクチャに導入された。 第12章− SSEおよびSSE2システム・プログラミング。システム・プログラミング・レベルで取 り扱い、考慮に入れる必要がある、ストリーミングSIMD 拡張命令の機能について説明する。これに は、タスク・スイッチング、例外処理、および既存のシステム環境との互換性の説明も含む。 第13章−システム管理。 IA-32 アーキテクチャのシステム管理モード(SMM)と温度モニタ機能 について説明する。 第14章−マシン・チェック・アーキテクチャ。Pentium プロセッサでインテル・アーキテクチャに 導入されたマシン・チェック・アーキテクチャについて説明する。 第15章−デバッグと性能モニタリング。インテル・アーキテクチャに用意されているデバッグ・レ ジスタおよびその他のデバッグ・メカニズムについて説明する。この章ではまた、タイム・スタン プ・カウンタと性能モニタリング・カウンタについても説明する。 第16章− 8086エミュレーション。IA-32 アーキテクチャの実アドレス・モードと仮想 8086 モード について説明する。 第17章− 16ビット・コードと32ビット・コードの混在。同一プログラムまたは同一タスク内で、 16 ビット・コードと 32 ビット・コードのモジュールを混在させる方法について説明する。 第18章− IA-32の互換性。各種の IA-32 プロセッサの互換性について説明する。これには、Intel®

286 プロセッサ、Intel386™ プロセッサ、Intel486™ プロセッサ、Pentium プロセッサ、P6 ファミリ、 Pentium 4 プロセッサ、インテル Xeon プロセッサが含まれる。P6 ファミリとは、Pentium Pro プロ セッサ、Pentium II プロセッサ、Pentium IIIプロセッサを指す。32 ビットの IA-32 プロセッサ(Intel386 プロセッサ、Intel486 プロセッサ、Pentium プロセッサ、P6 ファミリ・プロセッサ)間の違いは、

『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル』の全 3 巻を通じ

てアーキテクチャの特定の機能に関連する箇所で説明する。この章では、すべての IA-32 プロセッ サに当てはまる互換情報を提供し、16 ビットの IA-32 プロセッサ(Intel 8086 プロセッサと Intel 286 プロセッサ)に関する基本的な違いについても説明する。 付録A −性能モニタリング・イベント。性能モニタリング・カウンタでカウント可能なイベントを 併記するとともに、これらのイベントを選択する際に使用できるコードを併記する。Pentium プロ セッサおよびP6 ファミリ・プロセッサ両方のイベントについて説明する。 付録B −モデル固有レジスタ(MSR)。Pentium プロセッサ、P6 ファミリ・プロセッサ、Pentium 4 プロセッサ、インテルXeon プロセッサで使用可能なMSR と、それらの機能の一覧を示す。 付録C − P6ファミリ・プロセッサのMP初期化。MP システムでP6 ファミリ・プロセッサをブート するための MP プロトコルの使用法の例を示す。

付録D − LINT0およびLINT1入力のプログラミング。特定の割り込みベクタに対する LINT0 および LINT1 ピンのプログラミング方法の例を示す。

付録E −マシン・チェック・エラー・コードの解釈。P6 ファミリ・プロセッサ上で発生したマシ

ン・チェック・エラーのエラー・コードの解釈方法の例を示す。

付録F − APICバス・メッセージの形式。P6 ファミリおよびPentium プロセッサの APIC バス上に送 信されるメッセージの形式について説明する。

1 .5 .

表記法

本書では、データ構造フォーマット、命令のシンボリック表現、および 16 進数に対して特別な表記 法を使用している。この表記法を理解しておけば、本書を理解しやすくなる。1.5.1.

ビット・オーダとバイト・オーダ

メモリ内のデータ構造図では、小さい方のアドレスが図の下の方に示され、上に行くほど大きくな る。ビット位置は、右から左に番号が付けられている。セットされたビットの数値は、2 をビット位 置を表す数で累乗した値に等しくなる。IA-32 プロセッサは「リトル・エンディアン」マシンであり、 ワードのバイトは最下位バイトから順に番号が付けられている。図 1-1. にこれらの規則を示す。1.5.2.

予約ビットとソフトウェア互換性

レジスタやメモリのレイアウトの説明で、特定のビットが「予約済み」と記されていることがある。 ビットが予約済みとして記されている場合は、将来のプロセッサとの互換性を維持するため、これ らのビットが将来的に何らかの機能を持つものとみなした上で、ソフトウェア上でこれらのビット を取り扱わなければならない。予約ビットの動作は、未定義としてだけではなく、予測不可能とみ なさなければならない。予約ビットを処理する場合は、ソフトウェア上で、次に示すガイドライン に従わなければならない。•

予約ビットを含むレジスタの値をテストするときは、予約ビットのステートに依存してはなら ない。テストする前に、予約ビットをマスクアウトする。•

メモリまたはレジスタに格納するときは、予約ビットのステートに依存してはならない。•

予約ビットに書き込まれた情報が保存されるものとみなしてはならない。•

レジスタにロードするときは、マニュアル上で予約ビットに対して値を指定している場合には、 その値を予約ビットにロードしなければならない。マニュアルになければ、同じレジスタから 前に読まれた値を再ロードする。 図1-1. ビット・オーダとバイト・オーダ バイト 3 データ構造 バイト 1 バイト 2 バイト 0 31 24 23 16 15 8 7 0 上位アドレス ビット・オフセット 28 24 20 16 12 8 4 0 下位アドレス バイト・オフセット注記 ソフトウェアを、IA-32 レジスタの予約ビットのステートに依存させることは絶対 に避けること。予約ビットの値に依存すると、プロセッサが予約ビットを処理す る方法が決定されていないにもかかわらず、その未決定の方法にソフトウェアが 依存することになる。予約ビットの値に依存したプログラムを作成すると、将来 のプロセッサとの互換性を損なう危険がある。

1.5.3.

命令オペランド

命令をシンボルで表現する場合は、IA-32 のアセンブリ言語のサブセットを使用する。このサブセッ トでは、命令は次の形式をとる。label: mnemonic argument1, argument2, argument3

上記の形式において:

•

label は識別子で、後にコロンが続く。•

mnemonic は、同じ機能を持つ命令オペコードの予約名である。•

オペランド argument1、argument2、argument3 はオプションである。オペコードに応じて、0 ∼ 3 つのオペランドを使用する。オペランドを使用する場合、オペランドはリテラルかデータ項 目の識別子のいずれかの形式をとる。オペランド識別子は、レジスタの予約名であるか、また はプログラムの別の箇所(例には示されていないことがある)で宣言されたデータ項目に割り 当てられているものとみなされる。 演算命令や論理命令にオペランドが2 つある場合は、右側のオペランドがソースであり、左側がデス ティネーションになる。 例:LOADREG: MOV EAX, SUBTOTAL

この例では、LOADREG はラベル、MOV はオペコードのニーモニック識別子、EAX はデスティネー ション・オペランド、SUBTOTAL はソース・オペランドになる。アセンブリ言語によっては、ソー スとデスティネーションの順序が逆になることがある。

1.5.4.

16

進数と

2

進数

16 をベースとする数(16 進数)は、末尾に文字 H を付けた 16 進数字の文字列で表す(たとえば、 F82EH)。16 進数字は、0、1、2、3、4、5、6、7、8、9、A、B、C、D、E、F のいずれかである。 ベースを 2 とする数(2 進数)は、1 と 0 の文字列で表し、場合によって末尾に文字 B を付ける(た とえば、1010B)。「B」を付けるのは、数値のタイプに混乱が生じるような場合に限られる。1.5.5.

セグメント化アドレス指定

インテル® アーキテクチャ・プロセッサでは、バイトによるアドレス指定を採用している。つまり、 メモリはバイトの連続として構成されアクセスされる。1 バイトをアクセスするのか複数バイトをア クセスするのかにかかわらず、そのバイトを格納しているメモリへのアクセスには、1 つのバイト・ アドレスを使用する。アドレス指定が可能なメモリの範囲を、アドレス空間と呼ぶ。 プロセッサは、セグメント化アドレス指定もサポートしている。これは、プログラムがセグメント と呼ばれる多数の独立したアドレス空間を持つ場合のアドレス指定の一形式である。たとえば、プ ログラムはコード(命令)とスタックを別々のセグメントに保持できる。これにより、コード・ア ドレスは常にコード空間を、スタック・アドレスは常にスタック空間を参照することが可能になる。 セグメント内のバイト・アドレスを指定するには、次の表記法を使用する。 Segment-register:Byte-address たとえば、次のセグメント・アドレスは、DS レジスタがポイントするセグメント内のアドレスFF79H にあるバイトを指す。 DS:FF79H また、次のセグメント・アドレスは、コード・セグメントの命令アドレスを指す。CS レジスタは コード・セグメントをポイントし、EIP レジスタは命令のアドレスを格納する。 CS:EIP1.5.6.

例外

例外とは、命令がエラーを引き起こした場合に一般的に発生するイベントである。例えば、0 で除算 しようとすると例外が発生する。ただし、ブレークポイントのように、エラー以外の条件で発生す る例外もある。例外によっては、エラー・コードを提示するものもある。エラー・コードによって、 エラーに関する追加情報が示される。例外とエラー・コードを示すために使用する表記例を次に示 す。 #PF(fault code) この例が示すのは、フォルトのタイプを指すエラー・コードが報告される条件でのページ・フォル ト例外である。ある種の条件では、エラー・コードが発生する例外でも、正確なコードを報告でき ない場合がある。このような場合、一般保護例外の例が次に示すように、エラー・コードは 0 になる。 #GP(0) 例外のニーモニックと、その説明については、『IA-32 インテル® アーキテクチャ・ソフトウェア・ デベロッパーズ・マニュアル、下巻』の第 5 章「割り込みと例外の処理」を参照のこと。1 .6 .

参考文献

インテル・プロセッサに関連する資料の一覧は、以下のインテル・ウェブ・サイトに記載されている。 http://www.intel.co.jp/jp/developer/design/processor/index.htm (日本語) http://developer.intel.com/design/processor/index.htm (英語)このウェブ・サイトに記載されている資料には、オンラインで表示できるものと、オンラインで注 文できるものがある。入手可能な資料は、まずインテル・プロセッサ別に、次に資料のタイプ ( アプ リケーション・ノート、データ・シート、マニュアル、論文、および仕様のアップデート) 別に記載 されている。関連する資料には、以下のものがある。