割り込み

セクション 6. 割り込み

ハイライト

本セクションには下記の主要項目を記載しています。 6.1 はじめに ... 6-2 6.2 ノンマスカブル トラップ ... 6-5 6.3 割り込み処理タイミング ... 6-11 6.4 割り込み制御 / ステータス レジスタ ... 6-15 6.5 割り込みのセットアップ手順 ... 6-25 6.6 レジスタマップ ... 6-28 6.7 関連アプリケーション ノート ... 6-29 6.8 改訂履歴 ... 6-30 注意 : この日本語版文書は参考資料としてご利用ください。最新情報は必ずオリジ ナルの英語版をご参照願います。6.1

はじめに

dsPIC33E/PIC24E の割り込みコントローラは、CPU に対する多数の周辺モジュールからの割 り込み要求の中から、最も優先度の高い 1 つの割り込み要求を選択します。dsPIC33E/PIC24E 本モジュールは下記の特長を備えます。 • 最大 8 つのプロセッサ例外とソフトウェア トラップ • ユーザ選択可能な 7 段階の優先度 • 最大 254 ベクタの割り込みベクタテーブル (IVT) • 割り込みまたは例外要因の各々に一意のベクタ • 同一ユーザ指定優先度を持つ要因間の優先順位は自然順序優先度に従う • 固定された割り込みエントリとリターン レイテンシ6.1.1

割り込みベクタテーブル

図 6-1に示すように、IVT はプログラムメモリの 0x000004 から始まります。IVT には 254 個 のベクタがあり、そのうち 8 個はノンマスカブル トラップベクタ、残りは最大 246 個の割り込 み要因です。一般的に、各割り込み要因には固有のベクタが割り当てられます。各割り込みベ クタは 24 ビット幅のアドレスを格納します。各割り込みベクタ位置に書き込まれた値は、対 応する割り込みサービスルーチン (ISR) の開始アドレスを指します。 補助フラッシュを備えたデバイスでは、補助フラッシュメモリ内に 1 つの補助割り込みベクタ が存在します。この割り込みベクタは、補助フラッシュからプログラムを実行している際にト ラップまたは有効な割り込みが発生した時に実行される ISR の開始アドレス (24 ビット幅 ) を 格納します。補助割り込みベクタが利用可能かどうか、およびその格納位置については、各デ バイスデータシートの「メモリ構成」と「割り込みコントローラ」を参照してください。6.1.2

リセット シーケンス

例外コントローラはリセット処理には関与しないため、デバイスリセットは厳密には例外処理 ではありません。dsPIC33E/PIC24E は、リセット時にレジスタをクリアしてプログラム カウ ンタ (PC) を強制的にゼロに設定した後に、0x000000 からプログラムの実行を開始します。ユー ザ アプリケーションはリセットアドレスに GOTO 命令を書き込む事によって、プログラムの実 行を適当な起動ルーチンへリダイレクトできます。 補助フラッシュを備えたデバイスでは、オプションの設定により、リセット位置を補助フラッ シュに設定する事ができます。補助フラッシュが利用可能かどうかと、リセット位置を補助フ ラッシュに設定する方法については、各デバイスデータシートの「メモリ構成」と「特殊機能」 を参照してください。 Note: ファミリ リファレンス マニュアルの本セクションは、デバイス データシートの補 足を目的としています。本セクションの内容は dsPIC33E/PIC24E ファミリの一部 のデバイスには対応していません。 本書の内容がお客様のご使用になるデバイスに対応しているかどうかは、最新デ バイス データシート内の「割り込み」の冒頭に記載している注意書きでご確認く ださい。 デバイス データシートとファミリ リファレンス マニュアルの各セクションは、マ イクロチップ社のウェブサイト (http://www.microchip.com)でご覧になれます。Note: IVT の未実装または未使用ベクタ位置には、RESET 命令を実行する既定値割り込 みハンドラルーチンのアドレスを書き込む必要があります。

割り込み

図 6-1: 割り込みベクタテーブル IVT テーブルの下ほど自然順序優先度が低い リセット – GOTO 命令 0x000000 リセット – GOTO アドレス 0x000002 オシレータ障害トラップベクタ 0x000004 アドレスエラー トラップベクタ 0x000006 一般ハードトラップ ベクタ 0x000008 スタックエラー トラップベクタ 0x00000A 算術エラー トラップベクタ 0x00000C DMAC エラー トラップベクタ 0x00000E 一般ソフト トラップベクタ 0x000010 予約済み 0x000012 割り込みベクタ 0 0x000014 割り込みベクタ 1 0x000016 : : : : : : 割り込みベクタ 52 0x00007C 割り込みベクタ 53 0x00007E 割り込みベクタ 54 0x000080 : : : : : : 割り込みベクタ 116 0x0000FC 割り込みベクタ 117 0x0000FE 割り込みベクタ 118 0x000100 割り込みベクタ 119 0x000102 割り込みベクタ 120 0x000104 : : : : 割り込みベクタの詳細は 各デバイス データシート 内の「割り込み」を参照 してください。6.1.3

CPU 優先度ステータス

CPU は 16 段階の優先度 (0 ~ 15) で動作できます。割り込みまたはトラップ要因の優先度がそ の時点の CPU 優先度より高い場合にのみ、例外処理が起動します。周辺モジュールおよび外 部の割り込み要因は、優先度 0 ~ 7 に設定できます。CPU 優先度 8 ~ 15 は、トラップ要因向 けに予約されています。 トラップとは、ハードウェアおよびソフトウェア問題の検出を目的とするノンマスカブル割り 込み要因です (6.2 「ノンマスカブル トラップ」参照 )。 各トラップ要因の優先度は固定されてお り、1 つの優先度には 1 つのトラップだけが割り当てられます。優先度 0 に設定された割り込 み要因は、CPU 優先度よりも高くなる事がないため、実質的に無効になります。 現在の CPU 優先度は、下記のステータスビットにより示されます。• CPU ステータス レジスタ (SR<7:5>) の CPU 割り込み優先度ステータスビット (IPL<2:0>) • コア制御レジスタ (CORCON<3>) の CPU 割り込み優先度ステータスビット (IPL3)

IPL<2:0> ステータスビットは読み書き可能です。従ってユーザ アプリケーションでこれらの ビットに書き込んで CPU 優先度を設定する事により、その優先度以下の全ての割り込み要因 を無効にできます。例えば IPL<2:0> = 011 に設定した場合、優先度 0 ~ 3 の全ての要因は、 CPU に対して割り込めません。 トラップイベントは、全てのユーザ割り込み要因よりも高い優先度を持ちます。トラップイベ ントの実行中は IPL3 ビットがセットされます。ユーザ アプリケーションは IPL3 ビットをクリ アできますが、セットする事はできません。アプリケーションによっては、トラップ発生時に IPL3 ビットをクリアして、トラップの原因となった命令の直後の命令とは異なる命令に分岐さ せる必要があります。 IPL<2:0> を 111 に設定する事により、全てのユーザ割り込みを無効にで きます。

6.1.4

割り込み優先度

周辺モジュール割り込み要因には、7 段階の優先度を割り当てる事ができます。ユーザは、IPCx レジスタ内の各ニブルの下位 3 ビットを使って、各割り込みに優先度を割り当てる事ができま す。この場合、各ニブルの bit 3 は常に「0」として読み出されます。これらのビットは各割り 込みの優先度を定義します。割り当て可能な優先度は 1 ( 最低優先度 ) ~ 7 です。ある割り込 みに対応する IPC ビットを全てクリアすると、その割り込みは実質的に無効になります ( 優先 度 0)。 複数の割り込み要因に対して同一の優先度を割り当てる事ができます。ユーザによって同一の 優先度が割り当てられた複数の割り込み要因間の競合を解消するために、各割り込み要因には IVT 内の並び順に従う自然順序優先度が割り当てられています ( 割り込みベクタテーブルの正 確な情報は、各デバイスデータシート内の「割り込み」に記載しています )。番号が若い割り 込みベクタほど高い自然順序優先度を持ちます。保留中の割り込み要因の総合優先度は、まず ユーザ アプリケーションが IPCx レジスタで割り当てた優先度に従い、これが同じであれば、 IVT 内の自然順序優先度によって決まります。 自然順序優先度は、同一のユーザ アプリケーション割り当て優先度を持つ複数の割り込みが同 時に保留状態にある場合にのみ、それらの競合を回避するために使われます。優先度の競合が 解消して例外処理が始まった後は、これよりも高いユーザ アプリケーション割り当て優先度を 持つ割り込み要因だけが CPU に対して割り込めます。すなわち、例外処理の実行中に、同一 ユーザ アプリケーション割り当て優先度を持ち自然順序優先度がより高い割り込みが新たに 要求されても、それらは実行中の例外処理が完了するまで全て保留されます。 各割り込み要因には 7 段階の優先度を設定できます。ユーザ アプリケーションで優先度を設定 する事により、自然順序優先度の低い割り込みに非常に高い総合優先度を持たせる事ができま す。例えば、自然順序優先度が低い UART1 RX 割り込みに優先度 7 を設定し、逆に自然順序優 先度が高い外部割り込み 0 (INT0) に優先度 1 を設定する事ができます。Note: dsPIC33E/PIC24E の IVT に含まれている周辺モジュールと割り込み要因はデバイ スごとに異なります。本書には、dsPIC33E/PIC24E ファミリの全デバイスを包括 した全ての割り込み要因を記載しています。詳細は各デバイスのデータシートを 参照してください。

割り込み

6.2

ノンマスカブル トラップ

トラップはノンマスカブルでネスト可能な割り込みです。トラップの優先度は固定されていま す。トラップを使うと、アプリケーションのデバッグ中と動作中に異常動作を修正できます。 トラップエラー発生時にユーザ アプリケーションでトラップ条件の修正処理を実行しない場 合、トラップベクタにはデバイスリセット用ソフトウェア ルーチンのアドレスを書き込む必要 があります。そうでない場合、ユーザ アプリケーションはトラップ条件修正サービスルーチン のアドレスをトラップベクタに書き込む必要があります。 dsPIC33E/PIC24E は下記のノンマスカブル トラップ要因を実装しています。 • オシレータ障害トラップ • スタックエラー トラップ • アドレスエラー トラップ • 算術エラートラップ • DMAC エラートラップ • 一般ハードトラップ • 一般ソフトトラップ 多くのトラップ条件では、トラップを引き起こした命令の実行が完了してから例外処理が始ま ります。従って、トラップを引き起こした命令の動作をユーザ アプリケーションで修正しなけ ればならない場合があります。 各トラップ要因の優先度は IVT 内の順位によって決まります ( 優先度は固定されています )。オ シレータ障害トラップが最高の優先度を持ち、DMA コントローラ (DMAC) エラートラップが 最低の優先度を持ちます (図 6-1参照 )。さらに、トラップ要因はソフトトラップとハードト ラップに分類されます。6.2.1

ソフトトラップ

DMAC エラートラップ ( 優先度 10)、算術エラートラップ ( 同 11)、スタックエラー トラップ ( 同 12) はソフトトラップに分類されます。ソフトトラップは、IVT 内の順位によって優先度 が決まるノンマスカブル割り込み要因と同様に扱う事ができます。ソフトトラップは割り込み と同様に処理され、例外処理の前に検出と認識のために 2 サイクルを要します。このため、ソ フトトラップが認識される前に別の命令が実行される可能性があります。 6.2.1.1 スタックエラー トラップ ( ソフトトラップ、優先度 12) スタックはリセット時に 0x1000 に初期化されます。スタックポインタのアドレスが 0x1000 よ り低いと、スタックエラー トラップが発生します。 スタックポインタに関連付けられたスタックリミット (SPLIM) レジスタは、リセット時に初期 化されません。SPLIM レジスタにワード書き込みをするまで、スタック オーバーフロー チェッ クは有効になりません。 W15 を使ってソースまたはデスティネーション ポインタとして生成された全ての実効アドレ ス (EA) は、SPLIM レジスタ内の値と比較されます。実効アドレスの方が大きいと、スタック エラー トラップが発生します。また、実効アドレスの計算がデータ空間の終端 (0xFFFF) を超 えた場合も、スタックエラー トラップが発生します。 ス タ ッ ク エ ラ ー は、INTCON1 レジスタのスタックエラー トラップ ステータスビット (STKERR) をポーリングする事により、ソフトウェアで検出できます。トラップ サービスルー チン (TSR) への再入を防ぐために、STKERR ステータスフラグをソフトウェアでクリアする必 要があります。 6.2.1.2 算術エラー トラップ ( ソフトトラップ、優先度 11) 下記のイベントにより、算術エラートラップが発生する可能性があります。 • アキュムレータ A のオーバーフロー • アキュムレータ B のオーバーフロー • アキュムレータの致命的オーバーフローINTCON1 レジスタの下記 3 ビットの設定により、3 種類のアキュムレータ オーバーフロー ト ラップを有効にできます。 • INTCON1 レジスタのアキュムレータ A オーバーフロー トラップ イネーブルビット (OVATE) は、アキュムレータ A のオーバーフロー イベントに対するトラップを有効にします。 • INTCON1 レジスタのアキュムレータ B オーバーフロー トラップ イネーブルビット (OVBTE) は、アキュムレータ B のオーバーフロー イベントに対するトラップを有効にします。 • INTCON1 レジスタの致命的オーバーフロー トラップ イネーブル (COVTE) は、いずれかのア キュムレータで発生した致命的オーバーフロー イベントに対するトラップを有効にします。こ れらのトラップが検出されると、INTCON1 レジスタの下記の ERROR ビットがセットされます。 - アキュムレータ A オーバーフロー トラップ フラグビット (OVAERR) - アキュムレータ B オーバーフロー トラップ フラグビット (OVBERR) - アキュムレータ A 致命的オーバーフロー トラップ フラグビット (COVAERR) - アキュムレータ B 致命的オーバーフロー トラップ フラグビット (COVBERR) アキュムレータ A (B) オーバーフローとは、アキュムレータ A (B) で bit 31 からの桁上げが発生 した事を意味します。31 ビット飽和モードを有効にしたアキュムレータでは、オーバーフロー は発生しません。致命的オーバーフローとは、いずれかのアキュムレータで bit 39 からの桁上 げが発生した事を意味します。アキュムレータ飽和 (bit 31 または 39) を有効にした場合には、 致命的オーバーフローは発生しません。 ゼロ除算トラップを無効にする事はできません。ゼロ除算は、除算命令を実行する REPEAT ルー プの初回実行時にチェックされます。ゼロ除算が検出されると、INTCON1 レジスタの算術エ ラー ステータスビット (DIV0ERR) がセットされます。 アキュムレータ シフトトラップを無効にはできません。SFTAC 命令を使うと、リテラル値ま たはいずれかのワーキング レジスタ内の値を用いてアキュムレータをシフトできます。シフト 値が ±16 ビットを超えると算術エラートラップが発生し、INTCON1 レジスタのアキュムレー タ シフトエラー ステータスビット (SFTACERR) がセットされます。この場合 SFTAC 命令は 実行されますが、シフト結果はアキュムレータに書き込まれません。 算術エラートラップは、INTCON1 レジスタの算術エラー ステータスビット (MATHERR) をポー リングする事により、ソフトウェアで検出できます。トラップ サービスルーチンへの再入を防 ぐ た め に、MATHERR ステータスフラグをソフトウェアでクリアする必要があります。 MATHERR ステータスビットをクリアする前に、トラップの発生原因となった全ての条件をク リアする必要があります。アキュムレータ オーバーフローによるトラップが発生した場合、SR レジスタのアキュムレータ オーバーフロー ステータスビット (OA または OB) をクリアする必 要があります。 6.2.1.3 DMAC エラー トラップ ( ソフトトラップ、優先度 10) DMAC エラートラップは下記の条件で発生します。 • RAM 書き込み衝突 • DMA 対応周辺モジュールの RAM 書き込み衝突 書き込み衝突エラーは、ノンマスカブル CPU トラップイベントを保証するためのシステム整 合性に重大な影響を及ぼします。CPU と DAM チャンネルが同時に同一アドレスに書き込みを 試みた場合、CPU が優先されます (DMA 書き込みは無視 )。この場合 DMAC エラートラップが 発生し、INTCON1 レジスタの DMAC エラートラップ ステータスビット (DMACERR) がセッ トされます。 6.2.1.4 一般ソフトトラップ 一般ソフトトラップは、INTCON3 レジスタのいずれかのビットがセットされた時に発生しま す。INTCON3 レジスタの各ビットは、それぞれ特定のトラップエラー条件に割り当てられて います。 6.2.1.4.1 USB アドレスエラー ソフトトラップ (UAE)

USB エンドポイントは全て RAM にバッファとして実装されています。バッファには、CPU と USB モジュールのどちらからもアクセスできます。 アプリケーションでは、エンドポイント バッファ 記述子テーブル (BDT) を使って、エンドポイ ント バッファとその他のデータの位置を指定します。エンドポイント BDT のサイズは 512 バイ トです。エンドポイント BDT は、各エンドポイントに対応するエントリ (「エンドポイント記述 子」と呼ぶ ) を格納します。エンドポイント バッファ用の空間は、エンドポイントが有効であっ ても無効であっても関係なく割り当てられます。 エンドポイント BDT の開始アドレスは、アプリケーションで指定します。この 32 ビットアド レスは UxBDTP1、UxBDTP2、UxBDTP3 レジスタで指定しますが、アドレスを 512 バイト境 界に配置する必要があります ( つまり、アドレスの下位 9 ビットは 0 である事が必要です )。

割り込み

UxBDTP1、UxBDTP2、UxBDTP3 レジスタが未実装メモリ領域またはバッファの任意の 512 バ イトを指すアドレスに初期化された場合、 USB モジュールは未実装メモリにアクセスする結果 となり、USB アドレスエラー ソフトトラップが発行されて UAE ビットがセットされます。詳 細はセクション 25.「USB On-The-Go (OTG)」(DS70175) を参照してください。

6.2.1.4.2 DMA アドレスエラー ソフトトラップ (DAE) ダイレクトメモリ アクセス (DMA) コントローラは、周辺モジュール用データレジスタとデー タ空間 SRAM 間でデータを転送します。DMA モジュールが未実装メモリアドレスにアクセス を試みると、DMA アドレスエラー ソフトトラップが発行され、DAE ビットがセットされます。 詳細はセクション 22.「ダイレクトメモリ アクセス (DMA)」(DS70348) を参照してください。 6.2.1.4.3 DO スタック オーバーフロー ソフトトラップ (DOOVR) ハードウェアでは、最大で 4 重の DO ループを実行およびネスト可能です。CORCON レジスタ の DO レベルビット (DL<2:0>) は、DO ループのネストの深さを示し、DO スタックを指定する ために使われます。これらのビットは、DO ループがネストされるたびに自動的に更新されま す。DO レベルが 0 (DL<2:0> = 000) の場合、DO ループはネストされていない (DO ステートを 保存する必要はない ) 事を意味します。DO レベルが 4 (DL<2:0> = 100) の場合、既に 4 つの DO ループがネストされて処理中である事を示します。 DOスタックが既にフル状態(すなわちDL<2:0> = 100: 既に4つのDOループが処理中)である時に ユーザがさらに DO ループのネストを試みた場合、DO スタック オーバーフロー ソフトトラッ プが発行されます (DOOVR = 1)。DO 命令の実行によってトラップが発生した場合、その命令 の実行前の DO ステートと DO スタックは変更されません。ユーザはフォルト条件の復元を試み るか、タスクを中止するか、デバイスを単純にリセットする事ができます。

6.2.2

ハードトラップ

ハードトラップは優先度 13 ~ 15 の例外を含みます。アドレスエラー ( 優先度 13) とオシレー タエラー ( 同 14) はハードトラップです。 ソフトトラップと同様に、ハードトラップもノンマスカブル割り込み要因です。ただしソフト トラップとは異なり、ハードトラップはトラップを引き起こした命令の実行後に、CPU のコー ド実行を強制的に停止します。正常なプログラム実行フローは、トラップが認識され処理され るまで再開されません。 6.2.2.1 ハードトラップの優先度と競合 トラップの処理中に、それよりも優先度の高いトラップが発生すると、処理中のトラップは割 り込まれ、高優先度のトラップが認識 / 処理されます。低優先度トラップは、高優先度トラッ プの処理が終了するまで保留されます。 どのようなタイプのコード実行であっても、発生した各ハードトラップが認識 / 処理されるま で、コード実行を再開する事はできません。あるハードトラップが保留中 / 認識済み / 実行中 のいずれかである時に、これよりも低い優先度のハードトラップが発生した場合、高優先度ト ラップの処理が完了するまで低優先度トラップを認識できないため、ハードトラップの競合が 発生します。 ハードトラップ競合条件では、デバイスが自動的にリセットされます。リセットが発生すると、 リセット制御レジスタ (RCON<15>) のトラップ リセットフラグ ステータスビット (TRAPR) が セットされるため、ソフトウェアでリセットの発生を検出できます。詳細はセクション 8.「リ セット」(DS70602) を参照してください。 6.2.2.2 オシレータ障害トラップ ( ハードトラップ、優先度 14) オシレータ障害トラップイベントは下記の条件により発生します。 • フェイルセーフ クロックモニタ (FSCM) が有効な時に、システムクロック源の喪失を検出し た場合 • PLL を使って動作中に PLL ロックの喪失を検出した場合 • FSCM が有効な状態でパワーオン リセット (POR) が発生した時に PLL がロックに失敗した 場合 オシレータ障害トラップイベントは、INTCON1 レジスタのオシレータ障害トラップ ステータス ビット (OSCFAIL) または OSCCON レジスタのクロック障害ステータスビット (CF) をポーリン グする事により、ソフトウェアで検出可能です。トラップ サービスルーチンへの再入を防ぐため6.2.2.3 アドレスエラー トラップ ( ハードトラップ、優先度 13) アドレスエラー トラップが発生する可能性のある動作条件には下記が含まれます。 • 不正な位置のデータワード フェッチを試みた場合 : このような条件は、奇数の実効アドレス ( 最下位ビット (LSb) が 「1」) を使ってワードアクセスを行う命令を実行した場合に発生し ます。dsPIC33E/PIC24E のワードアクセスでは、常に偶数アドレス境界位置を指定する必要 があります。 • ビット操作命令が、奇数の実効アドレス ( 最下位ビット (LSb) が「1」) で間接アドレッシン グ モードを使った場合 • 未実装のデータアドレス空間からデータフェッチを試みた場合

• BRA #literal 命令または GOTO #literal 命令の literal が未実装のプログラムメモリ アドレスであった場合 • dsr/dsw ページが 0 の時に、ページングによるアドレス指定でデータの読み出しまたは書き 込みを試みた場合 • PC が未実装のプログラムメモリ アドレスに変更された後に命令を実行した場合 : PC は、値 をスタックに書き込んだ後に RETURN 命令を実行する事により変更できます。 アドレスエラー トラップが発生すると、データの破損を防ぐために、データ空間への書き込み が禁止されます。 アドレスエラーは、ADDRERR ステータスビット (INTCON1<3>) をポーリングする事により、 ソフトウェアで検出できます。トラップ サービスルーチンへの再入を防ぐために、ADDRERR ステータスフラグをソフトウェアでクリアする必要があります。 6.2.2.4 一般ハードトラップ 一般ハードトラップは下記の条件で発生します。 • INTCON2 レジスタの SWTRAP ビットがセットされた場合 • INTCON4 レジスタのいずれかのビットがセットされた場合

6.2.3

割り込み命令の無効化

DISI ( 割り込み無効化 ) 命令は、最大 16384 命令サイクルの割り込みを無効にします。この命令 は、処理時間が重視されるコードセグメントを実行する際に便利です。 DISI命令は優先度1~6の割り込みを無効にします。優先度7の割り込みと全てのトラップイベ ントは、DISI 命令がアクティブであっても CPU に割り込む事ができます。DISI 命令は、CPU 内の割り込み無効化カウント (DISICNT) レジスタと連動します。DISICNT レ ジスタが「0」以外であれば、優先度 1 ~ 6 の割り込みが無効になります。DISICNT レジスタ は、命令サイクルごとに 1 つデクリメントします。DISICNT レジスタが「0」までデクリメン トすると、優先度 1 ~ 6 の割り込みが再び有効になります。DISI 命令がカウントするサイク ル数 ( 命令コードで指定するサイクル数 ) には、PSV アクセスや命令ストール等により発生す るサイクルも全て含まれます。 DISICNT レジスタは読み書き可能です。ユーザ アプリケーションで DISICNT レジスタをクリ アする事により、先に実行した DISI 命令の効果を早期に終了できます。あるいは、DISINCT レジスタに値を書き込むか加算する事により、割り込み無効にする期間を延長できます。 DISICNT レジスタが既にゼロである場合、ゼロ以外の値を書き込んで割り込みを無効にする事 はできません。割り込み無効化の初期開始には DISI 命令を実行する必要があります。DISI 命 令を実行してから DISICNT レジスタがゼロまでデクリメントするまでの間であれば、ユーザ アプリケーションで DISINCT レジスタの値を変更して割り込み無効化期間を延長できます。 DISI 命令の効果によって割り込みが無効になると、INTCON2レジスタのDISI命令ステータス ビット (DISI) がセットされます。 Note: MAC クラス命令では、データ空間がX 領域と Y 領域に分割されます。このような 命令では、全ての Y 領域も未実装 X 領域として扱われ、全ての X 領域も未実装 Y 領域として扱われます。

Note: ユーザが SWTRAP ビット (INTCON2<13>) を「1」にセットすると、SGHT ビッ ト (INTCON4<0>) が自動的に「1」にセットされ、これによりコード実行は一般 ハードトラップ ハンドラへ移行します。トラップハンドラ内では、トラップの再 入を防ぐために、SWTRAP および SGHT ビットの両方をクリアする (「0」に設 定する ) 必要があります。 Note: DISI 命令を使うと、ユーザ割り込み要因を簡単に無効にできます( ただし、それ らの要因中に CPU 優先度 7 の要因が含まれていない場合 )。

割り込み

6.2.3.1 グローバル割り込みイネーブル (GIE) ビット

グローバル割り込みイネーブルビット (GIE) を使うと、全ての割り込みを一括で有効または無 効にできます。GIE ビットをクリアした場合の割り込みコントローラの挙動は、CPU の IPL ビット (レジスタ 6-1参照 ) を 7 に設定した時と同様となり、トラップを除く全ての割り込み が無効になります。GIE ビットを再びセットすると割り込みコントローラは IPL 値に基づいて 動作し、システムは、以前の割り込み優先度ビットの設定に応じて、以前の動作ステートに戻 ります。

6.2.4

割り込み動作

各命令サイクルでは、全ての割り込みイベントフラグが監視されます。保留中の割り込み要求 (IRQ) は、IFSx レジスタのフラグビット = 1 で示されます。割り込みイネーブル (IECx) レジス タ内の対応するビットがセットされると、IRQ が割り込みを生成します。IRQ が検出された命 令サイクルの残りの期間中に、保留中の全ての IRQ の優先度が評価されます。CPU が IRQ に応答する際に、実行中の命令は中断されません。すなわち、IRQ が検出された 時に実行中であった命令が完了してから、割り込みサービスルーチン (ISR) が実行されます。 現在のプロセッサ優先度 (IPL<2:0> ステータスビット (SR<7:5>) よりも高いユーザ割り当て優 先度を持つ保留 IRQ が存在すると、プロセッサに対する割り込みが発生します。この場合プロ セッサは、下記の情報をソフトウェア スタックに保存します。 • 現在のプログラム カウンタ (PC) の値 • プロセッサ ステータス レジスタ (SRL) の下位バイト • IPL3 ステータスビット (CORCON<3>) • スタックフレーム アクティブ (CORCON<3>) これにより、戻り PC アドレス値、MCU ステータスビット、現在のプロセッサ優先度が自動的 に保存されます。 これらの情報をスタックに保存した後に、CPU はその保留割り込みの優先度を IPL<2:0> ビッ トに書き込みます。このような動作により、RETFIE 命令によって ISR が終了するまでの間、 その ISR の優先度以下の全ての割り込みを無効にします。 図 6-2: 割り込みイベントのスタック動作 6.2.4.1 割り込みからの復帰 RETFIE ( 割り込みからの復帰 ) 命令は、割り込みシーケンス開始前のプロセッサの状態と優先 度を復元するために、PC 戻りアドレス、IPL3 ステータスビット、SFA ビット、SRL レジスタ をアンスタックします。

Note 1: GIE ビットを変更しても CPU の IPL ビットは変更されません。

2: GIE ビットをクリアしてから割り込みが無効になるまでに 1 サイクルの遅延が生 じます。 <Free Word> PC<15:1>; PC<22:16> 0 15 W15 (before IRQ) W15 (after IRQ) S tack G rows T o war d Higher A d dress SR<7:0>

This stack stores the IPL3 status bit (CORCON<3>) This stack stores the SFA bit (CORCON<2>)

6.2.4.2 割り込みのネスティング 既定値状態では割り込みのネスティングが可能です。つまり、実行中の ISR よりも高いユーザ アプリケーション割り当て優先度を持つ割り込み要因は、その ISR に割り込む事ができます。 割り込みのネスティングは、INTCON1 レジスタの割り込みネスティング ディセーブル ビット (NSTDIS) をセットする事により無効にできます。NSTDIS 制御ビットをセットすると、 実行中 の割り込みは IPL<2:0> を常に 111 に設定します ( すなわち CPU 優先度を強制的に 7 に設定 )。 この操作は、RETFIE 命令によって実行中の ISR が終了するまでの間、他の割り込み要因をマ スクします。割り込みネスティングを無効にした場合、ユーザ アプリケーション割り当て割り 込み優先度は、保留割り込み間の競合を解消する以外の効果を持ちません。 また、IPL<2:0> ビット (SR<7:5>) は読み出し専用になります。これにより、ユーザ アプリケー ションが IPL<2:0> を 111 ( 優先度 7) より低い値に設定してしまう事 ( すなわち割り込みのネス ティングを実質的に有効にしてしまう事 ) を防ぎます。

6.2.5

スリープおよびアイドルからの復帰

IECx レジスタの対応する制御ビットで有効にされた割り込み要因は、いずれもプロセッサをス リープまたはアイドルモードから復帰させる事ができます。ある要因の割り込みステータスフ ラグがセットされ、かつ IEC 制御レジスタの対応するビットによってその割り込み要因が有効 にされている場合、復帰信号が dsPIC33E/PIC24E CPU へ送られます。デバイスがスリープま たはアイドルモードから復帰すると、次のいずれかの動作が発生します。 • その要因の割り込み優先度が現在の CPU 優先度よりも高い場合、プロセッサは割り込みを 処理します ( すなわち、その割り込み要因の ISR に分岐します )。 • その要因に対してユーザ アプリケーションが割り当てた割り込み優先度が現在の CPU 優先 度以下である場合、プロセッサは CPU をスリープまたはアイドルモードに移行させた PWRSAV 命令の直後の命令から動作を再開します。6.2.6

アナログ - デジタル コンバータ (ADC) の外部変換要求

INT0 外部割り込み要求ピンは、ADC 向けの外部変換要求信号ピンとしても使います。INT0 割 り込み要因と同様に、ADC 外部変換要求でもエッジ極性を選択できます。

6.2.7

外部割り込みサポート

dsPIC33E/PIC24E は最大 5 つの外部割り込みピン要因 (INT0 ~ INT4) をサポートします。各 外部割り込みピンは、割り込みイベント検出用のエッジ検出回路を備えます。INTCON2 レジ スタは、各エッジ検出回路の極性を選択するための 5 つの制御ビット (INT0EP ~ INT4EP) を 備えます。これらのビットにより、各外部割り込みピンの極性 ( 立ち上がり / 立ち下がりのど ちらのエッジで CPU に割り込むか ) を個別に設定できます。詳細はレジスタ 6-4を参照してく ださい。 Note: CPU 優先度 0 を割り当てられたユーザ割り込み要因は、実質的に無効であるため、 スリープまたはアイドルモードから CPU を復帰させる事はできません。割り込み を復帰要因として使うには、その割り込みの CPU 優先度をプログラムで 1 以上に 設定する必要があります。

割り込み

6.3

割り込み処理タイミング

6.3.1

1 サイクル命令に対する割り込みレイテンシ

図 6-3に、1 サイクル命令の実行中に周辺モジュール割り込みが要求された場合のイベント シー ケンスを示します。割り込み処理には 10 命令サイクルを要します。図の各割り込み処理サイ クルには参照番号 ( 丸囲み番号 ) を表記しています。 命令サイクル中に周辺モジュール割り込みが発生すると、割り込みフラグ ステータスビットが セットされます。実行中の命令はこの命令サイクル内で完了します。割り込み発生後の次の命 令サイクル②では、PC と下位バイトステータス (SRL) レジスタの内容をテンポラリ バッファ レジスタに保存します。この命令サイクル②では、2 サイクル命令への割り込みシーケンスと の整合性を維持するために、NOP を実行します (6.3.2 「2 サイクル命令に対する割り込みレイテ ンシ」参照 )。命令サイクル③では、割り込み要因のベクタテーブル アドレスを PC に書き込 み、ISR の開始アドレスをフェッチします。命令サイクル④では、ISR アドレスを PC に書き 込みます。このサイクルは NOP として実行し、この間に ISR 内の先頭命令をフェッチします。 図 6-3: 1 サイクル命令実行中に割り込みが発生した場合のタイミング 11 FNOP 1 2 3 4 5 6 7 8 9 10INST INST FNOP FNOP Fetch Vector

FNOP FNOP FNOP FNOP ISR FNOP PC PC + 2 Vector # ISR 4 6 6 6 6 6 CPU Priority Interrupt Flag Status bit INST Executed 4 4 12 13 6 ISR 14 6

PUSH Low 16 bits of PC

PUSH SRL and High 8 bits of PC Save PC in

Peripheral interrupt event occurs at or before midpoint

temporary buffer of this cycle

(from temporary buffer) (from temporary buffer)

(PC - 2) 4 4 4 4 Fetch (PC) CPU IRQ

6.3.2

2 サイクル命令に対する割り込みレイテンシ

2 サイクル命令実行中の割り込みレイテンシは、1 サイクル命令の場合と同じです。割り込み 処理のサイクル①と②により、2 サイクル命令の動作を完了する事ができます。図 6-4は、2 サ イクル命令実行前のサイクル中に周辺モジュール割り込みイベントが発生した場合のタイミン グ図です。 図 6-5は、2 サイクル命令の第 1 サイクル実行中に周辺モジュール割り込みイベントが発生し た場合のタイミング図です。この場合の割り込み処理は 1 サイクル命令の場合 (6.3.1 「1 サイク ル命令に対する割り込みレイテンシ」参照 ) と同じです。 図 6-4: 2 サイクル命令実行前のサイクル中に割り込みが発生した場合のタイミング 図 6-5: 2 サイクル命令の第 1 サイクル実行中に割り込みが発生した場合のタイミング 11 FNOP 1 2 3 4 5 6 7 8 9 10 FNOP FNOP Fetch VectorFNOP FNOP FNOP ISR FNOP PC PC + 2 Vector # ISR 4 6 6 6 6 6 CPU Priority Interrupt Flag Status bit INST Executed 4 4 12 13 6 ISR 14 6

PUSH Low 16 bits of PC

PUSH SRL and High 8 bits of PC Save PC in

Peripheral interrupt event occurs at or before midpoint

temporary buffer of this cycle

(from temporary buffer) (from temporary buffer)

4 4 4 4 Fetch INST 1st Cycle INST 2nd Cycle INST (PC - 2) CPU IRQ 11 FNOP 1 2 3 4 5 6 7 8 9 10 FNOP FNOP Fetch Vector

FNOP FNOP FNOP ISR FNOP PC PC + 2 Vector # ISR 4 6 6 6 6 6 CPU Priority Interrupt Flag Status bit INST Executed 4 4 12 13 6 ISR 14 6

PUSH Low 16 bits of PC

PUSH SRL and High 8 bits of PC Save PC in

Peripheral interrupt event occurs at or before midpoint

temporary buffer of this cycle

(from temporary buffer) (from temporary buffer)

4 4 4 4 Fetch INST 1st INST 2nd Cycle INST (PC-2) ISR + 2 Cycle CPU IRQ

割り込み

6.3.3

割り込みからの復帰

割り込みから戻るには、プログラムで RETFIE 命令を呼び出す必要があります。 RETFIE 命令のサイクル①および②では、PC と SRL レジスタの内容をスタックからポップしま す。サイクル③では、更新されたプログラム カウンタが指すアドレスの命令をフェッチしま す。このサイクルは NOP 命令として実行します。サイクル④では、割り込み発生位置からプロ グラム実行を再開します。 図 6-6: 割り込みからの復帰6.3.4

例外レイテンシ

割り込みレイテンシは、固定レイテンシまたは可変レイテンシとして選択できます。例外プロ セスは、これら 2 つのモードのいずれかで実行できます。このモードは、コア制御レジスタの VAR ビット (CORCON<15>) の状態によって決まります。 6.3.4.1 固定レイテンシ (VAR = 0 かつ CPU が最優先マスタ )VAR = 0 ( 既定値のリセット状態 ) かつ CPU が最高優先度の EDS バスマスタ (MSTRPR<2:0> = 000) である場合、CPU は優先度の高い例外に対しても常に固定レイテンシ応答を提供しま す。割り込みレイテンシとは、割り込みが認識されてから ISR の先頭命令が実行されるまでの 遅延時間を意味します。固定レイテンシモードでは、TBLRDx 命令や PSV アクセスを要求する 命令を含む全ての命令に対して、割り込みレイテンシは一定となります。 ただし下記の状況では、割り込みレイテンシが変化します。 • PSV を介してデータにアクセスする MOV.D 命令では、次の PSV フェッチを完了するために 1 サイクルが追加されます。 • ストールサイクルに関連する TBLRDx または PSV アクセス命令では、1 サイクルが追加され ます。 • PSV アクセスの繰り返し実行では、最後の繰り返しで 1 サイクルが追加されます。 6.3.4.2 可変レイテンシ (VAR = 1 かつ CPU が最優先マスタ )

VAR = 1 かつ CPU が最高優先度の EDS バスマスタ (MSTRPR<2:0> = 000) である場合、CPU は全ての例外に対して可変レイテンシを提供します。複数の割り込みを有効にしてデバイスを ネスト無効モードで動作させる場合、割り込みの処理中に、それよりも高い優先度を持つ割り 込み要求が発生する可能性があります。従って、最も長い ISR を実行するのに必要な時間を最 大レイテンシに追加する必要があります。 VAR = 0 の場合、例外処理には 13 命令サイクルのフラッシュアクセス時間 (60 MHz の動作速 度で 216 ns) が必要です。 VAR = 1 の場合、例外処理時間は一定ではなく、9 ~ 13 命令サイクルのフラッシュアクセス時 間 (60 MHz の動作速度で 150 ~ 216 ns) が必要です。 4 4 4 4 6 4 CPU Priority RETFIE RETFIE INST Executed FNOP ISR last 6 ISR ISR + 2 PC 2nd Cycle TCY instruction 1 2 3 4 5 FNOP FNOP PC 6 4 PC 7 FNOP

6.3.5

割り込みレイテンシに関する特殊条件

dsPIC33E/PIC24E では、発生した周辺モジュール割り込み要因を保留して、 実行中の命令を完 了させる事ができます。1 サイクル命令と 2 サイクル命令のいずれも割り込みレイテンシは同 じです。ただし、割り込みの発生タイミングによっては、割り込みレイテンシが 1 サイクル増 える場合があります。アプリケーションがこのようなレイテンシの変化を受け付けない場合、 下記の動作を避ける必要があります。 • PSV を使ってプログラムメモリ空間内の値にアクセスする MOV.D 命令の実行 • 2 サイクル命令に対する命令ストールサイクルの追加 • PSV アクセスを行う 1 サイクル命令に対する命令ストールサイクルの追加 • PSVを使ってプログラムメモリ空間内の値にアクセスするビットテストおよびスキップ命令 (BTSC、BTSS)割り込み

6.4

割り込み制御 / ステータス レジスタ

割り込みコントローラには下記のレジスタが割り当てられています。 • INTCONx: 割り込み制御レジスタ (レジスタ 6-3~レジスタ 6-6) これらのレジスタは、グローバルな割り込み機能を制御します。以下のレジスタ名内の「x」 はレジスタ番号を表します。 - INTCON1: 割り込み制御レジスタ 1 は、割り込みネスティング ディセーブル ビット (NSTDIS) と、プロセッサ トラップ要因の制御フラグとステータスフラグを格納します。 - INTCON2: 割り込み制御レジスタ 2は、外部割り込み要求信号の挙動と代替ベクタテーブ ルの使用を制御します。 - INTCON3: 割り込み制御レジスタ 3は、ソフトトラップ ステータスビットを制御します。 - INTCON4: 割り込み制御レジスタ 4は、ソフトウェアが生成するハードトラップのステー タスビットを制御します。 • IFSx: 割り込みフラグステータス レジスタ 全ての割り込み要求フラグは IFSx レジスタに格納されます (「x」はレジスタ番号 )。各割 り込み要因にはステータスビットが割り当てられています。これらのステータスビットは、 対応する周辺モジュールまたは外部信号によりセットされ、ソフトウェアでクリアします。 • IECx: 割り込みイネーブル制御レジスタ 全ての割り込みイネーブル制御ビットは IECx レジスタに格納されます (「x」はレジスタ 番号 )。これらの制御ビットを使って、周辺モジュールまたは外部信号からの割り込みを 個別に有効にできます。 • IPCx: 割り込み優先度制御レジスタ 各ユーザ割り込み要因には 7 段階の優先度を割り当てる事ができます。IPC レジスタは、 各割り込み要因の優先度を個別に設定します。 • INTTREG: 割り込み制御 / ステータス レジスタ このレジスタは、対応する割り込みベクタ番号と新しい CPU 割り込み優先度を格納しま す。これらはベクタ番号 (VECNUM<7:0>) および割り込みレベル (ILR<3:0>) ビットフィー ルドにラッチされます。新しい割り込み優先度とは、保留中割り込みの優先度です。 • SR: ステータス レジスタ SR そのものは割り込みコントローラ ハードウェアの一部ではありませんが、現在の CPU 優先度を示す IPL<2:0> ステータスビット (SR<7:5>) を格納しています。ユーザ アプリケー ションでこの IPL ビットに書き込む事により、現在の CPU 優先度を変更できます。 • CORCON: コア制御レジスタ CORCON レジスタそのものは割り込みコントローラ ハードウェアの一部ではありません が、現在の CPU 優先度を示す IPL3 ステータスビットを格納しています。IPL3 は読み出し 専用ビットであるため、ユーザ アプリケーションでトラップイベントをマスクする事はで きません。この後に各レジスタの詳細な説明を記載しています。

Note: 割り込み要因の総数とタイプはデバイスごとに異なります。詳細は各デバイスの データシートを参照してください。

レジスタ 6-1: SR: ステータス レジスタ R-0 R-0 R/C-0 R/C-0 R-0 R/C-0 R-0 R-0 OA OB SA SB OAB SAB DA DC bit 15 bit 8 R/W-0 R/W-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 IPL<2:0>(1,2) RA N OV Z C bit 7 bit 0 凡例 : C = クリア可能ビット R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15-8 割り込みコントローラには使用せず SR ビットについてはセクション 2.「CPU」(DS70359) 参照 ) bit 7-5 IPL<2:0>: CPU 割り込み優先度ステータスビット(1,2)

111 = CPU 割り込み優先度は 7 (15)、ユーザ割り込みは無効 110 = CPU 割り込み優先度は 6 (14) 101 = CPU 割り込み優先度は 5 (13) 100 = CPU 割り込み優先度は 4 (12) 011 = CPU 割り込み優先度は 3 (11) 010 = CPU 割り込み優先度は 2 (10) 001 = CPU 割り込み優先度は 1 (9) 000 = CPU 割り込み優先度は 0 (8) bit 4-0 割り込みコントローラには使用せず (SR ビットについてはセクション 2.「CPU」(DS70359) 参照 )

Note 1: IPL<2:0> ビットは IPL<3> ビット (CORCON<3>) と連結して CPU 割り込み優先度を形成します。カッコ 内の値は IPL<3> = 1 の場合の値です。

割り込み

レジスタ 6-2: CORCON: コア制御レジスタ

R/W-0 U-0 R/W-0 R/W-0 R/W-0 R-0 R-0 R-0 VAR — US<1:0> EDT DL<2:0>

bit 15 bit 8

R/W-0 R/W-0 R/W-1 R/W-0 R/C-0 R-0 R/W-0 R/W-0 SATA SATB SATDW ACCSAT IPL3(1) SFA RND IF

bit 7 bit 0 凡例 : C = クリア可能ビット R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15 VAR: 例外処理可変レイテンシ制御ビット 1 = 例外処理レイテンシを可変にする 0 = 例外処理レイテンシを固定にする ( 詳細は6.3.4 「例外レイテンシ」参照 ) bit 14-4 割り込みコントローラには使用せず (CORCON ビットについてはセクション 2.「CPU」(DS70359) 参照 ) bit 3 IPL3: CPU 割り込み優先度ステータスビット 3(1)

1 = CPU 優先度は 8 以上 0 = CPU 優先度は 7 以下

bit 2-0 割り込みコントローラには使用せず

(CORCON ビットについてはセクション 2.「CPU」(DS70359) 参照 )

レジスタ 6-3: INTCON1: 割り込み制御レジスタ 1

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 NSTDIS OVAERR OVBERR COVAERR COVBERR OVATE OVBTE COVTE

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 U-0 SFTACERR DIV0ERR DMACERR MATHERR ADDRERR STKERR OSCFAIL —

bit 7 bit 0 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15 NSTDIS: 割り込みネスティング ディセーブル ビット 1 = 割り込みネスティングを無効にする 0 = 割り込みネスティングを有効にする bit 14 OVAERR: アキュムレータ A オーバーフロー トラップフラグ ビット 1 = アキュムレータ A のオーバーフローによるトラップが発生した 0 = アキュムレータ A のオーバーフローによるトラップは発生していない bit 13 OVBERR: アキュムレータ B オーバーフロー トラップフラグ ビット 1 = アキュムレータ B のオーバーフローによるトラップが発生した 0 = アキュムレータ B のオーバーフローによるトラップは発生していない bit 12 COVAERR: アキュムレータ A 致命的オーバーフロー トラップフラグ ビット 1 = アキュムレータ A の致命的オーバーフローによるトラップが発生した 0 = アキュムレータ A の致命的オーバーフローによるトラップは発生していない bit 11 COVBERR: アキュムレータ B 致命的オーバーフロー トラップフラグ ビット 1 = アキュムレータ B の致命的オーバーフローによるトラップが発生した 0 = アキュムレータ B の致命的オーバーフローによるトラップは発生していない bit 10 OVATE: アキュムレータ A オーバーフロー トラップ イネーブルビット 1 = アキュムレータ A のオーバーフロー トラップを有効にする 0 = このトラップを無効にする bit 9 OVBTE: アキュムレータ B オーバーフロー トラップ イネーブルビット 1 = アキュムレータ B のオーバーフロー トラップを有効にする 0 = このトラップを無効にする bit 8 COVTE: 致命的オーバーフロー トラップイネーブルビット 1 = アキュムレータ A または B の致命的オーバーフロー トラップを有効にする 0 = このトラップを無効にする bit 7 SFTACERR: アキュムレータ シフトエラー ステータスビット 1 = 無効なアキュムレータ シフトによる算術エラートラップが発生した 0 = 無効なアキュムレータ シフトによる算術エラートラップは発生していない bit 6 DIV0ERR: ゼロ除算エラー ステータスビット 1 = ゼロ除算によるエラートラップが発生した 0 = ゼロ除算によるエラートラップは発生していない bit 5 DMACERR: DAMC エラートラップ ステータスビット

1 = DMAC トラップが発生した 0 = DMAC トラップは発生していない bit 4 MATHERR: 算術エラー ステータスビット 1 = 算術エラートラップが発生した 0 = 算術エラートラップは発生していない bit 3 ADDRERR: アドレスエラー トラップ ステータスビット 1 = アドレスエラー トラップが発生した 0 = アドレスエラー トラップは発生していない

割り込み

bit 2 STKERR: スタックエラー トラップ ステータスビット 1 = スタックエラー トラップが発生した 0 = スタックエラー トラップは発生していない bit 1 OSCFAIL: オシレータ障害トラップ ステータスビット 1 = オシレータ障害トラップが発生した 0 = オシレータ障害トラップは発生していない bit 0 未実装 :「0」として読み出し レジスタ 6-3: INTCON1: 割り込み制御レジスタ 1 ( 続き )レジスタ 6-4: INTCON2: 割り込み制御レジスタ 2

R/W-1 R/W-0 R/W-0 U-0 U-0 U-0 U-0 U-0

GIE DISI SWTRAP — — — — —

bit 15 bit 8

U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 — — — INT4EP INT3EP INT2EP INT1EP INT0EP

bit 7 bit 0 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15 GIE: グローバル割り込みイネーブルビット 1 = 割り込みと対応する IE ビットを有効にする 0 = 割り込みを無効にする ( トラップは有効なまま ) bit 14 DISI: DISI 命令ステータスビット

1 = DISI 命令はアクティブ 0 = DISI 命令は非アクティブ bit 13 SWTRAP: ソフトウェア トラップ ステータスビット 1 = ソフトウェア トラップを有効にする 0 = ソフトウェア トラップを無効にする bit 12-5 未実装 : 「0」として読み出し bit 4 INT4EP: 外部割り込み 4 エッジ検出極性選択ビット 1 = 立ち下がりエッジで割り込む 0 = 立ち上がりエッジで割り込む bit 3 INT3EP: 外部割り込み 3 エッジ検出極性選択ビット 1 = 立ち下がりエッジで割り込む 0 = 立ち上がりエッジで割り込む bit 2 INT2EP: 外部割り込み 2 エッジ検出極性選択ビット 1 = 立ち下がりエッジで割り込む 0 = 立ち上がりエッジで割り込む bit 1 INT1EP: 外部割り込み 1 エッジ検出極性選択ビット 1 = 立ち下がりエッジで割り込む 0 = 立ち上がりエッジで割り込む bit 0 INT0EP: 外部割り込み 0 エッジ検出極性選択ビット 1 = 立ち下がりエッジで割り込む 0 = 立ち上がりエッジで割り込む

割り込み

レジスタ 6-5: INTCON3: 割り込み制御レジスタ 3

U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

bit 15 bit 8

U-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 U-0

— UAE DAE DOOVR — — — —

bit 7 bit 0

凡例 :

R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知

bit 15-7 未実装 : 「0」として読み出し

bit 6 UAE: USB アドレスエラー ソフトトラップ ステータスビット 1 = USB アドレスエラー ( ソフト ) トラップが発生した 0 = USB アドレスエラー ( ソフト ) トラップは発生していない bit 5 DAE: DMA アドレスエラー ソフトトラップ ステータスビット

1 = DAM アドレスエラー ソフトトラップが発生した 0 = DMA アドレスエラー ソフトトラップは発生していない bit 4 DOOVR: Do スタック オーバーフロー ソフトトラップ ステータスビット 1 = Do スタック オーバーフロー ソフトトラップが発生した 0 = Do スタック オーバーフロー ソフトトラップは発生していない bit 3-0 未実装 :「0」として読み出し レジスタ 6-6: INTCON4: 割り込み制御レジスタ 4

U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

bit 15 bit 8

U-0 U-0 U-0 U-0 U-0 U-0 U-0 R/W-0

— — — — — — — SGHT bit 7 bit 0 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15-1 未実装 :「0」として読み出し bit 0 SGHT: ソフトウェア生成ハードトラップ ステータスビット 1 = ソフトウェアが生成したハードトラップが発生した

レジスタ 6-7: IFSx: 割り込みフラグステータス レジスタ

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 IFS15 IFS14 IFS13 IFS12 IFS11 IFS10 IFS9 IFS8

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 IFS7 IFS6 IFS5 IFS4 IFS3 IFS2 IFS1 IFS0

bit 7 bit 0 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15-0 IFS15:IFS0: 割り込みフラグ ステータスビット 1 = 割り込み要求が発生した 0 = 割り込み要求は発生していない Note: ここには IFSx レジスタの一般的な定義しか記載していません。詳細は各デバイス データシートの「割り 込み」を参照してください。 レジスタ 6-8: IECx: 割り込みイネーブル制御レジスタ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 IEC15 IEC14 IEC13 IEC12 IEC11 IEC10 IEC9 IEC8

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 IEC7 IEC6 IEC5 IEC4 IEC3 IEC2 IEC1 IEC0

bit 7 bit 0 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15 IEC15:IEC0: 割り込みイネーブル制御ビット 1 = 割り込み要求を有効にする 0 = 割り込み要求を無効にする Note: ここには IECx レジスタの一般的な定義しか記載していません。詳細は各デバイス データシートの「割り 込み」を参照してください。

割り込み

レジスタ 6-9: IPCx: 割り込み優先度制御レジスタ U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 — IP3<2:0> — IP2<2:0> bit 15 bit 8 U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 — IP1<2:0> — 10, 2, 0 bit 7 bit 0 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15 未実装 :「0」として読み出し bit 14-12 IP3<2:0>: 割り込み優先度ビット 111 = 割り込み優先度 7 ( 最優先割り込み ) • • • 001 = 割り込み優先度 1 000 = 割り込み要因は無効 bit 11 未実装 :「0」として読み出し bit 10-8 IP2<2:0>: 割り込み優先度ビット これらのビットの定義は bit 14-12 と同じです。 bit 7 未実装 :「0」として読み出し bit 6-4 IP1<2:0>: 割り込み優先度ビット これらのビットの定義は bit 14-12 と同じです。 bit 3 未実装 :「0」として読み出し bit 2-0 IP0<2:0>: 割り込み優先度ビット これらのビットの定義は bit 14-12 と同じです。 Note: ここには IPCx レジスタの一般的な定義しか記載していません。詳細は各デバイス データシートの「割り 込み」を参照してください。レジスタ 6-10: INTTREG: 割り込み制御 / ステータス レジスタ

U-0 U-0 U-0 U-0 R-0 R-0 R-0 R-0

— — — — ILR<3:0> bit 15 bit 8 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 VECNUM<7:0> bit 7 bit 0 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 15-12 未実装 :「0」として読み出し

bit 11-8 ILR<3:0>: 新規 CPU 割り込み優先度ビット 1111 = CPU 割り込み優先度は 15 • • • 0001 = CPU 割り込み優先度は 1 0000 = CPU 割り込み優先度は 0 bit 7-0 VECNUM<7:0>: 保留中割り込みベクタ番号ビット 11111111 = 保留中の割り込みベクタ番号は 263 • • • 00000001 = 保留中の割り込みベクタ番号は 9 00000000 = 保留中の割り込みベクタ番号は 8

割り込み

6.5

割り込みのセットアップ手順

6.5.1

初期化

割り込み要因の設定手順は下記の通りです。 1. 割り込みをネストしない場合、NSTDIS 制御ビット (INTCON1<15>) をセットします。 2. 割り込み要因のユーザ アプリケーション割り当て優先度を選択します ( 対応する IPCx 制御 レジスタの制御ビットに書き込む )。優先度はアプリケーションと割り込み要因のタイプに よって決まります。複数の優先度を設定する必要がない場合、全ての有効割り込み要因の IPCx レジスタ制御ビットをゼロ以外の同じ値に設定できます。 3. 適切な IFSx ステータス レジスタで、その周辺モジュールに対応する割り込みフラグ ステー タスビットをクリアします。 4. 適切な IECx 制御レジスタで、その割り込み要因に対応する割り込みイネーブル制御ビット をセットして有効にします。6.5.2

割り込みサービスルーチン

ISR を宣言して IVT を適正なベクタアドレスに初期化する方法は、プログラミング言語 (C ま たはアセンブリ ) と、アプリケーションの開発に使う言語 - 開発ツールによって異なります。 一般的にユーザ アプリケーションは、ISR で処理する割り込み要因の割り込みフラグを、対応 する IFSx レジスタ内でクリアする必要があります。これをクリアしないと、アプリケーショ ンは ISR ルーチン終了後即座にまた同じ ISR ルーチンに再入します。ISR をアセンブリ言語で コーディングする場合、保存した PC 値、SRL 値、以前の CPU 優先度をアンスタックするた めに、RETFIE 命令を使って ISR を終了する必要があります。6.5.3

トラップサービスルーチン

TSR も ISR と同様にコーディングできますが、TSR への再入を防ぐために、INTCON1 レジス タで適切なトラップ ステータスフラグをクリアする必要があります。6.5.4

割り込みの無効化

INTCON2 レジスタの GIE ビットをセットするとユーザ割り込みが有効になります。このビッ トをクリアすると、割り込みは無効になります。 DISI 命令を使うと、優先度 1 ~ 6 の割り込みを簡単に一定時間無効にできます。DISI 命令は優 先度 7 の割り込み要因を無効にしません。 Note: デバイスリセットが発生すると、IPC レジスタが初期化され、全てのユーザ割り 込み要因は優先度 4 に設定されます。 Note: この場合、優先度 7 以下のユーザ割り込みだけを無効化にできます。トラップ要 因 ( 優先度 8 ~ 15) を無効にはできません。6.5.5

サンプルコード

例 6-1のサンプルコードは、割り込みのネスティングを有効にして Timer1/Timer2/Timer3/ 入力 状態変化通知割り込みをそれぞれ優先度 2/5/6/4 に設定する方法と、ステータス レジスタを使っ て割り込みを有効 / 無効にする方法を示しています。各 ISR には割り込みフラグをクリアする コードも示しています。 例 6-1: 割り込みセットアップのサンプルコード void enableInterrupts(void) {/* Enable level 1-7 interrupts */

/* No restoring of previous CPU IPL state performed here */ INTCON2bits.GIE = 1;

return; }

void disableInterrupts(void) {

/* Disable level 1-7 interrupts */

/* No saving of current CPU IPL setting performed here */ INTCON2bits.GIE = 0;

return; }

void initInterrupts(void) {

/* Interrupt nesting enabled here */ INTCON1bits.NSTDIS = 0;

/* Set Timer3 interrupt priority to 6 (level 7 is highest) */ IPC2bits.T3IP = 6;

/* Set Timer2 interrupt priority to 5 */ IPC1bits.T2IP = 5;

/* Set Change Notice interrupt priority to 4 */ IPC4bits.CNIP = 4;

/* Set Timer4 interrupt priority to 3 */ IPC6bits.T4IP = 3;

/* Set Timer1 interrupt priority to 2 */ IPC0bits.T1IP = 2;

/* Reset Timer1 interrupt flag */ IFS0bits.T1IF = 0;

/* Reset Timer2 interrupt flag */ IFS0bits.T2IF = 0;

/* Reset Timer3 interrupt flag */ IFS0bits.T3IF = 0;

/* Reset Timer4 interrupt flag */ IFS1bits.T4IF = 0;

/* Enable CN interrupts */ IEC1bits.CNIE = 1;

割り込み

例 6-1: 割り込みセットアップのサンプルコード ( 続き ) /* Enable Timer1 interrupt */

IEC0bits.T1IE = 1;

/* Enable Timer2 interrupt (PWM time base) */ IEC0bits.T2IE = 1;

/* Enable Timer3 interrupt */ IEC0bits.T3IE = 1;

/* Enable Timer4 interrupt (replacement for Timer2 */ IEC1bits.T4IE = 1;

/* Reset change notice interrupt flag */ IFS1bits.CNIF = 0;

return; }

void __attribute__((__interrupt__,no_auto_psv)) _T1Interrupt(void) {

/* Insert ISR Code Here*/ /* Clear Timer1 interrupt */ IFS0bits.T1IF = 0;

}

void __attribute__((__interrupt__,no_auto_psv)) _T2Interrupt(void) {

/* Insert ISR Code Here*/ /* Clear Timer2 interrupt */ IFS0bits.T2IF = 0;

}

void __attribute__((__interrupt__,no_auto_psv)) _T3Interrupt(void) {

/* Insert ISR Code Here*/ /* Clear Timer3 interrupt */ IFS0bits.T3IF = 0;

}

void __attribute__((__interrupt__,no_auto_psv)) _T4Interrupt(void) {

/* Insert ISR Code Here*/ /* Clear Timer4 interrupt */ IFS1bits.T4IF = 0;

}

void __attribute__((__interrupt__,no_auto_psv)) _CNInterrupt(void) {

/* Insert ISR Code Here*/ /* Clear CN interrupt */ IFS1bits.CNIF = 0; }

ファミリ

リファレンス

マニュアル

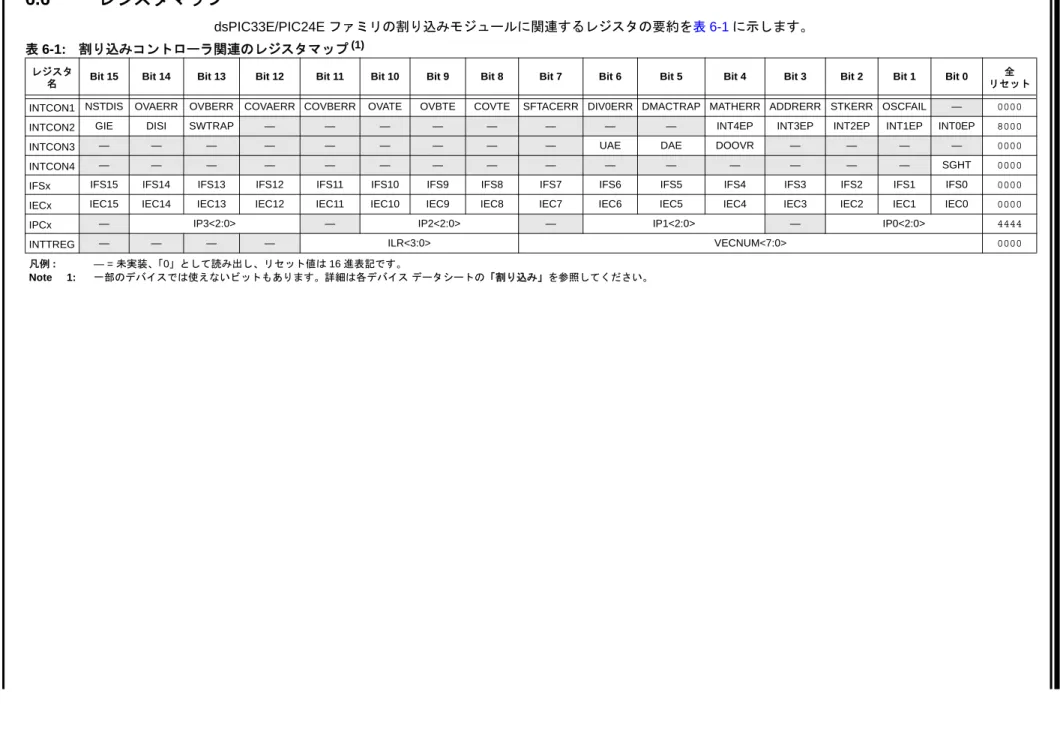

_JP p. 6-28 © 2012 Microchip T echnolo gy Inc. dsPIC33E/PIC24E ファミリの割り込みモジュールに関連するレジスタの要約を表 6-1に示します。 表 6-1: 割り込みコントローラ関連のレジスタマップ(1) レジスタ名 Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 全 リセット

INTCON1 NSTDIS OVAERR OVBERR COVAERR COVBERR OVATE OVBTE COVTE SFTACERR DIV0ERR DMACTRAP MATHERR ADDRERR STKERR OSCFAIL — 0000 INTCON2 GIE DISI SWTRAP — — — — — — — — INT4EP INT3EP INT2EP INT1EP INT0EP 8000 INTCON3 — — — — — — — — — UAE DAE DOOVR — — — — 0000 INTCON4 — — — — — — — — — — — — — — — SGHT 0000 IFSx IFS15 IFS14 IFS13 IFS12 IFS11 IFS10 IFS9 IFS8 IFS7 IFS6 IFS5 IFS4 IFS3 IFS2 IFS1 IFS0 0000 IECx IEC15 IEC14 IEC13 IEC12 IEC11 IEC10 IEC9 IEC8 IEC7 IEC6 IEC5 IEC4 IEC3 IEC2 IEC1 IEC0 0000 IPCx — IP3<2:0> — IP2<2:0> — IP1<2:0> — IP0<2:0> 4444 INTTREG — — — — ILR<3:0> VECNUM<7:0> 0000 凡例 : — = 未実装、「0」として読み出し、リセット値は 16 進表記です。