23

シリアル

ペリフェラル

インターフェイス

(S

PI

)

セクション 23. シリアル ペリフェラル インターフェイス (SPI)

ハイライト

本セクションには下記の主要項目を記載しています。 23.1 はじめに ... 23-2 23.2 ステータス / 制御レジスタ ... 23-7 23.3 動作モード ... 23-16 23.4 オーディオ プロトコル インターフェイス モード ... 23-30 23.5 割り込み ... 23-50 23.6 省電力およびデバッグモード中の動作 ... 23-53 23.7 各種リセットの影響 ... 23-54 23.8 SPI モジュールを使う周辺モジュール ... 23-54 23.9 関連アプリケーション ノート ... 23-55 23.10 改訂履歴 ... 23-5623.1

はじめに

シリアル ペリフェラル インターフェイス (SPI) モジュールは、外部の周辺モジュールまたは他 のマイクロコントローラ デバイスとの通信に便利に使える同期シリアル インターフェイスで す。SPI を使って通信可能な周辺デバイスには EEPROM、シフトレジスタ、ディスプレイ ド ライバ、アナログ / デジタル コンバータ (ADC)、オーディオ コーデック等があります。PIC32 ファミリの SPI モジュールは Motorola® SPI および SIOP インターフェイスとの互換性を持ち

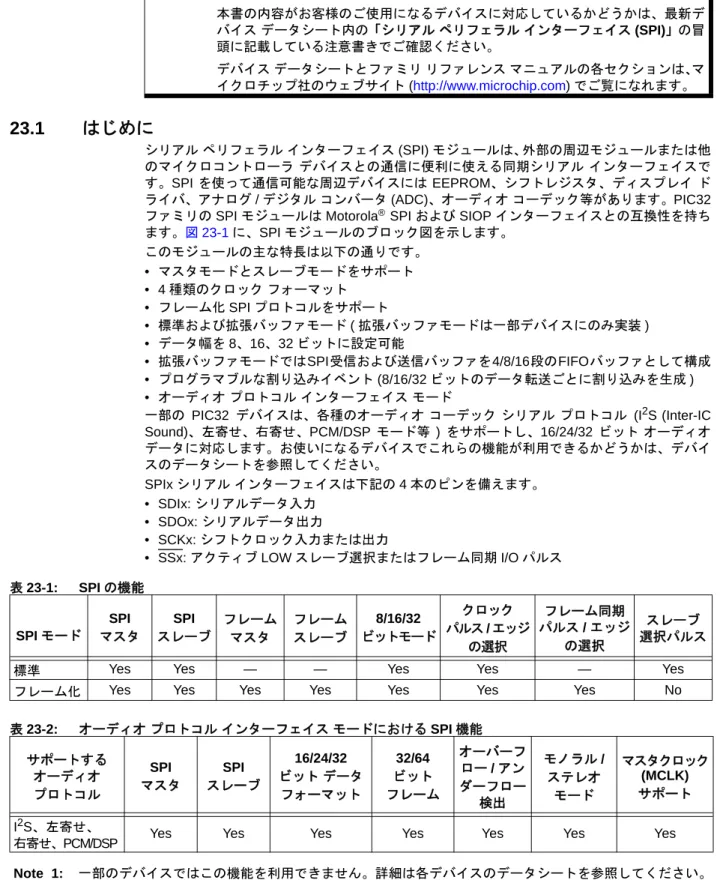

ます。図 23-1に、SPI モジュールのブロック図を示します。 このモジュールの主な特長は以下の通りです。 • マスタモードとスレーブモードをサポート • 4 種類のクロック フォーマット • フレーム化 SPI プロトコルをサポート • 標準および拡張バッファモード ( 拡張バッファモードは一部デバイスにのみ実装 ) • データ幅を 8、16、32 ビットに設定可能 • 拡張バッファモードではSPI受信および送信バッファを4/8/16段のFIFOバッファとして構成 • プログラマブルな割り込みイベント (8/16/32 ビットのデータ転送ごとに割り込みを生成 ) • オーディオ プロトコル インターフェイス モード 一部の PIC32 デバイスは、各種のオーディオ コーデック シリアル プロトコル (I2S (Inter-IC Sound)、左寄せ、右寄せ、PCM/DSP モード等 ) をサポートし、16/24/32 ビット オーディオ データに対応します。お使いになるデバイスでこれらの機能が利用できるかどうかは、デバイ スのデータシートを参照してください。 SPIx シリアル インターフェイスは下記の 4 本のピンを備えます。 • SDIx: シリアルデータ入力 • SDOx: シリアルデータ出力 • SCKx: シフトクロック入力または出力 • SSx: アクティブ LOW スレーブ選択またはフレーム同期 I/O パルス Note: ファミリ リファレンス マニュアルの本セクションは、デバイス データシートの 補足を目的としています。本書の内容は PIC32 ファミリの一部のデバイスには対 応していません。 本書の内容がお客様のご使用になるデバイスに対応しているかどうかは、最新デ バイス データシート内の「シリアル ペリフェラル インターフェイス (SPI)」の冒 頭に記載している注意書きでご確認ください。 デバイス データシートとファミリ リファレンス マニュアルの各セクションは、マ イクロチップ社のウェブサイト (http://www.microchip.com) でご覧になれます。 表 23-1: SPI の機能 SPI モード SPI マスタ SPI スレーブ フレーム マスタ フレーム スレーブ 8/16/32 ビットモード クロック パルス / エッジ の選択 フレーム同期 パルス / エッジ の選択 スレーブ 選択パルス

標準 Yes Yes — — Yes Yes — Yes フレーム化 Yes Yes Yes Yes Yes Yes Yes No

表 23-2: オーディオ プロトコル インターフェイス モードにおける SPI 機能 サポートする オーディオ プロトコル SPI マスタ SPI スレーブ 16/24/32 ビット データ フォーマット 32/64 ビット フレーム オーバーフ ロー / アン ダーフロー 検出 モノラル / ステレオ モード マスタクロック (MCLK) サポート I2S、左寄せ、

右寄せ、PCM/DSP Yes Yes Yes Yes Yes Yes Yes

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

図 23-1: SPI モジュールのブロック図 Internal Data Bus SDIx SDOx SSx SCKx SPIxSR(2) bit0 Shift Control Edge SelectEnable Master Clock Baud Rate Slave Select Sync Control Clock Control Transmit SPIxRXB(1) Receive and Frame

Note 1: SPIx 受信バッファ (SPIxRXB) および SPIx 送信バッファ (SPIxTXB) レジスタには、SPIxBUF レジスタを

介してアクセスします。拡張バッファモードでは、これらのバッファはマルチエレメント FIFO バッファ として機能します ( これらの FIFO バッファのポインタ計算は循環式です )。一部のデバイスだけが拡張 バッファモードを備えます。詳細は各デバイスのデータシートを参照してください。 2: アプリケーション ソフトウェアから SPIx シフトレジスタ (SPIxSR) に直接アクセスはできません。 3: CPU 読み出しポインタ (CRPTR) が SPI 書き込みポインタ (SWPTR) 以下である場合、アプリケーション が SPIxRXB レジスタからデータエレメントを読み出すと CRPTR がインクリメントし、データエレメン トが SPIxSR レジスタから SPIxRXB レジスタに転送されると SWPTR がインクリメントします。 4: SPI 読み出しポインタ (SRPTR) が CPU 書き込みポインタ (CWPTR) 以上である場合、アプリケーション が新しいデータエレメントを SPIxBUF レジスタに書き込むと CWPTR がインクリメントし、データが SPIxTXB レジスタから SPIxSR レジスタに転送されると SRPTR がインクリメントします。

Registers share address SPIxBUF SPIxBUF Generator Write Read SPIxTXB(1) PBCLK MCLK MCLKSEL CWPTR(4) SRPTR SWPTR(3) CRPTR

23.1.1

標準モードの SPI 動作

標準モード動作では、SPI マスタがシリアルクロックの生成を制御します。出力クロックパル スの数は転送データ幅 (8、16、32 ビット ) に対応します。図 23-2と図 23-3に、SPI マスタ -スレーブデバイス間の接続と SPI スレーブ - マスタデバイス間の接続を示します。 図 23-2: 標準的な SPI マスタ - スレーブデバイスの接続図 図 23-3: 標準的な SPI スレーブ - マスタデバイスの接続図 SDOx SDIx PIC32 Serial Clock Note 1: 標準モードの場合、スレーブ選択ピン (SSx) は必要に応じて使えます。 2: 受信専用モードでは、SDOx ピンの制御を無効にできます。 GPIO/SSx SCKx SlaveSelect(1) SDIx SDOx(2) PROCESSOR2 SSx SCKx[SPI Master] [Slave]

SDOx(2) SDIx PIC32 Serial Clock Note 1: 標準モードの場合、スレーブ選択ピン (SSx) は必要に応じて使えます。 2: 受信専用モードでは、SDOx ピンの制御を無効にできます。 SSx SCKx SlaveSelect(1) SDIx SDOx PROCESSOR2 SSx/GPIO SCKx

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

23.1.2

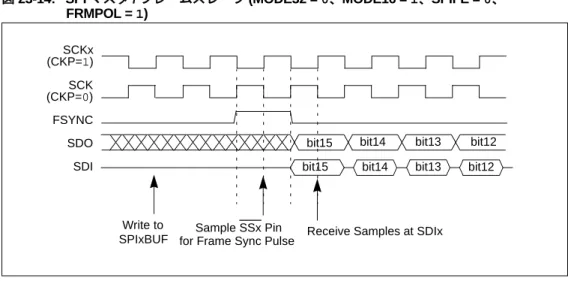

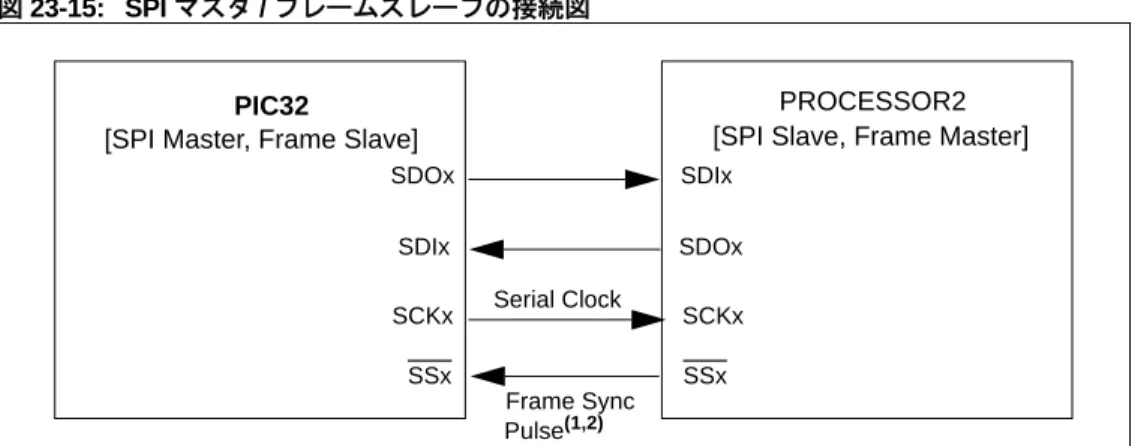

フレーム化モードの SPI 動作

フレーム化モード動作の場合、フレームマスタがフレーム同期パルスの生成を制御し、SPI マ スタは SPI クロックを常時生成します。図 23-4に SPI フレーム マスタデバイスの接続図を示 し、図 23-5に SPI フレーム スレーブデバイスの接続図を示します。 図 23-4: 標準的な SPI マスタ / フレームマスタ デバイスの接続図 図 23-5: 標準的な SPI マスタ / フレームスレーブ デバイスの接続図 SDOx SDIx PIC32 Serial Clock Note 1: フレーム化 SPI モードでは、SSx ピンを使ってフレーム同期パルスを送信 / 受信します。 2: フレーム化 SPI モードは、4 本のピンの全てを使います ( つまり SSx ピンを必ず使います )。 SSx SCKx FrameSync. Pulse(1,2) SDIx SDOx PROCESSOR2 SSx SCKx[SPI Master, Frame Master] [SPI Slave, Frame Slave]

SDOx SDIx Serial Clock Note 1: フレーム化 SPI モードでは、SSx ピンを使ってフレーム同期パルスを送信 / 受信します。 2: フレーム化 SPI モードは、4 本のピンの全てを使います ( つまり SSx ピンを必ず使います )。 SSx SCKx FrameSync. SDIx SDOx SSx SCKx PIC32

[SPI Master, Frame Slave]

PROCESSOR2 [SPI Slave, Frame Master]

23.1.3

オーディオ プロトコル インターフェイス モード

23.1.3.1 オーディオ マスタモードの SPI をコーデック スレーブに接続する 図 23-6に、PIC32 の SPI モジュールがビットクロック (BCLK) と左 / 右チャンネル クロック (LRCK) を生成する場合の接続図を示します。 図 23-6: SPI マスタがクロックを生成してコーデック スレーブに BCLK と LRCK を供給する 23.1.3.2 オーディオ スレーブモードの SPI をコーデックマスタに接続する 図 23-7に、コーデックマスタが BCLK と LRCK を生成する場合の接続図を示します。 図 23-7: コーデックマスタが外付け水晶振動子を使ってクロックを生成する SCKx (BCLK) SSx (LRCK) SDIx SDOx BCLK LRCK ADCDAT DACDAT PIC32 [SPI Master] Codec [Slave] Internal Clock SCK (BCLK) SSx (LRCK) SDIx SDOx BCLK LRCK ADCDAT DACDAT PIC32 [SPI Slave] Codec [Master]シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

23.2

ステータス / 制御レジスタ

SPI モジュールは下記の特殊機能レジスタ (SFR) を備えています。 • SPIxCON: SPI 制御レジスタ • SPIxCON2: SPI 制御レジスタ 2 • SPIxSTAT: SPI ステータスレジスタ • SPIxBUF: SPI バッファレジスタ• SPIxBRG: SPI baud レートレジスタ

表 23-3に、SPI モジュールに関連する全てのレジスタをまとめて示します。各レジスタの詳細

な説明は、この表の後に記載しています。

Note: PIC32 ファミリは、デバイスのタイプに応じて 1 つまたは複数の SPI モジュール

を内蔵しています。ピン、制御 / ステータスビット、レジスタの名前に含まれる添 え字「x」はモジュールの番号を表します。詳細は各デバイスのデータシートを参 照してください。 表 23-3: SPI 関連 SFR のまとめ レジスタ名 Bit レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

SPIxCON(1,2,3) 31:24 FRMEN FRMSYNC FRMPOL MSSEN(4) FRMSYPW(4) FRMCNT<2:0>(4)

23:16 MCLKSEL(4) — — — — — SPIFE ENHBUF(4)

15:8 ON — SIDL DISSDO MODE32 MODE16 SMP CKE 7:0 SSEN CKP MSTEN DISSDI(4) STXISEL<1:0>(4) SRXISEL<1:0>(4)

SPIxCON2(1,2,3,5) 31:24 — — — — — — — — 23:16 — — — — — — — — 15:8 SPISGNE XT — — FRMERRE N

SPIROVEN SPITUREN IGNROV IGNTUR

7:0 AUDEN — — — AUDMONO — AUDMOD<1:0> SPIxSTAT(1,2,3) 31:24 — — — RXBUFELM<4:0>(4)

23:16 — — — TXBUFELM<4:0>(4)

15:8 — — — FRMERR(4) SPIBUSY — — SPITUR

7:0 SRMT(4) SPIROV SPIRBE(4) — SPITBE — SPITBF(4) SPIRBF SPIxBUF 31:24 DATA<31:24> 23:16 DATA<23:16> 15:8 DATA<15:8> 7:0 DATA<7:0> SPIxBRG(1,2,3) 31:24 — — — — — — — — 23:16 — — — — — — — — 15:8 — — — BRG<12:8>(6) 7:0 BRG<7:0>(6) 凡例 : — = 未実装、「0」として読み出し、アドレス オフセット値は 16 進数で表記 Note 1: このレジスタに対応するクリアレジスタのアドレスは 0x4 バイト オフセットしています。クリアレジスタは、対応するレジスタの名前 の後に「CLR」を追加した名前を持ちます ( 例 : SPIxCONCLR)。クリアレジスタの任意のビットに「1」を書き込むと、対応するレジ スタの対応するビットがクリアされます。クリアレジスタからの読み出しは無視されます。 2: このレジスタに対応するセットレジスタのアドレスは 0x8 バイト オフセットしています。セットレジスタは、対応するレジスタの名前 の後に「SET」を追加した名前を持ちます ( 例 : SPIxCONSET)。セットレジスタの任意のビットに「1」を書き込むと、対応するレジス タの対応するビットがセットされます。セットレジスタからの読み出しは無視されます。 3: このレジスタに対応する反転レジスタのアドレスは 0xC バイト オフセットしています。反転レジスタは、対応するレジスタの名前の後 に「INV」を追加した名前を持ちます ( 例 : SPIxCONINV)。反転レジスタの任意のビットに「1」を書き込むと、対応するレジスタの対 応するビットが反転します。反転レジスタからの読み出しは無視されます。 4: 一部のデバイスではこのビットを利用できません。詳細は各デバイスのデータシートを参照してください。 5: 一部のデバイスではこのレジスタを利用できません。詳細は各デバイスのデータシートを参照してください。 6: BRG は最大 13 ビット です ( デバイスによってビット数は異なります )。詳細は各デバイスのデータシートを参照してください。

レジスタ 23-1: SPIxCON: SPI 制御レジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0 31:24 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

FRMEN FRMSYNC FRMPOL MSSEN(1,2) FRMSYPW(1) FRMCNT<2:0>(1) 23:16 R/W-0 U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-0

MCLKSEL — — — — — SPIFE ENHBUF(1) 15:8 R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

ON — SIDL DISSDO MODE32 MODE16 SMP CKE 7:0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

SSEN CKP MSTEN DISSDI STXISEL<1:0>(1,3) SRXISEL<1:0>(1,3)

凡例 :

R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知

bit 31 FRMEN: フレーム化 SPI サポートビット

1 = フレーム化 SPI サポートを有効にする (SSx ピンを FSYNC 入力 / 出力として使う ) 0 = フレーム化 SPI サポートを無効にする

bit 30 FRMSYNC: フレーム同期パルス SSx ピン方向制御ビット ( フレーム化 SPI モード専用 )

1 = フレーム同期パルス入力 ( スレーブモード ) 0 = フレーム同期パルス出力 ( マスタモード )

bit 29 FRMPOL: フレーム同期パルス極性ビット ( フレーム化 SPI モード専用 )

1 = フレームパルスはアクティブ HIGH 0 = フレームパルスはアクティブ LOW bit 28 MSSEN: マスタモード スレーブ選択イネーブルビット(1,2) 1 = スレーブ選択 SPI サポートを有効にする SS ピンは、マスタモードでの送信中に自動的に駆動されます。極性は FRMPOL ビットで指定します。 0 = スレーブ選択 SPI サポートを無効にする bit 27 FRMSYPW: フレーム同期パルス幅ビット(1) 1 = フレーム同期パルスは 1 ワード幅 (MODE<32,16> ビット (SPIxCON<11:10>) の定義に従う ) 0 = フレーム同期パルスは 1 クロック幅 bit 26-24 FRMCNT<2:0>: フレーム同期パルス カウンタビット このビットは 1 パルスあたりの送信データ キャラクタ数を制御します(1)。 111 = 予約済み ( 使用禁止 ) 110 = 予約済み ( 使用禁止 ) 101 = 32 データ キャラクタごとにフレーム同期パルスを生成する 100 = 16 データ キャラクタごとにフレーム同期パルスを生成する 011 = 8 データ キャラクタごとにフレーム同期パルスを生成する 010 = 4 データ キャラクタごとにフレーム同期パルスを生成する 001 = 2 データ キャラクタごとにフレーム同期パルスを生成する 000 = 1 データ キャラクタごとにフレーム同期パルスを生成する このビットはフレーム化 SPI モード (FRMEN = 1) でのみ効力を持ちます。 bit 23 MCLKSEL: マスタクロック選択ビット(2) 1 = baud レート ジェネレータは MCLK を使う 0 = baud レート ジェネレータは PBCLK を使う bit 22-18 未実装 :「0」を書き込み、読み出しは無視 Note 1: 一部のデバイスはこれらのビットを実装していません。詳細は各デバイスのデータシートを参照してく ださい。 2: FRMEN = 1 の場合、MSSEN ビットは使いません。 3: これらのビットは、拡張バッファモードを有効 (ENHBUF = 1) にしている場合にのみ効力を持ちます。

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

bit 17 SPIFE: フレーム同期パルスエッジ選択ビット ( フレーム化 SPI モード専用 )

1 = フレーム同期パルスは先頭ビットクロックと同時に発生する 0 = フレーム同期パルスは先頭ビットクロックに先行して発生する bit 16 ENHBUF: 拡張バッファ イネーブルビット(1)

1 = 拡張バッファを有効にする 0 = 拡張バッファを無効にする bit 15 ON: SPI モジュール ON ビット

1 = SPI モジュールを有効にする 0 = SPI モジュールを無効にする ON = 1 の場合、DISSDO および DISSDI ビットだけが変更可能です。1:1 の PBCLK 分周比を使っている 場合、周辺モジュールの ON ビットをクリアした命令の直後の SYSCLK サイクルでは、その周辺モジュー ルの SFR に対する読み出しまたは書き込みをユーザ ソフトウェアで実行しないでください。 bit 14 未実装 :「0」を書き込み、読み出しは無視 bit 13 SIDL: アイドル中停止ビット 1 = CPU がアイドルに移行すると動作を停止する 0 = アイドル中も動作を継続する

bit 12 DISSDO: SDOx ピン ディセーブル ビット

1 = モジュールは SDOx ピンを使わない ( このピンは対応する PORT レジスタによって制御される ) 0 = モジュールは SDOx ピンを制御する bit 11-10 MODE<32,16>: 32/16 ビット通信選択ビット AUDEN = 1 の場合 : MODE32 MODE16 通信 1 1 24 ビットデータ、32 ビット FIFO、32 ビット チャンネル /64 ビット フレーム 1 0 32 ビットデータ、32 ビット FIFO、32 ビット チャンネル /64 ビット フレーム 0 1 16 ビットデータ、16 ビット FIFO、32 ビット チャンネル /64 ビット フレーム 0 0 16 ビットデータ、16 ビット FIFO、16 ビット チャンネル /32 ビット フレーム AUDEN = 0 の場合 : MODE32 MODE16 通信 1 x 32 ビット 0 1 16 ビット 0 0 8 ビット bit 9 SMP: SPI データ入力サンプル位相ビット マスタモード (MSTEN = 1) の場合 : 1 = データ出力時間の最後に入力データをサンプリングする 0 = データ出力時間の中間で入力データをサンプリングする スレーブモード (MSTEN = 0) の場合 : SPI をスレーブモードで使う場合、SMP ビットの値は無視されます。モジュールは常に SMP = 0 を使い ます。

bit 8 CKE: SPI クロックエッジ選択ビット

1 = クロックのアクティブ状態からアイドル状態への遷移時にシリアル出力データが変化する (CKP ビッ ト参照 )

0 = クロックのアイドル状態からアクティブ状態への遷移時にシリアル出力データが変化する (CKP ビッ ト参照 )

フレーム化 SPI モードでは CKE ビットを使いません。フレーム化 SPI モード (FRMEN = 1) を使う場合、 ユーザはこのビットを「0」に設定する必要があります。 bit 7 SSEN: スレーブ選択イネーブル ( スレーブモード ) ビット 1 = スレーブモードで SSx ピンを使う 0 = スレーブモードで SSx ピンを使わない ( ポート機能がこのピンを制御する ) bit 6 CKP: クロック極性選択ビット 1 = クロックの HIGH レベルをアイドル状態、LOW レベルをアクティブ状態とする 0 = クロックの LOW レベルをアイドル状態、HIGH レベルをアクティブ状態とする レジスタ 23-1: SPIxCON: SPI 制御レジスタ ( 続き ) Note 1: 一部のデバイスはこれらのビットを実装していません。詳細は各デバイスのデータシートを参照してく ださい。 2: FRMEN = 1 の場合、MSSEN ビットは使いません。 これらのビットは、拡張バッファモードを有効 (ENHBUF = 1) にしている場合にのみ効力を持ちます。

bit 5 MSTEN: マスタモード イネーブルビット 1 = マスタモード

0 = スレーブモード

bit 4 DISSDI: SDI ディセーブル ビット

1 = SPI モジュールは SDIx ピンを使わない ( ポート機能がこのピンを制御する ) 0 = SPI モジュールが SDIx ピンを制御する

bit 3-2 STXISEL<1:0>: SPI 送信バッファ エンプティ割り込みモードビット(1,3)

11 = バッファがフルではない場合 ( バッファ内に 1 つまたは複数の空きエレメントがある場合 ) に SPIxTXIF をセットする 10 = バッファに 1/2 以上の空き容量がある場合に SPIxTXIF をセットする 01 = バッファが完全にエンプティである場合に SPIxTXIF をセットする 00 = 最後の転送データを SPISR にシフトアウトして送信動作が完了した時点で SPIxTXIF をセットする bit 1-0 SRXISEL<1:0>: SP 受信バッファフル割り込みモードビット(1,3) 11 = バッファがフルである場合に SPIxRXIF をセットする 10 = バッファ容量の 1/2 以上がデータを格納している場合に SPIxRXIF をセットする 01 = バッファがエンプティではない場合に SPIxRXIF をセットする 00 = 受信バッファ内の最後のワードを読み出した(つまりバッファがエンプティになった)時点でSPIxRXIF をセットする レジスタ 23-1: SPIxCON: SPI 制御レジスタ ( 続き ) Note 1: 一部のデバイスはこれらのビットを実装していません。詳細は各デバイスのデータシートを参照してく ださい。 2: FRMEN = 1 の場合、MSSEN ビットは使いません。 3: これらのビットは、拡張バッファモードを有効 (ENHBUF = 1) にしている場合にのみ効力を持ちます。

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

レジスタ 23-2: SPIxCON2: SPI 制御レジスタ 2 ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/031:24 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

23:16 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

15:8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-1 R/W-1 R/W-0 R/W-0

SPISGNEXT — — FRMERREN SPIROVEN SPITUREN IGNROV IGNTUR 7:0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

AUDEN(1,3) — — — AUDMONO(2) — AUDMOD<1:0>(2,4)

凡例 :

R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知

bit 31-16 未実装 :「0」を書き込み、読み出しは無視

bit 15 SPISGNEXT: 受信 FIFO からの読み出しデータ符号拡張ビット 1 = 受信 FIFO からのデータを符号拡張する

0 = 受信 FIFO からのデータを符号拡張しない bit 14-13 未実装 :「0」を書き込み、読み出しは無視

bit 12 FRMERREN: FRMERR 割り込みイベント イネーブルビット 1 = フレームエラーはエラー割り込みを生成する

0 = フレームエラーはエラー割り込みを生成しない bit 11 SPIROVEN: SPIROV 割り込みイベント イネーブルビット

1 = 受信オーバーフローはエラー割り込みを生成する 0 = 受信オーバーフローはエラー割り込みを生成しない bit 10 SPITUREN: SPITUR 割り込みイベント イネーブルビット

1 = 送信アンダーランはエラー割り込みを生成する 0 = 送信アンダーランはエラー割り込みを生成しない bit 9 IGNROV: 受信オーバーフロー無視ビット ( オーディオデータ送信用 ) 1 = ROVを重大なエラーと見なさない(ROV発生中、FIFO内のデータは受信データによって上書きされない) 0 = ROV を重大なエラーと見なし、SPI 動作を停止する bit 8 IGNTUR: 送信アンダーラン無視ビット ( オーディオデータ送信用 ) 1 = TUR を重大なエラーと見なさず、SPIxTXB がエンプティではなくなるまでゼロを送信する 0 = TUR を重大なエラーと見なし、SPI 動作を停止する bit 7 AUDEN: オーディオ コーデック サポート イネーブルビット(1,3) 1 = オーディオ プロトコルを有効にする 0 = オーディオ プロトコルを無効にする bit 6-5 未実装 :「0」を書き込み、読み出しは無視 bit 3 AUDMONO: オーディオデータ送信フォーマット ビット(2) 1 = オーディオデータはモノラル ( 各データワードを左右両方のチャンネルで送信する ) 0 = オーディオデータはステレオ Note 1: このビットは ON ビット = 0 の場合にのみ書き込み可能です。 2: このビットはONビット = 0の場合にのみ書き込み可能であり、AUDEN = 1の場合にのみ効力を持ちます。 3: オーディオモードを有効 (AUDEN = 1) にすると、SPIxCON レジスタ内の下記のビットはモジュールに よって内部で設定されます。 •ビットクロック (BCLK) と左 / 右チャンネル クロック (LRCK) の方向 ( 入力または出力 ) は、MSTEN ビッ トに基づいて選択される •FRMEN = 1、FRMCNT = 1、SMP = 0

•スレーブモードでは MSTEN = 0/FRMSYNC = 1、マスタモードでは MSTEN = 1/FRMSYNC = 0

4: I2S モードでは SPIFE = 0、右または左寄せモードでは SPIFE = 1、DSP/PCM モード以外では FRMSYPW = 0

bit 2 未実装 :「0」を書き込み、読み出しは無視 bit 1-0 AUDMOD<1:0>: オーディオ プロトコル モードビット(2,4) 11 = PCM/DSP モード 10 = 右寄せモード 01 = 左寄せモード 00 = I2S モード(5) レジスタ 23-2: SPIxCON2: SPI 制御レジスタ 2 ( 続き ) Note 1: このビットは ON ビット = 0 の場合にのみ書き込み可能です。 2: このビットはONビット = 0の場合にのみ書き込み可能であり、AUDEN = 1の場合にのみ効力を持ちます。 3: オーディオモードを有効 (AUDEN = 1) にすると、SPIxCON レジスタ内の下記のビットはモジュールに よって内部で設定されます。 •ビットクロック (BCLK) と左 / 右チャンネル クロック (LRCK) の方向 ( 入力または出力 ) は、MSTEN ビッ トに基づいて選択される •FRMEN = 1、FRMCNT = 1、SMP = 0

•スレーブモードでは MSTEN = 0/FRMSYNC = 1、マスタモードでは MSTEN = 1/FRMSYNC = 0

4: I2S モードでは SPIFE = 0、右または左寄せモードでは SPIFE = 1、DSP/PCM モード以外では FRMSYPW = 0

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

レジスタ 23-3: SPIxSTAT: SPI ステータスレジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/031:24 U-0 U-0 U-0 R-0 R-0 R-0 R-0 R-0

— — — RXBUFELM<4:0>(1)

23:16 U-0 U-0 U-0 R-0 R-0 R-0 R-0 R-0

— — — TXBUFELM<4:0>(1)

15:8 U-0 U-0 U-0 R/C-0, HS R-0 U-0 U-0 R/C-0,HS

— — — FRMERR SPIBUSY — — SPITUR(1)

7:0 R-0 R/C-0,HS R-0 U-0 R-1 U-0 R-0 R-0

SRMT(12) SPIROV SPIRBE(1) — SPITBE — SPITBF(1) SPIRBF

凡例 : C = クリア可能ビット HS = ハードウェアでセット

R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知

bit 31-29 未実装 :「0」を書き込み、読み出しは無視

bit 28-24 RXBUFELM<4:0>: 受信バッファエレメント カウントビット (ENHBUF = 1 の場合にのみ有効 )(1)

FIFO に格納されている受信サンプルの数を示します。 bit 23-21 未実装 :「0」を書き込み、読み出しは無視

bit 20-16 TXBUFELM<4:0>: 送信バッファエレメント カウントビット (ENHBUF = 1 の場合にのみ有効 )(1)

FIFO 内に残っている送信サンプルの数を示します。 bit 15-13 未実装 :「0」を書き込み、読み出しは無視

bit 12 FRMERR: SPI フレームエラー ステータスビット

1 = フレームエラーを検出した 0 = フレームエラーは検出していない FRMERR は、FRMEN = 1 の場合にのみ効力を持ちます。このビットはハードウェアによってのみセット されます。このビットはゼロを書き込む事によってクリアできます ( 命令 SPIxSTATCLR = 1<<12 の使用 を推奨 )。SPIxCON レジスタの ON ビットを使ってモジュールを一度無効にしてから再度有効にする事に よってクリアする事もできます。

bit 11 SPIBUSY: SPI 動作ステータスビット

1 = SPI モジュールはトランザクションを処理中 ( ビジー ) 0 = SPI モジュールはアイドル中 bit 10-9 未実装 :「0」を書き込み、読み出しは無視 bit 8 SPITUR: 送信アンダーラン ビット(1) 1 = 送信バッファでアンダーラン条件が発生した 0 = 送信バッファでアンダーラン条件は発生していない このビットは、フレーム化同期モードでのみ効力を持ちます。このビットはハードウェアによってのみ セットされます。このビットはゼロを書き込む事によってクリアできます ( 命令 SPIxSTATCLR = 1<<8 の 使用を推奨 )。SPIxCON レジスタの ON ビットを使ってモジュールを一度無効にしてから再度有効にする 事によってクリアする事もできます。 bit 7 SRMT: シフトレジスタ エンプティビット (ENHBUF = 1 の場合にのみ有効 )(1) 1 = SPI モジュール シフトレジスタはエンプティ 0 = SPI モジュール シフトレジスタはエンプティではない bit 6 SPIROV: 受信オーバーフロー フラグビット 1 = 新しいデータを完全に受信したが破棄した ( ユーザ ソフトウェアは SPIxBUF レジスタ内の先に受信し たデータをまだ読み出していない ) 0 = オーバーフローは発生していない このビットはハードウェアによってのみセットされます。このビットはゼロを書き込む事によってクリア できます ( 命令 SPIxSTATCLR = 1<<6 の使用を推奨 )。SPIxCON レジスタの ON ビットを使ってモジュー ルを一度無効にしてから再度有効にする事によってクリアする事もできます。 Note 1: 一部のデバイスはこれらのビットを実装していません。詳細は各デバイスのデータシートを参照してくだ さい。

bit 5 SPIRBE: 受信 FIFO エンプティビット (ENHBUF = 1 の場合にのみ有効 )

1 = RX FIFO はエンプティ (CRPTR = SWPTR)

0 = RX FIFO はエンプティではない (CRPTR < SWPTR) bit 4 未実装 :「0」を書き込み、読み出しは無視

bit 3 SPITBE: SPI 送信バッファエンプティ ステータスビット(1)

1 = 送信バッファ (SPIxTXB) はエンプティ

0 = 送信バッファ (SPIxTXB) はエンプティではない

SPI がデータを SPIxTXB から SPIxSR に転送すると、このビットはハードウェアで自動的にセットされます。 SPIxBUF にデータを書き込むと (SPIxTXB にデータが転送されると )、このビットはハードウェアで自動 的にクリアされます。

bit 2 未実装 :「0」を書き込み、読み出しは無視

bit 1 SPITBF: SPI 送信バッファフル ステータスビット(1)

1 = 送信はまだ開始していない (SPITXB はフル ) 0 = 送信バッファはフルではない

標準バッファモードの場合 :

コアが SPIBUF にデータを書き込むと ( データが SPITXB に転送されると )、このビットはハードウェア で自動的にセットされます。

SPI モジュールがデータを SPITXB から SPISR に転送すると、このビットはハードウェアで自動的にク リアされます。

拡張バッファモードの場合 :

このビットは FIFO 内に空き位置がなくなるとセットされます。 bit 0 SPIRBF: SPI 受信バッファフル ステータスビット

1 = 受信バッファ (SPIxRXB) はフル

0 = 受信バッファ (SPIxRXB) はフルではない 標準バッファモードの場合 :

SPI モジュールがデータを SPIxSR から SPIxRXB. に転送すると、このビットはハードウェアで自動的に セットされます。 SPIxBUF を読み出すと (SPIxRXB 内のデータが読み出されると )、このビットはハードウェアで自動的に クリアされます。 拡張バッファモードの場合 : このビットは FIFO 内に空き位置がなくなるとセットされます。 レジスタ 23-3: SPIxSTAT: SPI ステータスレジスタ ( 続き ) Note 1: 一部のデバイスはこれらのビットを実装していません。詳細は各デバイスのデータシートを参照してくだ さい。

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

レジスタ 23-4: SPIxBUF: SPI バッファレジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0 31:24 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DATA<31:24> 23:16 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DATA<23:16> 15:8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DATA<15:8> 7:0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DATA<7:0> 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知bit 31-0 DATA<31:0>: SPI 送信 / 受信バッファレジスタ

送信レジスタ (SPIxTXB) と受信レジスタ (SPIxRXB) のメモリに割り当てられた値として機能します。 32 ビット データモード (MODE<32,16> (SPIxCON<11:10>) = 1x) の場合 : このレジスタの全 32 ビット (SPIxBUF<31:0>) を使って 32 ビットキャラクタを格納します。 16 ビット データモード (MODE<32,16> (SPIxCON<11:10>) = 01) の場合 : このレジスタの下位 16 ビット (SPIxBUF<15:0>) だけを使って 16 ビットキャラクタを格納します。 8 ビット データモード (MODE<32,16> (SPIxCON<11:10>) = 00) の場合 : このレジスタの下位 8 ビット (SPIxBUF<7:0>) だけを使って 8 ビットキャラクタを格納します。

レジスタ 23-5: SPIXBRG: SPI baud レートレジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

31:24 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

23:16 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

15:8 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— — — BRG<12:8> 7:0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 BRG<7:0> 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 31-13 未実装 :「0」を書き込み、読み出しは無視 bit 12-0 BRG<12:0>:baud レート分周比ビット

23.3

動作モード

SPI モジュールは下記の動作モードを備えます。 • 8/16/32 ビットデータ送信モード • 8/16/32 ビットデータ受信モード • マスタモードとスレーブモード • フレーム化 SPI モード • オーディオ プロトコル インターフェイス モード23.3.1

8/16/32 ビット動作

SPI モジュールは SPI バスを介して 3 通りのデータ幅で送受信できます。データ幅の選択に よって SPI データの最小長さが決まります。例えば、32 ビットのデータ幅を選択した場合、全 ての送受信は 32 ビット値で実行されます。CPU からの全ての読み / 書きも 32 ビット値で実行 されます。従って、最大限のデータスループットが得られるよう、アプリケーション ソフト ウェアで適切なデータ幅を選択する必要があります。2 つの制御ビット MODE32 と MODE16 (SPIxCON<11:10>) は動作モードを定義します。これ らのビットは MODE<32,16> と表記される場合もあります。実行中に動作モードを変更するに は、SP モジュールがアイドル状態 ( トランザクションを一切実行していない状態 ) である事が 必要です。SPI モジュールを OFF (SPIxCON<15> = 0) にしてから動作モードを変更した場合、 モジュールを再度 ON にした時点で新しいモードが有効になります。 また、これに関連して下記の点に注意が必要です。 • トランザクションの実行中に MODE<32,16> ビットを変更してはならない • SPIxSR から最初にシフトアウトされるビットは動作モードに応じて下記のように異なる - 8 ビットモード : bit 7 - 16 ビットモード : bit 15 - 32 ビットモード : bit 31 • いずれのモードでもデータは SPIxSR の bit 0 にシフトインされる • SCKx ピンにおけるクロックパルス数も動作モードに応じて下記のように異なる - 8 ビットモード : 8 クロック - 16 ビットモード : 16 クロック - 32 ビットモード : 32 クロック

23.3.2

バッファモード

SPI は標準バッファモードと拡張バッファモードを備えます。 23.3.2.1 標準バッファモード SPI データ受信 / 送信バッファ(SPIxBUF) レジスタは、実際には 2 つの内部レジスタ ( 送信バッ ファレジスタ (SPIxTXB) と受信バッファレジスタ (SPIxRXB)) により構成されます。これら 2 つ の単方向レジスタは SPIxBUF の SFR アドレスを共有します。バイト / ワードの受信が完了すると、受信データは SPIxSR から SPIxRXB に転送され、SPIxRBF フラグがセットされます。SPIxRBF ビットは、ソフトウェアが SPIxBUF バッファを読み出す とクリアされます。

ソフトウェアが SPIxBUF にデータを書き込むと、そのデータは SPIxTXB に転送され、SPIxTBF ビットがハードウェアによってセットされます。SPIxTBF フラグは、データが SPIxSR から送 信されるとクリアされます。

SPI モジュールは、送信および受信動作をダブル バッファリングする事により、バックグラウ ンドで連続的にデータを転送できます。SPIxSR では送信と受信が同時に発生します。

Note 1: フレーム化 SPI モードでは SDIx、SDOx、SCKx、SSx ピンを全て使います。 2: スレーブ選択機能を使う場合も、上記の 4 本のピンを全て使います。 3: 標準 SPI モードで CKE = 1 に設定した場合、スレーブ選択機能を必ず有効にして 使う必要があります。従って、この場合も上記の 4 本のピンを全て使います。 4: 標準 SPI モードで DISSDO = 1 に設定し、スレーブ選択機能を有効にしない場合、 2 本のピン (SDIx と SCKx) だけを使います。 5: その他の全ての条件では 3 本のピン (SDIx、SDOx、SCKx) を使います。 Note: 一部のデバイスだけが拡張バッファモードを備えます。詳細は各デバイスのデー タシートを参照してください。

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

23.3.2.2 拡張バッファモードSPI 制御 (SPIxCON<16>) レジスタの拡張バッファ イネーブル (ENHBUF) ビットをセットする と、拡張バッファモードが有効になります。

拡張バッファモードでは、2 つの 128 ビット FIFO バッファを送信バッファ (SPIxTXB) と受信 バッファ (SPIxRXB) として使います。受信および送信 FIFO には SPIxBUF を介してアクセス できます。SPISR バッファでのデータ送受信方法は標準バッファモードと同じです。FIFO の 深さは、SPI 制御 (SPIxCON<11:10>) レジスタの 32/16 ビット通信選択 (MODE<32,16>) ビッ トで選択したデータ幅によって決まります。MODE フィールドで 32 ビットデータ幅を選択し た場合の FIFO の深さは 4 段、16 ビットデータ幅を選択した場合は 8 段、8 ビットデータ幅を 選択した場合は 16 段です。 送信 FIFO バッファ内の全てのエレメントにデータが格納されると ( バッファがフルになると )、 SPITBF ステータスビットがセットされます。このビットは、1 つまたは複数のエレメントが 空き状態になるとクリアされます。受信 FIFO バッファ内の全てのエレメントにデータが格納 されると ( バッファがフルになると )、SPIRBF ステータスビットがセットされます。このビッ トは、ソフトウェアが SPIxBUF バッファを読み出すとクリアされます。 送信 FIFO バッファ内の全てのエレメントが空き状態になると ( バッファがエンプティになる と )、SPITBE ステータスビットがセットされます。それ以外の場合、このビットはクリアされ ます。受信 FIFO バッファ内の全てのエレメントが空き状態になると ( バッファがエンプティ になると )、SPIRBE ビットがセットされます。それ以外の場合、このビットはクリアされま す。シフトレジスタ エンプティ (SRMT) ビットは、拡張バッファモードにおいてのみ効力を持 ち、シフトレジスタがエンプティになるとセットされ、それ以外の場合はクリアされます。 受信 FIFO 内の空きエレメントの読み出しまたは送信 FIFO 内のデータ格納済みエレメントへ の上書きに対するアンダーラン /オーバーフロー保護措置は備えていません。しかし、SPIxSTAT レジスタの送信アンダーラン ステータスビット (SPITUR) および受信オーバーフロー ステータ スビット (SPIROV) をその他のステータスビットと一緒に監視する事ができます。 SPI ステータス (SPIxSTAT<28:24>) レジスタ内の受信バッファ エレメント カウントビット (RXBUFELM<4:0>) は、受信 FIFO 内の未読み出しエレメントの数を示します。SPI ステータ ス (SPIxSTAT<20:16>)レジスタ内の送信バッファ エレメント カウントビット(TXBUFELM<4:0>) は、送信 FIFO 内の未送信エレメントの数を示します。

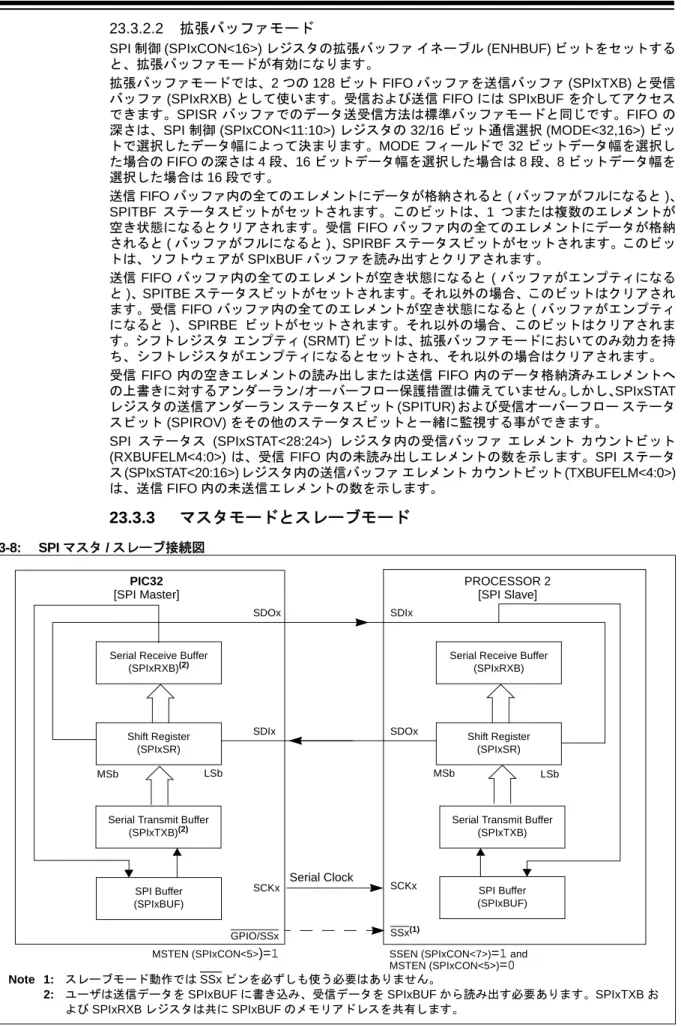

23.3.3

マスタモードとスレーブモード

図 23-8: SPI マスタ / スレーブ接続図

Serial Receive Buffer (SPIxRXB) Shift Register (SPIxSR) LSb MSb SDIx SDOx PROCESSOR 2 SCKx SSx(1)

Serial Transmit Buffer (SPIxTXB) Serial Receive Buffer

(SPIxRXB)(2) Shift Register (SPIxSR) MSb LSb SDOx SDIx PIC32 Serial Clock

SSEN (SPIxCON<7>)=1 and MSTEN (SPIxCON<5>)=0

Note 1: スレーブモード動作では SSx ピンを必ずしも使う必要はありません。

2: ユーザは送信データを SPIxBUF に書き込み、受信データを SPIxBUF から読み出す必要あります。SPIxTXB お

よび SPIxRXB レジスタは共に SPIxBUF のメモリアドレスを共有します。 GPIO/SSx

SCKx Serial Transmit Buffer

(SPIxTXB)(2) MSTEN (SPIxCON<5>)=1 SPI Buffer (SPIxBUF) SPI Buffer (SPIxBUF)

23.3.3.1 マスタモード動作 SPI モジュールをマスタモード動作向けに設定する手順は以下の通りです。 1. 対応する IECx レジスタで SPI 割り込みを無効にする。 2. ON ビットをクリアして SPI モジュールを停止 / リセットする。 3. 受信バッファをクリアする。 4. ENHBUF ビット (SPIxCON<16>) をクリア ( 標準バッファモードを使う場合 ) またはセッ ト ( 拡張バッファモードを使う場合 ) する。 5. SPI 割り込みを使わない場合、このステップを飛ばしてステップ 6 に進む。SPI 割り込み を使うなら下記を行う。 a) 対応する IFSx レジスタの SPIx 割り込みフラグ / イベントをクリアする。 b) 対応する IPCx レジスタの SPIx 割り込み優先度および副優先ビットを設定する。 c) 対応する IECx レジスタの SPIx 割り込みイネーブルビットをセットする。 6. baud レートレジスタ (SPIxBRG) を設定する。 7. SPIROV ビット (SPIxSTAT<6>) をクリアする。

8. SPIxCON レジスタに適切な値を書き込み、MSTEN ビット (SPIxCON<5>) を「1」にセッ トする。 9. ON ビット (SPIxCON<15>) をセットして SPI の動作を有効にする。 10. 送信データを SPIxBUF レジスタに書き込む。データを SPIxBUF レジスタに書き込むと送 信 ( および受信 ) がただちに始まる。 マスタモードでは、PBCLK を分周してシリアルクロックとして使います。分周比は SPIxBRG レジスタの設定に基づきます。シリアルクロックは SCKx ピンを介してスレーブデバイスへ出 力します。クロックパルスは送信すべきデータが存在する場合にのみ生成します。例外として フレーム化モードではクロックを常時生成します。詳細は23.3.7「SPI マスタモードのクロッ ク周波数」を参照してください。 マスタモードで SPI 制御レジスタ (SPIxCON<28>) のマスタモード スレーブ選択イネーブル (MSSEN) ビットをセットすると、スレーブ選択信号 (SS) を自動的に駆動できます。このビッ トをクリアすると、マスタモードでのスレーブ選択信号サポートは無効になります。FRMPOL ビット (SPIxCON<29>) はマスタモードでのスレーブ選択信号の極性を指定します。 MSSEN ビットを備えないデバイスでは、非フレーム化 SPI モードでのスレーブ選択信号は、 ソフトウェア制御の下に SSx ピンまたは他の汎用 I/O ピンを使って生成する必要があります。 CKP (SPIxCON<6>) および CKE (SPIxCON<8>) ビットは、クロックのどちらのエッジでデー タ送信が発生するのかを指定します。 送信するデータは SPIxBUF レジスタに書き込み、受信したデータは SPIxBUF レジスタから読 み出します。 マスタモードにおける SPI モジュールの動作は以下の通りです。 1. モジュールをマスタモード動作向けに設定して有効にすると、送信データが SPIxBUF レジ スタに書き込まれ、SPITBE ビット (SPIxSTAT<3>) がクリアされる。 2. SPIxTXB の内容がシフトレジスタ (SPIxSR) に転送され (図 23-8 参照 )、モジュールは SPITBE ビットをセットする。 3. 連続した 8/16/32 発のクロックパルスにより、送信データの 8/16/32 ビットが SPIxSR から SDOx ピンへシフトアウトされ、同時に SDIx ピン上のデータが SPIxSR へシフトインされ る。

Note: モードをスレーブからマスタに変更する場合、あらかじめ SPI デバイスを OFF に

しておく必要があります。 ( スレーブ選択モードを使う場合、SSx ピンまたは別の GPIO ピンを使ってスレー ブの SSx 入力を制御します。このピンはソフトウェアで制御する必要があります ) Note: MSSEN ビットは一部のデバイスだけが備えます。詳細は各デバイスのデータシー トを参照してください。SPI フレーム化モードを有効 (FRMEN = 1) にしている場 合、このビットをセットしないでください。

Note: CKE または CKP ビットを変更する場合、あらかじめ SPI デバイスを OFF にして

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

4. 転送が完了すると下記が発生する。a) SPIxRXIF 割り込みフラグがセットされる。SPI 割り込みを有効にするには SPIxRXIE 割り込みイネーブルビットをセットする必要がある。SPIxRXIF フラグビットはハー ドウェアで自動的にクリアされない。 b) 送信および受信動作が完了すると、SPIxSR の内容が SPIxRXB に転送される。 c) モジュールは SPIRBF ビット (SPIxSTAT<0>) をセットし、受信バッファがフルであ る事を示す。ユーザコードが SPIxBUF を読み出すと、ハードウェアが SPIRBF ビッ トをクリアする。拡張バッファモードの場合、SPIxRXB FIFO バッファが完全にエン プティになると SPIRBE ビット (SPIxSTAT<5>) がセットされる。このビットは、バッ ファがエンプティではなくなるとクリアされる。

5. SPI モジュールが SPIxSR から SPIxRXB にデータを転送しようとした時に SPIRBF ビットが セットされていると(受信バッファがフルだと)、モジュールはSPIROVビット(SPIxSTAT<6>) をセットしてオーバーフロー条件が発生した事を示す。

6. SPITBE ビット (SPIxSTAT<3>) がセットされていれば、ユーザ ソフトウェアはいつでも送 信データを SPIxBUF に書き込める。SPIxSR が先に書き込まれたデータをシフトアウトし ている間に SPIxBUF に次のデータを書き込めるため、データは連続的に送信できる。拡張 バッファモードの場合、SPIxTXB FIFO バッファが完全にフルになると SPITBF ビット (SPIxSTAT<1>) がセットされる。このビットは、バッファがフルではなくなるとクリアさ れる。

例 23-1: 16 ビット SPI マスタモードの初期化コード

Note: ユーザ ソフトウェアで SPIxSR レジスタに直接書き込む事はできません。SPIxSR

レジスタへの書き込みは、常に SPIxBUF レジスタを経由する必要があります。

/*

The following code example will initialize the SPI1 in Master mode.

It assumes that none of the SPI1 input pins are shared with an analog input.If so, the AD1PCFG and corresponding TRIS registers have to be properly configured.

*/

intrData;

IEC0CLR=0x03800000; // disable all interrupts SPI1CON = 0; // Stops and resets the SPI1. rData=SPI1BUF; // clears the receive buffer IFS0CLR=0x03800000; // clear any existing event IPC5CLR=0x1f000000; // clear the priority IPC5SET=0x0d000000; // Set IPL=3, Subpriority 1

IEC0SET=0x03800000; // Enable RX, TX and Error interrupts

SPI1BRG=0x1; // use FPB/4 clock frequency SPI1STATCLR=0x40; // clear the Overflow

SPI1CON=0x8220; // SPI ON, 8 bits transfer, SMP=1, Master mode

// from now on, the device is ready to transmit and receive data SPI1BUF=’A’; // transmit an A character

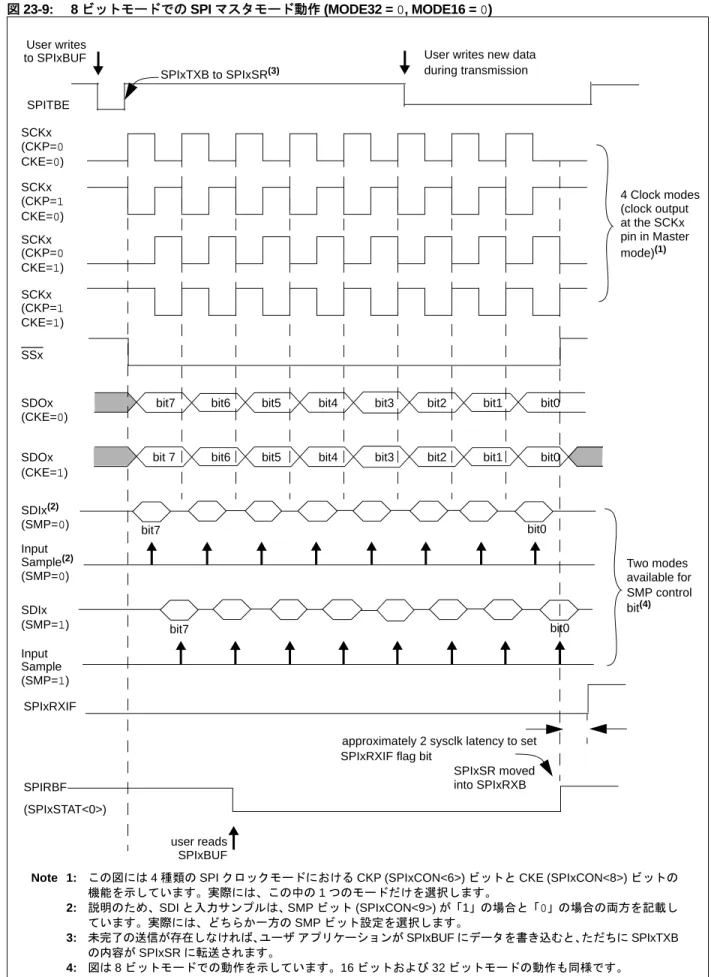

図 23-9: 8 ビットモードでの SPI マスタモード動作 (MODE32 = 0, MODE16 = 0) SCKx (CKP=0 SCKx (CKP=1 SCKx (CKP=0 SCKx (CKP=1 4 Clock modes Input Sample(2) Input Sample SDIx(2) bit7 bit0

SDOx bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

bit7 bit0 SDIx SPIxRXIF (SMP=1) (SMP=0) (SMP=1) CKE=1) CKE=0) CKE=1) CKE=0) (SMP=0) User writes to SPIxBUF

SDOx bit 7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 (CKE=0)

(CKE=1)

approximately 2 sysclk latency to set SPIxRXIF flag bit

Note 1: この図には 4 種類の SPI クロックモードにおける CKP (SPIxCON<6>) ビットと CKE (SPIxCON<8>) ビットの

機能を示しています。実際には、この中の 1 つのモードだけを選択します。 2: 説明のため、SDI と入力サンプルは、 SMP ビット (SPIxCON<9>) が「1」の場合と「0」の場合の両方を記載し ています。実際には、どちらか一方の SMP ビット設定を選択します。 3: 未完了の送信が存在しなければ、ユーザ アプリケーションが SPIxBUF にデータを書き込むと、ただちに SPIxTXB の内容が SPIxSR に転送されます。 4: 図は 8 ビットモードでの動作を示しています。16 ビットおよび 32 ビットモードの動作も同様です。 SPIxSR moved into SPIxRXB user reads SPIxBUF (clock output at the SCKx pin in Master mode)(1) (SPIxSTAT<0>) SPITBE SPIxTXB to SPIxSR(3)

User writes new data during transmission SPIRBF Two modes available for SMP control bit(4) SSx

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

23.3.3.2 スレーブモード動作 SPI モジュールをスレーブモード動作向けに設定する手順は以下の通りです。 1. 割り込みが有効になっている場合、対応する IECx レジスタで SPI 割り込みを無効にする。 2. ON ビットをクリアして SPI モジュールを停止 / リセットする。 3. 受信バッファをクリアする。 4. ENHBUF ビット (SPIxCON<16>) をクリア ( 標準バッファモードを使う場合 ) またはセッ ト ( 拡張バッファモードを使う場合 ) する。 5. SPI 割り込みを使う場合は下記を行う。 a) 対応する IFSx レジスタの SPIx 割り込みフラグ / イベントをクリアする。 b) 対応する IPCx レジスタの SPIx 割り込み優先度および副優先ビットを設定する。 c) 対応する IECx レジスタの SPIx 割り込みイネーブルビットをセットする。 6. SPIROV ビット (SPIxSTAT<6>) をクリアする。7. SPIxCON レジスタに適切な値を書き込み、MSTEN ビット (SPIxCON<5>) を「0」にクリ アする。

8. ON ビット (SPIxCON<15>) をセットして SPI の動作を有効にする。

9. マスタがシリアルクロックの供給を開始すると、送信 ( および受信 ) がただちに始まる。

スレーブモードでは、外部から SCKx ピンに供給されるクロックパルスに従ってデータを送受 信します。CKP ビット (SPIxCON<6>) と CKE ビット (SPIxCON<8>) は、クロックのどちらの エッジでデータ送信が発生するのかを指定します。 送信するデータは SPIxBUF レジスタに書き込み、受信したデータは SPIxBUF レジスタから読 み出します。 拡張バッファモードを含むモジュールのその他の動作はマスタモードと同じです。 23.3.3.2.1 スレーブモードの追加機能 スレーブモードは下記の追加機能を備えます。 • スレーブ選択同期 SSx ピンを使う事で同期スレーブモードが可能になります。スレーブモードで SSEN ビット (SPIxCON<7>) をセットすると、SSx ピンが LOW 状態に駆動されている場合にのみ送受信 が有効になります。SSx ピンを入力として機能させる必要があるため、このピンを使って ポート出力または他の周辺モジュール出力を駆動しない事が必要です。SSEN ビットをセッ トした状態で SSx ピンが HIGH に駆動されると、モジュールが送信の途中であっても SDOx ピンは駆動されなくなり、3 ステートになります。中止された送信は、再び SSx ピンが LOW に駆動された時に、SPIxTXB レジスタで保持されていたデータを使って再試行されます。 SSEN ビットをセットしなければ、SSx ピンはスレーブモードのモジュール動作に影響しま せん。 • SPITBE ステータスフラグの動作 スレーブモードでは、SPITBE ビット (SPIxSTAT<3>) の機能がマスタモードとは異なります。 スレーブモード動作の各種設定に応じて SPITBE は下記のように機能します。

- SSEN (SPIxCON<7>) がクリアされている場合、ユーザコードが SPIxBUF にデータ を書き込むと SPITBE はクリアされます。このビットは、モジュールが SPIxTXB の 内容を SPIxSR に転送するとセットされます。これはマスタモードにおける SPITBE ビットの機能と同様です。 - SSEN がセットされている場合、やはりユーザコードが SPIxBUF にデータを書き込 むと SPITBE はクリアされますが、SPIx モジュールがデータ送信を完了するまでセッ トされません。このため、SSx ピンが HIGH に遷移して中止された送信を後で再試行 できます。つまり、各データワードは全てのビットがレシーバへ送信されるまで SPIxTXB で保持されるという事です。

Note: モードをマスタからスレーブに切り換えるには、SPI モジュールをあらかじめ OFF

にしておく必要があります。

例 23-2: 16 ビット SPI スレーブモードの初期化コード

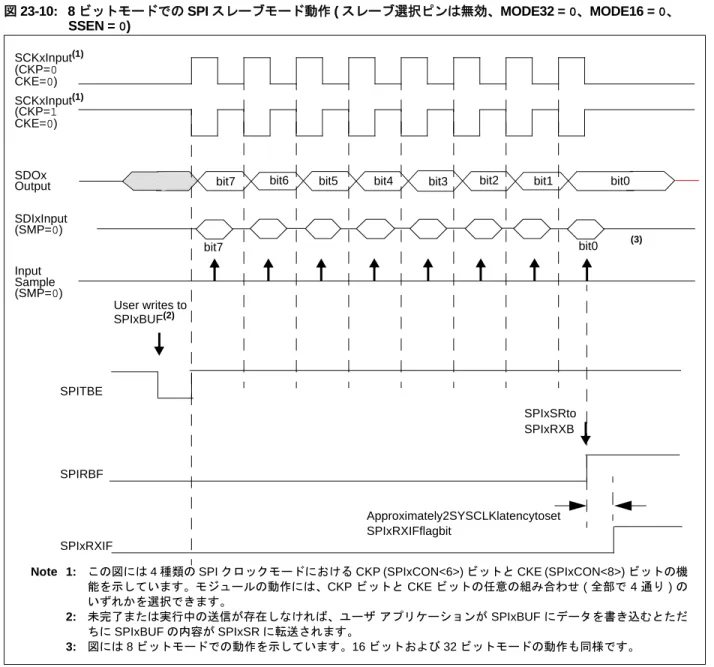

図 23-10: 8 ビットモードでの SPI スレーブモード動作 ( スレーブ選択ピンは無効、MODE32 = 0、MODE16 = 0、

SSEN = 0)

/*

The following code example will initialize the SPI1 in Slave mode.

It assumes that none of the SPI1 input pins are shared with an analog input.If so, the AD1PCFG and corresponding TRIS registers have to be properly configured.

*/

int rData;

IEC0CLR=0x03800000; // disable all interrupts SPI1CON = 0; // Stops and resets the SPI1. rData=SPI1BUF; // clears the receive buffer IFS0CLR=0x03800000; // clear any existing event IPC5CLR=0x1f000000; // clear the priority IPC5SET=0x0d000000; // Set IPL=3, Subpriority 1

IEC0SET=0x03800000; // Enable RX, TX and Error interrupts

SPI1STATCLR=0x40; // clear the Overflow

SPI1CON=0x8000; // SPI ON, 8 bits transfer, Slave mode

// from now on, the device is ready to receive and transmit data

SCKxInput(1) (CKP=1 SCKxInput(1) (CKP=0 Input Sample SDIxInput bit7 bit0

SDOx bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

SPIxRXIF (SMP=0) CKE=0) CKE=0) (SMP=0) User writes to SPIxBUF(2) SPIxSRto SPIxRXB SPITBE SPIRBF Output

Note 1: この図には 4 種類の SPI クロックモードにおける CKP (SPIxCON<6>) ビットと CKE (SPIxCON<8>) ビットの機

能を示しています。モジュールの動作には、CKP ビットと CKE ビットの任意の組み合わせ ( 全部で 4 通り ) の いずれかを選択できます。 2: 未完了または実行中の送信が存在しなければ、ユーザ アプリケーションが SPIxBUF にデータを書き込むとただ ちに SPIxBUF の内容が SPIxSR に転送されます。 3: 図には 8 ビットモードでの動作を示しています。16 ビットおよび 32 ビットモードの動作も同様です。 Approximately2SYSCLKlatencytoset SPIxRXIFflagbit (3)

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

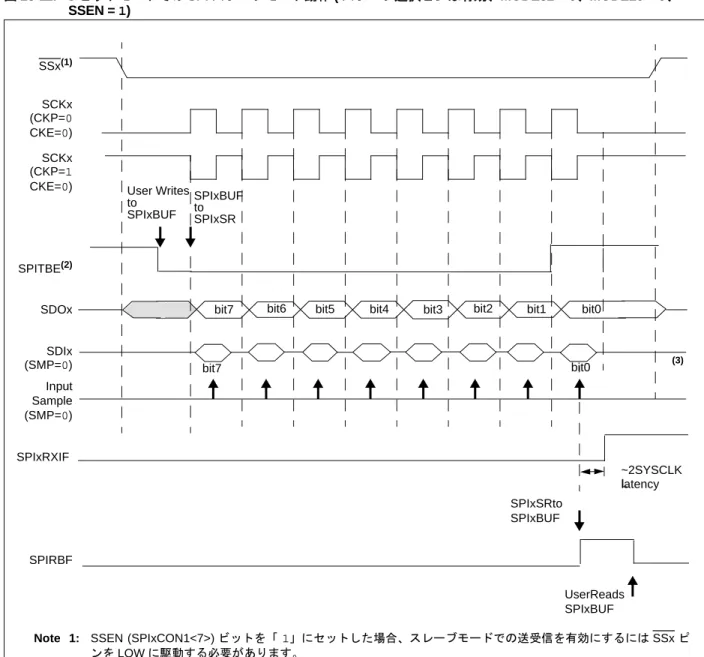

図 23-11: 8 ビットモードでの SPI スレーブモード動作 ( スレーブ選択ピンは有効、MODE32 = 0、MODE16 = 0、

SSEN = 1) SCKx (CKP=1 SCKx (CKP=0 Input Sample SDIx bit7 bit0

SDOx bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

SPIxRXIF (SMP=0) CKE=0) CKE=0) (SMP=0) User Writes SPIxBUF SPIxSRto SPIxBUF SSx(1)

Note 1: SSEN (SPIxCON1<7>) ビットを「 1」にセットした場合、スレーブモードでの送受信を有効にするには SSx ピ

ンを LOW に駆動する必要があります。

2: 全てのビットが送信されるまでSPITBE (SPIxSTAT<3>)はセットされず、送信データはSPIxTXBで保持されます。

3: 図には 8 ビットモードでの動作を示しています。16 ビットおよび 32 ビットモードの動作も同様です。 SPIRBF ~2SYSCLK latency SPITBE(2) SPIxBUF to SPIxSR to (3) L SPIxBUF UserReads

23.3.4

SPI エラー処理

新しいデータワードがシフトレジスタ(SPIxSR)にシフトインされた時点で、ユーザ ソフトウェ アが受信レジスタ (SPIxRXB) に先に書き込まれた内容を読み出し終えていない場合、SPIROV ビット (SPIxSTAT<6>) がセットされます。この場合、モジュールは新しく受信したデータを SPIxSR から SPIxRXB に転送しません。SPIROV ビットがクリアされるまで、後続のデータ受 信は無効になります。モジュールは SPIROV ビットを自動的にクリアしないため、ユーザ ソ フトウェアでクリアする必要があります。

23.3.5

SPIx 受信専用動作

DISSDO 制御ビット (SPIxCON<12>) をセットすると、SDOx ピンでの送信が無効になります。 これを使って SPIx モジュールを受信専用動作モードに設定できます。DISSDO ビットをセッ トすると、SDOx ピンは対応するポート機能により制御されます。

DISSDO ビットの機能は全ての SPI 動作モードで使えます。

23.3.6

フレーム化 SPI モード

SPI モジュールは、マスタおよびスレーブのどちらの動作モードでもごく基本的なフレーム化 SPI プロトコルをサポートします。SPI モジュールは、フレーム化 SPI モードをサポートする 下記の機能を備えます。

• フレーム化 SPI モードは FRMEN 制御ビット (SPIxCON<31>) で有効にします。これを有効 にした場合、フレーム同期パルスの入力または出力ピンとして SSx ピンを使います。SSEN (SPIxCON<7>) の状態は無視されます。

• FRMSYNC 制御ビット (SPIxCON<30>) は、SSx ピンの方向 ( 入力または出力 ) を指定しま す。この設定により、そのモジュールがフレーム同期パルスを受信するのか生成するのかが 決まります。

• FRMPOL 制御ビット (SPIxCON<29>) は、1 SPI クロックサイクルを決めるフレーム同期パ ルスの極性を指定します。 • FRMSYPW 制御ビット (SPIxCON<27>) をセットすると、フレーム同期パルス幅を 1 キャラ クタに設定できます。 • FRMCNT<2:0> 制御ビット (SPIxCON<26:24>) は、1 フレーム同期パルスあたりの送信デー タ キャラクタ数を指定します。 SPI モジュールは下記のフレーム化 SPI モードをサポートします。 • フレーム化マスタモード SPI モジュールはフレーム同期パルスを生成し、SSx ピンを使ってこのパルスを他のデバイ スに供給します。 • フレーム化スレーブモード SPI モジュールは SSx ピンを介して外部から供給されるフレーム同期パルスを使います。 フレーム化 SPI モードは、フレーム化しない通常のマスタおよびスレーブモードと組み合わせ て使えます。従って、下記のフレーム化 SPI 構成が可能です。 • SPI マスタモードとフレームマスタ モード • SPI マスタモードとフレームスレーブ モード • SPI スレーブモードとフレームマスタ モード • SPI スレーブモードとフレームスレーブ モード これら 4 通りのモードにより、SPIx モジュールでどのクロック ( シリアルクロック、フレーム 化同期パルス ) を生成するかが決まります。

ENHBUF ビット (SPIxCON<16>) では、フレーム化 SPI モードで使うバッファモード ( 標準ま たは拡張 ) を選択できます。

また、SPI モジュールをフレーム化 SPI モードで使うと、外部のオーディオ DAC/ADC および コーデックデバイスに接続できます。

Note: 一部のデバイスは FRMSYPW ビットを備えていません。詳細は各デバイスのデー

シリアル

ペリフェラル

インターフェイス

(S

PI

)

23

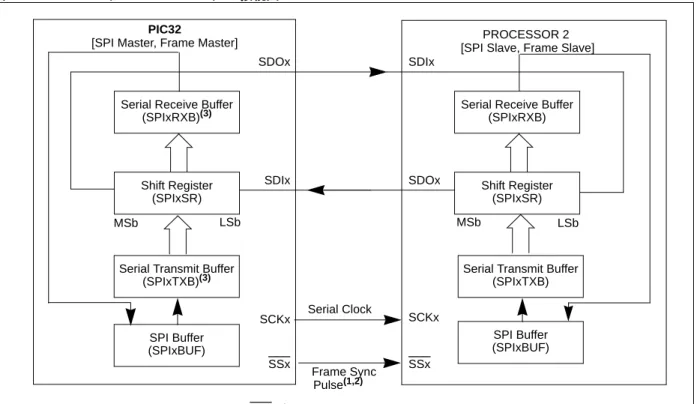

図 23-12: SPI マスタ / フレームマスタ の接続図 23.3.6.1 フレーム化 SPI モードにおける SCKx ピンの動作FRMEN (SPIxCON<31>) = 1 かつ MSTEN (SPIxCON<5>) = 1 の場合、SCKx ピンは出力とし て機能し、フリーランニングの SPI クロックを出力します。

FRMEN = 1 かつ MSTEN = 0 の場合、SCKx ピンは入力として機能します。SCKx ピンにはフ リーランニングの源クロックを供給する必要があります。

クロックの極性は CKP ビット (SPIxCON<6>) で選択します。フレーム化 SPI モードでは CKE ビット (SPIxCON<8>) を使いません。 CKE が「0」である場合、フレーム同期パルス出力と SDOx データ出力の状態は、SCKx ピン のクロックパルス立ち上がりエッジに同期して変化します。SDIx 入力ピンにおける入力データ は、シリアルクロック立ち下がりエッジに同期してサンプリングされます。 CKP が「1」である場合、フレーム同期パルス出力と SDOx データ出力の状態は、SCKx ピン のクロックパルス立ち下がりエッジに同期して変化します。SDIx 入力ピンにおける入力データ は、シリアルクロック立ち上がりエッジに同期してサンプリングされます。 23.3.6.2 フレーム化 SPI モードにおける SPI バッファの動作

FRMSYNC (SPIxCON<30>) = 0 の場合、SPIx モジュールはフレームマスタ モードで動作しま す。このモードでは、ユーザ ソフトウェアが送信データを SPIxBUF に書き込むと ( すなわち SPIxTXB レジスタに送信データが書き込まれると )、モジュールがフレーム同期パルスの生成 を開始します。フレーム同期パルスの終端で SPIxTXB の内容が SPIxSR に転送され、データ の送受信が始まります。 FRMSYNC = 1 の場合、モジュールはフレームスレーブ モードで動作します。このモードでは、 外部ソースがフレーム同期パルスを生成します。モジュールがフレーム同期パルスを検出する と、SPIxTXB レジスタの内容が SPIxSR に転送され、データ送受信が始まります。ユーザは、 同期パルスを受信する前に SPIxBUF に適切な送信データを書き込む必要があります。 23.3.6.3 SPI マスタ / フレームマスタ モード Serial Receive Buffer

(SPIxRXB)(3) Shift Register (SPIxSR) MSb LSb SDOx SDIx PIC32

Serial Receive Buffer (SPIxRXB) Shift Register (SPIxSR) LSb MSb SDIx SDOx PROCESSOR 2 Serial Clock Note 1: フレーム化 SPI モードでは、SSx ピンを使ってフレーム同期パルスを送信 / 受信します。 2: フレーム化 SPI モードは 4 本のピンの全てを使います ( つまり SSx ピンを必ず使います )。 3: SPIxTXB および SPIxRXB レジスタは、共に SPIxBUF レジスタのメモリアドレスを共有します。

SCKx

SSx SSx

SCKx Serial Transmit Buffer

(SPIxTXB)(3)

Serial Transmit Buffer (SPIxTXB) Frame Sync Pulse(1,2) SPI Buffer (SPIxBUF) SPI Buffer (SPIxBUF) [SPI Master, Frame Master] [SPI Slave, Frame Slave]

Note: フレーム同期パルスを受信すると、SPIxBUF にデータが書き込まれたかどうかに

関係なく送信が始まります。書き込みを実行しなかった場合、ゼロが送信されま す。