UltraScale アーキテ ク チ ャ

メ モ リ

リ ソース

ユーザー

ガイ ド

UG573 (v1.10) 2019 年 2 月 4 日この資料は表記のバージョンの英語版を翻訳したもので、内容に相違が生じる場合には原文を優先します。資料に

よっては英語版の更新に対応していないものがあります。日本語版は参考用としてご使用の上、最新情報につきまし

ては、必ず最新英語版をご参照ください。

次の表に、 こ の文書の改訂履歴を示 し ます。 日付 バージ ョ ン 内容 2019 年 2 月 4 日 1.10 「ア ド レ ス競合」 に共通 ク ロ ッ ク と 独立 ク ロ ッ ク の情報を追加。「シ ンプル デュ アル ポー ト ブ ロ ッ ク RAM」 で、 ポー ト A を書き込みポー ト 、 ポー ト B を読み出 し ポー ト に変更。 「UltraRAM の主な機能」 の 「 コ ン テ ン ツ ク リ ア機能」 を削除。 2018 年 2 月 9 日 1.9 表 2-2 の EN_A お よ び EN_B ポー ト の説明を更新。図 2-16 を更新。 2017 年 11 月 14 日 1.8 「共通 ク ロ ッ ク /シ ン グル ク ロ ッ ク FIFO」 の注記 (重要) を更新。「 イ ネーブル自動ス リ ー プ モー ド – EN_AUTO_SLEEP_MODE」 に注記を追加。「UltraRAM の概要」 を更新。 図 2-28 と その説明を削除。 2017 年 8 月 10 日 1.7 「共通 ク ロ ッ ク /シ ン グル ク ロ ッ ク FIFO」 に注記 (重要) を追加。「エン コ ー ド 専用 ECC で の読み出 し 」 を更新。 2017 年 5 月 4 日 1.6 表 2-5 を更新。 2017 年 3 月 15 日 1.5 「ブ ロ ッ ク RAM の概要」 の注記 (重要) を更新。表 1-16 に注記 2 を追加。「 リ セ ッ ト – RST_A、 RST_B」 を更新。「UltraRAM の タ イ ミ ン グ図」 を追加。 2016 年 7 月 20 日 1.4 「旧世代 と の違い」、「同期デ ュ アル ポー ト およ びシ ン グル ポー ト RAM」、「省電力 – RDADDRCHANGE[A|B]」、「パ ワー ゲーテ ィ ン グ イ ネーブル入力 – SLEEP」、「デー タ 出 力バ ス – DOUT_A、 DOUT_B」、「読み出 し ス テー タ ス出力 – RDACCESS_A、

RDACCESS_B」、「カ ス ケー ド レ ジ ス タ ス テージ (オプシ ョ ン) – REG_CAS_[A|B]」、

「UltraRAM のカ ス ケー ド 接続 と マ ト リ ク ス コ ン フ ィ ギ ュ レーシ ョ ン」、 お よ び 「カ ス ケー ド 接続のユーザー属性」 を改訂。表 1-16 お よ び表 1-32 に注記を追加。表 2-5 を更新。

「AVG_CONS_INACTIVE_CYCLES、 MATRIX_ID、 NUM_URAM_IN_MATRIX、 お よび NUM_UNIQUE_SELF_ADDR_A|B 属性」 を追加。図 2-1 お よ び図 2-5 を更新。

2015 年 11 月 24 日 1.3 UltraScale+ デバ イ ス の説明を追加。「UltraScale アーキテ ク チ ャ の概要」 を更新 し て UltraScale+ の説明を追加。「ブ ロ ッ ク RAM の概要」 の注記 (重要) を更新。「RAMB18/36

の未使用の入力」 に導入の段落を追加。 ユーザー ガ イ ド を再構成し て、 旧版の第 2 章 (ビ ル ト イ ン FIFO) および第 3 章 (ビル ト イ ン エ ラ ー訂正) を第 1 章 「ブ ロ ッ ク RAM リ ソ ー ス」 に統合 し 、 新たに第 2 章 「UltraRAM リ ソ ース」 を追加。 2015 年 2 月 24 日 1.2 「 メ モ リ 内容の初期化 – INIT_xx」 を更新。 2014 年 8 月 14 日 1.1 「ブ ロ ッ ク RAM の概要」 の箇条書 き の 11 番目を更新。表 1-8 の CASDINPA[3:0] と CASDINB[31:0] の説明を変更。表 1-16 の DOB_REG の説明を更新。図 1-6 の WDADDREN 入力を更新。表 1-14 を追加。「カ ス ケー ド 接続可能なブ ロ ッ ク RAM」 を更 新。「SLEEP」 お よ び 「省電力 – SLEEP_ASYNC」 を小修正。「共通 ク ロ ッ ク /シ ン グル ク ロ ッ ク FIFO」 の説明を小変更。図 1-21 お よ び図 1-22 に SLEEP 入力を追加。表 1-25 で、 SLEEP ポー ト を追加 し 、 CASOREGIMUX、 CASOREGIMUXEN、 CASDOMUX、 お よ び CASDOMUXEN の説明を変更。表 1-26 を更新。表 1-27 を追加。 第 1 章の

「PROG_EMPTY_THRESH」、「PROG_FULL_THRESH」、 お よ び 「REGISTER_MODE」 を 更新。 第 2 章の 「FIFO18E2/FIFO36E で設定で き る PROG_EMPTY_THRESH の範囲」 およ び 「FIFO18E2/FIFO36E2 で設定で き る PROG_FULL_THRESH の範囲」 の各表を削除。

表 1-8 の CASOUTSBITERR、 CASINDBITERR、 お よ び CASOUTDBITERR を更新。 2013 年 12 月 10 日 1.0 初版

改訂履歴 . . . 2

第 1 章: ブ ロ ッ ク RAM リ ソ ース

UltraScale アーキ テ ク チ ャ の概要 . . . 4 ブ ロ ッ ク RAM の概要 . . . 5 旧世代 と の違い . . . 7 ブ ロ ッ ク RAM の説明 . . . 8 同期デ ュ アル ポー ト お よびシ ン グル ポー ト RAM . . . 8 ブ ロ ッ ク RAM のその他の機能 . . . 15 ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ . . . 25 ブ ロ ッ ク RAM ポー ト 信号 . . . 29 ブ ロ ッ ク RAM のア ド レ ス マ ッ プ . . . 36 ブ ロ ッ ク RAM の属性 . . . 36 ブ ロ ッ ク RAM と FIFO の配置. . . 44 VHDL ま たは Verilog コ ー ド でのブ ロ ッ ク RAM の初期化 . . . 44 RAMB18E2 お よ び RAMB36E2 プ リ ミ テ ィ ブの設計上のその他の注意事項 . . . 45 ブ ロ ッ ク RAM のアプ リ ケーシ ョ ン . . . 47 ビル ト イ ン FIFO. . . 49 ビル ト イ ン エ ラ ー訂正 . . . 79第 2 章: UltraRAM リ ソ ース

UltraRAM の概要 . . . 85 UltraRAM の主な機能 . . . 86 UltraRAM のカ ス ケー ド 接続 . . . 86 UltraRAM のエ ラ ー訂正符号 . . . 87 ブ ロ ッ ク RAM と UltraRAM の違い . . . 87 UltraRAM のプ リ ミ テ ィ ブ . . . 89 UltraRAM のポー ト 名 と 説明 . . . 92 UltraRAM の属性 . . . 100 デ ュ アル ポー ト SRAM ア レ イ の動作 . . . 106 ビル ト イ ンエ ラ ー検出/訂正 . . . 114 UltraRAM の タ イ ミ ン グ図 . . . 117付録 A: その他の リ ソ ースおよび法的通知

ザ イ リ ン ク ス リ ソ ース . . . 126 ソ リ ュ ーシ ョ ン セン ター . . . 126 Documentation Navigator お よ びデザ イ ン ハブ. . . 126 参考資料 . . . 127 お読み く だ さ い: 重要な法的通知 . . . 128ブ ロ ッ ク RAM リ ソ ース

UltraScale アーキテ ク チ ャ の概要

ザ イ リ ン ク ス UltraScale™ アーキテ ク チ ャ は、 チ ッ プ上での効率的な配線 と デー タ処理だけでな く 、 ス マー ト プ ロ セ ッ シ ン グに よ っ て数百ギガ ビ ッ ト /秒レベルのシ ス テ ム性能を可能にする業界初の ASIC ク ラ ス のアーキテ ク チ ャ です。 UltraScale アーキテ ク チ ャ デバ イ スは、 次世代配線、 ASIC 方式の ク ロ ッ キ ン グ、 3D-on-3D IC、 マルチプ ロ セ ッ サ SoC (MPSoC) テ ク ノ ロ ジ、 新し い消費電力低減機能な ど、 業界最先端をい く 革新的な技術に よ っ て高帯域幅、 高使用率の幅広いシ ス テ ム要件に対応 し ます。 こ れ ら のデバ イ ス は多数の構築ブ ロ ッ ク が共通 と な っ てい る ため、 異な る プ ロ セ ス ノ ー ド 間や製品フ ァ ミ リ 間での拡張性に優れ、 複数のプ ラ ッ ト フ ォームに渡る シ ス テ ム レベルでの 投資を可能に し ます。

Virtex® UltraScale+™ デバ イ ス は、 最 も 高いシ リ アル I/O 帯域幅 と 信号処理帯域幅、 最大のオ ンチ ッ プ メ モ リ 集積度

な ど、 FinFET ノ ー ド で最高の性能 と 統合性を提供 し ます。 業界で最高性能を誇る FPGA フ ァ ミ リ の Virtex UltraScale+ デバ イ ス は、 1Tb/s を超え る ネ ッ ト ワ ー ク やデー タ セ ン タ ーか ら 、 完全統合型レーダー /早期警告シ ス テ ムにいた る ま で、 広範な アプ リ ケーシ ョ ンに最適です。

Virtex UltraScale デバ イ ス は、 シ リ アル I/O 帯域幅お よ び ロ ジ ッ ク 容量な ど において、 20nm で最高の性能 と 統合性を 提供 し ます。 20nm プ ロ セ ス ノ ー ド で業界唯一のハ イ エン ド FPGA と な る こ のデバ イ スは、 400G ネ ッ ト ワー ク か ら 大規模 ASIC のプ ロ ト タ イ ピ ン グやエ ミ ュ レーシ ョ ン な どのアプ リ ケーシ ョ ンに最適です。 Kintex® UltraScale+ デバ イ ス は、 ト ラ ン シーバー、 メ モ リ イ ン タ ーフ ェ イ ス ラ イ ン レー ト 、 100G コ ネ ク テ ィ ビ テ ィ コ ア な ど のハ イ エン ド 機能を備え る こ と で最 も コ ス ト 効率の高い ソ リ ュ ーシ ョ ン を可能に し 、 FinFET ノ ー ド で最 も 優れた価格/性能/ワ ッ ト のバ ラ ン ス を提供し ます。 こ の最新の ミ ッ ド レ ン ジ フ ァ ミ リ は、 パケ ッ ト 処理 と DSP を多 用す る 機能に最適であ る と 同時に、 ワ イ ヤ レ ス MIMO 技術、 Nx100G ネ ッ ト ワー ク 、 データ セン タ ーな ど広範なア プ リ ケーシ ョ ンに も 対応 し ます。 Kintex UltraScale は、 20nm で最高の価格/性能/ ワ ッ ト のバ ラ ン ス を提供す る デバ イ ス で、 ミ ッ ド レ ン ジ デバ イ ス と し て最高の信号処理帯域幅、 次世代 ト ラ ン シーバー、 最適な対 コ ス ト 性能を も た ら す低 コ ス ト パ ッ ケージ を提供 し ま す。 こ の フ ァ ミ リ は、 100G ネ ッ ト ワー ク やデータ セン タ ー アプ リ ケーシ ョ ンでのパケ ッ ト 処理だけでな く 、 次世代 の医療用画像処理、 8k4k ビデオ、 ヘテ ロ ジニア ス な ワ イ ヤ レ ス イ ン フ ラ な ど で必要 と さ れ る DSP 性能を重視する ア プ リ ケーシ ョ ンに も 最適です。

Zynq® UltraScale+ MPSoC デバ イ ス は、 64 ビ ッ ト のプ ロ セ ッ サ ス ケー ラ ビ リ テ ィ を実現 し つつ、 リ アル タ イ ム制御 と

ソ フ ト エン ジ ンおよ びハー ド エン ジ ン を兼ね備えてお り 、 グ ラ フ ィ ッ ク ス、 ビデオ、 波形、 お よびパケ ッ ト の処理 に対応 し ます。 高度な解析が可能な Arm® ベース のシ ス テ ム と タ ス ク のア ク セ ラ レーシ ョ ン が可能なオ ンチ ッ プ プ ロ グ ラ マブル ロ ジ ッ ク が統合 さ れてい る ため、 5G ワ イ ヤ レ ス、 次世代 ADAS、 イ ン ダ ス ト リ アル IoT な ど広範なア プ リ ケーシ ョ ンにおいて無限の可能性を引 き 出す こ と がで き ます。 こ のユーザー ガ イ ド では、 UltraScale アーキテ ク チ ャ の メ モ リ リ ソ ース について説明 し ます。 UltraScale アーキテ ク チ ャ に関す る その他の資料は、 ザ イ リ ン ク ス の ウ ェ ブサ イ ト (japan.xilinx.com/documentation) か ら 入手可能です。

ブ ロ ッ ク RAM の概要

UltraScale アーキ テ ク チ ャ デバ イ ス のブ ロ ッ ク RAM は 2 つの独立 し た 18Kb RAM ま たは 1 つの 36Kb RAM と し て構 成可能で、 いずれ も 最大 36 キ ロ ビ ッ ト のデータ を格納で き ます。 各ブ ロ ッ ク RAM には書き込みポー ト と 読み出 し ポー ト が 2 つずつあ り ます。 36Kb ブ ロ ッ ク RAM を TDP (True Dual Port) メ モ リ と し て使用する場合、 ポー ト の幅は 個別に 32Kx1、 16Kx2、 8Kx4、 4Kx9、 2Kx18、 1Kx36 のいずれかに設定で き ます。 36Kb ブ ロ ッ ク RAM を SDP (Simple Dual Port) メ モ リ と し て使用 し 、 書 き 込みポー ト と 読み出 し ポー ト を それぞれ 1 つずつ し か使用 し ない場合 は、 512x72 ビ ッ ト のポー ト 幅 も 可能です。 18Kb ブ ロ ッ ク RAM を TDP メ モ リ と し て使用する と 、 ポー ト の幅を個別 に 16Kx1、 8Kx2、 4Kx4、 2Kx9、 1Kx18 のいずれかに設定で き ます。 18Kb ブ ロ ッ ク RAM を SDP メ モ リ と し て使用 し 、 書 き 込みポー ト と 読み出 し ポー ト を それぞれ 1 つずつ し か使用 し ない場合は、 512x36 ビ ッ ト のポー ト 幅 も 可能 です。 7 シ リ ーズ FPGA のブ ロ ッ ク RAM 同様、 書 き 込み と 読み出 し は ク ロ ッ ク に同期 し て実行 さ れ ます。 2 つのポー ト は 対称でそれぞれ完全に独立 し てお り 、 保存 し たデー タ のみを共有 し ます。 各ポー ト は、 設定可能な幅のいずれかに 指定で き 、 も う 一方のポー ト か ら は独立 し てい ます。 さ ら に、 1 つのポー ト の読み出 し ポー ト と 書き込みポー ト には 別々の幅を設定可能です。 メ モ リ 内容は、 コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ームで初期化ま たは ク リ アで き ま す。 書 き 込み実行中のデー タ 出力は、 以前の出力を その ま ま維持す る か、 書 き 込まれてい る デー タ を出力す る か、 上書 き さ れ る 以前のデー タ を出力す る かを設定で き ます。 ブ ロ ッ ク RAM には次の特長があ り ます。 • ブ ロ ッ ク ご と の メ モ リ 格納機能に よ り 、 各ブ ロ ッ ク RAM に最大で 36Kb のデータ を格納で き ます。 • 2 つの独立 し た 18Kb ブ ロ ッ ク ま たは 1 つの 36Kb ブ ロ ッ ク RAM をサポー ト し ます。 • 各 36Kb ブ ロ ッ ク RAM を読み出 し ポー ト と 書き込みポー ト が 1 つずつの SDP モー ド と し て使用 し た場合、 ブ ロ ッ ク RAM のデー タ幅は 2 倍の 72 ビ ッ ト にな り ます。 18Kb ブ ロ ッ ク RAM を読み出し ポー ト と 書き込みポー ト が 1 つずつの SDP モー ド と し て使用 し た場合は、 データ 幅は 2 倍の 36 ビ ッ ト にな り ます。 • RAMB36 SDP メ モ リ と し て使用す る 場合、 一方のポー ト 幅は 512x64 ま たは 512x72 に固定 さ れ、 も う 一方の ポー ト 幅は 32Kx1 ~ 512x72 に設定で き ます。 RAMB18 SDP メ モ リ と し て使用する場合、 一方のポー ト 幅は 512x36 に固定 さ れ、 も う 一方のポー ト 幅は 16Kx1 ~ 512x36 に設定で き ます。

• 隣接す る ブ ロ ッ ク RAM を カ ス ケー ド 接続し 、 下段のブ ロ ッ ク RAM のデータ 出力を上段のブ ロ ッ ク RAM に入 力す る こ と で、 大容量のブ ロ ッ ク RAM ブ ロ ッ ク を構成可能です。 オプシ ョ ンのパ イ プ ラ イ ン レ ジ ス タ を使用 す る と 、 最大限の性能がサポー ト さ れます。

• 36Kb ブ ロ ッ ク RAM ま たは 36Kb FIFO は 64 ビ ッ ト の ECC (エ ラ ー訂正符号) ブ ロ ッ ク を 1 つ備え てい ます。 エン コー ド /デコー ド 機能が別々に使用可能です。 ECC モー ド にはエ ラ ー挿入機能があ り ます。 • 初期値に対す る 、 出力の同期セ ッ ト / リ セ ッ ト は、 ブ ロ ッ ク RAM 出力の ラ ッ チおよ びレ ジ ス タ モー ド の両方で 使用で き ます。 • 同期セ ッ ト ピ ン と 同期 リ セ ッ ト ピ ン を分離する こ と に よ り 、 オプシ ョ ンの出力レ ジ ス タ のセ ッ ト / リ セ ッ ト と ブ ロ ッ ク RAM の出力 ラ ッ チ段階を個別に制御で き ます。 • ブ ロ ッ ク RAM を共通 ク ロ ッ ク /シ ン グル ク ロ ッ ク FIFO と し て構成する と 、 フ ラ グの レ イ テ ン シのば ら つき が な く な り ます。 • 18、 36、 72 ビ ッ ト 幅のブ ロ ッ ク RAM ポー ト には、 バ イ ト ご と に個別の ラ イ ト イ ネーブルを含め る こ と がで き ます。 こ れは、 マ イ ク ロ プ ロ セ ッ サ と イ ン タ ーフ ェ イ スす る 際に頻繁に使用 さ れ る 機能です。 • 各ブ ロ ッ ク RAM には、 ビル ト イ ンの独立 ク ロ ッ ク FIFO メ モ リ と し て動作する ためのア ド レ ス シーケ ン ス処理

• すべての入力はポー ト ク ロ ッ ク に同期 し て取 り 込まれ、 Setup-to-Clock タ イ ミ ン グ仕様に従い ます。

• すべての出力は、 ラ イ ト イ ネーブル (WE) ピ ンの状態に よ っ て、 読み出し ま たは書き込み中に読み出し にな り ます。 こ れ ら の出力は、 Clock-to-Out 時間に有効にな り ます。 書き込み中の読み出 し の出力には、 3 つの動作 モー ド 、 WRITE_FIRST、 READ_FIRST、 NO_CHANGE があ り ます。

• 書 き 込みには、 ク ロ ッ ク エ ッ ジが 1 つ必要です。 • 読み出 し には、 ク ロ ッ ク エ ッ ジが 1 つ必要です。 • すべての出力ポー ト は、 オプシ ョ ンで ラ ッ チ ま たはレ ジ ス タ 付 き です。 別の読み出 し /書き込みを実行する ま で は、 出力ポー ト の値は一定です。 デフ ォ ル ト のブ ロ ッ ク RAM 出力はレ ジ ス タ モー ド です。 推奨: 出力データパスにはオプシ ョ ンの内部パイ プ ラ イ ン レ ジ ス タがあ り ます。 レ ジ ス タ モー ド の使用を強 く 推奨 し ます。 こ れに よ り 、 高 ク ロ ッ ク レー ト での動作が可能にな り ますが、 ク ロ ッ ク の 1 サ イ ク ル分のレ イ テ ン シが追 加 さ れます。 ブ ロ ッ ク RAM には次の使用規則があ り ます。

• ブ ロ ッ ク RAM の同期出力レ ジ ス タ (オプシ ョ ン) は、 DO_REG = 1 の と き に RSTREG を使用 し てセ ッ ト ま たは リ セ ッ ト (SRVAL) さ れます。 RSTREG と REGCE のど ち ら が優先 さ れる かは、 RSTREG_PRIORITY 属性で指定 し ます。 同期出力 ラ ッ チは DO_REG = 0 ま たは 1 の と き に RSTRAM を使用 し てセ ッ ト ま たは リ セ ッ ト (SRVAL) さ れます。 重要: ブ ロ ッ ク RAM のア ド レ ス ピ ンおよびラ イ ト イ ネーブル ピ ンでセ ッ ト ア ッ プ/ホール ド タ イ ム違反が生じ ない よ う に し ます。 こ れ ら のセ ッ ト ア ッ プ/ホール ド タ イ ムに違反する と 、 ラ イ ト イ ネーブルが Low であ っ て も 、 ブ ロ ッ ク RAM のデー タ内容が破損する こ と があ り ます。 こ れは主に、 ブ ロ ッ ク RAM の制御ピ ン を駆動 し てい る フ リ ッ プ フ ロ ッ プがシ ス テ ム全体の リ セ ッ ト な ど非同期に リ セ ッ ト さ れた場合に発生 し ます。 こ の問題を防ぐ には、 アサー ト と デ ィ アサー ト の両方に同期 リ セ ッ ト のみを使用 し て設計 し ます。

• ブ ロ ッ ク RAM の レ ジ ス タ モー ド が RSTREG で、 RSTREG_PRIORITY = REGCE の場合、 出力 DO レ ジ ス タ 値を リ セ ッ ト す る には、 REGCE = 1 と する必要があ り ます。 こ のモー ド では、 ブ ロ ッ ク RAM ア レ イ データ 出力 ラ ッ チは リ セ ッ ト さ れません。 ブ ロ ッ ク RAM の ラ ッ チ モー ド SRTRAM の場合、 出力 DO ラ ッ チ値を リ セ ッ ト す る にはブ ロ ッ ク RAM は イ ネーブル (EN = 1) にな っ てい る必要があ り ます。

• ブ ロ ッ ク RAM プ リ ミ テ ィ ブには RAMB36E2 と RAMB18E2 の 2 つがあ り ます。

• 特定のブ ロ ッ ク RAM プ リ ミ テ ィ ブを使用する と 、 読み出し およ び書き込みポー ト に異な る幅が選択可能です。 パ リ テ ィ ビ ッ ト はポー ト 幅が x9、 x18、 x36 の場合のみ利用で き ます。 読み出 し 幅が x1、 x2、 x4 の と き は使用 し ないで く だ さ い。 読み出 し 幅が x1、 x2、 ま たは x4 の場合、 有効な書き込み幅は x1、 x2、 x4、 x8、 x16、 x32 です。 同様に、 書 き 込み幅が x1、 x2、 ま たは x4 の場合、 プ リ ミ テ ィ ブの属性は 1、 2、 4、 9、 18、 あ る いは 36 に設定 さ れますが、 実際に使用可能な読み出 し 幅はそれぞれ x1、 x2、 x4、 x8、 x16、 ま たは x32 と な り ます。 表 1-1 に、 ポー ト 幅の組み合わせを示 し ます。

旧世代 と の違い

7 シ リ ーズ FPGA からの変更点

• SDP メ モ リ と し て使用す る 場合、 すべての書 き 込みモー ド (READ_FIRST、 WRITE_FIRST、 NO_CHANGE) がサ ポー ト さ れます。 • UltraScale アーキ テ ク チ ャ デバ イ ス では、 新 し いデー タ カ ス ケー ド 方式が採用 さ れ ま し た。 ブ ロ ッ ク RAM を ボ ト ム ア ッ プ方式で直接カ ス ケー ド 接続す る こ と に よ り 、 ほかの ロ ジ ッ ク リ ソ ース を使用する こ と な く 、 ブ ロ ッ ク RAM カ ラ ム内で大容量のブ ロ ッ ク RAM を構築で き ます。 • ブ ロ ッ ク RAM にア ド レ ス イ ネーブル機能が追加 さ れま し た。 こ れを無効にする と 、 ブ ロ ッ ク RAM で新 し いア ド レ ス は ラ ッ チ さ れません。 • 動的パ ワー ゲーテ ィ ン グ機能が追加 さ れま し た。 データ 内容を保持 し た ま ま ブ ロ ッ ク RAM を ス リ ープ モー ド に移行で き ます。

• RAM_MODE 属性は削除 さ れ ま し た。 ブ ロ ッ ク RAM を TDP モー ド ま たは SDP モー ド で使用す る かは、 Vivado®

ツールが自動で決定 し ます。

• ビル ト イ ン FIFO と IP FIFO が可能な限 り 協調動作する よ う に改善 さ れま し た。 こ れに よ り 、 ソ フ ト FIFO と ハー ド FIFO の イ ンプ リ メ ン テーシ ョ ンの切 り 替えが容易にな り ま し た。

• 複数の FIFO36 および FIFO18 のカ ス ケー ド 接続がサポー ト さ れ、 ハー ド ウ ェ アで よ り 深い FIFO を構築で き ます。 • 従来世代の非同期 リ セ ッ ト に代わ り 、 同期 FIFO リ セ ッ ト が追加 さ れま し た。 • 書 き 込み動作時の EMPTY/PROGEMPTY フ ラ グのデ ィ アサー ト 、 およ び読み出 し 動作時の FULL/PROGFULL フ ラ グのデ ィ アサー ト ま での FIFO レ イ テ ン シが変更 さ れま し た。 • リ セ ッ ト 中の WRERR および RDERR の動作が変更 さ れま し た。 • FIFO の非対称ポー ト がサポー ト さ れ ま し た。 書 き 込みポー ト と 読み出 し ポー ト を、 FIFO36E2 の場合は x4、 x9、 表 1-1: パ リ テ ィ ビ ッ ト の使用法 プ リ ミ テ ィ ブ 設定 有効な読み出 し 幅 有効な書き込み幅 読み出 し 幅 書き込み幅 RAMB18E2 1、 2、 4 9、 18 設定幅 と 同一 8、 16 RAMB18E2 9、 18 1、 2、 4 8、 16 設定幅 と 同一 RAMB18E2 1、 2、 4 1、 2、 4 設定幅 と 同一 設定幅 と 同一 RAMB18E2 9、 18 9、 18 設定幅 と 同一 設定幅 と 同一 RAMB36E2 1、 2、 4 9、 18、 36 設定幅 と 同一 8、 16、 32 RAMB36E2 9、 18、 36 1、 2、 4 8、 16、 32 設定幅 と 同一 RAMB36E2 1、 2、 4 1、 2、 4 設定幅 と 同一 設定幅 と 同一 RAMB36E2 9、 18、 36 9、 18、 36 設定幅 と 同一 設定幅 と 同一 注記: 1. 一方のポー ト 幅が 9 よ り 小 さ く 、 も う 一方が 9 以上の場合、 パ リ テ ィ ビ ッ ト DINP/DOUTP は使用 し ないで く だ さ い。

• WRCOUNT お よ び RDCOUNT がサポー ト す る ユーザー選択可能な機能が増え ま し た。

• ブ ロ ッ ク RAM の ECC にパ イ プ ラ イ ン レ ジ ス タ が追加 さ れ、 FMAX が向上 し ま し た。 • ハー ド ウ ェ ア FIFO は、 7 シ リ ーズの FIFO と 下位互換性があ り ません。

ブ ロ ッ ク RAM の説明

UltraScale アーキ テ ク チ ャ デバ イ ス には、 分散 RAM お よ び高速 SelectIO™ メ モ リ イ ン タ ーフ ェ イ ス だけでな く 、 多 数の 36Kb ブ ロ ッ ク RAM が備わっ ています。 各 36Kb ブ ロ ッ ク RAM には、 独立 し て制御 さ れ る 2 つの 18Kb RAM が あ り ます。 ブ ロ ッ ク RAM は、 デバ イ ス全体で ク ロ ッ ク 領域 (CR) 内にカ ラ ム状に配置 さ れます。 ブ ロ ッ ク RAM の デー タ 出力ブ ロ ッ ク を カ ス ケー ド 接続す る こ と で ビ ッ ト 数 と ワー ド 数の多い メ モ リ が イ ンプ リ メ ン ト で き る ほか、 消費電力を抑え る ス リ ープ モー ド 、 選択可能な書き込み動作モー ド を備えてい ます。

同期デ ュ アル ポー ト およびシ ングル ポー ト RAM

デー タ フ ロー

36Kb の TDP ブ ロ ッ ク RAM は、 36Kb の記憶領域 と 完全に独立 し た 2 つのア ク セ ス ポー ト (A お よ び B) で構成 さ れ てい ます。 同様に、 各 18Kb ブ ロ ッ ク RAM のデュ アル ポー ト メ モ リ は、 18Kb の記憶領域 と 完全に独立し た 2 つの ア ク セ ス ポー ト (A および B) で構成 さ れてい ます。 構造は完全に対称で、 両ポー ト は交換可能です。図 1-1 に RAMB36 の TDP のデー タ フ ロ ーを示 し ます。表 1-2 にポー ト の機能 と その説明を示 し ます。 デー タ の書 き 込み/読み出 し は、 いずれか一方のポー ト ま たは両方のポー ト で実行で き ます。 書き込みは、 それぞれ ク ロ ッ ク に同期 し て実行 さ れ、 各ポー ト には、 ア ド レ ス、 デー タ 入力、 デー タ 出力、 ク ロ ッ ク 、 ク ロ ッ ク イ ネーブ ル、 ラ イ ト イ ネーブルが含まれます。 読み出 し およ び書き込みは同期で実行 さ れます。 そのため、 1 つの ク ロ ッ ク エ ッ ジが必要です。 両方のポー ト で同 じ ア ド レ ス にア ク セ ス し た際に、 その調整を行 う 専用モニ タ ーはあ り ません。 重要: こ れら 2 つの ク ロ ッ ク の タ イ ミ ング を適切に調整する必要があ り ます。 同じ ア ド レ スに同時に書き込みを実行 し た場合、 物理的な破損はあ り ませんが、 書 き 込まれたデー タ は不確定にな り ます。 注記: Vivado ツールは、 ブ ロ ッ ク RAM が SDP モー ド ま たは TDP モー ド で使用 さ れてい る かを自動で判断し ます。X-Ref Target - Figure 1-1 図 1-1: RAMB36 を TDP モー ド で使用 し た場合のデー タ フ ロー DOUTPA DINPA ADDRA WEA ENA CASDOUTPB CASDOUTB RSTRAMA CLKA RSTREGA ARST_A REGCEA Sleep REGCEB DINPB ADDRB WEB ENB RSTRAMB RSTREGB CLKB

36-Kbit Block RAM

DOUTPB DOUTB DOUTA DINA DINB ARST_B 36 Kb Memory Array Port A 32 4 32 4 15 4 32 32 4 32 4 4 15 4 32 4 Port B CASDOUTPA CASDOUTA CASDINPB CASDINB 32 4 32 4 CASDINPA CASDINA X17295-020419

読み出 し

ラ ッ チ モー ド の読み出 し は、 ク ロ ッ ク エ ッ ジに同期 し て実行 さ れます。 読み出 し ア ド レ ス が読み出 し ポー ト に取 り 込ま れてか ら 、 RAM ア ク セ ス時間の後に、 格納 さ れたデータ が出力 ラ ッ チに読み込まれます。 出力レ ジ ス タ を使用 し た場合は、 読み出 し の レ イ テ ン シが 1 ク ロ ッ ク サ イ ク ル増加し ます。書き込み

書 き 込みは、 ク ロ ッ ク エ ッ ジに同期 し て実行 さ れます。 書き込みア ド レ スは書き込みポー ト に取 り 込まれ、 入力 デー タ が メ モ リ に格納 さ れます。 表 1-2: TDP モー ド でのポー ト の機能および説明 ポー ト 名 説明 DIN[A|B] デー タ 入力バ ス。 DINP[A|B](1) デー タ 入力パ リ テ ィ バス で、 追加データ 入力に使用で き ます。 ADDR[A|B] ア ド レ ス バス。 ADDREN[A|B] ア ド レ ス ラ ッ チ イ ネーブル。 Low の場合は、 前のア ド レ ス が ラ ッ チ さ れた ま ま と な り ます。 WE[A|B] バ イ ト ラ イ ト イ ネーブル。 EN[A|B] 非ア ク テ ィ ブの場合、 ブ ロ ッ ク RAM にデータ は書き込まれず、 出力バス が以前の状態 に保持 さ れます。RSTREG[A|B] 出力レ ジ ス タ の同期セ ッ ト / リ セ ッ ト (DO_REG = 1)。 REGCE よ り も 優先する かど う か は、 RSTREG_PRIORITY 属性で設定 し ます。 RSTRAM[A|B] 出力デー タ ラ ッ チの同期セ ッ ト / リ セ ッ ト 。 CLK[A|B] ク ロ ッ ク 入力。 DOUT[A|B] デー タ 出力バ ス。 DOUTP[A|B](1) デー タ 出力パ リ テ ィ バス で、 追加データ 出力に使用で き ます。 REGCE[A|B] 出力レ ジ ス タ ク ロ ッ ク イ ネーブル。 CASDIN[A|B] カ ス ケー ド データ 入力バス。 CASDINP[A|B] カ ス ケー ド パ リ テ ィ 入力バス。 CASDOUT[A|B] カ ス ケー ド データ 出力バス。 CASDOUTP[A|B] カ ス ケー ド パ リ テ ィ 出力バス。 SLEEP 動的シ ャ ッ ト ダ ウ ンに よ る 消費電力削減。 SLEEP がア ク テ ィ ブな場合、 ブ ロ ッ ク は省電 力モー ド です。 注記:

1. デー タ パ リ テ ィ ピ ン の詳細は、32 ページの 「デー タ 入力バ ス – DINADIN、 DINPADINP、 DINBDIN、 DINPBDINP」 を参照 し

て く だ さ い。

2. ブ ロ ッ ク RAM プ リ ミ テ ィ ブのポー ト 名 と ポー ト 機能名は異な る こ と があ り ます。

3. カ ス ケー ド 接続 し た場合のデー タ フ ロ ーお よ びポー ト の詳細は、17 ページの 「カ ス ケー ド 接続可能なブ ロ ッ ク RAM」 お よ び

書き込みモー ド

書 き 込み ク ロ ッ ク エ ッ ジ後の出力 ラ ッ チのデータ は、 WRITE_FIRST、 READ_FIRST、 NO_CHANGE の 3 つの書き込 みモー ド のいずれを設定す る かで決定 し ます。 こ のモー ド は、 コ ン フ ィ ギ ュ レーシ ョ ンで設定 し ます。 各ポー ト に 対 し て別々の書 き 込みモー ド を設定で き 、 デフ ォ ル ト のモー ド は WRITE_FIRST です。 WRITE_FIRST では新たな デー タ が書 き 込まれ る と 同時に、 その新規デー タ が出力バ ス に送信 さ れ、 READ_FIRST ではあ ら か じ め保存 さ れて い る デー タ が出力 さ れます。 NO_CHANGE では、 前回の読み出 し 処理の出力がその ま ま送信 さ れます。

WRITE_FIRST ま たは透過モー ド (デ フ ォル ト )

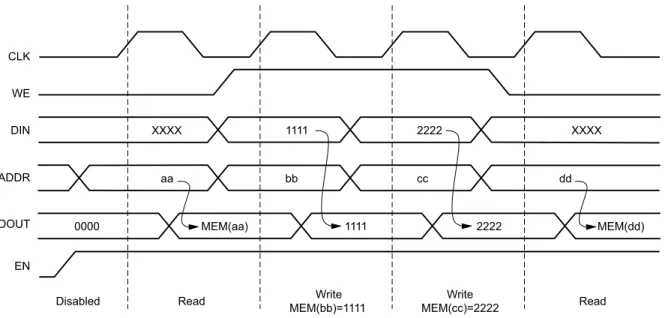

図 1-2 に示す よ う に、 WRITE_FIRST モー ド では入力デー タ を メ モ リ に書 き 込む と 同時にデー タ 出力に も 格納 さ れ ま す (透過書き込み)。 こ こ に示す波形は、 オプシ ョ ンの出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ない ラ ッ チ モー ド の場合 です。X-Ref Target - Figure 1-2

図 1-2: WRITE_FIRST モー ド での波形 CLK WE DIN ADDR DOUT EN Disabled Read XXXX 1111 2222 XXXX aa bb cc dd 0000 MEM(aa) 1111 2222 MEM(dd) Read Write MEM(bb)=1111 Write MEM(cc)=2222 X17296-020419

READ_FIRST または書き込み前読み出 し モー ド

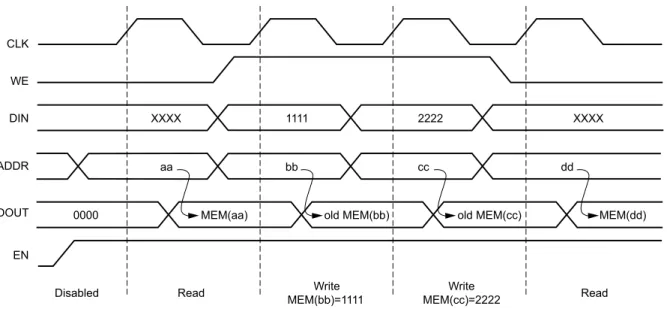

READ_FIRST モー ド では、 書 き 込み先ア ド レ ス に格納 さ れていたデー タ が出力 ラ ッ チに送信 さ れ、 それ と 同時に入 力デー タ が メ モ リ に格納 さ れます (書き込み前に読み込み)。図 1-3 の波形は、 オプシ ョ ン の出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ない ラ ッ チ モー ド の場合を示 し てい ます。

X-Ref Target - Figure 1-3

図 1-3: READ_FIRST モー ド での波形 CLK WE DIN ADDR DOUT EN Disabled Read XXXX 1111 2222 XXXX aa bb cc dd

0000 MEM(aa) old MEM(bb) old MEM(cc) MEM(dd)

Read Write MEM(bb)=1111 Write MEM(cc)=2222 X17297-020419

NO_CHANGE モー ド

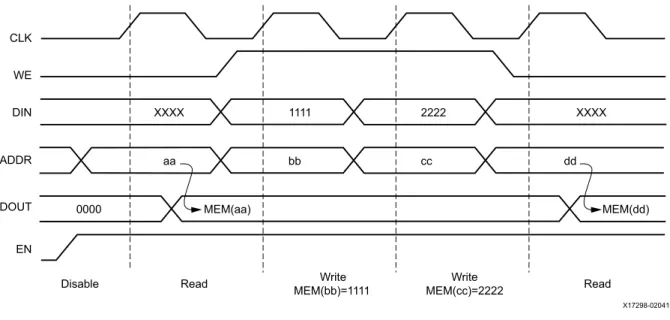

NO_CHANGE モー ド では、 書 き 込み中、 出力 ラ ッ チは変化 し ません。図 1-4 に示す よ う に、 デー タ 出力には最後に 読み込ま れたデー タ がその ま ま維持 さ れ、 同 じ ポー ト での書 き 込みに影響 さ れません。 こ こ に示す波形は、 オプ シ ョ ンの出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ない ラ ッ チ モー ド の場合です。 こ のモー ド が最 も 消費電力を削減で き ます。ア ド レ ス競合

ア ド レ ス競合 と は、 ブ ロ ッ ク RAM の両方のポー ト が同 じ ク ロ ッ ク サ イ ク ルで 1 つのア ド レ ス にア ク セ ス し た場合を いい ます。 基本的な ク ロ ッ ク タ イ プには、 共通 ク ロ ッ ク と 独立 ク ロ ッ ク の 2 種類があ り ます。 共通 (同期) ク ロ ッ ク は、 共通の ク ロ ッ ク バ ッ フ ァ ー ド ラ イ バーで駆動 し ます。 CLKA と CLKB を それ以外の接続 と し た場合は、 独立 (非同期) ク ロ ッ ク と な り ます。 CLOCK_DOMAINS 属性 も 適切に設定す る 必要があ り ます。 有効な値お よ びデフ ォ ル ト 値は、表 1-16 を参照 し て く だ さ い。 ア ド レ ス競合が発生す る 可能性のない場合 (SDP 構成)、 消費電力を削減す る ために書 き 込みモー ド を NO_CHANGE に設定する こ と を推奨し ます。 READ_FIRST モー ド は NO_CHANGE モー ド よ り も 消費電力が 15% 増え る ため、 ア ド レ ス競合を軽減する場合な ど、 機能上の必要があ る場合のみ使用 し て く だ さ い。 • 両方のポー ト が読み出 し を実行 し た場合、 動作は正 し く 完了 し ます。 • 両方のポー ト が異な る デー タ を書 き 込んだ場合、 こ の メ モ リ ア ド レ ス に書き込まれ るデータ は確定で き ません。 • 片方のポー ト が書 き 込みを実行 し 、 も う 一方のポー ト が読み出 し を実行 し た場合、 書 き 込みは常に正 し く 完了 し ますが、 メ モ リ の読み出 し 値は条件に よ っ て異な り ます。表 1-3 お よ び表 1-4 を参照 し て く だ さ い。 表 1-3 お よ び表 1-4 について説明 し ます。 • ラ イ ト イ ネーブルはア ク テ ィ ブ High です (1 = 書き込み、 0 = 読み出 し )。 • RF = READ_FIRST、 WF = WRITE_FIRST、 NC = NO_CHANGE• X = 不定値

X-Ref Target - Figure 1-4

図 1-4: NO_CHANGE モー ド での波形 CLK WE DIN ADDR DOUT EN Disable Read XXXX 1111 2222 XXXX aa bb cc dd 0000 MEM(aa) MEM(dd) Read Write MEM(bb)=1111 Write MEM(cc)=2222 X17298-020419

注記: 共通 ク ロ ッ ク のア ド レ ス競合 と は、 同 じ ク ロ ッ ク サ イ ク ルでポー ト ア ド レ ス が同 じ場合をいい ます。 注記: 独立 ク ロ ッ ク のア ク セ ス競合は、 ポー ト ア ド レ ス が同 じ で、 2 つのポー ト の ク ロ ッ ク エ ッ ジが同 じ ク ロ ッ ク サ イ ク ル内にあ る 場合に発生す る 可能性があ り ます。 SIM_COLLISION_CHECK 属性を ALL (デフ ォ ル ト 値) に設定 す る と 、 シ ミ ュ レーシ ョ ン中にア ド レ ス競合が発生 し た場合、 UNISIM でエ ラ ーを報告で き ます。 表 1-3: 共通ク ロ ッ ク ク ロ ッ ク タ イ プ 書き込み モー ド ポー ト A 書き込み モー ド ポー ト B ラ イ ト イ ネーブル ポー ト A (デー タ ) ラ イ ト イ ネーブル ポー ト B (デー タ ) ポー ト A からの 出力デー タ ポー ト B からの 出力デー タ 最終的な メ モ リ の値 共通 RF/WF/NC RF/WF/NC 0 0 古い メ モ リ データ 古い メ モ リ データ 変更な し 共通 RF RF/WF/NC 1 (DIA) 0 古い メ モ リ データ 古い メ モ リ データ DIA

共通 WF RF/WF/NC 1 (DIA) 0 DIA X DIA

共通 NC RF/WF/NC 1 (DIA) 0 変更な し X DIA

共通 RF/WF/NC RF 0 1 (DIB) 古い メ モ リ データ 古い メ モ リ データ DIB

共通 RF/WF/NC WF 0 1 (DIB) X DIB DIB

共通 RF/WF/NC NC 0 1 (DIB) X 変更な し DIB 共通 RF/WF/NC RF/WF/NC 1 1 X X X 表 1-4: 独立ク ロ ッ ク ク ロ ッ ク タ イ プ 書き込み モー ド ポー ト A 書き込み モー ド ポー ト B ラ イ ト イ ネーブル ポー ト A (デー タ ) ラ イ ト イ ネーブル ポー ト B (デー タ ) ポー ト A からの 出力デー タ ポー ト B からの 出力デー タ 最終的な メ モ リ の値 独立 RF/WF/NC RF/WF/NC 0 0 古い メ モ リ データ 古い メ モ リ データ 変更な し 独立 RF RF/WF/NC 1 (DIA) 0 古い メ モ リ データ X DIA

独立 WF RF/WF/NC 1 (DIA) 0 DIA X DIA

独立 NC RF/WF/NC 1 (DIA) 0 変更な し X DIA

独立 RF/WF/NC RF 0 1 (DIB) X 古い メ モ リ データ DIB

独立 RF/WF/NC WF 0 1 (DIB) X DIB DIB

独立 RF/WF/NC NC 0 1 (DIB) X 変更な し DIB

ブ ロ ッ ク RAM のその他の機能

出力レ ジス タ (オプシ ョ ン)

オプシ ョ ンの出力レ ジ ス タ を使用す る と 、 パ イ プ ラ イ ン処理におけ る コ ン フ ィ ギ ャ ラ ブル ロ ジ ッ ク ブ ロ ッ ク (CLB) フ リ ッ プ フ ロ ッ プへの配線遅延が削減 さ れ、 デザ イ ンのパフ ォーマ ン ス が向上 し ます。 こ れ ら の出力レ ジ ス タ には、 独立 し た ク ロ ッ ク お よ び ク ロ ッ ク イ ネーブルの入力が供給 さ れ る ため、 入力レ ジ ス タ の動作か ら 独立 し た値が保持 で き ます。図 1-5 にオプシ ョ ン の出力レ ジ ス タ を示 し ます。個別に選択可能な読み出 し ポー ト と 書き込みポー ト の幅

各ブ ロ ッ ク RAM ポー ト では、 データ 幅 と ア ド レ ス幅 (ア スペ ク ト 比) を制御で き ます。 TDP モー ド のブ ロ ッ ク RAM では こ の機能が拡張 さ れ、 各ポー ト での読み出 し お よ び書 き 込みに異な る デー タ ビ ッ ト 幅を設定で き る よ う にな っ てい ます。 た と えば、 ポー ト A が 36 ビ ッ ト の読み出 し 幅 と 9 ビ ッ ト の書き込み幅を持ち、 ポー ト B が 18 ビ ッ ト の 読み出 し 幅 と 36 ビ ッ ト の書き込み幅を持つよ う 設定可能です。 読み出 し ポー ト と 書 き 込みポー ト の幅が異な っ ていて、 WRITE_FIRST モー ド が設定 さ れてい る場合、 有効なすべて の書 き 込みバ イ ト に対 し て、 DOUT には有効な新規データ が現れます。 有効 と な っ ていないすべてのバ イ ト に対 し ては、 メ モ リ に保存 さ れた以前のデー タ が DOUT ポー ト に出力 さ れます。読み出 し ポー ト と 書 き 込みポー ト の幅を個別に設定で き る こ と に よ り 、 ブ ロ ッ ク RAM に CAM (Content Addressable Memory) を効率的に イ ン プ リ メ ン ト で き ます。 こ のオプシ ョ ンは、 UltraScale アーキ テ ク チ ャ デバ イ ス のブ ロ ッ ク RAM を TDP モー ド と し た場合、 すべてのポー ト サ イ ズ と モー ド で使用可能です。

X-Ref Target - Figure 1-5

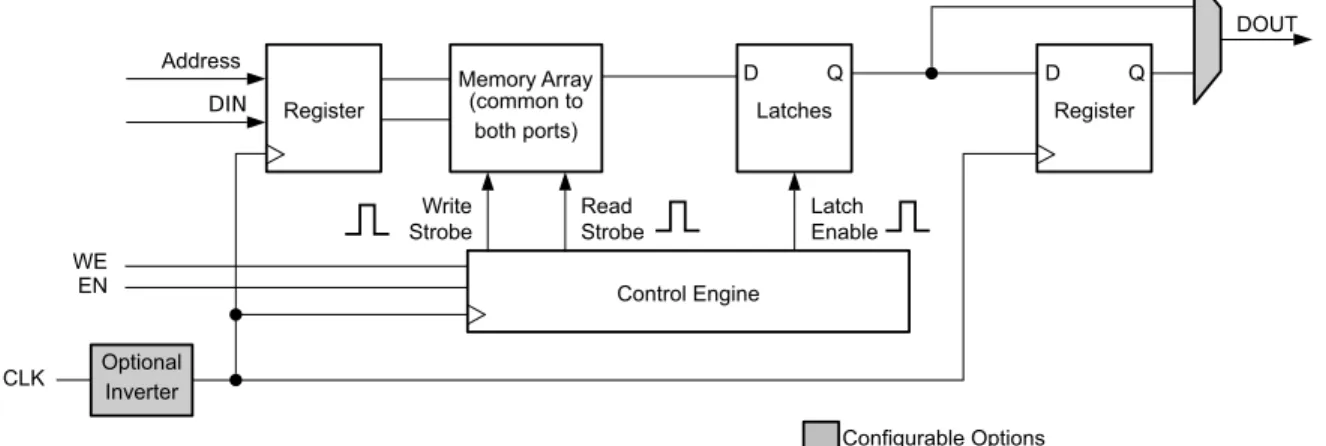

図 1-5: ブ ロ ッ ク RAM の論理図 (1 ポー ト のみ表示)

Optional Inverter

Register Latches Register

Control Engine WE EN CLK Write Strobe Read Strobe Q D D Q Configurable Options Memory Array (common to both ports) Latch Enable Address DIN DOUT X17299-020419

シ ン プル デ ュ アル ポー ト ブ ロ ッ ク RAM

18Kb ブ ロ ッ ク お よ び 36Kb ブ ロ ッ ク はそれぞれ、 SDP RAM モー ド と し て も 構成で き ます。 こ のモー ド では、 ブ ロ ッ ク RAM のポー ト 幅が 2 倍にな り 、18Kb ブ ロ ッ ク RAM では 36 ビ ッ ト 、36Kb ブ ロ ッ ク RAM では 72 ビ ッ ト と な り ま す。 ブ ロ ッ ク RAM を SDP メ モ リ と し て使用する場合、 ポー ト A を書き込みポー ト 、 ポー ト B を読み出 し ポー ト と し 、 読み出 し と 書 き 込みを同時に独立 し て実行で き ます。 読み出 し ポー ト と 書 き 込みポー ト が同 じ デー タ 位置に同 時にア ク セ スす る と 、 TDP モー ド のポー ト 競合 と 同様に競合が発生 し ます。 UltraScale アーキテ ク チ ャ デバ イ スは、 ブ ロ ッ ク RAM を SDP メ モ リ と し て使用 し た場合、 READ_FIRST、 WRITE_FIRST、 NO_CHANGE モー ド をサポー ト

し ます。

図 1-6 に、 ブ ロ ッ ク RAM を シ ン プル デ ュ アル ポー ト メ モ リ と し て使用 し た場合の RAMB36 のデー タ フ ロ ーを示 し ます。

X-Ref Target - Figure 1-6

図 1-6: RAMB36 を シ ン プル デ ュ アル ポー ト メ モ リ と し て使用 し た場合のデー タ フ ロー 36 Kb Memory Array DOUT RDEN RDADDR RDCLK REGCE DINP WRADDR WE WRCLK WREN DIN 64 8 8 15 15 64 DOUTP 8 RSTREG CASDOUTP CASDOUT 32 4 Sleep 32 4 CASDINP CASDIN ARST_B RSTRAM X17300-020419

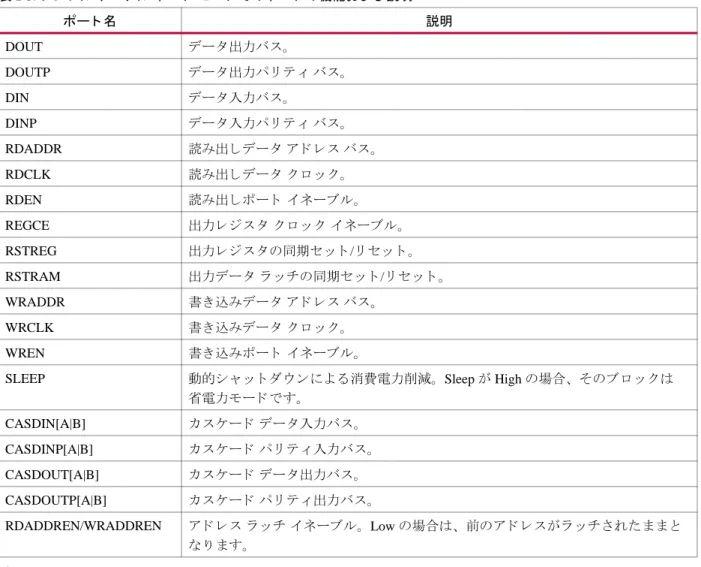

表 1-5 に、 シ ン プル デ ュ アル ポー ト メ モ リ と し て使用 し た場合の各ポー ト の機能 と その説明を示 し ます。

カ スケー ド 接続可能な ブ ロ ッ ク RAM

UltraScale アーキ テ ク チ ャ デバ イ ス は、 1 つの RAMB36 のデー タ 出力を次の RAMB36 に直列にカ ス ケー ド 接続 し て、 ボ ト ム ア ッ プ方式で よ り ワー ド 数の大 き いブ ロ ッ ク RAM を構築で き ます。 データ 出力を カ ス ケー ド 接続する こ の機 能は、 RAMB36 のすべてのポー ト 幅でサポー ト さ れます。 RAMB36E2 モジ ュールがサポー ト し てい る機能はすべ て、 カ ス ケー ド 接続 し たブ ロ ッ ク RAM で も 利用で き ます。 注記: 旧世代のアーキテ ク チ ャ でサポー ト さ れていた 64Kx1 のカ ス ケー ド 接続は廃止 さ れま し た。 新 し いカ ス ケー ド 接続の イ ンプ リ メ ン テーシ ョ ンで も 、 64Kx1 のカ ス ケー ド 接続 と 同じ 機能が得 ら れます。 表 1-5: シ ン プル デ ュ アル ポー ト モー ド でのポー ト の機能および説明 ポー ト 名 説明 DOUT デー タ 出力バ ス。 DOUTP デー タ 出力パ リ テ ィ バス。 DIN デー タ 入力バ ス。 DINP デー タ 入力パ リ テ ィ バス。 RDADDR 読み出 し デー タ ア ド レ ス バス。 RDCLK 読み出 し デー タ ク ロ ッ ク 。 RDEN 読み出 し ポー ト イ ネーブル。 REGCE 出力レ ジ ス タ ク ロ ッ ク イ ネーブル。 RSTREG 出力レ ジ ス タ の同期セ ッ ト / リ セ ッ ト 。 RSTRAM 出力デー タ ラ ッ チの同期セ ッ ト / リ セ ッ ト 。 WRADDR 書 き 込みデー タ ア ド レ ス バス。 WRCLK 書 き 込みデー タ ク ロ ッ ク 。 WREN 書 き 込みポー ト イ ネーブル。

SLEEP 動的シ ャ ッ ト ダ ウ ンに よ る 消費電力削減。 Sleep が High の場合、 そのブ ロ ッ ク は 省電力モー ド です。 CASDIN[A|B] カ ス ケー ド データ 入力バス。 CASDINP[A|B] カ ス ケー ド パ リ テ ィ 入力バス。 CASDOUT[A|B] カ ス ケー ド データ 出力バス。 CASDOUTP[A|B] カ ス ケー ド パ リ テ ィ 出力バス。 RDADDREN/WRADDREN ア ド レ ス ラ ッ チ イ ネーブル。 Low の場合は、 前のア ド レ ス が ラ ッ チ さ れた ま ま と な り ます。 注記: 1. カ ス ケー ド 接続 し た場合のデー タ フ ロ ーお よ びポー ト の詳細は、17 ページの 「カ ス ケー ド 接続可能なブ ロ ッ ク RAM」 お よ び 25 ページの 「ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ」 を参照 し て く だ さ い。

デー タ フ ロ ーは、 常に下段のブ ロ ッ ク RAM か ら 上段のブ ロ ッ ク RAM への方向です。 カ ス ケー ド 接続に使用する信 号配線お よ び制御 ロ ジ ッ ク はすべてハー ド ウ ェ アで実装 さ れます。 必要に応 じ て 3 つ以上のブ ロ ッ ク RAM を カ ス ケー ド 接続す る こ と も 可能です。 カ ス ケー ド モー ド では、 1 つの共通 ク ロ ッ ク ソ ース に よ っ て同 じ ブ ロ ッ ク RAM 入 力 (RDCLK ま たは WRCLK) を駆動する必要があ り ます。 ま た、 こ のデータ カ ス ケー ド 機能では下段の RAMB36 の 下側の RAMB18 を上段の RAMB36 の下側の RAMB18 に独立 し て カ ス ケー ド 接続する こ と も で き ます。 同様に、 下 段の RAMB36 の上側の RAMB18 は上段の RAMB36 の上側の RAMB18 にカ ス ケー ド 接続で き ます。

重要: 1 つのカ ス ケー ド チェーンに接続さ れたすべてのブ ロ ッ ク RAM は、 ポー ト 幅な どの共通入力を同じ にする な ど、 各機能の設定を揃え てお く 必要があ り ます。

図 1-7 に、 4 つのブ ロ ッ ク RAM を カ ス ケー ド 接続 し た場合の概念図を示 し ます。

ブ ロ ッ ク RAM は、 カ ス ケー ド 接続機能を さ ま ざ ま な構成で柔軟に イ ンプ リ メ ン ト で き ます。 データ パスおよ びパ イ プ ラ イ ン レ ジ ス タ を選択する 3 つのマルチプ レ ク サーは、 入力ピ ンで動的に制御で き ます (図 1-7 参照)。

X-Ref Target - Figure 1-7

図 1-7: ブ ロ ッ ク RAM のカ スケー ド アーキテ ク チ ャの概略図

BRAM3 Final

Output Data to the Next Block RAM

Data From the Previous Block RAM DOUTx CLK DINx D Q CASOREGIMUX CASDOMUX BRAM2 Final Output DOUTx CLK DINx D Q BRAM1 Final Output DOUTx CLK DINx D Q BRAM0 Final Output DOUTx CLK DINx D Q X17301-020419

図 1-8 は、 1 つのブ ロ ッ ク RAM ブ ロ ッ ク におけ る 機能 イ ン プ リ メ ン テーシ ョ ン を さ ら に詳 し く 示 し た も のです。 ブ ロ ッ ク RAM を カ ス ケー ド モー ド にする と 、 3 つのカ ス ケー ド マルチプ レ ク サー選択ピ ンが利用可能にな り ます。 CASDIMUX は、 カ ス ケー ド 入力デー タ か直接デー タ 入力か を選択 し ます。 CASOREGIMUX は、 ブ ロ ッ ク RAM の デー タ 出力 と カ ス ケー ド データ 入力のど ち ら をオプシ ョ ンの出力レ ジ ス タ に入力する かを選択 し ます。 こ の制御ピ ン を利用 し て カ ス ケー ド 接続をパ イ プ ラ イ ン化す る こ と で、 パフ ォーマ ン ス を最大にで き ます。 CASDOMUX は、 ブ ロ ッ ク RAM のデー タ出力 (オプシ ョ ンの出力レ ジ ス タ を使用する場合はその出力) と カ ス ケー ド データ 入力のど ち ら を出力す る か を選択 し ます。 最後の 2 つのカ ス ケー ド マルチプ レ ク サー選択ピ ンの入力にはレ ジ ス タ がついて お り 、 イ ネーブル制御ピ ンがあ り ます。 CASDOUT お よび CASDIN には、 ブ ロ ッ ク RAM カ ラ ム内に専用の イ ン タ ー コ ネ ク ト があ り ます。 カ ス ケー ド 接続は、 ブ ロ ッ ク RAM へのデータ 入力およ びブ ロ ッ ク RAM か ら のデータ 出力 と 同時に利用で き ます。 ブ ロ ッ ク RAM のデー タ カ ス ケー ド 機能を使用する と さ ま ざ ま なユース ケース を イ ンプ リ メ ン ト で き ますが、 こ こ では最 も 代表的な 3 つについて説明 し ます。 こ こ で示す例はいずれ も 3 つのブ ロ ッ ク RAM を カ ス ケー ド 接続 し てい ますが、 アプ リ ケーシ ョ ンでそれ以上のブ ロ ッ ク RAM が必要な場合は、 一部制約があ る も のの、 同じ 方法でブ ロ ッ ク RAM を追加で き ます。

標準デー タ 出力カ スケー ド モー ド

こ のカ ス ケー ド モー ド では、 下段のブ ロ ッ ク RAM のデータ 出力を上段のブ ロ ッ ク RAM の最終出力マルチプ レ ク サーに入力 し ます (図 1-9 参照)。 こ のカ ス ケー ド 接続は、 ブ ロ ッ ク RAM の カ ラ ム全体に適用で き ます。 こ のモー ド では、 わずかな ロ ジ ッ ク リ ソ ース を使用する だけで非常に ワー ド 数の多い RAM を イ ンプ リ メ ン ト で き ます。 必要 な ロ ジ ッ ク リ ソ ースは、 EN ピ ン を駆動する ロ ジ ッ ク 、 ブ ロ ッ ク RAM のピ ン を駆動する ロ ジ ッ ク 、 カ ス ケー ド マル チプ レ ク サーのセ レ ク ト 値を正 し く 決定す る ための ロ ジ ッ ク 、 そ し て DO_REG を使用する場合はデータ ア ラ イ メ ン ト のための ロ ジ ッ ク のみです。 入力マルチプ レ ク サーはブ ロ ッ ク RAM への書き込みデータ に常に DIN を選択し 、X-Ref Target - Figure 1-8

図 1-8: カ スケー ド 接続の機能ブ ロ ッ ク図 OREG (FF) EN, ADDR, WE DIN CASDOMUX CASDOMUXEN CASDOUT Attribute DO_REG REGCE Block RAM 0 1 0 1 0 D FF Q D FF Q D EN FF O D EN FF O 1 CASOREGIMUX CASOREGIMUXEN CASDIN DOUT X17302-020419

RAM か ら のカ ス ケー ド デー タ のいずれか を選択 し ます。 ブ ロ ッ ク RAM のチ ェ ーン の長 さ は最終的な Clock-to-Out パフ ォーマ ン ス に影響す る ため、 カ ス ケー ド 接続す る ブ ロ ッ ク RAM の数に よ っ てはパフ ォーマン ス が低下する こ と があ り ます。 ブ ロ ッ ク RAM の機能はすべてサポー ト さ れます。

重要: ブ ロ ッ ク RAM カ ラ ム内での配置順は CASCADE_ORDER 属性で指定し、 オプシ ョ ンのブ ロ ッ ク RAM レ ジ ス タ を使用す る か ど う かは DO_REG 属性で指定 し ます。

X-Ref Target - Figure 1-9

図 1-9: ブ ロ ッ ク RAM のカ スケー ド 接続 – 標準デー タ 出力カ スケー ド モー ド Block RAM 2 Optional Register DIN2 DO_REG CASDOMUX CASDIN CASCADE_ORDER = LAST 0 1 0 1 0 1 DOUT CASCADE_ORDER = MIDDLE CASDOUT CASDIN CASCADE_ORDER = FIRST Block RAM 1 Optional Register DIN1 DO_REG CASDOMUX 0 1 0 1 0 1 CASDOUT Block RAM 0 Optional Register DIN0 DO_REG 0 1 0 1 0 1 X17303-020419

パイ プ ラ イ ン モー ド のデー タ 出力カ スケー ド

パ イ プ ラ イ ン カ ス ケー ド モー ド のブ ロ ッ ク RAM は標準モー ド と よ く 似てい ますが、 アプ リ ケーシ ョ ンでは よ り 高 い動作周波数でのカ ス ケー ド 接続が可能にな り ます (図 1-10 参照)。 こ のカ ス ケー ド モー ド では、 動作周波数を高め る ためにブ ロ ッ ク RAM の出力レ ジ ス タ をパ イ プ ラ イ ン ス テージ と し て使用 し てお り 、 カ ス ケー ド データ は こ の出 力レ ジ ス タ を経由 し て伝搬 し ます。 オプシ ョ ンの レ ジ ス タ への入力を選択す る マルチプ レ ク サーは、 外部ピ ンの CASOREGIMUX で制御 し ます。 こ れに よ り 、 下段のブ ロ ッ ク RAM ま たは現在のブ ロ ッ ク RAM か ら のデー タ を出 力レ ジ ス タ に格納で き ます。 入力マルチプ レ ク サーはブ ロ ッ ク RAM への書き込みデータ に常に DIN を選択し 、 ブ ロ ッ ク RAM の出力マルチプ レ ク サーはブ ロ ッ ク RAM の出力データ ま たは下段のブ ロ ッ ク RAM か ら のカ ス ケー ド デー タ のいずれか を選択 し て レ ジ ス タ に書 き 込みます。 カ ス ケー ド ス テージ ご と の最終出力マルチプ レ ク サーは常 に レ ジ ス タ か ら のデー タ を選択 し て最終デー タ と し て出力 し ます。 こ のモー ド では、 すべての DO_REG 属性を TRUE に設定す る 必要があ り ます。 こ のカ ス ケー ド モー ド では、 カ ス ケー ド チ ェ ーン の長 さ は 1 ク ロ ッ ク 領域以内 に制限 さ れます。

X-Ref Target - Figure 1-10

図 1-10: ブ ロ ッ ク RAM のカ スケー ド 接続 – パイ プ ラ イ ン デー タ 出力カ スケー ド モー ド Block RAM 2 Optional Register DIN2 DO_REG CASDIN CASCADE_ORDER = LAST 0 1 0 1 0 1 DOUT CASCADE_ORDER = FIRST CASOREGIMUXA Block RAM 1 Optional Register DIN1 DO_REG CASDIN CASCADE_ORDER = MIDDLE 0 1 0 1 0 1 CASDOUT CASOREGIMUXA Block RAM 0 Optional Register DIN0 DO_REG 0 1 0 1 0 1 CASDOUT X17304-020419

ブ ロ ッ ク RAM ア レ イ マ ト リ ク ス (シス ト リ ッ ク) モー ド のデー タ 入力カ スケー ド

ブ ロ ッ ク RAM シ ス ト リ ッ ク モー ド では、 アプ リ ケーシ ョ ンは入力データ ま たはカ ス ケー ド データ のいずれかをブ ロ ッ ク RAM に書き込む こ と がで き ます (図 1-11 参照)。 その 1 サ イ ク ル後に、 アプ リ ケーシ ョ ンは下段のブ ロ ッ ク RAM か ら のデー タ を読み出 し て上段のブ ロ ッ ク RAM に書 き 込む こ と がで き ます。 デー タ は、 カ ス ケー ド チ ェ ーン に接続 さ れたブ ロ ッ ク RAM を動的に選択し て読み出す こ と がで き ます。 入力マルチプ レ ク サーは、 DIN データ ま た は下段のブ ロ ッ ク RAM か ら のカ ス ケー ド データ 出力のいずれかを動的に選択 し て現在のブ ロ ッ ク RAM に書き込み ます。 ブ ロ ッ ク RAM 出力マルチプ レ ク サーは常にブ ロ ッ ク RAM の出力データ を選択し 、 直接ま たはオプシ ョ ンの レ ジ ス タ を経由 し て DOUT に出力 し ます。 オプシ ョ ンの レ ジ ス タ を使用する か ど う かは DO_REG 属性で決定 し ま す。 こ のカ ス ケー ド モー ド では、 カ ス ケー ド チ ェーンの長 さ は 1 ク ロ ッ ク 領域以内に制限 さ れます。X-Ref Target - Figure 1-11

図 1-11: ブ ロ ッ ク RAM のカ スケー ド 接続 – ア レ イ (シス ト リ ッ ク) デー タ 入力カ スケー ド モー ド Block RAM 2 Optional Register DIN2 DO_REG CASCADE_ORDER = LAST 0 1 0 1 0 1 DOUT CASCADE_ORDER = MIDDLE CASDOUT CASCADE_ORDER = FIRST Block RAM 1 Optional Register DIN1 DO_REG 0 1 0 1 0 1 CASDOUT Block RAM 0 Optional Register DIN0 DO_REG 0 1 0 1 0 1 X17305-020419

ア ド レ ス イ ネーブル

こ れは、 ア ド レ ス EN が High の と き のみ新 し いア ド レ ス を キ ャ プチ ャ する機能です。 ア ド レ ス EN が Low の場合は 前のア ド レ ス が内部で ラ ッ チ さ れた ま ま と な り 、 内部ア ク セ ス に使用 さ れます。 ア ド レ ス入力が変化は無視 さ れま す。 こ の機能は ENADDREN 属性で制御 し ます。図 1-12 を参照 し て く だ さ い。

X-Ref Target - Figure 1-12

図 1-12: ア ド レ ス ラ ッ チ イ ネーブル ADDR[0] Register ADDR[n] Register ADDR[0] ADDR[0] ADDR[n] ADDREN CLK 0 1 0 1 ADDR[N] X17306-020817

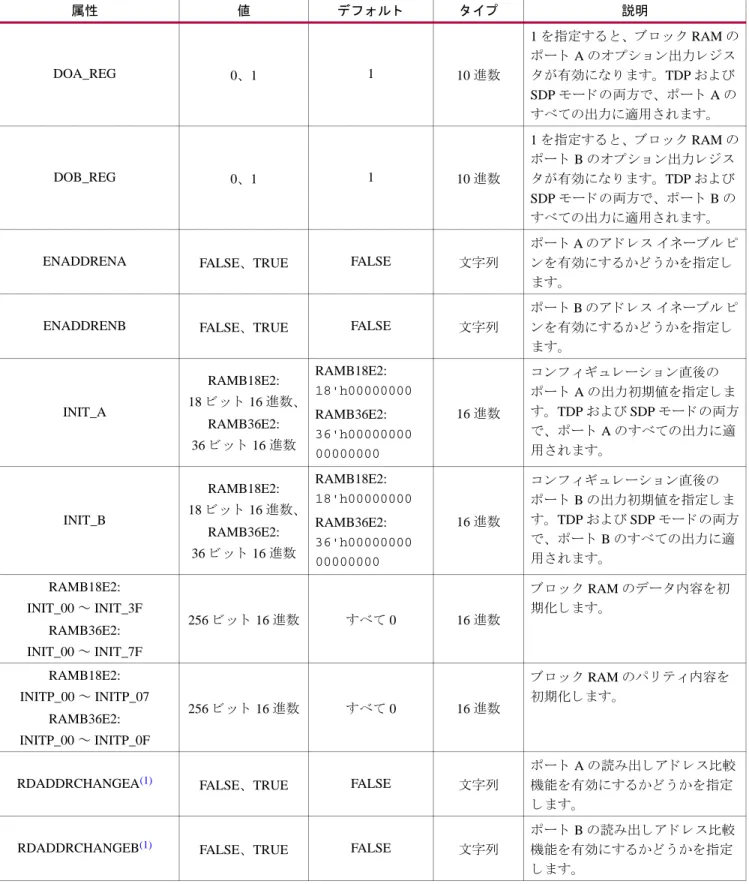

バイ ト ラ イ ト イ ネーブル

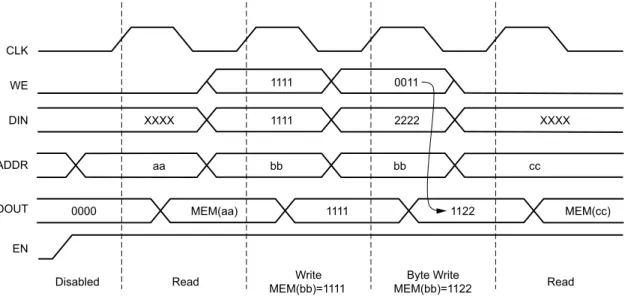

ブ ロ ッ ク RAM にはバ イ ト ラ イ ト イ ネーブル機能があ り 、 8 ビ ッ ト (1 バ イ ト ) 単位で入力データ を書き込む こ と がで き ます。 TDP モー ド の RAMB36E2 には、 4 つの独立 し たバ イ ト ラ イ ト イ ネーブル入力があ り ます。 TDP モー ド の RAMB36E2 にはポー ト A と ポー ト B の 2 つのポー ト があ り 、それぞれのポー ト に 4 ビ ッ ト の ラ イ ト イ ネーブル バ ス があ り ます (1 ビ ッ ト が各データ バ イ ト に対応)。 SDP モー ド の RAMB36E2 には書き込みポー ト が 1 つあ り 、 こ の ポー ト に 8 ビ ッ ト の ラ イ ト イ ネーブル バス があ り ます (1 ビ ッ ト が各データ バ イ ト に対応)。表 1-6 に、 36Kb お よ び 18Kb ブ ロ ッ ク RAM で利用で き る バ イ ト ラ イ ト イ ネーブルの数を示 し ます。 各バ イ ト ラ イ ト イ ネーブルは、 1 バ イ ト の入力デー タ と 1 パ リ テ ィ ビ ッ ト に対応し てい ます。 バ イ ト ラ イ ト イ ネーブル入力は、 データ 幅の設定に従っ て 駆動す る 必要があ り ます。 こ の機能は、 ブ ロ ッ ク RAM を使用し てマ イ ク ロ プ ロ セ ッ サ と 通信する際に役立ち ます。 バ イ ト ラ イ ト イ ネーブル機能は、 ECC モー ド では使用で き ません。 バ イ ト ラ イ ト イ ネーブルの詳細は、45 ページ の 「RAMB18E2 および RAMB36E2 プ リ ミ テ ィ ブの設計上のその他の注意事項」 を参照 し て く だ さ い。図 1-13 に、 RAMB36E2 のバ イ ト ラ イ ト イ ネーブルの タ イ ミ ン グ図を示 し ます。 RAMB36E2 で 36 ビ ッ ト 幅ま たは 18 ビ ッ ト 幅のデー タ パ ス を設定す る と 、 デー タ ワ ー ド 内で指定 し たバ イ ト 位置へ の書 き 込みを任意のポー ト で制御で き ます。 READ_FIRST モー ド の場合、 DOUT バス にはア ド レ ス指定 し た ワー ド 全体が書 き 込み前の内容で現れます。 WRITE_FIRST の場合は、 DOUT には新たに書き込まれた有効なバ イ ト と 未書 き 込みバ イ ト の メ モ リ の初期内容の組み合わせが出力 さ れます。X-Ref Target - Figure 1-13

図 1-13: バイ ト ラ イ ト 動作の波形 (x36 WRITE_FIRST) 表 1-6: 使用可能なバイ ト ラ イ ト イ ネーブル プ リ ミ テ ィ ブ 最大ビ ッ ト 幅 バイ ト ラ イ ト イ ネーブル数 TDP モー ド の RAMB36E2 36 4 SDP モー ド の RAMB36E2 72 8 TDP モー ド の RAMB18E2 18 2 SDP モー ド の RAMB18E2 36 4 CLK WE DIN ADDR DOUT EN Disabled Read XXXX 1111 2222 1111 0011 XXXX aa bb bb cc 0000 MEM(aa) 1111 1122 MEM(cc) Read Write MEM(bb)=1111 Byte Write MEM(bb)=1122 X17307-020419

ブ ロ ッ ク RAM の ECC (エ ラ ー訂正符号)

36Kb ブ ロ ッ ク RAM でのブ ロ ッ ク RAM お よ び FIFO イ ン プ リ メ ン テーシ ョ ン では、 64 ビ ッ ト の ECC を備え る こ と がで き ます。 こ の機能を使用す る と 、 ブ ロ ッ ク RAM の読み出し データ のシ ン グル ビ ッ ト およ びダブル ビ ッ ト エ ラ ーが検出で き ます。 シ ン グル ビ ッ ト エ ラ ーは出力データ で修正 さ れます。

未使用ブ ロ ッ ク RAM のパワー ゲーテ ィ ング

UltraScale アーキ テ ク チ ャ デバ イ ス は、未使用ま たは イ ン ス タ ン シエー ト さ れていないブ ロ ッ ク RAM の電源を 18Kb 単位で細か く 切断 し ます。 デザ イ ン内で イ ン ス タ ン シエー ト さ れていないすべての 18Kb ブ ロ ッ ク に対 し てパ ワー ゲーテ ィ ン グ を有効にす る こ と で、 消費電力を削減で き ます。 パ ワー ゲーテ ィ ン グ を有効に し た 18Kb ブ ロ ッ ク は コ ン フ ィ ギ ュ レーシ ョ ン時に初期化 さ れず、 0 を維持し ます。 コ ン フ ィ ギ ュ レーシ ョ ンおよび リ ー ド バ ッ ク には有効 な ビ ッ ト ス ト リ ームが必要です。 空白のビ ッ ト ス ト リ ームは使用で き ません。 イ ン ス タ ン シエー ト さ れていないブ ロ ッ ク RAM へのア ク セ スは、 内部動作を無効にする こ と に よ っ て避け る こ と がで き ます。ブ ロ ッ ク RAM のラ イ ブ ラ リ プ リ ミ テ ィ ブ

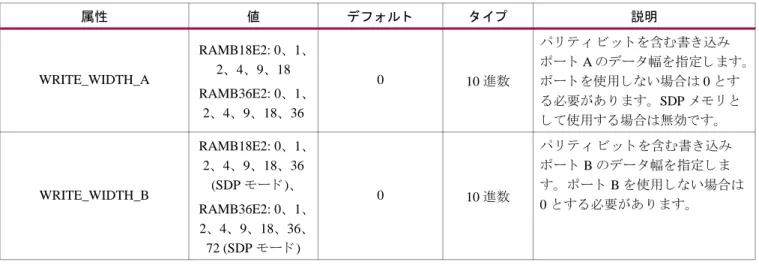

ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ、 RAMB18E2 および RAMB36E2 はすべてのブ ロ ッ ク RAM コ ン フ ィ ギ ュ レーシ ョ ンの基本構築ブ ロ ッ ク です。 その他のブ ロ ッ ク RAM のプ リ ミ テ ィ ブおよ びマ ク ロ は、 こ のプ リ ミ テ ィ ブを 基に し てい ます。 ブ ロ ッ ク RAM の属性に よ っ ては、 1 つのプ リ ミ テ ィ ブでのみ設定で き ます (パ イ プ ラ イ ン レ ジ ス タ 、 カ ス ケー ド な ど)。 9 ビ ッ ト 幅 (8+1)、 18 ビ ッ ト 幅 (16+2)、 36 ビ ッ ト 幅 (32+4) の コ ン フ ィ ギ ュ レーシ ョ ン では、 入力お よ び出力デー タ バ ス は 2 つのバス で表 さ れます。 各バ イ ト に関連付け ら れてい る 9 番目のビ ッ ト にはパ リ テ ィ ビ ッ ト (エ ラ ー訂正ビ ッ ト ) を保存する か、 追加のデータ ビ ッ ト と し て使用で き ます。 こ の 9 番目のビ ッ ト には、 特定の機能はあ り ません。 パ リ テ ィ ビ ッ ト 用に別のバス を使用 し た方が良いデザ イ ン も あ り ますが、 たいていの場合は、 通常のデータ バス と パ リ テ ィ バス を一緒に し て、 9 ビ ッ ト 、 18 ビ ッ ト 、 ま たは 36 ビ ッ ト バス を使用し て も 問題あ り ません。 読み出し / 書 き 込み、 お よ び保存はパ リ テ ィ ビ ッ ト を含めてすべてのビ ッ ト で同様に実行 さ れます。

図 1-14 に、 36Kb の TDP のブ ロ ッ ク RAM プ リ ミ テ ィ ブ (RAMB36) の I/O ポー ト を示 し ます。表 1-7 にプ リ ミ テ ィ ブ の一覧を示 し ます。

注記:図 1-14 には ECC 関連の ピ ンは示 し てい ません。 詳細は、「ビル ト イ ン エ ラ ー訂正」 を参照 し て く だ さ い。

X-Ref Target - Figure 1-14

図 1-14: ブ ロ ッ ク RAM ポー ト 信号 (RAMB36E2) DOUTPADOUTP DOUTPBDOUTP DINADIN DINPADINP ADDRARDADDR WEA ENARDEN RSTREGARSTREG CLKARDCLK DOUTADOUT DOUTBDOUT RSTRAMARSTRAM REGCEAREGCE DINBDIN DINPBDINP ADDRBWRADDR WEBWE ENBWREN RSTREGB RSTRAMB REGCEB CLKBWRCLK 32 4 15 4 32 4 32 4 32 4 15 9 CASDOUTPB CASDOUTB ARST_A Sleep ARST_B 32 4 32 4 CASDOUTPA CASDOUTA CASDINPB CASDINB 32 4 32 4 CASDINPA CASDINA CASOREGIMUXB CASOREGIMUXEN_B CASDOMUXEN_B CASDOMUXB CASOREGIMUXA CASOREGIMUXEN_A CASDOMUXEN_A CASDOMUXA X17308-020419

表 1-8 に、表 1-7 で示 し たプ リ ミ テ ィ ブの各ポー ト の名称 と 説明を示 し ます。 ECC ポー ト については、 「ビル ト イ ン エ ラ ー訂正」 で説明 し ます。 表 1-7: ブ ロ ッ ク RAM および FIFO プ リ ミ テ ィ ブ プ リ ミ テ ィ ブ 説明 RAMB36E2 • TDP メ モ リ と し て使用 し た場合、 x1、 x2、 x4、 x9、 x18、 x36 のポー ト 幅を サポー ト し ます。 • SDP メ モ リ と し て使用 し た場合、 読み出 し /書 き 込みポー ト 幅は x64 ま たは x72 で、 も う 一方のポー ト 幅は x1、 x2、 x4、 x9、 x18、 x36、 x72 です。 ECC モー ド では、 64 ビ ッ ト ECC エン コー ド /デ コ ー ド を サポー ト し ます。 RAMB18E2 • TDP メ モ リ と し て使用 し た場合、 x1、 x2、 x4、 x9、 x18 のポー ト 幅を サポー ト し ます。 • SDP メ モ リ と し て使用 し た場合、 読み出 し /書 き 込みポー ト 幅は x32 ま たは x36 で、 も う 一方のポー ト 幅は x1、 x2、 x4、 x9、 x18、 x36 です。 FIFO36E2 いずれのポー ト も 、 x4、 x9、 x18、 x36、 x72 のポー ト 幅がサポー ト さ れます。 ポー ト 幅を x72 と し た場合、 オプシ ョ ンで ECC がサポー ト さ れます。 FIFO18E2 いずれのポー ト も 、 x4、 x9、 x18、 x36 のポー ト 幅がサポー ト さ れます。 表 1-8: RAMB36E2 および RAMB18E2 のポー ト 名 と 説明 ポー ト 名 説明 DINADIN[31:0] ポー ト A データ 入力。 ア ド レ スは ADDRARDADDR で指定 し ます。 SDP メ モ リ と し て使用す る 場合のポー ト 名マ ッ ピ ン グは、31 ページの表 1-13 を参照 し て く だ さ い。 DINPADINP[3:0] ポー ト A データ パ リ テ ィ 入力。 ア ド レ スは ADDRARDADDR で指定し ます。 SDP メ モ リ と し て使用す る 場合のポー ト 名マ ッ ピ ン グは、31 ページの表 1-13 を参照 し て く だ さ い。 DINBDIN[31:0] ポー ト B データ 入力。 ア ド レ スは ADDRBWRADDR で指定 し ます。 SDP メ モ リ と し て使用す る 場合のポー ト 名マ ッ ピ ン グは、31 ページの表 1-13 を参照 し て く だ さ い。 DINPBDINP[3:0] ポー ト A データ パ リ テ ィ 入力。 ア ド レ スは ADDRBWRADDR で指定し ます。 SDP メ モ リ と し て使用す る 場合のポー ト 名マ ッ ピ ン グは、31 ページの表 1-13 を参照 し て く だ さ い。 ADDRARDADDR [14:0] ポー ト A ア ド レ ス入力バス。 SDP メ モ リ と し て使用する場合は RDADDR バス と な り ます。 ADDRBWRADDR[14:0] ポー ト B ア ド レ ス入力バス。 SDP メ モ リ と し て使用する場合は WRADDR バス と な り ます。 ADDRENA ポー ト A で新 し いア ド レ ス を キ ャ プチ ャする か ど う かを制御 し ます。 無効に し た場合 (Low)、 ラ ッ チ さ れてい る ア ド レ ス を使用 し ます。 ADDRENB ポー ト B で新 し いア ド レ ス を キ ャ プチ ャする か ど う かを制御 し ます。 無効に し た場合 (Low)、 ラ ッ チ さ れてい る ア ド レ ス を使用 し ます。 WEA[3:0] ポー ト A バ イ ト ラ イ ト イ ネーブル。 SDP メ モ リ と する場合は使用 し ません。 WEBWE[7:0] ポー ト B バ イ ト ラ イ ト イ ネーブル。 SDP モー ド では、 バ イ ト ラ イ ト イ ネーブル と な り ます。 ENARDEN ポー ト A イ ネーブル。 SDP メ モ リ と し て使用する場合は RDEN と な り ます。 ENBWREN ポー ト B イ ネーブル。 SDP メ モ リ と し て使用する場合は WREN と な り ます。

RSTREGARSTREG 同期出力レ ジ ス タ のセ ッ ト / リ セ ッ ト 。 SRVAL_A (DOA_REG = 1) で初期化 し ます。 REGCE よ り も 優先す る か ど う かは RSTREG_PRIORITY_A で設定 し ます。 SDP メ モ リ と し て使用する場 合は RSTREG と な り ます。

RSTRAMARSTRAM 同期出力 ラ ッ チのセ ッ ト / リ セ ッ ト 。 SRVAL_A (DOB_REG = 0) で初期化 し ます。 SDP メ モ リ と し て使用す る 場合は RSTRAM と な り ます。

RSTRAMB 同期出力 ラ ッ チのセ ッ ト / リ セ ッ ト 。 SRVAL_B (DOB_REG = 0) で初期化 し ます。 CLKARDCLK ポー ト A ク ロ ッ ク 入力。 SDP メ モ リ と し て使用する場合は RDCLK と な り ます。 CLKBWRCLK ポー ト B ク ロ ッ ク 入力。 SDP メ モ リ と し て使用する場合は WRCLK と な り ます。 REGCEAREGCE ポー ト A 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOA_REG = 1)。SDP メ モ リ と し て使用する場合 は REGCE と な り ます。 REGCEB ポー ト B 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOB_REG = 1)。 CASDINA[31:0] ポー ト A カ ス ケー ド データ 入力。 下段のブ ロ ッ ク RAM のデータ 出力か ら 接続 さ れます。 RAMB18E2 の場合は CASDINA[15:0] です。 CASDINPA[3:0] ポー ト A カ ス ケー ド パ リ テ ィ データ 入力。 下段のブ ロ ッ ク RAM のパ リ テ ィ データ 出力か ら 接続 さ れます。 RAMB18E2 の場合は CASDINPA[1:0] です。 CASDINB[31:0] ポー ト B カ ス ケー ド データ 入力。 下段のブ ロ ッ ク RAM のデータ 出力か ら 接続 さ れます。 RAMB18E2 の場合は CASDINB[15:0] です。 CASDINPB[3:0] ポー ト B カ ス ケー ド パ リ テ ィ データ 入力。 下段のブ ロ ッ ク RAM のパ リ テ ィ データ 出力か ら 接続 さ れます。 RAMB18E2 の場合は CASDINPB[1:0] です。

CASDOUTA[31:0] ポー ト A カ ス ケー ド データ 出力。 上段のブ ロ ッ ク RAM の CASDINA[31:0] に接続し ます。 RAMB18E2 の場合は CASDOUTA[15:0] です。

CASDOUTPA[3:0] ポー ト A カ ス ケー ド パ リ テ ィ データ 出力。上段のブ ロ ッ ク RAM の CASDINPA[3:0] に接続 し ます。 RAMB18E2 の場合は CASDOUTPA[1:0] です。

CASDOUTB[31:0] ポー ト B カ ス ケー ド データ 出力。 上段のブ ロ ッ ク RAM の CASDINB[31:0] に接続 し ます。 RAMB18E2 の場合は CASDOUTB[15:0] です。

CASDOUTPB[3:0] ポー ト B カ ス ケー ド パ リ テ ィ データ 出力。上段のブ ロ ッ ク RAM の CASDINPB[3:0] に接続 し ます。 RAMB18E2 の場合は CASDOUTPB[1:0] です。 CASDOMUXA ポー ト A のデータ カ ス ケー ド 出力マルチプ レ ク サーを制御する入力を選択し ます。 CASDOMUXEN_A CASDOMUXA レ ジ ス タ の制御を有効に し ます。 CASDOMUXB ポー ト B のデータ カ ス ケー ド 出力マルチプ レ ク サーを制御する入力を選択 し ます。 CASDOMUXEN_B CASDOMUXB レ ジ ス タ の制御を有効に し ます。 SDP メ モ リ と す る 場合は使用 し ません。 CASOREGIMUXA ポー ト A の出力レ ジ ス タ の前のカ ス ケー ド マルチプ レ ク サーを制御する入力を選択し ます。 CASOREGIMUXEN_A CASOREGIMUXA レ ジ ス タ の制御を有効に し ます。 CASOREGIMUXB ポー ト B の出力レ ジ ス タ の前のカ ス ケー ド マルチプ レ ク サーを制御する入力を選択し ます。 SDP メ モ リ と す る 場合は使用 し ません。 CASOREGIMUXEN_B CASOREGIMUXB レ ジ ス タ の制御を有効に し ます。 SDP メ モ リ と す る 場合は使用 し ません。 CASDIMUXA ポー ト A のカ ス ケー ド DIN マルチプ レ ク サーを制御する入力を選択 し ます。 CASDIMUXB ポー ト B のカ ス ケー ド DIN マルチプ レ ク サーを制御する入力を選択 し ます。 SDP メ モ リ と す る 場合は使用 し ません。 表 1-8: RAMB36E2 および RAMB18E2 のポー ト 名 と 説明 (続き) ポー ト 名 説明

![図 1-12: ア ド レ ス ラ ッ チ イ ネーブルADDR[0]RegisterADDR[n]Register ADDR[0]ADDR[0]ADDR[n]ADDRENCLK0101 ADDR[N] X17306-020817](https://thumb-ap.123doks.com/thumbv2/123deta/8647859.947403/23.918.174.815.244.770/図ドレスラッチイネーブルADDRADDRADDRNX1736281.webp)