Vivado Design Suite

ユーザー

ガイ ド

エ ンベデ ッ ド

プロセ ッ サ

ハー ド ウ ェ ア

デザイ ン

UG898 (v2016.3) 2016 年 10 月 5 日この資料は表記のバージョンの英語版を翻訳したもので、内容に相違が生じる場合には原文を優先します。資料に

よっては英語版の更新に対応していないものがあります。日本語版は参考用としてご使用の上、最新情報につきまし

ては、必ず最新英語版をご参照ください。

UG898 (v2016.4) 2016 年 11 月 30 日

次の表に、 こ の文書の改訂履歴を示 し ます。

日付 バージ ョ ン 改訂内容

2016 年 10 月 5 日 2016.3 第3 章の 「I/O 設定」 に Zynq® UltraScale+™ MPSoC デバ イ ス のセキ ュ ア デジ タ ル (SD)

ホ ス ト コ ン ト ロー ラ ーおよび PJTAG イ ン ターフ ェ イ ス の説明を追加。

第3 章の 「 ク ロ ッ ク 設定」 を ア ッ プデー ト 。

第4 章 「エンベデ ッ ド デザ イ ンでの MicroBlaze プ ロ セ ッ サの使用」 を若干変更。

第7 章の 「ザ イ リ ン ク ス パ ラ メ ーター指定マ ク ロ (XPM) メ モ リ 」 を追加。

2016 年 4 月 27 日 2016.1 第3 章 「エンベデ ッ ド デザ イ ンでの Zynq UltraScale+ MPSoC の使用」 を追加。

第4 章の 「MicroBlaze 設定 ウ ィ ザー ド : ア ド バン ス モー ド 」 を追加。 その他のマ イ ナーな編集上の修正。

目次

改訂履歴 . . . 2第 1 章: 入門

概要 . . . 5 ハー ド ウ ェ アお よ び ソ フ ト ウ ェ ア フ ローの概要 . . . 5 エンベデ ッ ド プ ロ セ ッ サ デザ イ ンのフ ロー . . . 7第 2 章: エ ンベデ ッ ド デザイ ン での Zynq-7000 プ ロ セ ッ サの使用

概要 . . . 8Vivado IDE での Zynq-7000 デバ イ ス の設計 . . . 8

Zynq ブ ロ ッ ク デザ イ ン と [Re-customize IP] ダ イ ア ロ グ ボ ッ ク ス の概要 . . . 12

プ ロ グ ラ マブル ロ ジ ッ ク (PL) の使用 . . . 31

Vivado ピ ン プ ラ ンナーでの PS I/O の表示 . . . 46

Vivado IDE で生成 さ れたエンベデ ッ ド フ ァ イ ル . . . 46

ソ フ ト ウ ェ ア開発キ ッ ト (SDK) の使用 . . . 47

第 3 章: エ ンベデ ッ ド デザイ ン での Zynq UltraScale+ MPSoC の使用

概要 . . . 49Vivado IDE での Zynq UltraScale+ デバ イ ス の設計 . . . 49

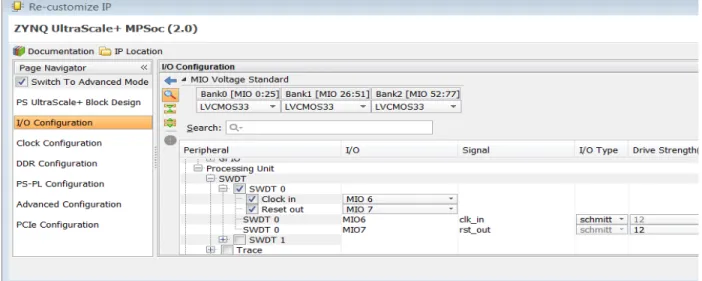

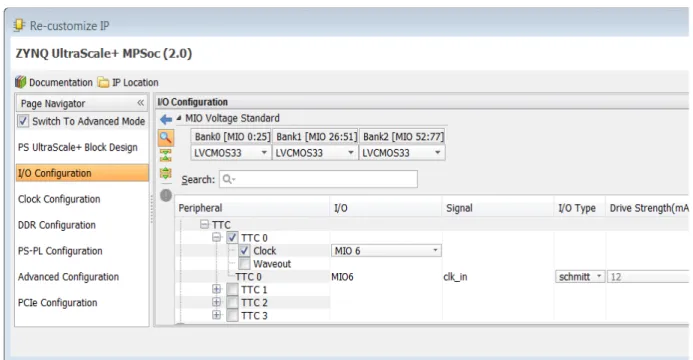

Zynq UltraScale+ MPSoc の [Re-customize IP] ダ イ ア ロ グ ボ ッ ク ス の概要 . . . 52

第 4 章: エ ンベデ ッ ド デザイ ン での MicroBlaze プ ロ セ ッ サの使用

MicroBlaze プ ロ セ ッ サ デザ イ ンの概要 . . . 78 MicroBlaze プ ロ セ ッ サを含む IP イ ン テ グ レーター デザ イ ンの作成 . . . 79 MicroBlaze 設定ウ ィ ザー ド . . . 82 MicroBlaze プ ロ セ ッ サの ク ロ ス ト リ ガー機能 . . . 103 カ ス タ ム ロ ジ ッ ク . . . 107 エンベデ ッ ド IP カ タ ロ グ . . . 108 接続 . . . 108第 5 章: MIG コ ア を含むデザイ ン

概要 . . . 115 メ モ リ IP の追加. . . 115第 6 章: IP イ ン テグレー タ ーの リ セ ッ ト および ク ロ ッ ク ト ポロ ジ

概要 . . . 126 MIG コ ア を含ま ない MicroBlaze デザ イ ン . . . 127 MIG コ ア を含む MicroBlaze デザ イ ン . . . 130 PL ロ ジ ッ ク を含ま ない Zynq デザ イ ン . . . 135 PL ロ ジ ッ ク を含む Zynq デザ イ ン . . . 137第 7 章: UpdateMEM を使用 し た BIT フ ァ イルの MMI および ELF デー タ でのア ッ プデー ト

概要 . . . 144 UpdateMEM . . . 145 メ モ リ (MEM) フ ァ イ ル . . . 147 ブ ロ ッ ク RAM メ モ リ マ ッ プ情報 (MMI) フ ァ イ ル . . . 148 ザ イ リ ン ク ス パ ラ メ ー ター指定マ ク ロ (XPM) メ モ リ . . . 155付録 A: その他の リ ソ ースおよび法的通知

ザ イ リ ン ク ス リ ソ ース . . . 156 参考資料 . . . 156 ト レーニ ン グ リ ソ ース . . . 157 お読み く だ さ い: 重要な法的通知 . . . 157第 1 章

入門

概要

こ の章では、Vivado® Design Suite フ ローを使用 し て、 Zynq®-7000 All Programmable (AP) SoC デバ イ ス ま たは

MicroBlaze™ プ ロ セ ッ サを使用し たエンベデ ッ ド デザ イ ン をプ ロ グ ラ ムする方法の概要を説明 し ます。 エンベデ ッ ド シ ス テ ムは複雑です。 エンベデ ッ ド デザ イ ンのハー ド ウ ェ ア部分 と ソ フ ト ウ ェ ア部分は、 それ自体が プ ロ ジ ェ ク ト です。1 つのシ ス テ ム と し て機能する よ う に こ れ ら 2 つのデザ イ ン コ ンポーネン ト を統合する と 、 追 加の課題が出て き ます。FPGA デザ イ ン プ ロ ジ ェ ク ト を追加する と 、 さ ら に複雑にな り ます。 デザ イ ン プ ロ セ ス を単純にする ため、 ザ イ リ ン ク ス では複数のツール セ ッ ト を提供 し てい ます。 基本的な ツール 名、 プ ロ ジ ェ ク ト フ ァ イ ル名、 こ れ ら のツールの略称を、 知っ てお く と 有益です。 Vivado 統合設計環境 (IDE) には、 プ ロ セ ッ サ ベース のデザ イ ン を統合する ための IP イ ン テ グ レーター ツールが含ま れてい ます。 こ の ツールをザ イ リ ン ク ス ソ フ ト ウ ェ ア開発キ ッ ト (SDK) と 合わせて使用する こ と で、 マ イ ク ロ プ ロ セ ッ サ ベース のシ ス テ ム と エンベデ ッ ド ソ フ ト ウ ェ ア アプ リ ケーシ ョ ン を設計およびデバ ッ グする ための統合環境 が提供 さ れてい ます。 エンベデ ッ ド プ ロ セ ッ サおよび SDK、 ハー ド ウ ェ ア/ ソ フ ト ウ ェ ア ク ロ ス ト リ ガー、 およびデザ イ ンのデバ ッ グ を

使用す る 例は、 『Vivado Design Suite チ ュー ト リ アル: エンベデ ッ ド プ ロ セ ッ サ ハー ド ウ ェ ア デザ イ ン』 (UG940) [参

照1] を参照 し て く だ さ い。 こ のチ ュー ト リ アルでは、 Vivado IP イ ン テグ レーターを使用し てエンベデ ッ ド プ ロ セ ッ

サ デザ イ ン を構築し 、 SDK および Vivado ロ ジ ッ ク 解析を使用 し てデザ イ ン をデバ ッ グ し ます。

ハー ド ウ ェ アおよび ソ フ ト ウ ェ ア フ ローの概要

Vivado ツールでは、 プ ロ セ ッ サに基づいて、 プ ロ グ ラ ム用のフ ローが提供 さ れてい ます。 Vivado IDE では、 接続を

画像で示す IP イ ン テグ レー ターを使用 し て、 デバ イ ス を指定し、 ペ リ フ ェ ラ ルを選択し、 ハー ド ウ ェ ア を設定で き

ます。

Zynq-7000 AP SoC では、 Vivado IP イ ン テ グ レーターを使用 し て、 ハー ド ウ ェ ア プ ラ ッ ト フ ォーム情報を XML 形式

のアプ リ ケーシ ョ ン と し て、 ほかのデー タ フ ァ イ ル と 共に取 り 込みます。 こ れ ら の情報が ソ フ ト ウ ェ ア デザ イ ン

ツールで使用 さ れ、 ボー ド サポー ト パ ッ ケージ (BSP) ラ イ ブ ラ リ の作成 と 設定、 コ ンパ イ ラ オプシ ョ ンの推論、 プ

ロ グ ラ マブル ロ ジ ッ ク (PL) のプ ロ グ ラ ム、 JTAG 設定の定義な ど、 ハー ド ウ ェ アに関する情報を必要 と する操作が

自動化 さ れます。Zynq-7000 AP SoC ソ リ ューシ ョ ン を使用する と 、 1 つの SoC でプ ロ グ ラ マブル ロ ジ ッ ク と 共に

ARM Cortex A9 デュ アル コ アがエンベデ ッ ド ブ ロ ッ ク と し て提供 さ れてい る ので、 エンベデ ッ ド デザ イ ンの複雑 さ が軽減 さ れます。

ザ イ リ ン ク ス では、Zynq-7000 AP SoC および MicroBlaze プ ロ セ ッ サ デバ イ ス用の ソ フ ト ウ ェ ア アプ リ ケーシ ョ ンの 開発お よ びデバ ッ グのために、 次のデザ イ ン ツールを提供 し てい ます。 • ソ フ ト ウ ェ ア IDE • GUI ベース の コ ンパ イ ラ ツールチ ェーン • JTAG デバ ッ ガー こ れ ら の ツールを使用す る と 、OS を必要 と し ないベア メ タ ル アプ リ ケーシ ョ ン と 、 オープン ソ ース Linux OS 用ア プ リ ケーシ ョ ンの両方を開発で き ます。Vivado IP イ ン テグ レーターには、 コ ン フ ィ ギ ュ レーシ ョ ン設定、 レ ジ ス タ メ モ リ マ ッ プ、 プ ロ グ ラ マブル ロ ジ ッ ク (PL) フ ァ ブ リ ッ ク 内の関連ロ ジ ッ ク な ど、 プ ロ セ ッ シ ン グ シ ス テ ム (PS) お よ びペ リ フ ェ ラ ルに関す る 情報が取 り 込まれます。 その後、PL 初期化用のビ ッ ト ス ト リ ーム を生成で き ます。 ソ フ ト ウ ェ ア ソ リ ューシ ョ ン と し ては、 Cortex-A9 プ ロ セ ッ サをサポー ト する サー ド パーテ ィ ソ ース か ら も 、 次の よ う な ツールが提供 さ れてい ます。 • ソ フ ト ウ ェ ア IDE • コ ンパ イ ラ ツールチ ェーン • デバ ッ グお よ び ト レース ツール • エンベデ ッ ド OS および ソ フ ト ウ ェ ア ラ イ ブ ラ リ • シ ミ ュ レー タ • モデルお よ び仮想プ ロ ト タ イ プ ツール サー ド パーテ ィ ツール ソ リ ューシ ョ ンに よ っ て、 その統合レベルおよび Zynq-7000 デバ イ ス の直接サポー ト は異な り ます。

SDK の詳細および Zynq デバ イ ス のプ ロ グ ラ ムについては、 『Zynq-7000 All Programmable SoC ソ フ ト ウ ェ ア開発者向

けガ イ ド 』 (UG821) [参照 2] を参照 し て く だ さ い。 SDK はス タ ン ド ア ロ ン製品で、https://japan.xilinx.com か ら ダ ウ ン

ロ ー ド で き ます。

図1-1 に、 エンベデ ッ ド ハー ド ウ ェ アのツール フ ローを示 し ます。

X-Ref Target - Figure 1-1

図 1-1: ハー ド ウ ェ ア デザイ ン ツールから ソ フ ト ウ ェ ア ツールへのハン ド オ フ Configure PS Generate Bitstream (optional) Hardware Handoff X12 502 PS Configuration Hardware Specification File (XML) BRAM Configuration (BMM) PL Configuration (bitstream) Export to Software Tools Add IP

エ ンベデ ッ ド プ ロ セ ッ サ デザイ ンのフ ロー

エンベデ ッ ド プ ロ セ ッ サ デザ イ ンの全体的な フ ローは、 次の よ う にな り ます。

1. 新 し い Vivado Design Suite プ ロ ジ ェ ク ト を作成し ます。

2. IP イ ン テ グ レーター ツールでブ ロ ッ ク デザ イ ン を作成 し、 Zynq Processing System 7 IP コ ア ま たは MicroBlaze プ

ロ セ ッ サ と 、 その他のザ イ リ ン ク ス IP ま たはユーザーのカ ス タ ム IP を イ ン ス タ ン シエー ト し ます。

3. 最上位 ラ ッ パーを作成 し て、 ブ ロ ッ ク デザ イ ン を最上位 RTL デザ イ ンに イ ン ス タ ン シエー ト し ます。

4. 最上位デザ イ ン を合成お よ び イ ンプ リ メ ン テーシ ョ ン し 、 ハー ド ウ ェ ア を SDK にエ ク ス ポー ト し ます。

5. ソ フ ト ウ ェ ア アプ リ ケーシ ョ ン を作成 し、 SDK で ELF (Executable Linkable File) フ ァ イ ルをハー ド ウ ェ ア デザ イ

ンに関連付け ます。

6. UpdateMEM を使用 し て、 ELF およびブ ロ ッ ク RAM の メ モ リ マ ッ プ情報 (MMI) と 、 ハー ド ウ ェ ア デバ イ ス

ビ ッ ト ス ト リ ームに統合 し ます。

エ ンベデ ッ ド デザイ ン での Zynq-7000 プ ロ

セ ッ サの使用

概要

こ の章では、Zynq®-7000 All Programmable (AP) SoC デバ イ ス を使用する場合の Vivado® Design Suite フ ローについて

説明 し ます。

こ こ に示す例では、 ザ イ リ ン ク ス ZC702 Rev 1.0 評価ボー ド を ターゲ ッ ト と し、 Vivado Design Suite のバージ ョ ンは

2016.3 を使用し てい ます。

重要: Vivado IP イ ンテグ レーターは、 Zynq デバイ スおよび MicroBlaze™ プ ロ セ ッ サを ターゲ ッ ト と するデザイ ン を

含むエンベデ ッ ド プ ロ セ ッ サ デザ イ ン を作成する ための、 XPS (Xilinx® Platform Studio) に代わ る ツールです。 XPS

では MicroBlaze プ ロ セ ッ サを ターゲ ッ ト と するデザ イ ンのみがサポー ト さ れます。 IP イ ン テグ レーター も XPS も

Vivado 統合設計環境 (IDE) か ら 使用で き ます。

Vivado IDE での Zynq-7000 デバイ スの設計

Zynq-7000 AP SoC デバ イ ス の設計は、 Vivado IDE を使用 し た場合 と 、 ISE® Design Suite およびエンベデ ッ ド 開発キ ッ

ト (EDK) を使用 し た場合で異な り ます。

Vivado IDE では、 エンベデ ッ ド 開発に IP イ ン テ グ レーターを使用 し ます。 IP イ ン テグ レーターは、 GUI ベース の イ ン タ ーフ ェ イ ス で、 複雑な IP サブシ ス テ ム を統合で き ます。

複雑なデザ イ ンに対応す る ため、Vivado IDE の IP カ タ ロ グか ら さ ま ざ ま な IP が提供 さ れています。

IP カ タ ロ グにカ ス タ ム IP を追加する こ と も で き ます。 詳細は、 『Vivado Design Suite ユーザー ガ イ ド : IP イ ン テ グ

Zynq-7000 プ ロ セ ッ サを含む IP イ ン テグ レー タ ー デザイ ンの作成

IP イ ン テ グ レーターで [Create Block Design] を ク リ ッ ク し、 [Create Block Design] ダ イ ア ロ グ

ボ ッ ク ス にデザ イ ン名を入力 し ます。

ブ ロ ッ ク デザ イ ンは、 プ ロ ジ ェ ク ト の一部 と し て作成する か、 [Directory] で指定 し た別のデ ィ レ ク ト リ に作成で き

ます。

[Specify source set] のプルダ ウ ン メ ニ ューか ら ソ ース タ イ プを指定する こ と も で き ます。 ブ ロ ッ ク デザ イ ン キ ャ ン

バ ス (図2-2) が開き ます。

X-Ref Target - Figure 2-1

図 2-1: [Create Block Design] ダ イ ア ログ ボ ッ ク ス

X-Ref Target - Figure 2-2

1. 空のブ ロ ッ ク デザ イ ン キ ャ ンバス で、[Add IP] ボ タ ン を ク リ ッ ク し て IP カ タ ロ グか ら IP を追加し ます (図2-3)。 ま たは、 キ ャ ンバ ス上で右 ク リ ッ ク し て [Add IP] を ク リ ッ ク し ます。

2. [Add IP] を ク リ ッ ク する と 検索ボ ッ ク ス が表示 さ れ る ので、図2-4 に示すよ う に [ZYNQ7 Processing System] を検

索 し て選択 し ます。

X-Ref Target - Figure 2-3

図 2-3: ブ ロ ッ ク デザイ ン キ ャ ンバスへの IP の追加

X-Ref Target - Figure 2-4

ZYNQ7 Processing System IP を選択 し てダブル ク リ ッ ク する と 、Vivado IP イ ン テ グ レーターでデザ イ ンに IP が追

加 さ れ、図2-5 に示すよ う にプ ロ セ ッ シ ン グ シ ス テ ムのグ ラ フ ィ ッ ク が表示 さ れます。

Tcl コ マン ド :

create_bd_cell -type ip -vlnv xilinx.com:ip:processing_system7:5.5 processing_system7_0

3. ZYNQ7 Processing System のグ ラ フ ィ ッ ク を ダブル ク リ ッ ク する と 、 [Re-customize IP] ダ イ ア ロ グ ボ ッ ク ス

(図2-6) が表示 さ れます。

X-Ref Target - Figure 2-5

図 2-5: デ フ ォル ト の ZYNQ7 Processing System のグ ラ フ ィ ッ ク表示

X-Ref Target - Figure 2-6

ブ ロ ッ ク デザ イ ンの内容を確認 し ます。 [Zynq Block Design] ページの緑色のブ ロ ッ ク は設定可能です。 緑色の ブ ロ ッ ク を ク リ ッ ク す る と 、 そのブ ロ ッ ク のオプシ ョ ン を設定す る ページが開 き ます。 こ れ ら のページは、

11 ページの図 2-6 の左側の Page Navigator か ら 選択する こ と も で き ます。

Zynq ブ ロ ッ ク デザイ ン と [Re-customize IP] ダ イ ア ログ

ボ ッ ク スの概要

Page Navigator か ら 設定可能なオプシ ョ ンの詳細は、 『Zynq-7000 All Programmable SoC テ ク ニカル リ フ ァ レ ン ス マ

ニ ュ アル』 (UG585) [参照 6] を参照 し て く だ さ い。 次のセ ク シ ョ ンでは、 Page Navigator の選択オプシ ョ ン を簡単に説

明 し ます。

プ ロ セ ッ シ ング システム (PS) と プ ログ ラ マブル ロジ ッ ク (PL) 間の設定

[PS-PL Configuration] ページには、 次の よ う なオプシ ョ ンがあ り ます。

X-Ref Target - Figure 2-7

12 ページの図 2-7 に示すダ イ ア ロ グ ボ ッ ク ス の上部には、 次の 4 つのボ タ ン あ り ます。

• [Documentation]: 資料 メ ニ ューが開き、 製品ガ イ ド 、 IP 変更ロ グ、 Zynq に関する資料を検索で き る ザ イ リ ン ク ス

ウ ェ ブサ イ ト にア ク セ ス で き ます。 開 く のは英語サ イ ト です。 ブ ラ ウ ザーの URL の www.xilinx.com を japan.xilinx.com に変更する と 日本語サ イ ト が表示 さ れます。

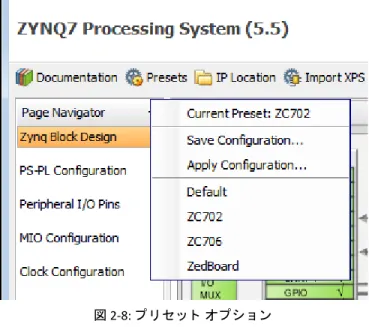

• [Presets]: 使用可能なプ リ セ ッ ト オプシ ョ ンに関する情報を表示 し ます。 ZYNQ7 Processing System の現在の設定

を フ ァ イ ルに保存 し た り 、 既存の設定を適用 し てそれを基にプ ロ セ ッ サの現在の イ ン ス タ ン ス を設定で き ます。

プ リ セ ッ ト は、 タ ーゲ ッ ト ボー ド に適用する こ と も で き ます。 使用可能なオプシ ョ ンは、図2-8 に示すよ う に、

[Defalut]、 [Microzed]、 [ZC702]、 [ZC706]、 [ZedBoard] です。

• [IP Location]: IP は、 プ ロ ジ ェ ク ト デ ィ レ ク ト リ 内に作成する か、 リ モー ト デ ィ レ ク ト リ に作成で き ます。

• [Import XPS Settings]: XPS ベース のプ ロ ジ ェ ク ト か ら の Zynq プ ロ セ ッ サの設定を記述し た XML フ ァ イ ルがあ る

場合は、 こ のボ タ ン を ク リ ッ ク し てその設定を イ ン ポー ト し 、Zynq プ ロ セ ッ サをすばや く 設定で き ます。

X-Ref Target - Figure 2-8

図 2-8: プ リ セ ッ ト オプシ ョ ン

X-Ref Target - Figure 2-9

一般設定

[General] を展開する と 、 次のオプシ ョ ンが表示 さ れます。

X-Ref Target - Figure 2-10

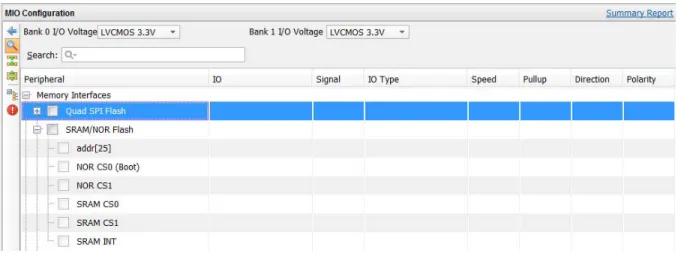

MIO および EMIO の設定

Page Navigator で [Peripheral I/O Pins] ま たは [MIO Configuration] を ク リ ッ ク す る と 、 I/O ピ ン を表示お よ び設定で き ま す。

Zynq-7000 PS では、 20 以上のペ リ フ ェ ラ ルを使用で き ます。 こ れ ら のペ リ フ ェ ラ ルは、 デバ イ ス の専用 MIO (Multiplexed I/O) に直接、 ま たは EMIO (Extended Multiplexed I/O) を介し て フ ァ ブ リ ッ ク に配線で き ます。

こ のページでは、MIO の I/O 規格お よびスルー レー ト 設定 も 選択で き ます。 ペ リ フ ェ ラ ルをオンにする と 、 その I/O

ペ リ フ ェ ラ ル ブ ロ ッ ク にチ ェ ッ ク マー ク が表示 さ れます。 ブ ロ ッ ク デザ イ ンには、 ペ リ フ ェ ラ ルが イ ネーブルか

デ ィ ス エーブルかの ス テー タ ス が表示 さ れます。

X-Ref Target - Figure 2-11

[MIO Configuration] ページで も 同様に設定で き ます (図2-12)。

7Z010 CLG225 の MIO および EMIO の詳細は、 『Zynq-7000 All Programmable SoC テ ク ニカル リ フ ァ レ ン ス マニ ュ ア

ル』 (UG585) [参照 6] の第 2 章 「信号、 イ ン ターフ ェ イ ス、 ピ ン」 を参照し て く だ さ い。

ピ ンの制限

7Z010 CLG225 デバ イ ス で使用可能な 32 個の MIO ピ ンに よ り 、 PS の機能が次の よ う に制限 さ れます。 • MIO を使用 し た場合、 USB ま たは イーサネ ッ ト コ ン ト ロー ラ ーのいずれかのみが使用可能です。 • SDIO か ら はブー ト で き ません。 • NOR/SRAM と の イ ン ターフ ェ イ スはあ り ません。 • NAND フ ラ ッ シ ュ の幅は 8 ビ ッ ト に制限 さ れます。X-Ref Target - Figure 2-12

バン ク設定

ペ リ フ ェ ラ ルを選択す る と 、 そのペ リ フ ェ ラ ルの各 I/O 信号が該当する MIO ロ ケーシ ョ ンに表示 さ れます。 こ のセ

ク シ ョ ンは主に、 さ ま ざ ま なペ リ フ ェ ラ ルの I/O 規格を選択する のに使用 し ます。 PS MIO I/O バ ッ フ ァ ーは 2 つの電

圧 ド メ イ ンに分け ら れ、 それぞれの ド メ イ ン内で各 I/O を個別にプ ロ グ ラ ムで き ます。 次の 2 つの I/O 電圧バン ク があ り ます。 • 0:15 ピ ン を含むバン ク 0。 • 16:53 ピ ン を含むバン ク 1。 各 MIO ピ ンは、 次の電圧信号用に個別にプ ロ グ ラ ムで き ます。 • 1.8 および 2.5/3.3 ボル ト • CMOS シ ン グルエン ド ま たは HSTL 差動レ シーバー モー ド 重要: バン ク全体を同じ電圧にする必要があ り ますが、 ピ ンには異な る I/O 規格を設定で き ます。

[MIO Configuration] ページで MIO を設定する と 、 [Zynq Block Design] ページのペ リ フ ェ ラ ルの図で MIO の選択を確 認で き ます。 ウ ィ ン ド ウ の左側に、 使用可能なペ リ フ ェ ラ ルが リ ス ト さ れます。 ペ リ フ ェ ラ ルのチ ェ ッ ク マー ク は、 そのペ リ フ ェ ラ ルが選択 さ れてい る こ と を示 し ます。

フ ラ ッ シ ュ メ モ リ イ ン タ ー フ ェ イ ス

[Re-customize IP] ダ イ ア ロ グ ボ ッ ク ス の [MIO Configuration] ページで、 次のいずれかを選択 し ます。 • 「 ク ワ ッ ド SPI フ ラ ッ シ ュ」

• 「SRAM/NOR フ ラ ッ シ ュ」

ク ワ ッ ド SPI フ ラ ッ シ ュ

図2-13 に、 ク ワ ッ ド SPI フ ラ ッ シ ュ で設定可能なオプシ ョ ン を示し ます。 リ ニア ク ワ ッ ド SPI フ ラ ッ シ ュ コ ン ト ロー ラ ーの主な機能は、 次の と お り です。 • シ ン グルま たはデ ュ アル 1x および 2x 読み出 し をサポー ト • プ ロ グ ラ ム、 読み出 し 、 お よ び コ ン フ ィ ギ ュ レーシ ョ ン を含むすべてのデバ イ ス操作が可能な I/O モー ド 用 32 ビ ッ ト APB 3.0 イ ン ターフ ェ イ ス • 読み出 し 操作用の 32 ビ ッ ト AXI リ ニア ア ド レ ス マ ッ プ イ ン ターフ ェ イ ス • シ ン グル チ ッ プ セ レ ク ト ラ イ ン をサポー ト • 書 き 込み保護信号をサポー ト • 4 ビ ッ ト の双方向 I/O 信号 • x1、 x2、 および x4 の読み出し 速度 • x1、 x2、 および x4 の書き込み速度 • マ ス タ ー モー ド で最大 100 MHz の ク ワ ッ ド SPI ク ロ ッ ク • ク ワ ッ ド SPI の読み出し 効率を改善する ための 252 バ イ ト 入力の FIFO の深 さ • 最大 128 Mb の集積度の ク ワ ッ ド SPI デバ イ ス をサポー ト • 2 つの並列の ク ワ ッ ド SPI デバ イ ス を含むデュ アル ク ワ ッ ド SPI をサポー トX-Ref Target - Figure 2-13

リ ニア ア ド レ ス マ ッ プ モー ド には、 次の機能 も あ り ます。 • AXI イ ン ターフ ェ イ ス を介 し た標準読み出 し専用 メ モ リ ア ク セ ス • 最大 2 つの SPI フ ラ ッ シ ュ メ モ リ • 1 つの メ モ リ で最大 16 MB、 2 つの メ モ リ で 32 MB のア ド レ ス空間 • 4 つの AXI 読み出し 受諾機能 • AXI の イ ン ク リ メ ン ト および ラ ッ プ ア ド レ ス バース ト 読み出 し • 標準 メ モ リ 読み出 し を SPI プ ロ ト コ ル (ま たはその逆) に自動的に変換 • シ リ アル、 デ ュ アル、 ク ワ ッ ド SPI モー ド

SRAM/NOR フ ラ ッ シ ュ

SRAM/NOR コ ン ト ロー ラ ーの機能は、 次の と お り です。 • 8 ビ ッ ト データ バス幅 • 最大 26 個のア ド レ ス信号 (64 MB) の 1 チ ッ プ セ レ ク ト • 最大 25 個のア ド レ ス信号 (32 MB + 32 MB) の 2 チ ッ プ セ レ ク ト • 16 ワー ド 読み出し および 16 ワー ド 書き込みデータ の FIFO • 8 ワー ド コ マン ド FIFO • チ ッ プご と に選択可能なプ ロ グ ラ マブル I/O サ イ ク ル タ イ ミ ン グ • 非同期 メ モ リ 操作モー ドX-Ref Target - Figure 2-14

NAND フ ラ ッ シ ュ

NAND コ ン ト ロー ラ ーの機能は、 次の と お り です。 • 1 チ ッ プ セ レ ク ト 信号を含む 8/16 ビ ッ ト の I/O 幅 • ONFI 仕様 1.0 • 16 ワー ド 読み出し および 16 ワー ド 書き込みデータ の FIFO • 8 ワー ド コ マン ド FIFO • I/O サ イ ク ル タ イ ミ ン グ をプ ロ グ ラ ム可能 • ECC アシ ス ト • 非同期 メ モ リ 操作モー ドX-Ref Target - Figure 2-15

ク ロ ッ ク設定

Zynq-7000 デバ イ ス の ク ロ ッ ク を設定する には、 次のいずれかの方法を使用し ます。

• Page Navigator で [Clock Configuration] を ク リ ッ ク し ます。

• [Zynq Block Design] ページで [Clock Generation] ブ ロ ッ ク を ク リ ッ ク し ます。

図2-17 に [Clock Configuration] ページ を示し ます。

X-Ref Target - Figure 2-16

図 2-16: ク ロ ッ ク設定

X-Ref Target - Figure 2-17

図2-18 に、 [Clock Configuration] ページでオプシ ョ ン を展開表示 し た と こ ろ を示 し ます。

PS の ク ロ ッ キ ン グの詳細は、 『Zynq-7000 All Programmable SoC テ ク ニカル リ フ ァ レ ン ス マニ ュ アル』 (UG585) [参

照6] を参照 し て く だ さ い。 [Clock Configuration] ページでは、 ペ リ フ ェ ラ ルの ク ロ ッ ク を設定で き ます。 PS のペ リ

フ ェ ラ ルでは、 通常内部 PLL ま たは外部 ク ロ ッ ク ソ ース か ら ク ロ ッ ク ソ ース を選択で き ます。 ほ と んどの ク ロ ッ ク

で PLL を選択し て ク ロ ッ ク を生成で き ます。

X-Ref Target - Figure 2-18

注記: 特定のペ リ フ ェ ラ ルの周波数は、 入力周波数、 同 じ PLL か ら 駆動 さ れる ほかのペ リ フ ェ ラ ルの周波数、 アーキ テ ク チ ャ での制限な ど、 多 く の要因に よ っ て異な り ます。 ツールで選択 さ れ る M 値 と D 値の詳細は、 ロ グ フ ァ イ ル に含ま れます。

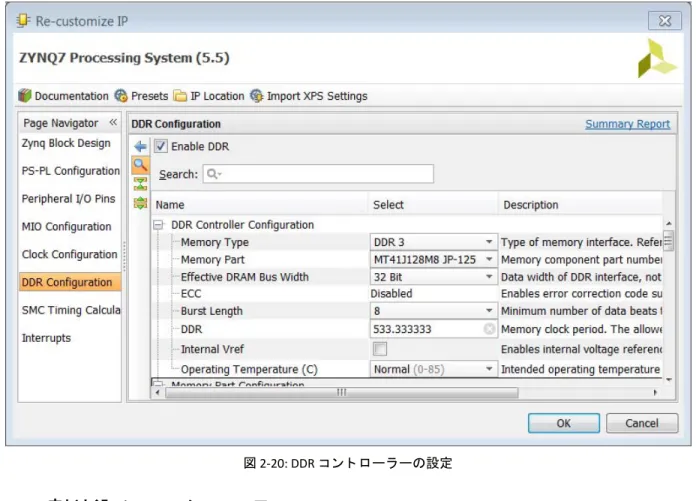

DDR の設定

DDR は、 次のいずれかの方法で設定で き ます。

• Page Navigator で [DDR Configuration] を ク リ ッ ク し ます。

• [Zynq Block Design] ページで [DDR2/3, LPDDR2 Controller] ブ ロ ッ ク を ク リ ッ ク し ます。

DDR メ モ リ コ ン ト ロー ラ ーでは DDR2、 DDR3、 DDR3L、 および LPDDR2 デバ イ ス がサポー ト さ れ、 AXI メ モ リ

ポー ト イ ン ターフ ェ イ ス - DDR イ ン ターフ ェ イ ス (DDRI)、 ト ラ ンザ ク シ ョ ン ス ケジ ュー ラ を含むコ ア コ ン ト ロー

ラ ー (DDRC)、 デジ タ ル PHY を含むコ ン ト ロー ラ ー (DDRP) の 3 つの主なブ ロ ッ ク で構成 さ れます。

DDRI ブ ロ ッ ク は、 4 つの 64 ビ ッ ト 同期 AXI イ ン ターフ ェ イ ス を介 し て同時に複数の AXI マ ス ターをサービ ス し ま

す。 それぞれの AXI イ ン ターフ ェ イ ス に専用の ト ラ ンザ ク シ ョ ン FIFO が含まれます。 DDRC には 2 つの 32 入力

CAM (Content Addressable Memory) が含まれ、 DDR メ モ リ 効率を最大限にする DDR データ サービ ス ス ケジ ュー リ ン グが実行 さ れます。 こ れには、 レ イ テ ン シの短いチ ャ ネル用の フ ラ イ バ イ チ ャ ネル も 含まれ、 CAM を介 さ ずに DDR メ モ リ にア ク セ ス で き ます。 PHY で コ ン ト ロー ラ ーか ら の読み出 しお よび書き込み要求が処理 さ れ、 ターゲ ッ ト DDR メ モ リ の タ イ ミ ン グ制約内 で特定の信号に変換 さ れます。PHY では コ ン ト ロー ラ ーか ら の信号を使用し て内部信号が生成 さ れ、 その内部信号 がデジ タ ル PHY を使用 し て ピ ンに接続 さ れます。 DDR ピ ンは PCB 信号 ト レース を使用 し て DDR デバ イ ス に直接接 続 さ れます。 シ ス テ ムは、DDRI を使用 し、 次の 4 つの 64 ビ ッ ト AXI メ モ リ ポー ト を介 し て DDR にア ク セ ス し ます。

• 1 つの AXI ポー ト は CPU および ACP の L2 キ ャ ッ シ ュ専用です。

• 2 つのポー ト は AXI_HP イ ン ターフ ェ イ ス専用です。 • AXI イ ン ターコ ネ ク ト のその他のマ ス ターは 4 番目のポー ト を共有 し ます。 DDRI は こ の 8 つのポー ト (読み出 し用 4 つ、 書き込み用 4 つ) か ら の要求を調整 (アービ ト レーシ ョ ン) し ます。 アー ビ タ は要求を選択 し 、 それを DDR コ ン ト ロー ラ ーおよび ト ラ ンザ ク シ ョ ン ス ケジ ュー ラ (DDRC) に渡 し ます。 こ のアービ ト レーシ ョ ンは、 要求が待機状態であ る 時間、 要求の重要度、 お よ び要求が前の要求 と 同 じ ページ内に あ る か ど う かな ど の状況に基づいて実行 さ れます。 DDRC は、 読み出し フ ロー と 書き込みフ ローのど ち ら で も、 1 つの イ ン ターフ ェ イ ス を介し て DDRI か ら要求を受信 し ます。 読み出 し要求には タ グ フ ィ ール ド が含まれていますが、 DDR は こ れをデータ と 共に戻し ます。 DDR コ ン ト ロ ー ラ ー PHY (DDRP) は DDR ト ラ ンザ ク シ ョ ン を駆動し ます。図2-20 に、 DDR コ ン ト ローラーの設定を示し ます。

X-Ref Target - Figure 2-19

注記: 8 ビ ッ ト イ ン ターフ ェ イ スはサポー ト さ れていませんが、 8 ビ ッ ト ポー ト を使用 し て 16/32 ビ ッ ト イ ン ター フ ェ イ ス を作成す る こ と はで き ます。

GIC - 割 り 込みコ ン ト ロー ラ ー

GIC (Generic Interrupt Controller) は、 次のいずれかの方法で設定で き ます。

• Page Navigator で [Interrupts] を ク リ ッ ク し ます。

• [Zynq Block Design] ページで [GIC] ブ ロ ッ ク を ク リ ッ ク し ます。

X-Ref Target - Figure 2-20

図 2-20: DDR コ ン ト ロー ラ ーの設定

X-Ref Target - Figure 2-21

図2-22 に、 割 り 込みポー ト の設定ページ を示 し ます。

GIC は、 PS および PL か ら CPU に送信 さ れる割 り 込みを管理する集中型 リ ソ ース です。 コ ン ト ロー ラ ーは、 プ ロ グ ラ ム さ れた と お り に割 り 込み ソ ース を イ ネーブルま たはデ ィ ス エーブルに し 、 優先順位を付けて、 選択 し た CPU に

送信 し ます。CPU イ ン ターフ ェ イ スは、 それに応 じ て次の割 り 込みを受信 し ます。 コ ン ト ロー ラ ーでは、 セキ ュ リ

テ ィ 重視のシ ス テ ム を イ ンプ リ メ ン ト す る 際のセキ ュ リ テ ィ 拡張 も サポー ト さ れてい ます。

コ ン ト ロ ー ラ ーは、ARM Generic Interrupt Controller Architecture バージ ョ ン 1.0 (GIC v1) (ベ ク ターな し) をベース に し

てい ます。

CPU のプ ラ イベー ト バスは、 一時的な妨害やイ ン ターコ ネ ク ト でのボ ト ルネ ッ ク を回避し て レ ジ ス タ にア ク セ ス し 、 高速な読み出 し/書き込み応答を可能に し ます。

すべての割 り 込み ソ ース が割 り 込み分配器に集め ら れ、 優先度の高い割 り 込みが個々の CPU に送信 さ れます。

X-Ref Target - Figure 2-22

GIC を使用する こ と で、 1 つの割 り 込みで複数の CPU を ターゲ ッ ト と し て も 、 一度に 1 つの CPU のみが割 り 込みを 受信す る よ う にで き ます。 すべての割 り 込み ソ ース には、 割 り 込み ID 番号 と 、 設定可能な優先順位お よびターゲ ッ

ト CPU の リ ス ト が含まれてい ます。

Zynq-7000 デバ イ ス の ロ ジ ッ ク ブ ロ ッ ク に関する情報は、『Zynq-7000 All Programmable SoC テ ク ニカル リ フ ァ レ ン ス

マニ ュ アル』 (UG585) [参照 6] および 『Zynq-7000 All Programmable SoC ソ フ ト ウ ェ ア開発者向けガ イ ド 』 (UG821) [参

照2] を参照 し て く だ さ い。

PS および PL 間のイ ン タ ー コ ネ ク ト

AXI_HP イ ン タ ー フ ェ イ ス

4 つの AXI_HP イ ン ターフ ェ イ スは、 DDR および OCM メ モ リ への高帯域幅のデータ パス を持つ PL バス マ ス ターを 提供 し ます。 各 イ ン タ ーフ ェ イ ス には、 読み出 し お よ び書 き 込み用に 2 つの FIFO バ ッ フ ァ ーが含まれます。 PL か ら メ モ リ への イ ン タ ー コ ネ ク ト では、 高速 AXI_HP ポー ト が 2 つの DDR メ モ リ ポー ト ま たは OCM のいずれかに配線 さ れます。AXI_HP イ ン ターフ ェ イ スは、 バ ッ フ ァ ー機能を強調 し て AXI FIFO イ ン ターフ ェ イ ス (AFI) と 呼ばれ

る こ と も あ り ます。

重要: PL ロ ジ ッ ク が通信で き る よ う にする ため、 LVL_SHFTR_EN を使用し て PL レベル シ フ ターを イ ネーブルにす

る 必要があ り ます。

Page Navigator で [PS-PL Configuration] を ク リ ッ ク し て [HP Slave AXI Interface] オプシ ョ ン を展開 し、 こ れ ら の イ ン

タ ーフ ェ イ ス を イ ネーブルに し て く だ さ い (図2-24)。

X-Ref Target - Figure 2-23

こ の イ ン タ ーフ ェ イ ス は、PL マ ス ター と 、 DDR やオンチ ッ プ RAM を含む PS メ モ リ の間に高スループ ッ ト データ パ ス を提供 し ます。 主な機能は次の と お り です。 32 ビ ッ ト ま たは 64 ビ ッ ト データ幅のマ ス ター イ ン ターフ ェ イ ス (ポー ト ご と に個別にプ ロ グ ラ ム) • 32 ビ ッ ト イ ン ターフ ェ イ ス モー ド でア ラ イ メ ン ト さ れた転送を効率的に 64 ビ ッ ト にダ イ ナ ミ ッ ク 拡張 (AxCACHE を使用 し て制御可能) • 32 ビ ッ ト イ ン ターフ ェ イ ス モー ド でア ラ イ メ ン ト さ れていない 32 ビ ッ ト 転送を 64 ビ ッ ト に自動拡張 • 書 き 込み コ マ ン ド の解放 し き い値を プ ロ グ ラ ム可能 • PL - PS 間のすべての AXI イ ン ターフ ェ イ ス で非同期 ク ロ ッ ク 周波数の ク ロ ッ ク 乗せ換えが可能 • 読み出 しお よび書き込みの両方に 1 KB (128 × 64 ビ ッ ト ) データ FIFO を使用し て レ イ テ ンシの長い転送を円滑化 • PL ポー ト か ら QoS 信号を使用可能 • PL に対し て使用可能な コ マン ド およびデータ FIFO のフ ィ ル レベル カ ウ ン ト • 標準 AXI 3.0 イ ン ターフ ェ イ ス をサポー ト • 読み出 し コ マ ン ド と 書 き 込み コ マ ン ド 別に、 イ ン タ ー コ ネ ク ト への コ マ ン ド 発行を プ ロ グ ラ ム可能 • 14 ~ 70 個の コ マン ド (バース ト 長に依存) の範囲で大容量の ス レーブ イ ン ターフ ェ イ ス読み出し を受諾可能 • 8 ~ 32 個の コ マン ド (バース ト 長に依存) の範囲で大容量の ス レーブ イ ン ターフ ェ イ ス書き込みを受諾可能

X-Ref Target - Figure 2-24

AXI_ACP イ ン タ ー フ ェ イ ス

ア ク セ ラ レー タ コ ヒ ーレ ン シ ポー ト (ACP) は、 プ ロ グ ラ マブル ロ ジ ッ ク マ ス ターにオプシ ョ ンの コ ヒ ーレ ン シお

よ び L1/L2 キ ャ ッ シ ュ を使用し て レ イ テ ン シの短いア ク セ ス を提供 し ます。

シ ス テ ムの観点か ら は、ACP イ ン ターフ ェ イ ス の接続は APU CPU と 似てい ます。 接続が似てい る こ と か ら 、 ACP

は APU ブ ロ ッ ク の外側で リ ソ ース ア ク セ ス を直接競い合い ます。

重要: PL ロ ジ ッ ク が通信で き る よ う にする ため、 LVL_SHFTR_EN を使用し て PL レベル シ フ ターを イ ネーブルにす

る 必要があ り ます。

[Zynq Block Design] で [64b AXI ACP Slave Ports] ブ ロ ッ ク を ク リ ッ ク し、 AXI_ACP を設定 し ます。

ま たは、[PS-PL Configuration] を ク リ ッ ク し て [ACP Slave AXI Interface] を展開 し ます。

図2-26 に、 ACP AXI ス レーブ イ ン ターフ ェ イ ス の設定を示 し ます。

X-Ref Target - Figure 2-25

図 2-25: AXI_ACP ブ ロ ッ ク

X-Ref Target - Figure 2-26

AXI_GP イ ン タ ー フ ェ イ ス

AXI_GP には、 次の よ う な機能があ り ます。 • 標準 AXI プ ロ ト コ ル • デー タ バス幅: 32 • マ ス タ ー ポー ト ID 幅: 12 • マ ス タ ー ポー ト 発行能力: 8 読み出 し、 8 書き込み • ス レーブ ポー ト ID 幅: 6 • ス レーブ ポー ト 受諾能力: 8 読み出 し、 8 書き込み こ れ ら の イ ン タ ーフ ェ イ ス は、 マ ス タ ー イ ン ターコ ネ ク ト およびス レーブ イ ン ターコ ネ ク ト のポー ト に直接接続 さ れます。 複雑な FIFO バ ッ フ ァ ーを使用 し てパフ ォーマン スおよびスループ ッ ト を増加する AXI_HP と は異な り 、 追 加の FIFO バ ッ フ ァ ーは使用 さ れません。 こ のため、 パフ ォーマン スはマ ス ター イ ン ターコ ネ ク ト と ス レーブ イ ン タ ー コ ネ ク ト に よ っ て制限 さ れます。 こ れ ら の イ ン タ ーフ ェ イ ス は、 汎用目的のみに使用 さ れ、 高パフ ォーマ ン ス を達成す る ための も のではあ り ません。 重要: PL ロ ジ ッ ク が通信で き る よ う にする ため、 LVL_SHFTR_EN を使用し て PL レベル シ フ ターを イ ネーブルにす る 必要があ り ます。[Zynq Block Design] で次のブ ロ ッ ク を ク リ ッ ク し、 AXI_GP イ ン ターフ ェ イ ス を設定 し ます。

ま たは、Page Navigator で [PS-PL Configuration] を ク リ ッ ク し て、 [GP Master AXI Interface] および [GP Slave AXI

Interface] オプシ ョ ン を展開 し ます。

X-Ref Target - Figure 2-27

図2-28 に、 GP AXI マ ス ターおよびス レーブの設定を示し ます。

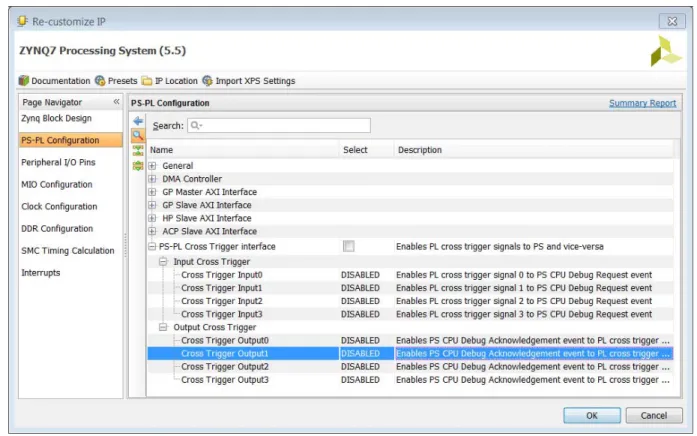

PS-PL ク ロ ス ト リ ガー イ ン タ ー フ ェ イ ス

エンベデ ッ ド ク ロ ス ト リ ガー (ECT) は、 ク ロ ス ト リ ガーの メ カニズ ムです。 ECT を使用する こ と に よ り 、 CoreSight

コ ン ポーネ ン ト は ト リ ガーを送受信 し 、 ほかの コ ン ポーネ ン ト と 通信で き ます。ECT は、 次の 2 つの コ ンポーネン ト と 共に イ ンプ リ メ ン ト さ れます。 • ク ロ ス ト リ ガー マ ト リ ッ ク ス (CTM) • ク ロ ス ト リ ガー イ ン ターフ ェ イ ス (CTI) 1 つま たは複数の CTM を組み合わせて、 複数チ ャ ネルを持つ イベン ト ブ ロー ド キ ャ ス ト ネ ッ ト ワー ク を形成 し ま す。CTI は、 1 つま たは複数チ ャ ネルで イ ベン ト を検出し、 受信し た イ ベン ト を ト リ ガーにマ ッ プ し 、 ト リ ガーを

CTI に接続 さ れた 1 つま たは複数の CoreSight コ ンポーネ ン ト に送信 し ます。 ま た、 接続 さ れた CoreSight コ ンポーネ

ン ト か ら の ト リ ガーを ま と めてマ ッ プ し て、 それ ら を 1 つま たは複数チ ャ ネルの イベン ト と し てブ ロー ド キ ャ ス ト し ます。CTM および CTI はど ち ら も 、 コ ン ト ロールおよびア ク セ ス ク ラ ス の CoreSight コ ンポーネン ト です。 ECT は、 次を使用し て構成 さ れます。 • 4 つのブ ロー ド キ ャ ス ト チ ャ ネル • 4 つの CTI 注記: パワーダ ウ ンはサポー ト さ れません。

X-Ref Target - Figure 2-28

ク ロ ス ト リ ガーは、ZYNQ7 Processing System の [Re-customize IP] ダ イ ア ロ グ ボ ッ ク ス で [PS-PL Configuration] ページ の [PS-PL Cross Trigger Interface] を展開 し、 チ ェ ッ ク ボ ッ ク ス をオンにする と イ ネーブルにで き ます。

プ ログ ラ マ ブル ロ ジ ッ ク (PL) の使用

PL は、 ユーザーが コ ン フ ィ ギ ュ レーシ ョ ン可能な機能を持つ豊富なアーキテ ク チ ャ を提供し ます。 コ ン フ ィ ギ ャ ラ ブル ロ ジ ッ ク ブ ロ ッ ク (CLB) • 6 入力ル ッ ク ア ッ プ テーブル (LUT) (LUT 内に メ モ リ 機能あ り ) • レ ジ ス タ お よ びシ フ ト レ ジ ス タ の機能 • カ ス ケー ド 可能な加算器 36 Kb ブ ロ ッ ク RAM • 最大 72 ビ ッ ト 幅ま でのデュ アル ポー ト • デ ュ アル 18 Kb と し て コ ン フ ィ ギ ュ レーシ ョ ン可能 • プ ロ グ ラ マブル FIFO ロ ジ ッ ク • ビル ト イ ン エ ラ ー訂正回路X-Ref Target - Figure 2-29

DSP デジ タ ル信号処理: DSP48E1 ス ラ イ ス • 25 × 18 の 2 の補数の乗算器/ア キ ュ ム レータ の高解像度 (48 ビ ッ ト ) シグナル プ ロ セ ッ サ • 対称フ ィ ル タ ー アプ リ ケーシ ョ ン を最適化する ため各加算器で 25 ビ ッ ト の消費電力削減 • ア ド バン ス機能: オプシ ョ ンのパ イ プ ラ イ ン処理、 オプシ ョ ンの ALU、 カ ス ケー ド 専用バス ク ロ ッ ク 管理 • ス キ ュ ーの小 さ い ク ロ ッ ク 分配用の高速バ ッ フ ァ ーお よ び配線 • 周波数合成お よ び位相シ フ ト • ジ ッ タ ーの少ない ク ロ ッ ク の生成お よ びジ ッ タ ー フ ィ ル ター 設定可能 I/O • 高パフ ォーマ ン ス の SelectIO™ テ ク ノ ロ ジ • シ グナル イ ン テ グ リ テ ィ を向上する ためのパ ッ ケージ内の高周波数デカ ッ プ リ ン グ キ ャ パシ タ • 低消費電力、 高速の I/O 操作用に ト ラ イ ス テー ト にで き るデジ タ ル制御 イ ン ピーダン ス

• HR (High Range) I/O で 1.2 ~ 3.3V をサポー ト

• HP (High Performance) I/O で 1.2V ~ 1.8V をサポー ト (7z030、 7z045、 および 7z100 デバ イ ス)

低消費電力のギガ ビ ッ ト ト ラ ン シーバー • 7z030、 7z045、 および 7z100 デバ イ ス • 最大 12.5 Gb/s ま で処理可能な高パフ ォーマン ス ト ラ ン シーバー (GTX) • チ ッ プ間 イ ン タ ーフ ェ イ ス用に最適化 さ れた低消費電力モー ド • ア ド バン ス送信プ リ エン フ ァ シ ス/ポ ス ト エン フ ァ シ ス、 レ シーバー リ ニア (CTLE)、 追加マージ ン用の適応等 化を含む判定帰還等化 (DFE) アナ ロ グ/デジ タ ル コ ンバー ター (XADC) • デ ュ アル 12 ビ ッ ト 1 MSPS アナ ロ グ/デジ タ ル コ ンバー ター (ADC) • 最大 17 個の柔軟性のあ る ユーザー設定可能なアナ ロ グ入力 • オンチ ッ プ ま たは外部基準オプシ ョ ン • オンチ ッ プ温度 (±4℃ 最大誤差) および電源 (±1% 最大誤差) センサー • ADC 測定に継続 JTAG ア ク セ ス PCI Express デザ イ ン用統合イ ン ターフ ェ イ ス ブ ロ ッ ク (7z030、 7z045、 および 7z100 デバ イ ス用) • エン ド ポ イ ン ト お よ びルー ト ポー ト 機能を含む PCI Express ベース の仕様 2.1 と 互換性あ り • Gen1 (2.5 Gb/s) および Gen2 (5.0 Gb/s) 速度をサポー ト ア ド バン ス コ ン フ ィ ギ ュ レーシ ョ ン オプシ ョ ン、 ア ド バン ス エ ラ ー レ ポー ト (AER)、 エン ド ツー エン ド CRC (ECRC)

カ ス タ ム ロ ジ ッ ク

Vivado IP パ ッ ケージ ャーを使用する と 、 ユーザーお よびサー ド パーテ ィ の IP (Intellectual Property) を Vivado IDE の Vivado IP カ タ ロ グか ら 使用で き る よ う にする こ と がで き ます。 こ の よ う に準備 さ れたサー ド パーテ ィ IP は、 Vivado Design Suite のデザ イ ンに イ ン ス タ ン シエー ト で き ます。

Vivado Design Suite の IP パ ッ ケージ フ ローを使用し て IP を開発する と 、 ザ イ リ ン ク ス IP、 サー ド パーテ ィ IP、 ま た

はカ ス タ マー開発 IP のどれで も Vivado Design Suite で同様に使用で き ます。

IP の開発時には、 IP パ ッ ケージ ャ ーを使用し て IP フ ァ イ ル と 関連データ を ZIP フ ァ イ ルにパ ッ ケージ化 し ます。 こ の生成 さ れた ZIP フ ァ イ ルを Vivado Design Suite の IP カ タ ロ グに イ ン ス ト ールする と 、 パ ラ メ ーターを選択 し て IP

を カ ス タ マ イ ズ し 、IP イ ン ス タ ン ス を生成で き る よ う にな り ます。 詳細は、 『Vivado Design Suite ユーザー ガ イ ド : IP

イ ン テ グ レー タ ーを使用 し た IP サブシ ス テ ムの設計』 (UG994) [参照 5] および 『Vivado Design Suite チ ュー ト リ アル:

IP イ ン テ グ レーターを使用 し た IP サブシ ス テ ムの設計』 (UG995) [参照 8] を参照し て く だ さ い。 推奨: IP をユーザーに渡す前に IP のパ ッ ケージに問題がない こ と を確認する ため、各 IP モジ ュールで IP ユーザー フ ロ ーを完全に実行 し 、IP が使用可能な状態であ る かど う かを検証する こ と をお勧め し ます。

Zynq-7000 プ ロ セ ッ シ ング シ ス テムのシ ミ ュ レーシ ョ ン

Zynq-7000 バス フ ァ ン ク シ ョ ン モデル (BFM) では、 Zynq-7000 ベース のアプ リ ケーシ ョ ンの論理シ ミ ュ レーシ ョ ン がサポー ト さ れます。BFM は、 PS-PL イ ン ターフ ェ イ スお よびプ ロ セ ッ シ ン グ シ ス テ ム (PS) ロ ジ ッ ク の OCM/DDR メ モ リ を模倣す る こ と に よ り 、 プ ロ グ ラ マブル ロ ジ ッ ク (PL) の機能検証を可能に し ます。 こ の BFM は暗号化 さ れた Verilog モジ ュールのパ ッ ケージ と し て提供 さ れてい ます。 BFM の操作は、 Verilog 構文フ ァ イ ルの Verilog タ ス ク

のシーケ ン ス に よ り 制御 さ れます。

機能

• ピ ン互換性のあ る 、Verilog ベース のシ ミ ュ レーシ ョ ン モデル • すべての AXI イ ン ターフ ェ イ ス をサポー ト ° AXI 3.0 に準拠 • 分散 メ モ リ モデル (DDR 用) および RAM モデル (OCM 用) • Verilog タ ス ク ベース の API• Vivado Design Suite で提供

• ブ ロ ッ キ ン グお よ び ノ ンブ ロ ッ キ ン グの割 り 込みをサポー ト

ア プ リ ケーシ ョ ン

Zynq-7000 BFM は、 Zynq-7000 PS ロ ジ ッ ク のシ ミ ュ レーシ ョ ン環境を提供する も ので、 通常デザ イ ンの ZYNQ7 Processing System ブ ロ ッ ク に置き換わ る も のです。 Zynq-7000 BFM モデルには、 次の よ う な機能があ り ます。

• AXI BFM マ ス ター API 呼び出 し に よ り PS マ ス ターか ら 開始 さ れる ト ラ ンザ ク シ ョ ン • PS ス レーブか ら イ ン ターコ ネ ク ト モデルを介 し た OCM および DDR メ モ リ のモデルで終了する ト ラ ンザ ク シ ョ ン • FCLK リ セ ッ ト および ク ロ ッ ク 供給サポー ト • PL か ら PS への入力割 り 込み • PS レ ジ ス タ マ ッ プ Zynq BFM の詳細は、 『Zynq-7000 バス フ ァ ン ク シ ョ ン モデル データ シー ト 』 (DS897) を参照 し て く だ さ い。

エ ンベデ ッ ド IP カ タ ログ

Vivado IP カ タ ロ グは、 IP の検索、 詳細情報の確認、 関連資料の表示を実行可能な統合 リ ポジ ト リ です。 Vivado IP カタ ロ グにサー ド パーテ ィ IP ま たはカ ス タ マー IP を追加する と 、 Vivado Design Suite フ ローか ら その IP にア ク セ ス で

き る よ う にな り ます。

図2-30 に、 Vivado IDE の IP イ ン テグ レーター内の IP カ タ ロ グ を示し ます。

X-Ref Target - Figure 2-30

設計ア シス タ ン ス を使用 し た接続

ZYNQ-7000 PS ま たは Zynq UltraScale+ MPSoC を設定し た ら 、 デバ イ ス のプ ロ グ ラ マブル ロ ジ ッ ク (PL) 部分に含め

る ほかの IP を イ ン ス タ ン シエー ト で き ます。 IP イ ン テ グ レーター キ ャ ンバス を右 ク リ ッ ク し、 [Add IP] を ク リ ッ ク し ます。 Vivado IP イ ン テグ レー ターには、 IP サブシ ス テ ム デザ イ ンの残 り の部分を完了 さ せる ため、 ブ ロ ッ ク オー ト メ ー シ ョ ンお よ び コ ネ ク シ ョ ン オー ト メ ーシ ョ ン と い う 2 つのビル ト イ ン機能があ り ます。 こ れ ら の機能を使用する と 、 基本的なマ イ ク ロ プ ロ セ ッ サ シ ス テ ム を IP イ ン テ グ レーター ツールで作成 し、 ポー ト を外部 I/O ポー ト に簡単に接 続で き ます。

ブ ロ ッ ク オー ト メ ーシ ョ ン

ブ ロ ッ ク オー ト メ ーシ ョ ンは、 Zynq-7000 AP SoC、 Zynq UltraScale+ MPSoC、 MicroBlaze プ ロ セ ッ サな どのマ イ ク ロ

プ ロ セ ッ サ、 ま たは一部の階層 IP を IP イ ン テグ レーター ツールのブ ロ ッ ク デザ イ ンに イ ン ス タ ン シエー ト する際

に使用で き ます。

図2-31 に示 さ れてい る [Run Block Automation] を ク リ ッ ク する と 、 単純な Zynq プ ロ セ ッ シ ン グ シ ス テ ム を簡単に作

成で き ます。

X-Ref Target - Figure 2-31

[Run Block Automation] ダ イ ア ロ グ ボ ッ ク ス には、図2-32 に示すよ う に、 オー ト メ ーシ ョ ンで使用可能なオプシ ョ ン

が表示 さ れます。 タ ーゲ ッ ト リ フ ァ レ ン ス ボー ド を使用 し てい る場合は、 [Apply Board Preset] チ ェ ッ ク ボ ッ ク ス を

オンにす る と 、 ボー ド プ リ セ ッ ト を イ ネーブルにで き ます。

[OK] を ク リ ッ ク する と 、 ブ ロ ッ ク オー ト メ ーシ ョ ン機能に よ り 、図2-33 の よ う な基本的なシ ス テ ムが作成 さ れます。

X-Ref Target - Figure 2-32

図 2-32: ZYNQ7 Processing System ブ ロ ッ クの [Run Block Automation] ダ イ ア ログ ボ ッ ク ス

X-Ref Target - Figure 2-33

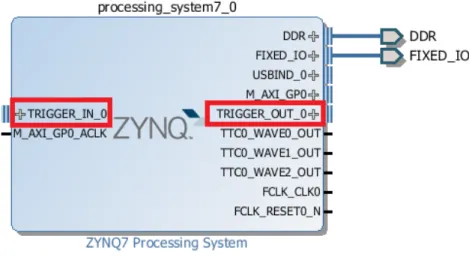

[Run Block Automation] ダ イ ア ロ グ ボ ッ ク ス の [Cross Trigger In] および [Cross Trigger Out] で適切な機能を選択する と 、 ク ロ ス ト リ ガー機能を イ ネーブルにで き ます。

[Cross Trigger In] お よび [Cross Trigger Out] のデフ ォル ト 値は [Disable] ですが、 [Enable] ま たは [New ILA] を選択する と 、 ク ロ ス ト リ ガーを使用で き ます。

[Cross Trigger In] お よび [Cross Trigger Out] で [Enable] を選択する と 、 ZYNQ7 の ク ロ ス ト リ ガー ピ ンが 1 つだけ使用 可能にな り ます。 こ れ ら の ピ ンへの接続は、 ユーザーが指定す る 必要があ り ます。

X-Ref Target - Figure 2-34

図 2-34: [Run Block Automation] ダ イ ア ログ ボ ッ ク スのク ロ ス ト リ ガー機能オプシ ョ ン

X-Ref Target - Figure 2-35

[New ILA] を選択する と 、 ク ロ ス ト リ ガー ピ ンが イ ネーブルにな る だけでな く 、 ILA (Integrated Logic Analyzer) コ ア に も 接続 さ れます。 Vivado IP イ ン テグ レー ターでは、ZC702 の よ う なザ イ リ ン ク ス ターゲ ッ ト リ フ ァ レ ン ス プ ラ ッ ト フ ォーム を使用 し てい る 場合、 ボー ド オー ト メ ーシ ョ ン機能 も 提供 さ れます。 詳細は、43 ページの 「IP イ ン テ グ レーターでのプ ラ ッ ト フ ォーム ボー ド フ ロー」 を参照 し て く だ さ い。 こ の機能を使用す る と 、IP のポー ト が ターゲ ッ ト ボー ド の FPGA ピ ンに接続 さ れます。 IP は適切に設定 さ れ、 ユー ザーの選択に基づいて I/O ポー ト に接続 さ れます。 ボー ド オー ト メ ーシ ョ ンでは、 物理制約が必要な IP に対し て自 動的に物理制約が生成 さ れます。 図2-33 で、 外部 DDR および FIXED_IO イ ン ターフ ェ イ ス が外部ポー ト に接続 さ れてい る こ と を確認し て く だ さ い。

コ ネ ク シ ョ ン オー ト メ ーシ ョ ン

IP イ ン テ グ レーターでキ ャ ンバス上に イ ン ス タ ン シエー ト さ れた IP の間に可能な接続が検出 さ れた場合、 コ ネ ク シ ョ ン オー ト メ ーシ ョ ン機能を使用で き ます。図2-37 では、 ZYNQ7 Processing System IP と 共に AXI BRAM Controller と Block Memory Generator IP が イ ン ス タ ン シ

エー ト さ れてい ます。

IP イ ン テ グ レーターで AXI BRAM Controller と ZYNQ7 Processing System IP の間に可能な接続が検出 さ れる ので、 コ

ネ ク シ ョ ン オー ト メ ーシ ョ ン機能を使用で き ます。

X-Ref Target - Figure 2-36

[Run Connection Automation] を ク リ ッ ク する と 、 次が実行 さ れます。

• AXI Interconnect、 Block Memory Generator、 および Processor System Reset IP が イ ン ス タ ン シエー ト さ れます。

• AXI Interconnect を使用 し て AXI BRAM Controller が ZYNQ Processing System IP に接続 さ れます。

• Processor System Reset IP が図2-38 に示す よ う に正 し く 接続 さ れます。

X-Ref Target - Figure 2-37

図 2-37: [Run Connection Automation] 機能を使用 し た接続

X-Ref Target - Figure 2-38

手動接続

図2-39 に、 ILA SLOT_0_AXI を、 監視する必要のあ る AXI イ ン ターフ ェ イ ス に接続する方法を示 し ます。 こ れは、

手動で実行で き ます。

カー ソ ルを IP ブ ロ ッ ク の イ ン ターフ ェ イ ス ま たはピ ン コ ネ ク タ の近 く に移動する と 、 カー ソ ルの形が鉛筆形に変わ

り ます。IP ブ ロ ッ ク の イ ン ターフ ェ イ ス ま たはピ ン コ ネ ク タ を ク リ ッ ク し、 接続先ブ ロ ッ ク に ド ラ ッ グ し ます。

X-Ref Target - Figure 2-39

I/O ポー ト の手動作成 と 接続

Vivado IP イ ン テグ レー ターでは、 手動で外部 I/O ポー ト を作成で き ます。 ピ ン、 バス、 ま たは イ ン ターフ ェ イ ス接

続を選択す る と 、 信号お よ び イ ン タ ーフ ェ イ ス を外部 I/O ポー ト に接続で き ます。

手動で I/O ポー ト を作成 し て接続する には、 ブ ロ ッ ク 図のポー ト を右 ク リ ッ ク し て、 次を ク リ ッ ク し ます。

• [Make External]: Ctrl キーを押し なが ら ク リ ッ ク し て複数のピ ン を選択 し てか ら 、 [Make External] を ク リ ッ ク で き

ます。 こ の コ マ ン ド に よ り 、IP のピ ンがブ ロ ッ ク デザ イ ンの I/O ポー ト に接続 さ れます。

• [Create Port]: ク ロ ッ ク 、 リ セ ッ ト 、 uart_txd な どの イ ン ターフ ェ イ ス以外の信号を接続する のに使用 し ます。

[Create Port] を使用する と 、 入力/出力、 ビ ッ ト 幅、 タ イ プ (clk、 reset、 ま たは data) の指定をユーザーが制 御 し やす く な り ます。 ク ロ ッ ク の場合、 入力周波数 も 指定で き ます。

• [Create Interface Port]: 機能を共有する信号を グループ化する イ ン ターフ ェ イ ス ポー ト を作成し ます。

た と えば、S_AXI は複数のザ イ リ ン ク ス IP の イ ン ターフ ェ イ ス ポー ト です。 こ の コ マン ド を使用する と 、 イ ン

タ ーフ ェ イ ス タ イ プおよびモー ド (マ ス ターま たはス レーブ) の指定を よ り 詳細に制御で き ます。

設計ア シス タ ン ス

IP イ ン テ グ レーターでは、 AXI ス ト リ ー ミ ン グ イ ン ターフ ェ イ ス が AXI メ モ リ マ ッ プ ド イ ン ターフ ェ イ ス に接続

さ れ る 際に、 設計ア シ ス タ ン ス が提供 さ れます。図2-40 の例では、 ス ト リ ー ミ ン グ イ ン ターフ ェ イ ス を含む FIR

Compiler IP を ZYNQ7 Processing System の ス レーブ ACP ポー ト に接続し よ う と し てい ます。

X-Ref Target - Figure 2-40

設計ア シ ス タ ン ス を使用す る には、図2-41 に示すよ う に、 FIR Compiler の M_AXIS_DATA イ ン ターフ ェ イ ス ピ ン と ZYNQ7 Processing System の S_AXI_ACP ポー ト 間を直接接続 し ます。

[Make Connection] ダ イ ア ロ グ ボ ッ ク ス が開き、 ス ト リ ーム バス イ ン ターフ ェ イ ス /fir_compiler_0/M_AXIS_DATA が メ モ リ マ ッ プ ド バス イ ン ターフ ェ イ ス

/processing_system7_0/S_AXI_ACP に接続 さ れる こ と を確認する メ ッ セージが表示 さ れます。 ま た、 ス ト リ ー ミ ン グ イ ン ターフ ェ イ ス と メ モ リ マ ッ プ ド イ ン ターフ ェ イ ス の ク ロ ッ ク 供給オプシ ョ ン も 設定で き ます。 デフ ォル

ト は [Auto] です。

X-Ref Target - Figure 2-41

図 2-41: 設計アシス タ ン スの起動

X-Ref Target - Figure 2-42

設計ア シ ス タ ン ス に よ り 、 高周波数/中周波数転送用に設定 さ れた DMA コ アが イ ン ス タ ン シエー ト さ れ、 設定後に [OK] を ク リ ッ ク する と 、 設定に基づいて接続 さ れます。

設計ア シ ス タ ン ス に よ り AXI Subset Converter、 AXI Direct Memory Access、 AXI Interconnect が イ ン ス タ ン シエー ト さ

れ、FIR Compiler の ス ト リ ー ミ ン グ イ ン ターフ ェ イ ス と PS7 の ACP イ ン ターフ ェ イ ス が接続 さ れます。AXI4-Stream

Subset Converter は、 互換性に若干の問題があ る AXI4-Stream 信号セ ッ ト を接続する ための ソ リ ューシ ョ ン を提供 し

ます。IP には、 イ ン ターフ ェ イ ス ご と に設定可能な AXI4-Stream 信号が含まれ、 一貫し た方法で 1 つの信号セ ッ ト

を別の信号セ ッ ト に変換で き ます。

IP イ ン テグ レー タ ーでのプ ラ ッ ト フ ォ ーム ボー ド フ ロー

Vivado Design Suite では、 ボー ド が自動的に認識 さ れます。 ターゲ ッ ト ボー ド に含まれる さ ま ざ ま な コ ンポーネン ト

が認識 さ れ る ので、IP を カ ス タ マ イ ズ し て、 そのボー ド の コ ンポーネン ト に接続 さ れ る よ う に IP を イ ン ス タ ン シ エー ト お よ び設定で き ます。 現在の と こ ろ、 複数の 7 シ リ ーズ ボー ド および Kintex UltraScale ボー ド がサポー ト さ れ てい ます。 IP イ ン テ グ レーターでは、 ボー ド に存在する コ ンポーネン ト すべてが [Board] ウ ィ ン ド ウ に表示 さ れます。 こ の ウ ィ ン ド ウ を使用 し て必要な コ ン ポーネ ン ト を選択 し 、IP イ ン テ グ レーターで提供 さ れ る設計アシ ス タ ン ス を使用する と 、 ブ ロ ッ ク デザ イ ン を選択 し たボー ド コ ンポーネ ン ト に簡単に接続で き ます。 I/O 制約はすべて こ のフ ローの一

部 と し て自動的に生成 さ れます。 詳細は、 『Vivado Design Suite ユーザー ガ イ ド : IP イ ン テグ レーターを使用 し た IP

サブシ ス テ ムの設計』 (UG994) [参照 5] のこ のセ ク シ ョ ンを参照 し て く だ さ い。

X-Ref Target - Figure 2-43

[Address Editor] ウ ィ ン ド ウでの メ モ リ マ ッ プ

ブ ロ ッ ク デザ イ ンに イ ン ス タ ン シエー ト さ れたペ リ フ ェ ラ ル (ス レーブ) の メ モ リ マ ッ プは自動的に割 り 当て ら れま

すが、 ア ド レ ス を手動で割 り 当て る こ と も で き ます。 こ のデザ イ ンのア ド レ ス マ ッ プを生成する には、 次を実行 し

ます。

1. ブ ロ ッ ク 図の上にあ る [Address Editor] タ ブを ク リ ッ ク し ます。

2. ツールバーの [Auto Assign Address] を ク リ ッ ク し ます。

ア ド レ ス は、[Offset Address] および [Range] 列に値を入力 し て手動で設定する こ と も で き ます。 詳細は、 『Vivado

Design Suite ユーザー ガ イ ド : IP イ ン テ グ レーターを使用 し た IP サブシ ス テ ムの設計』 (UG994) [参照 5] のこ のセ ク

シ ョ ンを参照 し て く だ さ い。

ヒ ン ト: [Address Editor] ウ ィ ン ド ウは、 バス マス ター と し て機能する IP (Zynq-7000 AP SoC、 Zynq UltraScale+ MPSoC

な ど) がデザ イ ンに含まれてい る場合にのみ表示 さ れます。

デザイ ン ルール チ ェ ッ クの実行

Vivado IP イ ン テグ レー ターでは、 デザ イ ン を作成中に リ アル タ イ ムで基本的な DRC が実行 さ れます。 ただ し、 デザ イ ン作成中にエ ラ ーが発生す る こ と があ り ます。 た と えば、 ク ロ ッ ク ピ ンの周波数が正 し く 設定 さ れていないな ど です。 包括的な DRC を実行する には、 [Validate Design] ツールバー ボ タ ン を ク リ ッ ク し ます。 警告お よ びエ ラ ーがない場合は、 それ ら がなかっ た こ と を示す メ ッ セージが表示 さ れます。ブ ロ ッ ク デザイ ンの最上位デザイ ンへの統合

ブ ロ ッ ク デザ イ ン を完成 し てデザ イ ン を検証 し た ら 、 次の 2 つの手順を実行し てデザ イ ン を完成 さ せます。 • 出力フ ァ イ ルの生成 • HDL ラ ッ パーの作成出力フ ァ イ ルを生成す る と 、Vivado IDE の [Sources] ウ ィ ン ド ウ にその IP の ソ ース フ ァ イ ル と 適切な制約が作成 さ れ ます。

プ ロ ジ ェ ク ト 作成時に タ ーゲ ッ ト 言語 と し て指定 し た言語に応 じ て、IP イ ン テ グ レーターに よ り 適切な フ ァ イ ルが

生成 さ れます。Vivado IDE で特定の IP の ソ ース フ ァ イ ルを指定 し た ターゲ ッ ト 言語で生成で き ない場合は、 コ ン

ソ ールにそれを示す メ ッ セージが表示 さ れます。

X-Ref Target - Figure 2-44

出力 フ ァ イルの生成

出力フ ァ イ ルを生成す る には、 次のいずれかを実行 し ます。

• [Sources] ウ ィ ン ド ウ の [Design Sources] フ ォルダー階層を展開し てデザ イ ン を右 ク リ ッ ク し 、 [Generate Output

Products] を ク リ ッ ク し ます。

• Flow Navigator の [IP Integrator] の下の [Generate Block Design] を ク リ ッ ク し ます。

ブ ロ ッ ク デザ イ ンで使用 さ れるすべての IP に対 し て、 ソ ース フ ァ イ ルお よび最適な制約が生成 さ れます。 ソ ース

フ ァ イ ルは、 プ ロ ジ ェ ク ト 作成中ま たは [Project Settings] ダ イ ア ロ グ ボ ッ ク ス で指定 し た ターゲ ッ ト 言語に基づいて

生成 さ れます。 出力フ ァ イ ルの生成については、 『Vivado Design Suite ユーザー ガ イ ド : IP イ ン テグ レーターを使用 し

た IP サブシ ス テ ムの設計』 (UG994) [参照 5] のこ のセ ク シ ョ ンを参照 し て く だ さ い。

HDL ラ ッ パーの作成

IP イ ン テ グ レーターのブ ロ ッ ク デザ イ ンは、 それ よ り 上位のデザ イ ンに統合で き ます。 こ れには、 デザ イ ン を上位

の HDL フ ァ イ ルに イ ン ス タ ン シエー ト し ます。

上位に イ ン ス タ ン シエー ト す る には、Vivado IDE の [Sources] ウ ィ ン ド ウ でブ ロ ッ ク デザ イ ン を右 ク リ ッ ク し、

[Create HDL Wrapper] を ク リ ッ ク し ます。 Vivado には、 HDL ラ ッ パーを作成する際に 2 つの選択肢があ り ます。 • Vivado で ラ ッ パーを作成 し て自動的にア ッ プデー ト さ れる よ う にする オプシ ョ ン (デフ ォル ト ) • ユーザーが変更可能な ス ク リ プ ト を作成 し て、 ユーザーが編集お よ び管理で き る よ う にす る オプシ ョ ン。 こ の オプシ ョ ン を選択 し た場合、 ブ ロ ッ ク デザ イ ンでポー ト レベルの変更を加え る たびに、 ラ ッ パーを ア ッ プデー ト す る 必要があ り ます。

X-Ref Target - Figure 2-45

図 2-45: HDL ラ ッ パーの作成

こ れに よ り 、IP イ ン テ グ レーター サブシ ス テ ムの最上位 HDL フ ァ イ ルが生成 さ れます。 こ れで、 デザ イ ン をエ ラ ボ レーシ ョ ン、 合成、 イ ンプ リ メ ン テーシ ョ ン な ど のデザ イ ン フ ローで使用で き ます。

Vivado ピ ン プ ラ ンナーでの PS I/O の表示

PCB ピ ン プ ラ ンニ ン グのガ イ ド ラ イ ンお よび こ れ ら のデバ イ ス のデザ イ ンについては、 『Zynq-7000 All

Programmable SoC PCB デザ イ ン ガ イ ド 』 (UG933) [参照 9] を参照 し て く だ さ い。

Vivado IDE で生成 さ れたエ ンベデ ッ ド フ ァ イル

Vivado IP イ ン テグ レーターか ら Zynq-7000 ま たは Zynq UltraScale+ MPSoC プ ロ セ ッ サ ハー ド ウ ェ ア デザ イ ン を SDK

にエ ク ス ポー ト す る と 、IP イ ン テ グ レーターで次のフ ァ イ ルが生成 さ れます。

こ れ ら の生成フ ァ イ ルの詳細は、『Zynq-7000 All Programmable SoC ソ フ ト ウ ェ ア開発者向けガ イ ド 』 (UG821) [参照 2]

ま たは 『Zynq UltraScale+ MPSoC ソ フ ト ウ ェ ア開発者向けガ イ ド 』 (UG1137) [参照 3] を参照 し て く だ さ い。

表 2-1: IP イ ン テグレー タ ーで生成 さ れる フ ァ イル フ ァ イル 説明 system.xml SDK を起動する と デフ ォル ト で開き、 シ ス テ ムのア ド レ ス マ ッ プを表示 し ます。 ps7_init.c ps7_init.h Zynq プ ロ セ ッ シ ン グ シ ス テ ムの初期化コー ド と 、 DDR ク ロ ッ ク 、 PLL、 MIO の初期化設定 が含まれます。SDK では、 プ ロ セ ッ シ ン グ シ ス テ ム上でアプ リ ケーシ ョ ン を実行で き る よ う に、 プ ロ セ ッ シ ン グ シ ス テ ム を初期化する際に こ れ ら の設定が使用 さ れます。 プ ロ セ ッ シ ン グ シ ス テ ムの設定の中には、 ZC702 評価ボー ド 用に固定 さ れてい る も の も あ り ます。 ps7_init.tcl INIT フ ァ イ ルの Tcl バージ ョ ンです。 ps7_init.html INIT フ ァ イ ルは初期化デー タ を記述 し ます。

![図 2-12: [MIO Configuration] ページ を使用 し たペ リ フ ェ ラル I/O ピ ンの設定](https://thumb-ap.123doks.com/thumbv2/123deta/8505903.924138/16.918.240.741.141.512/図22MIOConfigurationページを使用しペリフェラルIOピンの設定.webp)

![図 2-37: [Run Connection Automation] 機能を使用 し た接続](https://thumb-ap.123doks.com/thumbv2/123deta/8505903.924138/39.918.144.830.114.469/図237RunConnectionAutomation機能を使用した接続.webp)

![図 3-6: [Peripheral I/O Pins] ページ を使用 し たペ リ フ ェ ラル I/O ピ ンの設定](https://thumb-ap.123doks.com/thumbv2/123deta/8505903.924138/53.918.140.837.188.611/図3PeripheralIOPinsページを使用しペリフェラルIOピンの設定.webp)