Sample

Agilent Technologies

PCI Express

®

信号評価ハンドブック

(第1版 2012年6月)

このドキュメントは検討用のサンプルです。その内容は配布版からの抜粋で構成されて おり、すべてのページは含んでいません。Sample

この資料に掲載されているオシロスコープ画面はAgilent Infiniium 90000Aシリーズをベースとした執筆時点

のもので、お手持ちのオシロスコープの画面と異なる場合があります。また、ご紹介している機能はオプ ションによるものを含みます。

Sample

目次

Page

5

はじめに(本書の目的と対象読者)

7

第

1章 PCI Express信号の基礎

7 1-1. PCI Express信号の概要 8 1-2. PCI Express関連仕様と信号規格 9 1-3. 設計時の注意事項11

第2章

PCI Expressの信号品質評価

11 2-1. 信号品質評価の目的 11 2-2. コンプライアンス試験とは 12 2-3. PCI-SIGの公式試験内容 13 2-4. プリ・コンプライアンス試験 13 2-5. まとめ15

第3章

Gen1/Gen2 CEMアドイン・カードの信号品質評価

15 3-1. 概要 15 3-2. 必要機材 18 3-3. 必要アクセサリ類 19 3-4. 測定前の準備 25 3-5. DUTの接続 27 3-6. 測定の実施(共通) 30 3-7. 測定の実施 (Revision 1.1仕様のアドイン・カードの場合) 35 3-8 測定の実施 (Revision 2.x仕様のアドイン・カードを2.5GT/sで評価する場合) 40 3-9. 測定の実施 (Revision 2.x仕様のアドイン・カードを5GT/sで評価する場合) 45 3-10. 結果の保存 46 3-11. 公式試験の必要機材と手順第4章

Gen1/Gen2 CEMのマザーボードの信号品質評価

(第2版以降で追加予定)第5章 組込みボードでの

PCI Express信号品質評価

(第2版以降で追加予定)53

付録

A. チャンル間スキューの確認方法

54

付録

B. アジレントN5393Cの詳細設定

Sample

はじめに (本書の目的と対象読者)

PCI Express技術は今や幅広く普及し、前身のPCIバスが幅広く利用されたのと同様に、様々な機 器に採用されています。このためエンジニアの皆様はPCI Express技術を採用した機器を設計す る機会が増えてきていますが、その一方で、2.5Gbpsや5Gbpsといった高速信号を初めて扱うこ とになった、という方も少なくありません。しかも、PCI Expressはシリアル伝送規格のため、 パラレル・バスに親しんできた方々の中には、PCI Express信号をどのように評価したら良いの か、戸惑う方も少なからずいらっしゃるのではないかと思います。 本書は、PCI Expressを初めて扱う方であっても、自信をもって測定を実施していただけるガイ ドとして作成しました。本書はPCI Express採用ボードの設計者や評価担当の皆様を主な対象と して、開発したボードの評価を、どんな機材を使い、どんな手順で測定したら良いかを解説し ています。また、評価をスムースに進めるためにボード設計の時点で考慮すべき点についても 説明しています。 PCI Express採用ボードの設計にあたって本書をご一読いただき、事前に十分な知識を得て準備 を行ない、安心して評価に臨んでいただきたいと思います。 なお、実際の測定に際してご不明な点が出てきた場合には、弊社フリーダイヤルのオンライン 技術部へお問い合わせください。十分な知識を持った担当の技術者がサポートさせていただき ます。 本書が皆様の設計・評価のお役に立てば幸いです。 アジレント・テクノロジー株式会社 電子計測本部 アプリケーション・エンジニアリング部 *** 本書の対象範囲 *** ・この版ではPCI Express規格がサポートする伝送速度のうち、2.5Gbpsおよび5Gbpsの伝送速度 の評価について解説しています。 ・本書ではPCI-SIGのCEM仕様に基づくマザーボードおよびアドイン・カードの評価を中心に解 説しています。また、ボード上でのLSI間の通信にPCI Express技術が使用される場合の評価に ついても扱います。 アジレント・テクノロジー 計測オンライン技術部 ☎0120-421-345Sample

第1章 PCI Express信号の基礎

本章では、評価の対象となるPCI Express信号の概要について説明します。詳細については、以 下の規格書等を参照してください。PCI Express Base Specification, Revision 3.0, PCI-SIG

PCI Express Card Electromechanical Specification, Revision 2.0, PCI-SIG

1-1. PCI Express信号の概要

PCI Expressはシリアル方式の通信規格で、PCI-SIG(Peripheral Component Interconnect Special

Interest Group)が制定したものです。その基本的な構造を図1.1に示します。通信は双方向です がバス構造ではなく、送信と受信の経路は分離されていて、LSI間は1対1で通信します。ある LSIが複数のLSIと通信する場合には、通信相手のLSI毎に信号路を設けます。CPUに近い最上流 のLSIを「ルート・コンプレックス」、その相手(最下流)を「エンド・ポイント」と呼びま す。その他、経路切替をする機能を持ったLSIを「スイッチ」、PCI Expressから他の通信規格へ 接続するLSIを「ブリッジ」と呼びます。 信号伝送は差動信号を使い、送信側2本、受信側2本が相手のLSIに接続されます。この基本的な 送受2ペアの通信路を「レーン」と呼びます。伝送帯域を増やすために、複数のレーンを使う ことができます。LSIの通信ポートがNレーンの構成の場合、xNのポートと表現します。また、 ポート間が接続された状態をリンクと呼びます。 現在のところ各レーンの通信速度(片方向)は2.5Gbps, 5Gbps, 8Gbpsが許されていますが、使用 する通信速度に加え、それよりも遅い速度も必ずサポートしなければなりません。つまり、 5Gbpsで通信するシステムの場合には、2.5Gbpsもサポートする必要があります。逆に、2.5Gbps のみを使う場合には、必ずしも5Gbpsをサポートする必要はありません。また、リンクの通信 速度としては5GT/sのように表現するのが一般的です(GT/s: giga transfers per second)。また、 基準クロック(Reference Clock)には100MHzが使われます。 PETp0 TX0 TX1 TX0 TX1 RX0 RX1 RX0 RX1 Clock buffer/ driver 基準クロック100MHz差動 基準クロック100MHz差動 Clock Gen

Root Complex End Point

PETn0 PERp0 PERn0 PETp1 PETn1 PERp1 PERn1 コネクタ

Sample

5Gbpsまでの信号では「de-emphasis(デエンファシス)」という技術が使われます。一般的に はpre-emphasis(プリエンファシス)と呼ばれる技術と同じ目的で、伝送路の損失によって信 号の高周波成分が失われるのを、あらかじめ送出側で補償しようとするものです。de-emphasis では、送出する信号の符号(1または0)が連続する場合に、2ビット目以後の信号振幅を、フ ル・スイングに対して3.5dB低いレベルで送出します(図1.2)。5Gbpsの場合には、-3.5dBに加 え、-6dBのde-emphasisも定義されています。1-2. PCI Express関連仕様と信号規格

PCI ExpressはPCIに続く第3世代のPCバスとして開発されました。このため、主にPC内部でLSI間 の通信に使われています。またPCIがそうであったように、PCI -SIGのPCI Express規格をベース として多数の規格が開発されているため、どの規格に対して評価しようとしているのかに注意 が必要です。これは、測定ポイントや評価基準が規格毎に異なるためです。 関連する代表的な規格を列挙してみると、以下のようなものがあります。括弧内は規格を制定 している団体を示しています。PCI Express Base Specification (PCI-SIG)

PCI Expressの一番元となる規格で、LSI端での信号規格およびLSIの動作を規定しています。

PCI Express Card Electromechanical Specification (PCI-SIG) マザーボードやアドイン・カードのための規格。

PCI Express Mini Card Electromechanical Specification (PCI-SIG) 主にノートPCの内部に装着する小型カードのための規格。 ExpressCard (USB-org) 主にノートPCの機能拡張スロットの規格。 図1.2 de-emphasis Tx p Rx n p n 差動ドライバ出力 VTX-D+ 差動信号成分 VTX-Diffp-pp (VTX-D+ - VTX-D-) 差動ドライバ出力 VTX-D- - 3.5dB VTX-Diffp-pp VTX-Diffp-pp Transition Bit : データの極性が反転し たビット。 Non-Transition Bit: De-emphasis Bit: 直前のビットとデータの 極性が同じビット。

0 1 1 1 0 1 0

0 1 1 1 0 1 0

De-emphasis : 同じ極性のビットが続く時、連続する極性の2ビット目以後は最初の ビット(極性が変化した時のビット)よりも3.5dB低い差動振幅で送出 する。 送出データが直 前のデータと 送出データの振幅 違う 高 (Transition Bit) 同じ 低 (De-emphasis Bit)Sample

CompactPCI Express (PICMIG)産業用PCでPCI Expressを使うための規格。

COM Express (PICMIG)

組込み用PCの規格。 信号の詳細については各規格を参照してください。なお、注意点として、評価の基準となるア イ・マスクを定義していない仕様もあります(例:Mini Card)。このような場合には測定する ことはできても、測定結果の妥当性を判断する基準が仕様に規定されておらず、判断基準を自 分で作る(決める)必要があります。

1-3. 設計時の注意事項

PCI Expressを採用したボードやシステムを設計する際には、評価についても設計段階から考慮 しておくことが重要です。 ・信号経路上のどのポイントで評価すべきなのか ・そのポイントに評価の基準はあるか(例:アイ・マスク) ・どのように信号を取り出すのか(プロービング) ・その場所でプロービングが可能か 等を検討します。 安定した通信をおこなうためには、受信側のLSIが信号を誤りなく受信できることが必要です。 このため、伝送信号の品質を評価する際に最も重要なのは信号の受信端ですから、ここでプ ロービングできるように常に考慮しておくべきです。 Tips: LSIがBGAパッケージであっても、スルーホールを設けてBGAの直下でプロービングできる ようにしておくと良いでしょう。プロービングの妨げにならないよう、スルーホールの上 に部品を配置しない考慮も必要です。プロービング点がLSIの受信端(ピン)から離れる (距離ができる)と、LSI受信端からの反射信号が信号に重畳するため、正しい観測が行 えません。プロービング点の近くにグラウンド・パッドを設けることができれば、信号を シングルエンドでも観測でき理想的です。 Tips: 目的に応じた観測点(プロービング点)を選択し、そこでプロービングできるように設計 時に準備しましょう。高速信号では、目的に応じた適切な観測点以外では意味のある観測 ができないことを十分認識してください。 公式試験のように測定点が仕様で規定されている場合には、それも考慮する必要があります。 CEM仕様の場合にはコネクタ位置で測定することになります。CBBまたはCLBと呼ばれる測定 用のフィクスチャを使用しますが、詳細は後の章で説明します。 また、プロービングのためにパッドを設ける場合には、信号品質を劣化させたりシステム動作 に影響を与えたりしないように注意が必要です。Sample

Tips: 一般的な注意点としては、図1.3に示すように、評価点のなるべく近くに(理想的には評 価点で)、信号経路に対してスタブ(分岐)を構成しないように作成します。また、面積 を最小にすることで、信号品質への影響を最小限に抑えるようにします。面積が大きい場 合には信号に対して容量性負荷となり、信号品質に影響を与える場合があります。シミュ レーションを活用して影響を確認すると良いでしょう。 プロトコル・アナライザ用の測定ポイントを活用しようとする場合には、そのポイントが目的 とする測定に適しているかを検討する必要があります。一般に、プロトコル・アナライザのプ ロービング・ポイントはLSI間の中間の位置に置きますが、この位置は信号品質の評価には適 した位置ではありません。このポイントは信号受信端ではなく、また仕様で規定された評価ポ イントとは限らないためです。なお、プロトコル・アナライザへの信号が適切なものであるか を確認する目的としては使用できます。 図1.3 プロービング・ポイントを設ける際の一般的な注意 面積最小、 スタブにしない なるべく短く GND端子を設ける ※各図は説明のための概念図です。 必要なプロービング・ポイントを設計時に用意しておく。 原則 • 配線パターンを対称に(D+, D-) • スタブを作らない • パッド容量はシミュレーションで影響を確認 (プローブ・ヘッドのSPICEモデルを利用) ヒント • 必要なビア等を利用する • 半田付けプローブ・ヘッドの利用 • 差動だけでなく、single-endでもプロービングできる準備Sample

第2章 PCI Expressの信号品質評価

本章では、信号品質評価の概要について説明します。2-1. 信号品質評価の目的

信号品質評価の目的は ・仕様への適合性やマージンを確認する ・デバッグ の2つがあります。 仕様への適合性を確認するには、仕様で規定された評価ポイント(位置)で測定することが 必須です。それ以外の位置では評価の目的を達成できません。PCI Expressをはじめとする高 速信号は伝送路上の位置によって信号波形が異なるという特性を持っているため、評価位置 と評価基準(仕様)は一体として考えます。仕様では特定の位置に対しての基準が示されて いますが、それ以外の位置では、測定ができても評価基準がないために良否判定ができない 状況が発生します。 Tips: 高速信号は、伝送路の損失(周波数特性)や不均一性により、伝送中に波形が変化し ます。また、伝送路の途中や受信端での反射によって余分な信号が重畳しても波形が 変化します。理想的な伝送路ではこのような問題は発生しませんが、実際の基板や部 品は理想的ではありません。 評価ポイント(位置)と評価基準(仕様)の例: ・LSIの受信端(Rxピン):基本仕様のRx仕様に対して評価 ・マザーボードのPCI Expressコネクタ位置:CEM仕様のマザーボード項目に対して評価 ・アドイン・カードのエッジ・コネクタ位置:CEM仕様のアドイン・カード項目に対して評 価 デバッグの場合の測定ポイント(位置)は目的により様々ですが、信号品質の評価として最 も重要なのは受信端です。どのような信号をLSIが受け取っているかが重要だからです。2-2. コンプライアンス試験とは

一般に「コンプライアンス試験」と呼ぶ場合、DUT(被測定物)が目的の仕様を満足してい るかを確認する評価を指す場合(広義)と、仕様の主管団体が主催する「公式試験」を指す 場合(狭義)の2種類があります。PCI ExpressではPCI-SIGが主催するCompliance Workshopに おいて公式試験が実施されていて、ここでの試験内容がcompliance testingとして公開されて います。 Tips: 「コンプライアンス試験」を実施する場合、それが公式試験を指すのか、公式試験に 準拠した内容の自社試験(プリ・コンプライアンス試験と呼びます)を指すのか、も しくはそれ以外を指すのかを明確にすることをお勧めします。それによって測定点や 使用するツールも異なるからです。Sample

2-3. PCI-SIGの公式試験内容

公式試験は年間に5~6回、アメリカまたは台湾でPCI-SIGによりCompliance Workshopとして実 施されており、公式試験を受験するにはこのイベントに参加する必要があります。実施スケ ジュールは以下を参照してください。 http://www.pcisig.com/events/ 公式試験の内容はPCI-SIGのホームページで公開されており、表2.1のカテゴリがあります。 これらの項目は100%合格する必要があります。 表2.1 公式試験のカテゴリ 相互接続性を含めすべての項目に合格すれば、登録手続きにより、PCI-SIGのホームページで Integrators Listの中で公開されます。このリストは誰でも見ることができます。 http://www.pcisig.com/developers/compliance_program/integrators_list/ 公式試験の対象はCEM仕様に基づくマザーボードおよびアドイン・カードです。これ以外の フォーム・ファクタで作成された製品は受験することができません。 上述の公式試験の内容は製品カテゴリ(マザーボード、アドイン・カード)によって異なり、 例えばPlatform BIOSはマザーボードだけの項目です。また、対象の仕様(1.1, 2.0等)によっ ても、具体的な内容が異なります。 Tips: LSIやIPとして試験を受ける場合には、マザーボードまたはアドイン・カードとして実装すれば受験できます。また、Mini PCI Expressカード(Mini CEM)はアダプタ込みで受

験した例があります。CEM以外のフォーム・ファクタで公式試験の受験を考えている場

合には、早めにPCI-SIGへ相談することをお勧めします。

Tips:

対象の製品カテゴリ毎にどんな試験が必要かを示した資料(PCIe Workshop Testing

Summary)がPCI-SIGのホームページに用意されています。以下を参照してください。 http://www.pcisig.com/specifications/pciexpress/compliance 公式試験としては更に相互接続性試験にも合格する必要があります。相互接続性試験は、そ の回のCompliance Workshopに参加の受験者同士(マザーボード、アドイン・カード)の相互 接続性を確認する形で実施され、8割以上の相手と正常に接続できれば合格となります。 なお、公式試験は限られた時間の中で実施されるため、PCI Expressの機能や動作が漏れなく 検証されるわけではありません。公式試験に合格したからといって、製品の動作や相互接続 性をPCI-SIGが保証してくれることはありませんので、仕様への適合性は自社でしっかりと確 認することが必要です。 Electrical testing (電気信号品質の試験) Configuration testing (コンフィグレーション空間の試験) Link protocol testing (リンク層の試験)

Transaction protocol testing (トランザクション層の試験) Platform BIOS testing (BIOSの試験)

Sample

2-4. プリ・コンプライアンス試験

プリ・コンプライアンス試験は公式試験の予行演習として自社で実施するもので、公式試験 と同じ内容で実施します。実際に公式試験に参加しない場合でも、公式試験と同じ内容で試 験しておくことで、製品が公式試験に受かるレベルのものであるかを確認することができま す。 Tips: プリ・コンプライアンス試験はアジレントの有償サービスとして提供されている他、 一部のテスト・サービス会社(テスト・ハウス)でも実施されています。 Tips: 公式評価ツールであるSigtestはPCI-SIG会員企業のみが入手・使用できます。Sigtestが入 手できない場合には、プリ・コンプライアンス試験には弊社製品N5393Cをご利用くだ さい。2-5. まとめ

公式試験やプリ・コンプライアンス試験の位置づけを表2.2にまとめておきます。 表2.2 公式試験とプリコンプライアンス試験の位置づけ 目的 規格適合性 デバッグ 実 施 者 PCI-SIG 公式試験 --- 自社 プリ・コンプライアンス試験 デバッグSample

第3章 Gen1/Gen2 CEMアドイン・カードの信号品質評価

本章では5Gbps動作までのCEMアドイン・カードを対象として、電気信号品質を評価する方 法について具体的に解説します。3-1. 概要

CEMアドイン・カードの電気信号品質評価は、アドイン・カードに搭載されたLSIが送出す る信号をオシロスコープで評価する測定です。DUTがアドイン・カードの場合、公式試験で 使われるCBB(Compliance Base Board)と呼ばれる測定用の治具ボードを利用すると評価が 容易になります。3-2. 必要機材

以下の機材が必要になります(図3.1を参照)。これ以外にもアクセサリ類が必要ですが、 以降の項で個別に示します。 ・オシロスコープ ・CBB ・CBB用の電源(デスクトップPC用のATX電源。20ピン) ・接続用ケーブル オシロスコープはDUTの動作速度により表3.1に示す性能が必要です。また、自社試験の場合 にはPCI Express向けの自動評価ソフトウェアを利用するのが便利です。 表3.1 必要なオシロスコープの性能 CBBは表3.2のように2種類があります。どちらもPCI-SIGから直接購入します。購入方法の詳 細はPCI-SIGのホームページを参照してください。 表3.2 CBBの種類 Tips: CBB2でも仕様1.1対応の試験は実施できますが、搭載されている基準クロック源のジッ タ特性はCBB2の方が優れているため、仕様1.1対応の評価をCBB2を使って実施すると若 干良い結果になる可能性があります。公式試験に向けたプリ・コンプライアンス試験 として実施する場合には、正式な組み合わせで実施すべきでしょう。 2.5Gbpsまでの場合 6GHz帯域、20GSa/s(サンプル/秒)、2チャネル、8Mワード/チャネル 5.0Gbpsまでの場合 12GHz帯域、40GSa/s、2チャネル、8Mワード/チャネル CBB1 仕様1.1に対応した評価を実施する場合 CBB2 仕様2.0に対応した評価を実施する場合Sample

Tips: ATX電源はCBBに搭載した回路へ電源を供給すると同時に、PCI Expressコネクタを介し てDUTにも電源を供給します。DUTの消費電力が大きい場合にはATX電源の容量に注意 が必要です。逆に、DUTの消費電力が少ないとATX電源からの供給電圧が安定しない場 合があるので、ATX電源の負荷としてHDD等を接続しておくと良いでしょう。実際に公 式試験の会場では、ATX電源の負荷としてHDDを1台接続して運用されています。 Tips: 接続用の同軸ケーブルは高品質のものをお勧めします。ケーブルの高周波損失が大き いとDUTからの信号が劣化し、オシロスコープに入力された時点で信号のレベルが低下 したり信号品質が劣化する恐れがあるためです。 オシロスコープ 同軸ケーブル ATX電源(CBB用)Sample

5.0Gbpsまで対応する場合のオシロスコープの推奨構成を表3.3に、2.5Gbpsに対応した構成を 表3.4に示します。 Tips: Infiniium 90000AシリーズのDSAモデルには高速シリアル解析機能、ジッタ解析機能、帯 域制限機能、大容量メモリ(50Mワード/ch)が標準装備されていて、PCI Expressをはじ めとする各種高速シリアル信号の評価に適しています。 表3.1および表3.2の構成には、本章で説明するCBBを使った評価で必要になる機材に加え、デ バッグで有用な機材も含めてご紹介しています。 モデル番号 内容 数量Agilent DSA91304A オシロスコープ(4ch, 13GHz帯域, 40GSa/s, 50Mワード/ch) 1

オプション022 PCI Express信号品質評価ソフトウェア内蔵 1

Agilent 1169A InfiniiMax IIプローブ・アンプ(12GHz帯域、差動) 2

Agilent N5425A InfiniiMax IIプローブ・ヘッド(ZIFハンダ付けタイプ)12GHz帯域 2

Agilent N5426A InfiniiMax II ZIFチップ12GHz帯域 2

Agilent N5382A InfiniiMax IIプローブ・ヘッド(手持ち測定タイプ)12GHz帯域 1 Agilent E2675A InfiniiMax Iプローブ・ヘッド(手持ち測定タイプ)6GHz帯域 1

Agilent E2697A 高インピーダンス・プローブ 1

モデル番号 内容 数量

Agilent DSA90604A オシロスコープ(4ch, 6GHz帯域, 20GSa/s, 50Mワード/ch) 1

オプション022 PCI Express信号品質評価ソフトウェア内蔵 1

Agilent 1134A InfiniiMax Iプローブ・アンプ(7GHz帯域、差動) 2

Agilent N5425A InfiniiMax IIプローブ・ヘッド(ZIFハンダ付けタイプ)12GHz帯域 2

Agilent N5426A InfiniiMax II ZIFチップ12GHz帯域 2

Agilent N5382A InfiniiMax IIプローブ・ヘッド(手持ち測定タイプ)12GHz帯域 1 Agilent E2675A InfiniiMax Iプローブ・ヘッド(手持ち測定タイプ)6GHz帯域 1

Agilent E2697A 高インピーダンス・プローブ 1

表3.3 5GT/sに対応するオシロスコープ推奨構成

Sample

3-3. 必要アクセサリ類

3-2で紹介した他に、以下のアクセサリが必要です。 ・信号接続ケーブル ・50オーム終端 ・パワー・スプリッタ(ケーブル・スキューの確認時に使用) ・各種アダプタ(校正やスキュー確認で使用) ・ATX電源 ・ハード・ディスク・ドライブ(ATX電源の負荷用) ATX電源およびATX電源の負荷用のハード・ディスク・ドライブ(各1台)は使用するCBBに よらず同じものが使用できます。 CBB1を使用する場合のアクセサリを表3.5に示します。 同様に、CBB2を使用する場合のアクセサリを表3.6に示します。 表3.5 CBB1を使用する場合のアクセサリ 表3.6 CBB2を使用する場合のアクセサリ アクセサリ 要件 数量 信号接続ケーブル SMA(m)-SMA(m)同軸ケーブル 長さ90cm程度で、挿入損失がなるべく小さい高品質なものが好 ましい。 アジレント製品では15443A(2本ペア) 2 50オーム終端 SMA(m)型。数量は対象カードのレーン数により異なる。 1レーン: 不要 4レーン: 2個 8レーン: 6個 16レーン: 12個 アジレント製品では1810-0118 左記参照 パワー・ディバイダ アジレント製品では11636B 1 各種アダプタ Precision BNC(m)-SMA(f)アダプタ(アジレント54855-67604) SMA(m)-SMA(m)アダプタ(アジレント1250-1159) 各1 アクセサリ 要件 数量 信号接続ケーブル SMP(f)-SMA(m)同軸ケーブル 長さ90cm程度で、挿入損失がなるべく小さい高品質なものが好 ましい。 2 50オーム終端 SMP(f)型。数量は対象カードのレーン数により異なる。 1レーン: 不要 4レーン: 2個 8レーン: 4個 16レーン: 8個 左記参照 パワー・ディバイダ アジレント製品では11636B 1 各種アダプタ Precision BNC(m)-SMA(f)アダプタ (アジレント54855-67604) 1個 左記参照Sample

3-4. 測定前の準備

測定は以下のステップで行います。 ・測定機材のウォームアップと校正 ・接続 ・測定 以下では、測定機材のウォームアップと校正について説明します。 接続および測定は対象製品毎に項をあらためて説明します。[ 測定機材のウォームアップと校正 ]

オシロスコープは測定開始前に30分以上、できれば60分以上通電してウォームアップしてく ださい。校正および測定を実施する前にオシロスコープの内部温度を安定させることが目的 です。 校正は、オシロスコープ単体でのユーザ校正と、使用するケーブルとオシロスコープの組み 合わせでの校正(DC分圧比、チャネル間時間差)の2段階から成ります。 Tips: オシロスコープ単体でのユーザ校正は省略することができますが、より正確な測定を 行ないたい場合には実施をお勧めします。省略すると、前回の校正値が使用されます。 実施する場合、比較的時間のかかる作業になりますので、時間に余裕を見て実施する ことをお勧めします。 Tips: DC分圧比とチャネル間時間差(チャネル間スキュー)は使用するケーブルに依存しま す。一度校正したケーブルを使って測定する場合には、保存されている校正結果を利 用することができます。この場合、どのチャンネルにどのケーブルを接続するかとい う組み合わせは校正時と変えてはいけません。Sample

3-5. DUTの接続

図3.10または図3.11を参照して、測定のための接続を行ないます。 CBB上には複数のSMAコネクタ(CBB2の場合にはSMPコネクタ)が実装されていますが、測 定で使用するのは2個だけです。使用しない他のコネクタにはすべて50Ω終端を接続しておき ます。 Tips: SMPコネクタは中心導体が折れやすいため、コネクタへの抜き差しは慎重に垂直に行な います。SMPコネクタの挿抜ツールを使用することをお勧めします。弊社製品では E4809-23802が使用できます。 Tips: SMAコネクタはオス側にあるリングを回して締め付け/取り外しを行います。この時、 片方の手でケーブルを持ち、ケーブルが回らないように注意します。これはSMAコネク タの接続端面を摩耗して損傷しないようにするためです。過度の締め付けを防ぎ、適 切なトルクで締め付けるため、トルク・レンチを使用するようにしましょう。コネク タの適正トルクはコネクタのタイプ毎に異なるため、コネクタに合ったトルク・レン チを使用することが重要です。SMAコネクタの場合には、SMAコネクタ用(アジレント 8710-1582)を使用します。 Tips: コネクタが実装されていないレーンは、ボード上のチップ抵抗で終端されています。 ATX電源 CBB1 オシロスコープ 被測定ボー ド Precision BNCアダプタ SMA同軸ケーブルSample

ATX電源 CBB2 オシロスコープ 被測定ボー ド Precision BNCアダプタ SMP同軸ケーブル 図3.11 CBB2を使う場合の接続 図3.12 測定に使わないコネクタはすべて終端しておく 左:CBB1, 右:CBB2 モード遷移プッシュ・ スイッチ 終端 終端Sample

3-7. 測定の実施(Revision 1.1仕様のアドイン・カードの場合)

左側に表示されているTask Flowに従い、順番に設定していきます。 [Setup]タブは測定の基本的な設定を行います。 [Select Test]タブでは測定項目を選択します。必要な項目だけを選択することもできます。 [Configure]タブでは測定条件を設定します。評価UI数は仕様の規定では1M UIですが、デバッグ 等で簡単にチェックしたい場合などは、評価UI数を減らして測定しても良いでしょう。 [Connect]タブでは機器の接続とコンプライアンス・テスト・パターンの確認が表示されます。 内容を確認し[Run Test]ボタンを押すと、測定が始まります。 測定が終了したら、[Results]タブや[HTML Report]タブで結果を確認します。 [Setup]タブ: 基本的な設定を行います。 • Device: 対象の規格を選択します(本項ではPCIE 1.1)。• Test Point: 測定点を選択します(本項ではAdd-in Card Tests)。 Receiver Testは受信端で の信号品質を評価します(受信能力ではありません)。

• Reference Clock: Clean Clockは、ジッタの少ないクロックを使って試験する場合に選択しま す。CBBを使用する場合はClean Clockを選択します。

• User Comment: 任意のコメントを入力できます。試験レポートのコメント欄に表示されます。 • Embed/De-embed: 測定環境を反映できます(本書では扱いません)

Sample

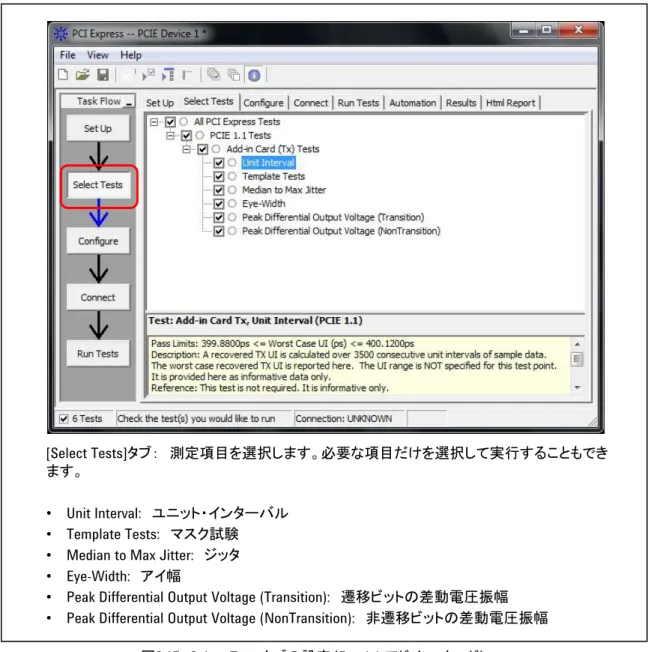

[Select Tests]タブ: 測定項目を選択します。必要な項目だけを選択して実行することもでき ます。

• Unit Interval: ユニット・インターバル • Template Tests: マスク試験 • Median to Max Jitter: ジッタ • Eye-Width: アイ幅

• Peak Differential Output Voltage (Transition): 遷移ビットの差動電圧振幅 • Peak Differential Output Voltage (NonTransition): 非遷移ビットの差動電圧振幅

Sample

図3.18 Configureタブの設定(Rev.1.1 アドイン・カード) [Configure]タブ: 測定条件を設定します。

• Number of UI: 評価に使うUI数(ビット数)を指定します。デフォルトは100万個です。測定

時間を短くして簡単にチェックしたい場合は、少ないUI数を指定します。 • Lane Number: 測定対象のレーン番号を設定します。測定結果には影響しませんが、レ ポートに表示されます。 • Sample Rate: サンプリング速度を設定します。デフォルトから変更する必要はありませ ん。 • Noise Reduction: 信号にノイズが多い場合に帯域を制限することができます。通常はデ フォルト(Automatic)で測定します。

• Signal Check: 信号が試験対象の信号かを、簡便な方法で確認します。通常はEnableに しておきます。

• Deembed Fixture: フィクスチャ(CBB等)の損失を固定値で入力できます。通常は0です。 • Connection Type: 信号の接続方法を設定します。同軸ケーブルによる接続ではDirectを

Sample

[Connect]タブ: 接続を確認したら最下部にチェックを入れ、Run Testを押します。自動測定 が開始されます。

[Results]タブ: 測定が終了すると結果の一覧が表示されます。

Test Name下の測定項目をクリックすると、その詳細が画面下部に表示されます。 図3.19 ConnectタブとRunTest(Rev.1.1 アドイン・カード)

Sample

3-11. 公式試験の必要機材と手順

公式試験では、これまでに説明したのと同じ機材やセットアップを使いますが、評価ツール としてSigtestが使われます。SigtestはPCI-SIGのホームページからダウンロードできますが、こ れはPCI-SIGの会員企業に限られます。また、ダウンロードにはPCI-SIGの会員企業の従業員で あることの他に、PCI-SIGホームページでの簡単な登録が必要です。 以下ではSigtestを使う場合の測定手順の概要を説明します。なお、公式な手順書はPCI-SIGの以 下のページからダウンロードできます。 http://www.pcisig.com/specifications/pciexpress/compliance/compliance_library ご注意: 公式試験に向けた準備としてプリ・コンプライアンス試験を実施する場合には、 公式な手順書を参照してください。以下は公式試験の手順を実施するための参考 として利用してください。 Tips: Sigtestは対象の規格によって以下の2種類がPCI-SIGのホームページに掲載されています。 ・仕様1.1用 Sigtest 2.1 ・仕様2.0用 Sigtest 3.1.9 Sigtestはオシロスコープにインストールすることも、外部PCにインストールすることも できます。オシロスコープにインストールすれば、サイズの大きな波形ファイルを移 動することなく解析でき、便利です。 (1) 必要機材 必要機材は3-2.および3-3.で説明した内容と同じです。 (2) 測定前の準備 事前の準備(機材のウォームアップ、校正、接続、信号確認)は3-4、3-5および3-6で説明した 内容と同じです。 3-6.を参考に、DUT(測定対象のアドイン・カード)から正しいコンプライアンス・テスト・ パターンが出力されていることをオシロスコープ画面で確認します。 Tips: Revision 2.0仕様に対応したDUTには以下の2種類があります。 ・2.5GT/sのみをサポートしているDUT ・5GT/sをサポートしているDUT 5GT/sをサポートしているDUTの場合、2.5GT/sと5GT/sの両方について試験します。 Tips: マルチ・レーンのアドイン・カードの場合、CBB上でコネクタが実装されているレーン のみが試験対象となります。 5GT/sの試験では、de-emphasisレベル-3.5dBおよび-6dBの両方について試験します。測定を始め る前にCBB2上のモード遷移スイッチを操作して、所望のde-emphasisレベル(-3.5dBまたはSample

(3) 測定操作[Control] > Default Setupを実行した後、オシロスコープを以下のように設定します。 ・チャネル: Channel 1およびChannel 3をオン

・電圧軸(Channel 1, Channel 3): 70mV/div, オフセット0 V

・トリガ:Channel 3, レベル0V, 立ち上がりエッジ(Channel 1や立ち下りエッジでも可) ・サンプリング: 20Gサンプル/秒(2.5GT/sの場合)または40Gサンプル/秒(5GT/sの場合) ・メモリ長: 2Mワード(Rev 1.1仕様の場合)8Mワード(Rev 2.0仕様の場合) ・波形補間:オフ Tips: 上記の設定が終了した段階で、オシロスコープの設定を保存しておくとよいでしょう。 操作は、[File] > Save Setup から適当な名前を付けてSaveします。

Tips: 仕様1.1に対する試験の場合には、メモリ長は2Mワード(各チャネル)に設定します。 これは250k UIの時間に相当します。8Mワードは1M UIに相当します。 オシロスコープをRunさせます。波形が電圧軸方向にも時間軸にも画面の中に納まっているこ とを確認します。電圧軸方向に納まっていない場合には、画面からはみ出さないように電圧 軸を調整します。電圧軸方向に余裕がありすぎる場合には、電圧軸を調整して大きく表示し てもかまいません。 以上の調整・確認が終わったら、Stopし波形を保存します。 [File] > Save > Waveform…

保存形式はCSVを選択します。 Tips:

仕様2.0試験用のSigtest 3.1.9以後ではBinary形式も選択できます。Binary形式の方がデー タ・サイズが小さく、保存時間も短くてお勧めです。

Sample

Channel 1の設定 Channel 3の設定

トリガの設定

Sample

(4) Sigtestによる評価

次にSigtestを起動し、保存しておいた波形データを指定します。Data TypeとしてSingle Endedを

選択します。選択が終了したら、データ・フォーマットの確認ボタン[Verify Data Format]を押

します。確認が成功すると画面下部の[Test]ボタンがアクティブになります。 [Technology[および[Template]で所望の試験を選択し、[Test]ボタンを押します。解析が終了する と結果(Pass, Fail)が表示されます。結果画面下部の[HTML]ボタンを押すと、解析結果が HTML形式で表示されます。 保存した波形データをDate File に設定します。

Verify Valid Data Fileを押すと データ形式の確認が行われ、そ の後Testボタンがアクティブにな ります。

TechnologyおよびTemplate FIleで 対象のDUTと仕様を選択します。 Apps Settings and Debug Modeを 設定(次図を参照)してからTest ボタンを押します。