Spartan-6 FPGA GTP

ト ラ ン シーバ

ユーザー

ガ イ ド

display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

本資料は英語版 (v2.0) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。 日付 バージ ョ ン 改訂内容 2009 年 6 月 24 日 1.0 初版 リ リ ース 2009 年 11 月 11 日 2.0 GTP_DUAL を GTPA1_DUAL に置換え。 第 1 章 : • 表 1-1 を削除。 • 19 ページの 「ポー ト お よ び属性の ま と め」 を追加。 • 27 ページの表 1-3 : SIM_RECEIVER_DETECT_PASS 属性の説明を更新。 • 32 ページの図 1-7 を更新。 • 31 ページの図 1-5、31 ページの図 1-6、33 ページの図 1-8、34 ページの図 1-9、35 ページの図 1-10、36 ページの図 1-11、 お よ び 37 ページの図 1-12 を追加。 第 2 章 : • 39 ページの 「 リ フ ァ レ ン ス ク ロ ッ ク 入力の構造」、 お よ び 48 ページの 「複数の外部 リ フ ァ レ ン ス ク ロ ッ ク を使用す る 場合」 を追加。 • 42 ページの図 2-2 を追加。 • リ フ ァ レ ン ス ク ロ ッ ク マルチプ レ ク サの構造に関す る 43 ページの図 2-3 の前の説明 を改訂。 • 44 ページの表 2-5 : CLKINEAST、CLKINWEST、PLLCLK、 お よ び PLLCLK ポー ト の説明を更新。GTPCLKFBEAST、GTPCLKFBSEL0EAST、GTPCLKFBSEL0WEST、GTPCLKFBSEL1EAST、GTPCLKFBSEL1WEST、 GTPCLKFBWEST、 お よ び REFCLKPWRDNB ポー ト を追加。

• 51 ページの表 2-7 : TXPLL_DIVSEL_REF 属性を削除。

• 53 ページの表 2-10 : 「PCIe Optimal Jitter」 と い う 用語を 「PCIe 追加マージ ン」 に変

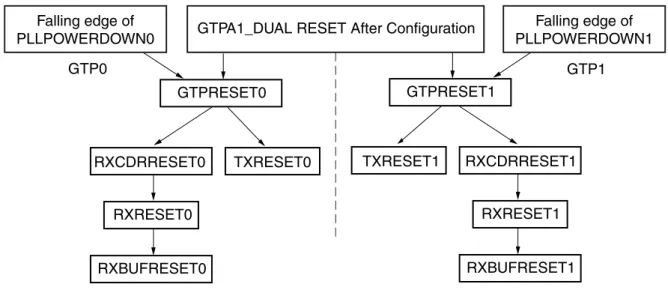

更。 表の メ モを追加。 • 55 ページの表 2-11 : 表の メ モ (1) を追加。GTPRESET の説明を更新。 PRBSCNTRESET お よ び RESETDONE の ド メ イ ン を変更。 • 54 ページの図 2-10 : PLLPOWERDOWN0 の立ち下が り エ ッ ジ を表すブ ロ ッ ク を追加。 • 56 ページの表 2-12 : RX_EN_MODE_RESET_BUF_(0/1) 属性お よ び表の メ モを追加。 • 57 ページの図 2-11、 お よ び 57 ページの図 2-12 を改訂。 • 60 ページの表 2-14 : 「推奨 さ れ る リ セ ッ ト 方法」 列のポー ト 名の後に (0/1) を追加。

(続 き) • 76 ページの 「TXUSRCLK お よ び TXUSRCLK2 の接続」 に GTPCLKOUT を説明す る 項目を追加。 • 77 ページの 「GTPCLKOUT を使用 し て GTP TX を駆動」 を追加。 • 84 ページの表 3-5 : 「ス キ ュ ー低減」 を 「TX レーン間の ス キ ュ ー低減」 に変更。 • 85 ページの表 3-7 : TX_BUFFER_USE の説明を更新。 • 85 ページの 「TX バ ッ フ ァ のバ イ パ ス」 を更新。 • 89 ページの図 3-10、89 ページの図 3-11、91 ページの図 3-12、 お よ び 92 ページの 図 3-13 を追加。 • 88 ページの表 3-10、90 ページの表 3-11、 お よ び 90 ページの表 3-12 を追加。 • 103 ページの表 3-22 : TXDETECTRX の説明を更新。 • 105 ページの表 3-23 : RXSTATUS お よ び TXCOMSTART の説明を更新。 第 4 章 : • 108 ページの図 4-2、111 ページの図 4-3、112 ページの図 4-4、113 ページの図 4-5、 114 ページの図 4-6、115 ページの図 4-7、 お よ び 123 ページの図 4-11 を更新。 • 109 ページの表 4-2 : TERMINATION_OVRD の説明で正確な抵抗値を 100Ωか ら 50Ωに変更。 • 110 ページの表 4-3 : 行 1 お よ び行 2 の RX 終端電圧を更新。 • 111 ページの表 4-4 : 内部バ イ ア ス を 800mV か ら 900mV に変更。 • 112 ページの表 4-5 : 終端電圧を VTT か ら MGTVTTRX に変更。 内部バ イ ア ス を 800mV か ら 900mV に変更。 • 113 ページの表 4-6 : 終端電圧を 2/3MGTAVTT か ら 3/4MGTAVTTRX に変更。 内部バ イ ア ス を 800mV か ら 900mV に変更。 • 114 ページの表 4-7 : 終端電圧を VTTか ら MGTVTTRX に変更。 内部バ イ ア ス を 800mV か ら 900mV に変更。 • 115 ページの表 4-8 : 終端電圧を 2/3MGTAVTT か ら 3/4MGTAVTTRX に変更。 内部バ イ ア ス を 800mV か ら 900mV に変更。 • 116 ページの表 4-9 : RXVALID ポー ト の方向を In か ら Out に変更。 • 116 ページの表 4-10 : OOBDETECT_THRESHOLD_(0/1) の説明を更新。 • 129 ページの表 4-22 : RX_PRBS_ERR_CNT_(0/1) の説明を更新。 • 132 ページの表 4-23 : RXSLIDE ポー ト を追加。 • 134 ページの表 4-24 : MCOMMA_10B_VALUE、MCOMMA_DETECT、

PCOMMA_10B_VALUE、PCOMMA_DETECT、 お よ び RX_SLIDE_MODE 属性 を追加。 • 「RX バ ッ フ ァ のバ イ パ ス」 を 141 ページの 「RX エ ラ ス テ ィ ッ ク バ ッ フ ァ のバ イ パ ス」 に置換え。 • 146 ページの図 4-23、147 ページの図 4-24、148 ページの図 4-25、 お よ び 149 ペー ジの図 4-26 を追加。 • 142 ページの図 4-22 お よ び 150 ページの図 4-27 の PCS パ ラ レルク ロ ッ ク の区画か ら RX ギ アボ ッ ク ス を削除。

2009 年 11 月 11 日 (続 き) 2.0 第 4 章 (続 き) : • 160 ページの表 4-37 : RXCHBONDI[2:0]、RXCHBONDO[2:0]、 RXCHBONDMASTER(0/1)、 お よ び RXCHBONDSLAVE(0/1) の説明を更新。 • 162 ページの表 4-38 : 属性 CB2_INH_CC_PERIOD_(0/1) お よ び RX_EN_MODE_RESET_BUF_(0/1) を追加。 CHAN_BOND_1/2_MAX_SKEW_(0/1)、CHAN_BOND_KEEP_ALIGN_(0/1)、 お よ び CHAN_BOND_SEQ_LEN_(0/1) の説明を更新。CHAN_BOND_SEQ_2_CFG を削除。 • 164 ページの 「チ ャ ネルボ ンデ ィ ン グモー ド 」、 お よ び 164 ページの 「チ ャ ネルボ ン デ ィ ン グの有効化」 の ス テ ッ プ 4 を更新。 • 170 ページの 「RXUSRCLK お よ び RXUSRCLK2 の接続」の式4-2 の前の RXUSRCLK お よ び RXUSRCLK2 の説明を更新。 • 式4-3 の RXDATAWIDTH を 1 に変更。 • 167 ページの表 4-39 : REFCLKOUT ポー ト の説明を更新。 第 5 章 : • 173 ページの 「概要」を追加。

• 173 ページの表 5-1 : MGTAVCC、MGTAVCCPLL0、MGTAVCCPLL1、

MGTAVTTRX、 お よ び MGTAVTTTX の説明に標準電圧を追加。 MGTRXP0/MGTRXN0、MGTRXP1/MGTRXN1、MGTTXP0/MGTTXN0、 お よ び MGTTXP1/MGTTXN1 の説明を更新。 • 175 ページの図 5-1 を追加。 • 182 ページの 「電源供給お よ びフ ィ ル タ リ ン グ」 を改訂。 • 185 ページの図 5-11、186 ページの図 5-12、186 ページの図 5-13、 お よ び 184 ページ の表 5-2 を追加。 付録 B : • 付録を追加。 日付 バージ ョ ン 改訂内容

改訂履歴. . . 3

このユーザー

ガ イ ド について

ユーザーガ イ ド の内容 . . . 13 その他の資料. . . 13 その他の資料. . . 14 その他の リ ソ ース . . . 14第

1

章

:

ト ラ ン シーバおよびツールの概要

概要 . . . 15 ポー ト お よ び属性の ま と め. . . 19Spartan-6 FPGA GTP Transceiver Wizard . . . 24

シ ミ ュ レーシ ョ ン . . . 26 機能の説明 . . . .26 シ ミ ュ レーシ ョ ン専用のポー ト お よ び属性. . . .26 SIM_GTPRESET_SPEEDUP . . . .28 SIM_RECEIVER_DETECT_PASS . . . .29 SIM_REFCLK0_SOURCE . . . .29 SIM_REFCLK1_SOURCE . . . .29 SIM_TX_ELEC_IDLE_LEVEL . . . .29 SIM_VERSION. . . .29 イ ンプ リ メ ン テーシ ョ ン. . . 30

第

2

章

:

ト ラ ン シーバの共有機能

リ フ ァ レ ン ス ク ロ ッ ク 入力の構造 . . . 39 機能の説明 . . . .39 ポー ト お よ び属性. . . .39 使用モー ド : リ フ ァ レ ン ス ク ロ ッ ク の終端処理. . . .40 リ フ ァ レ ン ス ク ロ ッ ク の選択お よ び分配. . . 40 機能の説明 . . . .40 ポー ト お よ び属性. . . .44 単一の外部 リ フ ァ レ ン ス ク ロ ッ ク を使用す る 場合. . . .46 複数の外部 リ フ ァ レ ン ス ク ロ ッ ク を使用す る 場合. . . .48 PLL . . . 49 機能の説明 . . . .49 ポー ト お よ び属性. . . .51 標準プ ロ ト コ ルの PLL 設定 . . . .53 リ セ ッ ト. . . 54 機能の説明 . . . .54 ポー ト お よ び属性. . . .55 コ ン フ ィ ギ ュ レーシ ョ ン完了後の GTP リ セ ッ ト . . . .57 GTPRESET アサー ト 後の GTP の リ セ ッ ト . . . .57 GTP コ ン ポーネ ン ト レベル リ セ ッ ト . . . .58 リ ン ク ア イ ド ル リ セ ッ ト のサポー ト . . . .58 GTPA1_DUAL タ イ ルの リ セ ッ ト . . . .58 例 . . . .61 電源投入お よ び コ ン フ ィ ギ ュ レーシ ョ ン . . . .61 リ フ ァ レ ン ス ク ロ ッ ク の電源投入後 . . . .61 リ フ ァ レ ン ス ク ロ ッ ク の変更後. . . .61 パ ラ レルク ロ ッ ク ソ ース の リ セ ッ ト. . . .61目次

TX バ ッ フ ァ エ ラ ー後. . . .62 RX バ ッ フ ァ エ ラ ー後. . . .62 チ ャ ネルボ ンデ ィ ン グ前 . . . .62 PRBS エ ラ ー後 . . . .63 パ ワーダ ウ ン . . . 63 機能の説明 . . . .63 ポー ト お よ び属性. . . .63 一般的なパ ワーダ ウ ン機能 . . . .64 PLL のパ ワ ーダ ウ ン. . . .64 TX お よ び RX のパ ワ ーダ ウ ン . . . .65 PCI Express のパ ワ ーダ ウ ン機能 . . . .66 パ ワ ーダ ウ ンへの移行時間 . . . .66 ループバ ッ ク. . . 67 機能の説明 . . . .67 ポー ト お よ び属性. . . .68 ダ イ ナ ミ ッ ク リ コ ン フ ィ ギ ュ レーシ ョ ンポー ト. . . 68 機能の説明 . . . .68 ポー ト お よ び属性. . . .68

第

3

章

:

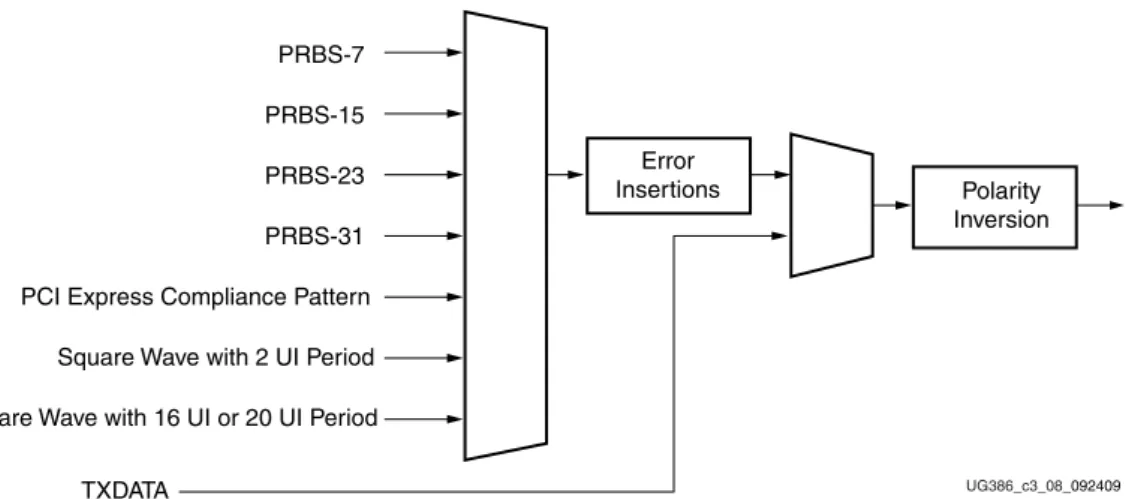

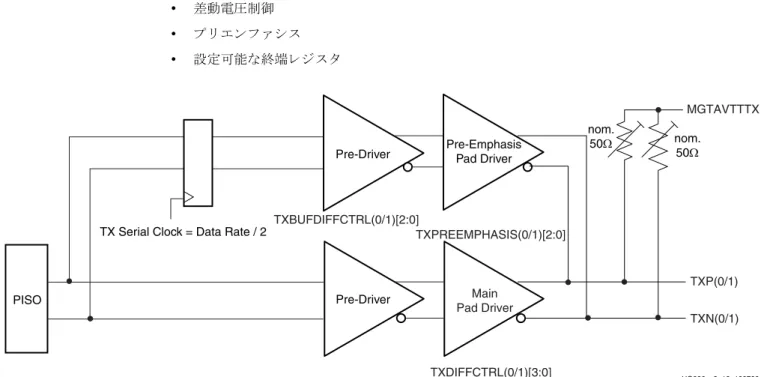

ト ラ ン ス ミ ッ タ

ト ラ ン ス ミ ッ タ (TX) の概要. . . 71 FPGA TX イ ン タ ーフ ェ イ ス . . . 72 機能の説明 . . . .72 ポー ト お よ び属性. . . .72 説明. . . .74 イ ン タ ーフ ェ イ ス幅の設定 . . . .75 TXUSRCLK お よ び TXUSRCLK2 の接続 . . . .76 GTPCLKOUT を使用 し て GTP TX を駆動 . . . .77 GTPCLKOUT に よ る GTP TX の駆動 (1 バ イ ト モー ド) . . . .77 GTPCLKOUT に よ る GTP TX の駆動 (2 バ イ ト モー ド) . . . .78 GTPCLKOUT に よ る GTP TX の駆動 (4 バ イ ト モー ド) . . . .79 TX の 8B/10B エン コーダ. . . 79 機能の説明 . . . .79 8B/10B のビ ッ ト お よ びバ イ ト 順序 . . . .79 K キ ャ ラ ク タ. . . .80 ラ ン ニ ン グデ ィ ス パ リ テ ィ. . . .80 ポー ト お よ び属性. . . .81 8B/10B エン コーダの有効/無効. . . .83 TX バ ッ フ ァ . . . 83 機能の説明 . . . .83 ポー ト お よ び属性. . . .84 TX バ ッ フ ァ の使用 . . . .85 TX バ ッ フ ァ のバ イ パ ス . . . 85 機能の説明 . . . .85 ポー ト お よ び属性. . . .86 TX バ ッ フ ァ をバ イ パス し て TX 位相ア ラ イ メ ン ト 回路を使用. . . .88 TX 位相ア ラ イ メ ン ト 回路を使用 し た TX レーン間ス キ ュ ーの最小化 . . . .89 フ ィ ー ド バ ッ ク パ ス を使用 し た電圧お よ び温度の変化への対応. . . .89 TX パ タ ーンジ ェ ネ レー タ. . . 93 機能の説明 . . . .93ポー ト お よ び属性. . . .96 TX 極性制御の使用 . . . .96 TX フ ァ ブ リ ッ ク ク ロ ッ ク 出力の制御. . . 96 機能の説明 . . . .96 シ リ アル ク ロ ッ ク 分周器 . . . .97 パ ラ レルク ロ ッ ク 分周器お よ びセ レ ク タ. . . .98 ポー ト お よ び属性. . . .98 TX の コ ン フ ィ ギ ュ レーシ ョ ン可能な TX ド ラ イ バ . . . 100 機能の説明 . . . .100 ポー ト お よ び属性. . . .100 使用モー ド – TX ド ラ イ バ. . . .102 標準 . . . .102 使用モー ド - 抵抗キ ャ リ ブ レーシ ョ ン . . . .102 PCI Express デザ イ ン用の TX レ シーバ検出機能 . . . 103 機能の説明 . . . .103 ポー ト お よ び属性. . . .103 TX OOB (帯域外) 信号 . . . 105 機能の説明 . . . .105 ポー ト お よ び属性. . . .105

第

4

章

:

レ シーバ

レ シーバ (RX) の概要. . . 107 RX アナ ロ グ フ ロ ン ト エン ド. . . 108 機能の説明 . . . .108 ポー ト お よ び属性. . . .109 使用モー ド – RX 終端 . . . .110 使用モー ド - 抵抗キ ャ リ ブ レーシ ョ ン . . . .115 RX OOB (帯域外) 信号. . . 116 機能の説明 . . . .116 ポー ト お よ び属性. . . .116 RX イ コ ラ イ ザ . . . 118 機能の説明 . . . .118 ポー ト お よ び属性. . . .119 使用モー ド ― 連続時間対応の RX リ ニ ア イ コ ラ イ ザ. . . .120 RX CDR . . . 120 機能の説明 . . . .120 ポー ト お よ び属性. . . .121 RX ク ロ ッ ク 分周制御. . . 122 機能の説明 . . . .122 シ リ アル ク ロ ッ ク 分周器 . . . .123 パ ラ レルク ロ ッ ク 分周器 . . . .124 ポー ト お よ び属性. . . .124 RX マージ ン解析. . . 125 機能の説明 . . . .125 水平方向のア イ マージ ン ス キ ャ ン. . . .125 ポー ト お よ び属性. . . .126 RX 極性制御 . . . 127 機能の説明 . . . .127 ポー ト お よ び属性. . . .127 RX 極性制御の使用 . . . .127 RX パ タ ーンチ ェ ッ カ . . . 128 機能の説明 . . . .128 ポー ト お よ び属性. . . .128 使用モデル . . . .129 RX バ イ ト お よ び ワー ド ア ラ イ メ ン ト. . . 129 機能の説明 . . . .129ア ラ イ メ ン ト ス テー タ ス信号. . . .131

ア ラ イ メ ン ト バ ウ ン ダ リ . . . .131

ポー ト お よ び属性. . . .132

RX の LOS (Loss of Sync) ス テー ト マシ ン . . . 135

機能の説明 . . . .135 ポー ト お よ び属性. . . .136 RX 8B/10B デ コ ーダ. . . 137 機能の説明 . . . .137 8B/10B デ コ ーダでのビ ッ ト お よ びバ イ ト 順 . . . .137 K キ ャ ラ ク タ お よ び 8B/10B カ ン マ. . . .138 RX ラ ン ニ ン グデ ィ ス パ リ テ ィ . . . .138 デ ィ スパ リ テ ィ エ ラ ーお よ び Out of Table エ ラ ー . . . .139 ポー ト お よ び属性. . . .139 RX エ ラ ス テ ィ ッ ク バ ッ フ ァ のバ イ パ ス. . . 141 機能の説明 . . . .141 ポー ト お よ び属性. . . .142 説明. . . .144 RX エ ラ ス テ ィ ッ ク バ ッ フ ァ をバ イ パ ス し て RX 位相ア ラ イ メ ン ト 回路を使用. . . . .144 RX エ ラ ス テ ィ ッ ク バ ッ フ ァ . . . 150 機能の説明 . . . .150 ポー ト お よ び属性. . . .151 RX エ ラ ス テ ィ ッ ク バ ッ フ ァ を使用 し て、 チ ャ ネルボ ンデ ィ ン グ ま たは ク ロ ッ ク コ レ ク シ ョ ン をサポー ト. . . .152 RX ク ロ ッ ク コ レ ク シ ョ ン. . . 152 機能の説明 . . . .152 ポー ト お よ び属性. . . .153 RX ク ロ ッ ク コ レ ク シ ョ ンの使用. . . .157 ク ロ ッ ク コ レ ク シ ョ ンの有効化. . . .157 RX エ ラ ス テ ィ ッ ク バ ッ フ ァ の制限設定 . . . .157 ク ロ ッ ク コ レ ク シ ョ ンシーケ ン ス の設定 . . . .158 ク ロ ッ ク コ レ ク シ ョ ンのオプシ ョ ン . . . .159 ク ロ ッ ク コ レ ク シ ョ ンのモニ タ リ ン グ . . . .159 RX チ ャ ネルボ ンデ ィ ン グ. . . 159 機能の説明 . . . .159 ポー ト お よ び属性. . . .160 RX チ ャ ネルボ ンデ ィ ン グの使用. . . .164 チ ャ ネルボ ンデ ィ ン グの有効化. . . .164 チ ャ ネルボ ンデ ィ ン グモー ド . . . .164 チ ャ ネルボ ンデ ィ ン グシーケ ン ス の設定 . . . .165 最大ス キ ュ ーの設定. . . .165 チ ャ ネルボ ンデ ィ ン グ と ク ロ ッ ク コ レ ク シ ョ ンの優先順位. . . .166 FPGA RX イ ン タ ーフ ェ イ ス . . . 166 機能の説明 . . . .166 ポー ト お よ び属性. . . .167 説明. . . .168 イ ン タ ーフ ェ イ ス幅の設定 . . . .168 RXUSRCLK お よ び RXUSRCLK2 の接続 . . . .170

第

5

章

:

ボー ド

デザイ ンのガ イ ド ラ イ ン

概要 . . . 173電源接続. . . .176 終端抵抗キ ャ リ ブ レーシ ョ ン回路. . . .176 GTP ト ラ ン シーバを使用す る 場合 と 未使用の場合の電源接続管理. . . .178 GTP バン ク をすべて使用す る 場合の接続. . . .178 同 じ GTP バン ク 内の GTP デ ュ アルを使用す る 場合 と し ない場合の電源接続. . . .178 リ フ ァ レ ン ス ク ロ ッ ク . . . 178 概要. . . .178 GTP の リ フ ァ レ ン ス ク ロ ッ ク に関す る チ ェ ッ ク 項目 . . . .180 イ ン タ ーフ ェ イ ス. . . .181 LVDS. . . .181 LVPECL . . . .181 AC カ ッ プ リ ン グ. . . .181 ク ロ ッ ク 分配 . . . .182 オシ レー タ か ら の 2 つ以上の差動 ク ロ ッ ク 入力ペアへ ク ロ ッ ク を提供 . . . .182 未使用の リ フ ァ レ ン ス ク ロ ッ ク 入力 . . . .182 電源供給お よ びフ ィ ル タ リ ン グ . . . 182 概要. . . .182 電圧レ ギ ュ レー タ. . . .182 リ ニ ア レ ギ ュ レー タ お よ びス イ ッ チン グレ ギ ュ レー タ . . . .182 電力分配ネ ッ ト ワー ク . . . .184 電源供給デカ ッ プ リ ン グキ ャ パシ タ . . . .184 PCB (プ リ ン ト 回路基板) の設計 . . . .184 ボー ド ス タ ッ ク ア ッ プ . . . .185 MGT 電源接続. . . .186 ク ロ ス ト ー ク . . . .187 SelectIO の使用ガ イ ド ラ イ ン. . . 187 推奨 さ れ る 信号 ラ ンチ (Signal Launch) . . . 187

付録

A : 8B/10B

有効な文字

付録

B : GTP

ト ラ ン シーバの

DRP

ア ド レ ス

マ ッ プ

こ のユーザー

ガ イ ド について

こ のユーザー ガ イ ド では、Spartan®-6 FPGA の GTX ト ラ ン シーバの使用方法について説明 し ま

す。 こ の文書では、

• Spartan-6 FPGA GTP ト ラ ン シーバを、GTP ト ラ ン シーバ と 略 し て表記 し てい ます。

• GTPA1_DUAL は、1 セ ッ ト の Spartan-6 FPGA GTP ト ラ ン シーバを イ ン ス タ ン シエー ト す る イ ン ス タ ン シエー ト プ リ ミ テ ィ ブ名です。GTP_DUAL と い う 語は、 こ の文書全体を通 し て GTPA1_DUAL タ イ ル と 同義に使用 さ れます。 • DUAL は、2 つの差動 リ フ ァ レ ン ス ク ロ ッ ク ピ ンのペアお よ びアナ ロ グ電源ピ ン を共有す る 、 2 つの GTP ト ラ ン シーバの ク ラ ス タ ま たはセ ッ ト です。 • ピ ン名の末尾に 0 ま たは 1 が付 く も の、 属性名の末尾に _0 ま たは _1 が付 く も のがあ り ます。 こ の接尾辞は、 レーン 0 と レーン 1 の レーン固有の設定、 ま たは PLL0 と PLL1 の固有の設定 に対応 し ます。 ピ ン名ま たは属性名に接尾辞が付いていない場合、 こ の名前は、 レーン固有の ピ ン ま たは属性に共通す る 名前です。 ソ フ ト ウ ェ アで ピ ン ま たは属性を使用す る 場合、 接尾辞 は必須です。

ユーザー

ガ イ ド の内容

こ のユーザーガ イ ド は、 次の各章か ら 構成 さ れてい ます。 • 第 1 章 「 ト ラ ン シーバお よ びツールの概要」 • 第 2 章 「 ト ラ ン シーバの共有機能」 • 第 3 章 「 ト ラ ン ス ミ ッ タ 」 • 第 4 章 「レ シーバ」 • 第 5 章 「ボー ドデザ イ ンのガ イ ド ラ イ ン」 • 付録 A 「8B/10B 有効な文字」その他の資料

次の資料 も 、http://japan.xilinx.com/6 か ら ダ ウ ン ロ ー ド で き ます。 • 『Spartan-6 フ ァ ミ リ 概要』 Spartan-6 フ ァ ミ リ の特徴 と 製品群の概要を説明 し てい ます。 • 『Spartan-6 FPGA デー タ シー ト: DC 特性お よ びス イ ッ チ特性』 Spartan-6 フ ァ ミ リ の DC 特性お よ びス イ ッ チ特性の仕様が記載 さ れてい ます。• 『Spartan-6 FPGA パ ッ ケージお よ びピ ン配置仕様』 デバ イ ス/パ ッ ケージの組み合わせお よ び最大 I/O 数の表、 ピ ン定義、 ピ ン配置表、 ピ ン配置図、 機械的図面、 温度仕様が記載 さ れてい ます。 • 『Spartan-6 FPGA コ ン フ ィ ギ ュ レーシ ョ ンガ イ ド 』 こ の包括的な コ ン フ ィ ギ ュ レーシ ョ ンガ イ ド は、 コ ン フ ィ ギ ュ レーシ ョ ン イ ン タ ーフ ェ イ ス (シ リ アル と パ ラ レル)、 マルチビ ッ ト ス ト リ ームの管理、 ビ ッ ト ス ト リ ームの暗号化、 バ ウ ン ダ リ ス キ ャ ンお よ び JTAG コ ン フ ィ ギ ュ レーシ ョ ン、リ コ ン フ ィ ギ ュ レーシ ョ ンテ ク ニ ッ ク の各 章で構成 さ れてい ます。

• 『Spartan-6 FPGA SelectIO リ ソ ース ユーザーガ イ ド 』

Spartan-6 の各デバ イ ス で使用可能な SelectIO™ リ ソ ース について説明 し てい ます。 • 『Spartan-6 FPGA ク ロ ッ キ ン グ リ ソ ースユーザーガ イ ド 』

Spartan-6 の各デバ イ ス で使用可能な DCM や PLL な ど の ク ロ ッ キ ン グ リ ソ ース について説 明 し てい ます。

• 『Spartan-6 FPGA ブ ロ ッ ク RAM リ ソ ースユーザーガ イ ド 』

Spartan-6 デバ イ ス のブ ロ ッ ク RAM の機能について説明 し てい ます。 • 『Spartan-6 FPGA コ ン フ ィ ギ ャ ブルロ ジ ッ ク ブ ロ ッ ク ユーザーガ イ ド 』

Spartan-6 の各デバ イ ス で使用可能な コ ン フ ィ ギ ャ ブル ロ ジ ッ ク ブ ロ ッ ク (CLB) の機能につ いて説明 し てい ます。

• 『Spartan-6 FPGA DSP48A1 ス ラ イ スユーザーガ イ ド 』

Spartan-6 の各デバ イ ス で使用可能な DSP48A1 ス ラ イ ス について説明 し てい ます。 • 『Spartan-6 FPGA メ モ リ コ ン ト ロ ー ラユーザーガ イ ド 』 Spartan-6 FPGA と 一般的な メ モ リ 規格の イ ン タ ーフ ェ イ ス を大幅に簡略化す る 専用の組み込 みマルチポー ト メ モ リ コ ン ト ロ ー ラ 、Spartan-6 FPGA メ モ リ コ ン ト ロ ー ラブ ロ ッ ク について 説明 し ます。 • 『Spartan-6 FPGA PCB デザ イ ンガ イ ド 』 PCB お よ び イ ン タ ーフ ェ イ ス レベルのデザ イ ン を決定す る 方法に焦点を当てた Spartan-6 デ バ イ ス の PCB デザ イ ン情報を提供 し ます。

その他の資料

次の資料 も 、 こ の文書の参考資料 と し て利用で き ます。 1. 『高速シ リ アル I/O を よ り 簡単に使用』 http://japan.xilinx.com/publications/books/serialio/index.htm 2. 『合成/シ ミ ュ レーシ ョ ンデザ イ ンガ イ ド 』 http://japan.xilinx.com/support/sw_manuals/xilinx8/download/その他の リ ソ ース

その他の資料を検索す る には、 次の Web サ イ ト にア ク セ ス し て く だ さ い。 http://japan.xilinx.com/support/documentation/index.htm第

1

章

ト ラ ン シーバおよびツールの概要

概要

GTP ト ラ ン シーバは、Spartan®-6 FPGA に搭載 さ れてい る 省電力 ト ラ ン シーバです。 こ の ト ラ ン シーバは、 柔軟に コ ン フ ィ ギ ュ レーシ ョ ン可能であ り FPGA のプ ロ グ ラ マブル ロ ジ ッ ク リ ソ ース と 密接に統合 さ れてい ます。 次の よ う な機能を含み多様な アプ リ ケーシ ョ ン をサポー ト し ます。• 終端お よ び電圧振幅が設定変更可能な CML (Current Mode Logic) シ リ アル ド ラ イ バ/バ ッ フ ァ • プ ロ グ ラ ム可能な TX プ リ エン フ ァ シ ス、 連続時間 RXリ ニア イ コ ラ イ ゼーシ ョ ン • 複数の業界規格をサポー ト • 614Mb/s ~ 810Mb/s • 1.22Gb/s ~ 1.62Gb/s • 2.45Gb/s ~ 3.125Gb/s • 8B/10B エン コーダ、 カ ン マア ラ イ メ ン ト 、 チ ャ ネルボ ンデ ィ ン グ、 ク ロ ッ ク コ レ ク シ ョ ン な ど の内蔵 さ れた PCS 機能オプシ ョ ン • 最小デー タ パ スレ イ テ ン シで確定的な固定レ イ テ ン シモー ド

• PCI Express®デザ イ ン用の ビー コ ン信号、 お よ び SATA デザ イ ン用の COM 信号サポー ト を

含む OOB 信号 • レ シーバア イ ス キ ャ ン

検証目的のための タ イ ム ド メ イ ンの水平方向ア イ ス キ ャ ン

は じ めて使用す る 場合は、 『High-Speed Serial I/O Made Simple』[参照1] を参照 し て く だ さ い。 こ の資料では、 高速シ リ アル ト ラ ン シーバ技術お よ びその応用例が説明 さ れてい ます。

Xilinx® CORE Generator™ ツールには、 異な る プ ロ ト コ ルの コ ン フ ィ ギ ュ レーシ ョ ン をサポー ト

す る ため、あ る いはカ ス タ マ ム コ ン フ ィ ギ ュ レーシ ョ ン を行 う ために、GTP ト ラ ン シーバを自動的 に コ ン フ ィ ギ ュ レーシ ョ ンす る ウ ィ ザー ド が含まれてい ます (24 ページの 「Spartan-6 FPGA GTP Transceiver Wizard」 参照)。

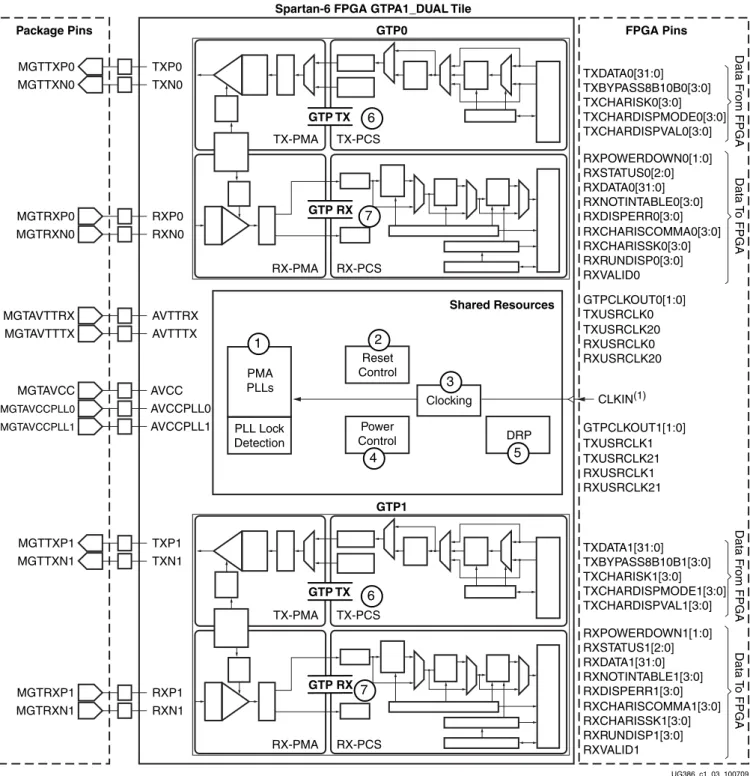

図 1-1 に、Spartan-6 FPGA GTP ト ラ ン シーバのブ ロ ッ ク 図を示 し ます。 使用モデルを含むレ シー バお よ び ト ラ ン ス ミ ッ タ の機能ブ ロ ッ ク については、 本ユーザーガ イ ド の各章で説明 し ます。

図 1-2 に、Spartan-6 デバ イ ス (XC6SLX45T) におけ る GTP ト ラ ン シーバの配置例を示 し ます。 1 つの GTPA1_DUAL タ イ ル内に 2 つの GTP ト ラ ン シーバが含まれます。小規模デバ イ ス の場合、 すべての GTPA1_DUAL タ イ ルは図 1-2 の よ う に上部 1 行に配置 さ れます。 大規模デバ イ ス の場 合、 ダ イ の上部お よ び下部に 1 行ずつ GTP ト ラ ン シーバの行があ り ます。

X-Ref Target - Figure 1-1

図 1-1 : Spartan-6 FPGA GTP ト ラ ン シーバブ ロ ッ ク の簡略図

TX-PMA

TX-PCS

FPGA TX Interface UG386_c1_01_100709 TX PIPE Control Phase Adjust FIFO PCIe BeaconFrom RX Parallel Data (Far-End PMA Loopback) To RX Parallel

Data (Near-End PCS Loopback)

From RX Parallel Data (Far-End PCS Loopback) PISO TX Pre-emp TX Clock Divider TX OOB and PCIe TX Driver Polarity Polarity SATA OOB 8B/ 10B Pattern Generator

RX-PMA

RX-PCS

FPGA RX Interface Loss of Sync RX PIPE Control RX Status Control SIPO RX Clock Divider RX EQ RX OOB RX CDR Elastic Buffer Pattern Checker Comma Detect and Align 10B /8BClockfromGTPA1_DUALPLL(s): one PLL per GTPA1_DUAL tile or one PLL per lane

概要 図 1-2 に示 さ れてい る そのほかの機能ブ ロ ッ ク の詳細は、 次の資料を参照 し て く だ さ い。 • 『Spartan-6 FPGA コ ン フ ィ ギ ュ レーシ ョ ン ユーザーガ イ ド』には、コ ン フ ィ ギ ュ レーシ ョ ン、 ク ロ ッ ク 、CMT、 お よ び I/O ブ ロ ッ ク に関す る 詳細情報が記載 さ れてい ます。 図 1-3 に、GTPA1_DUAL タ イ ル内にあ る 2 つの GTP ト ラ ン シーバブ ロ ッ ク の詳細を示 し ます。こ の 2 つの GTP ト ラ ン シーバは、2 つの リ フ ァ レ ン ス ク ロ ッ ク ピ ンペア を共有 し てい ます。

X-Ref Target - Figure 1-2

図 1-2 : Spartan-6 LX45T FPGA の GTP ト ラ ン シーバ Config Config I/O Ring Spartan-6 FPGA (XC6SLX45T) UG386_c1_02_100709 Integrated Block for PCI Express Operation GTPA1_DUAL Tile GTPA1_DUAL Tile DCM DCM DCM DCM Config Config I/O Ring Config Config I/O Ring I/O Ring I/O Ring

40 ページの 「 リ フ ァ レ ン ス ク ロ ッ ク の選択お よ び分配」 セ ク シ ョ ン では、 リ フ ァ レ ン ス ク ロ ッ ク ソ ースお よ び配線について詳 し く 説明 し ます

X-Ref Target - Figure 1-3

図 1-3 : GTPA1_DUAL タ イル内にある 2 つの GTP ト ラ ン シーバ

RX-PMA RX-PCS

GTP1 GTP0

Spartan-6 FPGA GTPA1_DUAL Tile

FPGA Pins Package Pins Shared Resources TX-PMA TX-PCS UG386_c1_03_100709 RX-PMA RX-PCS TX-PMA TX-PCS PMA PLLs PLL Lock Detection Reset Control TXDATA0[31:0] TXBYPASS8B10B0[3:0] TXCHARISK0[3:0] TXCHARDISPMODE0[3:0] TXCHARDISPVAL0[3:0] TXDATA1[31:0] TXBYPASS8B10B1[3:0] TXCHARISK1[3:0] TXCHARDISPMODE1[3:0] TXCHARDISPVAL1[3:0] RXPOWERDOWN0[1:0] RXSTATUS0[2:0] RXDATA0[31:0] RXNOTINTABLE0[3:0] RXDISPERR0[3:0] RXCHARISCOMMA0[3:0] RXCHARISSK0[3:0] RXRUNDISP0[3:0] RXVALID0 RXPOWERDOWN1[1:0] RXSTATUS1[2:0] RXDATA1[31:0] RXNOTINTABLE1[3:0] RXDISPERR1[3:0] RXCHARISCOMMA1[3:0] RXCHARISSK1[3:0] RXRUNDISP1[3:0] GTPCLKOUT0[1:0] GTPCLKOUT1[1:0] TXUSRCLK0 TXUSRCLK20 RXUSRCLK0 RXUSRCLK20 CLKIN(1) Data F rom FPGA TXUSRCLK1 TXUSRCLK21 RXUSRCLK1 RXUSRCLK21 Clocking Power Control DRP TXP0 MGTTXP0 TXN0 MGTTXN0 RXP0 MGTRXP0 RXN0 MGTRXN0 TXP1 MGTTXP1 TXN1 MGTTXN1 RXP1 MGTRXP1 RXN1 MGTRXN1 AVTTRX AVTTTX AVCC AVCCPLL0 Data F rom FPGA Data T o FPGA MGTAVCC MGTAVCCPLL0 AVCCPLL1 MGTAVCCPLL1 MGTAVTTRX MGTAVTTTX Data T o FPGA RXVALID1 GTP TX GTP RX GTP TX GTP RX 7 6 6 7 4 5 3 2 1 メ モ : 1. CLKIN は、2 つの差動 ク ロ ッ ク ピ ンペア を簡略 し て示 し てい ます。

ポー ト および属性のま と め

ポー ト および属性のま と め

ポー ト お よ び属性を各機能グループ (例 : リ フ ァ レ ン ス ク ロ ッ ク セ レ ク シ ョ ン) ご と に表に ま と め ま し た。 複数の章で言及 さ れてい る ポー ト お よ び属性については、 最初のページ を示 し ます。 表 1-1 に、 機能グループに基づいたポー ト お よ び属性の一覧を示 し ます。 表 1-1 : ポー ト のま と め ポー ト セ ク シ ョ ン (ページ番号) DRPDO[15:0] 69 ページ GTPCLKFBEAST[1:0] 44 ページ GTPCLKFBSEL0EAST[1:0] 44 ページ GTPCLKFBSEL0WEST[1:0] 45 ページ GTPCLKFBSEL1EAST[1:0] 45 ページ GTPCLKFBSEL1WEST[1:0] 45 ページ GTPCLKFBWEST[1:0] 45 ページ REFCLKPWRDNB0 45 ページ REFCLKPWRDNB1 45 ページ RXCHANBONDSEQ0 160 ページ RXCHANBONDSEQ1 160 ページ RXCHANISALIGNED0 160 ページ RXCHANISALIGNED1 160 ページ RXCHANREALIGN0 160 ページ RXCHANREALIGN1 160 ページ RXCLKCORCNT0[2:0] 154 ページ RXCLKCORCNT1[2:0] 154 ページ RXENCHANSYNC0 162 ページ RXENCHANSYNC1 162 ページ RXENPRBSTST0[2:0] 128 ページ RXENPRBSTST1[2:0] 128 ページ RXEQMIX0[1:0] 119 ページ RXEQMIX1[1:0] 119 ページ RXPOLARITY0 127 ページ RXPOLARITY1 127 ページ RXPRBSERR0 128 ページ RXPRBSERR1 128 ページ表 1-2 に、 機能グループに基づいたポー ト お よ び属性の一覧を示 し ます。 RXSLIDE0 133 ページ RXSLIDE1 133 ページ TXBUFDIFFCTRL0[2:0] 100 ページ TXBUFDIFFCTRL1[2:0] 100 ページ TXDIFFCTRL0[3:0] 101 ページ TXDIFFCTRL1[3:0] 101 ページ TXENPRBSTST0[2:0] 94 ページ TXENPRBSTST1[2:0] 94 ページ TXINHIBIT0 101 ページ TXINHIBIT1 101 ページ TXPOLARITY0 96 ページ TXPOLARITY1 96 ページ TXPRBSFORCEERR0 94 ページ TXPRBSFORCEERR1 94 ページ TXPREEMPHASIS0[2:0] 102 ページ TXPREEMPHASIS1[2:0] 102 ページ 表 1-2 : 属性のま と め 属性 セ ク シ ョ ン (ページ番号) AC_CAP_DIS_0 109 ページ AC_CAP_DIS_1 109 ページ CB2_INH_CC_PERIOD_(0,1) 202 ページ CHAN_BOND_1_MAX_SKEW_0 162 ページ CHAN_BOND_1_MAX_SKEW_1 162 ページ CHAN_BOND_2_MAX_SKEW_0 162 ページ CHAN_BOND_2_MAX_SKEW_1 162 ページ CHAN_BOND_KEEP_ALIGN_0 162 ページ CHAN_BOND_KEEP_ALIGN_1 162 ページ 表 1-1 : ポー ト のま と め (続き) ポー ト セ ク シ ョ ン (ページ番号)

ポー ト および属性のま と め CHAN_BOND_SEQ_1_2_0 162 ページ CHAN_BOND_SEQ_1_2_1 162 ページ CHAN_BOND_SEQ_1_3_0 162 ページ CHAN_BOND_SEQ_1_3_1 162 ページ CHAN_BOND_SEQ_1_4_0 162 ページ CHAN_BOND_SEQ_1_4_1 162 ページ CHAN_BOND_SEQ_1_ENABLE_0 162 ページ CHAN_BOND_SEQ_1_ENABLE_1 162 ページ CHAN_BOND_SEQ_2_1_0 163 ページ CHAN_BOND_SEQ_2_1_1 163 ページ CHAN_BOND_SEQ_2_2_0 163 ページ CHAN_BOND_SEQ_2_2_1 163 ページ CHAN_BOND_SEQ_2_3_0 163 ページ CHAN_BOND_SEQ_2_3_1 163 ページ CHAN_BOND_SEQ_2_4_0 163 ページ CHAN_BOND_SEQ_2_4_1 163 ページ CHAN_BOND_SEQ_2_ENABLE_0 163 ページ CHAN_BOND_SEQ_2_ENABLE_1 163 ページ CHAN_BOND_SEQ_2_USE_0 163 ページ CHAN_BOND_SEQ_2_USE_1 163 ページ CHAN_BOND_SEQ_LEN_0 163 ページ CHAN_BOND_SEQ_LEN_1 163 ページ CLK25_DIVIDER_(0,1) 200 ページ CLKINDC_B_(0,1) 207 ページ CLKRCV_TRST_(0,1) 207 ページ CLK_CORRECT_USE_0 157 ページ CLK_CORRECT_USE_1 157 ページ CLK_COR_ADJ_LEN_0 154 ページ CLK_COR_ADJ_LEN_1 154 ページ CLK_COR_DET_LEN_0 154 ページ CLK_COR_DET_LEN_1 154 ページ 表 1-2 : 属性のま と め (続き) 属性 セ ク シ ョ ン (ページ番号)

CLK_COR_INSERT_IDLE_FLAG_0 154 ページ CLK_COR_INSERT_IDLE_FLAG_1 154 ページ CLK_COR_KEEP_IDLE_0 155 ページ CLK_COR_KEEP_IDLE_1 155 ページ CLK_COR_MAX_LAT_0 155 ページ CLK_COR_MAX_LAT_1 155 ページ CLK_COR_MIN_LAT_0 155 ページ CLK_COR_MIN_LAT_1 155 ページ CLK_COR_PRECEDENCE_0 155 ページ CLK_COR_PRECEDENCE_1 155 ページ CLK_COR_REPEAT_WAIT_0 155 ページ CLK_COR_REPEAT_WAIT_1 155 ページ CLK_COR_SEQ_1_1_0 156 ページ CLK_COR_SEQ_1_1_1 156 ページ CLK_COR_SEQ_1_2_0 156 ページ CLK_COR_SEQ_1_2_1 156 ページ CLK_COR_SEQ_1_3_0 156 ページ CLK_COR_SEQ_1_3_1 156 ページ CLK_COR_SEQ_1_4_0 156 ページ CLK_COR_SEQ_1_4_1 156 ページ CLK_COR_SEQ_1_ENABLE_0 156 ページ CLK_COR_SEQ_1_ENABLE_1 156 ページ CLK_COR_SEQ_2_1_0 156 ページ CLK_COR_SEQ_2_1_1 156 ページ CLK_COR_SEQ_2_2_0 156 ページ CLK_COR_SEQ_2_2_1 156 ページ CLK_COR_SEQ_2_3_0 156 ページ CLK_COR_SEQ_2_3_1 156 ページ CLK_COR_SEQ_2_4_0 156 ページ 表 1-2 : 属性のま と め (続き) 属性 セ ク シ ョ ン (ページ番号)

ポー ト および属性のま と め CLK_COR_SEQ_2_ENABLE_1 156 ページ CLK_COR_SEQ_2_USE_0 156 ページ CLK_COR_SEQ_2_USE_1 156 ページ CM_TRIM_0[1:0] 109 ページ CM_TRIM_1[1:0] 109 ページ COMMA_10B_ENABLE_0 134 ページ COMMA_10B_ENABLE_1 134 ページ GTP_CFG_PWRUP_(0,1) 201 ページ MCOMMA_10B_VALUE_0 134 ページ MCOMMA_10B_VALUE_1 134 ページ OOB_CLK_DIVIDER_0 116 ページ OOB_CLK_DIVIDER_1 116 ページ PCI_EXPRESS_MODE_0 163 ページ PCI_EXPRESS_MODE_1 163 ページ PCOMMA_10B_VALUE_0 134 ページ PCOMMA_10B_VALUE_1 134 ページ PMA_COM_CFG_EAST 209 ページ PMA_COM_CFG_WEST 209 ページ PMA_RXSYNC_CFG_(0,1) 209 ページ PMA_RX_CFG_0 122 ページ RCV_TERM_GND_0 109 ページ RCV_TERM_GND_1 109 ページ RCV_TERM_VTTRX_0 109 ページ RCV_TERM_VTTRX_1 109 ページ RXEQ_CFG_0[7:0] 119 ページ RXEQ_CFG_1[7:0] 119 ページ RX_DECODE_SEQ_MATCH_0 157 ページ RX_DECODE_SEQ_MATCH_1 157 ページ RX_EN_MODE_RESET_BUF_(0,1) 202 ページ RX_LOS_INVALID_INCR_0 136 ページ RX_LOS_INVALID_INCR_1 136 ページ 表 1-2 : 属性のま と め (続き) 属性 セ ク シ ョ ン (ページ番号)

Spartan-6 FPGA GTP Transceiver Wizard

Spartan-6 FPGA GTP Transceiver Wizard は、GTP ト ラ ン シーバプ リ ミ テ ィ ブ (GTPA1_DUAL) を イ ン ス タ ン シエー ト す る ための ラ ッ パフ ァ イ ル生成に最適です。 こ の ウ ィ ザー ド は、 ザ イ リ ン ク ス の CORE Generator ツールに含まれてい ます。使用前に最新の IP ア ッ プデー ト がダ ウ ン ロ ー ド さ れ てい る こ と を確認 し て く だ さ い。 使用方法の詳細は、 『Spartan-6 FPGA GTP Transceiver Getting Started Guide』に記載 さ れてい ます。

1. ザ イ リ ン ク ス の CORE Generator ツールを起動 し ます。

2. GTP Transceiver Wizard は、 ツ リ ー構造の次のデ ィ レ ク ト リ 以下にあ り ます。 /FPGA Features & Design/IO Interfaces

図 1-4 を参照 し て く だ さ い。 RX_SLIDE_MODE_0 134 ページ RX_SLIDE_MODE_1 134 ページ TERMINATION_CTRL_0[4:0] 110 ページ TERMINATION_CTRL_1[4:0] 110 ページ TERMINATION_OVRD_0 110 ページ TERMINATION_OVRD_1 110 ページ TST_ATTR_(0,1) 207 ページ TXRX_INVERT_0 85 ページ TXRX_INVERT_1 85 ページ TX_DETECT_RX_CFG_(0,1) 206 ページ TX_IDLE_DELAY_(0,1) 206 ページ TX_TDCC_CFG_(0,1) 209 ページ 表 1-2 : 属性のま と め (続き) 属性 セ ク シ ョ ン (ページ番号)

Spartan-6 FPGA GTP Transceiver Wizard

3. [Spartan-6 FPGA GTP Transceiver Wizard] を ダブル ク リ ッ ク し て ウ ィ ザー ド を起動 し ます。

X-Ref Target - Figure 1-4

図 1-4 : Spartan-6 FPGA GTP Transceiver Wizard

シ ミ ュ レーシ ョ ン

機能の説明

GTP ト ラ ン シーバを使用す る シ ミ ュ レーシ ョ ンの場合、シ ミ ュ レーシ ョ ン環境お よ びテ ス ト ベンチ に対 し て特定の要件があ り ます。 『合成/シ ミ ュ レーシ ョ ンデザ イ ンガ イ ド』 [参照2]には、サポー ト さ れてい る シ ミ ュ レー タ の環 境設定方法を使用ハー ド ウ ェ ア記述言語 (HDL) に基づいて記載 し てい ます。 こ のデザ イ ン ガ イ ド は、 ザ イ リ ン ク スウ ェ ブサ イ ト か ら ダ ウ ン ロ ー ド で き ます。 GTP ト ラ ン シーバを使用す る デザ イ ン を シ ミ ュ レーシ ョ ンす る 際の要件は、 次の と お り です。 • シ ミ ュ レー タ が SecureIP モデルをサポー ト し てい る こ と 。構築 さ れたブ ロ ッ ク の イ ンプ リ メ ン テーシ ョ ンに使用 さ れた Verilog/HDL の暗号化バージ ョ ン をサポー ト し てい る 必要があ る 。 SecureIP は、 最新の IP 暗号化方法です。SecureIP モデルをサポー ト す る には、Verilog LRM - IEEE Std 1364-2005 暗号化に準拠 し たシ ミ ュ レー タ が必要です。 • VHDL シ ミ ュ レーシ ョ ン用の混合言語シ ミ ュ レー タ 。 SecureIP モデルは基本的に Verilog を使用 し ます。 こ れ ら を VHDL デザ イ ン で使用す る 場合 は、 混合言語シ ミ ュ レー タ が必要にな り ます。 シ ミ ュ レー タ は、VHDL と Verilog を同時にシ ミ ュ レーシ ョ ンで き る 必要があ り ます。 • GTPA1_DUAL SecureIP モデルが イ ン ス ト ール さ れてい る こ と 。 • SecureIP の使用に対応 し た適切なシ ミ ュ レー タ 設定 (初期化フ ァ イ ル、 環境変数)。• シ ミ ュ レーシ ョ ン ラ イ ブ ラ リ (例 : UNISIM、SIMPRIMS) を コ ンパ イ ルす る COMPXLIB を 適切な順序で実行す る 。 • 適切なシ ミ ュ レー タ リ ゾ リ ュ ーシ ョ ンの設定 (Verilog) • SecureIP をサポー ト す る 設定の詳細は、 シ ミ ュ レー タ のユーザーガ イ ド お よ び 『合成/シ ミ ュ レーシ ョ ンデザ イ ンガ イ ド 』を参照。

シ ミ ュ レーシ ョ ン専用のポー ト お よび属性

GTPA1_DUALプ リ ミ テ ィ ブには、 シ ミ ュ レーシ ョ ン専用の属性があ り ます。表 1-3 に、 シ ミ ュ レー シ ョ ン専用のGTPA1_DUALプ リ ミ テ ィ ブの属性を示 し ます。シ ミ ュ レーシ ョ ン 表 1-3 : GTPA1_DUAL のシ ミ ュ レーシ ョ ン専用の属性 属性 種類 説明 SIM_GTPRESET_SPEEDUP 整数 シ ミ ュ レーシ ョ ンにおいて、GTPRESET シーケ ン ス を完了 し て各 GTP ト ラ ン シーバの PMA PLL を ロ ッ ク す る ま での時間を短縮 し ます。 0 : 通常の時間内で GTPRESET シーケ ン ス を シ ミ ュ レーシ ョ ンす る (標準的な初期化時間は約 160μs)。 1 : GTPRESET シーケ ン ス の時間を短縮す る (高速初期化時間は 約 300ns)。 SIM_RECEIVER_DETECT_PASS ブール関数 GTP ト ラ ン シーバの TXDETECTRX 機能のシ ミ ュ レーシ ョ ンに使用 し ます。 TRUE : TX シ リ アルポー ト への RX 接続を シ ミ ュ レーシ ョ ンす る 。 TXDETECTRX が レ シーバ検出を開始 し 、RX ポー ト が接続 さ れ てい る こ と を示す RXSTATUS[2:0] = 011 が出力 さ れ る 。 FALSE (デフ ォ ル ト) : 未接続の TX ポー ト を シ ミ ュ レーシ ョ ンす る 。TXDETECTRX が レ シーバ検出を開始 し 、RX ポー ト が未接 続であ る こ と を示す RXSTATUS[2:0] = 000 が出力 さ れ る 。 SIM_REFCLK0_SOURCE 3 ビ ッ ト バ イ ナ リ GTP0 ト ラ ン シーバの PMA PLL が常に同 じ リ フ ァ レ ン ス ク ロ ッ ク ソ ー ス で駆動 さ れ る デザ イ ン を シ ミ ュ レ ーシ ョ ンす る 際、 使用 さ れ る リ フ ァ レ ン ス ク ロ ッ ク ソ ース を選択 し ます。 こ の属性で リ フ ァ レ ン ス ク ロ ッ ク を選択す る 場合、REFSELDYPLL0 ポー ト は000に設定す る 必要があ り ます。 オンザフ ラ イ で リ フ ァ レ ン ス ク ロ ッ ク ソ ース を変更 す る 必要があ る マルチ レー ト デザ イ ンの場合は、REFSELDYPLL0 ポー ト を使用 し て ソ ース を動的に選択 し ます。 000 : CLK00 ポー ト を ソ ース と し て選択 001 : GCLK00 ポー ト を ソ ース と し て選択 010 : PLLCLK00 ポー ト を ソ ース と し て選択 011 : CLKINEAST0 ポー ト を ソ ース と し て選択 100 : CLK10 ポー ト を ソ ース と し て選択 101 : GCLK10 ポー ト を ソ ース と し て選択 110 : PLLCLK10 ポー ト を ソ ース と し て選択 111 : CLKINWEST0 ポー ト を ソ ース と し て選択

シ ミ ュ レーシ ョ ン専用のポー ト はあ り ません。

SIM_GTPRESET_SPEEDUP

SIM_GTPRESET_SPEEDUP 属性を使用す る と 、 シ ミ ュ レーシ ョ ン中におけ る 各 GTP ト ラ ン シー バの PMA PLL が ロ ッ ク す る ま での時間を短縮で き ます。 TXOUTCLK ま たは RXRECCLK を使用 し て ク ロ ッ ク を生成す る デザ イ ンの場合、GTP ト ラ ン シーバが ロ ッ ク プ ロ セ ス中の途中では、こ れ ら の ク ロ ッ ク が フ ラ ッ ト ラ イ ン (変化 し ない状態) にな る 場合があ り ます。PLL ま たはデジ タ ル ク ロ ッ クマネージ ャ (DCM) を使用 し て TXOUTCLK ま たは RXRECCLK を生成す る 場合、 最終的な ク ロ ッ ク 出力は、GTP ト ラ ン シーバ と PLL (ま たは DCM) の両方が ロ ッ ク す る ま で有効にはな り ません。式 1-1 は、 シ ミ ュ レーシ ョ ンで TXOUTCLK ま たは RXRECCLK か ら の安定 し た ソ ース が有効にな る ま での概算時間 (PLL ま たは DCM で必 要な時間を含む) を求め る 等式です。 式1-1 PLL ま たは DCM を使用 し ない場合、 それ ら に該当す る 項は等式か ら 削除で き ます。 SIM_REFCLK1_SOURCE 3 ビ ッ ト バ イ ナ リ GTP1 ト ラ ン シーバの PMA PLL が常に同 じ リ フ ァ レ ン ス ク ロ ッ ク ソ ー ス で駆動 さ れ る デザ イ ン を シ ミ ュ レ ーシ ョ ンす る 際、 使用 さ れ る リ フ ァ レ ン ス ク ロ ッ ク ソ ース を選択 し ます。 こ の属性で リ フ ァ レ ン ス ク ロ ッ ク を選択す る 場合、REFSELDYPLL1 ポー ト は 000 に設定す る 必要があ り ます。 オンザフ ラ イ で リ フ ァ レ ン ス ク ロ ッ ク ソ ース を変更 す る 必要があ る マルチ レー ト デザ イ ンの場合は、REFSELDYPLL1 ポー ト を使用 し て ソ ース を動的に選択 し ます。 000 : CLK01 ポー ト を ソ ース と し て選択 001 : GCLK01 ポー ト を ソ ース と し て選択 010 : PLLCLK01 ポー ト を ソ ース と し て選択 011 : CLKINEAST1 ポー ト を ソ ース と し て選択 100 : CLK11 ポー ト を ソ ース と し て選択 101 : GCLK11 ポー ト を ソ ース と し て選択 110 : PLLCLK11 ポー ト を ソ ース と し て選択 111 : CLKINWEST1 ポー ト を ソ ース と し て選択 SIM_TX_ELEC_IDLE_LEVEL 1 ビ ッ ト バ イ ナ リ 電気的ア イ ド ルのシ ミ ュ レーシ ョ ンにおけ る TXN お よ び TXP の値を 設定 し ます。 設定可能な値は 0、1、X、 ま たは Z と な り 、 デフ ォ ル ト は X です。 SIM_VERSION リ ール 多様な シ リ コ ン の ス テ ッ ピ ン グ と 一致 さ せ る ため、 シ ミ ュ レーシ ョ ン バージ ョ ン を選択 し ます。 デフ ォ ル ト は 1.0 です。 表 1-3 : GTPA1_DUAL のシ ミ ュ レーシ ョ ン専用の属性 (続き) 属性 種類 説明シ ミ ュ レーシ ョ ン

SIM_RECEIVER_DETECT_PASS

GTP ト ラ ン シーバには、 ト ラ ン ス ミ ッ タ のシ リ アル ポー ト が現時点で レ シーバに接続 さ れてい る か を、 その ト ラ ン ス ミ ッ タ で検出す る TXDETECTRX 機能があ り ます。 こ の検出は、TXP/TXN 差 動ピ ンペアの立ち上が り 時間を計測す る こ と に よ っ て行われます (103 ページの「PCI Express デザ イ ン用の TX レ シーバ検出機能」 参照)。GTPA1_DUAL の SecureIP には、TXDETECTRX を シ ミ ュ レーシ ョ ンす る ための属性 (SIM_ RECEIVER_DETECT_PASS) があ り ます。 こ の属性は、TXP/TXN 差動ピ ンペアの立ち上が り 時 間の計測をモデル化せずに、GTP ト ラ ン シーバの TXDETECTRX を シ ミ ュ レーシ ョ ンで き ます。 SIM_RECEIVER_DETECT_PASS は、デフ ォ ル ト で FALSE に設定 さ れてい ます。こ の属性の場合 は、未接続の レ シーバを構築 し 、TXDETECTRX 動作は レ シーバが接続 さ れていない こ と を示 し ま す。 接続 さ れてい る レ シーバを構築す る 場合は、 その ト ラ ン シーバの SIM_RECEIVER_DETECT_ PASS を TRUE に設定 し て く だ さ い。

SIM_REFCLK0_SOURCE

GTPA1_DUAL の SecureIP モデルには、 シ ミ ュ レーシ ョ ン中に GTP0 ト ラ ン シーバの PMA PLL を駆動す る リ フ ァ レ ン ス ク ロ ッ ク を選択す る 属性 (SIM_REFCLK0_SOURCE) があ り ます。 こ の 属性は、GTP0 ト ラ ン シーバの PMA PLL の ク ロ ッ ク 入力が常に同 じ リ フ ァ レ ン ス ク ロ ッ ク ソ ース で駆動 さ れ る デザ イ ンで使用 さ れます。 リ フ ァ レ ン ス ク ロ ッ ク ソ ース には、 ト ラ ン シーバが属す る タ イ ル専用の ク ロ ッ ク 、西方向の リ フ ァ レ ン ス ク ロ ッ ク 、 東方向の リ フ ァ レ ン ス ク ロ ッ ク 、 お よ び FPGA ロ ジ ッ ク か ら の ク ロ ッ ク があ り ます。27 ページの表 1-3 に、 こ の属性の有効な設定を示 し ます GTP0 ト ラ ン シーバの PMA PLL を駆動す る リ フ ァ レ ン ス ク ロ ッ ク ソ ース を オンザフ ラ イ で変更 す る 必要があ る マルチ レー ト デザ イ ンの場合は、REFSELDYPLL0 ポー ト を使用 し て ソ ース を動 的に選択 し ます。

SIM_REFCLK1_SOURCE

GTPA1_DUAL の SecureIP モデルには、 シ ミ ュ レーシ ョ ン中に GTP1 ト ラ ン シーバの PMA PLL を駆動す る リ フ ァ レ ン ス ク ロ ッ ク を選択す る 属性 (SIM_REFCLK1_SOURCE) があ り ます。 こ の 属性は、GTP1 ト ラ ン シーバの PMA PLL の ク ロ ッ ク 入力が常に同 じ リ フ ァ レ ン ス ク ロ ッ ク ソ ース で駆動 さ れ る デザ イ ンで使用 さ れます。 リ フ ァ レ ン ス ク ロ ッ ク ソ ース には、 ト ラ ン シーバが属す る タ イ ル専用の ク ロ ッ ク 、西方向の リ フ ァ レ ン ス ク ロ ッ ク 、 東方向の リ フ ァ レ ン ス ク ロ ッ ク 、 お よ び FPGA ロ ジ ッ ク か ら の ク ロ ッ ク があ り ます。27 ページの表 1-3 に、 こ の属性の可能な設定を示 し ます GTP1 ト ラ ン シーバの PMA PLL を駆動す る リ フ ァ レ ン ス ク ロ ッ ク ソ ース を オンザフ ラ イ で変更 す る 必要があ る マルチ レー ト デザ イ ンの場合は、REFSELDYPLL1 ポー ト を使用 し て ソ ース を動 的に選択 し ます。

SIM_TX_ELEC_IDLE_LEVEL

こ の属性は、 電気的ア イ ド ルのシ ミ ュ レーシ ョ ン中におけ る ト ラ ン ス ミ ッ タ の作動出力ペア (TXN お よ び TXP) の値を設定 し ます。設定可能な値は 0、1、X、 ま たは Z と な り 、デフ ォ ル ト は X です。SIM_VERSION

こ の属性は、異な る シ リ コ ン ス テ ッ ピ ン グ と 一致 さ せ る ためにシ ミ ュ レーシ ョ ンバージ ョ ン を選択 し ます。 デフ ォ ル ト は 1.0 です。イ ン プ リ メ ン テーシ ョ ン

本章では、 デザ イ ンに イ ン ス タ ン シエー ト し た Spartan-6 FPGA GTPA1_DUAL タ イ ルをデバ イ ス リ ソ ースへマ ッ プす る 際に必要な情報を提供 し ます。 • デバ イ ス/パ ッ ケージの組み合わせにおけ る GTPA1_DUAL タ イ ルの位置 • 各 GTPA1_DUAL タ イ ルに関連す る 外部信号のパ ッ ド 番号 • デザ イ ンに イ ン ス タ ン シエー ト さ れた GTPA1_DUAL タ イ ルお よ び ク ロ ッ ク リ ソ ース が、 ユーザー制約フ ァ イ ル (UCF) を使用 し て、 ど の よ う にマ ッ プ さ れ る か 通常、設計の初期段階で GTP ト ラ ン シーバの位置を定義す る こ と に よ っ て、ク ロ ッ ク リ ソ ース の適 切な使用が可能にな り 、 ボー ド 設計時のシ グナル イ ン テ グ リ テ ィ 解析がシ ンプルにな り ます。 イ ン プ リ メ ン テーシ ョ ン フ ロ ーでは UCF 内の配置制約を使用す る こ と で、 こ の定義プ ロ セ ス をサポー ト し ます。 本章では、GTP の ク ロ ッ キ ン グ コ ン ポーネ ン ト の イ ン ス タ ン シエー ト 方法について説明 し ます。 GTPA1_DUAL タ イ ルのその他の ク ロ ッ キ ン グオプシ ョ ンの詳細は、40 ページの「 リ フ ァ レ ン ス ク ロ ッ ク の選択お よ び分配」 を参照 し て く だ さ い。 GTPA1_DUAL タ イ ルの位置は、XY 座標で指定 さ れます (X = 列、Y = 行)。Spartan-6 の小規模デ バ イ ス の場合、すべての GTP ト ラ ン シーバはダ イ 上部にあ る 行に配置 さ れます。大規模デバ イ ス の 場合、 ダ イ の上部お よ び下部に 1 行ずつ GTP ト ラ ン シーバの行があ り ます。 X0Y0 で指定 さ れた ト ラ ン シーバは、 それぞれのデバ イ ス/パ ッ ケージの組み合わせにおいて、 最下 位バン ク の最下位ポジシ ョ ンに配置 さ れます。上部のみに ト ラ ン シーバの行があ る デバ イ ス の場合、 Y 座標の値は常に 0 と な り ます。 上部 と 下部に ト ラ ン シーバの行があ る デバ イ ス の場合、 下部行の Y 座標の値は 0 と な り 上部行の Y 座標の値は 1 と な り ます。 GTP ト ラ ン シーバを使用す る デザ イ ン用の UCF フ ァ イ ルを作成す る 方法は 2 つあ り ます。 推奨方 法は、GTP Transceiver Wizard を使用す る 方法です (24 ページの「Spartan-6 FPGA GTP Transceiver Wizard」参照)。 ウ ィ ザー ド は、 ト ラ ン シーバを コ ン フ ィ ギ ュ レーシ ョ ン し 、GTP_DUAL 配置情報 のプ レース ホルダ を含む UCF テ ンプ レー ト を自動生成 し ます。こ の方法で生成 さ れた UCF は編集 可能で、 パ ラ メ ー タ や配置情報を アプ リ ケーシ ョ ン用にカ ス タ マ イ ズで き ます。 UCF 生成の 2 つ目の方法は手書 き に よ る も のです。こ の方法で作成す る 場合、設計者は、ト ラ ン シー バの動作を制御す る コ ン フ ィ ギ ュ レーシ ョ ン属性お よ び タ イ ル位置のパ ラ メ ー タ の両方を入力す る 必要があ り ます。GTP ト ラ ン シーバの コ ン フ ィ ギ ュ レーシ ョ ンに必要なすべてのパ ラ メ ー タ を確実 に入力す る よ う 、 十分に注意 し て く だ さ い。

イ ン プ リ メ ン テーシ ョ ン

図 1-5 に、CSG324 パ ッ ケージで使用可能なすべてのデバ イ ス におけ る 、ダ イ 左側部分の GTP ト ラ ン シーバの位置情報を示 し ます。

図 1-6 に、CSG324 パ ッ ケージで使用可能なすべてのデバ イ ス におけ る 、ダ イ 右側部分の GTP ト ラ ン シーバの位置情報を示 し ます。

X-Ref Target - Figure 1-5

図 1-5 : CSG324 パ ッ ケージの配置図 (1) XC6SLX25T: GTPA1_DUAL_X0Y0 XC6SLX45T: GTPA1_DUAL_X0Y0 B6 B4 A6 A4 C5 C7 D5 D7 A8 B8 C9 D9 MGTTXP1_101 MGTTXP0_101 MGTTXN1_101 MGTTXN0_101 MGTRXN0_101 MGTRXN1_101 MGTRXP0_101 MGTRXP1_101 MGTREFCLK0N_101 MGTREFCLK0P_101 MGTREFCLK1N_101 MGTREFCLK1P_101 B7 D10 C8 D6 A5 E7 E5 MGTAVCCPLL0_101 MGTAVCCPLL1_101 MGTAVCC_101 MGTAVTTRX_101 MGTAVTTTX_101 MGTRREF_101 MGTAVTTRCAL_101 UG386_c1_05_100909

Top

X-Ref Target - Figure 1-6

図 1-6 : CSG324 パ ッ ケージの配置図 (2) UG386_c1_06_100909 XC6SLX25T: Not Available XC6SLX45T: GTPA1_DUAL_X1Y0 B14 B12 A14 A12 C11 C13 D11 D13 A10 B10 E10 F10 MGTTXP1_123 MGTTXP0_123 MGTTXN1_123 MGTTXN0_123 MGTRXN0_123 MGTRXN1_123 MGTRXP0_123 MGTRXP1_123 MGTREFCLK0N_123 MGTREFCLK0P_123 MGTREFCLK1N_123 MGTREFCLK1P_123 B11 E11 E9 D12 A13 MGTAVCCPLL0_123 MGTAVCCPLL1_123 MGTAVCC_123 MGTAVTTRX_123 MGTAVTTTX_123

Top

図 1-7 に、FF484 パ ッ ケージで使用可能なすべてのデバ イ ス におけ る 、ダ イ 左側部分の GTP ト ラ ン シーバの位置情報を示 し ます。

X-Ref Target - Figure 1-7

図 1-7 : FF484 パ ッ ケージの配置図 (1)

Bottom

UG386_c1_07_100909 B8 B6 A8 A6 C7 C9 D7 D9 B10 A10 D11 C11Top

XC6SLX25T: GTPA1_DUAL_X0Y0 XC6SLX45T: GTPA1_DUAL_X0Y0 XC6SLX75T: GTPA1_DUAL_X0Y1 XC6SLX100T: GTPA1_DUAL_X0Y1 XC6SLX150T: GTPA1_DUAL_X0Y1 MGTTXP1_101 MGTTXP0_101 MGTTXN1_101 MGTTXN0_101 MGTRXN0_101 MGTRXN1_101 MGTRXP0_101 MGTRXP1_101 MGTREFCLK0N_101 MGTREFCLK0P_101 MGTREFCLK1N_101 MGTREFCLK1P_101 MGTAVCCPLL0_101 MGTAVCCPLL1_101 B9 D12 MGTAVCC_101 C10 MGTAVTTRX_101 MGTAVTTTX_101 D8 A7 MGTRREF_101 MGTAVTTRCAL_101 E9 E8 XC6SLX25T: Not Available XC6SLX45T: Not Available XC6SLX75T: GTPA1_DUAL_X0Y0 XC6SLX100T: GTPA1_DUAL_X0Y0 XC6SLX150T: GTPA1_DUAL_X0Y0 UNB UNB UNB UNB UNB UNB UNB UNB UNB UNB UNB UNB OPAD_X0Y0 OPAD_X0Y1 OPAD_X0Y2 OPAD_X0Y3 IPAD_X0Y0 IPAD_X0Y1 IPAD_X0Y2 IPAD_X0Y3 IPAD_X0Y4 IPAD_X0Y5 IPAD_X0Y6 IPAD_X0Y7イ ン プ リ メ ン テーシ ョ ン

図 1-8 に、FF484 パ ッ ケージで使用可能なすべてのデバ イ ス におけ る 、ダ イ 右側部分の GTP ト ラ ン シーバの位置情報を示 し ます。

X-Ref Target - Figure 1-8

図 1-8 : FF484 パ ッ ケージの配置図 (2)

Bottom

UG386_c1_08_100909Top

XC6SLX25T: Not Available XC6SLX45T: GTPA1_DUAL_X1Y0 XC6SLX75T: GTPA1_DUAL_X1Y1 XC6SLX100T: GTPA1_DUAL_X1Y1 XC6SLX150T: GTPA1_DUAL_X1Y1 B16 B14 A16 A14 C13 C15 D13 D15 B12 A12 F12 E12 MGTTXP1_123 MGTTXP0_123 MGTTXN1_123 MGTTXN0_123 MGTRXN0_123 MGTRXN1_123 MGTRXP0_123 MGTRXP1_123 MGTREFCLK0N_123 MGTREFCLK0P_123 MGTREFCLK1N_123 MGTREFCLK1P_123 B13 E13 MGTAVCCPLL0_123 MGTAVCCPLL1_123 E10 MGTAVCC_123 D14 A15 MGTAVTTRX_123 MGTAVTTTX_123 XC6SLX25T: Not Available XC6SLX45T: Not Available XC6SLX75T: GTPA1_DUAL_X1Y0 XC6SLX100T: GTPA1_DUAL_X1Y0 XC6SLX150T: GTPA1_DUAL_X1Y0 UNB UNB UNB UNB UNB UNB UNB UNB UNB UNB UNB UNB OPAD_X1Y0 OPAD_X1Y1 OPAD_X1Y2 OPAD_X1Y3 IPAD_X1Y0 IPAD_X1Y1 IPAD_X1Y2 IPAD_X1Y3 IPAD_X1Y4 IPAD_X1Y5 IPAD_X1Y6 IPAD_X1Y7図 1-9 に、FF676 パ ッ ケージで使用可能なすべてのデバ イ ス におけ る 、ダ イ 左側部分の GTP ト ラ ン シーバの位置情報を示 し ます。

X-Ref Target - Figure 1-9

図 1-9 : FF676 パ ッ ケージの配置図 (1)

Top

Bottom

UG386_c1_09_100909 MGTAVCCPLL0_101 MGTAVCCPLL1_101 B11 C12 MGTTXP1_101 MGTTXP0_101 B8 B6 MGTAVCC_101 C10 MGTTXN1_101 MGTTXN0_101 A8 A6 MGTAVTTRX_101 MGTAVTTTX_101 D8 A7 MGTRXN0_101 MGTRXN1_101 C7 C9 MGTRREF_101 MGTAVTTRCAL_101 E9 E11 MGTRXP0_101 MGTRXP1_101 D7 D9 MGTREFCLK0N_101 MGTREFCLK0P_101 A10 B10 MGTREFCLK1N_101 MGTREFCLK1P_101 C11 D11 XC6SLX75T: GTPA1_DUAL_X0Y1 XC6SLX100T: GTPA1_DUAL_X0Y1 XC6SLX150T: GTPA1_DUAL_X0Y1 MGTAVCCPLL0_245 MGTAVCCPLL1_245 AE12 AD13 MGTTXP1_245 MGTTXP0_245 AE9 AE7 MGTAVCC_245 AD11 MGTTXN1_245 MGTTXN0_245 AF9 AF7 MGTAVTTRX_245 MGTAVTTTX_245 AC9 AF8 MGTRXN0_245 MGTRXN1_245 AD8 AD10 MGTRREF_245 MGTAVTTRCAL_245 AB10 AB12 MGTRXP0_245 MGTRXP1_245 AC8 AC10 MGTREFCLK0N_245 MGTREFCLK0P_245 AF11 AE11 MGTREFCLK1N_245 MGTREFCLK1P_245 AD12 AC12 XC6SLX75T: GTPA1_DUAL_X0Y0 XC6SLX100T: GTPA1_DUAL_X0Y0 XC6SLX150T: GTPA1_DUAL_X0Y0イ ン プ リ メ ン テーシ ョ ン

図 1-10 に、FF676 パ ッ ケージで使用可能なすべてのデバ イ ス におけ る 、 ダ イ 右側部分の GTP ト ラ ン シーバの位置情報を示 し ます。

X-Ref Target - Figure 1-10

図 1-10 : FF676 パ ッ ケージの配置図 (2)

Top

Bottom

UG386_c1_10 _100909 XC6SLX75T: GTPA1_DUAL_X1Y1 XC6SLX100T: GTPA1_DUAL_X1Y1 XC6SLX150T: GTPA1_DUAL_X1Y1 B20 B18 A20 A18 C17 C19 D17 D19 C15 D15 A16 B16 MGTTXP1_123 MGTTXP0_123 MGTTXN1_123 MGTTXN0_123 MGTRXN0_123 MGTRXN1_123 MGTRXP0_123 MGTRXP1_123 MGTREFCLK0N_123 MGTREFCLK0P_123 MGTREFCLK1N_123 MGTREFCLK1P_123 C14 B15 MGTAVCCPLL0_123 MGTAVCCPLL1_123 C16 MGTAVCC_123 D18 A19 MGTAVTTRX_123 MGTAVTTTX_123 XC6SLX75T: GTPA1_DUAL_X1Y0 XC6SLX100T: GTPA1_DUAL_X1Y0 XC6SLX150T: GTPA1_DUAL_X1Y0 AE21 AE19 AF21 AF19 AD18 AD20 AC18 AC20 AD16 AC16 AF17 AE17 MGTTXP1_267 MGTTXP0_267 MGTTXN1_267 MGTTXN0_267 MGTRXN0_267 MGTRXN1_267 MGTRXP0_267 MGTRXP1_267 MGTREFCLK0N_267 MGTREFCLK0P_267 MGTREFCLK1N_267 MGTREFCLK1P_267 AD15 AE16 MGTAVCCPLL0_267 MGTAVCCPLL1_267 AD17 MGTAVCC_267 AC19 AF20 MGTAVTTRX_267 MGTAVTTTX_267図 1-11 に、FF900 パ ッ ケージで使用可能なすべてのデバ イ ス におけ る 、 ダ イ 左側部分の GTP ト ラ ン シーバの位置情報を示 し ます。

X-Ref Target - Figure 1-11

図 1-11 : FF900 パ ッ ケージの配置図 (1)

Top

Bottom

UG386_c1_11_100909 XC6SLX100T: GTPA1_DUAL_X0Y1 XC6SLX150T: GTPA1_DUAL_X0Y1 B11 B9 A11 A9 C10 C12 D10 D12 A13 B13 C14 D14 MGTTXP1_101 MGTTXP0_101 MGTTXN1_101 MGTTXN0_101 MGTRXN0_101 MGTRXN1_101 MGTRXP0_101 MGTRXP1_101 MGTREFCLK0N_101 MGTREFCLK0P_101 MGTREFCLK1N_101 MGTREFCLK1P_101 MGTAVCCPLL0_101 MGTAVCCPLL1_101 B14 C15 MGTAVCC_101 C13 MGTAVTTRX_101 MGTAVTTTX_101 D11 A10 MGTRREF_101 MGTAVTTRCAL_101 E12 E14 XC6SLX100T: GTPA1_DUAL_X0Y0 XC6SLX150T: GTPA1_DUAL_X0Y0 AJ11 AJ9 AK11 AK9 AH10 AH12 AG10 AG12 AK13 AJ13 AH14 AG14 MGTTXP1_245 MGTTXP0_245 MGTTXN1_245 MGTTXN0_245 MGTRXN0_245 MGTRXN1_245 MGTRXP0_245 MGTRXP1_245 MGTREFCLK0N_245 MGTREFCLK0P_245 MGTREFCLK1N_245 MGTREFCLK1P_245 MGTAVCCPLL0_245 MGTAVCCPLL1_245 AJ14 AH15 MGTAVCC_245 AH13 MGTAVTTRX_245 MGTAVTTTX_245 AG11 AK10 MGTRREF_245 MGTAVTTRCAL_245 AF12 AF14イ ン プ リ メ ン テーシ ョ ン

図 1-12 に、FF900 パ ッ ケージで使用可能なすべてのデバ イ ス におけ る 、 ダ イ 右側部分の GTP ト ラ ン シーバの位置情報を示 し ます。

X-Ref Target - Figure 1-12

図 1-12 : FF900 パ ッ ケージの配置図 (2) B23 B21 A23 A21 C20 C22 D20 D22 C18 D18 A19 B19 MGTTXP1_123 MGTTXP0_123 MGTTXN1_123 MGTTXN0_123 MGTRXN0_123 MGTRXN1_123 MGTRXP0_123 MGTRXP1_123 MGTREFCLK0N_123 MGTREFCLK0P_123 MGTREFCLK1N_123 MGTREFCLK1P_123 UG386_c1_12_100909 XC6SLX100T: GTPA1_DUAL_X1Y1 XC6SLX150T: GTPA1_DUAL_X1Y1 C17 B18 MGTAVCCPLL0_123 MGTAVCCPLL1_123 C19 MGTAVCC_123 D21 A22 MGTAVTTRX_123 MGTAVTTTX_123 XC6SLX100T: GTPA1_DUAL_X1Y0 XC6SLX150T: GTPA1_DUAL_X1Y0 AJ23 AJ21 AK23 AK21 AH20 AH22 AG20 AG22 AH18 AG18 AK19 AJ19 MGTTXP1_267 MGTTXP0_267 MGTTXN1_267 MGTTXN0_267 MGTRXN0_267 MGTRXN1_267 MGTRXP0_267 MGTRXP1_267 MGTREFCLK0N_267 MGTREFCLK0P_267 MGTREFCLK1N_267 MGTREFCLK1P_267 AH17 AJ18 MGTAVCCPLL0_267 MGTAVCCPLL1_267 AH19 MGTAVCC_267 AG21 AK22 MGTAVTTRX_267 MGTAVTTTX_267

Top

Bottom

第

2

章

ト ラ ン シーバの共有機能

リ フ ァ レ ン ス

ク ロ ッ ク入力の構造

機能の説明

図 2-1 に、 リ フ ァ レ ン ス ク ロ ッ ク 入力の構造を示 し ます。 入力は、3/4MGTAVCC に対 し て両側に 50Ω の内部抵抗で終端処理 さ れてい ます。 リ フ ァ レ ン ス ク ロ ッ ク は、IBUFDS プ リ ミ テ ィ ブ を使用 し て ソ フ ト ウ ェ アに イ ン ス タ ン シエー ト さ れます。 リ フ ァ レ ン ス ク ロ ッ ク を制御す る ポー ト お よ び 属性は、 各 IBUFDS へ接続 さ れずに GTPA1_DUAL に割 り 当て ら れます。ポー ト および属性

表 2-1 に、IBUFDS の リ フ ァ レ ン ス ク ロ ッ ク 入力ポー ト を示 し ます。X-Ref Target - Figure 2-1

図 2-1 : ク ロ ッ ク 入力の構造 + – UG386_c2_14_110509 Nom 50Ω CLKRCV_TRST_0/1 = MGTREFCLKP0/1 MGTREFCLKN0/1 REFCLKPWRDNB0/1 MGTAVCC = 1.2V CLKINDC_B_0/1 3/4 MGTAVCC Nom 50Ω 表 2-1 : リ フ ァ レ ン スク ロ ッ ク入力のポー ト (IBUFDS) ポー ト 方向 ク ロ ッ ク ド メ イ ン 説明 I IB 入力 (パ ッ ド) N/A こ れ ら は、MGTREFCLKP0/MGTREFCLKN0 お よ び MGTREFCLKP1/MGTREFCLKN1 へマ ッ ピ ン グ さ れ る リ フ ァ レ ン ス ク ロ ッ ク 入力ポー ト です。 O 出力 N/A こ の出力は、GTPA1_DUAL プ リ ミ テ ィ ブの CLK00、 CLK01、CLK10、 お よ び CLK11 信号を駆動 し ます。 詳細は、40 ページの 「 リ フ ァ レ ン ス ク ロ ッ ク の選択お よ び分配」 を参照 し て く だ さ い。

表 2-2 に、GTPA1_DUAL の リ フ ァ レ ン ス ク ロ ッ ク 入力ポー ト を示 し ます。 表 2-3 に、RX アナ ロ グ フ ロ ン ト エン ド の属性を示 し ます。

使用モー ド

:

リ フ ァ レ ン ス

ク ロ ッ ク の終端処理

リ フ ァ レ ン ス ク ロ ッ ク 入力は外部で AC カ ッ プ リ ン グ さ れます。 こ れを行 う 際に必要な ピ ンお よ び 属性の設定を表 2-4 に示 し ます。リ フ ァ レ ン ス

ク ロ ッ クの選択および分配

機能の説明

SerDes ト ラ ン シーバには、複数の リ フ ァ レ ン ス ク ロ ッ ク 入力があ り ます。 ク ロ ッ ク 入力の種類お よ び数は、以前の RocketIO™ ト ラ ン シーバ と は多少異な り ます。Spartan®-6 FPGA GTP ト ラ ン シーバ リ フ ァ レ ン ス ク ロ ッ ク は、 専用の ク ロ ッ ク 配線お よ びマルチプ レ ク サ リ ソ ース を使用 し て駆動 で き ます。 構造的には、1 つのデ ュ アル (DUAL) 内にGTPA1_DUALプ リ ミ テ ィ ブが 1 つあ り 、こ のプ リ ミ テ ィ ブには 2 つの ト ラ ン シーバが含まれます (TX と RX が 2 対ずつ)。各 GTPA1_DUAL タ イ ルには 2 表 2-2 : リ フ ァ レ ン スク ロ ッ ク入力のポー ト (GTPA1_DUAL) ポー ト 方向 ク ロ ッ ク ド メ イ ン 説明 REFCLKPWRDNB0 REFCLKPWRDNB1 入力 (パッ ド) 非同期 ク ロ ッ クバ ッ フ ァ 用の非同期パ ワ ー ダ ウ ン信号です (ア ク テ ィ ブ Low)。 表 2-3 : リ フ ァ レ ン スク ロ ッ ク入力の属性 (GTPA1_DUAL) 属性 種類 説明 CLKRCV_TRST_0 CLKRCV_TRST_1 ブール関数 制限 さ れてい ます。 こ の属性は、50Ω終端抵抗を有 効に し ます。 常に TRUE に設定 し て く だ さ い。 CLKINDC_B_0 CLKINDC_B_1 ブール関数 制限 さ れてい ます。 こ の属性は、50Ωの終端用の終 端電圧を有効に し ます。 常に TRUE に設定 し て く だ さ い。 表 2-4 : ポー ト および属性の設定 入力の種類 設定 ポー ト REFCLKPWRDNB0 = 1 REFCLKPWRDNB1 = 1 属性 CLKINDC_B_0 = 1 CLKINDC_B_1 = 1 CLKRCV_TRST_0 = 1 CLKRCV_TRST_1 = 1

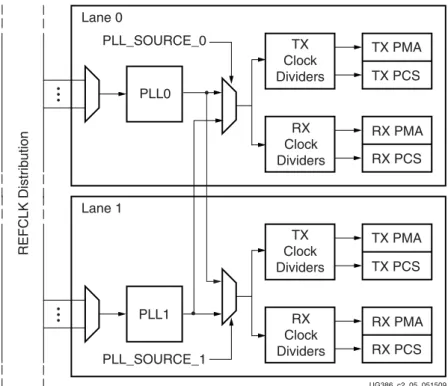

リ フ ァ レ ン ス ク ロ ッ クの選択および分配 リ フ ァ レ ン ス ク ロ ッ クセ レ ク シ ョ ンの特徴は次の と お り です。 • 隣接す る GTPA1_DUAL タ イ ルへの西方向 ク ロ ッ ク お よ び東方向 ク ロ ッ ク 配線 • 各 GTP PLL で利用可能な ク ロ ッ ク 入力 • PLL の リ フ ァ レ ン ス ク ロ ッ ク を静的ま たは動的に選択可能 図 2-2 に、2 つの GTP ト ラ ンシーバ、2 つの専用 リ フ ァ レ ン ス スク ロ ッ ク ピ ンペア、 および東西方 向の リ フ ァ レ ン ス ク ロ ッ ク 配線があ る GTPA1_DUAL のアーキテ ク チ ャ を示し ます。GTPA1_DUAL タ イル内にあ る各 PLL では、 リ フ ァ レ ン ス ク ロ ッ ク MUX の コ ン フ ィ ギ ュ レーシ ョ ンに基づいて、8 個の ク ロ ッ ク ソ ース を リ フ ァ レ ン ス ク ロ ッ ク ソ ース と し て使用で き ます。 • 外部ピ ンか ら の 2 つの リ フ ァ レ ン ス ク ロ ッ ク ピ ンペア • PLL0 用の CLK[0/1]0 • PLL1 用の CLK[0/1]1 • 東西か ら の 2 つの リ フ ァ レ ン ス ク ロ ッ ク ピ ンペア • PLL0 用の CLKINEAST0 お よ び CLKINWEST0 • PLL1 用の CLKINEAST1 お よ び CLKINWEST1 隣接す る GTPA1_DUAL タ イ ルがない場合、対応す る ポー ト は未接続 と な り フ ロ ーテ ィ ン グ状 態にな り ます。 • FPGA ロ ジ ッ ク の PLL か ら の 2 つの リ フ ァ レ ン ス ク ロ ッ ク ピ ンペア • PLL0 用の PLLCLK[0/1]0 • PLL1 用の PLLCLK[0/1]1 • FPGA ロ ジ ッ ク で生成 さ れ る 2 つの リ フ ァ レ ン ス ク ロ ッ ク 信号 • PLL0 用の GCLK[0/1]0 • PLL1 用の GCLK[0/1]1

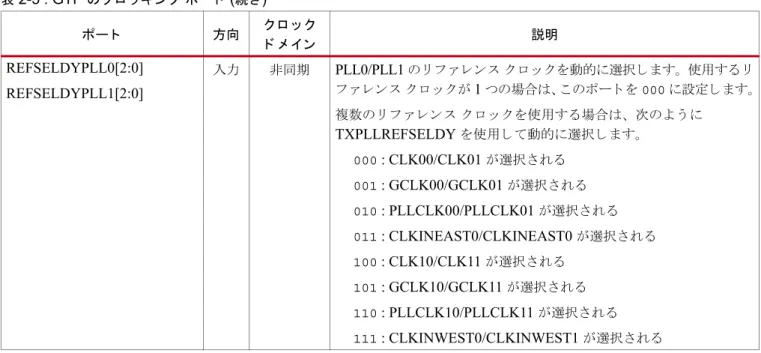

図 2-3 に、 リ フ ァ レ ン ス ク ロ ッ ク マルチプ レ ク サの構造図を示 し 、 各 PLL へ異な る ク ロ ッ ク ソ ー ス が提供 さ れ る 方法を示 し ます。複数の リ フ ァ レ ン ス ク ロ ッ ク がマルチプ レ ク サへ接続 さ れ る 場合 は、REFSELDYPLL0 お よ び REFSELDYPLL1 ポー ト が必要にな り ます。 リ フ ァ レ ン ス ク ロ ッ クマルチプレ ク サに リ フ ァ レ ン スク ロ ッ ク ソース を 1 個のみ接続する場合は、各 PLL に 1 つの リ フ ァ レ ン ス ク ロ ッ ク が定義されます。 こ の場合、PLL0 の リ フ ァ レ ン ス ク ロ ッ ク ソースは CLK00 ポー ト へ接続、PLL1 の リ フ ァ レ ン ス ク ロ ッ ク ソースは CLK01 ポー ト へ接続で き ます。 マルチプレ ク サの制御ポー ト (REFSELDYPLL0[2:0] および REFSELDYPLL1[2:0] ) を000を設定する と 、 ザ イ リ ン ク スの ソ フ ト ウ ェ アツールが複雑なマ ルチプレ ク サ構造を処理し て、 各 GTP ト ラ ンシーバの PLL に 1 つの リ フ ァ レ ン ス ク ロ ッ ク を使用す る よ う に配線し ます。ほ と んどの場合、GTPA1_DUAL タ イル内にあ る 2 つの ト ラ ンシーバは同じ外部 ク ロ ッ ク ソース を共有し、各 PLL には リ フ ァ レ ン ス ク ロ ッ ク が 1 つのみ存在し ます。詳細は、46 ペー ジの 「単一の外部 リ フ ァ レ ン ス ク ロ ッ ク を使用す る 場合」 を参照し て く だ さ い。

X-Ref Target - Figure 2-2

図 2-2 : GTP ト ラ ン シーバの リ フ ァ レ ン ス ク ロ ッ キング概要図 UG386_c2_12_103009 PLL_SOURCE_0 Controlled by Software REFCLKPLL1 REFCLKPLL0 PLL_SOURCE_1 CLK10/11 PLL0 0 2 3 4 5 6 7 1 MGTREFCLK1P MGTREFCLK1N IBUFDS PLL1 CLK00/01 MGTREFCLK0P MGTREFCLK0N IBUFDS 0 2 3 4 5 6 7 1 PLL_SOURCE_0 Controlled by Software REFCLKPLL1 REFCLKPLL0 CLKINEAST0/1 CLKINWEST0/1 PLL_SOURCE_1 CLK10/11 PLL0 0 2 3 4 5 6 7 1 MGTREFCLK1P MGTREFCLK1N IBUFDS PLL1 CLK00/01 MGTREFCLK0P MGTREFCLK0N IBUFDS 0 2 3 4 5 6 7 1

リ フ ァ レ ン ス ク ロ ッ クの選択および分配 リ フ ァ レ ン ス ク ロ ッ クマルチプ レ ク サに複数の リ フ ァ レ ン ス ク ロ ッ ク ソ ース が接続 さ れてい る 場 合は、 各 PLL に複数の リ フ ァ レ ン ス ク ロ ッ ク が定義 さ れます。 こ の場合、 リ フ ァ レ ン ス ク ロ ッ ク を動的に選択 し て切 り 替え る 必要があ る ため、 リ フ ァ レ ン ス ク ロ ッ ク を各 リ フ ァ レ ン ス ク ロ ッ ク マルチプ レ ク サ構造へ接続 し て、 必要に応 じ て REFSELDYPLL[2:0] の設定を変更す る 必要があ り ます。 1 つの GTPA1_DUAL タ イ ルを含む GTP ト ラ ン シーバでは、2 つの専用 リ フ ァ レ ン ス ク ロ ッ ク ピ ン を共有 し ます。 ユーザーデザ イ ンでは、 IBUFDSプ リ ミ テ ィ ブ を イ ン ス タ ン シエー ト し て、 こ れ ら の リ フ ァ レ ン ス ク ロ ッ ク へア ク セ ス し ます。 こ れ ら の ク ロ ッ ク は、GTPA1_DUAL タ イ ル内の GTP ト ラ ン シーバで使用で き ます (MGTREFCLK0P/N が CLK00 を駆動 し 、MGTREFCLK1P/N が CLK01 を駆動す る)。 ま た、GTPA1_DUAL タ イ ルが隣接配置 さ れてい る 場合は、 専用の リ フ ァ レ ン ス ク ロ ッ ク 配線を使用 し て東西方向の GTP ト ラ ン シーバへ こ れ ら の ク ロ ッ ク を配線す る こ と も 可能です。 各 GTP ト ラ ン シーバは、CLKINEAST0 ポー ト お よ び CLKINEAST1 ポー ト を ソ ース と す る 西側の GTPA1_DUAL タ イ ルか ら リ フ ァ レ ン ス ク ロ ッ ク を選択で き ます。 東側の GTPA1_DUAL タ イ ル は、CLKINWEST0 ポー ト お よ び CLKINWEST1 ポー ト か ら ク ロ ッ ク 供給 さ れます。 ま た、FPGA PLL の出力 ク ロ ッ ク を対応す る PLLCLK ポー ト へ接続す る こ と に よ っ て、 ト ラ ン シーバの専用 リ フ ァ レ ン ス ク ロ ッ ク ソ ース と し て使用で き ます。PLLCLK ポー ト は、 内部テ ス ト のために予約 さ れてい る ポー ト です。

X-Ref Target - Figure 2-3

図 2-3 : GTP ト ラ ン シーバの詳細図 0 1 2 3 4 5 6 7 CLK00 GCLK00 PLLCLK00 CLKINEAST0 CLK10 GCLK10 PLLCLK10 CLKINWEST0 REFSELDYPLL0[2:0] Out UG386_c2_01_103009 PLL0 0 1 2 3 4 5 6 7 CLK01 GCLK01 PLLCLK01 CLKINEAST1 CLK11 GCLK11 PLLCLK11 CLKINWEST1 REFSELDYPLL1[2:0] Out

User Design Default Configuration

PLL1 GTP Transceiver Reference Clock Selection

![図 3-6 : GTPCLKOUT[0] によ る TXUSRCLK および TXUSRCLK2 の駆動 (2 バイ ト TX イ ン タ ー フ ェ イ ス ) UG386_c3_15_100509BUFIO2GTPCLKOUT[0]TXUSRCLK2(1)TXUSRCLK(1)TXDATA (16 or 20 bits)PLLLKDETCLKOUT0TXUSRCLK2Note: 1: F= FTXUSRCLK / 2CLKOUT1LOCKEDRSTCLKINDesign inFPGA](https://thumb-ap.123doks.com/thumbv2/123deta/5818310.540095/78.892.241.818.618.928/によおよびTXUSRCLKバイトTXンターフェイスUG3BUFIOTXUSRCLK=.webp)

![図 3-7 : GTPCLKOUT[0] によ る TXUSRCLK および TXUSRCLK2 の駆動 (4 バイ ト TX イ ン タ ー フ ェ イ ス ) UG386_c3_16_100509BUFIO2GTPCLKOUT[0]TXUSRCLK2(1)TXUSRCLK(1)TXDATA (36 or 40 bits)PLLLKDETCLKOUT0TXUSRCLK2Note: 1: F= FTXUSRCLK /4CLKOUT1LOCKEDRSTCLKINDCM/PLLGTPTran](https://thumb-ap.123doks.com/thumbv2/123deta/5818310.540095/79.892.231.818.241.566/およびTXUSRCLK駆動バイトTXンターフェイスUG3TXUSRCLK=FTXUSRCLK.webp)