DCO

を備えた

オシレータ

59

セクション

59. DCO を備えたオシレータ

特長

本セクションには以下の主要項目を記載しています。 59.1 はじめに ...59-2 59.2 制御レジスタ ...59-4 59.3 動作 : クロック生成とクロック源 ...59-17 59.4 割り込み ...59-32 59.5 省電力モード中の動作 ...59-32 59.6 各種リセットの影響 ...59-32 59.7 クロック供給に関するガイドライン ...59-33 59.8 関連アプリケーション ノート ...59-36 59.9 改訂履歴 ...59-3759.1

はじめに

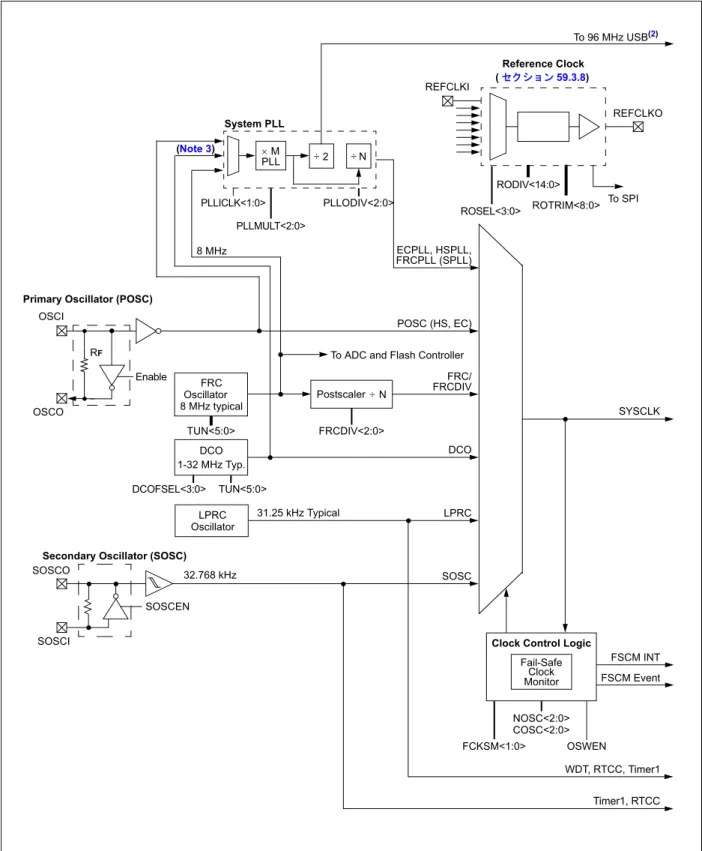

PIC32 のオシレータ システムは以下のモジュールと機能を備えています。 • クロック源として選択可能な 5 つの外部および内部オシレータ オプション • 逓倍比 / 出力分周比を選択可能な内蔵位相ロックループ (PLL) ( 内部および外部オシレータ 信号源の動作周波数を逓倍可能) • 高速起動と低消費電流を兼ね備えた内部デジタル制御オシレータ (DCO) • ソフトウェア制御による各種クロック源の切り換え • 柔軟な参照クロック ジェネレータ (REFO) • クロック障害を検出し、アプリケーションを安全に回復またはシャットダウンするフェイ ルセーフ クロック監視機能 (FSCM) 図 59-1に、オシレータ システムのブロック図を示します。 Note: ファミリ リファレンス マニュアルの本セクションは、デバイス データシートの補 足を目的としています。本セクションの内容はPIC32 ファミリの一部のデバイス には対応していません。 本書の内容がお使いのデバイスに対応しているかどうかは、最新デバイス データ シートの「オシレータ コンフィグレーション」の冒頭に記載している注意書きで ご確認ください。 デバイス データシートとファミリ リファレンス マニュアルの各セクションは、 Microchip 社のウェブサイト (http://www.microchip.com) からダウンロードできます。DCO

を備えた

オシレータ

59

図 59-1: PIC32 ファミリ オシレータ システムのブロック図(1)

Clock Control Logic

Fail-Safe Clock Monitor FSCM INT FSCM Event COSC<2:0> NOSC<2:0> OSWEN FCKSM<1:0>

Secondary Oscillator (SOSC)

SOSCEN SOSCO SOSCI POSC (HS, EC) FRCDIV<2:0> 8 MHz typical 31.25 kHz Typical FRC Oscillator LPRC Oscillator SOSC LPRC FRCDIV TUN<5:0> Postscaler PLLICLK<1:0> PLLODIV<2:0> 32.768 kHz PLLMULT<2:0> SYSCLK N DCO 1-32 MHz Typ. DCO REFCLKO To SPI Reference Clock RODIV<14:0> ROTRIM<8:0> N FRCPLL (SPLL) REFCLKI ROSEL<3:0> Enable OSCO OSCI RF

Primary Oscillator (POSC)

PLL

To ADC and Flash Controller

System PLL DCOFSEL<3:0> TUN<5:0> (セクション59.3.8) FRC/ 8 MHz ECPLL, HSPLL, (Note 3) M 2 To 96 MHz USB(2)

59.2

制御レジスタ

オシレータ モジュールは以下の特殊機能レジスタ (SFR) を備えています。 • OSCCON: オシレータ制御レジスタ(1) このレジスタはクロック切り換えを制御し、使用中のクロック源、PLL ロック、クロック 障害条件を監視するためのステータス情報を提供します。 • SPLLCON: システム PLL 制御レジスタ(1,2) このレジスタはシステムクロックPLL を制御するために使います。このレジスタを使うと、 入力周波数よりも高いシステム周波数を生成できます。 • REFOCON: 参照オシレータ制御レジスタ このレジスタは参照クロック ジェネレータを制御します。 • REFOTRIM: 参照オシレータ調整レジスタ(1,2,3) このレジスタは参照クロック ジェネレータを微調整します。 • CLKSTAT: クロック源ステータス レジスタ このレジスタは全てのオシレータに関するステータス情報を提供します。 • OSCTUN: FRC 調整レジスタ(1) このレジスタはソフトウェアによる内部 FRC オシレータ周波数の調整に使います。FRC オシレータ周波数を±12% のレンジで調整できます。 • DCOCON: デジタル制御オシレータ制御レジスタ このレジスタはDCO の動作と周波数の選択を制御します。 Note: オシレータ モジュール関連の設定には、上記のレジスタに加えてデバイス コン フィグレーション ワードレジスタも使います。これらのレジスタの詳細について は、各デバイス データシートの「その他の特殊機能」を参照してください。セクション

59. DCO

を備えたオシレータ

表 59-1の全オシレータレジスタには対応するクリア/ セット / 反転レジスタがあり、接尾辞はそれぞれ -CLR/-SET/-INV です。アド レスはそれぞれ0x4/0x8/0xC バイトオフセットしています。対応するレジスタを使って、そのメインレジスタを編集します。これらの レジスタの任意のビットに「1」を書き込むと、対応するレジスタの対応するビットがそれぞれクリア、セット、反転されます。これら のレジスタからの読み出しは無視されます。 表 59-1: オシレータ関連SFR の一覧 レジスタ名 ビットレンジ Bit 31/15 Bit 30/14 Bit 29/13 Bit 28/12 Bit 27/11 Bit 26/10 Bit 25/9 Bit 24/8 Bit 23/7 Bit 22/6 Bit 21/5 Bit 20/4 Bit 19/3 Bit 18/2 Bit 17/1 Bit 16/0 OSCCON 31:16 — — — — — FRCDIV<2:0> — — SLP2SPD — — — — —

15:0 — COSC<2:0> — NOSC<2:0> CLKLOCK r r SLPEN CF — SOSCEN OSWEN SPLLCON 31:16 — — — — — PLLODIV<2:0> — — — — — PLLMULT<2:0>

15:0 — — — — — — — — PLLICLK<1:0> — — — — — — REFOCON 31:16 — RODIV<14:0>

15:0 ON — SIDL OE RSLP — DIVSWEN ACTIVE — — — — ROSEL<3:0>

REFOTRIM 31:16 ROTRIM<8:0> — — — — — — — 15:0 — — — — — — — — — — — — — — — — CLKSTAT 31:16 — — — — — — — — — — — — — — — —

15:0 — — — — — — — — SPLLRDY — LPRCRDY SOSCRDY DCORDY POSCRDY DIVSPLLRDY FRCRDY OSCTUN 31:16 — — — — — — — — — — — — — — — —

15:0 ON r SIDL SRC LOCK POL ORNG ORNGPOL — — TUN<5:0>

DCOCON 31:16 — — ON — DCOFSEL<3:0> — — — — — — — — 15:0 — — SIDL — — — — — — — TUN<5:0>

レジスタ 59-1: OSCCON: オシレータ制御レジスタ(1) ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

31:24 U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-1 — — — — — FRCDIV<2:0>

23:16 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 — — SLP2SPD(4) — — — — — 15:8 U-0 R-y R-y R-y U-0 R/W-y R/W-y R/W-y

— COSC<2:0>(2) — NOSC<2:0>(2)

7:0 R/W-0 r-0 r-0 R/W-0 R/W-0, HS U-0 R/W-y R/W-y CLKLOCK — — SLPEN CF(3) — SOSCEN OSWEN

Legend: HS = ハードウェア セット 可能ビット y = POR 時にコンフィグレーション ビットの 値に設定 R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 「1」 = ビットはセット 「0」 = ビットはクリア r = 予約済みビット bit 31-27 未実装 : 「0」として読み出し bit 26-24 FRCDIV<2:0>: 内部高速 RC (FRC) オシレータ クロック分周比ビット 111 = 256 分周 110 = 64 分周 101 = 32 分周 100 = 16 分周 011 = 8 分周 010 = 4 分周 001 = 2 分周 000 = FRC を 1 分周する (POR 時の既定値 ) bit 23-22 未実装 : 「0」として読み出し bit 21 SLP2SPD: スリープからの 2 段階復帰ビット(4) 1 = デバイスは復帰し、NOSCx ビットによって選択されたクロック源の動作準備が完了するまで FRC ク ロックを使って動作する 0 = デバイスは復帰するが、NOSCx ビットによって選択されたクロック源の動作準備が完了するまで動作 しない bit 20-15 未実装 : 「0」として読み出し bit 14-12 COSC<2:0>: 切り換え前オシレータ選択ビット(2) 111 = 予約済み ( ポストスケーラ併用 FRC オシレータを選択 (FRCDIV)) 110 = 予約済み ( ポストスケーラ併用 FRC オシレータを選択 (FRCDIV)) 101 = 低消費電力 RC オシレータ (LPRC) 100 = セカンダリ オシレータ (SOSC) 011 = デジタル制御オシレータ (DCO) 010 = プライマリ オシレータ (POSC) (HS および EC モード ) 001 = システム PLL (SPLL) (ECPLL、HSPLL、FRCPLL モード ) 000 = ポストスケーラ併用 FRC オシレータ (FRCDIV) bit 11 未実装: 「0」として読み出し Note 1: このレジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。詳細はセクション 59.3.6.2「オシレータ切り換えシーケンス」を参照してください。 2: 初期値はデバイスリセットに関するFNOSC<2:0> コンフィグレーション ビットによって決まります。 示した定義は代表値であり、デバイスによって異なります。デバイス固有の詳細は各デバイス データ シート内の「オシレータ コンフィグレーション」を参照してください。 3: フェイルセーフ クロックモニタ有効時、このビットに「1」と書き込むと FSCM クロックも切り換わり ます。

DCO

を備えた

オシレータ

59

bit 10-8 NOSC<2:0>: 切り換え後オシレータ選択ビット(2) 111 = 予約済み ( ポストスケーラ併用 FRC オシレータを選択 (FRCDIV)) 110 = 予約済み ( ポストスケーラ併用 FRC オシレータを選択 (FRCDIV)) 101 = 低消費電力 RC オシレータ (LPRC) 100 = セカンダリ オシレータ (SOSC) 011 = デジタル制御オシレータ (DCO) 010 = プライマリ オシレータ (POSC) (HS および EC モード ) 001 = システム PLL (SPLL) (ECPLL、HSPLL、FRCPLL モード ) 000 = ポストスケーラ併用 FRC オシレータ (FRCDIV) bit 7 CLKLOCK: クロック選択ロック イネーブルビット 1 = クロックと PLL の選択がロックされる ( デバイスリセットによってのみクリア可能 ) 0 = クロックと PLL は変更可能 このビットがセットされている場合、NOSC<2:0> および OSWEN ビットへの書き込みは禁止されます。 bit 6-5 予約済み: 「0」として読み出し bit 4 SLPEN: スリープモード イネーブルビット 1 = WAIT 命令の実行によってデバイスはスリープに移行する 0 = WAIT 命令の実行によってデバイスはアイドルに移行する bit 3 CF: クロック障害検出ビット(3) 1 = FSCM がクロック障害を検出した 0 = クロック障害は検出されていない bit 2 未実装: 「0」として読み出しbit 1 SOSCEN: セカンダリ オシレータ (SOSC) イネーブルビット

1 = SOSC を有効にする 0 = SOSC を無効にする POR 時の既定値は FSOSCEN コンフィグレーション ビットによって指定します。 bit 0 OSWEN: オシレータ切り換えイネーブルビット 1 = NOSC<2:0> ビットが指定するオシレータへの切り換えを開始する 0 = オシレータ切り換えは完了した レジスタ 59-1: OSCCON: オシレータ制御レジスタ(1) ( 続き ) Note 1: このレジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。詳細はセクション 59.3.6.2「オシレータ切り換えシーケンス」を参照してください。 2: 初期値はデバイスリセットに関するFNOSC<2:0> コンフィグレーション ビットによって決まります。 示した定義は代表値であり、デバイスによって異なります。デバイス固有の詳細は各デバイス データ シート内の「オシレータ コンフィグレーション」を参照してください。 3: フェイルセーフ クロックモニタ有効時、このビットに「1」と書き込むと FSCM クロックも切り換わり ます。 4: この機能は一部のデバイスでのみ利用できます。詳細は各デバイスのデータシートを参照してください。

レジスタ 59-2: SPLLCON: システム PLL 制御レジスタ(1,2) ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

31:24 U-0 U-0 U-0 U-0 U-0 R/W-0

(3) R/W-0(3) R/W-0(3)

— — — — — PLLODIV<2:0> 23:16 U-0 U-0 U-0 U-0 U-0 R/W-0

(3) R/W-0(3) R/W-0(3)

— — — — — PLLMULT<2:0> 15:8 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

7:0 R/W-y R/W-0 U-0 U-0 U-0 U-0 U-0 U-0 PLLICLK<1:0>(4,5) — — — — — — Legend: y = POR 時にコンフィグレーション ビットの値に設定 R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 「1」 = ビットはセット 「0」 = ビットはクリア x = ビットは未知 bit 31-27 未実装 : 「0」として読み出し bit 26-24 PLLODIV<2:0>: SPLL 出力クロック分周比ビット(3) 111 = 256 分周 110 = 64 分周 101 = 32 分周 100 = 16 分周 011 = 8 分周 010 = 4 分周 001 = 2 分周 000 = 1 分周 bit 23-19 未実装 : 「0」として読み出し bit 18-16 PLLMULT<2:0>: システムクロック PLL 逓倍比ビット(3) 111 = 予約済み 110 = x24 101 = x12 100 = x8 011 = x6 010 = x4 001 = x3 000 = x2 bit 15-8 未実装: 「0」として読み出し Note 1: このレジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。詳細はセクション 59.3.6.2「オシレータ切り換えシーケンス」を参照してください。 2: SPLL をクロック源として選択 (COSC<2:0> = 001) している場合、このレジスタへの書き込みは禁止さ れます。 3: PLLODIVx と PLLMULTx のリセット値は代表値であり、デバイスによって異なります。詳細は各デバイ ス データシートを参照してください。 4: POR 時の既定値は FPLLICLK コンフィグレーション ビットによって指定します。詳細は各デバイス デー タシート内の「その他の特殊機能」を参照してください。デバイス コンフィグレーション ビットを使っ てPLL として選択できるのは POSC と FRC のみです。 5: このフィールドの幅はデバイスによって異なります。詳細はデバイスのデータシートを参照してください。

DCO

を備えた

オシレータ

59

bit 7-6 PLLICLK<1:0>: SPLL 入力クロック源ビット(4,5) ビット6 実装時のビット値 : 11 = 予約済み 10 = FRC 01 = DCO 00 = POSC ビット6 未実装時のビット値 : 1 = FRC 0 = POSC bit 5-0 未実装: 「0」として読み出し レジスタ 59-2: SPLLCON: システム PLL 制御レジスタ(1,2) ( 続き ) Note 1: このレジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。詳細はセクション 59.3.6.2「オシレータ切り換えシーケンス」を参照してください。 2: SPLL をクロック源として選択 (COSC<2:0> = 001) している場合、このレジスタへの書き込みは禁止さ れます。 3: PLLODIVx と PLLMULTx のリセット値は代表値であり、デバイスによって異なります。詳細は各デバイ ス データシートを参照してください。 4: POR 時の既定値は FPLLICLK コンフィグレーション ビットによって指定します。詳細は各デバイス デー タシート内の「その他の特殊機能」を参照してください。デバイス コンフィグレーション ビットを使っ てPLL として選択できるのは POSC と FRC のみです。 5: このフィールドの幅はデバイスによって異なります。詳細はデバイスのデータシートを参照してください。レジスタ 59-3: REFOCON: 参照オシレータ制御レジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0 31:24 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 — RODIV<14:8>(1,3) 23:16 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 RODIV<7:0>(1,3) 15:8 R/W-0 U-0 R/W-0 R/W-0 R/W-0 U-0 R/W-0, HC R-0, HS, HC ON(4) — SIDL OE RSLP(2) — DIVSWEN ACTIVE 7:0 U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0

— — — — ROSEL<3:0>(1,3) Legend: HC = ハードウェア クリア 可能ビット HS = ハードウェア セット可能ビット R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 「1」 = ビットはセット 「0」 = ビットはクリア x = ビットは未知 bit 31 未実装: 「0」として読み出し bit 30-16 RODIV<14:0> 参照クロック分周比ビット(1,3) 出力クロック周波数は、源クロック周波数/2 × [RODIV<14:0> + (ROTRIM<8:0> 512)] です。 この値は以下のように参照クロック分周比を選択します。詳細は式 59-2を参照してください。 111111111111111 = 出力クロック周波数 = 源クロック周波数 /65,534 111111111111110 = 出力クロック周波数 = 源クロック周波数 /65,532 • • • 000000000000010 = 出力クロック周波数 = 源クロック周波数 /4 000000000000001 = 出力クロック周波数 = 源クロック周波数 /2 000000000000000 = 出力クロック周波数 = 源クロック周波数 ( 分周しない ) bit 15 ON: 出力イネーブルビット(4) 1 = 参照オシレータ モジュールを有効にする 0 = 参照オシレータ モジュールを無効にする bit 14 未実装: 「0」として読み出し bit 13 SIDL: アイドル中周辺モジュール停止ビット 1 = デバイスがアイドルに移行するとモジュールは動作を停止する 0 = アイドル中もモジュールは動作を継続する bit 12 OE: 参照クロック出力イネーブルビット 1 = REFCLKO ピンで参照クロックを出力する 0 = REFCLKO ピンで参照クロックを出力しない bit 11 RSLP: スリープ中参照オシレータ モジュール動作ビット(2) 1 = スリープ中も参照オシレータ モジュール出力は動作を継続する 0 = スリープ中に参照オシレータ出力は停止する bit 10 未実装: 「0」として読み出し

Note 1: ACTIVE が 1 の時に ROSEL<3:0> と RODIV<14:0> に書き込まないでください。予測できない結果となる

可能性があります。

2: ROSEL<3:0> が 0000 または 0001 の場合、このビットは無視されます。

3: ON が 1 の時にこれらのビットに書き込んだ場合、その効果は DIVSWEN ビットが 1 にセットされるまで 反映されません。

DCO

を備えた

オシレータ

59

bit 9 DIVSWEN: 分周比切り換えイネーブルビット 1 = 分周比切り換えを実行中 0 = 分周比切り換えは完了した bit 8 ACTIVE: 参照クロック要求ステータスビット 1 = 参照クロック要求はアクティブ 0 = 参照クロック要求は非アクティブ bit 7-4 未実装: 「0」として読み出し bit 3-0 ROSEL<3:0>: 参照クロック源選択ビット(1,3) 1111 = 予約済み ( 使用禁止 ) • • • 1001 = 予約済み ( 使用禁止 ) 1000 = REFCLKI ピン 0111 = システム PLL 0110 = DCO 0101 = SOSC 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = 予約済み 0000 = SYSCLK レジスタ 59-3: REFOCON: 参照オシレータ制御レジスタ ( 続き )Note 1: ACTIVE が 1 の時に ROSEL<3:0> と RODIV<14:0> に書き込まないでください。予測できない結果となる

可能性があります。

2: ROSEL<3:0> が 0000 または 0001 の場合、このビットは無視されます。

3: ON が 1 の時にこれらのビットに書き込んだ場合、その効果は DIVSWEN ビットが 1 にセットされるまで 反映されません。

レジスタ 59-4: REFOTRIM: 参照オシレータ調整レジスタ(1,2,3) ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0 31:24 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ROTRIM<8:1>

23:16 R/W-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 ROTRIM0 — — — — — — — 15:8 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

7:0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — — Legend: R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 「1」 = ビットはセット 「0」 = ビットはクリア x = ビットは未知 bit 31-23 ROTRIM<8:0>: 参照オシレータ調整ビット 出力クロック周波数は、源クロック周波数/2 × [RODIV<14:0> + (ROTRIM<8:0> 512)] です。 この値は以下のように参照クロック分周比を選択します。詳細は式 59-2を参照してください。 111111111 = RODIVx 値に分周比 511/512 を加算する 111111110 = RODIVx 値に分周比 510/512 を加算する • • • 100000000 = RODIVx 値に分周比 256/512 を加算する • • • 000000010 = RODIVx 値に分周比 2/512 を加算する 000000001 = RODIVx 値に分周比 1/512 を加算する 000000000 = RODIVx 値に分周比 0/512 を加算する bit 22-0 未実装: 「0」として読み出し

Note 1: ON ビット (REFOCON<15>) が「1」の時にこのレジスタに書き込んだ場合、その効果は DIVSWEN

ビットが「1」にセットされるまで反映されません。

2: ON ビット (REFOCON<15>) と ACTIVE ビット (REFOCON<8>) の値が一致していない時にこのレジスタ に書き込まないでください。

DCO

を備えた

オシレータ

59

レジスタ 59-5: CLKSTAT: クロック源ステータス レジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/031:24 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

23:16 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

15:8 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

7:0 R-0, HSC R-0 R-0, HSC R-0, HSC R-0, HSC R-0, HSC R-0, HSC R-0, HSC SPLLRDY — LPRCRDY SOSCRDY DCORDY POSCRDY DIVSPLLRDY FRCRDY

Legend: HSC = ハードウェア セット / クリア可能ビット R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 「1」 = ビットはセット 「0」 = ビットはクリア x = ビットは未知 bit 31-8 未実装: 「0」として読み出し bit 7 SPLLRDY: システム PLL( ポストスケーラなし ) クロックレディ ステータスビット 1 = SPLL は安定しており動作準備ができている 0 = SPLL は動作準備ができていない bit 6 未実装: 「0」として読み出し bit 5 LPRCRDY: 低消費電力 RC (LPRC) クロックレディ ステータスビット 1 = LPRC は安定しており動作準備ができている 0 = LPRC は動作準備ができていない

bit 4 SOSCRDY: セカンダリ オシレータ (SOSC) クロックレディ ステータスビット

1 = SOSC は安定しており動作準備ができている 0 = SOSC は動作準備ができていない

bit 3 DCORDY: デジタル制御オシレータ (DCO) クロックレディ ステータスビット

1 = DCO は安定しており動作準備ができている 0 = DCO は動作準備ができていない

bit 2 POSCRDY: プライマリ オシレータ (POSC) クロックレディ ステータスビット

1 = POSC は安定しており動作準備ができている 0 = POSC は動作準備ができていない

bit 1 DIVSPLLRDY: システム PLL( ポストスケーラあり、SPLLDIV) クロックレディ ステータスビット

1 = SPLLDIV は安定しており動作準備ができている 0 = SPLLDIV は動作準備ができていない

bit 0 FRCRDY: 高速 RC オシレータ (FRC) クロックレディ ステータスビット

1 = FRC は安定しており動作準備ができている 0 = FRC は動作準備ができていない

レジスタ 59-6: OSCTUN: FRC 調整レジスタ(1) ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

31:24 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

23:16 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

15:8 R/W-0 r-0 R/W-0 R/W-1 R-0 R/W-0 R-0 R/W-0 ON(3) — SIDL(3) SRC(3) LOCK(3) POL(3) ORNG(3) ORNGPOL(3) 7:0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 — — TUN<5:0>(2,4,5) Legend: r = 予約済みビット R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 「1」 = ビットはセット 「0」 = ビットはクリア x = ビットは未知 bit 31-16 未実装 : 「0」として読み出し bit 15 ON: 自己調整イネーブルビット(3) 1 = FRC 自己調整を有効にする。TUNx ビットはハードウェアによって制御される 0 = FRC 自己調整を無効にする。TUNx ビットは読み書き可能である bit 14 予約済み: デバッガが使用 bit 13 SIDL: アイドル中の FRC 自己調整停止ビット(3) 1 = アイドル中は自己調整を停止する 0 = アイドル中でも自己調整を継続する bit 12 SRC: FRC 自己調整参照クロック源ビット(3) 1 = USB ホストクロックを使って FRC を調整する 0 = 32.768 kHz SOSC クロックを使って FRC を調整する bit 11 LOCK: FRC 自己調整ロック ステータスビット(3) 1 = 現在の FRC 精度は STSRC 参照精度の ±0.2% 以内である 0 = 現在の FRC 精度は STSRC 参照精度の ±0.2% 以内でない可能性がある bit 10 POL: FRC 自己調整ロック割り込み極性ビット(3) 1 = STLOCK が「0」の時に自己調整ロック割り込みが生成される 0 = STLOCK が「1」の時に自己調整ロック割り込みが生成される bit 9 ORNG: FRC 自己調整レンジ外ステータスビット(3) 1 = STSRC 参照クロックエラーが TUN<5:0> のレンジを超えている ( 調整は行われない ) 0 = STSRC 参照クロックは調整可能なレンジ内 ( 調整が行われる ) bit 8 ORNGPOL: FRC 自己調整レンジ外割り込み極性ビット(3) 1 = STOR が「0」の時に自己調整レンジ外割り込みが生成される 0 = STOR が「1」の時に自己調整レンジ外割り込みが生成される bit 7-6 未実装: 「0」として読み出し Note 1: このレジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。詳細はセクション 59.3.6.2「オシレータ切り換えシーケンス」を参照してください。 2: 最小および最大周波数偏差については、各デバイスのデータシートを参照してください。 3: このビットは一部のデバイスにのみ存在します。詳細は各デバイスのデータシートを参照してください。 4: これらのビットはSTEN = 0 の時にのみ書き込み可能です。 5: このフィールドのビット数はデバイスによって異なります。詳細は各デバイスのデータシートを参照して ください。

DCO

を備えた

オシレータ

59

bit 5-0 TUN<5:0>: FRC オシレータ調整ビット(2,4,5) 100000 = 最小周波数 100001 = • • • 111111 = 000000 = 中心周波数 ( オシレータは校正周波数 (8 MHz) で動作する ) 000001 = • • • 011110 = 011111 = 最大周波数 レジスタ 59-6: OSCTUN: FRC 調整レジスタ(1) ( 続き ) Note 1: このレジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。詳細はセクション 59.3.6.2「オシレータ切り換えシーケンス」を参照してください。 2: 最小および最大周波数偏差については、各デバイスのデータシートを参照してください。 3: このビットは一部のデバイスにのみ存在します。詳細は各デバイスのデータシートを参照してください。 4: これらのビットはSTEN = 0 の時にのみ書き込み可能です。 5: このフィールドのビット数はデバイスによって異なります。詳細は各デバイスのデータシートを参照して ください。レジスタ 59-7: DCOCON: デジタル制御オシレータ制御レジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

31:24 U-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-1 — — ON — DCOFSEL<3:0>(3)

23:16 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

15:8 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0

— — SIDL — — — — — 7:0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 — — TUN<5:0>(1,2) Legend: R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 「1」 = ビットはセット 「0」 = ビットはクリア x = ビットは未知 bit 31-30 未実装 : 「0」として読み出し bit 29 ON: 出力イネーブルビット 1 = DCO は有効で動作中である 0 = DCO は無効であるが、コンシューマ モジュールからの要求があれば有効化できる bit 28 未実装: 「0」として読み出し

bit 27-24 DCOFSEL<3:0>: DCO 周波数選択ビット ( 周波数値はデバイスのデータシート参照 )(3)

bit 23-14 未実装 : 「0」として読み出し bit 13 SIDL: DCO アイドル中停止ビット

1 = デバイスがアイドルモードに移行したら動作を停止する 0 = アイドル中も動作を継続する

bit 12-6 未実装: 「0」として読み出し

bit 5-0 TUN<5:0>: DCO 調整ビット(1,2)

100000 = 最小周波数 100001 = • • • 111111 = 000000 = 中心周波数 ( オシレータは校正周波数で動作する ) 000001 = • • • 011110 = 011111 = 最大周波数 Note 1: 最小および最大周波数偏差については、各デバイスのデータシートを参照してください。 2: このフィールドのビット数はデバイスによって異なります。詳細は各デバイスのデータシートを 参照してください。 3: 使用可能な周波数は各デバイスのデータシートを参照してください。

DCO

を備えた

オシレータ

59

59.3

動作 : クロック生成とクロック源

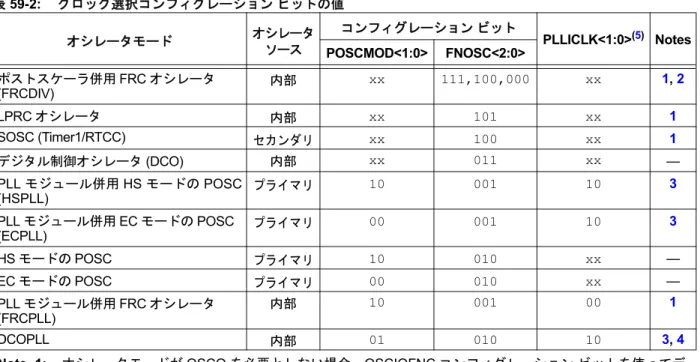

PIC32 ファミリのデバイスは、内部または外部のクロック源を使って生成する複数の内部ク ロックを備えています。これらのクロック源の一部は、PLL とプログラマブルな出力分周器ま たは入力分周器( もしくはその両方 ) を使って、入力周波数をアプリケーションに適した周波 数にスケーリングします。クロック源は、動作中にソフトウェアで切り換える事ができます。 オシレータ制御レジスタはハードウェアによりロックされているため、ソフトウェアでクロック 切り換えを実行する前に、ロック解除シーケンスを実行する必要があります。 1 つのクロック源 ( システムクロック (SYSCLK)) から単一のデバイスクロックを CPU とほとん どの周辺モジュールに提供されます。別のクロック源( 参照クロック ジェネレータ (REFO)) から ユーザ設定可能な出力クロックを外部デバイスを駆動または同期するために提供します。このク ロック源は一部の内蔵周辺モジュールでも使えます。ただし、システムクロック源としては使え ません。 これらのクロックの生成には、以下のいずれかのクロック源を使います。 • OSCI および OSCO ピン上のプライマリ オシレータ (POSC)• SOSCI および SOSCO ピン上のセカンダリ オシレータ (SOSC) • 内部高速 RC (FRC) オシレータ • デジタル制御オシレータ (DCO) • 内部低消費電力 RC (LPRC) オシレータ クロック源ごとに設定可能なオプション(PLL、入力分周比、出力分周比等 ) が異なります。 これらについては後で詳しく説明します。

59.3.1

システムクロック

(SYSCLK) の生成

SYSCLK の生成には、以下の 5 種類あるクロック源のいずれかを使います。 • POSC • SOSC • 内部 FRC オシレータ • DCO • LPRC オシレータ 一部のクロック源では、固有のクロック逓倍または分周( もしくはその両方の ) オプションを 選択できます。ユーザが値を指定しない限り、クロックのスケーリングは適用されません。 SYSCLK のクロック源はデバイス コンフィグレーションで選択しますが、動作中にソフトウェア で変更できます。動作中にクロック源を切り換える事ができるため、状況に応じて低速クロック に切り換える事で、アプリケーションの消費電力を低減できます。 表 59-2に、SYSCLK の生成に使えるオシレータとシステム PLL の組み合わせを示します。 Note: 外部クロックを使う周辺モジュール ( リアルタイム クロック / カレンダ (RTCC)、 Timer1 等 ) のクロック源については、詳細は『PIC32 ファミリ リファレンス マニュ アル、セクション14. タイマ』(DS60001105) と『PIC32 ファミリ リファレンス マ ニュアル、セクション29. リアルタイム クロック / カレンダ (RTCC)』(DS61125) を 参照してください。表 59-2: クロック選択コンフィグレーション ビットの値 オシレータモード オシレータ ソース コンフィグレーション ビット PLLICLK<1:0>(5) Notes POSCMOD<1:0> FNOSC<2:0> ポストスケーラ併用FRC オシレータ (FRCDIV) 内部 xx 111,100,000 xx 1, 2 LPRC オシレータ 内部 xx 101 xx 1 SOSC (Timer1/RTCC) セカンダリ xx 100 xx 1 デジタル制御オシレータ(DCO) 内部 xx 011 xx — PLL モジュール併用 HS モードの POSC (HSPLL) プライマリ 10 001 10 3 PLL モジュール併用 EC モードの POSC (ECPLL) プライマリ 00 001 10 3 HS モードの POSC プライマリ 10 010 xx — EC モードの POSC プライマリ 00 010 xx — PLL モジュール併用 FRC オシレータ (FRCPLL) 内部 10 001 00 1 DCOPLL 内部 01 010 10 3, 4

Note 1: オシレータモードが OSCO を必要としない場合、OSCIOFNC コンフィグレーション ビットを使ってデ

ジタルI/O ピンとして設定できます。 2: FOSC<2:0> = 111 は、未プログラム ( または消去済み ) デバイスの既定値のオシレータモードです。 3: PLL 併用モードを使う場合、PLL への入力周波数がデバイス データシートの「電気的特性」で指定され ているレンジに収まるようにする必要があります。 4: この機能は一部のデバイスでのみ利用できます。詳細は各デバイスのデータシートを参照してください。 5: このフィールドのビット数はデバイスによって異なります。詳細は各デバイスのデータシートを参照して ください。

DCO

を備えた

オシレータ

59

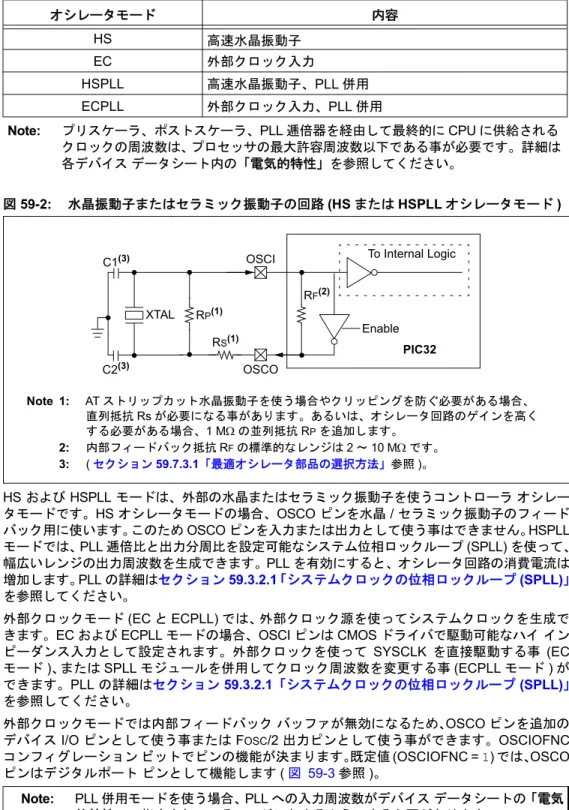

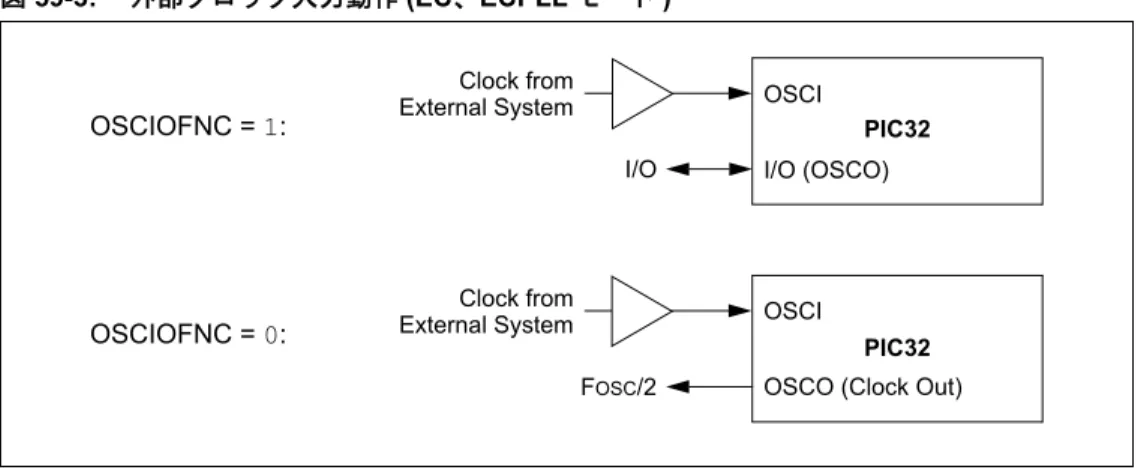

59.3.1.1 プライマリ オシレータ (POSC) プライマリ オシレータ (POSC) は、表 59-3に示す4 種類の動作モードを備えています。本デバ イスファミリでは、POSC を OSCI および OSCO ピンに接続します。POSC は、外部クロック 入力または外部の水晶/ セラミック振動子向けに設定できます。POSCMD<1:0> コンフィグレー ション ビットによってプライマリ オシレータのモードとオシレータピンの機能を設定します。 図 59-2に、POSC の各種コンフィグレーションを示します。 図 59-2: 水晶振動子またはセラミック振動子の回路(HS または HSPLL オシレータモード ) HS および HSPLL モードは、外部の水晶またはセラミック振動子を使うコントローラ オシレー タモードです。HS オシレータモードの場合、OSCO ピンを水晶 / セラミック振動子のフィード バック用に使います。このためOSCO ピンを入力または出力として使う事はできません。HSPLL モードでは、PLL 逓倍比と出力分周比を設定可能なシステム位相ロックループ (SPLL) を使って、 幅広いレンジの出力周波数を生成できます。PLL を有効にすると、オシレータ回路の消費電流は 増加します。PLL の詳細はセクション59.3.2.1「システムクロックの位相ロックループ (SPLL)」 を参照してください。 外部クロックモード(EC と ECPLL) では、外部クロック源を使ってシステムクロックを生成で きます。EC および ECPLL モードの場合、OSCI ピンは CMOS ドライバで駆動可能なハイ イン表 59-3: プライマリ オシレータの動作モード オシレータモード 内容 HS 高速水晶振動子 EC 外部クロック入力 HSPLL 高速水晶振動子、PLL 併用 ECPLL 外部クロック入力、PLL 併用 Note: プリスケーラ、ポストスケーラ、PLL 逓倍器を経由して最終的に CPU に供給される クロックの周波数は、 プロセッサの最大許容周波数以下である事が必要です。詳細は 各デバイス データシート内の「電気的特性」を参照してください。 Note 1: AT ストリップカット水晶振動子を使う場合やクリッピングを防ぐ必要がある場合、 直列抵抗Rs が必要になる事があります。あるいは、オシレータ回路のゲインを高く する必要がある場合、1 M の並列抵抗 RPを追加します。 2: 内部フィードバック抵抗RFの標準的なレンジは2 ~ 10 M です。 3: (セクション59.7.3.1「最適オシレータ部品の選択方法」参照)。 To Internal Logic PIC32 C1(3) C2(3) XTAL Enable OSCO OSCI RF(2) RP(1) RS(1)

図 59-3: 外部クロック入力動作(EC、ECPLL モード ) 59.3.1.1.1 プライマリ オシレータの設定 POSC は以下の手順で設定します。 1. 適切なコンフィグレーション レジスタの FNOSC<2:0> ビットを「010」(PLL を使わな い場合) または「001」(PLL を使う場合 ) に設定して、POSC を既定値オシレータとして 選択する。PLL を使う場合、FPLLICLK コンフィグレーション ビットをセットする (FRC ではなくPOSC に PLL を併用して SYSCLK を駆動する )。 2. POSCMOD<1:0> コンフィグレーション ビットで HS または EC モードのどちらかを選 択する。 3. コンフィグレーション レジスタの値はデバイスリセット時に OSCCON レジスタにコ ピーされる。実行中にこれらのレジスタを変更する事で調整もできる。 59.3.1.1.2 オシレータ起動タイマ (OST) 水晶振動子( またはセラミック振動子 ) を確実に起動して安定させるために、オシレータ起動 タイマ(OST) を使います。OST は 1024 TOSCサイクルをカウントする単純な10 ビットカウンタ です。このカウントが終了した後に、システムへのオシレータ クロックの供給が始まります。 このタイムアウト時間をTOSTと表記します。オシレータ信号の振幅がオシレータピンのしきい 値VILおよびVIHに達すると、OST はサイクルのカウントを始めます。

パワーオンリセット(POR) 時、ブラウンアウト リセット (BOR) 時、スリープモードからの復 帰時にオシレータを再起動するたびにTOST遅延が必要です。OST は POSC の HS モードと SOSC に適用されます (セクション59.3.1.2「セカンダリ オシレータ (SOSC)」参照)。 59.3.1.1.3 スリープからのプライマリ オシレータの起動 プライマリ オシレータ回路を設計する際は、スリープから確実に復帰できるように注意が必要 です。復帰時は、両方の負荷コンデンサがある程度充電され、位相差が最小になります。この ため、発振が安定するまでに通常よりも長い時間を要します。また、低電圧条件、高温度条件、 周波数の低いクロックモードではループゲインが制限されるため、これらの条件も起動時間を 長引かせる要因となります。 起動時間を長引かせる要因として以下が挙げられます。 • 低周波数回路 ( 低ゲインのクロックモードを使用 ) • ノイズの少ない環境 ( バッテリ駆動型機器等 ) • シールドされたボックス内での動作 ( ノイズの多い RF エリアから隔離した場合 ) • 低電圧 • 高温度 Note 1: デバイス コンフィグレーションの詳細は各デバイス データシートの「その他の 特殊機能」を参照してください。 2: OSCTUN レジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。 詳細はセクション59.3.6.2「オシレータ切り換えシーケンス」を参照してください。

Note: POSC を EC または ECPLL モード向けに設定した場合、オシレータ起動タイマは

無効です。 OSCI I/O (OSCO) I/O Clock from External System PIC32 OSCIOFNC = 1: OSCI

OSCO (Clock Out) FOSC/2

Clock from External System

PIC32

DCO

を備えた

オシレータ

59

59.3.1.2 セカンダリ オシレータ (SOSC) セカンダリ オシレータ (SOSC) は、外部の 32.768 kHz 水晶振動子を使う低消費電力動作向けの オシレータです。このオシレータはSOSCO および SOSCI ピンを使い、低消費電力動作用の補 助的な水晶振動子クロック源として機能します。このオシレータは、リアルタイム クロック(RTC) アプリケーション向けに、Timer1 またはリアルタイム クロック / カレンダ (RTCC) モジュール ( もしくはその両方 ) を駆動する事もできます。 59.3.1.2.1 SOSC の有効化SOSC は、SOSCEN ビット (OSCCON<1>) によってハードウェアで有効になります。SOSCEN ビットをセットするとセカンダリ オシレータが有効になります。この場合、セカンダリ オシ レータはSOSCO および SOSCI ピンを制御するため、これらのピンを I/O ポートやその他の 機能向けに使う事はできません。 SOSC がクロック源として使用可能になるまでに、ウォームアップ時間が必要です。オシレー タを有効にすると、ウォームアップ カウンタが 1024 までインクリメントします。このカウン トが終了すると、SOSCRDY ビット (CLKSTAT<4>) は「1」にセットされます。セクション 59.3.1.1.2「オシレータ起動タイマ (OST)」を参照してください。 59.3.1.2.2 SOSC を常時動作させる

SOSCEN ビット (OSCCON<1>) をセットすると、SOSC は常時動作します。このオシレータ を常時動作させておくと、低消費電力動作用の32 kHz システムクロックに素早く切り換える 事ができます。ただし、セカンダリ オシレータから高速のメインオシレータ ( 水晶振動子およ び/ または PLL を使用 ) へ戻る際には、やはりオシレータ起動時間が必要です ( セクション 59.3.1.1.2「オシレータ起動タイマ (OST)」参照)。 また、リアルタイム クロック アプリケーションでは、セカンダリ オシレータを常時動作させる 必要があります(Timer1 用に必要な場合もあります )。詳細は『PIC32 ファミリ リファレンス マ ニュアル、セクション14. タイマ』(DS60001105) と『PIC32 ファミリ リファレンス マニュアル、 セクション29. リアルタイム クロック / カレンダ (RTCC)』(DS61125) を参照してください。 例 59-1: SOSC の有効化 59.3.1.2.3 SOSC 外部クロック

周辺モジュールへのSOSC 入力は、SCLKIN ピンを使う外部クロック源と併用できます。SOSC 無効時、SCLKIN ピンは SOSC をクロック源として使うシステムおよび周辺モジュールへの SOSC 入力源となります。

Note: OSCCONレジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。

詳細はセクション59.3.6.2「オシレータ切り換えシーケンス」を参照してください。

SYSKEY = 0x0; // Ensure OSCCON is locked SYSKEY = 0xAA996655; // Write Key1 to SYSKEY SYSKEY = 0x556699AA; // Write Key2 to SYSKEY

// OSCCON is now unlocked // Make the desired change OSCCON |= 2; // Enable Secondary Oscillator

// Relock the SYSKEY

SYSKEY = 0x0; // Write any value other than Key1 or Key2 // OSCCON is relocked

59.3.1.3.1 PLL 併用 DCO オシレータモード (DCOPLL)

DCO に PLL を併用し、PLL 逓倍比と出力分周比を選択する事で幅広い周波数レンジで SYSCLK を生成できます。COSC<2:0> ビット (OSCCON<14:12>) が「001」かつ PLLICLK<1:0> ビット (SPLLCON<7:6>) が「10」の時は常に DCO PLL モードが選択されます。PLL 逓倍比と出力分 周比を選択する事で、目標のデバイス周波数を生成できます。DCO 出力周波数が最低入力周波 数を満たしている事が必要です。 59.3.1.4 内部高速 RC (FRC) オシレータ FRC オシレータはユーザ設定可能な入力分周器、PLL 逓倍比、出力分周比を備えた内部高速 RC オシレータです ( 公称値 8 MHz)。ユーザによる周波数の微調整も可能です。FRC オシレー タの詳細は各デバイス データシートの「オシレータ コンフィグレーション」を参照してくだ さい。 59.3.1.4.1 FRC ポストスケーラ モード (FRCDIV) 内部高速オシレータをクロック源として使う場合、公称値8 MHz 以外の FRC 出力も生成でき ます。FRC に出力分周器 ( ポストスケーラ ) を併用する FRCDIV モードでは、分周比を選択す る事により、8 MHz をそのまま出力する以外に、これよりも低い 7 通りのクロック周波数を選 択できます。出力分周比はFRCDIV<2:0> ビット (OSCCON<26:24>) で設定します。FRC の公 称出力周波数(8 MHz) からは、4 MHz (2 分周 ) ~ 31 kHz (256 分周 ) の周波数を生成できます。 FRCDIV<2:0> ビットの設定を変更するだけで、いつでも簡単に周波数を低減してアプリケー ションの消費電力を削減できます。 59.3.1.4.2 PLL 併用 FRC オシレータモード (FRCPLL) FRCにPLLを併用し、PLL逓倍比と出力分周比を選択する事で、幅広い周波数レンジでSYSCLK を生成できます。COSC<2:0> が「001」かつ PLLICLK<1:0> が「01」の時は常に FRC PLL モードが選択されます。PLL 逓倍比と出力分周比を選択する事で、目標のデバイス周波数を生 成できます。 59.3.1.4.3 FRC オシレータ調整レジスタ (OSCTUN) FRC オシレータ調整レジスタ OSCTUN を使うと、FRC オシレータの出力周波数を約 ±12% (typ.) の範囲で微調整できます。このレジスタの調整ビット値を増減すると、FRC オシレータ の工場校正周波数が一定量変化します。 Note: 一部のデバイスではこのPLL 入力源を利用できません。詳細は各デバイスのデー タシートを参照してください。 Note: OSCTUN レジスタへの書き込みを実行する前に、ロック解除シーケンスが必要です。 詳細はセクション59.3.6.2「オシレータ切り換えシーケンス」を参照してください。

DCO

を備えた

オシレータ

59

59.3.1.4.4 FRC 自己調整アクティブ クロック チューニング FRC アクティブ クロック チューニングは動作中に FRC を自動校正するための仕組みです。この システムでは、精度が既知であるクロック源からのアクティブ クロック チューニングを使って 公称周波数8 MHz からきわめて狭いレンジ内に FRC を維持します。これにより、周波数精度が フルスピードUSB デバイスに関する『USB 2.0 仕様』の要件に十分に適合します。自己調整システムはOSCTUN レジスタのビットで制御します。STEN ビット (OSCTUN<15>) をセットすると自己調整機能が有効になり、STSRC ビット (OSCTUN<12>) で選択したクロック 源をハードウェアで校正できます。STSRC = 1 の場合、外部 USB ホストからの Start-of-Frame (SOF) パケットをクロック源として使います。STSRC = 0 の場合、水晶振動子によって制御さ れるSOSC を校正源として使います。校正源に関わらず、TUN<5:0> ビット (OSCTUN<5:0>) はFRC オシレータの周波数の変更に使います。周波数の監視と調整は動的であり、動作中に 常時行われます。システムがアクティブ時はソフトウェアによるTUNx ビットへの書き込みは できません。 自己調整システムがハードウェア割り込み(FSTIF) を生成する事があります。割り込みは参照 クロック調整源からのFRC ドリフトが ±0.2% を超えるか、周波数偏差が TUNx ビットの修正 能力( つまり 1.5%) を超えた場合に発生します。このような条件を示すために STLOCK および STOR ステータスビット (OSCTUN<11,9>) が使われます。STPOL および STORPOL ビット (OSCTUN<10,8>) でこれらの条件が存在する時としない時のどちらで FSTIF 割り込みが発生 するかを設定します。STPOL および STORPOL ビットの両方をテストして、割り込みの正確 な原因を突き止める必要があります。 59.3.1.5 内部低消費電力 RC (LPRC) オシレータ LPRC オシレータは FRC とは別のオシレータです。このオシレータは公称値 31.25 kHz で発振 します。LPRC オシレータはウォッチドッグ タイマ (WDT)、フェイルセーフ クロックモニタ (FSCM)、Timer1、RTCC 用のクロック源です。また、消費電力の低減が重要である代わりに タイミングの精度はそれほど重要でないアプリケーションでは、LPRC オシレータを使用して デバイスに低周波数のクロックを供給できます。 59.3.1.5.1 LPRC オシレータの有効化 LPRC オシレータは POR 時に停止します。以下のいずれかが該当する場合に有効になります。 • フェイルセーフ クロックモニタが有効 • WDT が有効 Note: 自己調整機能により、USB デバイスモードで動作するための十分な精度を維持し ます。USB ホストとして機能するアプリケーションについては、それでも高精度 のクロック源(±0.05%) が必要です。

Note: USB を参照クロック調整源として使うには (STSRC = 1)、デバイスを USB デバ

イス動作用に設定し、動作しているUSB ホストまたは USB ハブポートに接続す る必要があります。SOSC を参照クロック調整源として使うには (STSRC = 0)、 クロック調整が行われるようSOSC を設定する必要があります。

Note: 自己調整システム無効時(STEN = 0)、STLPOL および STORPOL ビットは無視で

きます。

59.3.2

PLL クロック ジェネレータ

59.3.2.1 システムクロックの位相ロックループ (SPLL) システムクロックPLL はユーザ設定可能で、広い PLL 逓倍比と出力分周比を提供します。SPLL はPOSC の HS および EC モードと内部 FRC オシレータモードで使う事ができ、1 つのクロック 源から各種のクロック周波数を生成できます。 PLL 逓倍比と出力分周比の値は SPLLCON レジスタ (レジスタ 59-2) の PLLMULT<2:0> および PLLODIV<2:0> ビットに格納しています。リセット時、これらのビットの既定値はデバイスごと に異なり、それによりPLL コンフィギュレーションが決まります。動作中は、ソフトウェアで逓 倍比と出力分周比を変更する事で、アプリケーションに適したクロック周波数にスケーリングで きます。 SPLL の入力クロック源は PLLICLK<1:0> ビット (SPLLCON<7:6>) で決まります。SPLL 入力は FRC または POSC です。これらのビットをセットすると、SPLL は FRC の 8 MHz を入力とし て使います。PLLICLKx ビットの既定のリセット値は、FPLLICLK コンフィグレーション ビット によって決まります。これにより、デバイスリセット時に SPLL クロック源を自動的に設定で きます。 PLL 逓倍比と出力分周比の組み合わせにより、入力周波数を 1/128 ~ 24 倍にスケーリングで きます。SPLL 出力周波数は式 59-1のように求まります。 式 59-1: SPLL 出力周波数の計算 信頼性の高い動作を得るために、PLL モジュールの出力周波数はデバイスの最大クロック周波 数以下である事が必要です。PLL 入力分周比は、PLL への入力周波数がデバイスの仕様レンジ 内に収まるように選択する必要があります。 SPLL を設定する手順は以下の通りです。 1. 入力周波数と必要なシステムクロック周波数に基づいて適切なPLL逓倍比と出力分周比 の値を計算する。 2. デバイスのプログラム時に、FPLLICLK コンフィグレーション ビットを使って SPLL の 起動クロック源を設定する。 3. 実行時に、SPLLCON レジスタで SPLL の設定をアプリケーションに適合するよう必要 に応じて変更する。 59.3.2.2 PLL ロックステータス PLL が安定した出力を供給し始めるまでに一定時間を要するため、PLL ロック ステータスビット SPLLRDY (CLKSTAT<7>) によって PLL の状態が示されます。SPLLRDY は、PLL のロック状 態を示します。このビットは、PLL がロックを完了するまでに要する標準的な遅延 (TLOCK) が 経過した後に自動的にセットされます。このビットは、PLL がロックを完了するか、PLL 起動 タイマが終了した時点でセットされます。このビットは、PLL がロックを完了していなくても、 タイマが終了するとセットされます。SPLLRDY ビットは、PLL を併用するクロック源への切 り換え時とPOR 時にクリアされます。 PLL が起動中に安定しなかった場合、SPLLRDY ビットは PLL のロック状態を正しく反映しま せん。また、正常動作中にPLL がロックを喪失した場合も、SPLLRDY ビットには反映されま せん。PLL を併用しないクロック源が選択されている場合、LOCK ビットはクリア状態を保持 Note: このコンフィグレーション ビットでは、DCO を既定の PLL クロック源として選 択できません。 Note: デバイス コンフィグレーションの詳細は各デバイス データシートの「その他の特 殊機能」を参照してください。 FOSC = 入力周波数 (POSC、FRC、DCO から ) PLLMULT<2:0> = PLLMULT<2:0> により選択された逓倍比 PLLODIV<2:0> = PLLODIV<2:0> により選択された分周比DCO

を備えた

オシレータ

59

59.3.3

2 段階起動

外部の水晶振動子を使う全てのPOSC モード (PLL 併用モードを含む ) では、2 段階起動モー ドを使ってデバイスの起動時間を短縮できます。2 段階起動では、プライマリ オシレータ (POSC) が安定するまで、FRC クロックを SYSCLK 用クロック源として使います。ユーザが選 択したオシレータが安定した後に、クロック源はFRC から POSC に切り換わります。これに よりCPU は、オシレータが安定するまで待たずに、低速でコードの実行を開始できます。POSC が起動基準を満たした時点で、POSC へのクロック切り換えが自動的に発生します。 このモードは、IESO コンフィグレーション ビットによって有効になります。デバイス コンフィ グレーションの詳細は各デバイス データシートの「その他の特殊機能」を参照してください。 2 段階起動は、POR 後とスリープからの復帰後に実行されます。ソフトウェアは、COSC<2:0> ビット(OSCCON<14:12>) を読み出す事で、現在どちらのクロック源を使って動作しているの かを判別できます。59.3.4

スリープからの

2 段階復帰

スリープからの2 段階復帰を使うと、外部オシレータ、PLL、またはこれらを組み合わせて使って いる時にスリープからの起動時間を短縮できます。スリープからの2 段階復帰では、選択したク ロック源が安定するまでFRC クロックを SYSCLK として使います。選択したクロック源が安定 した後は、選択したクロックに切り替わります。この機能は、SLP2SPD ビット (OSCCCON<13>) によって制御されます。 クロック切り替えの状態はNOSCx、COSCx、OSWEN ビットを使ってファームウェアで監視 できます。デバイス起動時のCOSCx は「000」で、FRC がクロック源である事を反映してい ます。NOSCx ビットはデバイスがスリープに入る前のクロック源の値を取ります。NOSCx ビットで選択したオシレータ信号源が安定すると、そのクロック源に切り替わります。NOSCx ビットで選択したオシレータ信号源への切り替えが完了するまで、OSWEN ビットは「1」です。59.3.5

フェイルセーフ

クロックモニタ (FSCM) の動作

フェイルセーフ クロックモニタ (FSCM) 機能を使うと、使用中のオシレータで障害が発生して も、デバイスの動作を継続できます。FSCM は、使用中のクロック源で障害を検出すると、自 動的にSYSCLK を内部 FRC オシレータに切り換えます。内部 FRC オシレータへ切り換えて デバイスの動作を継続し、POSC への復帰を試みるか、あるいはクロック障害に対応したコー ドを実行できます。 FSCM 機能は、FCMEN コンフィグレーション ビットによって有効になります。FSCM は全て のPOSC モードで使えます。デバイス コンフィグレーションの詳細は各デバイス データシー トの「その他の特殊機能」を参照してください。 FSCM がクロック障害を検出すると、ノンマスカブル割り込み (NMI) が生成されます。NMI に 対応する割り込みサービスルーチン(ISR) は、 RMNICON レジスタの CF ビットを読み出す事 で、このNMI が FSCM によって生成された事を判別できます。詳細はデバイス データシート Note: ウォッチドッグ タイマ (WDT) が有効になっている場合、WDT は SYSCLK 周波数 に関係なく同じレートでカウントし続けます。2 段階起動中に WDT をサービスす る場合、SYSCLK の変化に注意する必要があります。 Note: この機能は一部のデバイスでのみ利用できます。詳細はデバイスのデータシートを 参照してください。59.3.5.1 FSCM 遅延 POR、BOR、スリープからの復帰後、FSCM が SYSCLK クロック源の監視を始めるまでに、 公称遅延時間(TFSCM) が挿入される場合があります。FSCM 遅延の目的は、オシレータや PLL が安定するまでの時間を確保する事にあります。FSCM 遅延は、内部システムリセット信号 SYSRST がリリースされた後に生成されます。FSCM 遅延タイミングの詳細は『PIC32 ファミ リ リファレンス マニュアル、セクション 7. リセット』(DS60001118) を参照してください。 TFSCM遅延は、FSCM が有効かつ SYSCLK として HS、HSPLL、SOSC モードのいずれかが 選択されている場合に適用されます。 59.3.5.2 FSCM と起動の遅いオシレータ 選択したデバイス オシレータが POR、BOR、スリープ後の起動に長時間を要する場合、オシ レータが完全に起動する前にFSCM 遅延が終了する可能性があります。この場合、FSCM はク ロック障害トラップを生成し、COSC<2:0> ビット (OSCCON<14:12>) に FRC オシレータを選 択する値を書き込みます。この結果、起動を試みていたオシレータは停止します。ソフトウェ アは、NMI ISR を使うか、CF ビット (OSCCON<3>) をポーリングする事で、クロック障害を 検出できます。 59.3.5.3 FSCM と WDT FSCM と WDT はどちらもタイムベースとして LPRC オシレータを使います。これらのデバイ スでは、クロック障害が発生してもWDT は影響を受けずに動作を続けます。 59.3.5.4 FSCM のソフトウェア トリガ ソフトウェアでFSCM 切り換えシーケンスをトリガすると、クロック源を物理的に取り除かな くても、PIC32 アプリケーションによる FSCM イベントの処理をテストできるので便利です。 ソフトウェアでFSCM イベントをトリガする手順は以下の通りです。 1. ロック解除シーケンスを実行してOSCCON レジスタの書き込みロックを解除する (セクション59.3.6.2「オシレータ切り換えシーケンス」参照)。 2. CF ビット (OSCCON<3>) に「1」を書き込む。 切り換えが完了すると、NMI 割り込みサービスルーチン (ISR) が始まります。 クロックを実際にFRC へ切り換える事なく NMI ISR をトリガする事もできます。これを行う には、RNMICON レジスタの CF ビットに「1」を書き込みます。詳細は『PIC32 ファミリ リ ファレンス マニュアル、セクション 7. リセット』(DS60001118) を参照してください。 59.3.5.5 FSCM イベント条件のクリア

MPLAB® XC32 C コンパイラが提供する NMI ハンドラ プロシージャ (_nmi_handler) を使う と、メインオシレータの再起動を試みる事ができます。

Note: TFSCMの仕様値については、各デバイス データシートの「電気的特性」を参照し

DCO

を備えた

オシレータ

59

59.3.6

クロック切り換え動作

アプリケーションは、ソフトウェアが制御する5 つのクロック源 (POSC、SOSC、FRC、LPRC、 DCO) を常時ほぼ無制限に切り換える事ができます。このような柔軟な切り換え動作によって 予期せぬ結果が生じる可能性もあるため、PIC32 は切り換えプロセスに保護ロック機能を組み 込んでいます。 59.3.6.1 クロック切り換えの有効化 クロック切り換えを有効にするには、FSCMEN コンフィグレーション ビットを「1」に書き換 える( プログラミングする ) 必要があります。 クロック切り換えが無効の場合、NOSC<2:0> 制御ビット (OSCCON<10:8>) を使ってクロック の選択を制御する事はできません。ただし、COSC<2:0> ビット (OSCCON<14:12>) は、 FNOSC<2:0> コンフィグレーション ビットで選択されているクロック源を反映します。 クロック切り換えが無効の場合、OSWEN 制御ビット (OSCCON<0>) は効果を持たず、常に 「0」を保持します。 59.3.6.2 オシレータ切り換えシーケンス ロック解除シーケンスは、ロック機能によって保護されている全てのレジスタのロックを解除 します。システムロックを解除している時間を最小限に留める事を推奨します。クロック切り 換えの推奨コードシーケンスは以下の通りです。 1. 必要に応じて、COSC<2:0> ビット (OSCCON<14:12>) を読み出して、現状使用中のオシ レータソースを確認する。 2. システムのロック解除シーケンスを実行する前に、割り込みとDMA を無効にする。 3. 連続した2 回のアセンブリ命令または C 命令を実行して SYSKEY レジスタに 2 つのキー 値(0xAA996655 と 0x556699AA) を書き込む事により、システムロック解除シーケンス を実行する。 4. NOSC<2:0> 制御ビットに切り換え先のオシレータソースを指定する値を書き込む。 5. OSCCON レジスタの OSWEN ビットをセットしてオシレータの切り換えを開始する。 6. SYSKEY レジスタにキー値以外の任意の値 ( 例 : 0x00000000) を書き込む事により、解除 したロックを再ロックする。クロックに影響されにくいコードの実行を継続する( 必須で はない)。 7. OSWEN ビットが「0」であるかどうかを確認する。このビットが「0」であれば、クロッ Note 1: プライマリ オシレータモードには 2 つのサブモード (HS と EC) があり、これは POSCMOD<1:0> コンフィグレーション ビットで選択します。プライマリ オシ レータモードと他のモード間の切り換えはソフトウェアで実行できますが、プラ イマリ オシレータのサブモードを切り換えるにはデバイスの再プログラミング が必要です。デバイス コンフィグレーションの詳細は各デバイス データシート の「その他の特殊機能」を参照してください。 2: また、PLL 併用クロック源を使って動作している時に、これに影響する PLL 逓倍 比、プリスケーラ値、ポストスケーラ値はいずれも変更しないでください。これら のクロック切り換え機能を実行するには、クロック源を一度PLL 非併用クロック 源(FRC 等 ) に切り換えた後に、必要なクロック源に切り換える必要があります。 この要件は、PLL を使うクロック源にのみ適用されます。上記の基本シーケンスが完了すると、SYSCLK ハードウェアは自動的に以下のように応答します。 1. クロック切り換えハードウェアは、COSC<2:0> ステータスビットと NOSC<2:0> 制御 ビットの新しい値を比較する。両者が一致する場合、クロック切り換えは冗長動作であ るため、OSWEN ビットは自動的にクリアされ、クロック切り換えを中止します。 2. 切り換え先のオシレータが動作中でなければ、ハードウェアはそのオシレータを起動す る。水晶振動子を起動する必要がある場合、ハードウェアはオシレータ起動タイマ(OST) が終了するまで待機する。切り換え先のクロック源がPLL を併用する場合、ハードウェ アはPLL ロック (SPLLRDY = 1) を検出するまで待機します。 3. ハードウェアはOSWEN ビットをクリアしてクロック切り換えに成功した事を示す。 加えて、NOSC<2:0> ビットの値を COSC<2:0> ステータスビットに転送します。 4. この時点で切り換え前に使っていたクロック源がOFF になる ( このクロックを使うモ ジュールが存在しない場合)。 図 59-4に、クロック源の切り換えタイミングを示します。 図 59-4: クロック切り換えのタイミング チャート Note: クロック切り換えシーケンス中もプロセッサはコード実行を継続します。この間 にタイミングが重要なコードの実行を避ける必要があります。

Old Clock Source

New Clock Source

SYSCLK

Both Oscillators Active OSWEN bit New Source Enabled New Source Stable Old Source Disabled