AD 変換器の回路構成と CMOS 回路技術

岩 田 穆

株式会社 エイアールテック

〒739-0005 東広島市西条大坪町 10-29-1205

E-mail: iwa@a-r-tec.jp, Tel: 082-424-7856

AD変換の原理として,逐次比較,並列比較,パイプライン,デルタシグマなど多くが考案され,信号周波数:DC~10GHz,分解能:3 ~24ビットの広い性能領域のAD変換器が実現されている.現在,情報,通信,センシング,制御など,あらゆるシステムに不可 欠なものとなっている.AD変換技術の開発はデバイススケーリングとシステムデジタル化の進展と一体になって進んできた. CMOSの時代になって,高い変換性能を低電力,小面積で効率的に実現し,大規模模デジタルチップへ搭載することが最大の課題 となっている.各AD変換方式が,純アナログ回路の限界を破り,高速デジタル回路と融合することにより,進展している.近年, AD開発の初期に主流であった逐次比較技術に回帰して,研究が活発になっている.回路規模が小さく時間領域インタリーブ方式 による高速化に適するので,高速通信システム用の高速AD変換器の低電力化を目指している.また,微細化デバイスに要求され る精度,雑音の特性を緩和するために,デジタル技術によるアナログ特性の自動補正,時にバックグラウンド補正技術が重要で ある.

AD Conversion Principles and CMOS Circuit Techniques

Atsushi IWATA

A-R-Tec Corp.,

10-29-1205 Saijo-Ohtsubo-cho, Higashi-Hiroshima, 739-0005 Japan

E-mail: iwa@a-r-tec.jp, Phone: 082-424-7856

Many kinds of AD conversion schemes of Successive approximation, Flash, Pipelined, Delta Sigma, were proposed and

integrated AD conversion devices with wide range of signal bandwidth: DC-10GHz and resolution: 3-20bits, have been

developed. Currently ADCs become indispensable for all systems in information processing, communication, sensing, and

control. AD conversion techniques have been developed with the progress of device scaling and digital systems. In the scaled

CMOS era, development of high performance converters which have high efficiency in dissipation power and chip area, and be

integrated to large scale logic chips, becomes the major subject. Recently, the traditional Successive Approximation AD

conversion technique has been developed recursively, because the scheme is suitable to attain high speed combining with the

time-domain interleave scheme, because of it features of low power dissipation and small size. To relax accuracy and noise of

scaled devices, automatic digital error correction techniques, especially, background calibration which can eliminate variations

due to process, voltage and temperature have also been intensively developed.

1. ま え が き

1975 年 頃 か ら 通 信 や 信 号 処 理 シ ス テ ム の デ ジ タ ル 化 と の 集 積 化 を 両 輪 と す る 技 術 革 新 が 進 み , こ の た め に 鍵 と な る AD 変 換 器 (ADC)は 急 速 に 進 歩 し て き た . 30 年 以 上 に 渡 り , 急 速 に 拡 大 す る 通 信 帯 域 や 処 理 速 度 の 要 求 に 応 え て ,MOS 微 細 化 の 特 徴 を 活 か す AD 変 換 回 路 技 術 の 研 究 が 活 発 に 続 い て い る .集 積 AD 変 換 器 の 黎 明 期 か ら ,研 究 開 発 に 携 わ っ て き た の で ,AD 変 換 に は 高 精 度 化 , 広 帯 域 化 , 低 電 力 化 , 低 電 圧 動 作 化 , 小 面 積 化 な ど 多 く の 性 能 の ト レ ー ド オ フ を 考 え 多 彩 な 回 路 方 式 が 提 案 さ れ ,実 用 化 さ れ た .こ こ で は 主 な AD 変 換 の 原 理 と CMOS 回 路 技 術 ,実 現 で き る 変 換 性 能 に つ い て 述 べ , 性 能 限 界 , ブ レ ー ク ス ル ー 技 術 , デ バ イ ス の 微 細 化 , 低 電 圧 化 に 対 応 し て 将 来 動 向 に つ い て 述 べ る .2. AD 変 換 方 式 と 変 換 性 能

変 換 方 式 は サ ン プ リ ン グ 周 波 数 (fs)に よ り , ナ イ キ ス ト サ ン プ ル と オ ー バ サ ン プ ル に 大 別 で き , 前 者 に は 逐 次 比 較 方 式 (SA),並 列 比 較 方 式 (Flash),パ イ プ ラ イ ン 方 式 (Pipe)が あ り , 後 者 に は Δ Σ 方 式 (DS)が あ る . AD 変 換 に は ア ナ ロ グ 量 を デ ジ タ ル の ビ ッ ト に 対 応 し た 基 準 量 が 必 須 で あ る . 多 ビ ッ ト ナ イ キ ス ト サ ン プ ル と 低 ビ ッ ト オ ー バ サ ン プ ル の 原 理 的 な 比 較 を 図 1 に 示 す . n ビ ッ ト で は 基 準 電 圧 か ら 2n個 の 基 準 を 生 成 す る た め に 加 重 素 子 が 必 要 に な る . 精 度 を 上 げ る た め に は 加 重 素 子 を 大 型 に す る , 素 子 数 を 増 や す , 素 子 を 物 理 的 に 調 整 す る な ど の 方 法 が 使 わ れ る が , チ ッ プ 面 積 増 や コ ス ト 増 が 問 題 と な る . こ れ を 解 決 す る た め に , 小 数 の 低 精 度 の 加 重 素 子 を 用 い て , デ ジ タ ル 補 正 で 解 決 す る 技 術 が 着 目 さ れ て い る . 一 方 ,1 ビ ッ ト 量 子 化 で は 信 号 周 波 数 の 100 倍 程 度 の fs が 必 要 あ る が ,MOS デ バ イ ス の 微 細 化 で 達 成 で き , 1 個 の 基 準 で 済 み 加 重 素 子 が 不 要 で あ る の で 非 線 形 性 が 発 生 し な い .12 ビ ッ ト 以 上 の 高 分 解 能 に 適 す る .fs が 高 い の で 折 り 返 し 成 分 も 高 い 周 波 数 に 発 生 す る . 図 1 サ ン プ リ ン グ 周 波 数 と 基 準 量 図 2 AD 変 換 技 術 の 歴 史 - 回 帰 す る 技 術 - 入 力 と 基 準 電 圧 と の 比 較 の 手 順 と 実 現 回 路 は 変 換 速 度 , 消 費 電 力 , 回 路 規 模 を 決 め る . 上 位 ビ ッ ト か ら 順 に 比 較・判 定 す る 方 式 に は SA 方 式 と サ イ ク リ ッ ク 方 式 が あ る . 各 識 別 基 準 電 圧 を 逐 次 発 生 し 入 力 と 比 較 す る の で ,回 路 は 簡 単 で 低 電 力 で あ る が , 原 理 的 に 変 換 速 度 は 遅 い . Pipe 方 式 も 逐 次 比 較 で あ る が ,時 系 列 デ ー タ に 対 し て パ イ プ ラ イ ン 並 列 動 作 す る . 回 路 規 模 は パ イ プ ラ イ ン 段 数 に 比 例 し て 増 加 す る が , 高 速 変 換 が 可 能 で あ る . Flash 方 式 は 2n個 の 基 準 電 圧 と コ ン パ レ ー タ を 同 時 に 動 作 さ せ 瞬 時 に 比 較 し ,AD 変 換 す る .回 路 規 模 ,消 費 電 力 は 大 き い が 原 理 的 に 最 も 高 速 な 変 換 が 可 能 で あ る . Flash 方 式 に も 比 較 , コ ー ド 変 換 , エ ラ ー 処 理 な ど に は パ イ プ ラ イ ン 処 理 を 用 い て 比 較 に 要 す る 時 間 の み で 変 換 速 度 が 決 ま る よ う に し て 高 速 化 し て い る . オ ー バ サ ン プ リ ン グ 方 式 で は DS 方 式 が 16 ビ ッ ト 以 上 の 高 分 機 能 ,高 SN の 変 換 器 の 主 流 に な っ て い る . 高 速 ク ロ ッ ク で 低 ビ ッ ト の 判 定 を 繰 り 返 す と い う 単 純 な 動 作 で あ る . 多 段 量 子 化 ノ イ ズ シ ェ ー ピ ン グ 方 式 (MASH) は パ イ プ ラ イ ン 処 理 と 取 り 入 れ た DS で あ る . 時 間 領 域 イ ン タ リ ー ブ (TI)方 式 は ,m 個 の 単 位 AD 変 換 器 を m 相 の ク ロ ッ ク で 動 作 さ せ , 等 価 的 に 変 換 速 度 を m 倍 に す る 方 式 で あ り . 単 位 AD 変 換 器 に は DS 以 外 の AD 変 換 方 式 が 適 用 で き , TI-Flash, TI-SA が あ る . 集 積 化 ADC の 開 発 の 歴 史 を 理 解 す る た め に 各 方 式 の ISSCC で の 発 表 件 数 を 図 2 に 示 す . ま た ,各 時 代 に 提 案 さ れ た 重 要 な 技 術 の 発 表 ( 年 , 論 文 番 号 )も 示 す . 70 年 代 SA,80 年 代 は Flash, 90 年 代 は DS,2000 年 代 は Pipe と DS の 開 発 が 進 み , 現 在 は SA, TI が 注 目 さ れ て い る . 各 方 式 の AD 変 換 器 の 開 発 例 と , 音 声 PCM 通 信 , デ ジ タ ル オ ー デ ィ オ , デ ジ タ ル 画 像 処 理 , 携 帯 通 信 な ど 応 用 分 野 を 図 3 に 示 す . 高 精 度 , 高 速 の 極 限 性 能 は デ ジ タ ル 計 測 器 応 用 が 技 術 を 先 導 し た .ま た ,セ ン サ ネ ッ ト に お け る 極 限 低 電 力 化 の 要 求 が 技 術 を 先 導 し て い る .セ ン サ 用 の マ イ コ ン 搭 載 ADC は 制 御 ,家 電 ,自 動 車 な ど . あ ら ゆ る シ ス テ ム に 応 用 さ れ て い る . 図 3 開 発 例 と 応 用 シ ス テ ム 100 1K 10K 100K 1M 10M 100M 1G 10G 20 30 40 50 60 70 80 90 100 110 120 Digital Audio UMTS GSM Video Measurement Digital Oscilo SNR [dB] BW [ H z ] SA Flash Pipe Delta Sigma 100 1K 10K 100K 1M 10M 100M 1G 10G 20 30 40 50 60 70 80 90 100 110 120 Digital Audio UMTS GSM Video Measurement Digital Oscilo SNR [dB] BW [ H z ] SA Flash Pipe Delta Sigma 2 4 6 8 10 1974 197 6 197 8 1980 1982 1984 1986 1988 1990 1992 1994 1996 1998 2000 2002 2004 2006 2008 年 0 SA PIpe Flash DS SA DS’86,11.5 MASH’87,3.5 DS-24b’94,10.6 DS-CT’99,3.2DS’97,13.2 SA-C array’75,3.1 SA-Codec’81,17.4,17.5 Flash-Bip’79,11.2 SA-TI ’06,31.5, ’08,30.3 Flash-TI ’03,18.3 SA-Self Calib.’90,10.6 Pipe’87,17.2 Pipe-TI’02,10.4 Flash-’99,18.5,18.6 Folding’98,9.7 Successive Approx. Pipelined Flash / Folding Flash-Int’02,10.3 1.5bMDAC ,’98,VL14.2 SA-Diff’’90,JSC25.p.173 ’04,14.1, ’06,31.3 SA-’08,12.4 Pipe’07,25.1 発表件 数 技術キーワード,年,論文番号 Delta Sigma 2 4 6 8 10 1974 197 6 197 8 1980 1982 1984 1986 1988 1990 1992 1994 1996 1998 2000 2002 2004 2006 2008 年 0 SA PIpe Flash DS SA DS’86,11.5 MASH’87,3.5 DS-24b’94,10.6 DS-CT’99,3.2DS’97,13.2 DS’86,11.5 MASH’87,3.5 DS-24b’94,10.6 DS-CT’99,3.2DS’97,13.2 SA-C array’75,3.1 SA-Codec’81,17.4,17.5 Flash-Bip’79,11.2 SA-TI ’06,31.5, ’08,30.3 Flash-TI ’03,18.3 SA-Self Calib.’90,10.6 Pipe’87,17.2 Pipe-TI’02,10.4 Flash-’99,18.5,18.6 Folding’98,9.7 Successive Approx. Pipelined Flash / Folding Flash-Int’02,10.3 1.5bMDAC ,’98,VL14.2 SA-Diff’’90,JSC25.p.173 ’04,14.1, ’06,31.3 SA-’08,12.4 Pipe’07,25.1 発表件 数 技術キーワード,年,論文番号 Delta Sigma 時間 電圧レベル 入力信号 1 2 3 4 5 0 7 8 9 10 11 12 6 入力信号 電圧レベル 1 2 3 4 5 0 7 8 9 10 11 12 6 多ビットA-D 変換 fs 4 2 1 1/4 1101110110110101 ビットストリームデジタル出力 8 4 2 11/2 1/4 多ビット:大小多数 のコップで計量 12ビット以上では 精度補正が必要 高速に繰り返し計量して精度向上 1ビット:1個のコップで計量 誤差が発生しない(a) Multi-bit Nyquist ADC

時間 4 2 1 8 2 1 (b) Oversamplig ADC 時間 電圧レベル 入力信号 1 2 3 4 5 0 7 8 9 10 11 12 6 入力信号 電圧レベル 1 2 3 4 5 0 7 8 9 10 11 12 6 多ビットA-D 変換 fs 4 2 1 1/4 1101110110110101 1101110110110101 ビットストリームデジタル出力 8 4 2 11/2 1/4 多ビット:大小多数 のコップで計量 12ビット以上では 精度補正が必要 高速に繰り返し計量して精度向上 1ビット:1個のコップで計量 誤差が発生しない

(a) Multi-bit Nyquist ADC

時間 4 2 1 8 2 1 (b) Oversamplig ADC

3. 集 積 回 路 に 適 し た 逐 次 比 較 方 式

SA(Successive Approximation) 方 式 は , S/H さ れ た ア ナ ロ グ 入 力 電 圧 と 帰 還 DAC 出 力 電 圧 を , 1 個 の コ ン パ レ ー タ (Comp)で 逐 次 的 に 比 較 し て 変 換 す る , 回 路 規 模 が 少 な い 利 点 と 引 き 替 え に , ビ ッ ト 数 に 等 し い 回 数 の 比 較 が 必 要 で あ り , 変 換 速 度 は 比 較 的 遅 い こ と が 欠 点 で あ っ た . 図 4 SA 方 式 AD 変 換 器 と 容 量 ア レ イ の 構 成3.1. 帰 還 DAC の 荷 重 素 子

2 進 荷 重 容 量 ア レ イ と ス イ ッ チ (SW)に よ る 電 荷 再 分 布 原 理 DA 変 換 器 が 高 精 度 で あ り ,S/H の 保 持 容 量 も 持 つ の で 主 流 と な っ て い る , 精 度 は 容 量 比 (C ratio) で 決 ま り , 2n個 の 単 位 容 量 を 用 い , こ の サ イ ズ を 大 き く す る と 精 度 が 上 が り , 10 ビ ッ ト は 実 現 で き る . C に は 高 線 形 性 が 要 求 さ れ る の で 2 層 ポ リ Si 容 量 が 用 い ら れ た . そ の 後 , 多 層 配 線 の 微 細 化 に 伴 い MIM 容 量 , MOM ( 配 線 間 ) 容 量 と 変 遷 し て い る . 回 路 的 に は , 容 量 ア レ イ の 面 積 を 削 減 で き る 2 ス テ ッ プ 容 量 ア レ イ , C-2C ラ ダ ー が 用 い ら れ る . 単 位 容 量 C0, 全 容 量 CT, 非 線 形 NI を 表 1 に 示 す . 表 1 各 種 容 量 ア レ イ の 特 性 (分 解 能 10bit)3.2. 精 度 を 高 め る キ ャ リ ブ レ ー シ ョ ン

素 子 偏 差 補 償 の た め に レ ー ザ な ど に よ る ト リ ミ ン グ は コ ス ト 的 に 不 利 で あ る の で , セ ル フ キ ャ リ ブ レ ー シ ョ ン が 開 発 さ れ , 補 正 用 DAC な ど の ア ナ ロ グ 補 正 回 路 を 用 い て 16 ビ ッ ト 以 上 が 達 成 さ れ た[1 ] ま た . 回 路 差 動 化 に よ り 電 源 雑 音 , 同 相 変 動 が 抑 圧 で き る よ う に な っ た .3.3. 消 費 電 力 の 低 減

電 力 消 費 の 主 要 因 で あ る コ ン パ レ ー タ (Comp) の 低 電 力 化 が 課 題 で あ る . 初 期 の Comp に 用 い ら れ た OPA の 帰 還 動 作 で オ フ セ ッ ト 電 圧 ( Voff) 補 償 は 消 費 電 力 が 大 き い の で , ラ ッ チ 回 路 に プ リ ア ン プ を 前 置 し て Voff 補 償 に よ り 電 力 が 削 減 さ れ た .さ ら に 低 減 す る に は 熱 雑 音 に よ る 識 別 の 不 確 定 が ネ ッ ク に な る . 精 度 を 落 と し て 電 力 を 節 約 し て , SA の 比 較 を 1 回 増 や し て , Comp の 雑 音 に よ る 誤 差 を デ ジ タ ル 補 正 す る 方 法 が 提 案 さ れ て い る .[2 ] 次 に C ア レ イ の 充 放 電 に よ る 電 力 消 費 の 抑 圧 が 必 要 で あ る . 電 荷 再 分 布 動 作 に お け る 電 荷 移 動 時 に SW の MOS に 電 流 の ジ ュ ー ル 熱 が 原 因 で あ る . こ の 対 策 と し て , 電 荷 移 動 量 を 減 ら す , 断 熱 充 電 で ジ ュ ー ル 熱 を 減 ら す 技 術 が 提 案 さ れ て い る .[ 3 ] さ ら に 逐 次 比 較 の 論 理 回 路 の 電 力 が 問 題 に な る . 現 在 ,最 も 低 電 力 な SA 方 式 AD は サ ブ ス レ ッ シ ョ ル ド 動 作 Comp と C ア レ イ 断 熱 充 電 に よ る C ア レ イ 電 荷 再 分 布 な ど 低 電 力 化 技 術 を 駆 使 し て , 1.9uW, 10 ビ ッ ト 1 MS/s を 達 成 し て お り , FOM=4.4fJ/step で あ る .4. 速 度 ・帯 域 を 極 め る 並 列 比 較 方 式

図 5 に 示 す よ う に 2b個 の Comp の ア レ イ を 用 い て 1 clock で 1 挙 に 量 子 化 し , サ ー モ メ ー タ 符 号 を エ ン コ ー ド し て 出 力 す る . S/H が 不 要 で あ る の で OPA, SW な ど 線 形 回 路 を 使 わ な い で デ ジ タ ル 回 路 主 体 で A/D 変 換 で き る .Comp,エ ン コ ー ダ を パ イ プ ラ イ ン 動 作 さ せ て . fs を あ げ る が , ク ロ ッ ク ジ ッ タ に よ る Comp 動 作 の 非 理 想 性 ,comp の し き い 値 ,動 作 速 度 の 偏 差 に よ る グ リ ッ チ の 抑 圧 が 必 要 で あ る . Flash か ら 派 生 し たフ ォ ー

ル デ ィ ン グ 方 式 が あ り

, ア ナ ロ グ 前 処 理 で 入 力 信 号 レ ベ ル を 折 り 返 し て 並 列 比 較 に 要 す る 規 模 を 抑 圧 方 式 で あ る . Flash 方 式 の 量 子 化 器 に は , オ フ セ ッ ト 補 償 型 イ ン バ ー タ チ ョ ッ パ 型 Comp の ア レ イ が , よ く 用 い ら れ る . 容 量 補 間 (イ ン タ ポ レ ー シ ョ ン )技 術 で コ ン パ レ ー タ の 数 を 1/2~ 1/8 に 減 ら し て 低 電 力 化 が 図 ら れ た .[ 4 ] し か し ,Voff 補 償 の た め の イ ン バ ー タ 帰 還 時 の 電 力 が 大 き い の で , 差 動 ラ ッ チ コ ン パ レ ー タ に プ リ ア ン プ を 前 置 す る こ と に よ り , 感 度 向 上 と 電 力 消 費 の 少 な い オ フ セ ッ ト 補 償 回 路 が 開 発 さ れ た . 多 数 の コ ン パ レ ー タ が 同 時 に 動 作 す る の で , ク ロ ッ ク が 寄 生 容 量 を 介 し て 入 力 側 に 結 合 す る キ ッ ク バ ッ ク が 精 度 を 劣 化 さ せ る , プ リ ア ン プ は こ れ を 抑 圧 す る 効 果 も あ る . Flash 方 式 で は 原 理 的 に は S/H が 不 要 で あ る が , 追 加 す る こ と に よ り 各 Comp の 動 作 タ イ ミ ン グ の 偏 差 を 抑 圧 す る 方 式 も あ る . 図 5 Flash AD 変 換 器 の ブ ロ ッ ク 図 変化点検出 バブル抑圧 Vin Vreftop Dout ラッチ コンパレータ バイ ナリ エ ン コ ー ダ Clock 出力レジス タ Vref 1 Vref 2 Vref 3 Clk1 Clk2 Clk3 Clk4 L L L L L L L L Vref 2n-1 Vrefbot クロック生成・ドライバ 信号遅延 2n-1個 クロック遅延 変化点検出 バブル抑圧 Vin Vreftop Dout ラッチ コンパレータ バイ ナリ エ ン コ ー ダ Clock 出力レジス タ Vref 1 Vref 2 Vref 3 Clk1 Clk2 Clk3 Clk4 L L L L L L L L Vref 2n-1 Vrefbot クロック生成・ドライバ 信号遅延 2n-1個 クロック遅延 0.507 0.049 0.0007 150000 5000 C2C Ladder 0.299 0.029 0.0016 57600 900 Two step BC 0.158 0.015 0.0070 51200 50Split Binary C Array

0.224 0.022 0.0070 51200 50 Binary C Array NL (LSB) Nlmax (%) σ(%) CT (fF) C0(fF) 0.507 0.049 0.0007 150000 5000 C2C Ladder 0.299 0.029 0.0016 57600 900 Two step BC 0.158 0.015 0.0070 51200 50

Split Binary C Array

0.224 0.022 0.0070 51200 50 Binary C Array NL (LSB) Nlmax (%) σ(%) CT (fF) C0(fF) Vref Ain S/H

DAC SARLogic

C Array Dout Clock Clock S/H DAC Comp SAR Logic C Array Vref Ain S/H

DAC SARLogic

C Array Dout Clock Clock S/H DAC Comp SAR Logic C Array C 2C 4C 8C C 2C 4C 8C Cc C 16 C 32 C 64 C C 2C 4C 8C C Vout Vout 2C C C C C C 2C 2C 2C 2C Vout C C2C Ladder Two step C Array

Binary C Array C 2C 4C 8C C 2C 4C 8C Cc C 16 C 32 C 64 C C 2C 4C 8C C Vout Vout 2C C C C C C 2C 2C 2C 2C Vout C C2C Ladder Two step C Array

5. 速 度 ・精 度 を 両 立 す る パ イ プ ラ イ ン 方 式

低 分 解 能 (1, 1.5b) の 変 換 ス テ ー ジ (MDAC) を 縦 続 接 続 し , 上 位 ビ ッ ト か ら 決 定 し , 変 換 誤 差 を 増 幅 し て 次 段 に 送 る . 各 段 の 回 路 を 順 次 次 の デ ー タ で 動 作 さ せ る パ イ プ ラ イ 並 列 動 作 さ せ て ス ル ー プ ッ ト が 向 上 で き る . 各 MDAC の 機 能 は 量 子 化 , DAC, 減 算 , 増 幅 , ホ ー ル ド と 多 い が , 低 ビ ッ ト で よ い の で 回 路 規 模 は 小 さ い . 図 6 に 示 す よ う に , コ ン パ レ ー タ 2 個 を 用 い た 1.5b の MDAC が 主 流 で あ る .[ 5 ] こ れ は 判 定 レ ベ ル 偏 差 が 発 生 し て も ,冗 長 性 に よ り 補 正 で き る .OPA を 共 用 し て MDAC に S/H 機 能 を 持 た せ る 方 法[6 ], 図 7 に 示 す よ う に 初 段 MDAC を 2bit 化 し て 伝 達 特 性 の 改 良 し , 図 8 に 示 す よ う に , 入 力 レ ン ジ 拡 大 あ る い は 電 源 電 圧 低 下 を 可 能 に し た .[ 7 ] ス テ ー ジ の 回 路 性 能 の 重 み 付 け に よ り ,容 量 の 小 型 化 , OPA の 低 電 力 化 と 要 求 特 性 の 緩 和 が 続 い て い る .パ イ プ ラ イ ン 方 式 の 変 換 性 能 は 10bit, 100MS/s, あ る い は 12bit, 50MS/s , で あ り , 電 源 電 圧 1V で , FOM=200fJ/step 程 度 に 到 達 し て い る . 図 6 パ イ プ ラ イ ン AD 変 換 器 の ブ ロ ッ ク 図 図 7 初 段 2bMDAC パ イ プ ラ イ ン AD 変 換 器[ 7 ] 図 8 SNDR の 電 源 電 圧 依 存 性 , 変 換 速 度 依 存 性[ 7 ]6. 高 分 解 能 デ ル タ シ グ マ 方 式

図 9 に 示 す よ う に , オ ー バ サ ン プ リ ン グ , ノ イ ズ シ ェ ー ピ ン グ (NS)技 術 に よ り 高 精 度 を 得 る 方 式 で あ る . 変 換 精 度 は オ ー バ サ ン プ リ ン グ 比 OSR= fs/ 2*BW で 決 ま り . NS 次 数 =k , 1bit 量 子 化 の 場 合 , SNR= -5.12+10(2k+1) log(OSR) と な り 1bit 量 子 化 器 と DAC で も OSR=64, k=2 で 90dB 以 上 の SNR が 得 ら れ る .6.1. 高 SNΔ Σ A/D 変 換 器

NS フ ィ ル タ に は SC 積 分 器 が 適 し て い る が ,SNR 向 上 に は NS 次 数 が 3 次 以 上 に な る と 安 定 性 の 確 保 が 必 要 に な る .図 10 の よ う に 1 次 ル ー プ を 縦 続 接 続 し て 高 次 NS を 実 現 す る Multi Stage Noise Shaping (MASH)が 考 案 さ れ た .[8 ] 高 次 NS で 90dB 以 上 の SN が 実 現 で き る の で , デ ジ タ ル オ ー デ ィ オ 用 の 主 流 方 式 と な り , そ の 後 の Δ Σ に 広 く 採 用 さ れ た . 高 精 度 の 極 限 と し て は 測 定 器 用 の 20-24bit が 実 用 化 さ れ た . 図 9 1 次 Δ Σ ブ ロ ッ ク 図 図 10 MASH ブ ロ ッ ク 図 ( 3 次 )

6.2. 広 帯 域 Δ Σ A/D 変 換 器

デ ジ タ ル 通 信 用 に は 100K~ 10MHz の 帯 域 向 上 が 要 求 さ れ る . SC 回 路 の セ ッ ト リ ン グ で ク ロ ッ ク 周 波 数 が 100MHz 以 下 に 制 限 さ れ る の で , OSR が 10~20 程 度 と 下 が る .低 OSR で も 高 SN を 実 現 す る こ と が 必 要 に な っ た の で , 3~5bit の マ ル チ ビ ッ ト 量 子 化 器 , 同 bit の 帰 還 DA, 精 度 向 上 の た め の Dynamic Element Matching (DEM)技 術 が 開 発 さ れ た .[ 9]6.3. 低 電 圧 動 作 Δ Σ A/D 変 換 器

低 電 圧 動 作 で は 積 分 器 の 出 力 振 幅 特 性 の 緩 和 が 要 求 さ れ , 図 11 に 示 す Feed Forward 型 で 振 幅 抑 圧 回 路 が 提 案 さ れ た . こ の 構 成 で 積 分 器 の 出 力 に は 量 子 化 雑 音 の み が 現 れ る .こ の 構 成 で Vdd=1.2V で , fS=40MS/s, SNDR=89dB, DR=96dB が 実 現 さ れ て い る .[ 1 0 ] 図 11 振 幅 抑 圧 回 路 DS 方 式 AD 変 換 器 Stage1 2b-MDAC with S/HStage2-3 Stage 4-6 Stage7 Vinp

Vinn

2

Digital error correction

2 x 2 3 x 3 3 10 DOUT 2.5b-MDAC 3b-Flash 1.5b-MDAC Stage1 2b-MDAC with S/H

Stage2-3 Stage 4-6 Stage7 Vinp

Vinn

2

Digital error correction

2 x 2 3 x 3 3

10

DOUT 2.5b-MDAC 3b-Flash 1.5b-MDAC

S/H

Nth 1.5b

MDAC

Flash

ADC

Digital Correction

D

OUT1st 1.5b

MDAC

Vin

S/H

Nth 1.5b

MDAC

Digital Correction

D

OUT1st 1.5b

MDAC

S/H

Nth 1.5b

MDAC

Flash

ADC

Digital Correction

D

OUT1st 1.5b

MDAC

Vin

S/H

Nth 1.5b

MDAC

Digital Correction

D

OUT1st 1.5b

MDAC

+VR -VR VO VI +VR -VR VOFS VINFS VDD GND VO(AMP)FS VODx Nn VODx Np(a) Transfer function (b) Output of AMP +VR -VR VO VI +VR -VR VOFS VINFS VDD GND VO(AMP)FS VODx Nn VODx Np

(a) Transfer function (b) Output of AMP

Y(z)=X(z)+(1-z-1)3Q 3 Q Dif z-1 Dif Q Q Int Int Int Dif Ain(X) Dout(Y) Y(z)=X(z)+(1-z-1)3Q 3 Q Dif z-1 Dif Q Q Int Int Int Dif Ain(X) Dout(Y) Q Dif z-1 Dif Q Q Int Int Int Dif Ain(X) Dout(Y)

6.4. 連 続 時 間 (CT)Δ Σ A/D 変 換 器

fS=100MHz 以 上 で は SC フ ィ ル タ 用 の OPA の セ ッ ト リ ン グ 時 間 を 1/2 ク ロ ッ ク 周 期 以 下 に す る に は , 消 費 電 力 が 大 幅 に 増 加 す る . 対 策 と し て 連 続 時 間 (CT)の RC ア ク テ ィ ブ フ ィ ル タ (RCAF), gmC フ ィ ル タ が 使 用 で き る . OTA は 低 電 力 化 が 可 能 で あ る が , 無 帰 還 積 分 器 で あ り , 帰 還 に よ る 精 度 改 善 が で き ず , 寄 生 容 量 に 影 響 さ れ や す い .ま た ,RC 時 定 数 の 偏 差 の 補 正 が 必 要 で あ る .ま た ,CT 型 は ク ロ ッ ク ジ ッ タ に 対 す る 感 度 が 高 い と い う 欠 点 が あ る . ク ロ ッ ク エ ッ ジ か ら の 遅 延 時 間 が Excess Loop Delay (EDL)で あ り , 主 に 量 子 化 器 と DAC の 遅 延 時 間 が 原 因 と な る . ELD が 大 き い と 動 作 の 安 定 性 が 悪 く な り SN 劣 化 や 発 振 が 起 こ る .[1 1 ] CT 型 Δ Σ ADC の ブ ロ ッ ク を 図 12 に 示 す .3 次 の Feed Back 型 ル ー プ フ ィ ル タ で 初 段 は 精 度 と DR が 要 求 さ れ る の で , RCAF, 2,3 段 目 に は gmC を 用 い , 時 定 数 補 正 回 路 を 搭 載 し て い る .量 子 化 器 は 4bit で オ フ セ ッ ト 補 正 と ト ラ キ ン グ 制 御 を 搭 載 し て い る .DAC は 4bit の 電 流 出 力 型 で , バ ッ ク グ ラ ウ ン ド 精 度 補 正 を 搭 載 し て い る . シ ミ ュ レ ー シ ョ ン 設 計 値 で は ,サ ン プ リ ン グ 周 波 数 300MHz, 帯 域 10MHz, SNDR 70dB の 性 能 が 電 源 1.2V, 消 費 電 流 3mA が 得 ら れ て い る . 図 12 CT 型 Δ Σ ADC の ブ ロ ッ ク 図7. 時 間 イ ン タ リ ー ブ (Time domain Interleave)

Flash 方 式 を イ ン タ リ ー ブ し た TI-Flash が 提 案 さ れ た .[ 1 2 ] SA を ベ ー ス に し た TI-SA(1 fs=24GHz)が 出 現 し た .[ 1 3 ] 最 近 の 開 発 例 は 図 13 に 示 す よ う に SA 方 式 AD に 小 面 積 の C-2C ラ ダ ー を 用 い , 16 相 の イ ン タ リ ー ブ で ゲ イ ン と オ フ セ ッ ト の バ ッ ク グ ラ ウ ン ド 補 正 用 に 2 個 の ADC を 追 加 し て い る . 多 層 ク ロ ッ ク の タ イ ミ ン グ も 補 正 し て い る . 45nmCMOS で チ ッ プ 面 積 1mm2,電 源 1.1V, 消 費 電 力 50mW, 分 解 能 7bit, fs=2.5GS/s を 達 成 し て い る .[1 4 ] 図 13 C2C ラ ダ ー を 用 い た TI-SA 方 式 AD 変 換 器[ 14 ]

8. 時 間 情 報 を 利 用 し た AD 変 換 器

係 数 AD 変 換 方 式 は ア ナ ロ グ 電 圧 を パ ル ス 幅 に 変 換 し て カ ウ ン タ で デ ジ タ ル に 変 換 す る 方 式 で あ り , 1970 年 代 か ら あ っ た . 時 間 情 報 は 低 電 圧 の 論 理 回 路 で 処 理 で き , 高 速 化 に 伴 っ て 精 度 が 上 が る の で , 技 術 動 向 に そ っ て い る . こ こ で は ア ナ ロ グ と デ ジ タ ル を 融 合 す る 方 式 に つ い て 述 べ る . 差 分 増 幅 器 (DeltAMP)と ア ナ ロ グ 時 間 デ ジ タ ル 変 換 器 (ATD)を 図 14 に 示 す .DeltaAMP は 前 置 し た 変 調 器 に よ り 入 力 電 圧 の 差 分 を 変 調 増 幅 す る の で , 電 源 電 圧 よ り も 大 き い 振 幅 を 扱 う こ と が で き る .deltaAMP の 出 力 を 2 個 の コ ン パ レ ー タ で レ ベ ル 検 出 し て , そ の タ イ ミ ン グ で 変 調 器 を 切 り 替 え て 信 号 を 折 り 返 す . こ の タ イ ミ ン グ の 時 間 情 報 を カ ウ ン タ で デ ジ タ ル に 変 換 す る も の で あ る .[ 1 5 ] 90nmCMOS テ ス ト チ ッ プ の 実 測 値 は 電 源 電 圧 0.5V.入 力 信 号 100kHz, 入 力 電 圧 2.0Vpp で SNR62dB(信 号 帯 域 120kHz)を 得 ,消 費 電 力 は 150μ W (DeltaAMP: 120μ W, ATC: 30μ W) で あ る . 図 14 DeltAM を 用 い た ア ナ ロ グ 時 間 デ ジ タ ル 変 換 器 (ATD)9. デ ジ タ ル ア シ ス ト 技 術

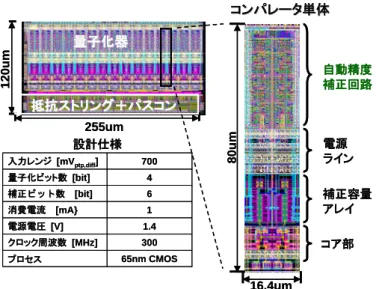

CMOS 技 術 の 進 歩 に よ り ,論 理 回 路 や メ モ リ の 面 積 が 小 さ く な っ た の で , ア ナ ロ グ 荷 重 素 子 の 偏 差 , ア ン プ の 利 得 や セ ッ ト リ ン グ の 不 足 を 許 容 し て , こ れ を デ ジ タ ル 補 正 す る 技 術 が 使 わ れ る よ う に な っ た . 小 面 積 で 高 精 度 を 得 る こ と が で き る .[ 1 6 ] 変 動 に は 製 造 偏 差 (P), 電 源 変 動 (V), 温 度 変 動 (T)に よ る も の が あ る . バ ッ ク グ ラ ウ ン ド 補 正 は 常 時 補 正 し な が ら AD 変 換 す る 方 法 で あ り , こ れ に よ り , PVT が 補 正 で き る . コ ン パ レ ー タ , DAC の 精 度 補 正 に よ く 用 い ら れ て い る . 最 小 サ イ ズ の MOS に よ り ア ナ ロ グ 回 路 の 速 度 ・ 電 力 ・ 面 積 を 低 減 さ せ , 精 度 や 雑 音 の 劣 化 を デ ジ タ ル 補 正 で 補 う こ と で , 従 来 の 回 路 設 計 に 比 べ て , 1 桁 以 上 の 低 電 力 化 が 達 成 さ れ た . 最 小 MOS サ イ ズ の コ ン パ レ ー タ 設 計 例 を 図 15 に 示 す .[ 1 7 ] こ の 補 正 は 処 理 機 能 と 一 体 化 し , ア ナ ロ グ 処 理 と デ ジ タ ル 処 理 を 融 合 さ せ て 実 現 す る の が 効 果 的 で あ る . Amp Vref_H Vref_L Modulator Vin+ Vin-Aout+ Aout- T-F F Vref_L Aout+ Aout-Vref_H Time Vref_L Vref_H Pulse timing AT Cou t ATCout Vin+ Time Vin-Vin+ Time Vin-Folding Control Schematic of DeltAMP A-to-T Converter rise fall C-2C SAADC-0Delay Line Driver

Clock Ain

Dout C-2C SAADC-1

Delay Line Driver

C-2C SAADC-2

Delay Line Driver

C-2C SAADC-17

Delay Line Driver

18個のうち2個は順次バックグラウンド補正

C-2C SAADC-0 Delay Line C-2C SAADC-0 Driver

Delay Line Driver

Clock Ain

Dout C-2C SAADC-1

Delay Line C-2C SAADC-1 Driver

Delay Line Driver

C-2C SAADC-2 Delay Line C-2C SAADC-2 Driver

Delay Line Driver

C-2C SAADC-17 Delay Line C-2C SAADC-17 Driver

Delay Line Driver

18個のうち2個は順次バックグラウンド補正 C1 C1 DAC1 R1 R1 Vinp VIinn DAC2 量子化器(4bit) 15 しきい値 補正 D-FF Delay Clock DAC3 C2 C2 C3 C3 トラッキング 時定数補正 線形性補正 Dout C1 C1 DAC1 R1 R1 Vinp VIinn DAC2 量子化器(4bit) 15 しきい値 補正 D-FF Delay Clock DAC3 C2 C2 C3 C3 トラッキング 時定数補正 線形性補正 Dout

図 15 最 小 MOS と デ ジ タ ル 補 正 を 用 い た 量 子 化 器 図 16. ADC の 先 端 性 能 ( FOM の 評 価 )

10. ま と め

将 来 ADC の 回 路 研 究 は デ バ イ ス 微 細 化 に と も な い , 変 換 効 率 FOM を 尺 度 と し て 各 方 式 が し の ぎ を 削 っ て い る .図 18 に FOM で 評 価 し た ADC の 先 端 性 能 を 示 す .デ バ イ ス の 微 細 化 に 伴 っ て SA 方 式 へ の 回 帰 な 変 換 原 理 の 融 合 , ア ン プ レ ス 低 電 力 技 術 , デ ジ タ ル 補 正 な ど の 回 路 技 術 も 進 歩 し て い る . 謝 辞 ADC の 研 究 開 発 に 協 働 い た だ い き ま し た 大 学 お よ び 企 業 の ア ナ ロ グ 回 路 設 計 者 の 皆 様 に 深 く 感 謝 い た し ま す . 参 考 文 献[1] G. Miller, et. al., An 16b 10us self-calibrating ADC, ISSCC, pp. 168-169, 1990.

[2] V. Giannini, et.al., An 820μW 9b 40MS/s Noise Tolerant Dynamic-SAR ADC in 90nm Digital CMOS,

ISSCC, pp.238-239, 2008.

[3] M. Elzakker, et.al., A 1.9uW 4.4fJ/Conversion-step 10b 1MS/s Charge-Redistribution ADC, ISSCC, pp.244-245, 2008.

[4] K. Kusumoto et. al., A 10-b 20-MHz 30-mW Interpolating CMOS Pipelined ADC, JSSC, Vol.28, No.12, pp.1200-1206, 1993.

[5] A. M. Abo and P. R. Gray, A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter, JSSC, Vol.34, No. 5, pp. 1999.

[6] M. Yoshioka, M. Kudo, K. Gotoh and Y. Watanabe, A 10b 125MS/s 40mW Pipelined ADC in 0.18μm CMOS, ISSCC. #15.4, 2005.

[7] K.Gotoh, H.Ando, A. Iwata, A 10-b 30-MS/s 3.4-mW Pipelined ADC with2.0-Vpp Full-swing Input at a

1.0-V Supply, ASSCC, pp. 57-60, 2008.

[8] Y. Matsuya, et. al., A 16-bit Oversampling Triple Integration Noise Shaping, JSSC, Vol. 22, No. 8, pp. 921-929, 1987.

[9] K. Vleugels, et. al., A 2.5-V Sigma–Delta Modulator for Broadband Communications Applications, JSSC, Vol. 36, No. 12, pp.1887-1898, 2001.

[10] K.Y. Nam et. al., A Low-Voltage Low-Power Sigma-Delta Modulator for Broadband Analog- to-Digital Conversion, JSSC, Vol.40, No.9, pp. 1855-1864, 2005.

[11] S. Yan, E. Sanchez-Sinencio, A continuous-Time ΣΔ modulator with 88 dB dynamic range and 1.1MHz signal bandwidth, ISSCC, pp.62-63, Feb. 2003. [12] Xicheng Jiang, et. al., A 2GS/s 6b ADC in 0.18µm

CMOS, ISSCC, #18.3, 2003.

[13] P. Schvan, et. al. A 24GS/s 6b ADC in 90nm CMOS, ISSCC, #20.3, 2008.

[14] E. Alpman, et. al. A 1.1V 50mW 2.5GS/s 7b Time-Interleaved C-2C SAR ADC in 45nm LP Digital CMOS, ISSCC, pp.76-77, 2009

[15] Y. Masui, T. Yoshida and A. Iwata, A 2.0Vpp Input, 0.5V Supply Delta Amplifier with A-to-D Conversion, ASSCC, pp.265-268, 2008.

[16] G. Van, et al., A 0.16pJ/Conversion-Step 2.5mW 1.25GS/s 4b ADC in a 90nm Digital CMOS Process, ISSCC, pp. 566-567, 2006. [17] 原 田 ,升 井 ,吉 田 ,岩 田 ,デジタル精 度 補 正 回 路 を搭 載 した高 速 ・低 電 力 CMOS 量 子 化 器 , 信 学 技 報 ICD 2008.10 1 消費電流 [mA} 6 補正ビット数 [bit] 65nm CMOS 300 1.4 4 700 プロセス クロック周波数 [MHz] 電源電圧 [V] 量子化ビット数 [bit] 入力レンジ [mVptp,diff] 設計仕様 1 消費電流 [mA} 6 補正ビット数 [bit] 65nm CMOS 300 1.4 4 700 プロセス クロック周波数 [MHz] 電源電圧 [V] 量子化ビット数 [bit] 入力レンジ [mVptp,diff] 設計仕様 1E+0 1E+1 1E+2 1E+3 1E+4 1E+5 1E+6 1E+7 1E+8 1E+9 10 20 30 40 50 60 70 80 90 100 110 120 130 SNDR [dB] Pow e r/ 2 *B W [p J ]

+SA, Flash, xPipe, DS

02 6 76 1 2 2 . . − × × = SNDR BW P FOM FOM=4fJ FOM=40f J FOM=400 fJ FOM=4p J 1E+0 1E+1 1E+2 1E+3 1E+4 1E+5 1E+6 1E+7 1E+8 1E+9 10 20 30 40 50 60 70 80 90 100 110 120 130 SNDR [dB] Pow e r/ 2 *B W [p J ]

+SA, Flash, xPipe, DS

02 6 76 1 2 2 . . − × × = SNDR BW P FOM FOM=4fJ FOM=40f J FOM=400 fJ FOM=4p J 02 6 76 1 2 2 . . − × × = SNDR BW P FOM FOM=4fJ FOM=40f J FOM=400 fJ FOM=4p J 16.4um 80um コンパレータ単体 コンパレータ単体 コア部 自動精度 補正回路 補正容量 アレイ 電源 ライン 255um 120um 抵抗ストリング+パスコン 抵抗ストリング+パスコン 量子化器 量子化器 16.4um 80um コンパレータ単体 コンパレータ単体 コア部 自動精度 補正回路 補正容量 アレイ 電源 ライン 255um 120um 抵抗ストリング+パスコン 抵抗ストリング+パスコン 量子化器 量子化器