Vivado Design Suite

ユーザー

ガ イ ド

プ ログ ラ ムおよびデバ ッ グ

UG908 (v2014.1) 2014 年 5 月 30 日本資料は表記のバージョンの英語版を翻訳したもので、内容に相違が生じる場合には原文を優先します。資料

によっては英語版の更新に対応していないものがあります。日本語版は参考用としてご使用の上、最新情報に

つきましては、必ず最新英語版をご参照ください。

次の表に、 こ の文書の改訂履歴を示 し ます。 日付 バージ ョ ン 改訂内容 2014 年 4 月 23 日 2014.1 次のセ ク シ ョ ンに新 し いセ ク シ ョ ン を追加 : • デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ーム設定の変更 • FPGA デバ イ ス のプ ロ グ ラ ム • 波形ウ ィ ン ド ウ を使用し た ILA プ ローブ データ の表示 • コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ のサポー ト 次のセ ク シ ョ ン を ア ッ プデー ト : • ト リ ガー入力ポー ト および出力ポー ト の イ ネーブル • コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス のプ ロ グ ラ ム • キ ャ プチ ャ ウ ィ ン ド ウ での数値の設定 • 自動再 ト リ ガーの使用 • ラ ボ マシ ンで動作中の リ モー ト ハー ド ウ ェ ア サーバーへの接続 2014 年 5 月 30 日 2014.1 リ ン ク を修正 (内容の変更はな し )

改訂履歴 . . . 2

第 1 章 : 概要

は じ めに . . . 5 デバ ッ グ用語集 . . . 6第 2 章 : デバイ スのプ ログ ラ ム

概要 . . . 7 ビ ッ ト ス ト リ ームの生成 . . . 7 ビ ッ ト ス ト リ ーム フ ァ イ ルのフ ォーマ ッ ト 設定の変更 . . . 8 デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ーム設定の変更 . . . 9 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス のプ ロ グ ラ ム . . . 10 FPGA デバ イ ス のプ ロ グ ラ ム . . . 16 Vivado ハー ド ウ ェ ア マネージ ャーを使用し た FPGA デバ イ ス のプ ロ グ ラ ム . . . 17第 3 章 : デザイ ンのデバ ッ グ

概要 . . . 24 RTL レベル デザ イ ン シ ミ ュ レーシ ョ ン . . . 24 イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン シ ミ ュ レーシ ョ ン . . . 24 イ ン シ ス テ ム ロ ジ ッ ク デザ イ ンのデバ ッ グ . . . 25 イ ン シ ス テ ム シ リ アル I/O デザ イ ンのデバ ッ グ . . . 25第 4 章 : イ ン シス テム ロ ジ ッ ク デザイ ンのデバ ッ グ フ ロー

概要 . . . 26 イ ン シ ス テ ム デバ ッ グ用のデザ イ ンのプ ローブ . . . 26 ネ ッ ト リ ス ト 挿入デバ ッ グ プ ローブ フ ロー . . . 27 HDL イ ン ス タ ンシエーシ ョ ン デバ ッ グ プ ローブ フ ローの概要 . . . 37 HDL イ ン ス タ ンシエーシ ョ ン デバ ッ グ プ ローブ フ ロー . . . 38 デバ ッ グ コ ア を含むデザ イ ンの イ ンプ リ メ ンテーシ ョ ン . . . 42第 5 章 : ハー ド ウ ェ アでのロ ジ ッ ク デザイ ンのデバ ッ グ

概要 . . . 43 Vivado ロ ジ ッ ク 解析を使用し たデザ イ ンのデバ ッ グ . . . 43 ハー ド ウ ェ ア ターゲ ッ ト に接続し て FPGA デバ イ ス をプ ロ グ ラ ム . . . 44 計測のための ILA コ アの設定 . . . 45 ILA プ ローブ情報の記述. . . 60 ILA プ ローブ情報の読み出 し . . . 60 ILA コ アか ら のデータ を波形ビ ューアーで表示. . . 60 ILA コ アでキ ャ プチ ャ さ れたデータ の保存および復元. . . 61 計測のための VIO コ アの設定 . . . 61 VIO コ アのス テータ ス の表示 . . . 63JTAG-to-AXI Master デバ ッ グ コ ア を使用 し たハー ド ウ ェ ア シ ス テ ム通信. . . 68 ラ ボ環境での Vivado ロ ジ ッ ク 解析の使用. . . 71 ハー ド ウ ェ ア マネージ ャ ーの Tcl オブジ ェ ク ト およびコ マン ド . . . 73 Tcl コ マン ド を使用 し た JTAG-to-AXI Master コ アへのア ク セ ス . . . 77 ILA を測定する Tcl コ マン ド の使用 . . . 78

第 6 章 : 波形ウ ィ ン ド ウを使用 し た ILA プ ローブ デー タ の表示

概要 . . . 79 波形 コ ン フ ィ ギ ュ レーシ ョ ンのカ ス タ マ イ ズ . . . 83 オブジ ェ ク ト 名の変更 . . . 86 バ ス の基数 . . . 87 アナ ロ グ波形の表示 . . . 89 ズーム機能 . . . 91第 7 章 : イ ン シス テム シ リ アル I/O デバ ッ グ フ ロー

概要 . . . 92 Vivado IP カ タ ロ グ を使用 し た IBERT コ アの生成 . . . 92 IBERT サンプル デザ イ ンの生成 と イ ンプ リ メ ンテーシ ョ ン . . . 94第 8 章 : ハー ド ウ ェ アでのシ リ アル I/O デザイ ンのデバ ッ グ

概要 . . . 95 Vivado シ リ アル I/O 解析を使用 し たデザ イ ンのデバ ッ グ . . . 95付録 A : デバイ ス コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ーム設定

付録 B : ト リ ガー ス テー ト マシ ンの言語記述

ス テー ト . . . 116 goto ア ク シ ョ ン . . . 116 条件分岐 . . . 117 カ ウ ン タ ー . . . 117 フ ラ グ . . . 118 条件文 . . . 118付録 C : コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ のサポー ト

Artix-7 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス . . . 123 Kintex-7 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス . . . 125 Virtex-7 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス . . . 127 Kintex UltraScale コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス. . . 129 Zynq-7000 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス . . . 131付録 D : その他の リ ソ ースおよび法的通知

ザ イ リ ン ク ス リ ソ ース . . . 133 ソ リ ュ ーシ ョ ン セン ター . . . 133 参考資料 . . . 133 法的通知 . . . 134概要

は じ めに

デザ イ ン を イ ン プ リ メ ン ト し た ら 、FPGA デバ イ ス を プ ロ グ ラ ム し 、 デザ イ ン を イ ン シ ス テ ムでデバ ッ グ し なが ら ハー ド ウ ェ アでデザ イ ン を実行 し ます。FPGA デバ イ ス のプ ロ グ ラ ムおよび イ ン シ ス テ ム デバ ッ グの実行に必要な コ マ ン ド はすべて、Vivado® 統合設計環境 (IDE) の Flow Navigator の [Program and Debug] にあ り ます (図1-1)。 X-Ref Target - Figure 1-1

デバ ッ グ用語集

ILA : ILA (Integrated Logic Analyzer) 機能を使用する と 、 FPGA デバ イ ス の イ ンプ リ メ ン ト 後のデザ イ ン を イ ン シ ス テ

ムでデバ ッ グで き ます。 こ の機能は、 デザ イ ンで信号を監視す る 必要があ る 場合に使用 し ます。 ま た、 ハー ド ウ ェ ア イ ベン ト を ト リ ガー し 、 デー タ を シ ス テ ム速度でキ ャ プチ ャ する ために も 使用で き ます。

ILA コ アは、 RTL コー ド に イ ン ス タ ン シエー ト する か、 Vivado デザ イ ン フ ローの合成後の段階に挿入し ます。 ILA コ アの詳細お よ びその Vivado Design Suite での使用方法は、第4 章お よ び第5 章を参照 し て く だ さ い。ILA コ ア IP の詳 細は、 『LogiCORE IP Integrated Logic Analyzer 製品ガ イ ド 』 (PG172) [参照 12] を参照し て く だ さ い。

VIO : VIO (Virtual Input/Output) は、内部 FPGA 信号を リ アル タ イ ムに監視および駆動で き るデバ ッ グ機能です。 ター

ゲ ッ ト ハー ド ウ ェ アへの物理的なア ク セ ス がない場合は、 こ のデバ ッ グ機能を使用し て、実際のハー ド ウ ェ アにあ る

信号を駆動お よ び監視で き ます。

こ のデバ ッ グ コ アは RTL コー ド に イ ン ス タ ン シエー ト する必要があ る ので、 ど のネ ッ ト を駆動する のか前 も っ て決

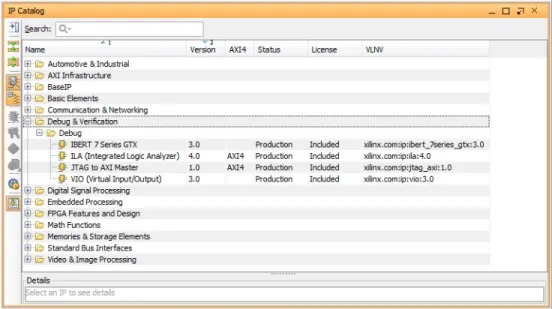

めてお く 必要があ り ます。こ の コ アは IP カ タ ロ グの Debug カテゴ リ に含まれます。VIO コ アの詳細およびその Vivado

Design Suite での使用方法は、第5 章を参照 し て く だ さ い。VIO コ ア IP の詳細は、 『LogiCORE IP Virtual Input/Output 製品ガ イ ド 』 (PG 159) [参照 8] を参照し て く だ さ い。

IBERT : IBERT (Integrated Bit Error Ratio Tester) Serial Analyzer デザ イ ン を使用する と 、 イ ンシ ス テ ム シ リ アル I/O の

検証お よ びデバ ッ グが可能にな り ます。 こ の機能を使用する と 、FPGA ベース シ ス テ ムの高速シ リ アル I/O リ ン ク を

計測お よ び最適化で き ま す。 単純な ク ロ ッ ク や接続の問題か ら 複雑なマージ ン解析お よ びチ ャ ネル最適化の問題 ま で、 さ ま ざ ま な イ ン シ ス テ ム デバ ッ グおよび検証の問題を解決する には、 IBERT Serial Analyzer デザ イ ン を使用する

こ と をお勧め し ます。

IBERT Serial Analyzer デザ イ ンは、 受信信号にレ シーバー イ コ ラ イ ゼーシ ョ ンが適用 さ れた後の信号の質を計測する

ために も 使用で き ます。 こ れに よ り 、TX か ら RX へのチ ャ ネルの最適なポ イ ン ト 、 つま り 実際の正 し いデータ が計

測 さ れ ま す。 こ のデザ イ ン には、IP カ タ ロ グ か ら IBERT コ ア を選択、 設定、 生成 し て、 こ の コ アの [Open Example Design] を選択する と ア ク セ ス で き ます。IBERT コ アの詳細およびその Vivado Design Suite での使用方法は、第7 章お よ び第8 章を参照 し て く だ さ い。 使用可能な さ ま ざ ま な IBERT デザ イ ンの詳細は、 『LogiCORE IP IBERT for 7 Series GTX Transceivers 製品ガ イ ド 』 (PG132) [参照 9]、『LogiCORE IP IBERT for 7 Series GTP Transceivers 製品ガ イ ド 』 (PG133)

[参照 10]、 『LogiCORE IP IBERT for 7 Series GTH Transceivers 製品ガ イ ド 』 (PG152) [参照 11] を参照 し て く だ さ い。

JTAG-to-AXI Master : JTAG-to-AXI Master デバ ッ グ機能は、ハー ド ウ ェ アで動作中の さ ま ざ ま な AXI フルおよび AXI

Lite ス レーブ コ ア と 通信する AXI ト ラ ンザ ク シ ョ ン を生成す る ために使用 さ れます。 AXI ト ラ ンザ ク シ ョ ン を生成

し 、 ラ ン タ イ ムに FPGA 内部で AXI 信号をデバ ッ グおよび駆動する には、 こ の コ ア を使用する こ と をお勧め し ます。

こ の コ アは、 プ ロ セ ッ サのないデザ イ ンでで も 使用で き ます。

こ の コ アは IP カ タ ロ グの Debug カテ ゴ リ に含まれます。JTAG-to-AXI コ アの詳細およびその Vivado Design Suite での 使用方法は、第5 章を参照 し て く だ さ い。JTAG-to-AXI コ アの詳細は、 『LogiCORE IP JTAG to AXI Master v1.0 製品ガ イ ド 』 (PG174) [参照 13] を参照し て く だ さ い。

デバイ スのプ ログ ラ ム

概要

FPGA デバ イ ス でのハー ド ウ ェ アのプ ロ グ ラ ムには、 次の 2 つの段階があ り ます。 1. イ ンプ リ メ ン ト 済みデザ イ ンか ら ビ ッ ト ス ト リ ーム データ プ ロ グ ラ ム フ ァ イ ルを生成 2. ハー ド ウ ェ アに接続 し 、 プ ロ グ ラ ム フ ァ イ ルを ターゲ ッ ト FPGA デバ イ ス にダ ウ ン ロー ド ア ド バン ス ハー ド ウ ェ ア プ ロ グ ラ ムの実行方法に関する詳細は、10 ページの 「コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス のプ ロ グ ラ ム」 を参照 し て く だ さ い。ビ ッ ト ス ト リ ームの生成

ビ ッ ト ス ト リ ーム デー タ フ ァ イ ルを生成する 前に、 ビ ッ ト ス ト リ ーム設定が正 し いか ど う かを確認する こ と が重要 です。 Vivado® IDE では、 次の 2 つのビ ッ ト ス ト リ ーム設定があ り ます。 1. ビ ッ ト ス ト リ ーム フ ァ イ ルのフ ォーマ ッ ト 設定 2. デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン設定Flow Navigator の [Bitstream Settings] を ク リ ッ ク す る か、 [Flow] → [Bitstream Settings] を ク リ ッ ク す る と 、 [Project Settings] ダ イ ア ロ グ ボ ッ ク ス の [Bitstream] ページが開き ます (図2-1)。 ビ ッ ト ス ト リ ーム設定が正し い こ と を確認し た ら 、write_bistream Tcl コ マ ン ド ま たは Flow Navigator の [Generate Bitstream] を使用 し て ビ ッ ト ス ト リ ーム デー タ フ ァ イ ルを生成で き ます。

ビ ッ ト ス ト リ ーム フ ァ イルのフ ォ ーマ ッ ト 設定の

変更

デフ ォル ト では、 write_bistream Tcl コ マン ド でバ イ ナ リ ビ ッ ト ス ト リ ーム フ ァ イ ル (.bit) が生成 さ れます。 生 成 さ れ る フ ァ イ ルの フ ォーマ ッ ト を変更する には、 次のオプシ ョ ン を使用 し ます。 • -raw_bitfile (オプシ ョ ン) : ロー ビ ッ ト フ ァ イ ル (.rbt) を生成し ます。 ロー ビ ッ ト フ ァ イ ルには、 バ イ ナ リ ビ ッ ト ス ト リ ーム フ ァ イ ル と 同 じ 情報が ASCII 形式で含まれます。 出力フ ァ イ ル名は filename.rbt と な り ます。 • -mask_file (オプシ ョ ン) : マ ス ク フ ァ イ ル (.msk) を生成し ます。 マ ス ク フ ァ イ ルには、 ビ ッ ト ス ト リ ーム フ ァ イ ルの コ ン フ ィ ギ ュ レーシ ョ ン データ が含まれる場所を示すマ ス ク データ が含まれます。 こ のフ ァ イ ルは、 検証時に ビ ッ ト ス ト リ ームのど のビ ッ ト を リ ー ド バ ッ ク データ と 比較するべき かを判断する ために使用 し ます。 マ ス ク ビ ッ ト が 0 の場合はそのビ ッ ト はビ ッ ト ス ト リ ーム データ に対 し て検証 さ れ、 マ ス ク ビ ッ ト が 1 の場合 はその ビ ッ ト は検証 さ れません。 出力フ ァ イ ル名は file.msk と な り ます。 • -no_binary_bitfile (オプシ ョ ン) : バ イ ナ リ ビ ッ ト ス ト リ ーム フ ァ イ ル (.bit) を生成し ません。 こ のオプ シ ョ ンは、 バ イ ナ リ ビ ッ ト ス ト リ ーム フ ァ イ ルを生成せずに、 ASCII 形式のビ ッ ト ス ト リ ーム フ ァ イ ルま たは マ ス ク フ ァ イ ルを生成 し た り 、 ビ ッ ト ス ト リ ーム レ ポー ト を生成し た り する場合に使用し ます。• -logic_location_file (オプシ ョ ン) : ラ ッ チ、 フ リ ッ プフ ロ ッ プ、 LUT、 ブ ロ ッ ク RAM、 I/O ブ ロ ッ ク 入力 お よ び出力の ビ ッ ト ス ト リ ーム位置を示す ASCII 形式の ロ ジ ッ ク ロ ケーシ ョ ン フ ァ イ ル (.ll) を生成 し ます。

こ の ロ ケーシ ョ ン フ ァ イ ルではビ ッ ト がフ レームおよびビ ッ ト 番号で示 さ れ、FPGA レ ジ ス タ の内容を調べる の

に役立ち ます。

• -bin_file (オプシ ョ ン) : デバ イ ス プ ロ グ ラ ム データ のみを含むバ イ ナ リ フ ァ イ ル (.bin) を生成し ます。 通

常の ビ ッ ト ス ト リ ーム フ ァ イ ル (.bit) に含まれるヘ ッ ダー情報は含まれません。

X-Ref Target - Figure 2-1

• -reference_bitfile <arg> (オプシ ョ ン) : 参照ビ ッ ト ス ト リ ーム フ ァ イ ルを読み込み、 指定し た参照フ ァ イ ルか ら の変更部分のみを 含む イ ン ク リ メ ン タ ル ビ ッ ト ス ト リ ーム フ ァ イ ル を生成 し ま す。 こ のパーシ ャ ル ビ ッ ト ス ト リ ームは、 既存のデバ イ ス を ア ッ プデー ト さ れたデザ イ ンで イ ン ク リ メ ン タ ルにプ ロ グ ラ ムす る 場合 に使用で き ます。

デバイ ス コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ー

ム設定の変更

デザ イ ン を読み込んだ ら 、[Tools] → [Edit Device Properties] を ク リ ッ ク し て、 [Edit Device Properties] ダ イ ア ロ グ ボ ッ ク ス (図2-2) でプ ロ グ ラ ムおよびコ ン フ ィ ギ ュ レーシ ョ ン プ ロ パテ ィ を編集で き ます。プ ロ パテ ィ の値の上にカー ソ ルを置 く と 、 関連す る 制約のプ ロ パテ ィ 名が表示 さ れ ます。 た と えば、[Enable Bitstream Compression] プ ロ パテ ィ に

関連付け ら れてい る 制約は BITSTREAM.GENERAL.COMPRESS です。 各プ ロパテ ィ の詳細は、付録A 「デバ イ ス コ

ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ーム設定」 を参照 し て く だ さ い。

デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン モー ド の設定に関する詳細は、『Vivado Design Suite ユーザー ガ イ ド : I/O および ク ロ ッ ク の配置』 (UG899) [参照 6] を参照し て く だ さ い。

X-Ref Target - Figure 2-2

重要: プ ロ パテ ィ を編集 し た場合、 [File] → [Save Constraints] を ク リ ッ ク し ない と 制約は保存 さ れ ません。 [File] → [Save Constraints] を ク リ ッ ク する と 、 プ ロ パテ ィ が ターゲ ッ ト 制約フ ァ イ ルに記述 さ れます。 デバ イ ス コ ン フ ィ ギ ュ

レーシ ョ ン プ ロ パテ ィ の変更は、 合成済みデザ イ ンに加え る こ と をお勧め し ます。

次は、 ビ ッ ト ス ト リ ームの圧縮を イ ネーブルにする Tcl コ マン ド の例です。

set_property BITSTREAM.GENERAL.COMPRESS TRUE [get_designs netlist_1]

コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバイ スのプ ログ

ラ ム

Vivado デバ イ ス プ ロ グ ラ マ機能を使用す る と 、 ザ イ リ ン ク ス FPGA デバ イ ス を JTAG を介 し て直接プ ロ グ ラ ムで き ます。Vivado では、 フ ラ ッ シ ュ ベース の コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス を JTAG を介し て間接的にプ ロ グ ラ ムする こ と も で き ます。 こ れには、 まず JTAG と フ ラ ッ シ ュ デバ イ ス イ ン ターフ ェ イ ス の間にデータ パス を供給 す る 特別な コ ン フ ィ ギ ュ レ ーシ ョ ン を使用 し てザ イ リ ン ク ス FPGA デバ イ ス を プ ロ グ ラ ム し 、 そのデー タ パス を使 用 し て コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス の内容をプ ロ グ ラ ム し ます。 Vivado デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン機能を使用する と 、 ザ イ リ ン ク ス FPGA ま たは メ モ リ デバ イ ス をザ イ リ ン ク ス ケーブルま たは Digilent ケーブルを使用 し て直接プ ロ グ ラ ムで き ます。適切な ケーブルの リ ス ト は、18 ページの 「hw_server を使用 し たハー ド ウ ェ ア ターゲ ッ ト への接続」 を参照 し て く だ さ い。 バ ウ ン ダ リ ス キ ャ ン モー ド で実行 する と 、 ザ イ リ ン ク ス FPGA およびコ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス を コ ン フ ィ ギ ュ レーシ ョ ン ま たはプ ロ グ ラ ムで き ます。 Vivado でサポー ト さ れる コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス の リ ス ト は、付録C 「コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ のサポー ト 」 を参照 し て く だ さ い。 Vivado で コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス をプ ロ グ ラ ム し 、 こ のデバ イ ス か ら 起動する には、 次の手順に従 い ます。 1. コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス で使用する ビ ッ ト ス ト リ ーム を生成し ます。 2. コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ フ ァ イ ル (.mcs) を作成し ます。 3. Vivado でハー ド ウ ェ ア ターゲ ッ ト に接続し ます。 4. コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス を追加し ます。 5. Vivado IDE を使用し て コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス をプ ロ グ ラ ム し ます。 6. FPGA デバ イ ス を起動し ます (オプシ ョ ン)。

コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバイ スで使用する ビ ッ ト ス ト

リ ームの生成

合成済みデザ イ ン ま たは イ ンプ リ メ ン ト 済みデザ イ ン を開 き 、[Tools] → [Edit Device Properties] を ク リ ッ ク し て [Edit Device Properties] ダ イ ア ロ グ ボ ッ ク ス を開き ます。

ダ イ ア ロ グ ボ ッ ク ス の左上にあ る検索フ ィ ール ド を使用 し て、すべての SPI ま たは BPI に関連する フ ィ ール ド を検索 し 、 適切なオプシ ョ ン を設定 し ます。 デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン設定の詳細は、付録A 「デバ イ ス コ ン フ ィ

ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ーム設定」 を参照 し て く だ さ い。

X-Ref Target - Figure 2-3

コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ フ ァ イルの作成

.mcs プ ロ グ ラ ム フ ァ イ ルを作成する には、 write_cfgmem Tcl コ マン ド を使用 し ます。 こ のフ ァ イ ルは、 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス のプ ロ グ ラ ムに使用し ます。

た と えば、1 つの 1G ビ ッ ト BPI コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス の .mcs フ ァ イ ルを生成する には、 次の コ マ ン ド を使用 し ます。

write_cfgmem -format mcs -interface bpix16 -size 128 / -loadbit "up 0x0 design.bit"-file design.mcs

注記 : write_cfgmem コ マン ド の -size オプシ ョ ンは メ ガ バ イ ト で指定 し、 メ ガ ビ ッ ト に基づ く フ ラ ッ シ ュ デバ イ ス の容量 と は異な り ます。 そのため上記の write_cfgmem コ マン ド の例では、 1G ビ ッ ト のフ ラ ッ シ ュ デバ イ ス のサ イ ズが 128MB と 指定 さ れてい ます。 write_cfgmem コ マン ド では、 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ フ ァ イ ル のサ イ ズが自動的に ビ ッ ト ス ト リ ームのサ イ ズに設定 さ れます。

Vivado IDE では、 write_cfgmem コ マ ン ド を使用 し て複数の .bit フ ァ イ ルをチ ェーン接続で き ます。 複数のビ ッ ト ス ト リ ーム を含む 1 つの 1G ビ ッ ト BPI コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス の .mcs フ ァ イ ルを生成する に は、 次の コ マ ン ド を使用 し ます。

write_cfgmem -format mcs -interface bpix16 -size 128 /

-loadbit "up 0 design1.bit up 0xFFFFF design2.bit" / -file design1_design2.mcs

write_cfgmem コ マ ン ド の詳細は、 『Vivado Design Suite ユーザー ガ イ ド : Tcl ス ク リ プ ト 機能の使用』 (UG894) [参 照7] を参照 し て く だ さ い。

Vivado でハー ド ウ ェ ア タ ーゲ ッ ト に接続

Vivado でハー ド ウ ェ ア ターゲ ッ ト に接続する には、 次の手順に従い ます。 1. ハー ド ウ ェ ア ターゲ ッ ト の FPGA モー ド ピ ンで、 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス か ら FPGA を コ ン フ ィ ギ ュ レ ーシ ョ ンす る のに適切な コ ン フ ィ ギ ュ レーシ ョ ン モー ド (マ ス タ ー SPI ま たはマ ス タ ー BPI) が選択 さ れてい る こ と を確認 し ます。 詳細は、 タ ーゲ ッ ト デバ イ ス の コ ン フ ィ ギ ュ レーシ ョ ン ユーザー ガ イ ド を参照し て く だ さ い。 2. ハー ド ウ ェ ア ターゲ ッ ト に接続する には、16 ページの 「FPGA デバ イ ス のプ ロ グ ラ ム」 の手順に従い ます。コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバイ スの追加

Vivado デバ イ ス プ ロ グ ラ マでハー ド ウ ェ ア ターゲ ッ ト に コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス を追加する には、 次の手順に従い ます。

1. 前述の手順に従っ てハー ド ウ ェ ア ターゲ ッ ト に接続し た後、 次の図に示すよ う にハー ド ウ ェ ア ターゲ ッ ト を右

ク リ ッ ク し て [Add Configuration Memory Device] を ク リ ッ ク し ます。 X-Ref Target - Figure 2-4

こ の メ ニ ュ ーを ク リ ッ ク する と 、[Add Configuration Memory Device] ダ イ ア ロ グ ボ ッ ク ス が開き ます。

2. 適切な コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス を選択し 、 [OK] を ク リ ッ ク し ます。

ヒ ン ト : [Search] フ ィ ール ド を使用し て、 ベンダー、 集積度、 タ イ プなどで絞 り 込みます。

こ れでハー ド ウ ェ ア ターゲ ッ ト デバ イ ス に コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス が追加 さ れま し た。 X-Ref Target - Figure 2-5

図 2-5 : [Add Configuration Memory Device] ダ イ ア ログ ボ ッ ク スのデバイ ス選択ページ

X-Ref Target - Figure 2-6

コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバイ スのプ ログ ラム

1. コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス を作成する と 、 Vivado デバ イ ス プ ロ グ ラ ムに よ り コ ン フ ィ ギ ュ レー シ ョ ン メ モ リ デバ イ ス をすぐ にプ ロ グ ラ ムする かど う かを確認する メ ッ セージが表示 さ れます。

[OK] を ク リ ッ ク する と 、 [Program Configuration Memory Device] ダ イ ア ロ グ ボ ッ ク ス が開き ます。

2. こ のダ イ ア ロ グ ボ ッ ク ス のすべてのオプシ ョ ン を適切に設定 し ます。 • [Configuration file] : コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス をプ ロ グ ラ ムする のに使用する .mcs フ ァ イ ルを 指定 し ます。 メ モ リ コ ン フ ィ ギ ュ レーシ ョ ン フ ァ イ ルは、 write_cfgmem Tcl コ マン ド で作成し ます。 詳細は、 12 ページの 「コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ フ ァ イ ルの作成」 を参照 し て く だ さ い。 • [Program Operations] : コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス で実行する プ ロ グ ラ ム操作を設定し ます。 ° [Address Range] : プ ロ グ ラ ムする コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス のア ド レ ス範囲を指定し ます。有 効な ア ド レ ス範囲の値は、 次の と お り です。

- [Configuration File Only] : 消去、ブ ラ ン ク チ ェ ッ ク 、プ ロ グ ラ ム、および検証に メ モ リ コ ン フ ィ ギ ュ レー

シ ョ ン フ ァ イ ルで必要なア ド レ ス空間のみを使用 し ます。

- [Entire Configuration Memory Device] : デバ イ ス全体を消去、 ブ ラ ン ク チ ェ ッ ク 、 プ ロ グ ラ ム、 および検 証 し ます。

X-Ref Target - Figure 2-7

図 2-7 : コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバイ ス を プ ログ ラムするかど う かを確認する メ ッ セージ

X-Ref Target - Figure 2-8

• [RS Pins] (オプシ ョ ン) : BPI コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス のみで使用 さ れる リ ビ ジ ョ ン セ レ ク ト ピ ンのマ ッ ピ ン グ を指定 し ます。 フ ラ ッ シ ュ の上位 2 つの FPGA ア ド レ ス ピ ンが FPGA RS[1:0] に接続 さ れます。 こ のオプシ ョ ン を イ ネーブルにす る と 、 プ ロ グ ラ ム用に FPGA RS[1:0] が駆動 さ れます。 アプ リ ケーシ ョ ンの使 用法は、 該当する FPGA コ ン フ ィ ギ ュ レーシ ョ ン ユーザー ガ イ ド を参照し て く だ さ い。 • [Erase] : コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス の内容を消去し ます。 • [Blank Check] : プ ロ グ ラ ムの前に コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス にデータ がない こ と を確認 し ます。 • [Program] : コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス を指定の コ ン フ ィ ギ ュ レーシ ョ ン フ ァ イ ル (.mcs) でプ ロ グ ラ ム し ます。 • [Verify] : プ ロ グ ラ ム後に コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス の内容が コ ン フ ィ ギ ュ レーシ ョ ン フ ァ イ ル (.mcs) に一致する こ と を検証し ます。 3. [OK] を ク リ ッ ク し、コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス に対 し て こ のダ イ ア ロ グ ボ ッ ク ス での選択に応じ て消去、 ブ ラ ン ク チ ェ ッ ク 、 プ ロ グ ラ ム、 および検証操作を実行し ます。 各操作が終了する と 、 それが通知 さ れ ます。

デバイ スの起動

コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス をプ ロ グ ラ ム し た ら 、ソ フ ト ブー ト 操作 (JPROGRAM) を発行し て接続 さ れ た コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ デバ イ ス か ら FPGA コ ン フ ィ ギ ュ レーシ ョ ン を開始で き ます。 ターゲ ッ ト FPGA を起動する には、 タ ーゲ ッ ト デバ イ ス を右 ク リ ッ ク し て [Boot Device] を ク リ ッ ク し ます。FPGA デバイ スのプ ロ グ ラ ム

ビ ッ ト ス ト リ ーム デー タ プ ロ グ ラ ム フ ァ イ ル を生成 し た ら 、 タ ーゲ ッ ト FPGA デバ イ ス にダ ウ ン ロ ー ド し ます。 Vivado には、 イ ン シ ス テ ム デバ イ ス プ ロ グ ラ ミ ン グ機能がビル ト イ ン さ れています。X-Ref Target - Figure 2-9

Vivado ハー ド ウ ェ ア マネージ ャ ーを使用 し た FPGA

デバイ スのプ ロ グ ラ ム

Vivado IDE ツールには、 1 つ以上の FPGA デバ イ ス を含むハー ド ウ ェ アに接続 し、 それ ら の FPGA デバ イ ス をプ ロ グ ラ ム し て、 それ ら の FPGA デバ イ ス にア ク セ ス す る 機能が含ま れてい ます。 ハー ド ウ ェ アへの接続は、 Vivado IDE GUI ま たは Tcl コ マン ド で実行で き ます。 ど ち ら の場合 も 、 ハー ド ウ ェ アに接続し、 ターゲ ッ ト FPGA デバ イ ス をプ ロ グ ラ ムする 手順は同 じ です。 1. ハー ド ウ ェ ア マネージ ャーを開き ます。 2. ホ ス ト コ ン ピ ュ ー タ ー上で稼働中のハー ド ウ ェ ア サーバーで制御 さ れてい る ハー ド ウ ェ ア タ ーゲ ッ ト を開 き ます。 3. ビ ッ ト ス ト リ ーム データ プ ロ グ ラ ム フ ァ イ ルを適切な FPGA デバ イ ス に関連付け ます。 4. プ ロ グ ラ ム フ ァ イ ルをハー ド ウ ェ ア デバ イ ス にプ ロ グ ラ ム (ダ ウ ン ロー ド ) し ます。

ハー ド ウ ェ ア マネージ ャ ーを開 く

デザ イ ン をハー ド ウ ェ アにプ ロ グ ラ ム し た り デバ ッ グする には、 まずハー ド ウ ェ ア マネージ ャーを開き ます。ハー ド ウ ェ ア マネージ ャーを開 く には、 次のいずれかを実行 し ます。• プ ロ ジ ェ ク ト を開いてい る 場合は、Flow Navigator で [Program and Debug] → [Open Hardware Manager] を ク リ ッ ク し ます。

• [Flow] → [Open Hardware Manager] を ク リ ッ ク し ます。 • [Tcl Console] ビ ュー で open_hw コ マン ド を実行し ます。

ハー ド ウ ェ ア タ ーゲ ッ ト 接続を開 く

次に、 ハー ド ウ ェ ア ターゲ ッ ト (1 つ以上の FPGA デバ イ ス で構成 さ れる JTAG チ ェーン を含むハー ド ウ ェ ア ボー ド

な ど) を開き、 ハー ド ウ ェ ア ターゲ ッ ト への接続を制御する ハー ド ウ ェ ア サーバーに接続し ます。 こ れには、 次のい

ずれかを実行 し ます。

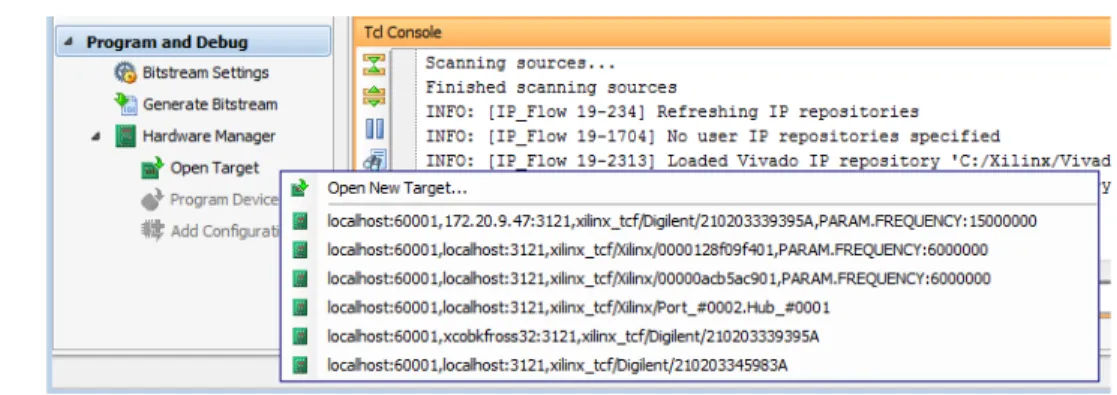

• Flow Navigator で [Program and Debug] → [Hardware Manager] → [Open Target] を ク リ ッ ク し 、 新規ま たは最近の ハー ド ウ ェ ア ターゲ ッ ト を開き ます (図2-10)。

X-Ref Target - Figure 2-10

• Hardware Manager 環境の上部にあ る緑のユーザー アシ ス タ ン ス バナーの [Open recent target] ま たは [Open a new hardware target] を ク リ ッ ク し 、 最近のま たは新規ハー ド ウ ェ ア ターゲ ッ ト を開き ます (図2-11)。 • Tcl コ マン ド を使用し て、 ハー ド ウ ェ ア ターゲ ッ ト への接続を開き ます。

hw_server を使用 し たハー ド ウ ェ ア タ ーゲ ッ ト への接続

hw_server でサポー ト さ れる 互換性のあ る JTAG ダ ウ ン ロー ド ケーブルおよびデバ イ スは、 次の と お り です。 • ザ イ リ ン ク ス プ ラ ッ ト フ ォーム ケーブル USB II (DLC10) • ザ イ リ ン ク ス プ ラ ッ ト フ ォーム ケーブル USB (DLC9G、 DLC9LP、 DLC9) • Digilent 社 JTAG-HS2 • Digilent 社 JTAG-SMT2 • Digilent 社 JTAG-HS1 • Digilent 社 JTAG-SMT1ロ ーカル マシ ン上の ターゲ ッ ト に接続する と 、Vivado に よ り hw_server が自動的に実行 さ れます。hw_server は、

ロ ーカル マシ ン ま たは リ モー ト マシ ン上で手動で実行する こ と も で き ます。 Windows プ ラ ッ ト フ ォーム上の Vivado フル イ ン ス ト ールでは、 コ マン ド プ ロ ンプ ト で次の コ マン ド を実行し ます。 C:\Xilinx\Vivado\<Vivado_version>\bin\hw_server.bat Windows プ ラ ッ ト フ ォーム上の ス タ ン ド ア ロ ンのハー ド ウ ェ ア サーバー イ ン ス ト ールを使用する 場合は、 コ マン ド プ ロ ンプ ト で次の コ マ ン ド を実行 し ます。 c:\Xilinx\HWSRVR\<Vivado_version>\bin\hw_server.bat 次のセ ク シ ョ ンの手順に従っ て、 こ のエージ ェ ン ト を使用 し て新 し いハー ド ウ ェ ア ターゲ ッ ト への接続を開き ます。 X-Ref Target - Figure 2-11

新 し いハー ド ウ ェ ア タ ーゲ ッ ト を開 く

Open New Hardware Target ウ ィ ザー ド では、 ウ ィ ザー ド の指示に従いなが ら 、 ハー ド ウ ェ ア サーバー と ターゲ ッ ト を 接続で き ます。 ウ ィ ザー ド でのプ ロ セ ス は次の と お り です。

1. ハー ド ウ ェ ア ターゲ ッ ト を接続する ローカルま たは リ モー ト サーバーを選択し ます。

• [Local server] : ハー ド ウ ェ ア ターゲ ッ ト を Vivado IDE を実行し てい る マシ ンに接続する 場合に選択し ます (図2-12)。 Vivado に よ り 、 ローカル マシ ン上で Vivado ハー ド ウ ェ ア サーバー (hw_server) および Vivado CSE サーバー (vcse_server) アプ リ ケーシ ョ ンが自動的に開始 さ れます。

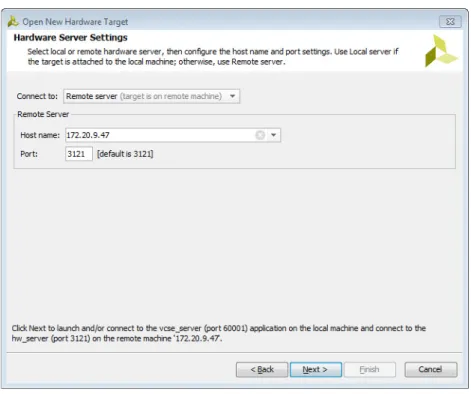

• [Remote server] : ハー ド ウ ェ ア ターゲ ッ ト を Vivado IDE を実行し てい る マシ ン と は異な る マシ ンに接続する場合

に選択 し ま す。 リ モー ト マシ ンのホ ス ト 名ま たは IP ア ド レ ス と 、 そのマシ ン上で実行中のハー ド ウ ェ ア サー

バー (hw_server) アプ リ ケーシ ョ ンのポー ト 番号を指定 し ます (図2-13)。 Vivado に よ り 、 ローカル マシ ン上で

Vivado CSE サーバー (vcse_server) が自動的に開始 さ れます。 リ モー ト デバ ッ グの詳細は、第5 章の 「 ラ ボ

マシ ンで動作中の hw_server サーバーへの接続」 を参照 し て く だ さ い。

重要: リ モー ト サーバーを使用する場合は、 ハー ド ウ ェ ア サーバーに接続する のに使用する Vivado のバージ ョ ン と

同 じ かそれ以降のバージ ョ ン の Vivado ハー ド ウ ェ ア サーバー (hw_server) アプ リ ケーシ ョ ン を手動で開始す る 必 要があ り ます。

ヒ ン ト : ラ ボ マシンに リ モー ト で接続する場合は、その リ モー ト マシン上に Vivado Design Suite のフル バージ ョ ン を イ ン ス ト ールする 必要はあ り ません。 軽量の Vivado ハー ド ウ ェ ア サーバー (ス タ ン ド ア ロ ン) ツールを イ ン ス ト ール で き ます。

X-Ref Target - Figure 2-12

2. ハー ド ウ ェ ア サーバーで制御 さ れてい る ターゲ ッ ト の リ ス ト か ら 、 適切なハー ド ウ ェ ア ターゲ ッ ト を選択し ま す。 タ ーゲ ッ ト を選択す る と 、 そのハー ド ウ ェ ア タ ーゲ ッ ト で使用可能なハー ド ウ ェ ア デバ イ ス が表示 さ れま す (図2-14)。

X-Ref Target - Figure 2-13

図 2-13 : リ モー ト ハー ド ウ ェ ア サーバーの使用

X-Ref Target - Figure 2-14

ハー ド ウ ェ ア タ ーゲ ッ ト の ト ラ ブルシ ュ ーテ ィ ング

ハー ド ウ ェ ア ターゲ ッ ト に接続する際に問題が発生する こ と があ り ます。次に、 よ く 発生する問題 と それ ら を解決す る のに推奨 さ れ る 方法を示 し ます。 • タ ーゲ ッ ト 上のハー ド ウ ェ ア デバ イ ス を正 し く 特定で き ない場合は、ハー ド ウ ェ アがデフ ォ ル ト の ターゲ ッ ト 周 波数で動作で き ない可能性があ り ます。 ハー ド ウ ェ ア ターゲ ッ ト ま たはケーブルの TCK ピ ンの周波数を調整で き ます (図2-14)。ハー ド ウ ェ ア ターゲ ッ ト の各 タ イ プでプ ロパテ ィ が異な る こ と があ り ます。プ ロ パテ ィ の詳細 は、 各ハー ド ウ ェ ア ターゲ ッ ト の資料を参照 し て く だ さ い。• Vivado ハー ド ウ ェ ア サーバーに よ り JTAG チ ェーンに含まれるすべてのデバ イ ス の命令レ ジ ス タ (IR) 長の自動

的な検出が試み ら れ ますが、 まれに正 し く 検出で き ない こ と があ り ます。 不明なデバ イ ス の IR 長をチ ェ ッ ク し

て、 正 し い こ と を確認 し て く だ さ い。IR 長を指定する必要があ る場合は、 Vivado で未知のデバ イ ス があ る場合、

Open New Hardware Target ウ ィ ザー ド の [Hardware Devices] の表に直接入力で き ます (図2-14)。

最近開いたハー ド ウ ェ ア タ ーゲ ッ ト を開 く

Open New Hardware Target ウ ィ ザー ド では、前に接続し たハー ド ウ ェ ア ターゲ ッ ト の リ ス ト も生成 さ れます。ウ ィ ザー ド を使用 し てハー ド ウ ェ ア タ ーゲ ッ ト に接続 し な く て も 、 Hardware Manager 環境で [Open recent target] リ ン ク を ク

リ ッ ク し 、 リ ス ト か ら 最近接続 し たハー ド ウ ェ ア サーバー/ターゲ ッ ト の組み合わせを選択する と 、前に接続し たハー

ド ウ ェ ア タ ーゲ ッ ト への接続を再開で き ま す。 こ の最近使用 さ れた タ ーゲ ッ ト の リ ス ト には、 Vivado IDE の Flow Navigator の [Program and Debug] → [Hardware Manager] → [Open Target] か ら も ア ク セ ス で き ます。

Tcl コ マ ン ド を使用 し てハー ド ウ ェ ア タ ーゲ ッ ト を開 く

Tcl コ マン ド を使用し て、 ハー ド ウ ェ ア サーバー /ターゲ ッ ト に接続する こ と も 可能です。 た と えば、 localhost 3121 で 実行中の hw_server (お よ び localhost ポー ト 60001 で実行中の vcse_server) で制御 さ れ る digilent_plugin タ ー ゲ ッ ト (シ リ アル番号 210203339395A) に接続する には、 次の Tcl コ マン ド を使用し ます。

connect_hw_server -host localhost -port 60001 -url localhost:3121 current_hw_target [get_hw_targets */xilinx_tcf/Digilent/210203339395A] set_property PARAM.FREQUENCY 15000000 [get_hw_targets

*/xilinx_tcf/Digilent/210203339395A] open_hw_target

ハー ド ウ ェ ア ターゲ ッ ト への接続を開 く と 、 [Hardware] ビ ューにハー ド ウ ェ ア サーバー、 ハー ド ウ ェ ア ターゲ ッ ト 、 お よ び開いてい る タ ーゲ ッ ト 用の さ ま ざ ま なハー ド ウ ェ ア デバ イ ス が表示 さ れます (図2-15)。

X-Ref Target - Figure 2-15

プ ログ ラ ム フ ァ イルをハー ド ウ ェ ア デバイ スに関連付け

ハー ド ウ ェ ア タ ーゲ ッ ト に接続 し た ら 、 FPGA デバ イ ス をプ ロ グ ラ ムする前に、 ビ ッ ト ス ト リ ーム デー タ プ ロ グ ラ ム フ ァ イ ル を デ バ イ ス に 関連付 け る 必要 が あ り ま す。 [Hardware] ビ ュ ー で ハー ド ウ ェ ア デバ イ ス を 選択 し、 [Properties] ビ ューで [Programming File] プ ロ パテ ィ が適切な ビ ッ ト ス ト リ ーム デー タ フ ァ イ ル (.bit) に設定 さ れて い る こ と を確認 し ます。

注記 : Vivado IDE では、 開いてい る ハー ド ウ ェ ア タ ーゲ ッ ト の最初のデバ イ ス の [Programming File] プ ロ パテ ィ 値 と し て、 現在の イ ンプ リ メ ン ト 済みデザ イ ンの .bit フ ァ イ ルが自動的に使用 さ れます。 こ の機能は、 Vivado IDE をプ

ロ ジ ェ ク ト モー ド で使用し た場合にのみ使用で き ます。 Vivado IDE を非プ ロ ジ ェ ク ト モー ド で使用する場合は、 こ

のプ ロ パテ ィ を手動で設定する 必要があ り ます。

ま た、set_property Tcl コ マン ド を使用し て、ハー ド ウ ェ ア デバ イ スの PROGRAM.FILE プ ロパテ ィ を設定で き ます。 set_property PROGRAM.FILE {C:/design.bit} [lindex [get_hw_devices] 0]

ハー ド ウ ェ ア デバイ スのプ ログ ラム

プ ロ グ ラ ム フ ァ イ ル を ハー ド ウ ェ ア デバ イ ス に関連付け た ら 、 [Hardware] ビ ュ ーでデバ イ ス を 右 ク リ ッ ク し、 [Program Device] を ク リ ッ ク し て、 ハー ド ウ ェ ア デバ イ ス をプ ロ グ ラ ム し ます。 program_hw_device Tcl コ マン ド

で も 同 じ 操作を実行で き ます。 た と えば、JTAG チ ェーンの最初のデバ イ ス をプ ロ グ ラ ムする には、 次の Tcl コ マン

ド を使用 し ます。

program_hw_devices [lindex [get_hw_devices] 0]

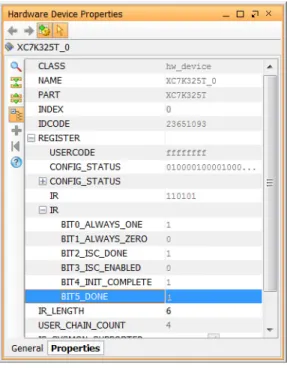

進捗状況 イ ン ジ ケ ー タ ーで プ ロ グ ラ ム が 100% 完了 し た こ と が示 さ れ た ら 、 プ ロ グ ラ ム が正常に完了 し た か を [Hardware Device Properties] ビ ュ ーの DONE の ス テータ ス で確認で き ます (図2-16)。

DONE の ス テータ ス は、 get_property Tcl コ マン ド で も 確認で き ます。 た と えば、 JTAG チ ェーンの最初のデバ イ ス であ る Kintex®-7 デバ イ ス の DONE ス テータ ス を確認する には、 次の Tcl コ マン ド を使用 し ます。

get_property REGISTER.IR.BIT5_DONE [lindex [get_hw_devices] 0] X-Ref Target - Figure 2-16

フ ラ ッ シ ュ デバ イ ス を使用 し た り 、 iMPACT ツールな どの外部デバ イ ス プ ロ グ ラ ム ツールを使用する な ど、 別の方 法でハー ド ウ ェ ア デバ イ ス をプ ロ グ ラ ム し た場合は、 ハー ド ウ ェ ア デバ イ ス を右 ク リ ッ ク し て [Refresh Device] を ク リ ッ ク する か、 refresh_hw_device Tcl コ マン ド を実行する と 、 ハー ド ウ ェ ア デバ イ ス の ス テータ ス を更新で き ま す。 こ れに よ り 、DONE ス テータ ス だけでな く 、 デバ イ ス の さ ま ざ ま なプ ロ パテ ィ が更新 さ れます。

ハー ド ウ ェ ア タ ーゲ ッ ト を閉 じ る

ハー ド ウ ェ ア ターゲ ッ ト を閉 じ る には、 [Hardware] ビ ュ ーでハー ド ウ ェ ア ターゲ ッ ト を右 ク リ ッ ク し、 [Close Target] を ク リ ッ ク し ます。Tcl コ マン ド で も 同じ 操作を実行で き ます。 た と えば、 localhost サーバー上の xilinx_platformusb/USB21 ターゲ ッ ト を閉じ る には、 次の Tcl コ マン ド を使用し ます。 close_hw_target {localhost/xilinx_tcf/Digilent/210203339395A}

ハー ド ウ ェ ア サーバーへの接続を閉 じ る

ハー ド ウ ェ ア サーバーへの接続を閉 じ る には、 [Hardware] ビ ュ ーでハー ド ウ ェ ア サーバーを右 ク リ ッ ク し、 [Close Server] を ク リ ッ ク し ます。 Tcl コ マン ド で も 同 じ 操作を実行で き ます。 た と えば、 localhost サーバーへの接続を閉じ る には、 次の Tcl コ マン ド を使用し ます。 disconnect_hw_server localhost第 3 章

デザイ ンのデバ ッ グ

概要

FPGA デザ イ ンのデバ ッ グは複数の段階を含む反復作業です。 複雑な問題を処理する 場合 と 同様に、 FPGA デザ イ ン のデバ ッ グ プ ロ セ ス も 、一度にデザ イ ン全体を処理する のではな く 、細分化し てセ ク シ ョ ン ご と に集中し て作業する のがベス ト です。1 回に 1 モジ ュールを追加 し なが ら デザ イ ン フ ローを反復 し、 デザ イ ン全体の中でそれを正し く 機 能 さ せる よ う にする のが、 実績のあ る デザ イ ンお よ びデバ ッ グ手法の 1 つです。 こ の手法は、 デザ イ ン フ ローの次の 段階で使用で き ます。 • RTL レベル デザ イ ン シ ミ ュ レーシ ョ ン • イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン シ ミ ュ レーシ ョ ン • イ ン シ ス テ ム デバ ッ グRTL レ ベル デザイ ン シ ミ ュ レ ーシ ョ ン

シ ミ ュ レーシ ョ ン検証プ ロ セ ス中にデザ イ ンの機能をデバ ッ グで き ます。ザ イ リ ン ク ス の Vivado® IDE では、 フル デ ザ イ ン シ ミ ュ レーシ ョ ン機能が提供 さ れてい ます。 デザ イ ンの RTL シ ミ ュ レーシ ョ ン を実行する には、 Vivado デザ イ ン シ ミ ュ レータ を使用で き ます。 RTL レベル シ ミ ュ レーシ ョ ン環境でデザ イ ン デバ ッ グ を実行する と 、 デザ イ ン 全体を完全に表示で き 、 デザ イ ン/デバ ッ グ サ イ ク ルをすばや く 反復実行で き る な ど の利点があ り ますが、 大型デザ イ ン を妥当な時間内にシ ミ ュ レーシ ョ ン し た り 、 実際のシ ス テ ム環境を正確にシ ミ ュ レーシ ョ ンす る のが困難であ る な ど の制限があ り ます。Vivado シ ミ ュ レータ の使用については、 『Vivado Design Suite ユーザー ガ イ ド : ロ ジ ッ ク シミ ュ レーシ ョ ン』 (UG900) [参照 1] を参照し て く だ さ い。

イ ン プ リ メ ン テーシ ョ ン後のデザイ ン シ ミ ュ レー

シ ョ ン

Vivado シ ミ ュ レータ は、 イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン シ ミ ュ レーシ ョ ンに も 使用で き ます。 Vivado シ ミ ュ レー タ を使用 し て イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン をデバ ッ グする と 、 デザ イ ンの タ イ ミ ン グ精度の高いモデル を使用で き る な ど の利点があ り ますが、 前のセ ク シ ョ ンで述べた よ う に、 ラ ン タ イ ムが長い こ と や、 シ ス テ ム モデル での正確 さ な ど の制限があ り ます。イ ン シ ス テム ロ ジ ッ ク デザイ ンのデバ ッ グ

Vivado IDE には、 イ ンプ リ メ ン テーシ ョ ン後の FPGA デザ イ ン を イ ン シ ス テ ムでデバ ッ グで き る ロ ジ ッ ク 解析機能 も あ り ます。 イ ン シ ス テ ムでのデザ イ ンのデバ ッ グには、 イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン を、 実際のシ ス テ ム環 境で、 シ ス テ ム ス ピー ド で、 タ イ ミ ン グ精度の高いデバ ッ グ を実行で き る と い う 利点があ り ますが、 シ ミ ュ レーシ ョ ン モデルを使用 し た場合に比べてデバ ッ グ信号を確認 し づ ら い、 デザ イ ンのサ イ ズや複雑 さ に よ っ てはデザ イ ン/イ ンプ リ メ ン テーシ ョ ン/デバ ッ グの反復実行の ラ ン タ イ ムが長 く な る可能性があ る な どの制限があ り ます。 Vivado ツールでは複数のデバ ッ グ方法が提供 さ れてい る ので、 ニーズに応じ た方法でデザ イ ン をデバ ッ グで き ます。 Vivado IDE の イ ンシ ス テ ム ロ ジ ッ ク デバ ッ グ機能については、第4 章 「 イ ンシ ス テ ム ロ ジ ッ ク デザ イ ンのデバ ッ グ フ ロ ー」 で説明 し ます。

イ ン シ ス テム シ リ アル I/O デザイ ンのデバ ッ グ

イ ン シ ス テ ム シ リ アル I/O の検証およびデバ ッ グ を可能にする ため、 Vivado IDE にはシ リ アル I/O 解析機能が含まれ

てい ます。 こ の機能を使用す る と 、FPGA ベース シ ス テ ムの高速シ リ アル I/O リ ン ク を計測およ び最適化で き ます。 Vivado シ リ アル I/O 解析機能は、 単純な ク ロ ッ ク や接続の問題か ら 複雑なマージ ン解析およびチ ャ ネル最適化の問題 ま で、 さ ま ざ ま な イ ン シ ス テ ム デバ ッ グおよび検証の問題を解決する ために使用で き ます。 Vivado シ リ アル I/O 解析 機能を使用する と 、 ほかの外部装置を使用す る の と 比較 し て、受信信号に レ シーバー イ コ ラ イ ゼーシ ョ ンが適用 さ れ た後の信号の質が計測 さ れ る と い う 利点があ り ます。 こ れに よ り 、TX か ら RX へのチ ャ ネルの最適なポ イ ン ト 、 つ ま り 実際の正 し いデー タ が計測 さ れます。 Vivado ツールでは、 ギガ ビ ッ ト ト ラ ン シーバー エン ド ポ イ ン ト を実行する ために使用 さ れる デザ イ ンお よびラ ン タ イ ム ソ フ ト ウ ェ ア を生成で き、 高速シ リ アル I/O チ ャ ネルを計測 し、 最適化する のに利用で き ます。 IBERT デザ イ ン を生成す る 方法は、第7 章 「 イ ン シ ス テ ム シ リ アル I/O デバ ッ グ フ ロ ー」 を参照 し て く だ さ い。 ラ ン タ イ ム Vivado シ リ アル I/O 解析機能の使用方法は、第8 章 「ハー ド ウ ェ アでのシ リ アル I/O デザ イ ンのデバ ッ グ」 を参照 し て く だ さ い。

第 4 章

イ ン システム ロ ジ ッ ク デザイ ンのデバ ッ グ

フ ロー

概要

Vivado® ツールには、 実際のハー ド エア デバ イ ス上でデザ イ ンの イ ン シ ス テ ム デバ ッ グ を実行する 機能が多数含ま れてい ます。 イ ン シ ス テ ム デバ ッ グ フ ローには、 次の 3 つの段階があ り ます。 1. プ ロ ーブ : デザ イ ンでプ ローブする信号を特定し 、 プ ローブ方法を指定し ます。 2. イ ンプ リ メ ンテーシ ョ ン : プローブする ネ ッ ト に追加さ れたデバ ッ グ IP を含むデザイ ンを イ ンプ リ メ ン ト し ます。 3. 解析 : デザ イ ンに含まれ るデバ ッ グ IP にア ク セ ス し 、 機能的な問題をデバ ッ グおよび検証し ます。 こ の イ ン シ ス テ ム デバ ッ グ フ ローは、前のセ ク シ ョ ンで説明 し た反復デザ イ ン/デバ ッ グ フ ローを使用する こ と を意 図 し てい ます。 イ ン シ ス テ ム デバ ッ グ フ ローを使用する場合は、 デザ イ ン サ イ ク ルので き る だけ早い段階で、 デザ イ ンの一部がハー ド ウ ェ アで機能す る よ う にす る こ と をお勧め し ます。 こ の章では、 イ ン シ ス テ ム デバ ッ グ フ ロー の 3 つの段階を説明 し、 Vivado ロ ジ ッ ク デバ ッ グ機能を使用 し てデザ イ ンがハー ド ウ ェ ア上で機能する よ う にす る 方法を示 し ます。イ ン シ ス テム デバ ッ グ用のデザイ ンのプ ローブ

イ ン シ ス テ ム デバ ッ グ フ ローのプ ローブ段階には、 次の 2 つの段階があ り ます。 1. プ ロ ーブする 信号ま たはネ ッ ト を特定 2. デザ イ ンにデバ ッ グ コ ア を追加する方法を決定 多 く の場合、 プ ロ ーブす る 信号お よ びそのプ ロ ーブ方法は、 ほかの信号のプ ロ ーブに影響 し ます。 ま ず、 デザ イ ン ソ ース コ ー ド にデバ ッ グ IP コ ンポーネ ン ト イ ン ス タ ン ス を手動で追加する か (HDL イ ン ス タ ン シエーシ ョ ン プ ロー ブ フ ロー )、 合成済みネ ッ ト リ ス ト に Vivado ツールで自動的にデバ ッ グ コ アが追加 さ れる よ う にする か (ネ ッ ト リ ス ト 挿入プ ロ ーブ フ ロー ) を決定する と 有益です。表4-1 に、 異な るデバ ッ グ方法の利点 と 欠点を示 し ます。ネ ッ ト リ ス ト 挿入デバ ッ グ プ ローブ フ ロー

Vivado ツールでデバ ッ グ コ ア を挿入する方法は、 さ ま ざ ま なニーズに対応で き る よ う 複数あ り ます。

• シ ンプルな ウ ィ ザー ド を使用 し 、 デバ ッ グする ネ ッ ト に基づいて、ILA (Integrated Logic Analyzer) コ ア を自動的 に生成お よ び設定 し ます。 こ れが一番簡単な方法です。

• [Debug] ビ ューを使用し て、 個々の コ ア、 ポー ト 、 およびパ ラ メ ーターを設定し ます。 [Debug] ビ ュ ーは、 合成済

みデザ イ ン を 開い た状態で レ イ ア ウ ト セ レ ク タ ーで [Debug] を選択、 [Layout] → [Debug] を ク リ ッ ク 、 ま たは [Windows] → [Debug] を ク リ ッ ク する と 表示 さ れます。

• Tcl の XDC デバ ッ グ コ マン ド のセ ッ ト を手動で XDC 制約フ ァ イ ルに入力する か、 Tcl ス ク リ プ ト を作成 し ます。

こ れ ら の方法を組み合わせて利用 し 、 デバ ッ グ コ ア を挿入およびカ ス タ マ イ ズする こ と も で き ます。

デバ ッ グする HDL 信号のマー ク

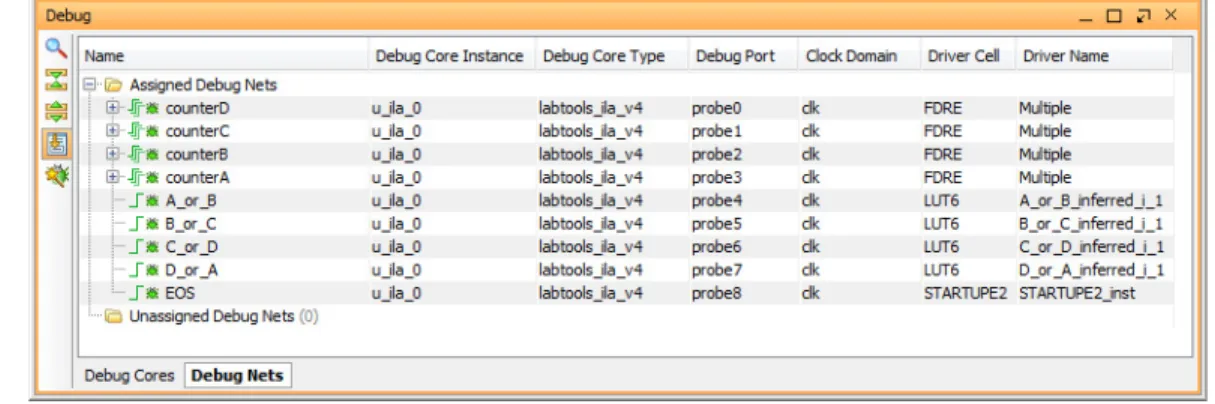

合成の前に HDL ソ ース レベルでデバ ッ グする 信号を特定する には、mark_debug 制約を使用し ます。HDL でデバ ッ グ用にマー ク さ れた信号に対応する ネ ッ ト が、[Debug] ビ ューの [Unassigned Debug Nets] の下に表示 さ れます。 注記 : [Debug] ビ ューの [Debug Nets] タ ブはデバ ッ グに選択し たネ ッ ト のネ ッ ト 中心の表示で、 [Debug Cores] タ ブは コ ア プ ロ パテ ィ を表示および設定可能な コ ア中心の表示です。

デバ ッ グ用にネ ッ ト を マー ク する 方法は、 プ ロ ジ ェ ク ト が RTL ソ ース ベース であ る か合成済みネ ッ ト リ ス ト ベース

であ る かに よ っ て異な り ます。RTL ネ ッ ト リ ス ト ベース のプ ロ ジ ェ ク ト の場合は、 次の方法を使用し ます。

• Vivado 合成を使用する場合、 VHDL および Verilog ソ ース フ ァ イ ルで mark_debug 制約を使用し てデバ ッ グ用

のネ ッ ト を マー ク で き ます。 mark_debug 制約に有効な値は、 TRUE ま たは FALSE です。 Vivado 合成では、 こ

の制約の値を SOFT に設定する こ と はで き ません。

• XST (Xilinx Synthesis Technology) を使用する場合、 VHDL および Verilog ソ ース フ ァ イ ルで mark_debug 制約を 使用 し てデバ ッ グ用のネ ッ ト を マー ク で き ます。有効な値は TRUE ま たは FALSE だけでな く 、SOFT に設定し て 指定ネ ッ ト を最適化で き ます。 表 4-1 : デバ ッ グ ス ト ラ テ ジ デバ ッ グ目標 推奨デバ ッ グ プ ログ ラム フ ロー HDL ソ ー ス コ ー ド でデバ ッ グ信号 を 特定 し 、 フ ロ ーの後の方でデバ ッ グ を イ ネーブル/デ ィ ス エーブルにで き る よ う にす る • mark_debug プ ロ パテ ィ を使用し て、HDL でデバ ッ グ用の信号に タ グ を付け る • Set Up Debug ウ ィ ザー ド を使用し て、 ネ ッ ト リ ス ト 挿入プ ローブ フ ロ ーを実行する HDL ソ ース コー ド を変更せずに、合成 済みデザ イ ン ネ ッ ト リ ス ト でデバ ッ グ ネ ッ ト を特定す る • 合成済みデザ イ ン ネ ッ ト リ ス ト でネ ッ ト を右 ク リ ッ ク し て [Mark Debug] を ク リ ッ ク し 、 デバ ッ グする ネ ッ ト を選択する • Set Up Debug ウ ィ ザー ド を使用し て、 ネ ッ ト リ ス ト 挿入プ ローブ フ ロ ーを実行する Tcl コ マン ド を使用 し てデバ ッ グ プ ロ ーブ フ ローを自動化する • set_property Tcl コ マン ド を使用し 、 デバ ッ グする ネ ッ ト に mark_debug プ ロ パテ ィ を設定する • ネ ッ ト リ ス ト 挿入プ ローブ フ ロー用の Tcl コ マン ド を使用 し、 デバ ッ グ コ ア を作成 し てデバ ッ グ ネ ッ ト に接続する HDL ソ ース で ILA デバ ッ グ コ ア イ ン ス タ ン ス に信号を接続す る • デバ ッ グする HDL 信号を特定する • HDL イ ン ス タ ン シエーシ ョ ン プ ローブ フ ローを使用し 、 ILA (Integrated Logic Analyzer) コ ア を生成 し て イ ン ス タ ンシエー ト し、 デザ イ ンのデバ ッ グ信号に接続する

合成済みネ ッ ト リ ス ト ベース のプ ロ ジ ェ ク ト の場合は、 次の方法を使用 し ます。

• Synopsis® 社の Synplify® 合成ツールを使用する場合、 VHDL ま たは Verilog で mark_debug および syn_keep 制約を使用す る か、SDC (Synopsys Design Constraints) フ ァ イ ルで mark_debug 制約を使用 し て、 デバ ッ グ用に ネ ッ ト を マー ク で き ます。Synplify では SOFT 値はサポー ト さ れません。 こ れは、 こ の動作が syn_keep 制約で 制御 さ れ る ためです。

• Mentor Graphics® 社の Precision® 合成ツールを使用する 場合、 VHDL ま たは Verilog で mark_debug 制約を使用 し てデバ ッ グ用にネ ッ ト を マー ク で き ます。

次のセ ク シ ョ ンに、Vivado 合成、 XST、 Synplify、 および Precision ソ ース フ ァ イ ルの構文例を示し ます。

Vivado 合成での mark_debug の構文例

次に、Vivado 合成を使用する場合の VHDL および Verilog の構文例を示し ます。

• VHDL の構文例

attribute mark_debug : string;

attribute mark_debug of char_fifo_dout: signal is "true";

• Verilog の構文例

(* mark_debug = "true" *) wire [7:0] char_fifo_dout;

XST での mark_debug の構文例

次に、XST を使用する 場合の VHDL および Verilog の構文例を示 し ます。

• VHDL の構文例

attribute mark_debug : string;

attribute mark_debug of char_fifo_dout: signal is "true";

• Verilog の構文例

(* mark_debug = "true" *) wire [7:0] char_fifo_dout;

Synplify での mark_debug の構文例

次に、Synplify を使用する場合の VHDL、 Verilog、 SDC の構文例を示し ます。

• VHDL の構文例

attribute syn_keep : boolean; attribute mark_debug : string;

attribute syn_keep of char_fifo_dout: signal is true; attribute mark_debug of char_fifo_dout: signal is "true";

• Verilog の構文例

(* syn_keep = "true", mark_debug = "true" *) wire [7:0] char_fifo_dout;

• SDC の構文例

define_attribute {n:char_fifo_din[*]} {mark_debug} {"true"} define_attribute {n:char_fifo_din[*]} {syn_keep} {"true"}

重要: SDC ソースのネ ッ ト 名には、 接頭辞 と し て n: を付け る必要があ り ます。

注記 : SDC (Synopsys Design Constraints) は、 特に タ イ ミ ン グ解析において設計の要件を ツールに渡すための業界標準 です。 SDC 仕様の リ フ ァ レ ン ス コ ピーは、 次の Synopsys 社のサ イ ト か ら 登録をする と 入手で き ます。

Precision での mark_debug の構文例

次に、Precision を使用する場合の VHDL、 Verilog、 XCF の構文例を示し ます。

• VHDL の構文例

attribute mark_debug : string;

attribute mark_debug of char_fifo_dout: signal is "true";

• Verilog の構文例

(* mark_debug = "true" *) wire [7:0] char_fifo_dout;

デザイ ンの合成

次に、Vivado IDE で [Run Synthesis] を ク リ ッ ク する か、 次の Tcl コ マン ド を使用し て、 デバ ッ グ コ ア を含むデザ イ ン を合成 し ます。

launch_runs synth_1 wait_on_run synth_1

synth_design Tcl コ マ ン ド を使用 し てデザ イ ン を合成す る こ と も で き ま す。 デザ イ ン の さ ま ざ ま な合成方法は、 『Vivado Design Suite ユーザー ガ イ ド : 合成』 (UG901) [参照 2] を参照し て く だ さ い。

合成済みデザイ ン でデバ ッ グ用のネ ッ ト を マー ク

Flow Navigator で [Open Synthesized Design] を ク リ ッ ク し て合成済みデザ イ ン を開き、 [Debug] レ イ ア ウ ト を選択し て [Debug] ビ ューを表示し ます。 デバ ッ グ用にマー ク し た HDL 信号に対応する ネ ッ ト が、 [Debug] ビ ューの [Unassigned Debug Nets] フ ォ ルダーの下に表示 さ れます (図4-1)。

• [Netlist]、 [Schematic] な どの任意のビ ューでネ ッ ト を右 ク リ ッ ク し 、 [Mark Debug] を ク リ ッ ク し ます。

• 任意の ビ ュ ーでネ ッ ト を選択 し 、[Debug] ビ ューの [Unassigned Debug Nets] フ ォルダーに ド ラ ッ グ ア ン ド ド ロ ッ プ し ます。

• Set Up Debug ウ ィ ザー ド でネ ッ ト を選択 し ます。 詳細は、「Set Up Debug ウ ィ ザー ド を使用し たデバ ッ グ コ アの 挿入」 を参照 し て く だ さ い。

X-Ref Target - Figure 4-1

Set Up Debug ウ ィ ザー ド を使用 し たデバ ッ グ コ アの挿入

デバ ッ グ用にネ ッ ト を マー ク し た ら 、 それ ら のネ ッ ト をデバ ッ グ コ アに割 り 当て ます。 Vivado IDE の Set Up Debug ウ ィ ザー ド を使用する と 、 デバ ッ グ コ ア を自動作成し 、 デバ ッ グ ネ ッ ト を コ アの入力に割 り 当て る こ と がで き ます。 Set Up Debug ウ ィ ザー ド を使用し てデバ ッ グ コ ア を挿入する には、 次の手順に従い ます。

1. [Debug] ビ ュ ーの [Unassigned Debug Nets] フ ォ ルダーを使用する か、 ネ ッ ト を直接 ク リ ッ ク し て、 デバ ッ グする ネ ッ ト を選択 し ます (オプシ ョ ン)。

2. Vivado IDE の メ イ ン メ ニ ュ ーか ら [Tools] → [Set Up Debug] を ク リ ッ ク する か、 Flow Navigator の [Synthesized Design] の下にあ る [Set Up Debug] を ク リ ッ ク し ます。

3. [Next] を ク リ ッ ク し ます。 [Specify Nets to Debug] ページが開き ます (図4-2)。

4. [Add/Remove Nets] を ク リ ッ ク し 、ネ ッ ト を追加する か、既存のネ ッ ト を削除し ます。デバ ッ グ ネ ッ ト を右 ク リ ッ ク し て [Remove Nets] を ク リ ッ ク し て も、 表か ら ネ ッ ト を削除で き ます。

5. デバ ッ グ ネ ッ ト を右 ク リ ッ ク し て [Select Clock Domain] を ク リ ッ ク し、 ネ ッ ト の値をサンプ リ ン グする ク ロ ッ ク ド メ イ ン を変更 し ます。

注記 : Set Up Debug ウ ィ ザー ド は、 同期エ レ メ ン ト のパス を検索 し、 デバ ッ グ ネ ッ ト に最適な ク ロ ッ ク ド メ イ ン を自 動的に選択 し よ う と し ます。 こ の選択は必要に応 じ て [Select Clock Domain] ダ イ ア ロ グ ボ ッ ク ス で変更で き ますが、 表に含まれ る 各 ク ロ ッ ク ド メ イ ンはそれぞれ別の ILA コ ア イ ン ス タ ン ス にな る こ と に注意 し て く だ さ い。

6. デバ ッ グ ネ ッ ト の選択が完了 し た ら 、 [Next] を ク リ ッ ク し ます。

注記 : Set Up Debug ウ ィ ザー ド に よ り 、 ク ロ ッ ク ド メ イ ンにつき 1 つの ILA コ アが挿入 さ れます。 デバ ッ グのために

選択 さ れたネ ッ ト は、 挿入 さ れた ILA コ アのプ ローブ ポー ト に自動的に割 り 当て ら れます。 ウ ィ ザー ド の最終ペー

ジは コ ア生成のサマ リ ページで、 検出 さ れた ク ロ ッ ク 数、 生成および削除 さ れる ILA コ アの数が示 さ れます。

X-Ref Target - Figure 4-2

7. [ILA (Integrated Logic Analyzer) General Options] ページで ILA データ深 さ ([Sample of Data Depth]、 C_DATA_DEPTH)、 入力パ イ プ段数 ([Input Pipe Stages]、 C_INPUT_PIPE_STAGES)、 キ ャ プチ ャ制御機能の イ ネー ブル ([Capture Control]、C_EN_STRG_QUAL)、ADVANCED ト リ ガー機能 ([Advanced Trigger]、C_ADV_TRIGGER)

を設定 し ます。 こ れ ら のオプシ ョ ンの説明は、34 ページの表 4-2 を参照し て く だ さ い。 注記 : ADVANCED ト リ ガー モー ド ま たは BASIC キ ャ プチ ャ モー ド については、第5 章 「ハー ド ウ ェ アでの ロ ジ ッ ク デザ イ ンのデバ ッ グ」 を参照 し て く だ さ い。 8. [Next] を ク リ ッ ク し 、 最後のページに進みます。 9. 内容を確認 し た ら [Finish] を ク リ ッ ク し、 合成済みデザ イ ン ネ ッ ト リ ス ト に ILA コ ア を挿入および接続 し ます。 こ れで、 デバ ッ グ ネ ッ ト が ILA デバ ッ グ コ アに割 り 当て ら れま し た (図4-4)。

X-Ref Target - Figure 4-3

図 4-3 : Set Up Debug ウ ィ ザー ド : [ILA (Integrated Logic Analyzer) General Options] ページ

X-Ref Target - Figure 4-4

[Debug] ビ ュ ーを使用 し たデバ ッ グ コ アの追加 と カ ス タ マ イ ズ

[Debug] ビ ューの [Debug Cores] タ ブでは、 Set Up Debug ウ ィ ザー ド にない ILA コ アおよびデバ ッ グ コ ア ハブの挿入 に関す る 詳細な設定を実行で き ます。 コ アの生成お よ び削除、 デバ ッ グ ネ ッ ト の接続、 コ ア パ ラ メ ーターの設定な ど を実行で き ます。[Debug] ビ ューの [Debug Cores] タ ブには、 次の も のが表示 さ れます。 • デバ ッ グ ハブ (dbg_hub) コ アに接続 さ れてい るデバ ッ グ コ アの リ ス ト

• 割 り 当て ら れていないネ ッ ト の リ ス ト

デバ ッ グ コ アおよびポー ト は、 ポ ッ プア ッ プ メ ニ ューま たはビ ューの上部にあ る ツールバーか ら 制御で き ます。

デバ ッ グ コ アの生成および削除

[Debug] ビ ューでデバ ッ グ コ ア を生成する には、 ツールバーの [Create Debug Core] を ク リ ッ ク し ます。 [Create Debug Core] ダ イ ア ロ グ ボ ッ ク ス (図4-5) を使用する と 、 親イ ン ス タ ン スおよびデバ ッ グ コ ア名を変更し た り 、 コ アのパ ラ メ ー タ ーを設定で き ます。 既存のデバ ッ グ コ ア を削除す る には、 [Debug] ビ ューで コ ア を右 ク リ ッ ク し、 [Delete] を ク リ ッ ク し ます。[Create Debug Core] ダ イ ア ロ グ ボ ッ ク ス に表示 さ れ る ILA コ アのオプシ ョ ンの説明は、34 ページ の表4-2 を参照し て く だ さ い。

X-Ref Target - Figure 4-5

デバ ッ グ コ ア ポー ト の追加、 削除、 および カ ス タ マ イズ

デバ ッ グ コ アの追加および削除だけでな く 、 各デバ ッ グ コ アのポー ト を追加、 削除、 お よびカ ス タ マ イ ズで き ます。

デバ ッ グ ポー ト を追加する には、 次の手順に従い ます。

1. [Debug] ビ ューでデバ ッ グ コ ア を選択し ます。

2. ツールバーの [Create Debug Port] を ク リ ッ ク し ます。 [Create Debug Port] ダ イ ア ロ グ ボ ッ ク ス が表示 さ れます (図4-6)。 3. ポー ト 幅を指定 し ます。 4. [OK] を ク リ ッ ク し ます。 5. デバ ッ グ ポー ト を削除する には、 [Debug] ビ ュ ーでポー ト を右 ク リ ッ ク し 、 [Delete] を ク リ ッ ク し ます。

デバ ッ グ コ アへのネ ッ ト の接続および接続解除

ネ ッ ト お よ びバ ス (バ ス ネ ッ ト ) を [Schematic] ま たは [Netlist] ビ ュ ーか ら デバ ッ グ コ アのポー ト に ド ラ ッ グ ア ン ド ド ロ ッ プで き ます。 ネ ッ ト の選択に応 じ てポー ト が自動的に拡張 さ れます。 ま た、 ネ ッ ト ま たはバ ス を右 ク リ ッ ク し 、 [Assign to Debug Port] を ク リ ッ ク し て も 、 ネ ッ ト ま たはバス をデバ ッ グ ポー ト に割 り 当て る こ と がで き ます。 デバ ッ グ コ ア の ポ ー ト か ら ネ ッ ト の 接続 を 解除す る に は、 ポ ー ト に 接続 さ れ て い る ネ ッ ト を 右 ク リ ッ ク し 、 [Disconnect Net] を ク リ ッ ク し ます。デバ ッ グ コ アのプ ロパテ ィ の変更

各デバ ッ グ コ アには、 コ アの動作を カ ス タ マ イ ズする パ ラ メ ーターがあ り ます。 debug_core_hub デバ ッ グ コ アの プ ロ パテ ィ の変更については、41 ページの 「デバ ッ グ コ ア ハブの BSCAN ユーザー ス キ ャ ン チ ェーンの変更」 を参 照 し て く だ さ い。 ILA デバ ッ グ コ アのプ ロ パテ ィ も 変更で き ます。 た と えば、 ILA デバ ッ グ コ アでキ ャ プチ ャ さ れ る サンプルの数を 変更する には、 次の手順に従い ます (図4-7)。1. [Debug ] ビ ュ ーで ILA コ ア (u_ila_0 な ど) を選択し ます。

2. [Cell Properties] ビ ューで [Debug Core Options] タ ブを ク リ ッ ク し ます。

3. [C_DATA_DEPTH] の ド ロ ッ プダ ウ ン リ ス ト か ら 、 キ ャ プチ ャする サンプル数を選択し ます。 X-Ref Target - Figure 4-6

![図 2-3 : [Edit Device Properties] ダ イ ア ログ ボ ッ ク ス : 検索フ ィ ール ド](https://thumb-ap.123doks.com/thumbv2/123deta/5849066.548300/11.918.144.832.236.801/2EditPropertiesダイアログボックス検索フィールド.webp)

![図 2-5 : [Add Configuration Memory Device] ダ イ ア ログ ボ ッ ク スのデバイ ス選択ページ](https://thumb-ap.123doks.com/thumbv2/123deta/5849066.548300/14.918.230.733.137.564/2AddConfigurationダイアログボックスデバイス選択ページ.webp)

![図 2-8 : [Program Configuration Memory Device] ダ イ ア ログ ボ ッ ク ス](https://thumb-ap.123doks.com/thumbv2/123deta/5849066.548300/15.918.228.742.427.796/図28ProgramConfigurationMemoryDeviceダイアログボックス.webp)

![図 4-5 : [Create Debug Core] ダ イ ア ログ ボ ッ ク ス](https://thumb-ap.123doks.com/thumbv2/123deta/5849066.548300/32.918.316.659.491.774/図45CreateDebugCoreダイアログボックス.webp)

![図 4-6 : [Create Debug Port] ダ イ ア ログ ボ ッ ク ス](https://thumb-ap.123doks.com/thumbv2/123deta/5849066.548300/33.918.314.659.348.632/図46CreateDebugPortダイアログボックス.webp)