Vivado Design Suite

チュートリアル

デザイン フローの概要

Notice of Disclaimer

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products.To the maximum extent permitted by applicable law:(1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications.You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent.Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx.Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:http://www.xilinx.com/warranty.htm#critapps.

©Copyright 2012-2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries.All other trademarks are the property of their respective owners.

本資料は英語版 (v2013.2) を翻訳したもので、内容に相違が生じる場合には原文を優先します。 資料によっては英語版の更新に対応していないものがあります。 日本語版は参考用としてご使用の上、最新情報につきましては、必ず最新英語版をご参照ください。 この資料に関するフィードバックおよびリンクなどの問題につきましては、jpn_trans_feedback@xilinx.com までお知らせください。いただきましたご意 見を参考に早急に対応させていただきます。なお、このメール アドレスへのお問い合わせは受け付けておりません。あらかじめご了承ください。

改訂履歴

日付 バージョン 改訂内容 2013/06/19 2013.2 リリースに合わせて更新 2013/04/25 2013.2 若干の文章の修正 2013/03/20 2013.2 リリースに合わせて更新目次

TOC

Vivado Design Suite チュートリアル

デザイン フローの概要

このチュートリアルでは、ザイリンクス Vivado®Integrated Design Environment (IDE) 用の使用モデルと デザイン フローについて説明します。小さなサンプル デザインを使用し、RTL からビットストリームまで の基本的な手順を 2 つのデザイン フローで説明します。どちらのフローでも Vivado IDE、または バッチ Tcl スクリプトを実行することができます。Vivado ツールの Tcl API には非常に柔軟性があり、デザイン の設定および実行、解析およびデバッグがしやすくなっています。

プロジェクト モードと非プロジェクト モード

デザイン ツールでデザイン プロセスおよびデザイン データが自動的に管理したい場合もあれば、ソー スおよびプロセスを自分で管理する必要がある場合もあります。Vivado Design Suite では、デザイン ソ ース ファイルの管理、合成およびインプリメンテーション結果の保存、デザイン フローのプロジェクト ス テータスの管理のため、プロジェクト ファイル (.xpr) とディレクトリ構造を使用します。デザイン データ、 プロセス、およびステータスを自動管理するには、プロジェクトの形で管理することが必要です。そのた め、このフローはプロジェクト モードと呼ばれます。 一方で、ソースのコンパイル、デザインのインプリメント、結果のレポートという FPGA デザイン プロセスを ソース ファイルのコンパイルのように実行するフローもあります。このコンパイル スタイル フローは、非プ ロジェクト モードと呼ばれます。Vivado Design Suite ではどちらも簡単に使用できます。プロジェクト モードおよび非プロジェクト モードの概要は次のセクションで説明します。これらのデザイン モードの説明、機能、それぞれの利点といった詳細については、『Vivado Design Suite ユーザー ガイ ド : デザイン フローの概要』 (UG892) を参照してください。

非プロジェクト モード

この使用モデルはスクリプト ベースのユーザー用で、デザイン データの管理やデザイン ステートのチェ ックを Vivado ツールで自動的に管理したくない場合に使用します。Vivado ツールは、単にさまざまなソ ース ファイルを読み込んで、フロー全体を通してメモリにあるデザインをコンパイルします。インプリメン テーション プロセスの任意の段階で、さまざまなレポートを生成し、デザイン ルール チェック (DRC) を 実行し、デザイン チェックポイントを書き出すことができます。フロー全体を通して、メモリ内のデザイン や保存されているチェックポイントを Vivado IDE で開き、デザインを解析し、ネットリスト/制約を修正した りできます。ただし、非プロジェクト モードの場合、ソース ファイルは Vivado IDE で修正できません。ま た、このモードでは、ソース ファイルおよび run の管理、ソース ファイルへのクロスプローブ、デザイン ス テートのレポートなどのプロジェクト ベースの機能は使用できません。つまり、ソース ファイルがアップデ ートされるたびに、デザインを再度読み込む必要があります。デザイン フローの概要 非プロジェクト モードでは、デフォルトではレポートや中間ファイルは作成されないため、Tcl コマンドで レポートやデザイン チェックポイントの作成を指示する必要があります。

プロジェクト モード

この使用モデルは、デザイン プロセス全体を Vivado ツールで管理するユーザー向けで、ソース ファイ ル/制約/結果の管理、統合 IP デザイン、ソースへのクロスプローブなど、さまざまな機能が使用できま す。プロジェクト モードでは、ディレクトリ構造を作成して、デザイン ソース ファイル、IP データ、合成お よびインプリメンテーション run の結果、関連レポートなどを管理します。Vivado Design Suite では、ソー ス ファイルのステータス、コンフィギュレーション、デザインのステートなどが管理およびレポートされま す。複数の run を作成および設定して、さまざまな制約およびコマンド オプションを確認できます。 Vivado IDE では、インプリメンテーション結果を RTL ソース ファイルにクロスプローブできます。また、 Tcl コマンドを使用してフロー全体をスクリプトにし、必要であれば Vivado IDE を開きます。Tcl コマンドの使用

Tcl コマンドおよびスクリプト手法は、使用されるデザイン フローによって異なります。非プロジェクト モー ドを使用する場合、ソース ファイルは read_verilog、read_vhdl、read_edif、read_ip、および read_xdc コ マンドを使用して読み込まれます。Vivado Design Suite は、メモリ内にデザイン データベースを作成し、 データを合成、シミュレーションおよびインプリメンテーションに渡します。プロジェクト モードを使用する 場合、ソース ファイルを管理したり、デザイン ステータスをチェックするためのプロジェクト ディレクトリ構 造を作成するため、create_project、add_files、import_files、add_directories コマンドを使用します。 synth_design、opt_design、place_design、route_design のような個別の基本コマンドは、バッチ フローで はこれらをすべて含んだ launch_runs コマンドに置き換えられます。launch_runs コマンドには、基本コ マンドがまとめられていて、またデフォルト レポートを生成し、run ステータスをチェックするためのコマン ドも含まれています。プロジェクト モードの Tcl スクリプトは非プロジェクト モードのものとは異なります。こ のチュートリアルでは、Vivado IDE だけでなく、プロジェクト モードと非プロジェクト モードの両方につい て説明します。 このチュートリアルで説明される解析機能の多くは、ほかのチュートリアルで詳しく説明されています。こ こではすべてのコマンドやコマンド オプションを説明するわけではありませんので、ご了承ください。ツ ールで提供される Tcl コマンドのリストを確認するには、『Vivado Design Suite Tcl コマンド リファレンス ガイド』 (UG835) を参照してください。チュートリアル デザインの説明 このチュートリアルには、それぞれ個別に実行できる 2 つの演習があります。 演習 1 : 非プロジェクト デザイン フローの使用 • bft デザインをインプリメントするための サンプルの run スクリプトについて学びます。 • 各段階でさまざまなレポートを表示して確認します。 • vivado.log ファイルを確認します。 • デザイン チェックポイントを書き出します。

• 合成後 Vivado IDE を開いて、タイミング制約の定義および I/O プランニングを確認し、制約の アップデート方法を学びます。 • インプリメント済みデザインのチェックポイントを開いて、タイミング、消費電力、使用率、配線を 解析します。 演習 2 : プロジェクト ベース デザイン フローの使用 • 新しいプロジェクトを作成します。 • Vivado IDE を使用して bft デザインをインプリメントする方法について学びます。 • 各段階でさまざまなレポートを表示して確認します。 • 合成済みデザインを開いて、タイミング制約の定義、I/O プランニング、デザイン解析を確認しま す。 • インプリメント済みデザインを開いて、タイミング、消費電力、リソース使用率、配線およびクロス プローブを解析します。

• Vivado を終了して、launch_runs で作成された vivado.jou ファイルを元に Tcl スクリプトを作成し ます。 • 新しく作成した Tcl スクリプトを使用してデザインを実行し直します。 • Vivado IDE でプロジェクトを開いて、実行後のデザイン ステータスが正しいかどうか確認します。

チュートリアル デザインの説明

このチュートリアルでは bft という小型のサンプル デザインを使用します。この bft デザインには VHDL および Verilog のソース ファイルが複数と、XDC 制約ファイルが 1 つ含まれています。 このデザインは xc7k70T デバイスをターゲットにしています。小型デザインを使用することで、チュートリ アルを最小ハードウェア要件で実行し、時間内に完了させることができるだけでなく、データ サイズも小 さくすることができます。ソフトウェア要件

ソフトウェア要件

このチュートリアルを実行するには、Vivado Design Suite 2013.2 以降のバージョンのツールがインストー ルされていることが前提になっています。インストール手順についての詳細は、『Vivado Design Suite ユ ーザー ガイド : リリース ノート、インストールおよびライセンス 』 (UG973) を参照してください。

ハードウェア要件

サポートされている OS は、Redhat 5.6 Linux 64 ビットおよび 32 ビット、Windows 7 の 64 ビットおよび 32 ビットです。

Vivado ツールを使用するには 2GB 以上の RAM を使用してください。

チュートリアル デザイン ファイルのディレクトリ

このチュートリアルのファイルは Vivado Design Suite の次のディレクトリにあります。<Vivado_install_area>/Vivado/<version>/examples/Vivado_Tutorial また、ローカル ディレクトリにチュートリアル ファイルを保存したり、変更を加える前の元の状態にファイ ルを戻すため、提供されている ZIP ファイルを随時抽出することもできます。 書き込み権のあるディレクトリに ZIP ファイルを解凍します。 <Vivado_install_area>/Vivado/<version>/examples/Vivado_Tutorial.zip このチュートリアルでは、解凍された Vivado_Tutorial ディレクトリを <Extract_Dir> と記述します。 注記 : このチュートリアルの演習では、チュートリアル デザイン データを変更します。このチュートリアル を開始するたびに、元の Vivado_Tutorial ディレクトリから新しくコピーしてください。

手順 1 : サンプル スクリプトの確認

演習 1 : 非プロジェクト デザイン フローの使用

この演習では、非プロジェクト モードとそれに関する Tcl コマンドについて説明します。手順 1 : サンプル スクリプトの確認

サンプル スクリプト <Extract_Dir>/Vivado_Tutorial/run_bft_batch.tcl をテキスト エディターで開 1. いて、ステップを確認してください。STEP#0:Define output directory location. STEP#1:Setup design sources and constraints.

STEP#2:Run synthesis, write design checkpoint and generate reports. STEP#3:Run placement and optimization commands, write design

checkpoint and generate reports.

STEP#4:Run routing command, write design checkpoint and generate reports. STEP#5:Generate a bitstream. ほとんどの Tcl コマンドがコメント アウトされていることがわかります。これらを手動で 1 つずつ実 行します。 サンプル スクリプトはこのチュートリアルの後半でコマンドをコピーして貼り付けるので、開いたまま 2. にしておきます。

手順 2 : サンプル デザインを使用して Vivado ツールを

起動

• Linux の場合 : 演習資料を保存したディレクトリに移動します。 1. cd <Extract_Dir>/Vivado_TutorialVivado Design Suite Tcl シェルを起動し、チュートリアル デザインを作成するための Tcl スクリプトを 2.

実行します。

vivado –mode tcl –source run_bft_batch.tcl

• Windows の場合 :

Vivado Design Suite Tcl シェルを起動します。 1.

[スタート] → [すべてのプログラム] → [Xilinx Design Tools] → [Vivado 2013.2] → [Vivado 2013.2 Tcl Shell] をクリック

Tcl シェルで演習資料が保存されているディレクトリに移動します。 2.

手順 3 : デザインの合成

Vivado% cd <Extract_Dir>/Vivado_Tutorial

チュートリアル デザインを作成するため Tcl スクリプトを実行します。 3.

Vivado% source run_bft_batch.tcl

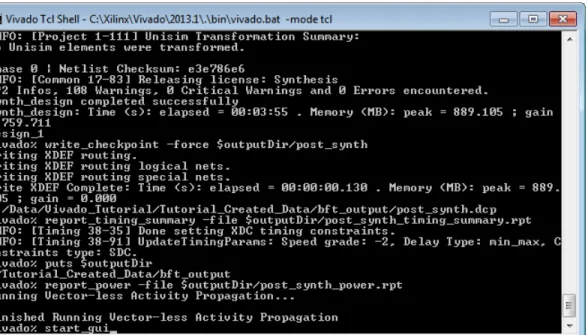

ここから先は Vivado Design Suite Tcl シェルを「Tcl シェル」と呼びます。このスクリプトが完了した後は Tcl プロンプト「Vivado%」が表示されます。 図 1 : Vivado および Tcl スクリプトの起動 Vivado ツールの Tcl プロンプトから、その他の Tcl コマンドを入力できます。

手順 3 : デザインの合成

run_bft_batch.tcl スクリプトから synth_design コマンドをコピーして Tcl シェルに貼り付け、合成が終 1. 了するのを待ちます。Tcl シェルには右クリックのポップアップ メニューを使用すると貼り付けることが できます。synth_design -top bft -part xc7k70tfbg484-2 -flatten rebuilt

注記 : サンプル スクリプトのコマンドはコメントになっています。行頭の # 文字はコピーするとコメ ントとして処理されてしまうので、コピーしないようにしてください。

合成レポートをスクロールして確認します。 2.

手順 4 : Vivado IDE の起動

Vivado Tcl プロンプトが表示されたら、合成の後に続く write_checkpoint、report_timing_summary、 3.

report_power コマンドをコピーして貼り付けます。

write_checkpoint -force $outputDir/post_synth

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt report_power -file $outputDir/post_synth_power.rpt

別のウィンドウを開いて、出力ディレクトリに作成されたファイルを確認します。Windows の場合は、 4. ファイル ブラウザーを使用した方が確認しやすいでしょう。 <Extract_Dir>/Vivado_Tutorial/Tutorial_Created_Data/bft_output テキスト エディターを使用し、作成されたさまざまなレポート ファイル (*.rpt) を確認します。 5.

手順 4 : Vivado IDE の起動

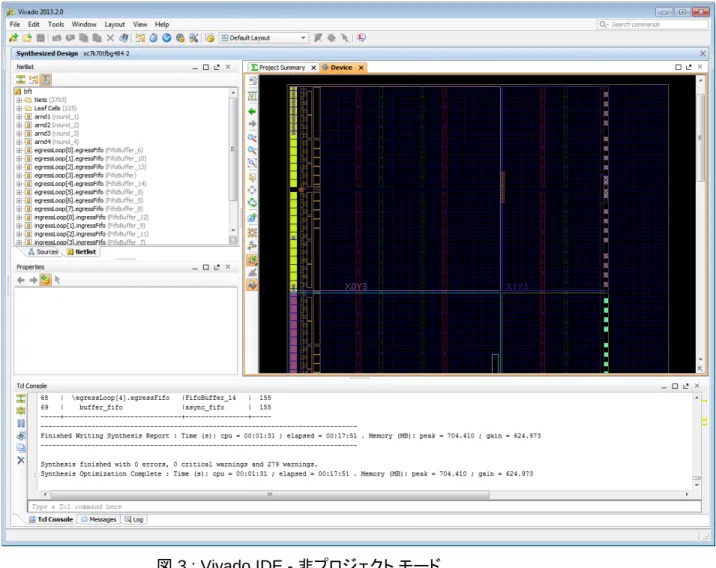

Vivado プロジェクトがディスクに作成されていなくても、メモリ内のデザインはツールで使用できるため、 Tcl シェルから Vivado IDE を起動してデザインを表示します。 非プロジェクト モードでは、デザイン プロセスのさまざまな段階で Vivado IDE を使用できます。現在の ネットリストおよび制約は Vivado IDE のメモリに読み込まれており、解析および修正ができます。ロジッ クまたは制約への変更はすべてメモリに即時反映され、次のツールへ渡されます。これは、ファイルを保 存し読み込み直す必要のある ISE ツールとは大きく異なる点です。start_gui コマンドで Vivado IDE を開きます。 1.

Vivado% start_gui

図 2 : start_gui で Vivado IDE を開く

手順 4 : Vivado IDE の起動

図 3 : Vivado IDE - 非プロジェクト モード

ヒント : Vivado IDE を閉じ、Vivado Design Suite の Tcl シェルに戻るには、stop_gui コマンドを 使用します。Vivado IDE で [File] → [Exit] をクリックすると、Vivado ツールは完全に終了しま す。

非プロジェクト モードの場合はデザインにプロジェクトが含まれないため、Vivado IDE でソース ファイルや run の管理はできません。つまりメモリ内のデザインを実際に解析しているということ になります。Vivado の Flow Navigator およびその他のプロジェクト ベースのコマンドも非プロジ ェクト モードでは使用できません。

手順 5 : タイミング制約と I/O 配置の定義

手順 5 : タイミング制約と I/O 配置の定義

タイミング制約と物理制約は一般的にインプリメンテーション前に定義しておく必要があります。Vivado ツールでは、制約ファイルから制約を読み込んだり、Vivado IDE を使用してインタラクティブに制約を入 力したりできます。タイミング制約の定義

[Window] → [Timing Constraints] をクリックして [Timing Constraints] ビューを開きます。 1. 図 4 : タイミング制約の定義 [Timing Constraints] ビューの左側には、さまざまな制約タイプがツリー構造で表示されていま す。これはタイミング制約のメニューで、簡単に定義できます。 [Timing Constraints] ビューの右側の表には、wbClk と bftClk という 2 つのクロック制約が定義 されていることに注目してください。現在定義されている制約の値は、この表をクリックして直接 変更できます。

図 4 にあるように [Timing Constraints] ビューの左側にある [Clocks] の下にある [Create Clock] をダ 2.

ブルクリックします。

手順 5 : タイミング制約と I/O 配置の定義 [Create Clock] ダイアログ ボックスが開き、クロック制約を定義できます。画面下部の Tcl コマン ド部分には、実行される XDC コマンドが表示されます。 現段階では、タイミング制約は作成または変更しないでください。 図 5 : [Create Clock] ダイアログ ボックス [Cancel] をクリックします。 3. ビュー タブの X マークをクリックして、[Timing Constraints] ビューを閉じます。 4.

Vivado Design Suite には、デザイン解析および制約設定に関するさまざまな機能があります。これ らの機能についての詳細は、その他のチュートリアルを参照してください。機能の一部を [Tools] メ ニューで確認します。

I/O プランニング

Vivado は I/O ピン割り当てを実行および検証する包括的な機能を備えています。これについては I/O プランニング用チュートリアルを参照してください。

図 6 にあるように、メイン ツールバーのレイアウト セレクターから [I/O Planning] を選択します。 1.

[Package] ビューをアクティブ ウィンドウにします。 2.

注記 : [Package] ビューが開いていない場合は、メイン ウィンドウで [Window] → [Package] をク リックします。

手順 5 : タイミング制約と I/O 配置の定義 [Package] ビューで配置済み I/O ポートを選択します。これはパッケージ 3. ピン内でオレンジ色のブロックとして表示されています。 選択した I/O ポートを同じ I/O バンク内の別のピン サイトにドラッグします。 4. [I/O Ports] ビューでポート名およびパッケージ ピン サイトを確認します。 5.

[I/O Port Properties] ビューに表示されるデータを確認します。ビューの一 6. 番下のタブをそれぞれクリックします。 移動させたポートの名前とサイトを覚えておきます。 7. インプリメンテーションの後で、XDC ファイルでこのポートの LOC 制約を検索するので、この情 報は控えておいたほうがよいでしょう。 図 6 : [I/O Planning] ビュー レイアウト

手順 6 : 変更した制約のエクスポート

手順 6 : 変更した制約のエクスポート

変更した制約は後で使用するために出力しておくことができます。また、最新の変更を含むデザイ ン チェックポイントを保存することもできます。デザイン チェックポイントについては、このチュートリア ルの後半で説明します。

重要 : Vivado Design Suite では、NCF/UCF 制約はサポートされていません。既存の UCF 制約は XDC 制約に変換する必要があります。詳細は、『Vivado Design Suite 移行 手法ガイド』 (UG911) を参照してください。

新しい I/O LOC 制約値を含む、変更された XDC 制約ファイルを出力するには、[Export 1.

Constraints] コマンドを使用します。

[File] → [Export] → [Export Constraints] をクリック

[Export Constraints] ダイアログ ボックスが開き、作成するファイルの名前を指定できます。

図 7 : [Export Constraints] コマンド ファイルの名前とディレクトリを入力し、[OK] をクリックします。

2.

[Export fixed location constraints only] チェックボックスに注目してください。これがオンになって いると、配置されたセルすべてではなく、固定セルの LOC 制約のみがエクスポートされます。固 定セルと固定されていないセルの詳細については、『Vivado Design Suite ユーザー ガイド : デ ザイン解析およびクロージャ テクニック』 (UG906) を参照してください。

テキスト エディターで制約ファイルを開くには [File] → [Open File] をクリックします。 3.

[Open File] ダイアログ ボックスの一番下の [File of type] フィルターで [All Files] を選択します。 4. 新しくエクスポートした制約ファイルを選択して [OK] をクリックします。 5. このファイルに変更した I/O ポートの配置が含まれているのがわかります。 6. ASCII ファイルはすべてテキスト エディターで開くことができるため、Tcl スクリプト、制約ファイ ルを編集したり、レポートを表示しやすくなっています。テキスト エディターはコンテキスト センシ ティブで、Verilog、VHDL、Tcl といったファイルの種類を表示すると、キーワードやコメントがハ イライトされます。

IDE 画面下にある [Tcl Cosole] タブをクリックして、stop_gui コマンドを入力します。 7.

手順 7 : デザインのインプリメンテーション Vivado IDE が閉じて、Tcl シェルの Tcl プロンプトに戻ります。

手順 7 : デザインのインプリメンテーション

run_bft_batch.tcl スクリプトを開きます。既に開いている場合は前面に表示します。 1. opt_design から write_bitstream へと順にスクリプトの Tcl コマンドをそれぞれコピーして貼り付けま 2. す。 opt_design place_designwrite_checkpoint -force $outputDir/post_place

report_timing_summary -file $outputDir/post_place_timing_summary.rpt route_design

write_checkpoint -force $outputDir/post_route

report_timing_summary -file $outputDir/post_route_timing_summary.rpt report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt

report_clock_utilization -file $outputDir/clock_util.rpt report_utilization -file $outputDir/post_route_util.rpt report_power -file $outputDir/post_route_power.rpt report_drc -file $outputDir/post_imp_drc.rpt

write_verilog -force $outputDir/bft_impl_netlist.v write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc write_bitstream -force $outputDir/bft.bit

それぞれのコマンドをチェックし、実行されたときにどのようなメッセージが表示されるか確認します。 3. 次の出力ディレクトリで作成されたファイルを確認します。 4. <Extract_Dir>/Vivado_Tutorial/Tutorial_Created_Data/bft_output テキスト エディターを使用して作成されたさまざまなレポート ファイル (*.rpt) を確認します。 5. bft_impl.xdc ファイルを開きます。 6. 変更した I/O ポート制約を使用してデザインがインプリメントされたことを確認します。 7.

手順 8 : デザイン チェックポイントを開く

手順 8 : デザイン チェックポイントを開く

Vivado IDE では、保存したデザイン チェックポイントを開くことができます。これはデザインのスナップシ ョットで、Vivado IDE または Tcl シェルで開いて合成、インプリメンテーション、解析に使用できます。

start_gui で Vivado IDE を再び開きます。 1. メモリにあるアクティブ デザインが Vivado IDE に読み込まれます。 インプリメントされたデザイン チェック ポイントが読み込まれ、現在のメモリ内のデザインは閉じま す。 インプリメントされたチェックポイントを開きます。 2.

[File] → [Open Checkpoint] をクリックして、チェックポイント ファイルを選択します。 <Extract_Dir>/Vivado_Tutorial/Tutorial_Created_Data/bft_output/

post_route.dcp

[Yes] をクリックして、メモリ内のデザインを閉じます。 3.

プロンプトが表示されたら、[Close Without Saving] を選択します。 4. これで配置配線されたデザイン チェックポイントを基に Vivado IDE の表示および解析機能を 使用できるようになりました。

手順 9 : インプリメンテーション結果の解析

Vivado にはさまざまな観点からデザインおよびデバイス データを確認する拡張機能が含まれ、消費電 力、タイミング、リソース使用率、クロックなどの標準レポートを生成することができます。Tcl API を使用し た Vivado ツールのカスタム レポート機能は豊富です。 report_timing_summary を実行し、配置後のタイミング データを解析します。 1.[Tools] → [Timing] → [Report Timing] をクリック

[Report Timing Summary] ダイアログ ボックスで [OK] をクリックして、デフォルトの run オプションを 2.

使用します。

[Timing Summary] ビューに表示される情報を確認します。[Timing Summary] ビューの左側の ツリー表示からさまざまなカテゴリを選択して、表示されるデータを確認してみてください。 report_timing コマンドでタイミング解析を実行します。

3.

[Tools] → [Timing] → [Report Timing] をクリック

[Report Timing] ダイアログ ボックスで [OK] をクリックして、デフォルトの run オプションを使用します。 4.

[Timing Result] ビューの最初にリストされるパスを選択します。 5.

[Path Properties] ビューを最大化するかフロートさせて、パスの詳細を確認します。 6.

手順 9 : インプリメンテーション結果の解析

図 8 : 最大化した [Path Properties] ビュー

ビュー上部にある [Restore] または [Dock] ボタンをクリックし、[Path Properties] ビューを元に戻しま 7.

す。

[Timing Result] のビューで右クリックし、ポップアップ メニューから [Schematic] をクリックして、選択 8. されているパスの回路図を開きます。 注記 : [Schematic] ビューは F4 キーを押しても開くことができます。 回路図上の接続を展開表示させたり、デザイン階層を確認するには、セル、ピン、ワイヤなど回路図 9. オブジェクトをダブルクリックします。 [Schematic] ビューを閉じるか、[Device] ビューのタブをクリックして前面に表示します。 10.

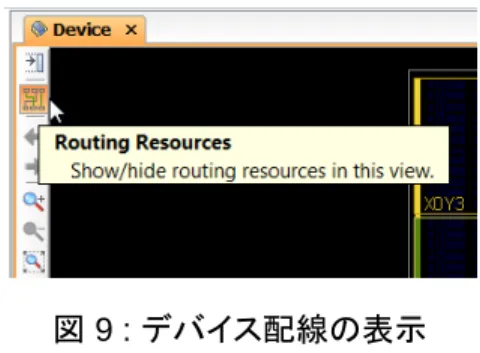

[Device] ビューで [Routing Resources] ボタンをクリックして詳細なデバイス配線を表示します。 11.

手順 9 : インプリメンテーション結果の解析

図 9 : デバイス配線の表示

[Device] ビューには、選択したパスの配線がハイライトされて表示されます。

[Device] ビューで [Auto Fit Selection] ボタンをクリックし、選択したオブジェクトが自動的にフィットす 12. るようにします。 図 10 : デバイス配線の表示 [Timing Result] ビューからその他のパスをいくつか選択します。 13. 選択したパスの配線を [Device] ビューで確認します。 14.

[Tools] メニューをクリックし、[Timing] や [Report] などのタブにある解析機能を確認します。 15.

[Report Power]、[Report Clock Interaction]、[Report Clock Networks]、[Report Utilization] など、利 16.

用可能なコマンドの一部を実行します。

手順 10 : Vivado ツールの終了

手順 10 : Vivado ツールの終了

Vivado ツールでは、vivado.log というログ ファイルと、vivado.jou というジャーナル ファイルが Vivado が起動されたディレクトリに書き込まれます。このログ ファイルはデザイン セッション中に実行さ れた Tcl コマンド、これらのコマンドを実行して返されたメッセージの記録です。ジャーナル ファイルに はセッション中に実行された Tcl コマンドが記録され、これを基に新しい Tcl スクリプトを作成できます。 Vivado IDE を終了します。 [Tcl Console] ビュー タブを選択して、「stop_gui」と入力します。 1. Vivado を終了させます。 2. Vivado% exit Vivado ツールのログ ファイル (vivado.log) を確認します。 3. Windows の場合は、このログ ファイルを検索して開くのにファイル ブラウザーを使用したほうが 簡単かもしれません。この Vivado ログとジャーナル ファイルのディレクトリは、Vivado ツールが 起動されたディレクトリです。または Windows のデスクトップ アイコンにこの 2 つのファイルのデ ィレクトリを設定しておくと便利です。この設定は演習 2 で行います。 この演習では、次のディレクトリにあるログ ファイルを検索します。 <Extract_Dir>/Vivado_Tutorial/vivado.log1 ログ ファイルには、Vivado のセッション中に実行された Tcl コマンドの履歴と結果がすべて 含まれます。 Vivado のジャーナル ファイル (vivado.jou) を確認します。 4. Windows の場合は、ファイル ブラウザーを使用した方が確認しやすいでしょう。この演習では、 次のディレクトリにあるジャーナル ファイルを検索します。 <Extract_Dir>/Vivado_Tutorial/vivado.jou ジャーナル ファイルには、Vivado のセッション中に実行された Tcl コマンドのみが含まれま す。ログ ファイルにあるような詳細は記録されません。ジャーナル ファイルは、前のデザイン セ ッションから Tcl スクリプトを作成する際に使用すると便利です。 これについては、次の演習で 説明します。

手順 1 : プロジェクトの作成

演習 2 : プロジェクト デザイン フローの使用

この演習では、プロジェクトの作成、ソース ファイルの管理、デザイン解析、制約定義、合成およびイン プリメンテーションの run の管理などのプロジェクト モード機能について説明します。

まず Vivado IDE でサンプル デザインを使用して FPGA デザイン フロー全体について説明し、IDE の 主な機能をいくつか確認します。これらの機能については、別のチュートリアルで説明しています。最後 に、バッチ run スクリプトを作成して、デザイン プロジェクトをインプリメントし、Tcl スクリプトの実行と Vivado IDE での作業とを切り替えます。この切り替え作業は非常に簡単です。

手順 1 : プロジェクトの作成

Vivado の起動

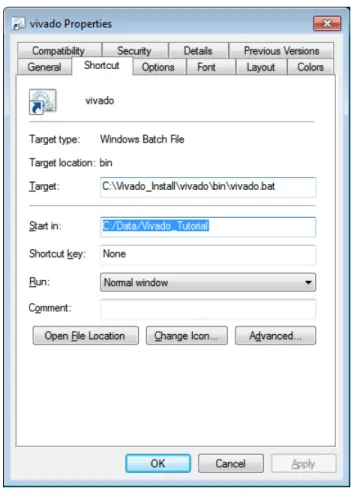

• Linux の場合 : 演習資料を保存したディレクトリに移動します。 1. cd <Extract_Dir>/Vivado_Tutorial Vivado IDE を起動します。 2. vivado • Windows の場合は、Vivado ツールを起動させるためデスクトップ アイコンをクリックする前に、 vivado.log および vivado.jou ファイルのある場所を指定するようアイコンを設定します。 Vivado 2013.2 用のデスクトップ アイコンを右クリックし、ポップアップ メニューから [Properties] を選 1. 択します。 [ショートカット] タブで [作業フォルダー] の値に抽出したチュートリアルのディレクトリを指定します 2. (図 11 を参照)。 <Extract_Dir>/Vivado_Tutorial/ [OK] をクリックしてダイアログ ボックスを閉じます。 3.手順 1 : プロジェクトの作成

図 11 : 開始ディレクトリの設定

Vivado 2013.2 のデスクトップ アイコンをダブルクリックして Vivado IDE を起動します。 4.

新規プロジェクトの作成

Vivado IDE が開いたら、Getting Started ページで [Create New Project] をクリックします。 1.

[New Project] ページで [Next] をクリックします。 2.

プロジェクト名とディレクトリを指定します。 3.

[Project name] : project_bft 4.

[Project location] : <Extract_Dir>/Vivado_Tutorial/Tutorial_Created_Data 5.

[Next] をクリックします。 6.

手順 1 : プロジェクトの作成

図 12 : [Create New Project]

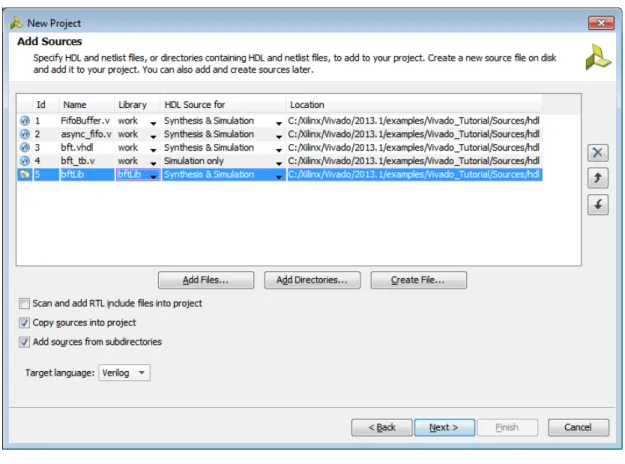

プロジェクト タイプは [RTL Project] をオンにして [Next] をクリックします。 7. [Add Files] をクリックします。 8. a. <Extract_Dir>/Vivado_Tutorial/Sources/hdl/ を参照します。 b. Ctrl キーを押しながら次のファイルを選択します。 async_fifo.v、bft.vhdl、bft_tb.v、FifoBuffer.v c. [OK] をクリックしてファイル ブラウザーを閉じます。 [Add Directories] をクリックします。 9. a. <Extract_Dir>/Vivado_Tutorial/Sources/hdl/bftLib ディレクトリを選択します。 b. [Select] をクリックします。

[HDL Sources for] の列で bft_tb.v をクリックし、[Synthesis & Simulation] を [Simulation only] に 10.

変更します。

図 13 にあるように[Library] の列で bftLib をクリックし、値を [work] から [bftLib] に変更します。 11.

手順 1 : プロジェクトの作成

図 13 : RTL ソースの追加

[Copy sources into project] および [Add sources from subdirectories] のチェックボックスをオンにしま 12.

す。

[Target Language] を [Verilog] に設定します。 13.

[Next] をクリックします。 14.

この段階では IP を追加しないので [Next] をクリックして [Add Existing IP] ページを飛ばします。 15.

[Add Constraints] ページで [Add Files] をクリックします。 16.

a. <Extract_Dir>/Vivado_Tutorial/Sources/bft_full.xdc を選択します。 b. [OK] をクリックしてファイル ブラウザーを閉じます。

[Copy constraints files into project] はオンにします。 17.

[Next] をクリックして [Default Part] ページに移動します。 18.

手順 1 : プロジェクトの作成

図 14 : 制約の追加

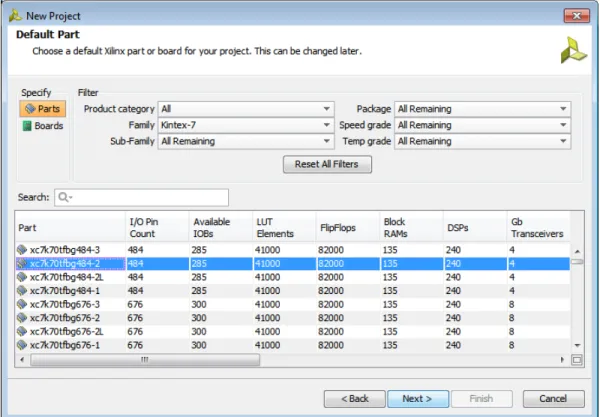

[Default Part] ページの [Family] フィルターで [Kintex-7] を選択します。 19.

リストの上までスクロールして、xc7k70tfbg484-2 パーツを選択し、[Next] をクリックします。 20.

[Finish] をクリックして [New Project Summary] ページを閉じると、プロジェクトが作成されます。 21.

手順 2 : [Sources] ビューとテキスト エディターの使用

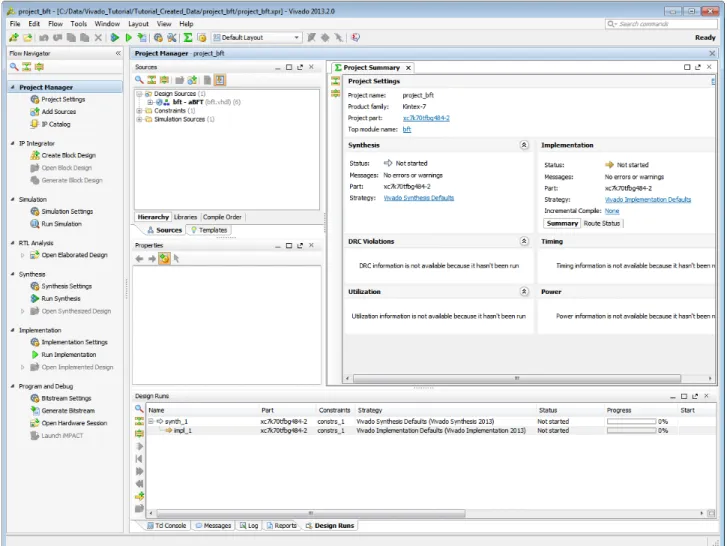

Vivado IDE が開き、デフォルトのレイアウトで project_bft が開きます。

図 16 : Vivado IDE で開いたプロジェクト「BFT」

手順 2 : [Sources] ビューとテキスト エディターの使用

Vivado ツールには、Verilog、VHDL、EDIF、NGC 形式のコア、SDC、XDC、TCLの 制約ファイル、そし てシミュレーション テストベンチなど、異なるデザイン ソースを追加できます。これらのファイルは [Sources] ビューの下にある [Hierarchy]、[Library]、[Compile Order] を使用してソートすることができま す。Vivado IDE にはコンテキスト センシティブなテキストエディターが含まれていて、RTL ソース、制約ファ イル、Tcl スクリプトを作成したりできます。Vivado IDE を設定してサードパーティのテキスト エディター を使用することもできます。Vivato ツールの設定方法については『Vivado Design Suite ユーザー ガイ ド : IDE の使用』 (UG893) を参照してください。

手順 2 : [Sources] ビューとテキスト エディターの使用

[Sources] ビューとプロジェクト サマリの確認

[Project Summary] の情報を確認します。デザイン フロー全体で各デザイン プロセスが終了するた 1.

びに詳細な情報が表示されます。

[Sources] ビューの [Design Sources]、[Constraints] および [Simulation Sources] フォルダーを展開し 2.

て確認します。

図 17 : ソースの表示

[Design Sources] フォルダーからは、VHDL、Verilog ソース ファイルおよびライブラリの情報が 確認できます。デフォルトでは [Hierarchy] タブが表示されています。

[Libraries] タブおよび [Compile Order] タブをクリックすると、ソース ファイルのリスト方法が違うこと 3.

がわかります。

[Libraries] タブはファイルの種類別にソース ファイルが分けられています。[Compile Order] タ ブには合成で使用されるファイルの順序が表示されています。 [Hierarchy] タブをクリックします。 4.

テキスト エディターの使用

[Sources] ビューで VHDL ソースの 1 つを選択します。 1. 右クリックし、ポップアップ メニューでどういうコマンドが表示されるか確認してみてください。 2. [Open File] をクリックし、テキスト エディターでスクロールしてファイルの内容を確認してみます。 3.手順 2 : [Sources] ビューとテキスト エディターの使用 [Sources] ビューでソース ファイルをダブルクリックしても、テキスト エディターで表示することが できます。 図 18 : コンテキスト センシティブなテキストエディター テキスト エディターで表示される RTL コードは、キーワードやコメントが色表示されていているこ とに注目してください。予約されている単語の表示に使用される色やフォントは [Tools] → [Options] コマンドを使用して設定できます。Vivato ツールの設定方法については『Vivado Design Suite ユーザー ガイド : IDE の使用』 (UG893) を参照してください。

テキスト エディターで右クリックし、[Find in Files] をクリックします。[Replace in Files] コマンドも実行 4.

できます。

さまざまな検索オプションを含む [Find in Files] ダイアログ ボックスが表示されます。

手順 3 : RTL デザインのエラボレーション

[Find what] フィールドに「clk」と入力し、[Find] をクリックします。 5.

[Find in Files] ビューが Vivado IDE の下部にあるメッセージ エリアに表示されます。

図 20 : 検出結果の表示 [Find in Files] ビューで表示されたファイルの 1 つを展開し、ファイル内の [clk] をクリックします。 6. 選択したファイルがテキスト エディターで開き、そのファイルに含まれる「clk」がテキスト エディタ ーでハイライトされます。 [Find in Files] ビューを閉じます。 7. テキスト エディターを閉じます。 8. 次の手順では、合成を実行する前に使用できるデザイン コンフィギュレーションおよび解析機能につい ていくつか説明します。

手順 3 : RTL デザインのエラボレーション

Vivado IDE には、RTL 解析および IP カスタマイズ環境も含まれています。RTL デザインのパフォーマ ンスや消費電力を改善するための RTL DRC (デザイン ルール チェック) も複数含まれています。Flow Navigator で [Open Elaborated Design] をクリックしてデザインをエラボレートします。 1.

メイン ツールバーのレイアウト セレクターから [Default Layout] を選択します。 2.

[Open Elaborated Design] をクリックすると、RTL ネットリスト、回路図、グラフィカルな階層を含む さまざまな階層ビューが表示されます。ビュー同士は連動していて、あるビューで選択したもの は別のビューでも選択されるため、すばやく RTL をデバッグおよび最適化できます。

[RTL Netlist] ビューでロジック階層を確認し、回路図が表示されていない場合は右クリックで 3.

[Schematic] をクリックして回路図を表示します。

[RTL Schematic] ビューでロジック インスタンスを選択し、右クリックで [Go to Source] または [Go to 4.

手順 4 : IP カタログの使用

選択したセルのロジックがハイライトされた状態で RTL ソース ファイルがテキスト エディターで 開きます。[Go to Definition] コマンドの場合は、モジュール定義を含む RTL ソースが開きま す。[Go to Source] をクリックすると、選択したセルのインスタンスを含む RTL ソースが開きます。 Vivado IDE の一番下の [Messages] ビューをクリックして、メッセージを確認します。

5.

[Messages] ビューのツールバーで [Collapse All] ボタンをクリックします。 6. [Elaborated Design] メッセージを展開します。 7. メッセージに含まれるリンクをクリックすると、メッセージに関する RTL ソース ファイルが開きま す。 リンクの 1 つをクリックします。関連した行がハイライトされた状態でテキスト エディターに RTL ソー 8. ス ファイルが開きます。 テキスト エディターを閉じます。 9. ビューの右上の X マークをクリックしてエラボレート済みデザインを閉じます。 10.

手順 4 : IP カタログの使用

ザイリンクス IP カタログから、IP コンフィギュレーションおよび生成機能を利用できます。カタログはさま ざまな方法でソートおよび検索できます。IP はカスタマイズ、生成、インスタンシエートできます。Flow Navigator で [IP Catalog] をクリックします。 1.

IP カタログに表示されるカテゴリーやフィルター機能を確認します。 2.

[Basic Elements] フォルダーの [Counters] フォルダーを展開します。 3.

[DSP48 Macro] をダブルクリックします。 4.

[Customize IP] ダイアログ ボックスが Vivado 内に直接開きます。Vivado Design Suite ツール内 で IP のカスタマイズおよびコンフィギュレーションができます。IP コンフィギュレーションおよびイ ンプリメンテーションの詳細については、『Vivado Design Suite: IP を使用した設計』 (UG896) お よび『Vivado Design Suite チュートリアル : IP を使用した設計』 (UG939) を参照してください。 [Cancel] をクリックして、現在のデザインには IP を追加せずに [Customize IP] ダイアログ ボックスを 5.

閉じます。

X マークをクリックして、IP カタログを閉じます。 6.

手順 5 : ビヘイビアー シミュレーションの実行

手順 5 : ビヘイビアー シミュレーションの実行

Vivado IDE には、Vivado シミュレータが含まれており、プロジェクトのシミュレーション ソースを追加およ び管理できます。ユーザーは、シミュレーション オプションを設定し、シミュレーション ソース セットを作 成/管理できるほか、合成前に RTL ソースのビヘイビアー シミュレーションを実行できます。

Flow Navigator の [Simulation] の下にある [Simulation Settings] をクリックします。 1. 図 21 : [Simulation] ページ [Compliation]、[Simulation]、[Netlist]、[Advanced] の各タブをクリックして設定可能なものを確認し 2. ます。 [Cancel] をクリックします。 3.

Flow Navigator で [Simulation] をクリックし、[Run Behavioral Simulation] をクリックします。 4.

[Simulation] の各設定を確認します。 5.

シミュレーションについては、『Vivado Design Suite ユーザー ガイド : ロジック シミュレーション』 UG900) および『Vivado Design Suite チュートリアル : ロジック シミュレーション』 (UG937) を参照 してください。

シミュレーション画面を X マークをクリックして閉じます。 6.

手順 6 : デザイン run の設定の確認 変更を保存するかどうか尋ねるメッセージが表示されたら、[No] をクリックします。 7.

手順 6 : デザイン run の設定の確認

演習 1 で使用した非プロジェクト モードと、この演習で使用するプロジェクト モードとの大きな違いの 1 つに、合成およびインプリメンテーションのデザイン run のサポートがあります。非プロジェクト モードで はデザイン run はサポートされていません。 デザイン run とは、合成およびインプリメンテーション プロセスの様々なステップで利用可能な多くのオ プションを設定および保存する方法です。オプションを設定し、今後の run で使用するためのストラテジ としてコンフィギュレーションを保存することができます。また、Tcl.pre および Tcl.post スクリプトを定義し て、プロセスの各ステップの前後で実行し、デザイン プロセスの前後でレポートを生成することもできま す。 合成およびインプリメンテーション run を実行する前に、これらの設定およびストラテジを確認します。 Flow Navigator で [Synthesis] をクリックしします。1.

[Project Settings] ダイアログ ボックスが開きます。Vivado 合成のオプションをここで設定すること ができます。合成オプションについての詳細は、『Vivado Design Suite ユーザー ガイド : 合成』 (UG901) を参照してください。

手順 6 : デザイン run の設定の確認

図 22 : 合成の設定

合成オプションを確認したら、[Project Settings] ダイアログ ボックスの左側の [Implementation] をクリ 2.

ックします (図 22)。

[Project Settings] ダイアログ ボックスの表示がインプリメンテーション用に切り替わります。この演 習ではインプリメンテーションのオプションは変更しませんが、インプリメンテーション run のオプ ションを確認をします。合成オプションについての詳細は、『Vivado Design Suite ユーザー ガイ ド : インプリメンテーション』 (UG904) を参照してください。

手順 6 : デザイン run の設定の確認

図 23 : インプリメンテーションの設定

[Cancel] をクリックして、[Project Settings] ダイアログ ボックスを閉じます。 3.

手順 7 : デザインの合成およびインプリメンテーション

手順 7 : デザインの合成およびインプリメンテーション

合成およびインプリメンテーション run のオプションを設定すると、次のことが実行できるようになります。 • [Run Synthesis] で合成のみを実行 • [Run Implementation] で合成が実行されていない場合はまず合成を実行してから、インプリメンテー ションを実行 • [Generate Bitstream] で、合成が実行されていない場合はまず合成を実行してからインプリメンテー ションを実行し、ザイリンクス デバイスをプログラムするためのビットストリームを出力 このチュートリアルでは、これらの手順をひとつずつ実行します。Flow Navigator で [Run Synthesis] をクリックして、終了するまで待ちます。 1.

進捗状況は Vivado IDE の右上のバーに表示されます。ツールでほかの作業ができるように、 Vivado の合成エンジンがバックグラウンドで実行されます。合成プロセスがバックグランドで実 行している間、Vivado IDE のビューの確認、レポートの実行、デザインの評価などの作業を引き 続き行うことができます。Vivado IDE の一番下の [Log] ビューに合成ログが表示されます。これ は [Reports] ビューにも表示されます。

合成が終了したら、次のステップを尋ねるメッセージが表示されます。

図 24 : [Synthesis Completed] ダイアログ ボックス

[Run Implementation] を選択し、[OK] をクリックします。 2.

インプリメンテーション プロセスが起動しますが、ある程度の初期化が実行された後にこのプロ セスはバックグランドで実行されます。このチュートリアルの次の手順では、インプリメンテーショ ンの終了を待つ間に、合成されたデザインのデザイン解析を実行します。

手順 8 : 合成済みデザインの解析

手順 8 : 合成済みデザインの解析

合成済みデザインを開いて、デザイン解析、タイミング制約定義、I/O 配置、フロアプラン、デバッグ コア の挿入などを実行します。これらの機能についてはほかのチュートリアルで説明されていますが、この手 順でも簡単に説明します。

Flow Navigator で [Open Synthesized Design] をクリックし、デザインが読み込まれるのを待ちます。 1. Vivado IDE で合成済みデザインを開いても、インプリメンテーションはまだバックグラウンドで続行さ れています。合成済みデザインを確認している間にインプリメンテーションが完了し、次のステップを 選択する [Implementation Completed] ダイアログ ボックスが開きます。 図 25 : [Implementation Completed] ダイアログ ボックス 何も選択せずに [Cancel] をクリックしてダイアログ ボックスを閉じます。 2. 合成済みデザインは開いたままの状態です。インプリメント済みデザインは合成済みデザインの 機能を確認してから開きます。 メイン ツールバーのレイアウト セレクターから [Default Layout] を選択します。 3.

Vivado IDE の下部にある [Reports] ビュー タブをクリックします。 4.

[Reports] ビューが開かない場合は、[Window] → [Report] をクリックして開きます。 [Vivado Synthesis Report] をダブルクリックしてレポートを確認します。

5.

[Utilization Report] をダブルクリックしてレポートを確認します。 6.

確認を終えたらすべてのレポートを閉じます。 7.

Vivado IDE の一番下の [Messages] ビュー タブをクリックします。 8.

[Messages] ビューが開かない場合は、[Window] → [Messages] をクリックして開きます。 [Messages] ビューの上部には、エラー、クリティカル警告、警告、情報、ステータスといった種類 別にメッセージを表示したり非表示にすることができるフィルター機能があります。

手順 8 : 合成済みデザインの解析 [Synthesis] メッセージを展開表示します。 10. 合成メッセージをスクロールすると、ソース ファイル内の特定の行へのリンクがあります。リンクをいく 11. つかクリックしてみると、テキスト エディターが開き、そのソース ファイルの該当行がハイライトされた 状態でソース ファイルが開きます。 図 26 : ソース ファイルにリンクされている合成メッセージ

Flow Navigator で [Synthesis] → [Synthesized Design] → [Report Timing Summary] をクリックしま 12.

す。

[Report Timing Summary] ダイアログ ボックスが開きます。ダイアログ ボックス内のフィールドや オプションを確認します。

デフォルトの設定のまま [OK] をクリックします。 13.

手順 8 : 合成済みデザインの解析

図 27 : タイミング サマリ レポート

インプリメンテーション前のタイミング概算を表示する [Timing Summary] ビューが表示されま す。ビューの左側のツリー表示のカテゴリをいくつかクリックしてみます。

Flow Navigator で [Report Power] をクリックします。 14. [Report Power] ダイアログ ボックスが開きます。ダイアログ ボックス内のフィールドやオプション を確認します。 デフォルトの設定のまま [OK] をクリックします。 15. [Power Results] ビューが開きます。インプリメンテーション前の消費電力概算を表示する [Power Results] ビューが表示されます。このレポートはダイナミックで、マウスでレポートの特定 セクションをポイントすると、その箇所の詳細が図 28 のように表示されます。 ビューの左側のツリー表示のカテゴリをいくつかクリックしてみます。 図 28 : 消費電力レポート

手順 9 : インプリメント済みデザインの解析

[Timing Summary] および [Power Results] ビューを閉じ、またテキスト エディターのウィンドウが開い 16. ていればそれも閉じます。

手順 9 : インプリメント済みデザインの解析

Vivado IDE ではインタラクティブにメモリにあるデザイン上でデザイン制約およびネットリストを変更する ことができます。デザインを保存すると、制約の変更が元のソースの XDC ファイルにも書き込まれます。 または、変更を新しい制約ファイルに保存して、元の制約を保持することもできます。これにより、元のソ ース ファイルを変更することなく、フロアプランも含め、さまざまなタイミングおよび物理制約を試すことが できます。インプリメント済みデザインを開く

Flow Navigator で [Open Implemented Design] をクリックします。 1. [Yes] をクリックして合成済みデザインを閉じ、保存するかどうか尋ねるメッセージが表示されたら 2. [Don't Save] をクリックします。 インプリメント済みデザインを読み込むと、そのインプリメンテーション結果が [Device] ビューに 表示されます。

Vivado IDE の下部にある [Reports] ビュー タブをクリックします。 3.

[Reports] ビューが開かない場合は、[Window] → [Report] をクリックして開きます。配置配線か らのレポートをいくつか選択して確認します。確認したら、各レポートを閉じます。

Vivado IDE の一番下の [Messages] ビュー タブをクリックします。 4.

[Reports] ビューが開かない場合は、[Window] → [Report] をクリックして開きます。 [Collapse All] ボタンをクリックし、展開されたメッセージをすべて閉じます。

5.

[Implementation] フォルダーを展開表示します。 6.

[Design Initialization]、[Opt Design]、[Place Design]、[Route_Design] のメッセージを確認しま す。

配線の解析

デザインが配置配線されたら、タイミング レポートを生成してすべてのタイミング制約が満たされたかどう かを検証します。[Timing Report] ビューでパスを選択して [Device] ビューでその配線されたパスを確 認します。タイミングに問題がある場合は、RTL ソース ファイルまたはデザイン制約を確認して、問題を 解決します。

[Device] ビューで [Routing Resources] ボタンをクリックしてデバイス配線を表示します。 1.

[Device] ビューに配線された接続が表示されます。配線のエレメントを表示するにはデバイスを 拡大表示し、配線を全体的に確認するには縮小表示にします。

手順 9 : インプリメント済みデザインの解析

図 29 : [Routing Resources] ボタン

[Device] ビューで [Auto Fit Selection] ボタンをクリックすると、選択したオブジェクトが自動的に画面 2.

にフィットした状態で中央に表示されます。

Flow Navigator で [Implemented Design] → [Report Timing Summary] をクリックします。 3.

[Report Summary Timing] ダイアログ ボックスで [OK] をクリックしてデフォルトのレポートを生成しま 4.

す。

[Timing Summary] ビューの左側で [Intra-Clock Paths] → [bftClk] → [HOLD] をクリックします。 5.

表形式のレポートの右端にあるパスをクリックすると、それが [Device] ビューで選択されてハイラ イトされます。さまざまなパスをクリックして、パス配線を確認してください。

[Timing Summary] ビューの左側で [Intra-Clock Paths] → [bftClk] → [HOLD] をクリックします。 6.

表形式のレポートの右端にあるパスをクリックすると、それが [Device] ビューで選択されてハイラ イトされます。さまざまなパスをクリックして、パス配線を確認してください。

手順 9 : インプリメント済みデザインの解析

図 30 : タイミング パスの配線の確認

[Device] ビューまたは [Timing Summary] ビューでタイミング パスを選択した状態で右クリックし、 7.

[Schematic] をクリックします。

注記 : [Schematic] ビューは F4 キーを押しても開くことができます。

[Schematic] ビューが開き、選択したタイミング パスの回路図が表示されます。[Expand]、 [Collapse Outside]、[Expand Cone] などの [Schematic] ビューのポップアップ メニューのコマンド を使用し、回路図を表示形式を変更してタイミング パス上のロジック セルを確認します。 [Schematic] ビューを閉じます。

8.

[Device] ビューで [Routing Resources] ツールバー アイコンを再びクリックし、配線リソースの表示を 9.

オフにします。

これで [Device] ビューには配置されたインスタンスだけが表示され、配線された接続の詳細は 表示されなくなります。

手順 11 : ビットストリーム ファイルの生成

手順 11 : ビットストリーム ファイルの生成

XDC 制約ファイルには、すべての I/O ポートに対する LOC および IOSTANDARD 制約が含まれるの で、ビットストリームを生成できます。[Write Bitstream] を実行する前に、このコマンドの設定を確認しま す。

Flow Navigator で [Program and Debug] の下の [Bitstream Settings] をクリックします。 1.

[Project Settings] ダイアログ ボックスが開きます。write_bitstream コマンドのオプションをここで 設定できます。これらのオプションの説明や使用方法については、『Vivado Design Suite ユー ザー ガイド : プログラムおよびデバッグ』 (UG908) を参照してください。

図 31 : ビットストリームの設定

[Cancel] をクリックして、[Project Settings] ダイアログ ボックスを閉じます。 2.

Flow Navigator の [Program and Debug] の下にある [Generate Bitstream] ボタンをクリックします。 3.

ビットストリームが生成されたら [Bitstream Generation Completed] ダイアログ ボックスが開くので 4.

[OK] をクリックしてレポートを表示します。

手順 12 : Vivado の終了

Vivado では次の 2 つのファイルが作成されます。手順 13 : ジャーナル ファイルからの Tcl スクリプトの作成

Vivado ツールのログ ファイル (vivado.log) : Vivado のセッション中に実行された Tcl コマンドの履歴と結果がす べて含まれます。

Vivado ツールのジャーナル ファイル (vivado.jou) : Vivado のセッション中に実行された Tcl コマンドのみが含ま れます。その他の詳細は、ログ ファイルに記録されます。

これらのファイルから、さまざまなデザイン タスクを実行するために Vivado ツールで使用された Tcl コマ ンドを学ぶことができます。Vivado のジャーナル ファイルも新しく Tcl スクリプトを作成するにあたり参考 にすると便利です。完了したデザイン フローの vivado.jou を使用すると、デザインを完成させるために 使用された Tcl コマンドがすべて確認できます。すべての Tcl コマンドおよびそのオプションの詳細は、 『Vivado Design Suite Tcl コマンド リファレンス ガイド』 (UG835) を参照してください。

[File] → [Exit] をクリックするか、Tcl コマンド ラインで「exit」と入力します。 1.

[OK] をクリックして Vivado ツールを閉じます。 2.

Vivado のログ ファイル (vivado.log) を確認します。Windows の場合は、ファイル ブラウザーを使 3. 用した方が確認しやすいでしょう。 <Extract_Dir>/Vivado_Tutorial/vivado.log 注記 : これは、演習 2 の手順 1 の [作業フォルダー] で設定したディレクトリです。 内容を確認したら、ファイルを閉じます。 4.

手順 13 : ジャーナル ファイルからの Tcl スクリプトの作

成

バッチ モードで実行すると、Vivado IDE で実行するよりも高速で、メモリ使用量も少なくて済みます。デ ザインを完成させるのに複数 run が必要な場合は、Tcl スクリプトを使用してフローを自動化することを お勧めします。また、主なステップの後にレポート生成コマンドをスクリプトに追加し、特定ファイルおよ びディレクトリにレポートが出力されるように設定することもできます。ジャーナルの確認

演習の手順 1 ~ 12 に沿って作業を行ったので Vivado ツールで自動的にジャーナル ファイルが作成 されました。ここではこのファイルから Tcl スクリプトを手動で作成します。新しいスクリプトを実行すると、 Vivado IDE を使用してこれまでの手順に沿って作成したように、プロジェクト ファイル (.xpr) およびディ レクトリ構造が作成されます。このプロジェクトを Vivado IDE に読み込むと、予測通りの結果およびプロ ジェクト ステータスが表示されます。 テキスト エディターで vivado.jou を開きます。 1.Vivado のジャーナル ファイル (vivado.jou) を確認します。Windows の場合は、ファイル ブラウザ 2.

ーを使用した方が確認しやすいでしょう。

<Extract_Dir>/Vivado_Tutorial/vivado.jou

手順 13 : ジャーナル ファイルからの Tcl スクリプトの作成 図 32 : 演習 2 の Vivado ジャーナル ファイル 注記 : Linux を使用している場合は、表示されるパスは異なります。 コメント (# で始まる行) は不要なので削除します。 3. Tcl スクリプトで IDE は開きたくないので、start_gui の行も削除します。 4.

[Save As] コマンドでファイルを <Extract_Dir>/Vivado_Tutorial/run_bft.tcl に保存します。 5. run_bft.tcl スクリプトを開いた状態で、「project_bft」を検索し、「project_bft_batch」にすべて置換 6. します。 このスクリプトを確認し、演習 1 で使用した非プロジェクト モードと、このプロジェクト モードとの違い 7. を確認します。 プロジェクトの作成および制約セットの設定に add_files および set_property コマンドが使用され ていることに留意してください。 また、synth_design などの代わりに launch_runs が使用されていることにも注目してください。プ ロジェクト ベースのデザインを作成または実行するときは launch_runs を使用します。

注意 : synth_design や opt_design などの個々のコマンドを launch_runs と併用すると、 プロジェクトが破損する可能性があるため、推奨しません。launch_runs コマンドには、コマ ンドを個別に実行して、カスタム レポートを作成する Tcl オプションがあります。詳細は、 『Vivado Design Suite Tcl コマンド リファレンス ガイド』 (UG835) を参照してください。

![図 4 にあるように [Timing Constraints] ビューの左側にある [Clocks] の下にある [Create Clock] をダ 2.](https://thumb-ap.123doks.com/thumbv2/123deta/6717579.708768/12.918.103.813.320.801/図4にあるようにTimingConstraintsビューの左側にあるClocksの下にあるCreateClockをダ2.webp)

![図 7 : [Export Constraints] コマンド ファイルの名前とディレクトリを入力し、[OK] をクリックします。](https://thumb-ap.123doks.com/thumbv2/123deta/6717579.708768/15.918.265.681.458.674/7Exportコマンドファイルの名前とディレクトリを入力OKクリックます.webp)

![図 8 : 最大化した [Path Properties] ビュー](https://thumb-ap.123doks.com/thumbv2/123deta/6717579.708768/18.918.111.868.127.587/図8最大化したPathPropertiesビュー.webp)