アドイン・カードまたはマザーボードで

PCI Express

®

3.0 CEM

仕様に基づいたレシーバ・

テストに合格する方法

Application Note

1.

はじめに3

2. RX

テストと校正手順の概要4

2.1.

一般的なRX

テスト:概要4

2.2. PCIe CEM

リビジョン3.0

用のRX

ストレス・テスト信号の校正方法5

2.3.

校正およびテスト手順7

3.

校正、ディエンベディング、BERT-EQ

校正のセットアップ9

3.1. PCI-SIG

から提供されるテスト・ボード:CBB

およびCLB

9

3.2.

校正のセットアップ9

3.3.

テスト・セットアップのディエンベディング11

3.4. BERT PG

イコライゼーションの校正12

4.

ストレス信号の校正14

4.1. RJ

の校正14

4.2. SJ

の校正16

4.3. DM-SI

の校正17

4.4.

最終ストレス信号の校正、EH

およびEW

18

4.5. Agilent N5990A-101

19

5. RX

テスト20

5.1. AIC

のテスト・セットアップ20

5.2. MB

のテスト・セットアップ21

5.3. DUT

のループバックへの設定22

5.4.

実際のRX

テストと測定時間24

6.

まとめ27

7.

付録28

7.1.

機器28

7.2. CEM

およびPHY

テスト仕様バージョン0.9

に基づいたRX

ストレス信号の仕様

29

7.3. TX

イコライゼーションおよびプリセット29

7.4.

参考資料30

7.5.

用語集31

目次

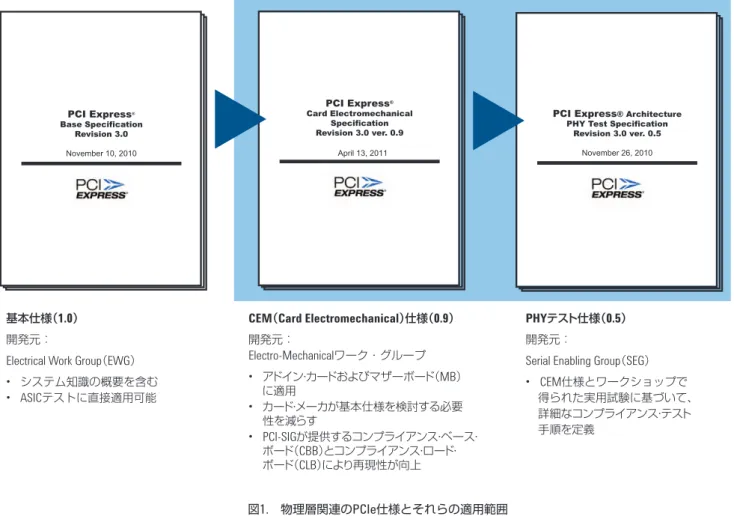

図1. 物理層関連のPCIe仕様とそれらの適用範囲

1.

はじめに

PCI Express® Base Specification Revision 3.0 November 10, 2010 PCI Express® Card Electromechanical Specification Revision 3.0 ver. 0.9 April 13, 2011PCI Express® Architecture PHY Test Specification

Revision 3.0 ver. 0.5

November 26, 2010

CEM(Card Electromechanical)仕様(0.9) 開発元:

Electro-Mechanicalワーク・グループ 基本仕様(1.0)

開発元:

Electrical Work Group(EWG) • システム知識の概要を含む • ASICテストに直接適用可能

PHYテスト仕様(0.5) 開発元:

Serial Enabling Group(SEG) • CEM仕様とワークショップで 得られた実用試験に基づいて、 詳細なコンプライアンス・テスト 手順を定義 • アドイン・カードおよびマザーボード(MB) に適用 • カード・メーカが基本仕様を検討する必要 性を減らす • PCI-SIGが提供するコンプライアンス・ベース・ ボード(CBB)とコンプライアンス・ロード・ ボード(CLB)により再現性が向上 本書の発行時点では、

CEM

仕様(現行バージョン0.9

)とPHY

テスト仕様(現行 バージョン0.5

)はいずれもリリースされていません。このアプリケーション・ ノートは、発行時点での規格の状況を反映しています。 本書の目的は、カード・ベンダのプレリリース・テストを支援することです。 仕様はまだ確定していないので、校正のターゲット値や校正手順は変更され る可能性があります。関連する仕様の最新バージョンを必ず参照して、上記 の内容と異なる場合は、変更があったかどうかを確認してください。2010

年11

月にPCIe®

基本仕様のリビジョン3.0

がリリースされて以降、多くの半導体 ベンダがこれに基づいてベアASIC

をテストしています[1

]。現在は、PCIe 3.0

アドイ ン・カード(AIC

)およびPCIe 3.0

スロットを備えたマザーボード(MB

)が開発されてい ます。これらの製品は、PCIe CEM

(Card Electromechanical

)仕様[2

]に基づいて テストする必要があります。これに対するPHY

テスト仕様[3

]は、現在SEG

(Serial

2.1

一般的な

RX

テスト:概要

RX

テストでは、ワーストケースの入力信号でも、レシーバがデジタル信号のコンテン ツを正しく検出できることを確認します。このテストでは、ビット・エラー・レート・ テスタのパターン・ジェネレータ(BERT PG

)から被試験RX

に、校正済みのストレス ド・アイ信号を印加します。この信号は、ターゲット・システム内で動作しているRX

の入力で予測される信号劣化から構成されています。これには、ジッタなどのタイミ ング障害や、クロストークをエミュレートする重畳電圧が含まれます。後者はノイズ と呼ばれることがあります。ノイズは通常、ガウス分布になりますが、このテスト に用いられるノイズ電圧の形状は、正弦波です。 デジタル・コンテンツの検出が正しいかどうかを確認するには、RX

の出力信号をDUT

のトランスミッタ(TX

)1経由で内部的にループバックさせた後、BERT

のエラー・ ディテクタ(ED

)を使用します。RX

テストの簡素化したブロック図を図2

に示します。 図2. RXテストの簡素化した ブロック図2. RX

テストと

校正手順の概要

PCIe 2.x

からリビジョン3.0

への最大の変更点は、カード上のRX

テストが標準になっ たことです。このアプリケーション・ノートでは、校正手法とテストに関する情報とと もに、Agilent

から提供されているツールについても紹介しています。これらのソリ ューションは、リビジョン3.0

に移行しようとしているインテグレータを支援するため に、関連するPCI-SIG®

ワークグループおよびワークショップへのアクティブな参加に よって得られたAgilent

の経験を活用しています。本書について

このアプリケーション・ノートでは、PCIe 3.0 AIC

またはMB

に対するレシーバ・ コンプライアンス・テストの実行に必要な以下のステップについて説明します。1.

PHY

テスト仕様に基づいて、閉じたアイのレシーバ・ストレス信号を校正 します。これは、次の2

点でPCI Express

リビジョン2.x

と異なります。a

)RX

ストレス信号が、個々の信号劣化ではなく、アイの高さと幅で指定 されるようになりました。b

) 仕様の基準面がASIC

内部、すなわち(基準)レシーバのイコライゼーシ ョンの後に定義されているため、測定されたテスト信号のポスト・プ ロセッシングが必要になります。2.

リンク・トレーニングおよびステータス・ステート・マシン(LTSSM

)で被 試験デバイス(DUT

)を操作し、ループバック状態にします。3.

ループバックした信号のビットとエラーをカウントして、ビット・エラー 比(BER

)を求め、コンプライアンスを確認します。RX

TX

I/OセルJ-BERT N4903B

ル ー プ バ ッ クAS

IC

2.2. PCIe CEM

リビジョン

3.0

用の

RX

ストレス・テスト信号の校正方法

ストレス信号の適切な校正は、有効で再現性のあるテスト結果を実現し、相互運用性 を保証するために不可欠です。CEM

仕様では、この目的を達成するためにいくつか の手法が採用されています。第1

に、基本仕様に比べてRX

仕様が簡素化されていて、 コモン・モード電圧ストレスやジッタ耐力周波数掃引などのいくつかのパラメータが削 除されています。第2

に、PCI-SIG

リビジョン3.0

テスト・ツール(コンプライアンス・テ スト・ボードおよびSigTest

ソフトウェアを含む)により、明確に定義されたテスト環 境が構成されます。 ただし、PCIe 2.x

で使用されていた単純な手法、すなわちランダム・ジッタと正弦波 ジッタ(RJ

とSJ

)を個別に校正することによりストレス信号を指定するという手法は、 以下の理由で使用できません。•

実際のシステムにも、RJ

と有界非相関ジッタ(BUJ

)は存在します。これは、PG

のRJ

と正弦波ジッタ(SJ

)によりエミュレートされます。しかし、8 GT/s

の速度では、 ジッタの最大の成分はプリント基板材料の高周波損失から生じ、データ依存ジッタ (DDJ

)、特に符号間干渉(ISI

)の原因となります。SIG

から提供されるテスト・ボードを使用するリビジョン3.0

のAIC

テスト・セットア ップでは、DDJ

の大部分は、リビジョン3.0

コンプライアンス・ベース・ボード(CBB

) ライザ・カードによって意図的に発生されるものです(図7

を参照)。一方、テスト・ セットアップのそれ以外のコンポーネント(ケーブル、スプリッタ、DC

ブロック、そ れにBERT PG

自体)からも、無視できないDDJ

が生じます。PCIe 2.x

に比べる と、各ベンダのテスト・セットアップ間のわずかな違いが、結果のストレス信号に より大きな影響を及ぼします。DDJ

に影響するすべてのパラメータを正確に指定 し、十分な確度で個別に測定することは、現実的に困難です。このため、ストレ ス信号は、影響するすべての効果の結果として、アイの高さ(EH

)とアイの幅(EW

) で表されるアイの開口部によって指定されます。• RX

入力を最も正確にエミュレートするテスト・ポイント、すなわちコンプライアン ス・ロード・ボード(CLB

)のTX

コネクタでテスト・パターンのストレス成分を直接 測定することは不可能です。このテスト・ポイントではアイが閉じているからです。•

このため、基本仕様と同様に、ストレス信号のアイの開口部は、アダプティブ基準 イコライザ(EQ

)の後で定義されています。このイコライザは、連続時間リニア・イ コライザ(CTLE

)とデシジョン・フィードバック・イコライザ(DFE

)を備え、基準ク ロック・リカバリ(CR

)回路からクロックが供給されます[1

]。基準

RX

lim TP 6 基準クロック -16 -14 -12 -10 -8 -6 -4 -2 01E+07 1E+08 1E+09 1E+10 1E+11

x Z-1 -d1 xk yk yk* Σ 判定回路 VEYE TEYE

1

TP 6FF

CR

CTLE

リミット・ アンプDFE

TP 2-P 1E+09 1E+08 -16 -20 -30 -40 -50 -60 -14 -12 -10 -8 -6 -41E+05 1E+06 1E+07 1E+08 1E+09

①

. 4 GHz

にピークがある7

種類の異な る「DC

減衰」設定を持つCTLE

②.

ピークがなく10 MHz

の帯域幅を 持つOJTF

によって指定された基 準CR

③. d1

のリミットが±30 mV

に指定さ れている1

タップDFE

RX

ストレス信号の校正には、少なくとも2

つの方法が使用できます。1

つは基本仕 様で用いられている方法、もう1

つは以下で説明する代替方法です。後者の方法は、RX

テスト中はBERT PG

がTX

をエミュレートするという事実に基づいています。こ のため、RX

ストレス信号の校正には、TX

コンプライアンス・テストと同じ方法が使用 できます。すなわち、指定されたすべての信号劣化を伴うリビジョン3.0

コンプライ アンス・パターンをリアルタイム・オシロスコープで捕捉し、PCI-SIG

メンバに提供さ れているSigTest

ソフトウェアでポストプロセッシングを行います。これにより、基準RX

のCTLE

とDFE

が最適化され、EH

とEW

が計算されます。 図4. 基本仕様とCEM仕様の校正方法の比較 基本仕様の方法 Seasimを使用: 平均ステップ応答、シミュレートされた パターン/信号劣化/基準RX CEMの方法 SigTestを使用: コンプライアンス・パターン+信号劣化「オン」、 オシロスコープのアベレージングなし N4916B N4915A オプション014B N4903B 81150A 長い校正チャネル CBBリビジョン3 CBBリビジョン3 CLB N4916B J-BERT N4903B SEASIM 入力パラメータ: RJ=2 ps、rms SJ=0.1 UIpp DM-SI=14 mVpp DM-SI EH @TP2-P カスタム・テスト・ボード TP2 ブレークアウト・ チャネル TP6 複製 チャネル TP5 ASIC RX DUT TX 内部 ルー プバ ッ ク TP3=TXパッド TP2=RXピン TP2-P=EQ後のRX 0 8 16 24 32 40 48 56 64 72 80 0 10 20 30 40 50 Ca lc ulat ed Eye H ei gh t [ mV] 基準 クロック この校正方法は、Seasim

ソフトウェアを使用して平均ステップ応答に基づいてスト レス信号をシミュレートする基本仕様の方法とは異なります(この方法が選ばれた理 由は、測定がオシロスコープのノイズの影響を受けないことでした[4

])。注記:SEGでは現在、EWG(Electrical Work Group)が基本仕様で採用している統計アイ解 析シミュレータ(SeaSim)を使用する方法と、PHYテスト仕様で指定されているSigTestを 使用するSEGの方法との間の相関を確認する作業を進めています。この作業の結果によっ ては、現在使用されている方法に調整が必要になる可能性があります。

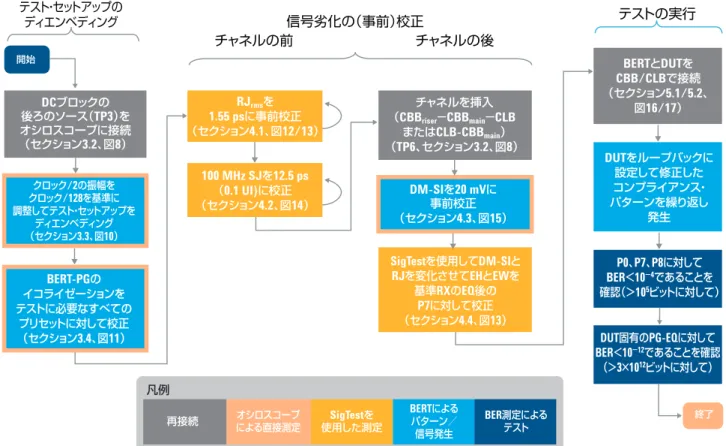

凡例 信号劣化の(事前)校正 チャネルの前 チャネルの後 テスト・セットアップの ディエンベディング テストの実行 BERT-PGの イコライゼーションを テストに必要なすべての プリセットに対して校正 (セクション3.4、図11) RJrmsを 1.55 psに事前校正 (セクション4.1、図12/13) クロック/2の振幅を クロック/128を基準に 調整してテスト・セットアップを ディエンベディング (セクション3.3、図10) 100 MHz SJを12.5 ps (0.1 UI)に校正 (セクション4.2、図14) DM-SIを20 mVに 事前校正 (セクション4.3、図15) チャネルを挿入 (CBBriser−CBBmain−CLB またはCLB-CBBmain) (TP6、セクション3.2、図8) DCブロックの 後ろのソース(TP3)を オシロスコープに接続 (セクション3.2、図8) SigTestを使用してDM-SIと RJを変化させてEHとEWを 基準RXのEQ後の P7に対して校正 (セクション4.4、図13) DUTをループバックに 設定して修正した コンプライアンス・ パターンを繰り返し 発生 BERTとDUTを CBB/CLBで接続 (セクション5.1/5.2、 図16/17) P0、P7、P8に対して BER<10−4であることを 確認(>105ビットに対して) DUT固有のPG-EQに対して BER<10−12であることを確認 (>3×1012ビットに対して) 終了 BERTによる パターン/ 信号発生 SigTestを 使用した測定 再接続 による直接測定オシロスコープ BER測定によるテスト 開始

図5. PCIe CEM仕様3.0リビジョン3.0に基づいたBERT PGのディエンベディング、 ストレスド・アイ信号校正、RXテストのフロー・チャート

2.3.

校正およびテスト手順

8 GT/s

という高いデータ・レートでは、テスト・セットアップのディエンベディングを 行って、BERT

のEQ

により周波数応答を補正する必要があります。このポストカー ソル設定は、RX

テスト中にEQ

プリセットを作成する際に考慮する必要があります。 ジェネレータの調整については、セクション3

で説明します。個々の信号劣化の事前 校正を伴うストレス信号の2

段階の校正と、EH

およびEW

の最終調整については、セ クション4

で説明します。DUT

のループバックへの設定とRX

テスト自体については、 セクション5

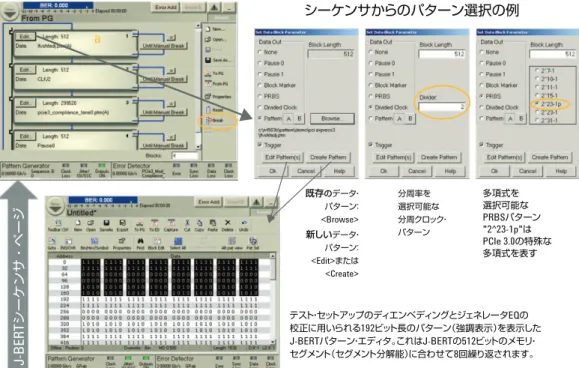

で説明します。図6. パターン・シーケンサを使用するAgilentのJ-BERTのデータ・セットアップでは、 休止、分周クロック、PRBS、および<Break>ボタン(円内)によるそれらの間の高速切 り替えなどにより、アルゴリズム・パターンの設定が容易 シーケンサからのパターン選択の例 既存のデータ・ パターン: <Browse> 分周率を 選択可能な 分周クロック・ パターン 新しいデータ・ パターン: <Edit>または <Create> 多項式を 選択可能な PRBSパターン "2^23-1p"は PCIe 3.0の特殊な 多項式を表す テスト・セットアップのディエンベディングとジェネレータEQの 校正に用いられる192ビット長のパターン(強調表示)を表示した J-BERTパターン・エディタ。これはJ-BERTの512ビットのメモリ・ セグメント(セグメント分解能)に合わせて8回繰り返されます。

J-B

ER

T

シ ー ケ ン サ ・ ペ ー ジa

注記:校正プロセスの各ステップでは、さまざまなデータ・パターンが必要になります。 これらの設定と使用は、Agilent N4903B J-BERT高性能シリアルBERTの強力なパターン・ シーケンサと、その手動シーケンス進行機能(図6を参照)によって簡単に行えます。3.1. PCI-SIG

から提供されるテスト・ボード:

CBB

および

CLB

図7

に示すのは、CEM

仕様に基づくテストに使用されるリビジョン3.0 CBB

およびコ ンプライアンス・ロード・ボード(CLB

)です。リビジョン2

と異なり、CBB

はメイン・ カードとライザ・カードの2

つのボードから構成されます(図7e

および7f

)。2

つのボー ドの間のコネクタとライザ・カード上のトレースが追加されたことにより、新しい(リ ビジョン3

)CBB

はサーバ・ボード上の条件をより正確に反映しています。 ライザ・カードとCLB

のRX SMP

コネクタは、ASIC

のTX

のパッドと電気的に同一で あることを意図しています。このため、パッケージをシミュレートする構造がカード 上に存在します(図7a

、b

、g

)。CLB

には2

つのバージョンがあります。1

つは1x

と16x

のコネクタを持つもの、もう1

つは4x

と8x

のコネクタを持つもの(図には示して いない)です。3.

校正、ディエンベディ

ング、

BERT-EQ

校正の

セットアップ

図7. リビジョン3のCBBおよびCLBボード:a)とb)CLBおよびライザ・カードのパッケ ージ・シミュレーション部分の詳細図とg)等価回路、1xおよび16x CLB、c)RX側、d)TX 側、e)CBBライザ・カード、f)CBBメイン・ボード。CLB用のPCIeコネクタ(中央)とライ ザ・カード用のエッジ・コネクタ(左)を装備 CBBライザ・カードと CLBのRX SMPコネクタは、 TXパッドを表しています。 ボード上の構造 (C−トレース−C、拡大図)は、 ICパッケージをシミュレート しています(拡大図)。e)

CBBライザ・カード

f)

CBBメイン・カード

d)

CLB x1/x16

TX側

c)

CLB x1/x16

RX側

a)

b)

g

)

3.2.

校正のセットアップ

校正のセットアップを図8

に示します。BERT PG

の出力信号は、差動ノイズ電圧 と重畳されます。これが差動モード正弦波干渉(DM-SI

)です。図8

に示すように、Agilent N4903B

からドライブされるAgilent N4916B

ディエンファシス信号コンバ ータの出力が、N4903B-J20

のP1

出力からのDM-SI

と、非対称スプリッタによって 結合されます。必要なAC

結合を実現するために、DC

ブロックが用いられます(必要 な測定器と付属品の一覧については、セクション7.1

の表2

を参照してください)。低 損失ケーブルは、両端にSMP

コネクタを備え、位相マッチングされており、テスト信 号発生器出力(TP3

)を表しています。CBB

およびCLB

がチャネルを構成し、アイが 閉じる原因となるストレス信号のDDJ

の大部分はここから生じます。テスト・ポイントの 番号は基本仕様に 基づく

TP

6

=R

X

ピ ンTP

3

=TX

パ ッ ド DM-SI N4916B N4903B • AgilentJ-BERT N4903B 内部ジッタの生成およびオプション J20による2.1 GHz DM-SIの生成 • N4916B ディエンファシス・シグナル・コンバータ • DCブロックおよび非対称加算器 DCブロック 非対称スプリッタTP

2-P

=EQ

後 のR

X

校正の場合 チャネル前: ケーブル をSMP→SMA アダプタを通して オシロスコープへ チャネル後: ケーブル をCBBライザ・ カードまたはCLBのRX SMP コネクタへ、ケーブルをCLB またはCBBメイン・カードの TX SMPコネクタからオシロスコープへCBB +

CLB

2/14 dB 2 図8. 校正のセットアップAIC

とMB

のどちらをテストするかによって、接続とシグナル・フローが異なります。• AIC

:図8

で1

と記されたケーブル(ケーブル

)が、CBB

のライザ・カード上のRX

コネクタに接続されます。信号は、両方のPCIe

コネクタからCBB

メイン・ボード経 由でCLB TX SMP

コネクタに流れます(図16

も参照)。• MB

:ケーブル

は、CLB

上のRX

コネクタに接続され、信号はCBB

メイン・カード 上のPCIe

コネクタ経由でTX

コネクタに流れます(図17

も参照)。 校正の際には、いくつかのパラメータが図8

のTP3

(チャネルの前の点線

)またはTP6

(チャネルの後ろの実線

)で測定されます。3.3.

テスト・セットアップのディエンベディング

前述のように、どちらのテスト・ケースでも、AIC

テストではライザ・カード上、MB

テストではCLB

上にあるRX

コネクタは、PCIe ASIC

のTX

パッドを表します。すなわ ち、図8

に示すケーブル・ペア

のSMP

コネクタでは、ほぼ理想に近い乱れのない信 号性能が実現され、以下のような理由で調整が必要になります。1.

テスト機器の固有の信号性能と、ケーブル、スプリッタ、DC

ブロックを組み合 わせたものの周波数応答は、理想的ではありません。2.

同時に、テスト機器、セットアップ、複数の測定器ベンダから提供されるアク セサリに関して、パラメータは同一ではありません。 必要な信号性能は、低周波(LF

)と高周波(HF

)の両方の信号成分に対して振幅が等 しく、全体的にフラットな周波数応答です。これを実現するには、十分な大きさの 容易に観察できるHF

成分とLF

成分を持つテスト・パターンを使用して、BERT PG

のEQ

を調整します。このために、パターンは64

個の1

と64

個の0

(LF

部分を表すク ロック/128

)の後に、64

ビットの1010

(4 GHz

の基本波周波数を表すクロック/2

)が続 く形を取ります。コンプライアンス・パターンにも、このようなセクションが含まれて います。 図9a

は、テスト・セットアップ全体のTP3

での理想的でない周波数応答を示していま す。HF

パターンはLF

部分に比べて約0.5 dB

下がっています。図9b

は、調整後の波 形です。これを実現するには、HF

とLF

の信号振幅が等しくなるようにN4903B/

N4916B

出力のディエンファシス・ポストカーソル(Post-Cur1

)の設定を変更した後、N4903B/N4916B

の出力振幅を800 mVpp

に再調整します(図10

を参照)。 図9. 64個の1、64個の0、64個の"1010"の繰り返しパターンのスクリーンショット a)HF信号(クロック/2)の振幅がLF信号(クロック/128、64×1-64×0)に比べてわずかに 小さい。b)テスト・セットアップの周波数応答が-0.7 dB補正されているa)

b)

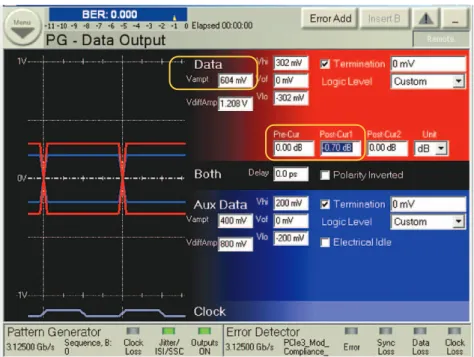

a) b)図10. J-BERTのデータ出力セットアッ プ・ページ:黄色の枠で囲まれているの は振幅(Vampt)とEQ(Pre-Cur、Post-Cur1) の入力フィールド。Post-Cur2はこのアプ リケーションでは使用しません。 振幅の再調整が必要な理由は、リビジョン

3.0

の定義によると、LF

信号が減衰または ディエンファシスを受けても、振幅は最大信号(HF

部分)に関連して決まるからです。 上記の調整によって得られたPost-Cur1de-embed

とVamptde-embed

の値は、後で使用 するために記録します。関連するすべてのJ-BERT

設定の一覧を、セクション4

末尾 の表1

に示します。3.4. BERT PG

イコライゼーションの校正

RX

テストの際には、いくつかのTX

イコライゼーションがBERT PG

によってエミュレ ートされます。これらはプリセットP0

、P7

、P8

であり、DUT

によってはもう1

つの 設定が加わることもあります(セクション5.4

を参照)。プリセットは、N4916B

の工 場校正とリニアリティによって十分な確度で実現できます(下の2

を参照)。ただし、SEG

ではBERT PG

のEQ

を校正することを推奨しているので、その手順を以下に簡 単に説明します[5

]。1.

適切なパターンを出力するようにBERT PG

を設定します。例えば、テスト・セ ットアップのディエンベディングに使用される128

ビットのクロック/128

パター ンと64

ビットのクロック/2

パターンの組み合わせです(図6

を参照)。2.

表5

に基づいて、BERT PG

を指定された値に設定します。この際、ディエンベ ディング値PostCurs1de-embed

を考慮します。Pre-Cur

=プリシュート、Post-Cur1

=ディエンファシス+Post-Cur1

de-embed3.

Va

、Vb

、Vc

、Vd

の 電 圧 をオシロスコープで 測 定 し ま す。 こ の 際、Vb

に はV

ampliude測定、V

dにはV

p-p測定、V

aとV

cには手動マーカ測定を使用します(図11

を参照)。4.

次の式を使用して、プリシュートとディエンファシスの実際の値を求めます。 ディエンファシス=20log10Vb/Va

、プリシュート=20log10 Vc/Vb

、(ブースト=20log

10V

d/V

b)5.

必要なディエンファシスとプリシュートが得られるように、J-BERT

のEQ

設定Pre-Cur

とPost-Cur1

を調整します。6.

振幅が指定されたウィンドウの範囲外の場合(表3

を参照)、J-BERT

のVampt

を 変えて最大振幅(V

d)を指定された値(800 mV

diff,pp)に再調整し、上で求めた すべての値を後で使用するために記録しておきます(表1

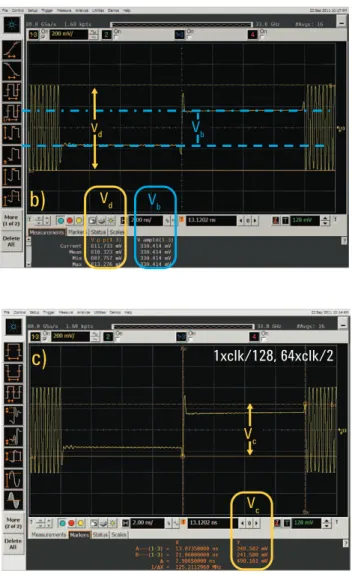

を参照)。図11. P7に対して必要なBERT PG EQを実現するための波形測定 を示す画面キャプチャ:a)Vcおよびb)Vaに対するマーカ設定と 読み値、c)VbおよびVeの自動測定、d)測定結果と理想設定との 比較

V

dV

b 1xclk/128,128*clk/2 VdV

bb)

V

c1xclk/128, 64xclk/2

V

cc)

V

aV

aa)

V

dV

b 1xclk/128,128*clk/2 VdV

bb)

V

c1xclk/128, 64xclk/2

V

cc)

V

aV

aa)

V

dV

b 1xclk/128,128*clk/2 VdV

bb)

V

c1xclk/128, 64xclk/2

V

cc)

V

aV

aa)

V[a mV] V[b mV] V[c mV] V[d mV] 658 332 494 810 プリシュート・ディエンファシス・ブースト 測定値[dB] 3.45 −5.94 7.75 理想値[dB] 3.5 −6.0 7.0PCIe

リビジョン3.0

基本仕様に指定された可能なすべてのPCIe

リビジョン3.0

イコライ ゼーション設定とプリセットの一覧を、表4

と表5

に示します(セクション7.3

を参照)。 注記:オシロスコープは、帯域幅(BW)が20~25 GHzのものを使用することが重要です。 これは、急峻なフィルタの副作用によって正確なレベル測定が困難になるのを防ぐため です。サンプリング・オシロスコープを使用すれば通常はこのような問題は生じません。 d)4.

ストレス信号の校正

パターン・ジェネレータ(PG

)のEQ

の校正が終わった後、RJ

、SJ

、DM-SI

を校正する 必要があります。EW

を閉じるために、2

つのジッタ信号劣化が使用されます。EH

を閉じるためには、BERT PG

の振幅を下げる代わりに、DM-SI

を追加します。こ の方法を選択したのは、他のレーンからの高周波クロストークをエミュレートする ためです。これはRX

のCTLE

によって低周波信号成分よりも増幅され、HF S/N

比(SNR

)を悪化させます。このため、DM-SI

の周波数は、CTLE

のパスバンド内の2.1 GHz

に指定されています。 ジッタ分離および測定用に、SEG

はSigTest

ソフトウェア・ツールを提供しています。 このツールは、各ベンダのオシロスコープに実装されている独自のジッタ分離アルゴ リズムから生じる違いを防ぐ役割を果たします。ストレス信号校正は次の2

つのステ ップで行われます。1.

RJ

およびSJ

パラメータがチャネルの前で個別に(事前)校正されるのに対して、DM-SI

振幅はチャネルの後で事前校正されます。これは、周波数2.1 GHz

の信 号が、実際のコンポーネントやチャネルの特性によっては、大幅に(10 dB

程度) 減衰されることがあるからです。2.

次に、完全にストレスを加えたコンプライアンス・パターンに対して、必要なア イの開口部をTP6

で実現するために、チャネルの後でRJ

とDM-SI

の微調整を行 います。AIC

とMB

に対する校正手順は、使用するチャネル構成とSigTest

テンプレートの違い を除いて同じです(表3

を参照)。4.1. RJ

の校正

RJ

は1010

(クロック/2

)パターンを使用して校正されます(J-BERT

のパターン・セッ トアップについては図6

を参照)。J-BERT

のRJ

の値は、適切な10 MHz

ハイパス・フ ィルタをオンにした状態で(図12

を参照)、指定されたRJ

の値よりもわずかに小さい 開始値に設定されます(表3

を参照)。 図12. RJ-BWのセットアップの詳細が示されたJ-BERTのジッタ・セットアップ・ページ波形は記録され(

1,000

万サンプル)、.bin

フォーマットで保存されます。これをSigTest

ソフトウェアにロードして、表3

に記載されたテクノロジーとテンプレートを 使用してRJ

を計算します。このテンプレートを使用する場合、どのチャネルに対し てもイコライゼーションやエンベディングは行われません。したがって、意味がある のはジッタの結果だけです(図13

を参照)。J-BERT

でRJ

の値を適切に調整しながらこの手順を繰り返して、SigTest

で計算さ れたRJ

値が必要な許容範囲内に入るようにします(表3

を参照)。J-BERT

で最後に 調整されたRJ

の値を、後で使用するためにRJ

pre-adjとして手作業で記録しておく必 要があります(表1

を参照)。 注記:波形ファイルは比較的大きいので、波形を別のPCに転送する時間を節約するため に、SigTestソフトウェアをオシロスコープのPCにインストールしておくと便利です。 結果パネル 入力パネル EHおよび EW(カード)、 RJおよびSJの 校正用 図13. SigTest入力パネル(左上):最終校正に使用するテクノロジーとテンプレートを表 示した入力パネル(セクション4.4)、左下の部分図はジッタ校正(RJおよびSJ)用の代替設 定。結果画面(右):青の長方形はEHとEWの結果、黒の長方形はRJの結果、オレンジの長 方形はSJ校正に使用するp-pジッタの結果。4.2. SJ

の校正

SJ

の校正には、コンプライアンス・パターン1を使用します(図6

を参照)。基準として、全固有ジッタ(

TJ

)を測定します。このためには、J-BERT

のすべてのジッタ源とDM-SI

をオンにし、0

に設定します。その状態で波形を捕捉して.bin

形式で記録し、SigTest

ソフトウェアにロードして、TJ0

(図13

に示す“Max Peak to Peak Jitter

”)を求めます。

SJ

の生成には、J-BERT

のPJ1

またはPJ2

が使用できます。コンプライ アンス・テストの範囲を超えて、基本仕様に類似した周波数掃引による特性評価が必 要な場合には、PJ2

が適しています(図14

を参照)。 校正の際には、PJ2

を100 MHz

で0.1 UI

に設定します(図14

を参照)。次に、波形を 捕捉し、SigTest

でジッタ値を計算します。すべてのジッタ源を0

に設定した基準測 定(TJ0

)と現在の測定との間の差は、注入されたSJ

に等しくなります。SJ

が指定さ れた範囲に入らない場合(表3

を参照)は、J-BERT

で周期ジッタ(PJ

)の大きさを調整 して、PJ

calの適切な設定が得られるまでこの手順を繰り返します(表1

を参照)。 PJ2を示すジッタ・セットアップ・ページa)

b)

c)

パス フェール 各ステップのBER合否結果を示す ジッタ耐力コンプライアンス測定b)

d)

図14. J-BERTのグラフィカル・ユーザ・インタフェース(GUI)の画面キャプチャ。 a)一定値によるPJ2、b)リニア・バックグラウンド掃引、c)定義済みの曲線に基づく掃 引のセットアップ、d)ジッタ耐力コンプライアンス・テスト。 1. コンプライアンス・パターンおよび修正コンプライアンス・パターンは、 J-BERTソフトウェア・リビジョン7.1以上で使用できます。4.3. DM-SI

の校正

(事前)校正が必要な最後の信号劣化は、DM-SI

です。これはEH

の調整に用いられま す。このパラメータは、チャネルの後のTP6

で測定されます(図8

を参照)。このため には、CBB

メイン・ボードにCLB

を挿入し、ケーブル

のSMP

コネクタをオシロスコ ープから取り外して、AIC

テストの場合はCBB

ライザ・カード上、MB

テストの場合 はCLB

上のRX

コネクタに接続します。マッチドSMP-SMA

ケーブルのもう1

つのペア

(図8

および表2

を参照)は、AIC

テストの場合はCLB

上、MB

テストの場合はCBB

メイン・ボード上のTX

コネクタから、オシロスコープの入力にSMP-SMA

アダプタを 外して接続します。BERT PG

は、一定値0

のパターンを出力するように設定します。これは、J-BERT

のパターン・シーケンサで「休止」セグメントを使用すれば容易に実現できます(図6

を参照)。DM-SI

は、2.1 GHz

の周波数に設定し、振幅を変化させて、オシロスコー プで測定されるp-p

振幅が表3

に示された許容範囲内に入るようにします。DM-SIpre-cal

の値を求めて、後で使用するために記録します(図15

および表1

を参照)。b)

a)

図15. J-BERTの a)DM-SIのセットアップ画面と b)波形表示の画面キャプチャ4.4.

最終ストレス信号の校正、

EH

および

EW

すべての信号劣化とプリセットの(事前)調整が終わった後、最終ストレス信号の調整 を行う必要があります。このためには、P7

(表5

を参照)とコンプライアンス・テスト・ パターンを選択し、関連するすべてのJ-BERT

パラメータ(振幅、および電圧/タイ ミングの劣化)を先に記録した値に設定します。オシロスコープを使用してチャネル の後で波形を捕捉し、SigTest

ソフトウェアにロードします。計算には、表3

に示すSigTest

テクノロジーとテンプレートを使用します。これらのテンプレートを使用して、SigTest

はチャネルの残りの部分をエンベッドし(“Upload and Verify Data

”を押す前に

SigTest

入力パネルで“Embed

”をチェックしておく必要があります。図13

を参照)、CTLE

およびDFE

に対して基準イコライゼーションを最適化します。この 最適化が必要なのは、アイの開口部がASIC

内部で指定されているからです(図3

およ び図8

のTP2-P

を参照)。EH

およびEW

の計算値が表3

に示されたリミット内にない場 合は、RJ

とDM-SI

を適切に変更する必要があります。1.

指定されたEW

を満たすようにRJ

を調整2.

指定されたEH

を満たすようにDM-SI

を調整3.

EW

を再チェックし、必要ならRJ

を再調整4.

最終校正値RJ

calおよびDM-SI

calを後で使用するために記録AIC

校 正 に 使 用 す る す べ て のパラメータの 代 表 値 を 表1

に 示 し ま す。 た だ し、J-BERT

の設定は実際のテスト・セットアップに使用されるパッシブ・コンポーネントや 測定器の特性に依存するため、in-situ

調整が必要となります。ディエンベディング

P7

P8

Vampt/mV 604 604 604 Pre-curs/dB 0 4.1 4.1 Post-cur1/dB −0.7 −4.5 −7.1事前調整

最終調整(

EW/EH

)

RJ/mUI(ps) 11.5(1.44) 11.5(1.44) PJ2 110(13.8) 110(13.8) DM-SI/mV 45 110 表1. 校正済みRXストレス信号を得るための代表的なJ-BERT設定。実際のセットアップ での値は、実際に使用するコンポーネントによって異なる可能性があります。4.5. Agilent N5990A-101

適切な校正を実現するには、さまざまなパラメータを調整する必要があり、いくつ かのパラメータについては反復調整が必要です。このプロセスは、Agilent N5990A

自動コンプライアンス/デバイス特性評価テスト・ソフトウェアとオプション101 PCI

EXPRESS®

を使用することで、容易に自動化できます。N5990A

の最新バージョン には、リビジョン3.0 CEM

テストのPHY

テスト仕様に基づいた校正手順が含まれてい ます。N5990A-101

で実現される校正は、コンプライアンス・ポイントだけでなくさ らに広い範囲で有効です。これにより、指定されたコンプライアンス・ポイントでの テストに加えて、DUT

マージンを判定するための特性評価や、特定の問題の解析も 実行できます。校正手順のまとめ

8 GT/s

という比較的高い転送レートと、PCI-SIG

ボードの設計方法(TX

パッケージ のエミュレーション)のために、ストレス信号の校正にいくつかの影響が生じます。•

テスト・セットアップの周波数応答(TP3

まで)をディエンベディングすること により、さまざまなベンダのテスト機器間の差を除去する必要があります。•

振幅、EQ

、ジッタ、電圧ノイズなどのすべての信号パラメータをin-situ

で校正 する必要があります。•

各オシロスコープ独自の抽出アルゴリズムによるわずかな違いを避けるため に、ジッタの値は捕捉した波形からSigTest

ソフトウェアによって抽出され ます。•

ストレス信号は、個別に校正された成分によって定義することはできません。 ほとんどの成分は個別に事前校正されるだけで、ストレス信号の最終校正は、RJ

とDM-SI

を変化させて必要なEH

とEW

を得ることによって行われます。• EH

とEW

はSigTest

ソフトウェアを使用して求められ、イコライゼーションが得 られます。これは、ストレス信号がRX

内部の基準EQ

の後で定義されるからです。• Agilent J-BERT

を使用した実用的なセットアップを紹介しました。• Agilent N5990

オートメーション・ソフトウェア・オプション101

の使用をお勧 めします。5. RX

テスト

このセクションでは、2

つのテスト・セットアップと、DUT

をループバックにトレーニ ングするためのツールについて説明します。さらにBER

測定と統計の性質に関する 一般的な事項についても説明します。5.1. AIC

のテスト・セットアップ

ソース出力ケーブル

(図8

および図16

を参照)をCBB

ライザ・カード上のSMP RX

コ ネクタに接続します。被試験AIC

を、CBB

メイン・ボード上のPCIe

コネクタに挿入し ます。100 MHz

の基準クロックを出力するために、J-BERT

のトリガ出力を80

分周 に設定します。出力をSMP-Ref-Clk

入力コネクタに接続し、エラー・ディテクタ(ED

) 入力をケーブル

でCBB

メイン・ボード上のSMP-TX

コネクタに接続します(図16

を 参照)。CBB

リビジョン

3

CBB

リビジョン

3

長い校正チャネル

アドイン・カード

RX入力 TX出力 基準クロック入力 100 MHz 非対称スプリッタ PSPL 5370-14dB DCブロック、N9398CN4916B

2.1 GHz 差動モード 正弦波干渉J-BERT

N4903B

ASIC

1 2 図16. Agilent J-BERT N4903BおよびN4916Bディエンファシス信号コンバータと CBBライザ・カードを使用したAICテスト・セットアップ5.2. MB

のテスト・セットアップ

MB

テスト用には、ソース出力ケーブル

(図8

および図17

を参照)をCLB

のSMP-RX

コネクタに、ED

入力をSMP-TX

コネクタに接続します。ほとんどのMB

は、外部100 MHz

基準クロックで動作させることはできません。このため、J-BERT

のPG

を 外部クロック・モードに設定します。クロック入力は、N4880A

の基準クロック逓倍器 のフェーズ・ロック・ループ(PLL

)でドライブされます。これは、100 MHz

の基準ク ロックをJ-BERT

の外部クロック入力用の8 GHz

のクロックに変換し、PCIe

仕様に従 ってすべての帯域内ジッタ(特にスペクトラム拡散クロック(SSC

)による変調)を保存 します。 図17

と表2

に示すように、MB

のバックチャネルTX

の信号アイを開くために、アイの 開口部用の信号リピータが必要です。これは、リンク・トレーニング中にJ-BERT

によ って適切なTX

イコライゼーションが要求された場合でも必要になることがあります (セクション5.3

を参照)。 マザーボードCLB

TX出力 基準クロック出力 RX入力 N4916B J-BERT N4903B N4880A 8 GHz 100 MHz 2.1 GHz 差動モード 正弦波干渉 ASIC リピータ 非対称スプリッタ PSPL 5370-14dB DCブロック、N9398C 1 2 図17. J-BERT N4903B、N4916Bディエンファシス信号コンバータ、N4880A基準 クロック逓倍器とCLBを使用したMBテスト・セットアップ5.3. DUT

のループバックへの設定

RX

テストを実行するには、DUT

をループバックにトレーニングする必要があります (セクション2.1

を参照)。このために、J-BERT

は、リンク・トレーニング・ステータス・ ステート・マシン(LTSSM

)のステートにより、DUT

を操作する必要があります(図18

を参照)。すべてのPCIe

デバイスが処理できる最小速度は2.5 GT/s

です。このため、 リンクパートナーとの間の最初の通信は、2.5 GT/s

の転送速度で行われ、<ポーリン グ>から<構成>に進みます(図18

の黄色の矢印)。その後、両方のデバイスが電気 的アイドルに入り、8 GT/s

への速度変更を行います(図18

の黄色/黒の矢印と囲み 記事の説明)。これ以後、ループバック・ステートに入った後で、J-BERT

は指定され たパターンを8 GT/s

で送出し、それによってDUT

は<ループバック・エントリ>ステ ートから<ループバック>ステートに移行します。 無効 ホット・リセット ループバック リカバリLO

L2

L1

LOs

ポーリング 構成 検出 初期ステートまたは データ・リンク層 によって指定 図18. LTSSMとループバックへの経路BERT

が

8 GT/s

の速度で動作している間

に、ビット逓倍を使用して

2.5 GT/s

のパ

ターンが生成されます。

2

つの速度は整

数倍の関係にないため、非対称の方式

が用いられます。

3

ビットを

4

回、

4

ビ

ットを

1

回送信することにより、

16

ビッ

ト

/5

ビット=

8 GT/s/2.5 GT/s

の比が実現

されます。この非対称のビット逓倍の

ために、

2.5 GT/s

モードではジッタの

発生が避けられません。しかし、この

ジッタはリンク・トレーニング中にし

か発生せず、

PCIe 1.0

仕様のリミットよ

りも小さいため、安全マージンがあり

ます。

8 GT/s

信号

8/2.5

=

16/5

=

3.2

2.5 GT/s

信号

2.5 GT/s

信号のエミュレーション

8 GT/s

のビット数

/2.5 GT/s

のビット

2.5 GT/s

の指定されたアイの開口部

2.5 GHzサンプリング・ポイント3 3 4 3 3

標準のコンフォーマンス・パターン・シーケンスは、実効的に2

つの異なる転送速度 (2.5 GT/s

で8B/10B

コード化、および8 GT/s

で128B/130B

コード化と部分スクラ ンブル)を使用してデバイスをループバックに設定するもので、比較的複雑です。こ のパターンは、Agilent J-BERT

ソフトウェア・リビジョン7.1

以上で提供されていま す。ただし、CEM

およびPHY

テスト仕様はまだ開発中なので、プレリリース・デバイ スのすべてが規格に準拠したLTSSM

を備えているわけではありません。このため、J-BERT

で提供されるベース仕様に完全に準拠したシーケンスが常に動作するとは限 りません。このため、Agilent

はN5990A

オプション301

リンク・トレーニング・スイー ト(LTS

)を提供しています。これを使用すれば、ユーザ選択可能な抽象レベルでシー ケンスを編集できます(図20

を参照)。リンク・トレーニング・シーケンスとそのパラメ ータをセットアップした後、LTS

で作成したビット・パターンとシーケンス(ループバッ ク用の選択可能な繰り返しテスト・パターンを含む)を、J-BERT

のPG

とED

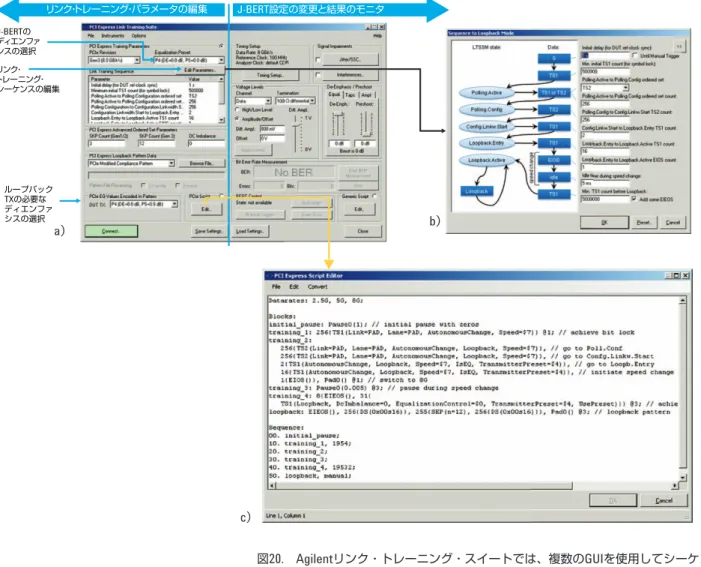

にダウン ロードできます。 図19. 2.5 GHzパターン図20. Agilentリンク・トレーニング・スイートでは、複数のGUIを使用してシーケンスと パターンをユーザ選択可能なレベルで編集可能。a)J-BERTパラメータ・エディタを備え たメインGUI、b)パターン・シーケンス用の上位レベルのエディタ、c)スクリプト言語 エディタ

5.4.

実際の

RX

テストと測定時間

テストには2

つのタイプがあります。1

つめのタイプは、最終システムにおいて、TX-RX

ペアがそれぞれの属性を交換するための最小限の通信を確立できることを確 認するために用いられます。また、最大共通速度で動作したときに、各デバイスが 相手のデバイスを最適なBER

性能にトレーニングできることも確認します。このた めには、指定されたTX EQ

プリセットP0

、P7

、P8

に対して、BER

性能が10

−4より も高いことを確認する必要があります(表5

を参照)。2

つめのテストは、RX

ジッタ耐 力テストです。これは、RX

動作のBER

性能が10

−12よりも高いことを確認するため に用いられます。このテストでは、J-BERT PG

のEQ

を該当するプリセットに設定す るか、表4

に指定された定義済みEQ

設定のうちDUT

で要求されているものに設定し ます。 注記:このPG EQは、リカバリ・ステートでのインタラクティブ・リンク・トレーニング から生じるEQと一致するとは限りません。ここでいうPG EQは、被試験PCIe-ASICまたは カードのデザイナまたはテスト・エンジニアによって事前に指定された設定のことです。 どちらのタイプのテストでも、校正済みのストレス・パターンをDUT

に印加し、 J-BERTの ディエンファ シスの選択 ループバック TXの必要な ディエンファ シスの選択 J-BERT設定の変更と結果のモニタ リンク・ トレーニング・ シーケンスの編集 リンク・トレーニング・パラメータの編集 a) b) c)ここで問題となるのは、十分な信頼度レベル(

CL

)でBER

測定を行うために、どの程 度の測定時間が必要か、あるいはどの程度多くのビットを観察する必要があるのか ということです。通常用いられるCL

=95

%のレベルに必要なビット数を図21

に示 します。統計的な性質より、DUT

のBER

の値を厳密に求めることは不可能です。与 えられたCL

で、BER

があるしきい値より上または下であることがわかるだけです [6

]。ここで判定しようとしているのは、BER

がしきい値を下回るかどうかです。1

つめのタイプのテストについては、ターゲットBER

に関して95

%の信頼度レベルを 実現するのに必要なビット数はごく少数(0

エラーの場合は3

×10

4ビット、最大5

エラーの場合は

10

5ビット。図21a

を参照)ですが、一般的なBERT

のBER

測定の更新頻度などの実用的な理由から、

10

9ビット程度を測定します。2

つめのタイプのテストに関しては、BER

結果で必要な信頼度レベルを実現するため に観察するビットとエラーの数が、はるかに重要な意味を持ちます。8 GT/s

の転送 速度で、BER

が10

−12よりも小さいことを信頼度95

%で確認するための最小測定時 間は、6

分15

秒になります(テスト中にエラーが発生しない場合)。1.97 2.61

3.29

2.00

4.00

6.00

8.00

10.00

12.00

ウ ン ト さ れ た ビ ッ ト 数( 1e 12 )BER

評価のためにカウントが必要なビット数

BER<1e-12

BER>1e-12

3.00

4.74

6.30

7.75

9.15

10.51

11.84

1.0E-121.6E-122.1E-122.6E-123.1E-123.5E-12 3.9E-124.4E-12 3.1E-124.9E-12 6.6E-128.1E-12 9.5E-121.1E-11 1.2E-111.4E-11 6.2E-12 9.9E-12 1.3E-11 1.6E-11 1.9E-11 2.2E-11 2.5E-112.8E-11

0.0E+00

5.0E-11

1.0E-11

1.5E-11

2.0E-11

2.5E-11

3.0E-11

0

1

2

3

4

5

6

7

エラー数BER

95

%の

BER

とエラー数および

測定時間の関係

6.25分 2分 1分0.05 0.36

0.81 1.37

1.97 2.61

3.29

0.00

2.00

4.00

6.00

8.00

10.00

12.00

0

1

2

3

4

5

6

7

カ ウ ン ト さ れ た ビ ッ ト 数( 1e 12 ) エラー数BER

評価のためにカウントが必要なビット数

BER<1e-12

BER>1e-12

3.00

4.74

6.30

7.75

9.15

10.51

11.84

1.0E-121.6E-122.1E-122.6E-123.1E-123.5E-12 3.9E-124.4E-12 3.1E-124.9E-12 6.6E-128.1E-12 9.5E-121.1E-11 1.2E-111.4E-11 6.2E-12 9.9E-12 1.3E-11 1.6E-11 1.9E-11 2.2E-11 2.5E-112.8E-11

0.0E+00

5.0E-11

1.0E-11

1.5E-11

2.0E-11

2.5E-11

3.0E-11

0

1

2

3

4

5

6

7

エラー数BER

95

%の

BER

とエラー数および

測定時間の関係

6.25分 2分 1分 図21. a)BERとエラー数および測定ビット数の関係 b)与えられた測定時間で達成可能なBER a) b)25

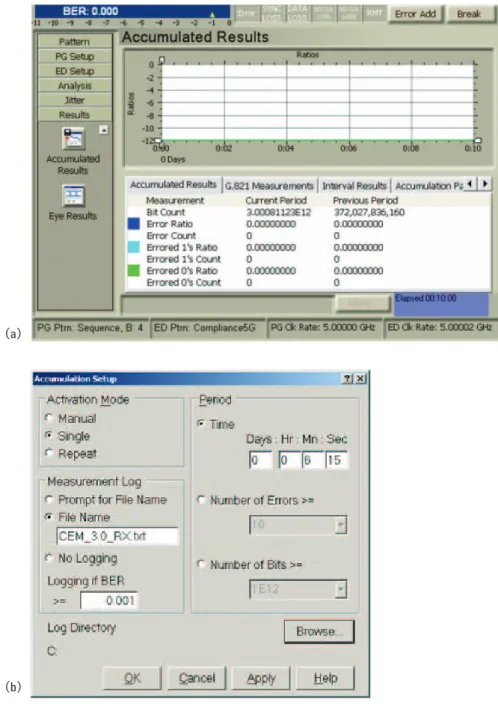

図

22

は、積算BER

結果を表示したJ-BERT

のGUI

の画面キャプチャです。これはRX

テストの実行に便利です。BER

が10

−12より小さいことを確認する場合、測定時間 を前もって知ることは不可能です。発生するエラーの数によって測定時間が変わる からです(図21a

)。ソフトウェア自動化を使用しない場合、この画面では意味のある 時間(6

分15

秒、10

分、13

分、16

分など)が経過した時点で積算エラー数を確認すれ ばよいので、現在のBER

結果でエラーがあるかどうかを常に監視し続ける必要はあ りません。 別の方法として、測定時間を事前に決めておき、積算エラー数に基づいてDUT

のBER

を求めることもできます(図21b

を参照)。 図22. a)J-BERTの積算ビット・エラー結果とb)セットアップ画面 (b) (a)RX

ストレス信号の校正手順について説明しました。CEM

仕様を満たすための、Agilent

機器を使用した実用的で完全でワークショップによる実証済みのテスト・セ ットアップを紹介しました。Agilent

製品には以下のような利点があることを説明し ました。• J-BERT

のパターン・シーケンサにより、校正中に必要な複数のパターンを容易に セットアップして切り替えることができる• N5990A

オプション301

リンク・トレーニング・スイートを使用して、ユーザ選択可 能な抽象レイヤでパターン・シーケンスをセットアップすることにより、ユーザ選 択可能な抽象レイヤでLTSSM

を通じてDUT

をループバックに設定できる• N5990A

オプション101

オートメーション・ソフトウェアを使用して、コンプライアン ス・ポイントだけでなく広い範囲のストレス信号パラメータに対して校正を実行で きるので、DUT

のマージンを求めるための特性評価が可能•

結論として、Agilent

機器を使用することにより、セットアップ時間を短縮し、よ り高度な解析を実行し、PCI-SIG

ワークショップで実証された手順を利用できま す。このアプリケーション・ノートで紹介したCEM

テスト用の方法とセットアップ 以外にも、Agilent

は基本仕様に基づいた校正とテストのためのセットアップと自 動化ソフトウェアを提供しています[4

]。 注記:このアプリケーション・ノートは、CEMおよびPHYテスト仕様の暫定版に基づいて います。パラメータ値やテスト手順は変更される可能性があります。6.

まとめ

7.

付録

7.1.

機器

テスト・セットアップを構築するのに必要な測定器と付属品を表1

に示します。概要

番号/オプション

数量

J-BERT

高性能シリアルBERT

N4903B 1 12.5 Gb/s BERT N4903B-C13 1 RJ、SJ、BUJ、RJ、s-RJ注入 N4903B-J10 1 SSC生成 N4903B-J11 1 干渉チャネル(ISI、S.I.) N4903B-J20 1 ジッタ耐力コンプライアンス・スイート N4903B-J12 1(R1) 補助データ出力(PRBSおよびパターンの供給) N4903B-002 1(R1) ビット・リカバリ・モード N4903B-A01 1(R1) ディエンファシス信号コンバータ N4916B-STD 1 N4916BをN4903Bと接続するためのマッチド・ケーブル・キット N49156-010 1 基準クロック逓倍器 N4880A 1 デジタル・シグナル・アナライザ(13 GHz

以上の帯域幅) DSAX91604A以上 1 テスト・オートメーション・ソフトウェア・ プラットフォーム・コア製品 N5990A-010 1PCIeレシーバ・テスト(SEASIMソフトウェアを含む) N5990A-101 1

リンク・トレーニング・スイート N5990A-301 1 アクセサリ SMAケーブル・ペア(±25 psのマッチング) 15443A 1 ピックオフ・ティー、14 dB(5X)、SMA J-P-J PSPL 5372-112 14 dB 2 DCブロック、50 kHz∼26.5 GHz N9398C 2 SMA-SMPケーブル・ペア N4235-61602 3

SMP SMAアダプタ Pastenack PE9511 2

PCI-SIG CBB(メインおよびライザ・カード)+CLB PCI-SIG 1 リピータ National Semiconductor DS80PCI800EVK 1 (MB2) 1. R:このアプリケーション・ノートで説明している基本測定の実行には不要ですが、日常の作業には有用なので推奨される製品。 2. MB:マザーボード・テスト用にのみ必要 表2. 図8のテスト・セットアップ用の機器

7.2. CEM 0.9

および

PHY

テスト仕様バージョン

0.5

に基づいた

RX

ストレス信号の仕様

表3. RXテスト用PHYテスト仕様パラメータ

最小

最大

単位

Sig test

テクノロジー テンプレート Vpp 800 mV − −VRX-EH-BGアイの高さ 50 mV PCI_3_CARD PCI_3_8GB_MULTI_CTLE_

DFE_80ps_50mV TRX BH 8Cアイの幅 0.36(45) UI(ps) PCI_3_CARD PCI_3_8GB_MULTI_CTLE_ DFE_80ps_50mV R(ランダム・ジッタ)j 1.5 1.6 ps RMS PCI_3__0_RX_CAL PCIE_3_8G_Rx_Sj_CAL S(正弦波ジッタ)j 100 MHz 12.5 14.5 ps PP PCI_3__0_RX_CAL PCIE_3_8G_Rx_Sj_CAL 2.1 GHzの差動モード正弦波干渉 14 15 mV PP − −

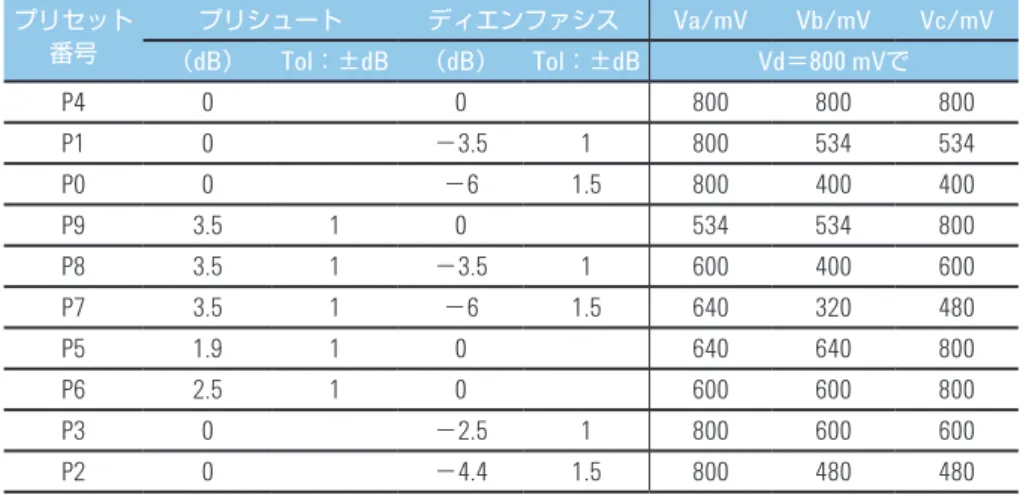

7.3. TX

イコライゼーションとプリセット

PS DE C+1 ブースト 0/24 1/24 2/24 3/24 4/24 5/24 6/24 7/24 8/24 C−1 0/24 0.0 0.0 0.0 −0.8 0.0 −1.6 0.0 −2.5 0.0 3.5 0.0 −4.7 0.0 −6.0 0.0 −7.6 0.0 −9.5 0.0 0.8 1.6 2.5 3.5 4.7 6.0 7.6 9.5 1/24 0.8 0.0 0.8 −0.8 0.9 −1.7 1.0 −2.3 1.2 −3.9 1.3 −5.3 1.6 −6.8 1.9 −8.8 0.8 1.6 2.5 3.5 4.7 6.0 7.6 9.5 2/24 1.6 0.0 1.7 −0.9 1.9 −1.9 2.2 −3.1 2.5 −4.4 2.9 −6.0 3.5 −8.0 1.6 2.5 3.5 4.7 6.0 7.6 9.5 3/24 2.5 0.0 2.8 −1.0 3.1 −2.2 3.5 −3.5 4.1 −5.1 4.9 7.0 2.5 3.5 4.7 6.0 7.6 9.5 4/24 3.5 0.0 3.9 −1.2 4.4 −2.5 5.1 −4.1 6.0 −6.0 3.5 4.7 6.0 7.6 9.5 5/24 4.7 0.0 5.3 −1.3 6.0 −2.9 7.0 −4.9 4.7 6.0 7.6 9.5 6/24 6.0 0.0 6.8 −1.6 8.0 −3.5 6.0 7.6 9.5 −9.5 9.5 −8.8 9.5 −8.0 9.5 7.0 9.5 −6.0 9.5 −4.9 9.5 3.5 −2.3 −1.9 −1.0 0.0 減振幅最小リミット 全振幅リミットまたは最大減振幅リミット 表4. 指定されたTXイコライゼーション設定の一覧表5. プリセットのリスト プリセット 番号 プリシュート ディエンファシス Va/mV Vb/mV Vc/mV (dB) Tol:±dB (dB) Tol:±dB Vd=800 mVで P4 0 0 800 800 800 P1 0 −3.5 1 800 534 534 P0 0 −6 1.5 800 400 400 P9 3.5 1 0 534 534 800 P8 3.5 1 −3.5 1 600 400 600 P7 3.5 1 −6 1.5 640 320 480 P5 1.9 1 0 640 640 800 P6 2.5 1 0 600 600 800 P3 0 −2.5 1 800 600 600 P2 0 −4.4 1.5 800 480 480

7.4.

参考資料

[1] PCIe基本仕様リビジョン3 [2] PCIe CEM仕様リビジョン3 [3] PCIe PHYテスト仕様リビジョン3[4]『PCI Express® rev. 3.0のレシーバ・ストレス・テストで信号を正確に校正することに

より、8 GT/sのデータ・レートでの相互運用性を保証』、Application Note、カタログ 番号5990-6599JAJP(http://cp.literature.agilent.com/litweb/pdf/5990-6599JAJP.pdf) [5] Digital Communications Test and Measurement; Dennis Derickson-Marcus Mueller;

Prentice Hall

[6] Total Jitter Measurement at Low Probability Levels, Using Optimized BERT Scan Method、カタログ番号5989-2933EN( http://cp.literature.agilent.com/litweb/pdf/5989-2933EN.pdf)

AIC アドイン・カード ASIC アプリケーション専用集積回路 BER ビット・エラー比 BERT ビット・エラー・レート・テスタ BERT PG ビット・エラー・レート・テスタ・パターン・ジェネレータ BUJ 有界非相関ジッタ BW 帯域幅 CBB コンプライアンス・ベース・ボード

CEM Card Electro-Mechanical(PCIeインタフェースを使用した アドイン・カードおよびマザーボードの仕様を記述する PCI-SIG規格) CL 信頼度レベル CLB コンプライアンス・ロード・ボード CR クロック・リカバリ CTLE 連続時間リニア・イコライザ DDJ データ依存ジッタ DFE デシジョン・フィードバック・イコライザ DM-SI 差動モード正弦波干渉 DUT 被試験デバイス ED エラー・ディテクタ EH アイの高さ EQ イコライザ EW アイの幅

EWG Electrical Work Group

GUI グラフィカル・ユーザ・インタフェース HF 高周波 ISI 符号間干渉 LF 低周波 LTS リンク・トレーニング・スイート LTSSM リンク・トレーニングおよびステータス・ステート・マシン MOI Method of Implementation

MB マザーボード

PCI Peripheral Component Interconnect PCIe PCI Express

PCI-SIG PCI Special Interest Group

PG パターン・ジェネレータ PHY 物理層または物理層デバイス PLL フェーズ・ロック・ループ PJ 周期ジッタ RJ ランダム・ジッタ RX レシーバ Seasim 統計アイ解析シミュレータ SEG Serial Enabling Group SIG Special Interest Group

SNR S/N比 SigTest シグナル・テスト(TX出力信号の信号解析またはRXテスト 信号の校正のためにPCI-SIGからメンバに提供される ソフトウェア) SJ 正弦波ジッタ TJ 全ジッタ TX トランスミッタ UI ユーザ・インタフェース

7.5.

用語集

www.agilent.co.jp

www.agilent.co.jp/find/jbert

www.agilent.co.jp/find/automation

www.agilent.co.jp/find/berts

www.agilent.co.jp/find/pci-express

PCI-SIG、PCI Express、PCIeは、PCI-SIGの 登録商標/サービス・マークです。

アジレント・テクノロジー株式会社

本社〒192-8510

東京都八王子市高倉町9-1

計測お客様窓口

受付時間9:00-18:00

(土・日・祭日を除く)TEL

■■0120-421-345

(042-656-7832)

FAX

■■0120-421-678

(042-656-7840)

contact_japan@agilent.com

電子計測ホームページwww.agilent.co.jp

●記載事項は変更になる場合があります。 ご発注の際はご確認ください。© Agilent Technologies, Inc. 2012 Published in Japan, July 20, 2012 5990-9208JAJP 0000-00DEP 電子計測UPDATE www.agilent.co.jp/find/emailupdates-Japan Agilentからの最新情報を記載した電子メール を無料でお送りします。