101 Innovation Drive San Jose, CA 95134

ホワイトペーパー

SoC FPGA 選定におけるアーキテクチャの重要性

はじめに . . . 1–1 現在市販されている SoC FPGA . . . 1–1 2 チップ・プロセッサ/ FPGA アプリケーションに対する利点 . . . 1–4 ASIC ベースのプロセッサに対する利点 . . . 1–4 他のプロセッサやマイクロコントローラに対する利点 . . . 1–5 特定のアプリケーションに適した SoC FPGA の選択方法 . . . 1–5 システム性能 . . . 1–6 L3 インタコネクトの重要性:最大性能のためのセントラル・スイッチ . . . 1–6 プロセッサ - FPGA インタコネクト:統合デバイスの利点を実現 . . . 1–8 DDR メモリ・コントローラの性能 . . . 1–10 FPGA とプロセッサの DDR メモリ・コントローラの接続 . . . 1–13 ハードウェア・アクセラレーションとキャッシュ・コヒーレンシ . . . 1–14 追加のメモリ・コントローラによる最大システム性能の向上 . . . 1–15 システム信頼性および柔軟性 . . . 1–16 ECC によるメモリ内容の保護 . . . 1–17 共有メモリのメモリ保護 . . . 1–18 ウォッチドッグ・リセットとその FPGA ロジックに対する影響 . . . 1–20 フェイルセーフ・ブートおよびコンフィギュレーション . . . 1–20 柔軟性 . . . 1–21 さまざまなプロセッサ・ブートおよび FPGA コンフィギュレーション・オプション . . . 1–21 複数のブート・イメージ . . . 1–23 オンチップ FPGA インタフェース . . . 1–25 共通フットプリントでの集積度/トランシーバ/機能のマイグレーション . . . 1–26 システム・コスト . . . 1–27 統合機能 . . . 1–27 高速トランシーバ . . . 1–27 電源コスト . . . 1–28 消費電力 . . . 1–28 統合による消費電力削減 . . . 1–29 省電力モード . . . 1–29 パワーオン/パワーオフ・シーケンス要件 . . . 1–30 将来のロードマップ . . . 1–31 アルテラの 3 世代プロセッサ・ロードマップ . . . 1–31 シリコン・プロセス・テクノロジ . . . 1–32 FinFET テクノロジ . . . 1–32 ツールのロードマップ . . . 1–33 開発ツール . . . 1–34 開発ツールの課題 . . . 1–36 ARM との互換性は前提であり、FPGA の実装が差異化をもたらす . . . 1–36 チップ全体のデバッグ . . . 1–37 FPGA 対応デバッグ . . . 1–37 1 本のデバッグ・ケーブルによる ARM および FPGA の開発 . . . 1–38 ハードウェアとソフトウェア間のクロストリガ . . . 1–38 ハードウェアおよびソフトウェア・イベントの追跡・監視 . . . 1–39 CPU および FPGA のプロファイリング . . . 1–39 マルチコア・デバッグ . . . 1–40 標準ツールおよびフロー . . . 1–40

結論 . . . 1–42 詳細情報について . . . 1–43 謝辞 . . . 1–43 文書改訂履歴 . . . 1–43

WP-01202-1.0 ホワイトペーパー

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in

このホワイトペーパーでは、システム・アーキテクト、エンジニア、およびマネー ジャが開発アプリケーションへ SoC FPGA を検討する際に、最適なデバイスを選択す る上で役立つさまざまな評価基準について解説します。本書の主な内容については、 ビデオ・シリーズ「SoC FPGA におけるアーキテクチャの重要性」でも紹介されてい ます。

はじめに

SoC FPGA デバイスは、プロセッサと FPGA アーキテクチャを 1 つのデバイスに集積 したものです。この 2 つのテクノロジを融合することで、高集積化、低消費電力化、 ボード・サイズの削減、プロセッサと FPGA 間の帯域幅向上をはじめとするさまざま な利点が得られます。クラス最高のデバイスは、スタンドアロン・プロセッサ/ FPGA アプローチの利点を確保しながら、プロセッサ/ FPGA 統合システム固有の利点を生 かしています。

現在市販されている SoC FPGA

現在市販されている主な SoC FPGA は、表 1 に示す 3 種類です。これらのデバイスの プロセッサは、「ハード化」された専用プロセッサ・サブシステムです ( つまり、FPGA ファブリックに実装されたソフト IP (Intellectual Property) コアではありません )。この 3 種類のデバイス・ファミリはいずれも、完全なメモリ階層と専用ペリフェラルを備 えた、一般的な ARM® プロセッサとほぼ同様にブート/実行/動作するフル機能の ARM プロセッサを採用しています。Microsemi SmartFusion2 SoC FPGA は、主にマイクロコントローラ・アプリケーション をターゲットにした ARM Cortex™-M3 エンベデッド・プロセッサをベースにしていま す。それに対し、アルテラ SoC FPGA および Xilinx Zynq-7000 デバイスは、デュアル コア ARM Cortex-A9 アプリケーション・プロセッサを使用しています。SoC FPGA は、 プロセッサの他に豊富なペリフェラル、オンチップ・メモリ、FPGA スタイルのロ ジック・アレイ、各種 I/O を搭載しています (表 1 参照 )。

表 1. 現在市販されている SoC FPGA ( 1 / 3 )

アルテラ SoC FPGA Xilinx Zynq-7000 EPP Microsemi SmartFusion2

プロセッサ ARM Cortex-A9 ARM Cortex-A9 ARM Cortex-M3

プロセッサ・クラス アプリケーション・プロ セッサ アプリケーション・プロ セッサ マイクロコントローラ シングルまたはデュア ルコア シングルまたはデュアル デュアル シングル プロセッサ最大周波数 1.05 GHz 1.0 GHz 166 MHz

L1 キャッシュ データ:32 KB 命令:32 KB データ:32 KB 命令:32 KB データ・キャッシュなし 命令:8 KB L2 キャッシュ 統合:512 KB、ECC ( 誤り訂正コード ) 付き 統合:512 KB なし メモリ・マネージメン ト・ユニット (MMU) あり あり あり 浮動小数点演算ユニッ ト/ NEON™ マルチメ ディア・エンジン あり あり なし アクセラレーション・ コヒーレンシ・ポート (ACP) あり あり なし

割り込みコントローラ 汎用 (GIC) 汎用 (GIC) ネスト型ベクタ (NVIC)

オンチップ・プロセッ

サ RAM 64 KB、ECC 付き 256 KB、ECC なし 64 KB、ECC なし

ダイレクト・メモリ・ アクセス (DMA) コント ローラ 8 チャネル ARM DMA330 32 ペリフェラル要求 (FPGA + ハード・プロ セッサ・システム ) 8 チャネル ARM DMA330 4 ペリフェラル要求 (FPGA のみ ) 1 チャネル HPDMA 4 要求 外部メモリ・コント ローラ あり あり あり サポートするメモリ・ タイプ LPDDR2、DDR2、 DDR3L、DDR3 LPDDR2、DDR2、 DDR3L、DDR3 LPDDR、DDR2、DDR3 外部メモリ ECC 16 ビット、32 ビット 16 ビット 8 ビット、16 ビット、32 ビット 外部メモリ・バス最大 周波数 400 MHz (Cyclone® V SoC)、533 MHz (Arria® V SoC) 533 MHz 333 MHz 表 1. 現在市販されている SoC FPGA ( 2 / 3 )

SoC FPGA は、次世代のシステム・デザインに適しているのでしょうか。システム設 計者、アーキテクト、またはハードウェア・マネージャがその判断を行う際、以下の 3 つについて確認いただくことが、助けになるかもしれません。 プロセッサ・ペリフェ ラル 1 個の 4 線式 SPI コント ローラ (4 チップ・セレク ト ) 1 個の NAND コントロー ラ (MLC または SLC) 2 個の 10/100/1G イーサ ネット・コントローラ 2 個の USB 2.0 On-the-Go (OTG) コントローラ 1 個の SD/MMC/SDIO コン トローラ 2 個の UART 4 個の I2C コントローラ 2 個の CAN コントローラ 2 個の SPI マスタ、2 個の SPI スレーブ・コントロー ラ 4 個の 32 ビット汎用タイ マ 2 個の 32 ビット・ウォッ チドッグ・タイマ 1 個または 2 個の 4 線式 SPI コントローラ (2 チッ プ・セレクト ) 1 個のスタティック・メモ リ・コントローラ (NAND-SLC、NOR、または SSRAM) 2 個の 10/100/1G イーサ ネット・コントローラ 2 個の USB 2.0 OTG コン トローラ 2 個の SD/SDIO コント ローラ 2 個の UART 2 個の I2C コントローラ 2 個の CAN コントローラ 2 個の SPI コントローラ ( マスタまたはスレーブ ) 2 個の 16 ビット・トリプ ルモード・タイマ/カウ ンタ 1 個の 24 ビット・ウォッ チドッグ・タイマ 1 個の 10/100/1G イーサ ネット・コントローラ 2 個の USB 2.0 OTG コン トローラ 2 個の UART 2 個の I2C コントローラ 1 個の CAN コントローラ 2 個の SPI 2 個の汎用タイマ 1 個のウォッチドッグ・タ イマ 1 個のリアルタイム・ク ロック (RTC)

FPGA ファブリック Cyclone V、Arria V Artix-7、Kintex-7 Fusion2 FPGA のロジック集積 度範囲 25 K ~ 462 K LE 28 K ~ 444 K LC 6 K ~ 146 K LE FPGA 内のハード・メ モリ・コントローラ 最大 3 個、ECC 付き なし なし 高速トランシーバ すべての集積度で利用可 能 高集積デバイスのみ 高集積デバイスのみ アナログ・ミックス ド・シグナル (AMS) なし 2 x 12 ビット、1 MSPS ア ナログ - デジタル・コン バータ (ADC) なし ブート・シーケンス プロセッサ優先、FPGA 優 先、または同時 プロセッサ優先 プロセッサ・ブート、 FPGA は不揮発性 表 1. 現在市販されている SoC FPGA ( 3 / 3 )

既存のデザインは、FPGA と独立したマイクロプロセッサを使用しているか。 現行世代は、マイクロプロセッサを含む独自の ASIC を使用しているか。 現在はマイクロプロセッサを使用しているが、アプリケーションにより合ったペ リフェラル・セットがあれば有益か。

2 チップ・プロセッサ/ FPGA アプリケーションに対する利点

FPGA と独立したマイクロプロセッサをすでに使用しているデザインの場合は、明ら かに SoC FPGA を検討すべきです。 SoC FPGA を使用すれば、ボード・スペース、消費電力、およびシステム・コストを 最大 50% 削減しながら、同等以上の機能性と性能が得られる可能性があります。FPGA とマイクロプロセッサを同じシリコンに統合することにより、一方のプラスティッ ク・パッケージのコストが不要になることに加え、デバイスが 1 個になれば 2 個の場 合よりもボード・スペースの節約になります。また、デザインに含まれる CPU と FPGA がそれぞれ別の外部メモリを使用している場合、両方のメモリ・デバイスを 1 つに統合できる可能性があり、そうすればシステム・コスト、ボード・スペース、お よび消費電力をさらに削減することが可能です。プロセッサと FPGA 間の信号が同一 シリコン内でやりとりされるようになるため、別のチップを使用する場合に比べて、 通信に必要な消費電力が大幅に削減されます。しかも、統合ソリューションの場合、 プロセッサと FPGA 間の何千もの内部接続のおかげで、2 チップ・ソリューションに 比べて大幅な広帯域幅化と低レイテンシ化につながります。ASIC ベースのプロセッサに対する利点

現行世代がマイクロプロセッサを含む独自の ASIC を使用している場合はどうでしょ うか。現在 ASIC テクノロジを使用しているデザイン・チームのほとんどは恐らく、 すでにある時点で FPGA について検討したことがあり、たいていプロトタイピングま たはエミュレーション・フェーズで使用しています。多くの ASIC 設計者にとって、 従来 ARM プロセッサが搭載されていないことが量産への FPGA テクノロジの使用の 障害となっていました。この新しいタイプの SoC FPGA は、現在の 28nm プロセス・ テクノロジで最大 1 GHz で動作するフル機能かつ完全互換の高性能デュアルコア ARM Cortex-A9 プロセッサを搭載しており、そうした障害はなくなりました。 SoC FPGA はプログラマブル・ロジック・テクノロジを利用しているため、プログラ マブル・デザインでは次のような標準 ASIC テクノロジに対する従来の FPGA の利点 をすべて享受できます 高価なマスクが不要または購入の必要性が最小限 - 1 個でも百万個単位でもコス ト効果の高い SoC FPGA ソリューションを構築・出荷可能 市場投入期間の短縮 - 製造リードタイムが不要。大手電子部品代理店から市販デ バイスを入手可能 リスクの低減 - 製品出荷後もいつでも SoC FPGA の再プログラミングが可能。イ ンフィールド・アップデート/アップグレードをサポート 市場要件の変化や新規格に適応 エンベデッド・プロセッサ、高速トランシーバ、またはその他の先進システム・ テクノロジに対する追加のライセンスまたはロイヤルティの支払いが不要

他のプロセッサやマイクロコントローラに対する利点

最後のシナリオでは、通常は FPGA ではなくスタンドアロン・マイクロプロセッサま たはハイエンドを使用するシステムも、これらの最新 SoC FPGA の利点を享受できる 可能性があります。多くの設計者は入手可能な市販プロセッサを調査しますが、アプ リケーションに最適とは言えないデバイスで妥協し、イーサネット・ポート、USB チャネル、割り込みラインなどが不足しているプロセッサを選んでしまうことが少な くありません。これらの SoC FPGA は、カスタム ARM マイクロプロセッサを机の上 で直ちに開発できるほどの能力を備えています。従来は市販の派生プロセッサ製品が なかったために妥協を余儀なくされたシステム・デザインも、アプリケーションに合 わせたカスタマイズが可能になります。その結果、競合他社がコピーまたは模倣する ことが困難になり、ハードウェア、ソフトウェア両面でのデザインの差異化が実現し ます。特定のアプリケーションに適した SoC FPGA の選択方法

表 1 に示すさまざまなベンダーのプログラマブル SoC 製品は、一見したところでは似 ているように見えるかもしれません。いずれも ARM プロセッサ、各種ペリフェラル、 および FPGA を 1 個のデバイスに集積しています。しかし、実際には、データシート に表れていない部分にも目を向けながら綿密に評価することが非常に重要です。基礎 となるアーキテクチャとその影響は、特定のアプリケーションに対して評価しなけれ ばなりません。SoC FPGA はアーキテクチャが重要です。調査・検討を進めるうちに、 アーキテクチャ・レベルで大きな違いが数多く明らかになります。 では、どう選択すればよいのでしょうか。このホワイトペーパーでは、アプリケー ションに最適なプログラマブル SoC を選択する際のデザイン上の検討事項および技 術上のトレードオフの判断について解説します。主な選択基準は以下の 6 つの領域で す。 システム性能 システム信頼性および柔軟性 システム・コスト 消費電力 将来のロードマップ 開発ツール

システム性能

異なる要素間の効率的なデータ移動に影響する SoC FPGA アーキテクチャの領域は、 究極的には次の 2 つです。 インタコネクト オンチップおよびオフチップのメモリ帯域幅L3 インタコネクトの重要性:最大性能のためのセントラル・スイッチ

SoC アーキテクチャについて最初に検討すべき項目は、レベル 3 (L3) インタコネクト です。L3 インタコネクトは、データ転送用 L1/L2 キャッシュの次のレベルであるこ とに名前が由来し、メモリ、FPGA ファブリック、プロセッサ、およびペリフェラル 間のデータをルーティングします。表 2 に、SoC FPGA ベンダー間の L3 システム・イ ンタコネクトに関する機能比較を示します。アルテラ SoC FPGA は、L3 メイン・スイッチ、L3 マスタ・ペリフェラル・スイッチ、 および L3 スレーブ・ペリフェラル・スイッチという 3 つのスイッチからなる L3 シス テム・インタコネクトを備えています。これは、図 1に示すように、ARM の AMBA® NIC-301 ネットワーク・インタコネクト・インフラストラクチャを使用して実装され ています。 アルテラ SoC FPGA は、ノンブロッキング・スイッチ・アーキテクチャでレイテンシ を最小限に抑えるために、少階層バスを使用しています。インタコネクトは、複数の マスタからの複数の同時トランザクションを、各マスタが無停止 ( つまり「ノンブ ロッキング」) で動作するのに十分な帯域幅でサポートできるように設計されていま す。バス・アービトレーションをガイドするために、各マスタに優先順位レベルを割 り当てることができます。優先順位が同じマスタのアービトレーションは、最長時間 未使用法 (LRU) アルゴリズムを使用して行われます。 図 1. アルテラ SoC FPGA のインタコネクト・アーキテクチャ

マルチレベル階層を使用した SoC FPGA アーキテクチャも可能ですが、レイテンシが 生じる可能性があります。分散アービトレーションは、1 つの交差点に何人もの交通 整理員を配置するようなものです。このアプローチでは、マスタが停止しないように するには中央 QoS ( サービス品質 ) モジュールを使用する必要があります。また、分 散アービトレーションには調整の問題もあり、DDR メモリ・ポートのアービトレー ションと競合する可能性があります。

プロセッサ - FPGA インタコネクト:統合デバイスの利点を実現

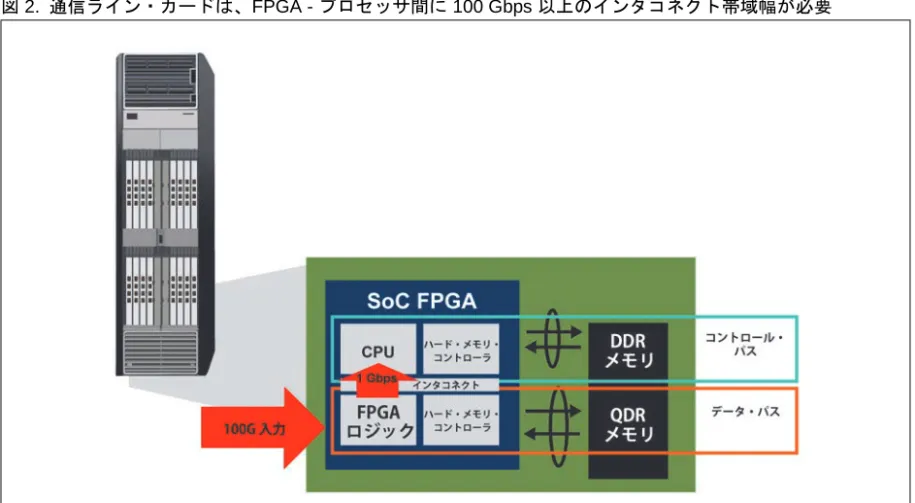

SoC FPGA アーキテクチャの大きな利点の 1 つは、プロセッサと FPGA の緊密なオン チップ結合です。この性能上の利点を実現するには、システム・データ転送のボトル ネックとならないように十分な帯域幅 ( 幅および速度 ) を備えた、適切なタイプのプ ロセッサ - FPGA インタコネクトを構築することが不可欠です。 この点について説明するために、図 2に示す通信ライン・カード・アプリケーション は 100 Gbps のネットワーク・データを処理する必要があるとします。FPGA は受信 データを高速で処理できますが、たとえプロセッサがトラフィックの 1 % しか処理し ない場合でも、1 Gbps ものデータが FPGA ロジックとプロセッサ間のインタコネクト を流れなければなりません。幸い、現在市販されている SoC FPGA は、FPGA ロジッ クとプロセッサの間で最大 125 Gbps あるいはそれ以上という、このタイプのアプリ ケーションには十分すぎるほどのスループットをサポートしています。

表 2. SoC FPGA デバイスの L3 システム・インタコネクト機能比較

機能 アルテラ SoC FPGA ベンダー B

インフラストラクチャ ARM AMBA NIC-301 ARM AMBA NIC-301

バス階層 少階層 マルチレベル

アービトレーション マスタごとに優先順位をプログラム

可能。優先順位が同じ要求には LRU。分散。QoS ブロックで制御。

一部の SoC FPGA デバイスは、構造上、データパスとコントロール・パスが帯域幅を 奪い合います。プロセッサは、FPGA ロジック内のハードウェア・アクセラレータへ のアクセスをセットアップし、コンフィギュレーションする必要があるかもしれませ ん。これらのコントロール・トランザクションがデータ・トラフィックと競合した場 合、高スループット・データ・トラフィックがブロックされ、受信データの連続処理 が中断する可能性があります。同様に、広帯域幅データ・トラフィックによってコン トロール信号に遅延が生じ、コントロール・レイテンシが増加する可能性もあります。 これを防止するために、アルテラ SoC FPGA は、低レイテンシ/ノンブロッキングの 「軽量」インタコネクト・ブリッジを別に備えています。プロセッサは、この単純な 32 ビット ARM AXI™ (Advanced eXtensible Interface) インタフェースを介して、FPGA 内のコントロール・レジスタにアクセスするため、高スループット・データ・フロー をブロックしたり、影響を与えたりすることがありません ( 図 3 の 低レイテンシ )。 一方、プロセッサと FPGA 間の広帯域幅データ接続は、32、64、または 128 ビット幅 トランザクションをサポートしています (図 3 の 高スループット )。表 3 に、両方の データパスのコンフィギュレーションを示します。 図 3. アルテラ SoC FPGA は、高スループット・データパスとノンブロッキング低レイテンシ・コントロー ル・パスを装備

表 3. SoC FPGA 内のプロセッサ - FPGA システム・インタコネクト機能 ( 1 / 2 )

機能 アルテラ SoC FPGA ベンダー B

広帯域幅プロセッサ/ FPGA インタコネクト

1 個の 32/64/128 ビット AXI (CPU → FPGA) 1 個の 32/64/128 ビット AXI (FPGA → CPU)

2 個の 32 ビット AXI (CPU → FPGA) 2 個の 32 ビット AXI (FPGA → CPU) 低レイテンシ・プロセッサ/ FPGA インタコネクト 1 個の 32 ビット AXI (CPU → FPGA) 一方の広帯域幅バスを 利用しなければならな い プロセッサ/ FPGA インタコネクトの合計最大理論帯域幅 (1) 10.8 Gbps 4.8 Gbps プロセッサ/ FPGA インタコネクト・データ幅 x32、x64、または x128 x32 固定

DDR メモリ・コントローラの性能

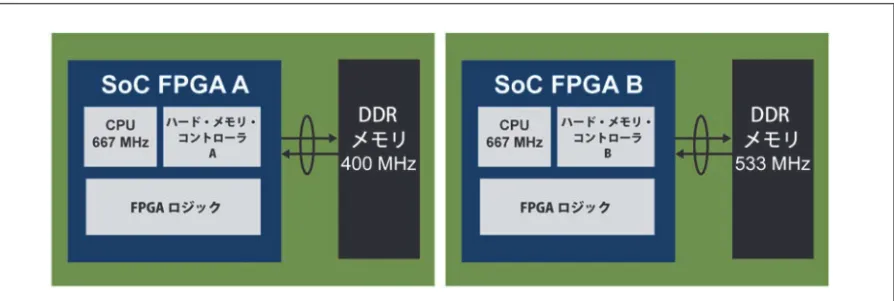

デザインに使用する DDR DRAM を選択する際、通常はメモリ速度によって実際の性 能が決まると思うはずです ( 表 4 を参照 )。しかし、メモリ・データ転送の優先順位 付け、スケジューリング、および処理をどうインテリジェントに行うか等、他の要因 も全体的なメモリ性能に大きく影響する可能性があります。 この影響について説明するために、図 4 に示すように、メモリ・バス速度が異なる 2 つの SoC FPGA デバイスについて考えてみましょう。どちらも 667 MHz で動作する デュアルコア ARM Cortex-A9 プロセッサを搭載していますが、一方のデバイスは 400 MHz で動作する外部メモリを使用し、もう一方は 533 MHz で動作する外部メモリを 使用しています。一見したところ、533 MHz メモリを使用するシステムの方が、メモ リ性能が高い分、33% 高い性能を示すと思われるかもしれません。しかし、メモリ・ コントローラ・アーキテクチャの進歩により、実際にはかなり異なる結果となります。 プロセッサ/ FPGA トランザクション・バッファ 書き込み 16 個 + ECC 読み出し 16 個 + ECC 書き込み 8 個 読み出し 8 個 注: (1) インタコネクト・バス速度を 150 MHz と仮定。理論最大値 = バス速度 X データ幅。プロトコルおよびバッファリングのオー バーヘッドにより、実際の帯域幅は低くなります。表 3. SoC FPGA 内のプロセッサ - FPGA システム・インタコネクト機能 ( 2 / 2 )

機能 アルテラ SoC FPGA ベンダー B

図 5 は、LMbench というシステム性能ベンチマークの結果です。アルテラは、メモ リ・システム性能の業界標準ベンチマーク (www.bitmover.com/lmbench) であることか ら、LMbench を採用しています。LMbench バージョン 3 による部分読み出し/書き込 みのケースは、典型的なエンベデッド・アプリケーションの転送を示しています。 図 5. LMbench の部分読み出し/書き込みメモリ帯域幅テストは、高度なコントローラの利点を実証 高いほど優秀 転送サイズ (バイト) メ モ リ 帯域幅 (MB/秒) 5,000 4,000 3,000 2,000 1,000 0 512 1 K 2 K 4 K 8 K 16 K 32 K 64 K 128 K 256 K 512 K 1 M 2 M 4 M 8 M 16 M 32 M 64 M より高度なメモリ・コントローラを搭載 しているため、アルテラ SoC FPGA の 400 MHz DDR3 メモリ・インタフェース は、競合デバイスの 533 MHz DDR3 メ モリ・インタフェースよりパフォーマン スが優れています。 ベンダー B CPU: 667 MHz DDR3: 533 MHz アルテラ SoC FPGA CPU: 667 MHz DDR3: 400 MHz

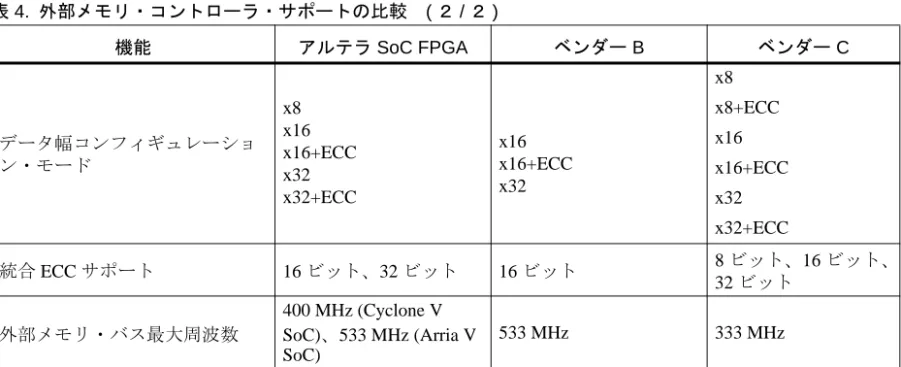

測定帯域幅は、データ・サイズが L1 キャッシュから L2 キャッシュ、外部メモリへと 移動するにつれて、徐々に低下します。 図 6 に示すように、より高度なメモリ・コントローラを搭載したアルテラ SoC FPGA は、メモリ動作周波数が低いにもかかわらず、最大 17% 高いメモリ帯域幅を引き出 しています。 これらの結果は、SoC FPGA を比較する際に、メモリ・バス仕様だけでなく、メモリ・ システム性能の測定値を確認することが重要であることを示しています。これもアー キテクチャが重要である領域の例です。最新のメモリ・コントローラは、システム・ メモリの効率を最大化するために高度なアルゴリズムを採用しています。これらのア ルゴリズムは、トランザクションの優先順位の管理、コマンド/データのリオーダリ ング、および DWRR (Deficit Weight Round Robin) のような高度なアルゴリズムによる 保留トランザクションのスケジューリングによって、最大限の帯域幅を引き出しま す。さらに、ソフトウェアによるシステムのカスタム・データ・プロファイルに合わ せたメモリ・コントローラのカスタマイズ、優先順位の設定、ポートまたはトランザ クション・チャネルの割り当て、さらには帯域幅共有の微調整によって性能向上を図 ることも可能です。優れたメモリ・コントローラは、システム・メモリから広帯域幅 を引き出すだけでなく、動作周波数を下げて消費電力を削減することも可能にしま す。 図 6. データ転送サイズ別の LMbench メモリ帯域幅の差 表 4. 外部メモリ・コントローラ・サポートの比較 ( 1 / 2 ) 機能 アルテラ SoC FPGA ベンダー B ベンダー C プロセッサ・システム用ハード 外部メモリ・コントローラ あり あり あり サポートする最大アドレス空間 4 G 1 G 4 G サポートするメモリ・タイプ LPDDR2、DDR2、 DDR3L、DDR3 LPDDR2、DDR2、 DDR3L、DDR3 LPDDR、DDR2、 DDR3

FPGA とプロセッサの DDR メモリ・コントローラの接続

SoC FPGA アプリケーションのコスト削減のためのオプションとして、FPGA 内に組 み込まれている機能は、プロセッサの DDR メモリ・コントローラを介してシステム・ メイン・メモリにアクセスできます。ただし、プロセッサのメモリ・コントローラを 共有すると、プロセッサまたは FPGA の性能が制限される可能性があります。そのた め、FPGA からプロセッサのメモリ・コントローラへの接続は帯域幅に最適化しなけ ればなりません。

表 5 に示すように、アルテラ SoC FPGA とベンダー B の SoC FPGA のいずれも、FPGA からプロセッサのメモリ・コントローラまでのビット幅は全体で 256 ビットです。ベ ンダー B のデバイスでは、4 個の 64 ビット・ポートのうち、2 個はメモリ・コント ローラにスイッチングされ、残りの 2 個はオンチップ・メモリ (OCM) にスイッチン グされます。アルテラ SoC FPGA では、256 ビット・ポートのラインはすべてプロセッ サのメモリ・コントローラに直接接続されており、最大 6 個の独立したコマンド/応 答ポート、4 個の読み出しポート、または 4 個の書き込みポートにコンフィギュレー ションできます。256 ビット・インタフェースを共有する各ポートは、異なるバス・ プロトコル、異なるデータ幅、および異なるコンフィギュレーションを潜在的にサ ポートできます。たとえば、アルテラ SoC FPGA では、プロセッサの DDR メモリ・ コントローラに対する FPGA インタフェースは、128 ビット Avalon® Memory-Mapped インタフェースと 2 個の 64 ビット AXI ポートを同時にサポートします。アルテラの FPGA-DDR メモリ・インタフェースは、最大インタフェース・クロック・レートで最 大 9,600 M バイト / 秒のピーク帯域幅をサポートします。 この追加の帯域幅は、FPGA インタフェースとプロセッサのメモリ・コントローラの 直接接続により、介在するスイッチまたはインタコネクト・レイヤから解放された結 果です。直接接続により、すべてのメモリ・ポートにおいて、最大限の帯域幅と優先 順位付けにおける最大限の柔軟性が得られます。それに対し、ベンダー B のインタ フェース上の 4 個のポートは、プロセッサのメモリ・コントローラ上の 2 個のポート に多重化されるため、最大帯域幅が低下します。 データ幅コンフィギュレーショ ン・モード x8 x16 x16+ECC x32 x32+ECC x16 x16+ECC x32 x8 x8+ECC x16 x16+ECC x32 x32+ECC 統合 ECC サポート 16 ビット、32 ビット 16 ビット 8 ビット、16 ビット、 32 ビット 外部メモリ・バス最大周波数 400 MHz (Cyclone V SoC)、533 MHz (Arria V SoC) 533 MHz 333 MHz 表 4. 外部メモリ・コントローラ・サポートの比較 ( 2 / 2 ) 機能 アルテラ SoC FPGA ベンダー B ベンダー C

プロセッサのメモリ・コントローラに対するこれらの FPGA インタフェースは、トラ フィックの相対優先順位もサポートしています。アルテラ SoC FPGA には、デバイス 内の通信をカスタマイズできるように 8 つの絶対優先順位レベルがあり、FPGA から のトランザクションを動的かつ個別に優先順付けすることが可能です。一方、ベン ダー B の SoC FPGA の絶対優先順位レベルは 2 つです。

ARM Cortex-A9 プロセッサを搭載した SoC FPGA は、ARM の AXI Exclusive 機能もサ ポートしています。これは、基本的にトランザクションに関するハードウェア・ベー スの特殊なセマフォ操作ですが、操作中に特定のマスタにバスを割り当てません。AXI Exclusive セマフォ・タイプ操作は、バス・アクセス、レイテンシ、または達成可能な 最大帯域幅に影響しません。アルテラ SoC FPGA デバイスの AXI Exclusive 機能は、す べての DDR メモリ・ポートにわたるトランザクションをサポートしています。他の デバイスではポート単位でのみ利用可能です。

ハードウェア・アクセラレーションとキャッシュ・コヒーレンシ

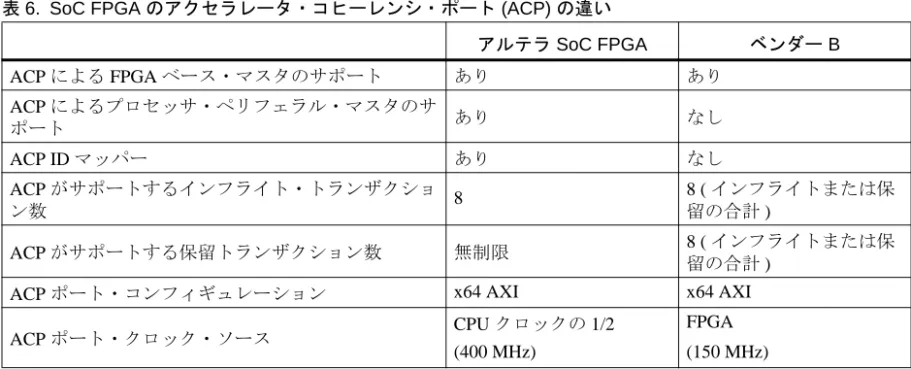

統合プロセッサ/ FPGA システムのもう 1 つの潜在的利点として、計算量の多い機能 を FPGA ロジックで高速化することでシステム性能の向上が可能であることが挙げ られます。CRC ( 巡回冗長検査 ) の計算から TCP/IP スタック全体のオフロードまで、 ほぼすべての処理を FPGA ロジックで高速化することでプロセッサをオフロードで きます。FPGA ベースのアクセラレータによって新しい結果が出たら、プロセッサが データのビューを更新できるように、可能な限り迅速にデータをプロセッサに戻す必 要があります。 表 5. FPGA とプロセッサの DDR メモリ・コントローラの接続 機能 アルテラ SoC FPGA ベンダー B FPGA-DDR メモリ・イン タコネクト・パス 256 ビット、AXI/Avalon-MM インタ フェース (FPGA → DRAM) 4 個の 64 ビット AXI (FPGA → DRAM およびオンチップ RAM) 個別ポート・サイズ・オ プション 8/16/32/64/256 ビット 32/64 ビット 最大 FPGA - インタコネク ト・ポート 6 個のコマンド/応答ポート 4 個の読み出しポート 4 個の書き込みポート 4 個の x64 読み出しポート 4 個の x64 書き込みポート プロセッサ DDR ハード・ メモリ・コントローラ・ ポートに対する最大イン タコネクト 6 個のコマンド/応答ポート 4 個の読み出しポート 4 個の書き込みポート 2 個の x64 読み出しポート 2 個の x64 書き込みポート (4 個のポートから多重化 ) 接続 直接 スイッチング (4 個の FPGA ポートをメ モリ・インタコネクト内の 2 個の DDR メモリ・ポートに多重化 ) FIFO サイズ 16 x 256 = 512 バイト + ECC 128 x 64 = 1 K バイト 相対トラフィック優先順 位 あり あり 絶対優先順位レベル 8 2 AXI Exclusive メモリ共有 最大ポート数 全ポート、全 ID 1 ポート、2 IDARM Cortex-A9 ベースの SoC FPGA は、アクセラレータ・コヒーレンシ・ポート (ACP) と呼ばれる機能を備えています。ACP により、FPGA ベースのハードウェア・アクセ ラレータによって生成された新しいデータは、低レイテンシの直接接続を介して、迅 速だけでなくコヒーレントに、プロセッサの L2 キャッシュに直接転送されます。 ACP ロジックはコヒーレンシを自動的に維持するため、コヒーレントなデータ転送に は約 30 サイクルが必要です。データ・コヒーレンシを保証するための他の方法は L2 キャッシュをフラッシュすることですが、それには数百サイクルが必要です。表 6 に

示すように、アルテラ SoC FPGA は FPGA ベースの機能とプロセッサ・ペリフェラル の両方に対してコヒーレント・トランザクションをサポートしています。他の SoC FPGA は、1 個の専用ポートを介した FPGA 機能のみをサポートしており、プロセッ サ・ペリフェラルからのトランザクションはサポートしていません。 本来、ACP インタフェースは一般に専用アクセラレータも、ACP サポートを必要と するペリフェラルも少数しか備えていないフルカスタム SoC デバイス用に設計され たものです。そのため、ARM ACP インタフェースがサポートするインフライト・ト ランザクションまたは保留トランザクションは、合計 8 つのみです。しかし、SoC FPGA は、柔軟なプログラマブル・アーキテクチャのため、コヒーレント・サポート が必要なハードウェア・アクセラレータをさらに多く搭載していることがあります。 そうした機能を 8 つ以上サポートするために、アルテラ SoC FPGA は、8 つのインフ ライト・トランザクションに加えて、無制限数の保留トランザクションをサポートす る ACP ID マッパーを備えています。

追加のメモリ・コントローラによる最大システム性能の向上

どの SoC FPGA も、主にプロセッサのコードおよびデータの保存・検索用として、専 用 DDR ハード・メモリ・コントローラをプロセッサ・サブシステムの一部として備 えています。プロセッサの・メモリ・コントローラは、コスト削減のために、FPGA 内のロジック機能と共有することも可能です。表 6. SoC FPGA のアクセラレータ・コヒーレンシ・ポート (ACP) の違い

アルテラ SoC FPGA ベンダー B ACP による FPGA ベース・マスタのサポート あり あり ACP によるプロセッサ・ペリフェラル・マスタのサ ポート あり なし ACP ID マッパー あり なし ACP がサポートするインフライト・トランザクショ ン数 8 8 ( インフライトまたは保 留の合計 ) ACP がサポートする保留トランザクション数 無制限 8 ( インフライトまたは保 留の合計 )

ACP ポート・コンフィギュレーション x64 AXI x64 AXI

ACP ポート・クロック・ソース CPU クロックの 1/2

(400 MHz)

FPGA (150 MHz)

しかし、最大、性能、アプリケーションによっては、表 7 に示すように、プロセッサ のメモリ・コントローラと FPGA のメモリ・コントローラを分けておいた方がよい場 合もあります。アプリケーション・ソフトウェアが特に高負荷な場合、プロセッサ専 用のメモリ・アレイを確保すると有効です。同様に、広帯域幅 FPGA アプリケーショ ンも専用のメモリ・アレイを確保すると有効です。 表 8 に示すように、アルテラの 28nm SoC FPGA は、1 個または 3 個の、独立したハー ド DDR メモリ・コントローラを搭載、FPGA ロジック機能専用、プロセッサの・メ モリ・コントローラと同じ、高度な機能を備えてどの市販 SoC FPGA も、プログラマ ブル・ロジックからの専用メモリ・コントローラの構築および FPGA ファブリックへ の追加をサポートしています。欠点は、これらのソフト・コントローラと他のアプリ ケーション・ロジックの間で FPGA リソース・アクセスの競合が発生することです。 また、ソフト・メモリ・コントローラの構築およびタイミング収束に時間がかかるた め、より重要な独自 IP の開発に振り向けられる貴重な設計時間が減ることにもなり かねません。

システム信頼性および柔軟性

高度に統合された SoC FPGA は、より信頼性に優れたシステムの構築にも役立ちま す。市販 SoC FPGA デバイスを差異化する重要な側面は次の 2 つです。 表 7. さまざまなアプリケーション・タイプにおけるプロセッサおよび FPGA メモリ・インタフェースの使用 アプリケーション・ タイプ プロセッサ・メモリ・コントローラ FPGA メモリ・コントローラ 最少コスト プロセッサと FPGA 機能がプロセッサのメモ リ・コントローラを使用して共通の DDR メモ リ・サブシステムを共有 使用しない プロセッサと FPGA が 共通の大容量メモリ領 域を共有 プロセッサと FPGA 機能がプロセッサのメモ リ・コントローラを使用して共通の DDR メモ リ・サブシステムを共有 他の FPGA 機能に利用可能 高負荷な計算システム プロセッサのメモリ・コントローラはプロ セッサ専用 FPGA 機能はすべて、FPGA のメ モリ・コントローラを使用して HPS のメモリ・コントローラをオ フロード 広帯域幅 FPGA 機能 プロセッサはプロセッサのメモリ・コント ローラを使用し、場合によっては他の狭帯域 幅 FPGA 機能と共有 FPGA メモリ・コントローラは FPGA 専用 表 8. FPGA アプリケーション専用のハード・メモリ・コントローラおよびソフト・メモリ・コントローラ 機能 アルテラ SoC FPGA ベンダー B ベンダー C FPGA ファブリック内のハード・メモ リ・コントローラ 1 ~ 3 個 ( デバイスによ る ) なし なし FPGA ファブリック内のソフト・メモ リ・コントローラ あり、FPGA ロジックを 使用 あり、FPGA ロジッ クを使用 あり、FPGA ロ ジックを使用 システム内で利用可能なメモリ保護の程度 SoC FPGA のソフトウェア・バグへの対応

ECC によるメモリ内容の保護

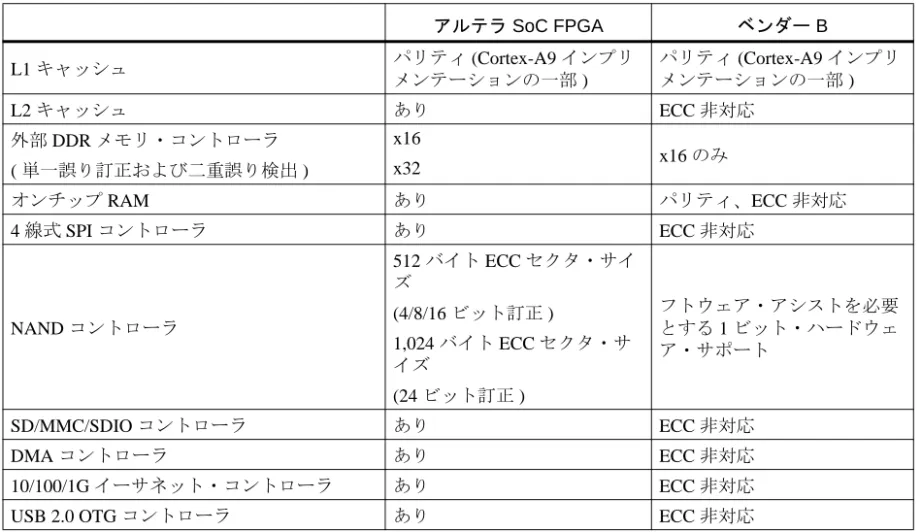

現在のデザインにおける傾向として、エラーの検出、修正、および監視の必要性が高 まっています。メモリ・サイズおよび集積度が増大し続ける中、エラー検査および訂 正の必要性と重要性も高まっています。ほとんどの最新システムは、データの完全性 の確保を支援する専用ハードウェアを備えています。f 詳細については、ホワイトペーパー「 Error Correction Code in SoC FPGA-Based Memory Systems」( 英語版・PDF) を参照してください。 SoC FPGA の観点から見て、これにはメモリ・コントローラの一部としてだけでなく、 プロセッサのオンチップ・メモリ、キャッシュ、およびペリフェラル・バッファ内に 統合された ECC ( 誤り訂正符号 ) 保護が含まれます。ECC 回路により、予期しない データ・エラーや壊れたデータに対するシステムの堅牢性と耐性が向上します。 当面の対策として、データの完全性が不可欠であるアプリケーション、システム・メ イン・メモリに ECC を追加することが不可欠ですが、保護可能なものをすべて保護 することが重要です。つまり、メイン・メモリだけでなく、L2 キャッシュおよびオ ンチップ RAM も ECC で保護することが重要ということです。これもアーキテクチャ が重要である領域の例です。考え抜かれたアーキテクチャでは、データ転送パスのす べてのステップに配慮が行き届き、各ステップに適切な保護が組み込まれています。 ECC 保護は、デバイスに組み込まない限り、追加することが極めて困難で、しかも法 外なコストがかかります。 表 9 に、システム全体にわたって実装された ECC 回路を要約します。

表 9. SoC FPGA の ECC

アルテラ SoC FPGA ベンダー B L1 キャッシュ パリティ (Cortex-A9 インプリメンテーションの一部 ) パリティ (Cortex-A9 インプリメンテーションの一部 ) L2 キャッシュ あり ECC 非対応 外部 DDR メモリ・コントローラ ( 単一誤り訂正および二重誤り検出 ) x16 x32 x16 のみ オンチップ RAM あり パリティ、ECC 非対応 4 線式 SPI コントローラ あり ECC 非対応 NAND コントローラ 512 バイト ECC セクタ・サイ ズ (4/8/16 ビット訂正 ) 1,024 バイト ECC セクタ・サ イズ (24 ビット訂正 ) フトウェア・アシストを必要 とする 1 ビット・ハードウェ ア・サポート SD/MMC/SDIO コントローラ あり ECC 非対応 DMA コントローラ あり ECC 非対応

L1 キャッシュは、ARM Cortex-A9 プロセッサの一体部分です。性能上の理由に加え、 サイズが比較的小さいことから、ARM によって実装された L1 キャッシュは、パリ ティを使用してシングルビット・エラーを検出するもので、完全な ECC は備えてい ません。 NAND フラッシュも注目する価値があります。NAND フラッシュは、ファイル・シス テムの格納に役立ちますが、NOR フラッシュに比べて信頼性に欠けます。そのため、 NAND フラッシュ の ECC はエラーをなくすのに有効です。初期の NAND フラッ シュ・メモリ・コントローラには、シングルビット ECC 保護が組み込まれていまし た。これはある程度有効ですが、CPU が ECC を管理しなければならないため、性能 に大きく影響する可能性があります。最新の NAND メモリ・コントローラ、マルチ ビット ECC 保護を備えています。具体的には、アルテラ SoC FPGA に実装された NAND フラッシュ・コントローラは、512 バイト・セクタ・サイズに対する 4/8/16 ビット訂正、および 1,024 バイト・セクタ・サイズに対する 24 ビット訂正を備えてい ます。これにより、性能を低下させることなく、必要な保護が得られます。

共有メモリのメモリ保護

メモリ保護は、より高度なプロセッサに付随することが多い機能です。名称がメモ リ・マネージメント・ユニット (MMU) にせよ、メモリ保護ユニット (MPU) にせよ、 プロセッサのメモリ保護装置は、異常または不正なプロセッサ・トランザクションが 他のメモリ領域を読み出したり、破損させたりするのを防止します。Cortex-A9 プロ セッサでは、この保護概念は、セキュリティが重要なシステムにシステム規模のアプ ローチを提供する TrustZone® テクノロジによって拡張されています。一部の SoC FPGA は、メモリ保護を FPGA まで拡大しています。なぜ FPGA からのメ モリ保護、あるいは FPGA のメモリ保護が必要なのでしょうか。プロセッサと FPGA は、コスト削減、ボード・スペース削減、または消費電力削減のために、1 つの外部 DDR メモリ・インタフェースを共有できます。もしカスタム FPGA ロジックがプロ セッサのデータ、アプリケーション・コード、またはオペレーティング・システム (OS) カーネルに属するメモリのセクションを誤って上書きしたらどうなるでしょう か。これは、システム障害やプロセッサの異常動作の原因となる可能性があります。

これを防止するために、図 7 に示すように、特定のメモリ領域をオペレーティング・ システムおよびエンベデッド・ソフトウェア・アプリケーションの専用にすると同時 に、他のメモリ領域を FPGA ベースの機能専用にすることができます。メモリ保護に より、FPGA ベースの機能によるオペレーティング・システムまたはエンベデッド・ ソフトウェアの領域の破損が防止されます。 表 10 に、FPGA から外部メモリへのアクセスに関するメモリ保護についてまとめて います。

どちらの SoC FPGA も ARM の TrustZone セキュリティ機能をサポートしていますが、 アルテラ SoC FPGA の保護領域の方が 1 M バイトまでと、グラニュラリティが高く なっています。しかも、アルテラ SoC FPGA は、特定の領域に対する 20 個のユーザー 定義可能保護ルールをサポートしています。そのため、よりきめ細かい調整と正確な コントロールが可能で、FPGA マスタによる不要な領域へのアクセスを防止できます。 図 7. プロセッサと FPGA がメモリを共有する場合の DDR メモリ保護 表 10. FPGA から外部メモリへのアクセスに関するメモリ保護 機能 アルテラ SoC FPGA ベンダー B TrustZone セキュリティ あり あり TrustZone 領域サイズのグラニュラ リティ 1 M バイト境界 64 M バイト境界 メモリ保護 20 個のユーザー定義保護ルール。 ルールごとに以下を定義: TrustZone アドレス範囲 マスタ ID 範囲 ポート範囲 ( マスク ) 包括/除外 TrustZone

ウォッチドッグ・リセットとその FPGA ロジックに対する影響

ウォッチドッグ・タイマは、異常なソフトウェアによってシステムが無効化されるこ とを防止します。前世代の 2 チップ ( プロセッサと FPGA) ソリューションでプロセッ サが異常停止した場合、FPGA は動作し続けますが、プロセッサのウォッチドッグ・ タイマがプロセッサをリセットし、システムはできる限り安全に回復します。適切に 設計された SoC FPGA は、同様の「独立」動作をサポートするほか、必要に応じて FPGA をリコンフィギュレーションすることが可能です。しかし、システム設計者が FPGA のリコンフィギュレーションを必要な動作として指定しない限り、すべての場 合において FPGA をリコンフィギュレーションする必要はないはずです。多くの場 合、プロセッサのセルフ・リセット中も、FPGA ロジックが外部スティミュラスの監 視・反応を続ける方が重要かもしれません。したがって、この状況における FPGA リ コンフィギュレーションの処理方法について確認することが重要です。 表 11 に示すように、アルテラ SoC FPGA のリセット回路は、従来の使用方法に適合 しています。プロセッサと FPGA のリセット回路は独立して動作します ( オプション として、リセット・イベントの相互通信も可能 )。CPU リセットに対する FPGA 部分 の反応として、コンフィギュレーション済み FPGA ロジック部分のみをリセットする か、FPGA を完全にリコンフィギュレーションするか、あるいは完全に無視するかを 開発者が決定します。ベンダー B の SoC FPGA では、CPU リセットが発生すると常 に FPGA ロジックはリコンフィギュレーションされます。フェイルセーフ・ブートおよびコンフィギュレーション

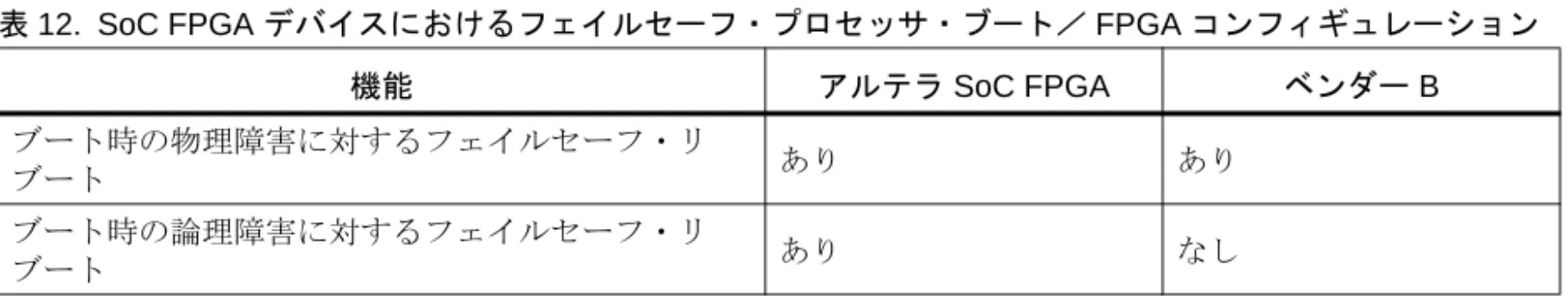

SoC FPGA は、完全にプログラマブルなシングルチップ・システムであるため、プロ セッサを正常にブートし、FPGA をコンフィギュレーションするまでは完全に機能し ません。SoC FPGA は、リモートでのインフィールド・システム・アップデートをサ ポートするシステムに不可欠な機能として、ブートまたはコンフィギュレーションが 失敗した場合のフェイルセーフ・リカバリ手段を備えています。表 12 に要約するよ うに、コンフィギュレーション中に物理障害が発生した場合、SoC FPGA は「フェイ ルセーフ」リカバリを実行します。また、コンフィギュレーション・ヘッダまたはコ ンフィギュレーション・イメージ自体に CRC エラーが発生した場合は、代替のコン フィギュレーション・イメージを自動的にロードします。表 11. SoC FPGA における CPU リセット

機能 アルテラ SoC FPGA ベンダー B CPU リセットに対する FPGA の反応 ユーザー定義: ユーザー・デザインに応じて FPGA ロジック内のフ リップフロップをリセット FPGA ロジックをリコンフィギュレーション 無反応 常に FPGA をリコンフィ ギュレーション

アルテラ SoC FPGA は、さらにその他の論理障害に対するフェイルセーフ・リカバリ 手段も備えています。アルテラ SoC FPGA が正常にブートすると、ブート・ローダ・ ソフトウェアはコンフィギュレーションの成功を示すビットを設定します。しかし、 ブート・ローダがビットの設定に失敗した場合、ウォッチドッグ・タイマはウォー ム・リセットをトリガしてブート・プロセスを再実行します。アルテラ SoC FPGA が ブート・プロセスを再実行すると、プロセッサは前回のブートの試みが失敗したもの と判断し、最後の既知の良好なイメージを選択します。

柔軟性

柔軟性は、多くの設計者が最初から FPGA を使用する共通の理由です。完全にプログ ラマブルな SoC は、デザインの柔軟性をシステム・レベルにまで広げます。このセク ションでは、SoC FPGA を選択する際に考慮すべきアーキテクチャ上の要素として、 次の 3 つに焦点を当てます。 プロセッサ・ブートおよび FPGA コンフィギュレーション・オプション オンチップ FPGA インタフェース 共通のパッケージ・フットプリントさまざまなプロセッサ・ブートおよび

FPGA コンフィギュレーション・オプション

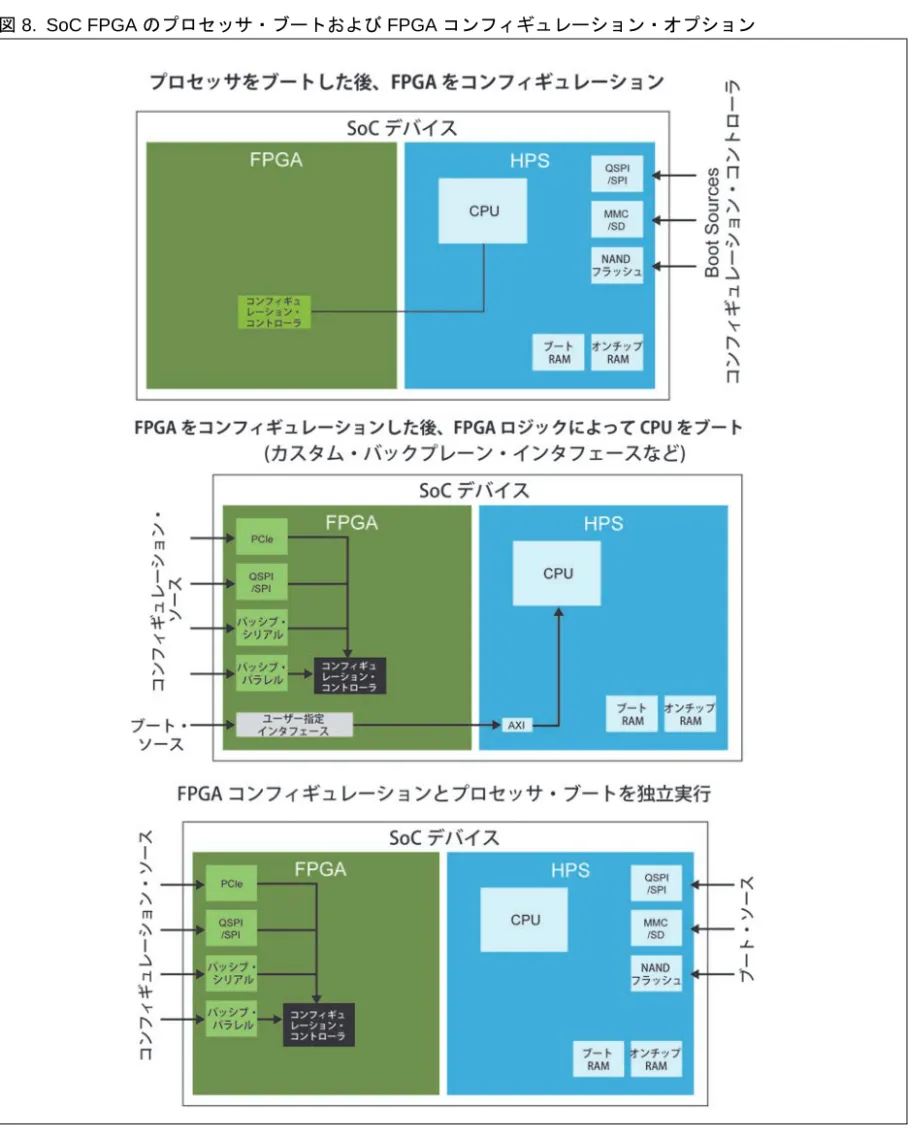

柔軟性の必要性は、ブートにも当てはまります。図 8 に示すように、SoC FPGA には プロセッサのブートおよび FPGA のコンフィギュレーションに関して、3 つのオプ ションがあります。表 12. SoC FPGA デバイスにおけるフェイルセーフ・プロセッサ・ブート/ FPGA コンフィギュレーション

機能 アルテラ SoC FPGA ベンダー B

ブート時の物理障害に対するフェイルセーフ・リ

ブート あり あり

ブート時の論理障害に対するフェイルセーフ・リ

どの SoC FPGA も、最初にプロセッサをブートした後、ソフトウェア制御下で FPGA をコンフィギュレーションする、プロセッサのような「CPU 優先」 ( 図 8 の上 ) をサ ポートしています。このモードは、プロセッサが FPGA を大きな「ペリフェラル」デ バイスとしてコンフィギュレーションすることを除いて、通常のプロセッサ・ブート と同様に機能します。このモードの利点は、最初にプロセッサを起動する従来の方法 に従っているため、既存のブート・コードを容易に変換できることです。欠点として は、プロセッサのブート中の遅延が許容されないシステムの場合、コンフィギュレー ション時間の制約があることや、プロセッサがブート中に FPGA が実行した方が好都 合な機能もあることなどが挙げられます。 2 番目のオプション (図 8 の中央 ) は、最初に FPGA をコンフィギュレーションした 後、FPGA ロジックによって CPU をブートします。この方法の用途としては、FPGA にシステムを検証させ、セキュリティ保護させてから、プロセッサにブートまたはそ の他のセキュア・ブート・モードを許可することや、FPGA を使用してカスタム・バッ クプレーンを起動した後、それを使用してプロセッサをブートすることが考えられま す。 3 番目のオプション (図 8 の下 ) は、プロセッサ・ブート・メカニズムと FPGA コン フィギュレーション・メカニズムが完全に独立しています。この例では、プロセッサ はいずれかのフラッシュ・メモリ・ソースからブートします。それとは別に、FPGA はいずれかのデータ・ソースからコンフィギュレーションされます。そのため、FPGA サブシステムを短時間 (13 ms 程度 ) でコンフィギュレーションし、FPGA の残りの部 分を PCI Express® (PCIe®) インタフェースにコンフィギュレーションさせることが可 能です。

表 13 に、2 つの SoC FPGA がサポートする各種ブート・モードを示します。現在、 ARM Cortex-A9 プロセッサ・ベースの SoC FPGA の中で、これら 3 つのオプションを すべてサポートして設計されているのはアルテラ SoC FPGA のみです。

複数のブート・イメージ

多くの SoC 開発者は、その固有の信頼性 (NOR テクノロジ )、比較的低いコスト、最 小の I/O 要件のため、4 線式 SPI フラッシュにブート・イメージを格納することを好 みます。プロセッサが FPGA のコンフィギュレーションを行うシステムの場合、以下 をはじめとするハードウェアおよびソフトウェアの内容がフラッシュ・ブート・イ メージに含まれます。表 13. SoC FPGA のプロセッサ・ブートおよび FPGA コンフィギュレーション・オプション

機能 アルテラ SoC FPGA ベンダー B

最初に CPU をブートした後、CPU が FPGA をコンフィギュレーショ

ン あり あり

最初に FPGA をコンフィギュレーションし、FPGA ファブリックまた

はバックプレーンによって CPU をブート あり なし

CPU ブート・コード オペレーティング・システム (OS) /リアルタイム・オペレーティング・システム (RTOS) アプリケーション・コードおよびデータ FPGA コンフィギュレーション 工場出荷時のデフォルト・イメージを格納したものが 1 つ、システム・アップデート を格納したものが少なくとも 1 つという具合に、一般に複数の「ブート・イメージ」 が望まれます。工場出荷時のデフォルト・イメージは、アップデートが正常にロード されなかった場合に備えて必ず格納されます。そうすれば、システムは自動的に既知 の良好なイメージに戻した上で、アップデートを再試行できます。 表 14 に、ソフトウェア要件が「最小限」と「高度」の場合に基づくブート・イメー ジ全体、および FPGA 集積度が低/中/高の場合のハードウェア・イメージの見積も りを示します。 4 線式 SPI デバイスの場合、選択する SoC ベンダーによっては、必要なストレージ容 量が問題となることがあります。アルテラは、最大 4 G バイト のアドレス空間をサ ポートした 4 線式 SPI インタフェース、および最大 4 つのチップ・セレクトを提供し ています。ベンダー B の 4 線式 SPI がサポートするアドレス範囲は 16 M バイト、チッ プ・セレクトは最大 2 つで、合計ブート・イメージ・サイズは 32 MB に制限されて います。 表 14. ブート・イメージのサイズ要件および 4 線式 SPI デバイスへのマッピング ソフトウェア要件 最小限 高度 ユーザー・スペース・コード (M バイト ) 5 5 5 50 50 50 Linux カーネル (M バイト ) 3 3 3 5 5 5 ブート・コード (M バイト ) 0.5 0.5 0.5 0.5 0.5 0.5 FPGA 集積度 低 中 高 低 中 高 FPGA ハードウェア・イメージ (M バイト ) 2.4 6.1 14.4 2.4 6.1 14.4 必要な合計ストレージ容量 シングル・イメージ (M バイト ) 11 15 23 58 62 70 デュアル・イメージ (M バイト ) 22 29 46 116 123 140 アルテラ SoC FPGA シングル・イメージ (4 線式 SPI デバイス数 ) 1 1 1 1 1 1 デュアル・イメージ (4 線式 SPI デバイス数 ) 1 1 1 1 1 2 ベンダー B シングル・イメージ (4 線式 SPI デバイス数 ) 1 1 2 ― ― ― デュアル・イメージ (4 線式 SPI デバイス数 ) 2 2 ― ― ― ―

表が示すように、アルテラ SoC FPGA は複数の大容量ブート・イメージをサポートで きます。ベンダー B の SoC FPGA は、扱うことができるブート・イメージのサイズお よび数が限られています。なお、上記見積もりでは、4 線式 SPI デバイスの最大サイ ズを 1 Gb (128 M バイト ) としています。

オンチップ FPGA インタフェース

柔軟性は、オンチップ FPGA インタフェースについても言えることです。アプリケー ションが標準ベースの多機能インタフェースを必要とする場合もあれば、シンプルな もので十分な場合や、カスタマイズされたものが必要な場合もあります。 高度な機能を必要とするアプリケーションのために、SoC FPGA はプロセッサ、ハー ド・ペリフェラル、および FPGA ロジックの接続に ARM の AXI を使用しています。 AXI 規格は、実証済みの業界標準を使用して、データ幅の広い高速インタフェースを 提供します。しかし、IP コアが AXI の多機能性をすべて必要としない場合や、拡張 性の方が重要な場合はどうでしょうか。極端な話をすれば、1000 線のカスタム・イン タフェースが必要な場合もあれば、LED の点滅やスイッチの読み出しのために 1 線で 十分な場合もあります。こうしたさまざまなニーズに対応するために、アルテラ SoC FPGA は AXI インタ フェースに加え、Avalon® Memory-Mapped (Avalon-MM) インタフェースおよび Avalon Streaming (Avalon-ST) インタフェースをサポートしています。これらのスケーラブル なアルテラ・インタフェース規格は、要件があまり厳しくない機能やその他の特定機 能に適しています。このため、IP 設計者は機能ごとに最適なインタフェースを選択で きます。また、アルテラ FPGA の既存顧客は、これらのインタフェースに基づいて構 築され、AXI の恩恵が得られない IP について、AXI への移行を強制されることなく IP を使用し続けることが可能です。

f Avalon インタフェースの詳細については、「Avalon Interface Specification」を参照して

ください。 表 15 に、FPGA IP インタフェースをまとめています。 表 15. SoC デバイスがサポートする FPGA IP インタフェース 機能 SoC FPGAアルテラ ベンダー B FPGA IP インタフェース AXI Avalon-MM Avalon-ST AXI

共通フットプリントでの集積度/トランシーバ/機能のマイグレー

ション

共通のパッケージ・フットプリントは、設計・開発・展開における柔軟性を高めます。 アルテラ SoC FPGA は、図 9 に示すように、ゲート集積度が異なるデバイス間でも、 パッケージ・フットプリントが同じであるため、デザインのマイグレーションを容易 に行えるように設計されています。さらに、パッケージ・フットプリントが共通であ る限り、トランシーバ内蔵デバイスとトランシーバ非内蔵デバイスの間でのマイグ レーションも可能です。さらなるコスト削減のために、トランシーバ非内蔵モデルに はデュアルコア・プロセッサ・バージョンまたはシングルコア・プロセッサ・バー ジョンが用意されています。これらのオプションにより、単一のプリント基板プラッ トフォームでさまざまなコスト目標や機能目標に対応できます。 図 9. アルテラ Cyclone V SoC ファミリの集積度/パッケージ・マイグレーション 注: 1. DRAM 専用 I/O を含む。 KLE 25 40 85 110 484 19 x 19 0.8 mm 66 66 66 66 161 672 23 x 23 0.8 mm 138 138 138 138 188 896 31 x 31 1.0 mm 288 288 188 ピン パッケージ・サイズ ボール・ピッチ I/O 数 デバイス・ ファミリ Cyclone V SoC FPGA HPS I/O(1) アルテラ:トランシーバ非搭載デバイス KLC 28 85 225 13 x 13 0.8 mm 54 86 400 17 x 17 0.8 mm 100 125 130 484 19 x 19 0.8 mm 200 130 ピン パッケージ・サイズ ボール・ピッチ I/O 数 デバイス・ ファミリ A PS I/O(1) ベンダー B:トランシーバ非搭載デバイス KLE 25 40 85 110 350 460 672 23 x 23 1.0 mm 145、6 145、6 145、6 145、6 188 896 31 x 31 1.0 mm 288、9 288、9 188 896 31 x 31 1.0 mm 178、12 178、12 216 ピン パッケージ・サイズ ボール・ピッチ I/O 数 (I/O、トランシーバ) デバイス・ ファミリ Cyclone V SoC FPGA HPS I/O(1) アルテラ:トランシーバ搭載デバイス 1,152 35 x 35 1.0 mm 350、18 350、18 216 1,517 40 x 40 1.0 mm 528、30 528、30 216 Arria V SoC FPGA KLC 74 125 350 444 485 19 x 19 0.8 mm 150、4 150、4 157 484 23 x 23 1.0 mm 163、4 130 676 27 x 27 1.0 mm 250、8 250、8 130 ピン パッケージ・サイズ ボール・ピッチ I/O 数 (I/O、トランシーバ) デバイス・ ファミリ A PS I/O(1) ベンダー B:トランシーバ搭載デバイス 900 31 x 31 1.0 mm 362、16 362、16 130 1,156 35 x 35 1.0 mm 362、16 362、16 130 Bシステム・コスト

現在出荷されているほとんどすべてのシステムは、コスト圧力の高まりにさらされて います。SoC FPGA は高度な機能を備えた革新的な製品ですが、アルテラ SoC FPGA は部品コストとシステム・コストの両方を考慮して設計されています。1 個の SoC FPGA に置き換えることで、コンポーネント・コストの最大 50% 削減に加え、システ ム・コストの削減にもつながる可能性があります。表 16 に、システム・コスト要素 比較を示します。 SoC FPGA のコストを検討する際は、次の 3 つの側面について考えることが重要です。 SoC にすでに統合されている同等機能の数 アプリケーションにおける高速トランシーバの必要性および必要数 付随する電源コスト

統合機能

SoC FPGA ソリューションはどう統合されているのでしょうか。アプリケーションに もよりますが、プロセッサ、すべてのペリフェラル、複数の DSP、豊富なオンチッ プ・メモリ、高速トランシーバ、クロック管理、および大量のカスタム・ロジックに 相当するシステムを 1 個の SoC FPGA に収容することが可能です。いずれにせよ、検 討すべき事項は多くあります。 シングルコアとデュアルコアの両方のプロセッサ・バージョンが用意されている か。 ARM プロセッサ・コアに加え、どのようなペリフェラルが統合されているか。 ハード・メモリ・コントローラはいくつ搭載されているか。 PLL (Phase-Lock Loop) は統合されているか。 コンフィギュレーション・オプションによるコスト削減方法はあるか。 FPGA アプリケーション用のハード・メモリ・コントローラは内蔵されているか、 追加の FPGA ロジックをコントローラに割り振る必要があるか。 プラットフォームのコスト最適化を図るための共通パッケージ・フットプリント はあるか。高速トランシーバ

高速トランシーバも非常に重要な機能であり、デザインのコストに大きく影響する可 能性があります。アルテラ SoC FPGA には、製品ライン全体にわたって高速トラン シーバ・オプションが用意されています。具体的には、最も大規模なフル機能のデバ イスはもちろん、ローエンドのエントリー・レベル・デバイスでも、高速トランシー バ内蔵製品がオプションとして入手可能です。高速トランシーバは、PCIe のようなア プリケーションには不可欠です。高速トランシーバが内蔵されていない場合、外部イ ンタフェース・コンポーネントが必要であり、システムの部品 (BOM) コストが増加 します。その一方で、高速トランシーバが不要なエンベデッド・デザインもあるため、 アルテラでは SoC FPGA コンポーネント・コスト削減のために、高速トランシーバを 内蔵していない SoC FPGA 製品も提供しています。電源コスト

必要な電圧レールの数および容量は、デザインのコストおよび複雑度に大きく影響し ます。どの SoC FPGA にも複数の電圧レールが必要ですが、必要な数はそれぞれ異な ります。また、SoC FPGA によっては、厳密なパワーオン/パワーオフ・シーケンス・ コントロールが必要であり、より高度な ( つまり、より高コストの ) 電源が必要にな ります。特に、パワーオフ・シーケンスは、発生し得るあらゆる潜在的な電力損失条 件のため容易ではありません。理想的には、パワーオンまたはパワーオフ条件がデバ イスの長期的な信頼性に影響する場合、そうした要件は回避すべきです。アルテラ SoC FPGA には、パワーオンまたはパワーオフ・シーケンス要件は一切ありません。 表 16 を参照してください。消費電力

消費電力の削減は、多くのデザインにおいて、決定的要因とは言わないまでも、ます ます重要な要因となっています。 SoC FPGA デバイスを選択する際、消費電力に関して検討すべき重要な領域は次の 3 つです。 表 16. SoC FPGA のシステム・コスト要素比較 機能 アルテラ SoC FPGA ベンダー B シングルコアとデュアルコアのプロセッサ・ オプション あり なし ( デュアルコアのみ ) プロセッサ・システムおよび FPGA ファブ リックのハード・メモリ・コントローラ あり ( プロセッサ・システムに 1 個、FPGA に最大 3 個 ) なし ( プロセッサ・システムに 1 個、FPGA はなし ) 全デバイスへの高速トランシーバ内蔵 ( 統合 PCIe に必要 ) あり なし (6 製品中 2 製品が高速トラン シーバ非内蔵 ) 統合アナログ・ミックスド・シグナル なし あり (2 x 12 ビット、1 MSPS ADCs) 相対トラフィック優先順位 あり あり ロジック集積度の範囲 25、40、85、110、350、 460 KLE 28、74、85、125、350、444 KLC パッケージ・マイクグレーション あり 限定的 パワーオフ・シーケンス要件 なし あり ( 追加の外部回路が必要 ) 統合

省電力モード

パワーオン/パワーオフ・シーケンス要件

統合による消費電力削減

図 10 に示すように、単にプロセッサと FPGA コンポーネントを 1 個の SoC FPGA に 統合するだけで、システム消費電力の 10% ~ 30% 削減につながる可能性があります。 多くの場合、高い電圧でデバイス間の信号を伝送する I/O は、アプリケーションの中 で最も消費電力の大きい機能の 1 つです。 10 ページの「DDR メモリ・コントローラの性能」で述べたように、よりスマートな メモリ・コントローラも消費電力の削減につながります。スマートなメモリ・コント ローラはデータ転送の効率が高いため、メモリ帯域幅を犠牲にすることなく、動作ク ロック周波数を下げることが可能です。たとえば、図 5 に示すように、400 MHz DDR3 とスマートなメモリ・コントローラを組み合わせることにより、533 MHz DDR3 と通 常のメモリ・コントローラの組み合わせと同等以上の性能を達成することが可能で す。この効率向上とクロック・レート低減は、数ミリワットというシステム消費電力 バジェットの大きな節約につながります。