LTC4225-1/LTC4225-2

1

422512f標準的応用例

特長

n 冗長電源用の電力経路と突入電流の制御 n パワー・ショットキー・ダイオードに代わる低損失 デバイス n 電源の入ったバックプレーンに対して安全にホット スワップ可能 n 動作電圧範囲: 2.9V∼18V n NチャネルMOSFETを制御 n 1μs以内でピーク・フォールト電流を制限 n ターンオンおよび逆ターンオフ時間: 0.5μs n 回路ブレーカで調整可能な電流制限 n 発振のないスムーズな切り替え n 電流制限フォールトの遅延を調整可能 n フォールトおよびパワー状態出力 n LTC4225-1:フォールト後にラッチオフ n LTC4225-2:フォールト後に自動リトライ n 24ピン4mm×5mm QFNおよびSSOPパッケージアプリケーション

n 冗長電源 n 電源ホールドアップ n MicroTCAシステムおよびサーバー n テレコム・ネットワーク n 電源プライオリタイザデュアル理想ダイオードおよび

Hot Swap

コントローラ

概要

LTC®4225は、直列に接続された外付けNチャネルMOSFET を制御することにより、2つの電源レール用に理想ダイオー ドとHot Swap™の機能を提供します。2個の高電力ショット キー・ダイオードと関連のヒートシンクの代わりに、理想ダイ オードとして機能するMOSFETを使用することにより、消費電 力とボードスペースを節減します。Hot Swap制御MOSFETに より、突入電流を制限するので、電源の入ったバックプレーン に対しボードを安全に挿入/引抜き可能です。また、素早く機 能する電流制限と内蔵の時限回路ブレーカにより、電源出力 を短絡フォールトから保護します。 LTC4225はバック・トゥ・バックMOSFETの順方向電圧降下 を制御し、一方の電源から他方の電源へ発振のないスムーズ な電流の移行を可能にします。理想ダイオードは素早くオン するので、電源切り替え時の負荷電圧の垂下を小さくします。 入力電源が故障または短絡した場合、高速ターンオフによっ て逆電流過渡を最小限に抑えます。 LTC4225は個別のオン/オフ制御が可能で、電源のフォールト とパワーグッドの状態を知らせます。LTC4225-1はラッチオフ 回路ブレーカを搭載しており、LTC4225-2はフォールト後に自 動リトライを行ないます。 L、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標 です。Hot Swapはリニアテクノロジー社の商標です。他の全ての商標はそれぞれの所有者に 所有権があります。 µTCAアプリケーション CPO1 ON1 137k 12V 12V ON2 INTVCC GND 0.1µF 0.1µF 0.1µF 47nF 47nF 12V 7.6A PLUG-IN CARD 1 PLUG-IN CARD 2 BACKPLANE 422512 TA01aIN1 SENSE1 DGATE1 Si7336ADP LTC4225 0.004Ω Si7336ADP Si7336ADP 0.004Ω Si7336ADP HGATE1 OUT1

CPO2 IN2 SENSE2 DGATE2 HGATE2 OUT2 FAULT1 PWRGD1 EN1 TMR1 TMR2 EN2 PWRGD2 FAULT2 20k 20k 137k 12V 7.6A 電力損失と負荷電流

LOAD CURRENT (A) 0 0 POWER DISSIP ATION (W) 0.5 1.0 1.5 2.0 2.5 3.0 2 4 6 8 422512 TA01 DIODE (SBG1025L) MOSFET (Si7336ADP) POWER SAVED

LTC4225-1/LTC4225-2

2

422512f絶対最大定格

電源電圧 IN1、IN2 ...–0.3V~24V INTVCC ...–0.3V~7V 入力電圧 ON1、ON2、EN1、EN2 ...–0.3V~24V TMR1、TMR2 ... –0.3V~(INTVCC+0.3V) SENSE1、SENSE2 ...–0.3V~24V 出力電圧 FAULT1、FAULT2、PWRGD1、PWRGD2 ...–0.3V~24V CPO1、CPO2 (Note 3) ...–0.3V~35V DGATE1、DGATE2 (Note 3) ...–0.3V~35V HGATE1、HGATE2 (Note 4) ...–0.3V~35V OUT1、OUT2 ...–0.3V~24V (Notes 1、2) 8 9 TOP VIEW 25 UFD PACKAGE 24-LEAD (4mm × 5mm) PLASTIC QFN 10 11 12 24 23 22 21 20 6 5 4 3 2 1 SENSE1 IN1 INTVCC GND ON2 IN2 SENSE2 FAULT1 ON1 EN1 TMR1 TMR2 EN2 FAULT2 DGA TE1 CPO1 HGA TE1 OUT1 PWRGD1 DGA TE2 CPO2 HGA TE2 OUT2 PWRGD2 7 14 15 16 17 18 19 13 TJMAX = 125°C, θJA = 34°C/WEXPOSED PAD (PIN 25) PCB GND CONNECTION OPTIONAL

1 2 3 4 5 6 7 8 9 10 11 12 TOP VIEW GN PACKAGE 24-LEAD PLASTIC SSOP NARROW

24 23 22 21 20 19 18 17 16 15 14 13 CPO1 DGATE1 SENSE1 IN1 ON1 INTVCC GND ON2 IN2 SENSE2 DGATE2 CPO2 HGATE1 OUT1 PWRGD1 FAULT1 EN1 TMR1 TMR2 EN2 FAULT2 PWRGD2 OUT2 HGATE2 TJMAX = 125°C, θJA = 85°C/W

ピン配置

平均電流 FAULT1、FAULT2、PWRGD1、PWRGD2 ...5mA INTVCC...1mA 動作温度範囲 LTC4225C ... 0°C~70°C LTC4225I ... –40°C~85°C 保存温度範囲... –65°C~150°C リード温度(半田付け、10秒) GNパッケージ ...300°CLTC4225-1/LTC4225-2

3

422512f

発注情報

鉛フリー仕様 テープアンドリール 製品マーキング* パッケージ 温度範囲

LTC4225CUFD-1#PBF LTC4225CUFD-1#TRPBF 42251 24-Lead (4mm × 5mm) Plastic QFN 0°C to 70°C

LTC4225CUFD-2#PBF LTC4225CUFD-2#TRPBF 42252 24-Lead (4mm × 5mm) Plastic QFN 0°C to 70°C

LTC4225IUFD-1#PBF LTC4225IUFD-1#TRPBF 42251 24-Lead (4mm × 5mm) Plastic QFN -40°C to 85°C

LTC4225IUFD-2#PBF LTC4225IUFD-2#TRPBF 42252 24-Lead (4mm × 5mm) Plastic QFN -40°C to 85°C

LTC4225CGN-1#PBF LTC4225CGN-1#TRPBF LTC4225GN-1 24-Lead Plastic SSOP 0°C to 70°C

LTC4225CGN-2#PBF LTC4225CGN-2#TRPBF LTC4225GN-2 24-Lead Plastic SSOP 0°C to 70°C

LTC4225IGN-1#PBF LTC4225IGN-1#TRPBF LTC4225GN-1 24-Lead Plastic SSOP -40°C to 85°C

LTC4225IGN-2#PBF LTC4225IGN-2#TRPBF LTC4225GN-2 24-Lead Plastic SSOP -40°C to 85°C

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。*温度等級は出荷時のコンテナのラベルで識別されます。 鉛ベースの非標準仕様の製品の詳細については、弊社へお問い合わせください。 鉛フリー製品のマーキングの詳細については、http://www.linear-tech.co.jp/leadfree/ をご覧ください。 テープアンドリールの仕様の詳細については、http://www.linear-tech.co.jp/tapeandreel/ をご覧ください。

電気的特性

lは全動作温度範囲の規格値を意味する。それ以外はTA=25 Cでの値。注記がない限り、VIN = 12V。SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS 電源

VIN Input Supply Range l 2.9 18 V

IIN Input Supply Current l 2.8 5 mA

VIN(UVL) Input Supply Undervoltage Lockout IN Rising l 1.75 1.9 2.05 V

∆VIN(HYST) Input Supply Undervoltage Lockout

Hysteresis

l 10 50 90 mV

VINTVCC Internal Regulator Voltage l 4.5 5 5.6 V

VINTVCC(UVL) Internal VCC Undervoltage Lockout INTVCC Rising l 2.1 2.2 2.3 V

∆VINTVCC(HYST) Internal VCC Undervoltage Lockout Hysteresis l 30 60 90 mV

理想ダイオード制御

∆VFWD(REG) Forward Regulation Voltage

(VINn – VOUTn)

l 10 25 40 mV

∆VDGATE External N-Channel Gate Drive

(VDGATEn – VINn) IN < 7V, ∆VFWD = 0.1V, I = 0, –1µA IN = 7V to 18V, ∆VFWD = 0.1V, I = 0, –1µA l l 5 10 127 14 14 V V

ICPO(UP) CPOn Pull-Up Current CPO = IN = 2.9V

CPO = IN = 18V

l l

-60

-50 -95 -85 -120 -110 µAµA

IDGATE(FPU) DGATEn Fast Pull-Up Current ∆VFWD = 0.2V, ∆VDGATE = 0V, CPO = 17V –1.5 A

IDGATE(FPD) DGATEn Fast Pull-Down Current ∆VFWD = –0.2V, ∆VDGATE = 5V 1.5 A

tON(DGATE) DGATEn Turn-On Delay ∆VFWD = 0.2V, CDGATE = 10nF l 0.25 0.5 µs

tOFF(DGATE) DGATEn Turn-Off Delay ∆VFWD = –0.2V, CDGATE = 10nF l 0.2 0.5 µs

Hot Swap制御

∆VSENSE(CB) Circuit Breaker Trip Sense Voltage

(VINn – VSENSEn)

l 47.5 50 52.5 mV

∆VSENSE(ACL) Active Current Limit Sense Voltage

(VINn – VSENSEn)

l 55 65 75 mV

∆VHGATE External N-Channel Gate Drive

(VHGATEn – VOUTn) IN < 7V, I = 0, –1µA IN = 7V to 18V, I = 0, –1µA l l 4.8 10 127 14 14 V V

LTC4225-1/LTC4225-2

4

422512f

電気的特性

lは全動作温度範囲での規格値を意味する。それ以外はTA = 25 Cでの値。注記がない限り、VIN = 12V。

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

IHGATE(UP) External N-Channel Gate Pull-Up Current Gate Drive On, HGATE = 0V l -7 -10 -13 µA

IHGATE(DN) External N-Channel Gate Pull-Down Current Gate Drive Off, OUT = 12V,

HGATE = OUT + 5V

l 150 300 500 µA

IHGATE(FPD) External N-Channel Gate Fast

Pull-Down Current Fast Turn-Off, OUT = 12V, HGATE = OUT + 5V

l 100 200 300 mA

tPHL(SENSE) Sense Voltage (INn – SENSEn)

High to HGATEn Low ∆VSENSE = 300mV, CHGATE = 10nF

l 0.5 1 µs

tOFF(HGATE) ENn High to HGATEn Low

ONn Low to HGATEn Low INn Low to HGATEn Low

l l l 20 10 10 40 20 20 µs µs µs

tD(HGATE) ONn High, ENn Low to HGATEn

Turn-On Delay

l 50 100 150 ms

tP(HGATE) ONn to HGATEn Propagation Delay ON = Step 0.8V to 2V l 10 20 µs

入力/出力ピン

ISENSE SENSEn Input Current SENSE = 12V l 10 50 100 µA

VON(TH) ONn Threshold Voltage ON Rising l 1.21 1.235 1.26 V

∆VON(HYST) ONn Hysteresis l 40 80 140 mV

VON(RESET) ONn Fault Reset Threshold Voltage ON Falling l 0.55 0.6 0.63 V

ION(LEAK) ONn Input Leakage Current ON = 5V l 0 ±1 µA

VEN(TH) ENn Threshold Voltage EN Rising l 1.185 1.235 1.284 V

∆VEN(HYST) ENn Hysteresis l 40 130 200 mV

IEN(UP) ENn Pull-Up Current EN = 1V l -7 -10 -13 µA

VTMR(TH) TMRn Threshold Voltage TMR Rising

TMR Falling

l l

1.198

0.15 1.235 0.2 1.272 0.25 V V

ITMR(UP) TMRn Pull-Up Current TMR = 1V, In Fault Mode l -75 -100 -125 µA

ITMR(DN) TMRn Pull-Down Current TMR = 2V, No Faults l 1.4 2 2.6 µA

ITMR(RATIO) TMRn Current Ratio ITMR(DN)/ITMR(UP) l 1.4 2 2.7 %

IOUT OUTn Current OUT = 11V, IN = 12V, ON = 2V

OUT = 13V, IN = 12V, ON = 2V

l l

50

2.2 120 4 mAµA

VOL Output Low Voltage (FAULTn, PWRGDn) I = 1mA l 0.15 0.4 V

VOH Output High Voltage (FAULTn, PWRGDn) I = –1µA l INTVCC – 1 INTVCC – 0.5 V

IOH Input Leakage Current (FAULTn, PWRGDn) V = 18V l 0 ±1 µA

IPU Output Pull-Up Current

(FAULTn, PWRGDn) V = 1.5V

l -7 -10 -13 µA

tRST(ON) ONn Low to FAULTn High l 20 40 µs

Note 1:絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可 能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響 を与える可能性がある。 Note 2:デバイスのピンに流れ込む電流は全て正。デバイスのピンから流れ出す電流は全て負。 注記がない限り、全ての電圧はGNDを基準にしている。 Note 3:内部クランプにより、DGATEピンとCPOピンは、INを基準に最小10V高い電圧およびダ イオード1個だけ低い電圧に制限される。これらのピンをクランプより高い電圧にドライブす るとデバイスを損傷するおそれがある。 Note 4:内部クランプにより、HGATEピンは、OUTを基準に最小10V高い電圧およびダイオード 1個だけ低い電圧に制限される。このピンをクランプ電圧より高い電圧にドライブするとデバ イスを損傷するおそれがある。

LTC4225-1/LTC4225-2

5

422512f

標準的性能特性

ダイオードのゲート電圧と電流 Hot Swapゲート電圧と電流 OUTの電流と電圧

回路ブレーカの トリップ電圧と温度 アクティブ電流制限の 検出電圧と温度 アクティブ電流制限 遅延と検出電圧 IN電源の電流と電圧 INTVCCのロード・レギュレーション CPOの電圧と電流 (注記がない限り、TA = 25 C, VIN = 12V。 VIN (V) 0 0 IIN (mA) 1 2 3 4 3 6 9 12 422512 G01 15 18 ILOAD (mA) 0 0 INTV CC (V) 1 2 3 4 5 6 –2 –4 –6 –8 422512 G02 –10 VIN = 12V VIN = 3.3V ICPO (µA) 0 12 10 8 6 4 2 0 –2 –60 –100 422512 G03 –20 –40 –80 –120 VCPO – V IN (∆ VCPO ) (V) V IN = 18V VIN = 2.9V IDGATE (µA) 0 12 10 8 6 4 2 0 –2 –60 –100 422512 G04 –20 –40 –80 –120 VDGA TE – V IN (∆ VDGA TE ) (V) VIN = 18V VIN = 2.9V VOUT = VIN – 0.1V IHGATE (µA) 0 14 12 10 8 6 4 2 0 –6 –10 422712 G05 –2 –4 –8 –12 GA TE DRIVE (∆ VHGA TE ) (V) VIN = 12V VOUT = VIN VIN = 2.9V TEMPERATURE (°C) –50 48

CIRCUIT BREAKER TRIP VOLTAGE (mV)

49 50 51 52 –25 0 25 50 422512 G07 75 100 TEMPERATURE (°C) –50 63

ACTIVE CURRENT LIMIT SENSE VOLTAGE (mV)

64 65 66 67 –25 0 25 50 422512 G08 75 100

SENSE VOLTAGE (VIN – VSENSE) (mV)

50 0.1

ACTIVE CURRENT LIMIT DELA

Y (µs) 10 100 100 150 200 250 300 422512 G09 1 CHGATE = 10nF VOUT (V) 0 –0.5 IOUT (mA) 0 0.5 1.0 1.5 2.5 3 6 9 12 422512 G06 15 18 2.0 VIN = 12V

LTC4225-1/LTC4225-2

6

422512f HGATEのプルアップ電流と温度 TMRのプルアップ電流と温度 PWRGD出力 L 電圧と電流、FAULT の標準的性能特性

注記がない限り、TA = 25 C、VIN = 12V。ピン機能

CPO1、CPO2:チャージポンプの出力。CPO1またはCPO2から 対応するIN1ピンまたはIN2ピンにコンデンサを接続します。 このコンデンサの値は、理想ダイオード制御の外部MOSFET のゲート容量(CISS)の約10倍です。このコンデンサに蓄えら れる電荷は、高速ターンオン時にゲートをプルアップするのに 使われます。高速ターンオンが不要であれば、このピンをオー プンのままにしておきます。 DGATE1、DGATE2:理想ダイオードMOSFETのゲート・ドラ イブ出力。このピンは理想ダイオード制御の外部Nチャネル MOSFETのゲートに接続します。内部クランプにより、ゲート 電圧はINを基準に12V上およびダイオード電圧だけ下に制 限されます。高速ターンオン時、1.5AのプルアップがCPOか らDGATEを充電します。高速ターンオフ時、1.5Aのプルダウ ンがDGATEをINに放電します。EN1、EN2:イネーブル入力。このピンを接地してHot Swap 制御をイネーブルします。このピンが H のとき、MOSFET はオンすることができません。10μAの電流源がこのピンを INTVCCよりダイオード1個だけ下までプルアップします。ON が H のときENが L になると、内部タイマによりデバウンス のための100msのスタートアップ遅延が生じ、その後フォール トがクリアされます。 露出パッド (UFDパッケージ): 露出パッドはオープンのまま にするか、デバイスのグランドに接続することができます。 FAULT1、FAULT2:フォールト状態出力。10μAの電流源によっ て通常は H に(INTVCCよりダイオード1個だけ下に)引き上 げられているオープン・ドレイン出力。外部プルアップを使っ てINTVCCより上に引き上げることができます。これは、過電 流フォールト・タイムアウト後に回路ブレーカがトリップすると L になります。使用しない場合、オープンのままにします。 GND: デバイスのグランド。

HGATE1、HGATE2: Hot Swap MOSFETゲート・ドライブ出力。

このピンはHot Swap制御の外部NチャネルMOSFETのゲー トに接続します。10μAの内部電流源がMOSFETのゲートを 充電します。内部クランプにより、ゲート電圧はOUTを基準に 12V上およびダイオード1個だけ下に制限されます。ターンオ フ時、300μAのプルダウンがHGATEをグランドに放電します。 出力の短絡またはINTVCCの低電圧ロックアウトの間、高速 200mAプルダウンがHGATEをOUTに放電します。

IN1、IN2: 正電源入力およびMOSFETゲート・ドライブのリ

ターン。5V INTVCC電源は、内部ダイオードORを介して、IN1 およびIN2から生成されます。このピンで検出される電圧を 使って、順方向電圧のレギュレーションおよび逆方向ターン オフのためにDGATEを制御します。また、電流検出抵抗の正 電圧側を検出します。DGATEが放電するとき、ゲートの高速 プルダウン電流はこのピンを通ってリターンします。 TEMPERATURE (°C) –50 –9.0

HGATE PULL-UP CURRENT (µA)

–9.5 –10.0 –10.5 –11.0 –25 0 25 50 422512 G10 75 100 TEMPERATURE (°C) –50 –97

TMR PULL-UP CURRENT (µA) –98

–99 –100 –101 –103 –25 0 25 50 422512 G11 75 100 –102 CURRENT (mA) 0

OUTPUT LOW VOL

TAGE (V) 0.4 0.6 4 422512 G12 0.2 0 1 2 3 5 0.8

LTC4225-1/LTC4225-2

7

422512fピン機能

INTVCC:内部5V電源のデカップリング出力。このピンには 0.1μF以上のコンデンサが必要です。500μA未満の外部負荷 をこのピンに接続することができます。 ON1、ON2: オン制御入力。1.235Vより高い立ち上がりエッジが外部Hot Swap MOSFETをオンし、1.155Vより低い立ち下 がりエッジがそれをオフします。このピンをINからの外部抵抗 分割器に接続して、電源の低電圧状態をモニタします。ONピ ンを0.6Vより下にすると、電子回路ブレーカをリセットします。

OUT1、OUT2: 出力電圧検出およびMOSFETゲート・ドライブ

のリターン。このピンは外部MOSFETの出力側に接続します。 このピンで検出される電圧はDGATEを制御するのに使われ ます。HGATEが放電するとき、ゲートの高速プルダウン電流 はこのピンを通ってリターンします。 PWRGD1、PWRGD2:電源状態出力。10μAの電流源によって 通常は H に(INTVCCよりダイオード1個だけ下に)引き上げ られているオープン・ドレイン出力。外部プルアップを使って INTVCCより上に引き上げることができます。これは、HGATE とOUTの間のMOSFETゲート・ドライブが4.2Vのゲート-ソー ス電圧を超えると L になります。使用しない場合、オープン のままにします。 SENSE1、SENSE2: 電流検出の負入力。このピンを電流検出 抵抗の出力に接続します。電流制限回路がHGATEピンを制 御して、INとSENSEの間の電圧を65mVに制限します。TMR ピンで設定されるフォールト・フィルタ遅延より長い間、検出 電圧が50mVを超えると、回路ブレーカがトリップします。 TMR1、TMR2: タイマ・コンデンサの端子。このピンとグランド

の間にコンデンサを接続して、外部Hot Swap MOSFETがオ フする前の電流制限の12ms/μFの持続時間を設定します。 オフ時間の長さは617ms/μFなので、2%のデューティ・サイク ルになります。

LTC4225-1/LTC4225-2

8

422512fブロック図

+ – + – A1 + – GA1 HGATE1 CPO1 DGATE1 OUT1 ON1 HGATE2 CPO2 DGATE2 OUT2 65mV 50mV 50mV 65mV IN1 SENSE1 ECB1 SENSE2 IN2 10µA + – + – 25mV HGATE1 ON 1.235V 0.6V 1.235V 0.6V 10µA INTVCC 10µA INTVCC CP1 25mV 2.2V + – 100µA INTVCC 12V INTVCC 10µA 100µA + –A2 + – INTVCC INTVCC UV3 + – + – + – CHARGE PUMP 1 GATEDRIVER 1 DRIVER 2GATE

CHARGE PUMP 2 5V LDO GA2 + – 100µA INTVCC 2µA 10µA

INTVCC INTVCC INTVCC

+ – IN1 1.9V IN2 1.9V UV1 UV2 + – + – FAULT1 RESET CP2 CP5 + – 1.235V 0.2V CP7 + – CP8 100µA 2µA EXPOSED PAD* 1.235V 0.2V CP9 CP10 + – 1.235V

CARD1 PRESENCE DETECT

HGATE2 ON

FAULT2 RESET

LOGIC

CARD2 PRESENCE DETECT +

–

TMR1

GND

*UFD PACKAGE ONLY FAULT1 EN1

10µA 10µA 10µA

INTVCC PWRGD1 ON2 CP6 CP3 CP4 TMR2 422512 BD FAULT2 PWRGD2 EN2 INTVCC + – + – + – + – 1.235V + – + – ECB2 12V 12V 12V

LTC4225-1/LTC4225-2

9

422512f動作

LTC4225は理想ダイオードとして機能し、電力経路の外部 バック・トゥ・バックNチャネルMOSFET(MDとMH)を制御す ることによって電流制限と過電流保護を行います。これによ り、µTCAのような、冗長電源から給電されるバックプレーン を備えたシステムで、ボードを安全に挿抜することができます。 LTC4225は2個の独立した理想ダイオードとHot Swapコント ローラを備えており、2個の入力電源をそれぞれ独立に制御 します。 LTC4225が最初にパワーアップするとき、バック・トゥ・バック MOSFETのゲートは L に保持され、それらをオフ状態に保ち ます。ゲート・ドライブ・アンプ(GA1、GA2)が、INピンとOUT ピンの間の電圧をモニタし、DGATEピンをドライブします。 アンプは、大きな順方向電圧降下を検出すると、DGATEピン を直ちにプルアップし、理想ダイオード制御のMOSFETをオ ンします。CPOピンとINピンの間に接続された外部コンデン サに蓄えられた電荷が、理想ダイオードMOSFETを短時間 でオンするのに必要な電荷を与えます。デバイスのパワーアッ プ時に、内部チャージポンプがこのコンデンサを充電します。 DGATEピンがCPOピンから電流をソースし、INピンおよび GNDピンに電流をシンクします。 ONピンを H に引き上げ、ENピンを L に引き下げると、 100msのデバウンス・タイミング・サイクルが開始されます。こ のタイミング・サイクル経過後、チャージポンプからの10μA の電流源がHGATEピンをランプアップさせます。Hot Swap MOSFETがオンすると、INピンとSENSEピンの間に接続さ れた外部センス抵抗(RS)によって設定されるレベルに突入電 流が制限されます。アクティブ電流制限アンプ(A1、A2)は、 電流検出抵抗の両端で65mVになるようにMOSFETのゲー トをサーボ制御します。望むなら、HGATEからGNDにコン デンサを追加して、突入電流をさらに下げることができます。 MOSFETのゲートのオーバードライブ(HGATEからOUTの 電圧)が4.2Vを超えると、PWRGDピンが L になります。 両方のMOSFETがオンすると、ゲート・ドライブ・アンプ がDGATEを制御して、センス抵抗とバック・トゥ・バック MOSFET両端の順方向電圧降下(VIN – VOUT)を25mVに サーボ制御します。負荷電流により電圧降下が25mVより大 きくなると、ゲート電圧が上昇して、理想ダイオード制御に使 われるMOSFETをエンハンスします。大きな出力電流では、 MOSFETは完全にオン状態にドライブされており、MOSFET 両端の電圧降下は直列に接続された2個のMOSFETの ILOAD • RDS(ON)の和に等しくなります。 MOSFETが導通しているとき入力電源が短絡すると、大きな 逆電流が負荷から入力に向けて流れ始めます。ゲート・ドラ イブ・アンプはこの故障状態が現れると直ちにそれを検出し、 DGATEピンをプルダウンして、理想ダイオードMOSFETをオ フします。 電源の出力に過電流フォールトが生じる場合、電流は65mV/ RSに制限されます。TMRピンのコンデンサを充電する100μA によって設定されるフォールト・フィルタの遅延後、回路ブレー カがトリップし、HGATEピンを L にし、Hot Swap MOSFET をオフします。フォールトの生じた電源だけが影響を受け、 対応するFAULTピンが L にラッチします。この時点で、 DGATEピンは H のままで、理想ダイオードをオン状態に保 ちます。 内部クランプが、DGATEからINの電圧およびCPOからIN の電圧の両方を12Vに制限します。また、同じクランプがCPO ピンとDGATEピンを、INピンよりダイオード電圧だけ下に 制限します。別の内部クランプがHGATEからOUTの電圧を 12Vに制限し、さらに、HGATEピンをOUTピンよりダイオー ド電圧だけ下にクランプします。 LTC4225への電力は、低損失レギュレータ(LDO)への内部ダ イオードOR回路を介して、INピンまたはOUTピンのどちらか らか供給されます。このLDOはINTVCCに5Vの電源を生成し、 LTC4225の内部低電圧回路に給電します。LTC4225-1/LTC4225-2

10

422512fアプリケーション情報

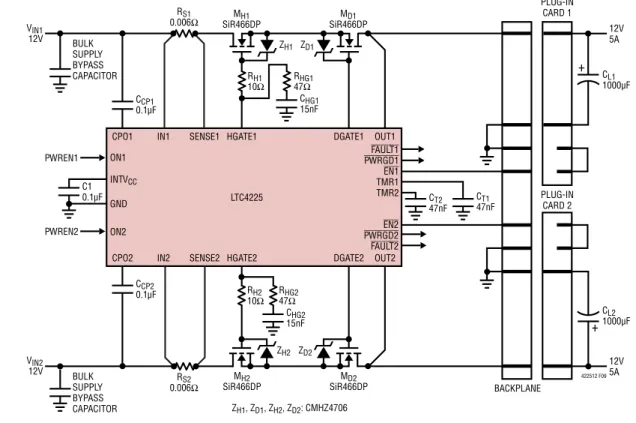

高い可用性を要するシステムでは、冗長性をもたせてシステ ムの信頼性を高めるため、多くの場合、並列に接続された電 源やバッテリ・フィードが採用されます。電源のOR接続用ダイ オードは、これらの電源を負荷ポイントで接続するのに一般に 使われますが、ダイオードのかなりの順方向電圧降下による 電力損失の代価を払います。LTC4225は、パス素子に外部N チャネルMOSFETを使ってこの電力損失を最小にするので、 MOSFETがオンしているときの電源から負荷への電圧降下を 低くすることができます。入力ソースの電圧が出力共通電源 電圧よりも下になると、対応するMOSFETがオフするので、理 想ダイオードの機能と性能に一致します。電流センス抵抗を 追加し、ゲート制御を別にした2個のMOSFETをバック・トゥ・ バックに構成することにより、LTC4225は突入電流制御と過 電流保護によって理想ダイオードの性能を強化します(図1を 参照)。これにより、コネクタを損傷することなく、電源の入っ ているバックプレーンに対してボードを安全に挿抜することが できます。 内部VCC電源 LTC4225はINピンに与えられる2.9V∼18Vの入力電源で 動作することができます。デバイスへの電源は、INTVCCピン を出力にする低損失レギュレータ(LDO)によって内部で5V に安定化されます。内部ダイオードOR回路はINピンとOUT ピンの高い方の電源を選択して、LDOを介してデバイスに給 電します。ダイオードOR方式により、IN電源が急落またはオ フしたとき、OUTの負荷容量によってデバイスの電源は短時 間動作状態に保つことができます。 低電圧ロックアウト回路は、INTVCC電圧が2.2Vを超えるま で、全てのMOSFETがオンするのを防ぎます。0.1μFのバイパ ス・コンデンサをできるだけINTVCCピンとGNDピンに近づ けて配置することを推奨します。LDOの動作に影響を与えな いように、INTVCCピンには外部電源を接続しません。500μA 未満の小さな外部負荷をINTVCCピンに接続することができ ます。 ターンオン・シーケンス OUTピンのボード電源は2個のバック・トゥ・バックNチャネ ルMOSFET(MD、MH)で制御されます。電源側のMOSFET MDは理想ダイオードとして機能し、負荷側のMHは出力負荷 に供給される電力を制御するHot Swapとして機能します。セ ンス抵抗(RS)は過電流検出のために負荷電流をモニタしま す。HGATEのコンデンサ(CHG)はゲートのスルーレートを制 御して突入電流を制限します。CHGを伴った抵抗RHGは電流 制御ループを補償し、RHはHot Swap MOSFETの高周波数 の発振を防ぎます。 CPO1 ON1 R2 137k R4 137k VIN1 12V VIN2 12V ON2 INTVCC GND C1 0.1µF CF1 10nF CF2 10nF CCP1 0.1µF CCP2 0.1µF CT2 47nF CHG1 15nF BULK SUPPLY BYPASS CAPACITOR BULK SUPPLY BYPASS CAPACITOR CT1 47nF 12V 7.6A PLUG-IN CARD 1 PLUG-IN CARD 2 BACKPLANE 422512 F01IN1 SENSE1 DGATE1 MD1 Si7336ADP Si7336ADPMH1 LTC4225 RS1 0.004Ω MD2 Si7336ADP Si7336ADPMH2 RS2 0.004Ω HGATE1 OUT1

CPO2 IN2 SENSE2 DGATE2 HGATE2 OUT2 FAULT1 PWRGD1 EN1 TMR1 TMR2 EN2 PWRGD2 FAULT2 RH1 10Ω R47ΩHG1 CHG2 15nF RH2 10Ω R47ΩHG2 R5 100k R6100k VIN1 VIN2 R7 100k R8100k R1 20k R3 20k 12V 7.6A CL1 1600µF + CL2 1600µF + 図1.2つのμTCAスロットに12Vの電力を供給するμTCAアプリケーション

LTC4225-1/LTC4225-2

11

422512fアプリケーション情報

通常の起動時に、理想ダイオードMOSFETが最初にオンし ます。内部で生成される電源(INTVCC)がその2.2Vの低電圧 ロックアウト・スレッショルドを超えると、直ちに内部チャージ ポンプがCPOピンを充電することができます。起動時にはHot Swap MOSFETはオフしているので、OUTは低いままです。そ の結果、理想ダイオードのドライブ・アンプはINピンとOUTピ ンの間の大きな準方向電圧降下を検出し、DGATEをCPOピ ンの電圧までプルアップします。Hot Swap MOSFETをオンすることができる前に、100msの デバウンス・サイクルの間ENが L に留まり、ONが H に留 まって、挿入時のどんな接触バウンスも止んでいるようにする 必要があります。デバウンス・サイクルの終わりに、内部フォー ルト・ラッチがクリアされます。次いで、Hot Swap MOSFETは、 チャージポンプからの10μA電流源によってHGATEを充電 することにより、オンすることができます。HGATEピンの電圧 は10µA/CHGに等しい勾配で上昇し、電源から負荷コンデン サ(CL)に流れ込む突入電流は次の値に制限されます。 IINRUSH= CL CHG• 10µA

Hot Swap MOSFETがオンするとき、OUT電圧はHGATEの 電圧に追従します。電流検出抵抗(RS)両端の電圧が高くな りすぎると、内部電流制限回路によって突入電流が制限され ます。MOSFETのゲートのオーバードライブが4.2Vを超える と、対応するPWRGDピンが L になって、パワーグッド状態 であることを表示します。OUTが入力電源電圧に達すると、 HGATEは引き続きランプアップを続けます。内部12Vクラン プがHGATEの電圧をOUTより上に制限します。 両方のMOSFETがオンすると、ゲート・ドライブ・アンプが理 想ダイオードMOSFETのゲートを制御して、RS、MDおよび MHの両端のその順方向電圧降下を25mVにサーボ制御し ます。負荷電流によって25mVを超える電圧降下が生じてい るとすれば、MOSFETは完全にオン状態にドライブされてお り、MOSFET両端の電圧降下はILOAD • RDS(ON)に等しくな ります。

ターンオフ・シーケンス

GATEは様々な条件でオフされます。Hot Swap MOSFETの 通常のターンオフは、ONピンをその1.155Vのスレッショルド (ONピンのヒステリシスは80mV)より下にするか、またはEN

ピンをその1.235Vのスレッショルドより上にすることにより開 始されます。さらに、回路ブレーカをトリップするほど長く過電 流フォールトが持続すると、Hot Swap MOSFETもオフします。 通常は、LTC4225は、300μAの電流シンクでHGATEピンを グランドに引き下げてMOSFETをオフします。 INTVCCがその低電圧ロックアウト・スレッショルド(2.2V)よ り下になると、全てのMOSFETがオフします。DGATEピンは 100μAの電流でINピンよりダイオード1個分下までプルダウン され、HGATEピンは200mAの電流によってOUTピンにプル ダウンされます。 ゲート・ドライブ・アンプは理想ダイオードMOSFETを制御し て、入力電源がOUTより下になると逆電流を防ぎます。入力 電源が急落すると、ゲート・ドライブ・アンプは、INがOUTよ り20mV低くなったたことを検出するや否や、高速プルダウ ン回路によって理想ダイオードMOSFETをオフします。入力 電源がもっと緩やかに低下すると、ゲート・ドライブ・アンプは MOSFETを制御して、OUTをINより25mV下に維持します。 図2.理想ダイオード・コントローラの起動波形 図3.Hot Swapコントローラの起動シーケンス IN 10V/DIV CPO 10V/DIV DGATE 10V/DIV OUT 10V/DIV 20ms/DIV 422512 F02 ON 5V/DIV HGATE 10V/DIV OUT 10V/DIV PWRGD 10V/DIV 50ms/DIV 422512 F03

LTC4225-1/LTC4225-2

12

422512f ENによるボードの検出 ENピンが L になったときONが H であって、ボードが接続 されていることを示すと、LTC4225は接触デバウンスのため に100msのタイミング・サイクルを開始します。ボードを挿入す るとき、ENピンにバウンスがあるとタイミング・サイクルが再ス タートします。100msのタイミング・サイクルの終わりに、内部 フォールト・ラッチがクリアされます。タイミング・サイクルの終 わりにENピンが L のままだと、HGATEが10μAの電流源 で充電され、Hot Swap MOSFETをオンします。ENピンが H になってボードが取り外されたことを示すと、 20μsの遅延の後、HGATEピンが300μAの電流シンクでプル ダウンされ、Hot Swap MOSFETをオフします。ラッチされた フォールトはクリアされません。 過電流フォールト LTC4225は回路ブレーカ機能付きの調整可能な電流制限を 備えており、短絡や過度の負荷電流に対して外部MOSFET を保護します。外部センス抵抗(RS1、RS2)の電圧が、電子回 路ブレーカ(ECB)とアクティブ電流制限(ACL)アンプによっ てモニタされます。TMRピンで設定されるフォールト・フィル タ遅延より長い時間センス抵抗両端の電圧が∆VSENSE(CB) (50mV)を超えると、電子回路ブレーカがHGATEからOUT への200mAの電流によってHot Swap MOSFETをオフします。 ECBスレッショルド∆VSENSE(CB)の1.3倍であるACLスレッ ショルド∆VSENSE(ACL) (65mV)を検出電圧が超えると、アク ティブ電流制限が開始されます。Hot Swap MOSFETのゲー トはACLアンプによる制御の下に置かれ、出力電流が安定 化されてセンス抵抗両端のACLスレッショルドを維持しま す。この時点で、TMRピンのコンデンサを充電する100μA の電流により、フォールト・フィルタがタイムアウトを開始しま す。TMRピンの電圧がそのスレッショルド(1.235V)を超える と、HGATEが300μAによってグランドに引き下げられ、外部 MOSFETがオフし、それに関連したFAULTが L になります。 Hot Swap MOSFETがオフした後、TMRピンのスレッショル ドが0.2Vに達するまで、TMRピンのコンデンサが2μAのプル ダウン電流によって放電します。これに、TMRピンの14タイミ ング・サイクルに相当するクールオフ時間が続きます。ラッチオ フするデバイス(LTC4225-1)の場合、ONピンを L にするか、 またはENピンを H から L にトグルしてラッチされたフォー ルトをクリアするまで、HGATEピンの電圧はクールオフ時 間が終了しても再スタートしません。自動リトライのデバイス (LTC4225-2)の場合、クールオフ時間が終了するとラッチされ たフォールトが自動的にクリアされ、HGATEピンが充電を再 スタートし、MOSFETをオンします。12V出力の過電流フォー ルトを図4に示します。 12V出力に、図5に示されているような厳しい短絡フォールト が生じた場合、出力電流は数十アンペアに急増することがあ ります。LTC4225は1μs以内に応答し、HGATEからOUTの 電圧をゼロボルトに引き下げて、電流を制御下に置きます。 RHGとCHGのネットワークにより、Hot Swap MOSFETのゲー トはほとんど即座に回復し、電子回路ブレーカがタイムアウト するまで電流がアクティブに制限されます。電源ピンの寄生イ ンダクタンスにより、バイパス・コンデンサのない入力電源は 高電流サージの間急落し、次いで電流が遮断されると上方 向にスパイクを生じる可能性があります。入力コンデンサがな い場合の、2個の電源のための、Z1、RSNUB1、CSNUB1および Z2、RSNUB2、CSNUB2で構成される入力電源過渡変動サプ レッサを図11に示します。

アプリケーション情報

図4.12V出力の過電流フォールト 図5.12V出力の重度の短絡 OUT 10V/DIV HGATE 10V/DIV ILOAD 40A/DIV 100µs/DIV 422512 F04 OUT 10V/DIV HGATE 10V/DIV ILOAD 40A/DIV 2µs/DIV 422512 F05LTC4225-1/LTC4225-2

13

422512f アクティブ電流ループの安定性 HGATEピンのアクティブ電流ループは、外部Nチャネル MOSFETの寄生ゲート容量によって補償されます。これ以 外の補償部品は通常不要です。CISS ≤ 2nFのMOSFETを選 択した場合、HGATEピンに接続されたRHGとCHGの補償 ネットワークが必要とされる可能性があります。CHGの値は、 出力負荷容量に許容される突入電流に基づいて選択されま す。出力の短絡によるゲートの高速プルダウン後、CHGに直 列に接続された抵抗(RHG)が、アクティブ電流制限のための MOSFETゲートの復旧を加速します。最適性能を得るため、 CHGの値は100nF以下、RHGは10Ω∼100Ωにします。 TMRピンの機能 TMRピンからGNDに接続した外部コンデンサ(CT)は、電源 の出力がアクティブに電流制限されているとき、フォールト・ フィルタとして機能します。センス抵抗両端の電圧が回路ブ レーカのトリップ・スレッショルド(50mV)を超えると、TMRが 100μAでプルアップされます。それ以外は、2μAで引き下げら れます。1.235VのTMRスレッショルドを超えるとフォールト・ フィルタがタイムアウトし、対応するFAULTピンが L になり ます。フォールト・フィルタの遅延、つまり回路ブレーカの時間 遅延は次のとおりです。 tCB = CT • 12[ms/µF] 回路ブレーカのタイムアウト後、TMRピンのコンデンサは、 1.235VのTMRスレッショルドから0.2Vに達するまで2μAで プルダウンされます。次いで、TMRピンのコンデンサの100μA の電流による充電と、2μAの電流による0.2Vへの放電か らなる14クーリング・サイクルを完了します。そのポイントで、 「フォールトのリセット」のセクションで説明されているよう に、フォールトがクリアされていれば、HGATEピンの電圧はス タートアップすることができます。クールオフ時間の間にラッチ されたフォールトがクリアされると、対応するFAULTピンが H になります。過電流フォールト後のMOSFETの全クール オフ時間は次のようになります。 tCOOL = CT • 11[s/µF] クールオフ時間経過後、ラッチされたフォールトがクリアされ ないと、フォールトがクリアされるまでクーリング・サイクルが 継続します。 クールオフ時間経過後、ラッチオフ・デバイス(LTC42251)の場 合、フォールトがクリアされた場合だけHGATEピンをプルアッ プすることができます。自動リトライのデバイス(LTC4225-2) の場合、クールオフ時間が終了するとラッチされたフォールト が自動的にクリアされ、HGATEピンの電圧が再スタートでき ます。 フォールトのリセット(LTC4225-1) ラッチオフ・デバイス(LTC4225-1)の場合、回路ブレーカが トリップした後、過電流フォールトがラッチされ、対応する FAULTピンが L にアサートされます。LTC4225が2個の電 源のMOSFETを制御する場合、フォールトの生じた電源の Hot Swap MOSFETだけがオフし、他方は影響を受けません。 ラッチされたフォールトをリセットし、出力を再スタートするに は、対応するONピンを100μs以上0.6Vより下にしてから、 1.235Vより上にします。ONピンの立ち下がりエッジでフォー ルト・ラッチがリセットし、FAULTピンがデアサートします。ON が再度 H になると、HGATEピンの電圧が再スタートする前 に100msのデバウンス・サイクルが開始されます。ENピンを H にしてから再度 L にトグルしてもフォールトをリセットし ますが、FAULTピンは100msのデバウンス・サイクルの終わ りに H になり、その後、HGATEピンの電圧が上昇を開始し ます。全ての電源をINTVCC低電圧ロックアウト・スレッショ ルド(2.2V)より下にすると、全てのMOSFETがオフし、全ての フォールト・ラッチをリセットします。電源のどれかがINTVCC のUVLOスレッショルドより上に回復すると、通常のスタート アップの前に100msのデバウンス・サイクルが開始されます。 フォールト後の自動リトライ(LTC4225-2) 自動リトライのデバイス(LTC4225-2)の場合、「TMRピンの機 能」のセクションで説明されているように、クールオフ・タイミン グ・サイクルの後、ラッチされたフォールトが自動的にリセット されます。クールオフ時間が終了するとフォールト・ラッチがク リアされ、FAULTピンが H になります。HGATEピンの電圧 はスタートアップすることができ、Hot Swap MOSFETをオン します。出力短絡が持続すると電源は短絡状態にパワーアッ プし、回路ブレーカがタイムアウトしてFAULTが再度 L にな るまでアクティブ電流制限を行います。新しいクールオフ・サイ クルが始まり、2μAの電流でTMRがランプダウンします。出力 の短絡が解消するまで、このプロセス全体が繰り返されます。 tCBとtCOOLはTMRの容量(CT)の関数なので、自動リトライ のデューティ・サイクルは(CTには関係なく)0.1%です。 過電流フォールトの後の自動リトライのシーケンスを図6に示 します。アプリケーション情報

LTC4225-1/LTC4225-2

14

422512f 電源の低電圧のモニタ ONピンはターンオン制御および入力電源モニタとして機能し ます。それぞれのONピンの入力電源(IN1、IN2)とGNDの間 に接続された抵抗分割器が電源の低電圧状態をモニタしま す。低電圧スレッショルドは抵抗を適切に選択して設定され、 次のように与えられます。 VIN(UVTH)= 1+ RTOP RBOTTOM ⎛ ⎝⎜ ⎞ ⎠⎟• VON(TH) ここで、VON(TH)はONの立ち上がりスレッショルド(1.235V) です。 入力電源が20μsより長い時間その低電圧スレッショルドより 下になると低電圧フォールトが生じます。FAULTピンは L に なりません。ONピンの電圧が1.155Vを下回ったが0.6Vより 上に留まっている場合、HGATEからグランドへの300μAのプ ルダウンによってHot Swap MOSFETがオフします。入力電源 がその低電圧スレッショルドを超えると、Hot Swap MOSFET は、100msのデバウンス・サイクルなしに直ちに再度オンします。 ただし、ONピンの電圧が0.6Vより下になると、Hot Swap MOSFETをオフし、関連したフォールト・ラッチをクリアします。 入力電源がその低電圧スレッショルドより上に回復すると、 Hot Swap MOSFETは、100msのデバウンス・サイクルが経過 してから再度オンします。一方の電源の低電圧フォールトは 他方の電源の動作には影響を与えません。理想ダイオード MOSFETによって制御される理想ダイオード機能は、低電圧 フォールト状態によって影響を受けません。 内部で生成する電源(INTVCC)がその2.2V UVLOスレッ ショルドより下になるまで両方のIN電源が下がると、全ての MOSFETがオフし、フォールト・ラッチがクリアされます。入力 電源が回復し、INTVCCがそのUVLOスレッショルドを超える と、新たなスタートアップ・サイクルから動作が再開されます。 電源のグリッチを除去するため、ONピンには10μsのグリッチ・ フィルタが備わっています。抵抗分割器とともにフィルタ・コン デンサ(CF)をONピンに接続することにより、RC時定数によっ てグリッチ・フィルタ遅延がさらに延長され、誤ったフォールト を防ぎます。 パワーグッド・モニタ 内部回路がMOSFETのゲートのHGATEピンとOUTピン の間のオーバードライブをモニタします。各電源のパワー グッド状態は、それぞれに対応するオープン・ドレイン出力 (PWRGD1またはPWRGD2)を通して通知されます。それら は通常外部のプルアップ抵抗または内部の10μAプルアップに よって H に引き上げられます。パワーグッド出力は、HGATE のスタートアップの間にゲートのオーバードライブが4.2Vを 超えると L にアサートされます。L にアサートされると、パ ワーグッド状態はラッチされ、ONピンを L にするか、ENピ ンを L から H にトグルするか、またはINTVCCが低電圧 ロックアウト状態になる場合にだけクリアすることができます。 HGATEがアクティブ電流制限状態で安定化している間、パ ワーグッド出力は L のまま留まりますが、回路ブレーカがタ イムアウトしてHGATEピンを L に引き下げると、H になり ます。 CPOとDGATEのスタートアップ CPOピンとDGATEピンの電圧は、最初にパワーアップした とき、INピンよりダイオード1個分下にプルアップされます。 INTVCCがその低電圧ロックアウト・レベルをクリアしてから 7μs後、CPOがランプアップを開始します。さらに40μs後、 DGATEもCPOとともにランプアップを開始します。CPOのラ ンプレートは、CPOピンとDGATEピンの合計容量に流れ込 むCPOのプルアップ電流によって決まります。内部クランプが CPOピンの電圧をINピンの12V上に制限し、DGATEピンの 最終電圧はゲート・ドライブ・アンプによって決まります。内部 12Vクランプが、INより上のDGATEピンの電圧を制限します。アプリケーション情報

図6.フォールト後の自動リトライ TMR 1V/DIV HGATE 5V/DIV FAULT 10V/DIV ILOAD 20A/DIV 50ms/DIV 422512 F06LTC4225-1/LTC4225-2

15

422512f MOSFETの選択 LTC4225はNチャネルMOSFETをドライブして負荷電流を 流します。MOSFETの重要な特性は、オン抵抗(RDS(ON))、 最大ドレイン-ソース電圧(BVDSS)、およびスレッショルド電 圧です。理 想ダイオードMOSFETとHot Swap MOSFETのゲート・ ドライブは、IN1とIN2の電源電圧が2.9V∼7Vのとき、それ ぞれ5Vおよび4.8Vより大きいことが保証されています。IN1 とIN2の電源電圧が7Vより大きいとき、ゲート・ドライブは 10Vより大きいことが保証されています。ゲート・ドライブは 14V以下に制限されます。このため、ロジック・レベル・スレッ ショルドのNチャネルMOSFETおよび7Vより上では標準N チャネルMOSFETを使うことができます。定格ブレークダウン 電圧が14V未満のとき、外部のツェナー・ダイオードを使って、 MOSFETのゲートからソースまでの電位を14Vより下にクラ ンプすることができます。 全電源電圧がMOSFETの両端に現れることがあるので、最 大許容ドレイン-ソース電圧(BVDSS)は電源電圧より高くなけ ればなりません。入力または出力がグランドに接続されると、 全電源電圧がMOSFETの両端に現れます。RDS(ON)は、最大 負荷電流を流し、同時にMOSFETの電力定格を超えないよ うに、十分小さくなければなりません。 CPOコンデンサの選択 CPOピンとINピンの間のコンデンサ(CCP)の推 奨 値は、 理想ダイオードMOSFETの入力容量(CISS)の約10倍です。 コンデンサが大きいほど、それに応じて内部チャージポンプに よって充電するのに長い時間を要します。小さなコンデンサは MOSFETのゲート容量と電荷を共有するので、ゲートの高速 ターンオン・イベントの間の電圧降下が大きくなります。 電源の過渡変動に対する保護 入力と出力の容量が非常に小さい場合、入力または出力 の短絡発生時の急激な電流変化により、INピンとOUT ピンの24Vの絶対最大定格を超える過渡変動が生じる 可能性があります。このようなスパイクを最小に抑えるに は、幅の広いトレースや厚いトレースめっきを使って電力 トレースのインダクタンスを減らします。また、10μF電解コ ンデンサおよび0.1μFセラミック・コンデンサを使ってロー カルにバイパスします。または、代わりに、トランジェント 電圧サプレッサ(Z1、Z2)を使って入力をクランプします。 10Ω、0.1μFのスナバが応答を減衰させ、リンギングを除去し ます(図11を参照)。 設計例 部品選択の設計例として、2個の電源の最大負荷電流が7.6A の12Vシステムを検討します(図1を参照)。 まず、12V電源の適切な電流検出抵抗(RS1とRS2)の値を選 択します。最大負荷電流ILOAD(MAX)、回路ブレーカの最小ト リップ電流ITRIP(MIN)および回路ブレーカのスレッショルドの 下限値ΔVSENSE(CB)(MIN)に基づいてセンス抵抗の値を計算 します。低い方の電源の逆ターンオフが作動する前に高い方 の電源の回路ブレーカが誤ってトリップすることなく、バック フィード電流がセンス抵抗を通って短時間流れることができ るようにするため、ITRIP(MIN)/ILOAD(MAX)比として与えられた 負荷電流マージンが備わっています。1.5倍の負荷電流マー ジンを仮定すると、次にようになります。

ITRIP(MIN) = 1.5 • ILOAD(MAX) = 1.5 • 7.6A = 11.4A

RS=∆VSENSE(CB)(MIN) ITRIP(MIN) = 47.5mV 11.4A = 4.16mΩ 許容誤差1%の4mΩセンス抵抗を選択します。 次に、最 大 負荷で望みの順 方 向 電 圧 降 下を達 成する MOSFETのRDS(ON)を計算します。バック・トゥ・バックに接続 された2個のMOSFET両端の順方向電圧降下(∆VFWD)を 60mVと仮定すると次のようになります。 RDS(ON,TOTAL)≤ ∆VFWD ILOAD(MAX)= 60mV 7.6A = 7.9mΩ Si7336ADPは 良 い 選 択 肢 で あり、VGS = 10Vで の 最 大 RDS(ON)が3mΩなので、電 源 経 路の2個のMOSFETでは 合 計6mΩになります。Si7336ADPの入力容 量(CISS)は約 5600pFです。10倍の推奨値をわずかに超えますが、CPOピン のCCP1とCCP2に0.1μFのコンデンサを選択します。

アプリケーション情報

LTC4225-1/LTC4225-2

16

422512f 次に、パワーアップ時または出力短絡時に、選択された MOSFET (i7336ADP)の熱定格を超えないことを検証します。 パワーアップ時に負荷コンデンサ(CL)を充電する突入電流 により、MOSFETが電力を消費すると仮定すると、MOSFET 内部で消費されるエネルギーは負荷コンデンサに蓄えられる エネルギーと同じであり、次のように与えられます。 ECL=1 2• CL• VIN2 CL = 1600µFでは、CLを充電するのに要する時間は次のよう に計算されます。 tCHARGE=CL• VIN IINRUSH= 1600µF • 12V 1A = 19ms突入電流はHot Swap MOSFETのゲートに容量(CHG)を追 加することにより、1Aに設定されます。 CHG=CL• IHGATE(UP) IINRUSH = 1600µF • 10µA 1A = 16nF CHGには15nFの実際的な値を選択します。 MOSFETの平均電力損失は次のように計算します。 PAVG= ECL tCHARGE= 1 2• 1600µF • 12V

(

)

2 19ms = 6W 選択されたMOSFETは、パワーアップ時に、19msの間6Wを 許容できなければなりません。Si7336ADPのSOA曲線は、 100msの間30Vで1.5A(45W)を示しています。これは要件を 満たすのに十分です。MOSFET内部の電力損失による接合部 温度の増加は∆T = PAVG • ZthJCです。ここで、ZthJCは接合部 からケースまでの熱抵抗です。この条件では、Si7336ADPの データシートは、ZthJC = 0.8 C/Wを使って接合部温度が4.8 C だけ増加することを示しています(単一パルス)。 出力短絡時の電力パルスの持続時間と大きさは、TMRの容 量(CT)およびLTC4225のアクティブ電流制限の関数です。短 絡回路の持続時間は、CT = 0.047µFでは、CT • 12[ms/µF] = 0.56msとして与えられます。最大短絡電流は、最大アクティブ 電流制限のスレッショルド∆VSENSE(ACL)(MAX)と最小RS値 を使って計算します。ISHORT(MAX)=∆VSENSE( ACL)(MAX) RS(MIN) = 75mV 3.96mΩ= 18.9A したがって、MOSFETの最大電力損失は0.56msの間18.9A • 12V = 227Wです。Si7336ADPのデータシートは、この短絡状態 でのワーストケースの接合部温度の上昇は、ZthJC = 0.1 C/W を使って22.7 Cであることを示しています(単一パルス)。CT = 0.047µFを選択すると、MOSFETの最大接合部温度を超える ことはありません。Si7336ADPのSOA曲線は、1msの間30Vで 15A(450W)を示しています。これも要件を満たします。 つぎに、ON1ピンとON2ピンの抵抗分割器を選択して、12V 電源では9.6Vの低電圧スレッショルドを設定します。まず、 20kになるように下側の抵抗(R1とR3)を選択します。次いで、 R2とR4の上側の抵抗の値を計算します。 RTOP= VIN(UVTH) VON(TH) – 1 ⎛ ⎝ ⎜ ⎞ ⎠ ⎟ • RBOTTOM RTOP= 9.6V 1.235V– 1 ⎛ ⎝⎜ ⎞ ⎠⎟• 20k = 135k R2とR4には最も近い1%抵抗値の137kを選択します。さらに、 INTVCCピンには0.1μFのバイパス・コンデンサ(C1)、ONピン には10nFのフィルタ・コンデンサ(CF)があり、電源グリッチが Hot Swap MOSFETをオフするのを防ぎます。

PCBのレイアウトに関する検討事項 LTC4225の回路ブレーカを適切に作動させるには、センス抵 抗へのケルビン接続を強く推奨します。配線による誤差を小さ くするため、PCBレイアウトはバランスのとれた対称形にしま す。さらに、センス抵抗とパワーMOSFETのPCBレイアウトに は、デバイスの電力損失を最適化するために正しい熱管理手 法を使います。推奨PCBのレイアウトを図7に示します。

アプリケーション情報

LTC4225-1/LTC4225-2

17

422512f INピンとOUTピンのトレースはMOSFETの端子にできるだ け近づけて接続します。MOSFETへのトレースは幅を広く、長 さを短くして抵抗性の損失を最小にします。MOSFETを通る 電力経路に関連したPCBトレースは抵抗を小さくします。PCB のトレース抵抗、電圧降下および温度上昇を最小に抑えるに は、1オンス銅箔の推奨トレース幅は、1AのDC電流当たり0.03 インチです。1オンスの銅箔のシート抵抗は約0.5mΩ/平方 であり、高電流アプリケーションではトレース抵抗による電圧 降下がたちまち大きくなることに注意してください。 24 23 22 21 20 8 1 2 3 4 5 6 7 19 18 17 16 15 14 13 9 10 11 12 LTC4225UFD C1 RH1 CCP1 CCP2 RH2 Z1 Z2 VIAS TO GND PLANE RS1 IN1 OUT1 OUT2 422512 F07 CURRENT FLOW TO LOAD•

•

MD1PowerPAK SO-8 PowerPAK SO-8MH1

MD2

PowerPAK SO-8 PowerPAK SO-8MH2

S D S D S D G D D G D S D S D S S D S D S D G D D G D S D S D S

•

•

• •

•

• •

•

•

CURRENT FLOWTO LOAD CURRENT FLOWTO LOAD

CURRENT FLOW TO LOAD TRACK WIDTH W: 0.03" PER AMPERE ON 1oz Cu FOIL W IN2 W W RS2 W INTVCCピンのバイパス・コンデンサ(C1)をINTVCCとGND の間にできるだけ近づけて配置することも重要です。また、 CPO1ピンとIN1ピンの近くにCCP1を配置し、CPO2ピンと IN2ピンの近くにCCP2を配置します。過渡電圧サプレッサ(Z1 とZ2)を使う場合、それらを短いリード長でLTC4225の近く に実装します。 図7.パワーMOSFETとセンス抵抗の推奨PCBレイアウト

アプリケーション情報

LTC4225-1/LTC4225-2

18

422512fアプリケーション情報

電源プライオリタイザ 2つの電源のうち、単に電圧の高い方を使うのではなく、優先 順位に基づいてどちらかを出力に接続するアプリケーション を図8に示します。5Vの主電源(INPUT 1)が(それが利用可 能である限り)いつでも出力に接続されます。主電源を利用で きないときだけ、12Vのバックアップ電源(INPUT 2)から電力 が供給されます。ON1ピンのR1-R2分圧器によって設定され る4.3V UVスレッショルドをINPUT 1が超えている限り、MH1 がオンしてINPUT 1を出力に接続します。MH1がオンしている とき、PWRGD1は L になり、ON2を L に引き下げ、MH2を オフすることによりIN2の経路をディスエーブルします。主電源 に不具合が生じ、INPUT 1が4.3Vを下回ると、ON1がMH1 をオフし、PWRGD1が H になるので、ON2はMH2をオンし てINPUT 2を出力に接続することができます。ダイオードD1 がON2をオフ状態の間0.6Vより上に保つので、ON2が H になると、100msのターンオン遅延が作動することなく、MH2 は直ちにオンします。INPUT 1が利用可能な電圧に戻ると、 MH1がオンし、MH2がオフします。理想ダイオードMOSFET のMD1とMD2は、いかなる条件でも、一方の入力から他方へ のバックフィードを防ぎます。 その他のアプリケーション ほとんどのアプリケーションでは、バック・トゥ・バック MOSFETは、電源側のMOSFETが理想ダイオードとして構 成され、負荷側のMOSFETがHot Swap制御として構成され ます。ただし、アプリケーションによっては、理想ダイオードの MOSFETとHot Swap制御のMOSFETが、図9に示されてい るように、入れ替わることがあります。Hot Swap MOSFETが 電源側に配置され、理想ダイオードMOSFETが負荷側に配 置され、ソース端子が一緒に接続されます。この構成が12V 電源で動作すると、LTC4225の内部12VクランプはDGATE からINピンの電圧とHGATEからOUTピンの電圧を制限す るだけなので、入力または出力がグランドに接続される場合、 MOSFETのゲート-ソースのブレークダウン電圧を超える可 能性があります。入力または出力の短絡時にはMOSFETの GATEピンとSOURCEピンの間に24Vの電圧が現れる可 能性があるので、ゲート-ソースのブレークダウン電圧の定 格が25V以上のMOSFETを選択します。ゲート-ソースのブ レークダウン電圧定格がもっと低いMOSFETを選択する場 合、ブレークダウンを防ぐため、図9に示されているように、 MOSFETのGATEピンとSOURCEピンの間に外部ツェナー・ ダイオードによるクランプが必要です。 図8.2チャネル電源プライオリタイザ CPO1 ON1 EN1 ON2 EN2 INTVCC GND CCP1 0.1µF C1 0.1µF CF1 0.1µF CHG1 33nF CL 470µF CT2 47nF Z1 SMAJ13A INPUT 1 INPUT 2 5V PRIMARY SUPPLY 12V BACKUP SUPPLY CCP2 0.1µF CT1 47nF IN1 SENSE1 DGATE1MD1 SiR466DP SiR466DPMH1 LTC4225 RS1 0.006Ω MD2 SiR466DP SiR466DPMH2 RS2 0.006Ω R3 3.92k D1 LS4148 HGATE1 RH1 10Ω R47ΩHG1 VOUT 5A OUT1

CPO2 IN2 SENSE2 DGATE2 HGATE2 OUT2

422512 F08 FAULT1 PWRGD2 FAULT2 Z2 SMAJ13A R4 41.2k R2 49.9k R1 20k PWRGD1 TMR1 TMR2 + +

LTC4225-1/LTC4225-2

19

422512f

アプリケーション情報

図9.電源側にHot Swap MOSFET、負荷側に理想ダイオードMOSFETを配置したアプリケーション

CPO1 ON1 VIN1 12V PWREN1 VIN2 12V ON2 INTVCC GND C1 0.1µF CCP1 0.1µF CCP2 0.1µF CT2 47nF CHG1 15nF BULK SUPPLY BYPASS CAPACITOR BULK SUPPLY BYPASS CAPACITOR CT1 47nF 12V 5A PLUG-IN CARD 1 PLUG-IN CARD 2 BACKPLANE 422512 F09

IN1 SENSE1 HGATE1

MD1 SiR466DP MH1 SiR466DP LTC4225 RS1 0.006Ω MH2 SiR466DP SiR466DPMD2 ZH1, ZD1, ZH2, ZD2: CMHZ4706 RS2 0.006Ω DGATE1 OUT1

CPO2 IN2 SENSE2 HGATE2 DGATE2 OUT2 FAULT1 PWRGD1 EN1 TMR1 TMR2 EN2 PWRGD2 FAULT2 RH1 10Ω ZH1 ZD1 RHG1 47Ω CHG2 15nF RH2 10Ω R47ΩHG2 12V 5A CL1 1000µF PWREN2 + CL2 1000µF + ZH2 ZD2 図10.12Vと3.3Vの入力電源に理想ダイオードを使ったプラグイン・カードの電源ホールドアップ CPO1 ON1 EN1 R2 137k R4 28k VIN2 3.3V ON2 EN2 INTVCC GND C1 0.1µF CF1 0.1µF CF2 0.1µF CCP1 0.1µF Z1 SMAJ13A CCP2 0.1µF CT2 0.1µF CHG1 15nF CL1 1000µF 12V 10A CT1 22nF BACKPLANE

CONNECTOR CARDCONNECTOR 422512 F10

IN1 SENSE1 DGATE1 MD1 SiR158DP SiR158DPMH1 LTC4225 RS1 0.003Ω MD2 SiR468DP SiR468DPMH2 RS2 0.015Ω HGATE1 OUT1

CPO2 IN2 SENSE2 DGATE2 HGATE2 OUT2 FAULT1 PWRGD1 TMR1 TMR2 PWRGD2 FAULT2 RH1 10Ω R47ΩHG1 R5 2.7k D2 D1 R6 2.7k VIN1 R1 20k R3 20k Z2 SMAJ13A VIN1 12V R7 2.7k D1 D2 R8 2.7k VIN2 + CL2 100µF 3.3V 2A D1: GREEN LED LN1351C D2: RED LED LN1261CAL

LTC4225-1/LTC4225-2

20

422512fアプリケーション情報

図11.出力をダイオード接続した、カードに置かれたアプリケーション R2 137k R4 137k VIN2 12V CF1 0.1µF CF2 0.1µF BACKPLANECONNECTOR CARDCONNECTOR R1 20k R3 20k VIN1 12V CPO1 ON1 EN1 ON2 EN2 INTVCC GND C1 0.1µF CCP1 0.1µF Z1 SMAJ13A CCP2 0.1µF CT2 47nF CL 1000µF 12V 5A CT1 47nF 422512 F11

IN1 SENSE1 DGATE1 MD1 SiR466DP SiR466DPMH1 LTC4225 RS1 0.006Ω MD2 SiR466DP SiR466DPMH2 RS2 0.006Ω HGATE1 OUT1

CPO2 IN2 SENSE2 DGATE2 HGATE2 OUT2 FAULT1 PWRGD1 TMR1 TMR2 PWRGD2 FAULT2 R5 100k R6100k VIN1 Z2 SMAJ13A R7 100k R8100k VIN2 + CHG1 15nF RH1 10Ω R47ΩHG1 CHG2 15nF RH2 10Ω R47ΩHG2 CSNUB2 0.1µF RSNUB2 10Ω CSNUB1 0.1µF RSNUB1 10Ω

LTC4225-1/LTC4225-2

21

422512fアプリケーション情報

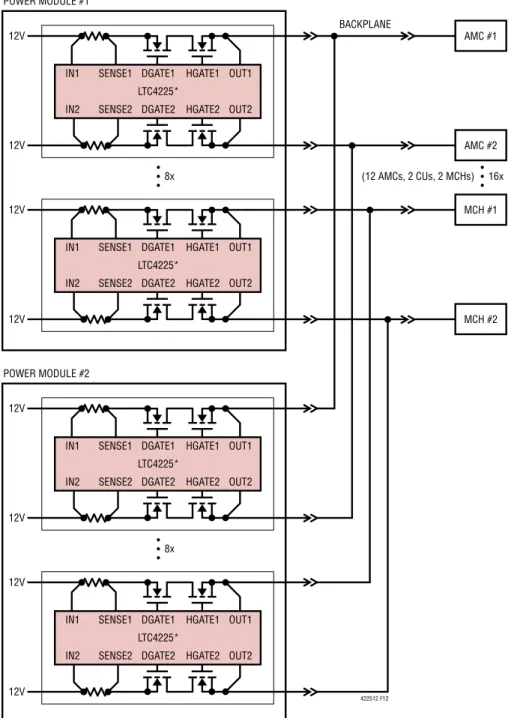

IN1 12V 12V OUT1 BACKPLANE POWER MODULE #1 SENSE1 DGATE1 LTC4225* • • • HGATE1 IN2 SENSE2 DGATE2 OUT28x •• •16x (12 AMCs, 2 CUs, 2 MCHs) HGATE2 AMC #1 AMC #2 IN1 12V 12V OUT1 SENSE1 DGATE1 LTC4225* HGATE1 IN2 SENSE2 DGATE2 HGATE2 OUT2

MCH #1 MCH #2 IN1 12V 12V OUT1 POWER MODULE #2 SENSE1 DGATE1 LTC4225* • • • HGATE1 IN2 SENSE2 DGATE2 OUT2

8x HGATE2

IN1 12V

12V

*ADDITIONAL DETAILS OMITTED FOR CLARITY

OUT1 SENSE1 DGATE1 LTC4225* HGATE1 IN2 OUT2 422512 F12

SENSE2 DGATE2 HGATE2

LTC4225-1/LTC4225-2

22

422512fパッケージ

UFDパッケージ 24 ピン・プラスチック QFN(4mm 5mm) (Reference LTC DWG # 05-08-1696 Rev A) 4.00 ± 0.10 (2 SIDES) 5.00 ± 0.10 (2 SIDES) NOTE: 1. 図はJEDECパッケージ外形MO-220のバリエーション(WXXX-X)にするよう提案されている 2. 図は実寸とは異なる 3. 全ての寸法はミリメートル 4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。 モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと 5. 露出パッドは半田メッキとする 6. 網掛けの部分はパッケージのトップとボトムのピン1の位置の参考に過ぎない ピン1 トップマーキング (Note 6) 0.40 ± 0.10 23 24 1 2 露出パッドの底面 0.75 ± 0.05 R = 0.115TYP R = 0.05 TYP ピン1のノッチ R = 0.20またはC = 0.35 0.25 ± 0.05 0.50 BSC 0.200 REF 0.00 – 0.05 (UFD24) QFN 0506 REV A 推奨する半田パッドのピッチと寸法 半田付けされない領域には半田マスクを使用する 0.70 ±0.05 0.25 ±0.05 0.50 BSC 2.65 ± 0.05 2.00 REF 3.00 REF 4.10 ± 0.05 5.50 ± 0.05 3.10 ± 0.05 4.50 ± 0.05 パッケージの外形 2.65 ± 0.10 2.00 REF 3.00 REF 3.65 ± 0.10 3.65 ± 0.05LTC4225-1/LTC4225-2

23

422512f リニアテクノロジー・コーポレーションがここで提供する情報は正確かつ信頼できるものと考えておりますが、その使用に関する責務は 一切負いません。また、ここに記載された回路結線と既存特許とのいかなる関連についても一切関知いたしません。なお、日本語の資料は あくまでも参考資料です。訂正、変更、改版に追従していない場合があります。最終的な確認は必ず最新の英語版データシートでお願いいたします。パッケージ寸法

GNパッケージ 24ピン・プラスチックSSOP(細型0.150インチ) (Reference LTC DWG # 05-08-1641) .337 – .344* (8.560 – 8.738) GN24 (SSOP) 0204 1 2 3 4 5 6 7 8 9 10 11 12 .229 – .244 (5.817 – 6.198) .150 – .157**(3.810 – 3.988) 16 17 18 19 20 21 22 23 24 15 1413 .016 – .050 (0.406 – 1.270) .015 ± .004 (0.38 ± 0.10)× 45° 0° – 8° TYP .0075 – .0098 (0.19 – 0.25) .0532 – .0688 (1.35 – 1.75) .008 – .012 (0.203 – 0.305) TYP .004 – .0098 (0.102 – 0.249) .0250 (0.635) BSC .033 (0.838) REF .254 MIN 推奨半田パッド・レイアウト .150 – .165 .0250 BSC .0165 ±.0015 .045 ±.005 *寸法にはモールドのバリを含まない。 モールドのバリは各サイドで0.006"(0.152mm)を超えないこと **寸法にはリード間のバリを含まない。 リード間のバリは各サイドで0.010"(0.254mm)を超えないこと インチ (ミリメートル) NOTE: 1. 標準寸法: インチ 2. 寸法は 3. 図は実寸とは異なるLTC4225-1/LTC4225-2

24

422512f

LINEAR TECHNOLOGY CORPORATION 2011 LT 0211 • PRINTED IN JAPAN

リニアテクノロジー株式会社

〒102-0094 東京都千代田区紀尾井町3-6紀尾井町パークビル8F TEL 03- 5226-7291 ● FAX 03-5226-0268 ● www.linear-tech.co.jp

関連製品

標準的応用例

Hot Swapに理想ダイオード制御が続くプラグイン・カードのダイオードOR接続アプリケーション

CPO1 ON1 EN1 VIN2 5V ON2 EN2 INTVCC GND C1 0.1µF CCP1 0.1µF Z1 SMAJ7A CCP2 0.1µF CT2 0.1µF CL 100µF 5V 5A CT1 0.1µF BACKPLANE

CONNECTOR CARDCONNECTOR

422512 TA02

IN1 SENSE1 HGATE1 MH1 Si7790DP Si7790DPMD1 LTC4225 RS1 0.006Ω MH2 Si7790DP Si7790DPMD2 RS2 0.006Ω DGATE1 OUT1

CPO2 IN2 SENSE2 HGATE2 DGATE2 OUT2 FAULT1 PWRGD1 TMR1 TMR2 PWRGD2 FAULT2 Z2 SMAJ7A VIN1 5V PWREN + R1 10k 製品番号 説明 注釈

LTC1421 デュアル・チャネルHot Swapコントローラ 3V∼12Vで動作、–12Vをサポート、SSOP-24

LTC1645 デュアル・チャネルHot Swapコントローラ 3V∼12Vで動作、パワー・シーケンス制御、SSOP-8またはSO-14

LTC1647-1/LTC1647-2/

LTC1647-3 デュアル・チャネルHot Swapコントローラ 2.7V∼16.5Vで動作、SO-8またはSSOP-16 4

LTC4210 シングル・チャネルHot Swapコントローラ 2.7V∼16.5Vで動作、アクティブ電流制限、SOT23-6

LTC4211 シングル・チャネルHot Swapコントローラ 2.7V∼16.5Vで動作、多機能電流制御、MSOP-8またはMSOP-10

LTC4215 シングル・チャネルHot Swapコントローラ 2.9V∼15Vで動作、I2C互換モニタ、SSOP-16またはQFN-24

LTC4216 シングル・チャネルHot Swapコントローラ 0V∼6Vで動作、アクティブ電流制限、MSOP-10またはDFN-12

LTC4218 シングル・チャネルHot Swapコントローラ 2.9V∼26.5Vで動作、アクティブ電流制限、SSOP-16またはDFN-16

LTC4221 デュアル・チャネルHot Swapコントローラ 1V∼13.5Vで動作、多機能電流制御、SSOP-16

LTC4222 デュアル・チャネルHot Swapコントローラ 2.9V∼29Vで動作、I2C互換モニタ、SSOP-36またはQFN-32

LTC4223 デュアル電源ホットスワップ・コントローラ 12Vと3.3Vを制御、アクティブ電流制限、SSOP-16またはDFN-16

LTC4224 デュアル・チャネルHot Swapコントローラ 2.7V∼6Vで動作、アクティブ電流制限、MSOP-10またはDFN-10

LTC4352 低電圧理想ダイオード・コントローラ 2.9V∼18Vで動作、Nチャネルを制御、MSOP-12またはDFN-12

LTC4354 負電圧ダイオードORコントローラおよびモニタ 80V動作、2個のNチャネルを制御、SO-8またはDFN-8

LTC4355 正高電圧理想ダイオードORおよびモニタ 9V∼80Vで動作、2個のNチャネルを制御、SO-16またはDFN-14

LTC4357 正高電圧理想ダイオード・コントローラ 9V∼80Vで動作、Nチャネルを制御、MSOP-8またはDFN-6