Stellaris

®

LM3S9B96 Microcontroller

20 章 ユニバーサル・シリアル・バス (USB) コントローラ

。JAJU152

SPMS182D 翻訳版(20 章)

最新の英語版:

http://www.ti.com/lit/gpn/lm3s9b96

JAJU152

Stellaris LM3S9B96 Microcontroller Data Sheet (Rev. D) 20 章 翻訳版

20

ユニバーサル・シリアル・バス

(USB) コントローラ

Stellaris

®USB コントローラは、USB ホストやデバイス、OTG 機能との Full Speed または Low Speed でのポイ

ントツーポイント通信機能コントローラとして動作します。SUSPEND 信号および RESUME 信号を採用した USB

2.0 標準に準拠しています。コントロール転送用にハード・ワイヤードされたエンドポイント 2 個 (IN 用 1 つ、

OUT 用 1 つ) と、ファームウェアで定義されるエンドポイント 30 個の計 32 個のエンドポイントを備え、大規模な

ダイナミック FIFO とともに、複数のパケット・キューイングをサポートします。FIFO への

μDMA アクセスにより、シ

ステム・ソフトウェアの介在を最小限に抑えることができます。接続と切断をソフトウェアで制御し、USB デバイス起

動時のフレキシビリティを提供します。また、このコントローラは、OTG 標準のセッション要求プロトコル (SRP) およ

びホスト・ネゴシエーション・プロトコル (HNP) に準拠します。

Stellaris

®USB モジュールの主な機能は次のとおりです。

USB-IF 認証標準に準拠

USB 2.0 Full Speed (12 Mbps) および Low Speed (1.5 Mbps) 動作に対応

PHY 内蔵

4 つのデータ転送タイプ: コントロール転送、インタラプト転送、バルク転送、アイソクロナス転送

32 個のエンドポイント

– コントロール転送専用 IN エンドポイントおよび OUT エンドポイント各 1 個

– 転送タイプが設定可能な IN エンドポイントおよび OUT エンドポイント各 15 個

4 KB の専用エンドポイント・メモリ: エンドポイント 1 個を、ダブル・バッファ 1023 バイト・アイソクロナス・パケ

ット・サイズ用に設定

VBUS ドループおよび有効な ID の検出と割り込み

マイクロ・ダイレクト・メモリ・アクセス・コントローラ (μDMA) を使用した効率的なデータ転送

– 最大 3 個までの IN エンドポイントおよび 3 個までの OUT エンドポイントに対し、個別の送信チャネル

と受信チャネルを設定可能

– FIFO のデータ量が指定したレベルに達したときにチャネル要求をアサート

20.1 ブロック図

3

20.2 信号の説明

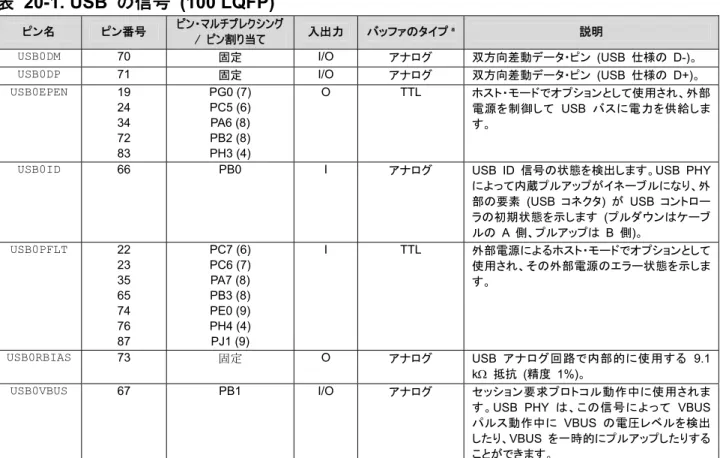

表 20-1 と表 20-2 に USB コントローラの外部信号の一覧を示し、それぞれの機能について説明します。USB

コントローラ信号は特定の GPIO 信号の代替機能であり、リセット後はデフォルトの GPIO 信号になります。次の

表中、「ピン・マルチプレクシング / ピン割り当て」の列に、これらの USB 信号に可能な GPIO ピンの配置を示し

ます。

USB 機能を選択するには、GPIO 代替機能選択 (GPIOAFSEL) レジスタの AFSEL ビットをセットする必

要があります。括弧内の数値は、指定された GPIO ポート・ピンに USB 信号を割り当てるために、GPIO ポート

制御

(GPIOPCTL) レジスタの PMCn フィールドに設定する値を示しています。USB0VBUS 信号と USB0ID 信号

は、

GPIO デジタル・イネーブル (GPIODEN) レジスタの対応する DEN ビットをクリアすることによって設定します。

GPIO の設定の詳細については、「9 汎用入出力 (GPIO)」を参照してください。その他の信号 (ピン・マルチプレク

シング / ピン割り当ての列に「固定」と記載) の割り当てピンと機能は固定です。

注:

OTG モードで使用する場合、USB0VBUS と USB0ID は、USB コントローラに専用のピンであり、また USB

コネクタの VBUS 信号および ID 信号に直接接続されるため、設定は必要ありません。USB コントローラを

専用ホストまたはデバイスとして使用する場合、USB 汎用制御&ステータス (USBGPCS) レジスタの

DEVMODOTG ビットと DEVMOD ビットを使用して USB0VBUS 入力と USB0ID 入力を内部的に固定レベルに

接続し、PB0 ピンと PB1 ピンを解放して GPIO で使用できるようにすることができます。

電源内蔵

デバイスが

正しく動作するには、引き続き VBUS 値を監視し、ホストが VBUS を解除した場合に電源内蔵デバイスが

D+/D- プルアップ抵抗をディスエーブルすることを保証する必要があります。この機能は、VBUS に標準

GPIO を接続することによって実現できます。

表

20-1. USB の信号 (100 LQFP)

ピン名 ピン番号 ピン・マルチプレクシング

/ ピン割り当て 入出力 バッファのタイプ

a 説明

USB0DM 70 固定 I/O アナログ 双方向差動データ・ピン (USB 仕様の D-)。 USB0DP 71 固定 I/O アナログ 双方向差動データ・ピン (USB 仕様の D+)。 USB0EPEN 19 24 34 72 83 PG0 (7) PC5 (6) PA6 (8) PB2 (8) PH3 (4) O TTL ホスト・モードでオプションとして使用され、外部 電源を制御して USB バスに電力を供給しま す。

USB0ID 66 PB0 I アナログ USB ID 信号の状態を検出します。USB PHY によって内蔵プルアップがイネーブルになり、外 部の要素 (USB コネクタ) が USB コントロー ラの初期状態を示します (プルダウンはケーブ ルの A 側、プルアップは B 側)。 USB0PFLT 22 23 35 65 74 76 87 PC7 (6) PC6 (7) PA7 (8) PB3 (8) PE0 (9) PH4 (4) PJ1 (9) I TTL 外部電源によるホスト・モードでオプションとして 使用され、その外部電源のエラー状態を示しま す。 USB0RBIAS 73 固定 O アナログ USB アナログ回路で内部的に使用する 9.1 kΩ 抵抗 (精度 1%)。 USB0VBUS 67 PB1 I/O アナログ セッション要求プロトコル動作中に使用されま す。USB PHY は、この信号によって VBUS パルス動作中に VBUS の電圧レベルを検出 したり、VBUS を一時的にプルアップしたりする ことができます。

a. 「TTL」は、ピンの電圧レベルが TTL 互換であることを示します。

表

20-2. USB の信号 (108BGA)

ピン名 ピン番号 ピン・マルチプレクシング / ピン割り当て 入出力 バッファのタイプ a 説明USB0DM C11 固定 I/O アナログ 双方向差動データ・ピン (USB 仕様の D-)。 USB0DP C12 固定 I/O アナログ 双方向差動データ・ピン (USB 仕様の D+)。 USB0EPEN K1 M1 L6 A11 D10 PG0 (7) PC5 (6) PA6 (8) PB2 (8) PH3 (4) O TTL ホスト・モードでオプションとして使用され、外部 電源を制御して USB バスに電力を供給しま す。

USB0ID E12 PB0 I アナログ USB ID 信号の状態を検出します。USB PHY によって内蔵プルアップがイネーブルになり、外 部の要素 (USB コネクタ) が USB コントロー ラの初期状態を示します (プルダウンはケーブ ルの A 側、プルアップは B 側)。 USB0PFLT L2 M2 M6 E11 B11 B10 B6 PC7 (6) PC6 (7) PA7 (8) PB3 (8) PE0 (9) PH4 (4) PJ1 (9) I TTL 外部電源によるホスト・モードでオプションとして 使用され、その外部電源のエラー状態を示しま す。 USB0RBIAS B12 固定 O アナログ USB アナログ回路に対して内部的に使用する 9.1 kΩ 抵抗 (精度 1%)。 USB0VBUS D12 PB1 I/O アナログ セッション要求プロトコル動作中に使用されま す。USB PHY は、この信号によって VBUS パルス動作中に VBUS の電圧レベルを検出 したり、VBUS を一時的にプルアップしたりする ことができます。