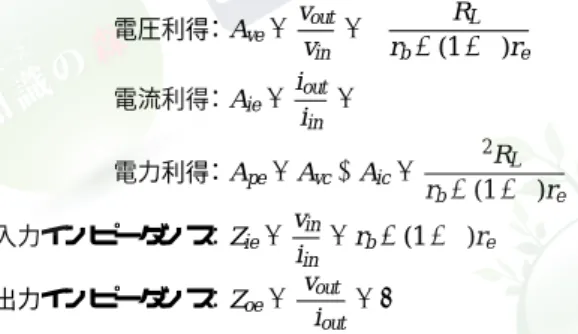

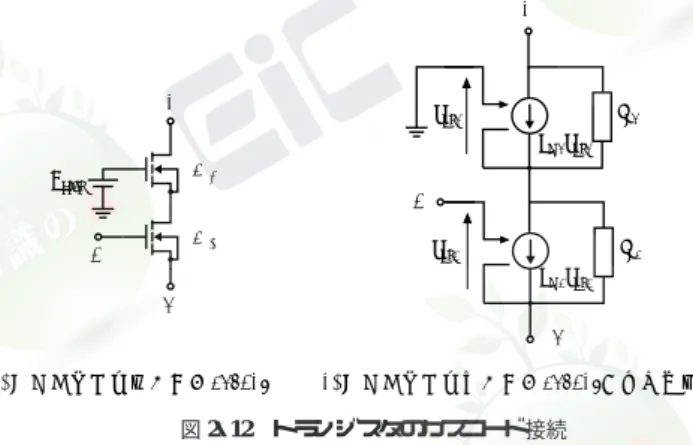

(a) 4 1. A v = / 2. A i = / 3. A p = A v A i = ( )/( ) 4. Z i = / 5. Z o = /( ) = 0 2 1

22

0

0

全文

図

関連したドキュメント

1.4.2 流れの条件を変えるもの

Found in the diatomite of Tochibori Nigata, Ureshino Saga, Hirazawa Miyagi, Kanou and Ooike Nagano, and in the mudstone of NakamuraIrizawa Yamanashi, Kawabe Nagano.. cal with

4)線大地間 TNR が機器ケースにアースされている場合は、A に漏電遮断器を使用するか又は、C に TNR

漏洩電流とB種接地 1)漏洩電流とはなにか

2 E-LOCA を仮定した場合でも,ECCS 系による注水流量では足りないほどの原子炉冷却材の流出が考

直流電圧に重畳した交流電圧では、交流電圧のみの実効値を測定する ACV-Ach ファンクショ

[r]

あれば、その逸脱に対しては N400 が惹起され、 ELAN や P600 は惹起しないと 考えられる。もし、シカの認可処理に統語的処理と意味的処理の両方が関わっ