VIN 5 V C1 4.7 Fµ D1 Rset 0.57Ω VIN SW FB GND CTRL COMP C2 1 Fµ 350 mA 220 nF TPS61165 L 1 : TOKO #A 915 _Y-100M C1 : Murata GRM 188R61 A475 K C2 : Murata GRM 188R61 E105K D1 : ONsemi MBR0540T1 LED : OSRAM LW-W 5SM ON/OFF DIMMING CONTROL L1 10 Hµ 図 1. 標準アプリケーション

高輝度白色LEDドライバ

2mm

× 2mmQFNとSOT-23パッケージ

特 長

● 入力電圧範囲:3V ∼ 18V

● 10直列LEDまで使用可能な38VのLED断線保護

● 2%精度の200mV基準電圧

● 1.2MHzのスイッチング周波数で動作する1.2Aの

FETスイッチを内蔵

● 自由度の高い1線通信によるデジタルまたはPWM

信号による輝度制御

● ソフトスタート機能内蔵

● 最高効率:90%

● 2mm × 2mm × 0.8mmの6ピンサーマルパッド付き

QFNとSOT-23パッケージ

アプリケーション

● 高輝度LED照明

● 中型液晶用白色LEDバックライト

概 要

40V耐圧のFETスイッチを内蔵する事により、TPS61165は最 大10個までの直列LEDを駆動できる昇圧コンバータです。昇圧 コンバータは1.2MHzの固定スイッチング周波数で動作し、 1.2Aのスイッチ電流制限により汎用の高輝度LED照明に使用す ることができます。 白色LED電流の初期設定値は外部の電流検出抵抗Rsetにより 設定され、標準アプリケーション図に示されるように帰還電圧 は200mVに制御されます。動作時、LED電流はCTRLピンによ る1線式デジタル通信制御(EasyscaleTM通信手順)により制御 できます。別の方法として、パルス幅変調(PWM)信号を CTRLピンに供給する事により、デューティ比に応じて帰還電 圧を決定させることができます。デジタル制御とPWMモード のいずれの方式でもTPS61165はLEDをパルス電流で駆動しな いので出力コンデンサでの可聴域ノイズを発生させる事は有り ません。最良の保護の為に本製品はLED断線保護回路を内蔵し ており、LEDが断線状態となった時にTPS61165をディスエー ブルして出力電圧が絶対最大定格を超える事を防止します。 TPS61165はサーマルパッドつきの省スペースな2mm× 2mm QFNパッケージとSOT-23パッケージで供給されます。 JAJS453参 考 資 料

TPS61165

www.tij.co.jpこの資料は、Texas Instruments Incorporated(TI)が英文で記述した資料 を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI)が英文から和文へ翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補 助的参考資料としてご使用下さい。 製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。 SLVS790A 翻訳版 最新の英語版資料 http://www.ti.com/lit/gpn/tps61165 Easyscaleは、テキサス・インスツルメンツの登録商標です。

製品情報

(1)TA OPEN LED PROTECTION PACKAGE(2) PACKAGE MARKING

TPS61165DRV CCQ –40°C ∼ 85°C 38 V (typical) TPS61165DBV DAK (1) 最新のパッケージおよび発注情報については、TIホームページwww.ti.comを参照してください。 (2) DRVパッケージはテープ/リールで供給されています。型番にRを付けると(TPS61165DRVR)リールあたりの数量は3000個です。 型番にTを付けると(TPS61165DRVT)リールあたりの数量は250個です。

絶対最大定格

動作環境温度範囲内(特に記述のない限り) (1) VALUE 単位Supply Voltages on VIN(2) –0.3 ∼ 20 V

Voltages on CTRL(2) –0.3 ∼ 20 V

VI

Voltage on FB and COMP(2) –0.3 ∼ 3

Voltage on SW(2) –0.3 ∼ 40 V

V

PD Continuous Power Dissipation 「許容損失」表を参照

TJ Operating Junction Temperature Range –40 ∼ 150 °C

TSTG Storage Temperature Range –65 ∼ 150 °C

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、 このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時 間置くことは、本製品の信頼性に影響を与えることがあります。 (2) 全ての電圧値は回路のグランド端子を基準にしています。

許容損失定格

DERATINGBOARD PACKAGE RθJC RθJA FACTOR ABOVE TA< 25°C TA= 70°C TA= 85°C

TA = 25C Low-K DRV(1) 20°C/W 140°C/W 7.1mW/°C 715mW 395mW 285mW High-K DRV(2) 20°C/W 65°C/W 15.4mW/°C 1540mW 845mW 615mW High-K DBV(2) n/a 210°C/W 4.7mW/°C 470mW 258mW 188mW (1) このデータを導き出すのに用いられたJEDEC low-K(1s)ボードは、大きさが3インチ × 3インチで、ボードの表面に2オンスの銅配線のある2層ボードです。 (2) このデータを導き出すのに用いられたJEDEC high-K(2s2p)ボードは、大きさが3インチ × 3インチで、内部に1オンスの電源プレーンとグランド・プレーン およびボードの表面と裏面に2オンスの銅配線のある多層ボードです。

推奨動作条件

MIN TYP MAX 単位

VI Input voltage range, VIN 3 18 0

VO Output voltage range VIN 38 V

L Inductor(1) 10 22 µH

fdim PWM dimming frequency 5 100 kHz

CIN Input capacitor 1 µF

CO Output capacitor 1 10 µF

TA Operating ambient temperature –40 85 °C

TJ Operating junction temperature –40 125 °C

静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を 内蔵しています。保存時または取り扱い時に、MOSゲートに 対する静電破壊を防止するために、リード線どうしを短絡して おくか、デバイスを導電性のフォームに入れる必要があります。

電気的特性

VIN = 3.6V, CTRL = VIN, TA = –40°C ∼ 85°C, typical values are at TA = 25°C(特に記述のない限り)

パラメータ テスト測定 MIN TYP MAX 単位

SUPPLY CURRENT

VI Input voltage range, VIN 3 18 V

IQ Operating quiescent current into VIN Device PWM switching no load 2.3 mA

ISD Shutdown current CRTL=GND, VIN = 4.2 V 1 µA

UVLO Under-voltage lockout threshold VIN falling 2.2 2.5 V Vhys Under-voltage lockout hysterisis 70 mV ENABLE AND REFERENCE CONTROL

V(CTRLh) CTRL logic high voltage VIN = 3 V to 18 V 1.2 V

V(CTRLl) CTRL logic low voltage VIN = 3 V to 18 V 0.4 V

R(CTRL) CTRL pull down resistor 400 800 1600 kΩ

toff CTRL pulse width to shutdown CTRL high to low 2.5 ms

tes_det Easy Scale detection time(1) CTRL pin low 260 µs

tes_delay Easy Scale detection delay 100 µs

tes_win Easy Scale detection window time Measured from CTRL high 1 m s

VOLTAGE AND CURRENT CONTROL

VREF Voltage feedback regulation voltage 196 200 204 mV

Voltage feedback regulation voltage under VFB= 50 mV 47 50 53

V(REF_PWM) brightness control V mV

FB= 20 mV 17 20 23

IFB Voltage feedback input bias current VFB= 200 mV 2 µA

fS Oscillator frequency 1.0 1.2 1.5 MHz

Dmax Maximum duty cycle VFB= 100 mV 90% 93%

tmin_on Minimum on pulse width 40 ns

Isink Comp pin sink current 100 µA

Isource Comp pin source current 100 µA

Gea Error amplifier transconductance 240 320 400 umho

Rea Error amplifier output resistance 6 MΩ

fea Error amplifier crossover frequency 5 pF connected to COMP 500 kHz POWER SWITCH

N-channel MOSFET on-resistance VIN = 3.6 V 0.3 0.6

RDS(ON) Ω

VIN = 3.0 V 0.7

ILN_NFET N-channel leakage current VSW= 35 V, TA= 25°C 1 µA

OC and OLP

ILIM N-Channel MOSFET current limit D = Dmax 0.96 1.2 1.44 A

ILIM_Start Start up current limit D = Dmax 0.7 A

tHalf_LIM Time step for half current limit 5 ms

Vovp Open LED protection threshold Measured on the SW pin 37 38 39 V

Open LED protection threshold on FB Measured on the FB pin, percentage of

V(FB_OVP) Vref, Vref = 200 mV and 20 mV 50%

tREF VREFfilter time constant 180 µs

Each step, Measured as number of

tstep VREFramp up time cycles of the 1.2 MHz clock 213 µs EasyScale TIMING

tstart Start time of program stream 2 µs

tEOS End time of program stream 2

2

360 µs tH_LB High time low bit Logic 0 180 µs

tL_LB Low time low bit Logic 0 2×tH_LB 360 µs (1)EasyScaleTMモードを選択するには、CTRLピンはt

VIN CTRL SW FB COMP GND TOP VIEW Thermal Pad 6-PIN 2mm x 2mm x 0.8mm QFN VIN SW FB GND CTRL COMP 1 2 4 3 5 6 TOP VIEW 6-PIN SOT-23

デバイス情報

MIN TYP MAX

tH_HB High time high bit Logic 1 tL_HB 360 µs

tL_HB Low time high bit Logic 1

2×

2 180 µs

VACKNL Acknowledge output voltage low Open drain, Rpullup =15 kΩ to VIN 0.4 V

tvalACKN Acknowledge valid time See(2) 2 µs

tACKN Duration of acknowledge condition See(2) 512 µs

THERMAL SHUTDOWN

Tshutdown Thermal shutdown threshold 160 °C

Thysteresis Thermal shutdown threshold hysteresis 15 °C

(2) 認証は0の状態でアクティブ。この状態はRFAビットがセットされている場合にのみ適用されます。オープン・ドレイン出力で、 ラインはホスト側で抵抗により“H”レベルにプルアップすることが必要です。

電気的特性

VIN = 3.6V, CTRL = VIN, TA = –40°C ∼ 85°C, typical values are at TA = 25°C(特に記述のない限り)

パラメータ テスト測定 単位 端子 I/O 説明 DRV DBV NAME NO. NO. VIN 6 1 I IC用の入力電源ピンです。VINを3V∼18Vの電源電圧に接続します。 このピンはICのスイッチング・ノードです。SWピンをインダクタのスイッチ側に接続します。 このピンはLED断線検出の為に出力電圧を検出する為にも使用されます。 SW 4 3 I GND 3 4 O グランド・ピンです。 FB 1 6 I 電流のフィードバック・ピンです。電流検出抵抗をFBとGNDの間に接続します。 トランスコンダクタンス誤差増幅器の出力です。レギュレータを補償するためこのピンに外部コンデン サを外付けします。 COMP 2 5 O 昇圧型レギュレータのコントロール・ピンです。これはイネーブル制御やPWMかデジタル制御による調 光に用いられる多機能ピンです。 CTRL 5 2 I Thermal サーマル・パッドはアナログ・グランド・プレーンにはんだ付けしなければなりません。理想的な放熱設 計となるよう、できれば、サーマル・ビアを用いてグランド・プレーンと接続してください。 Pad

ピン機能

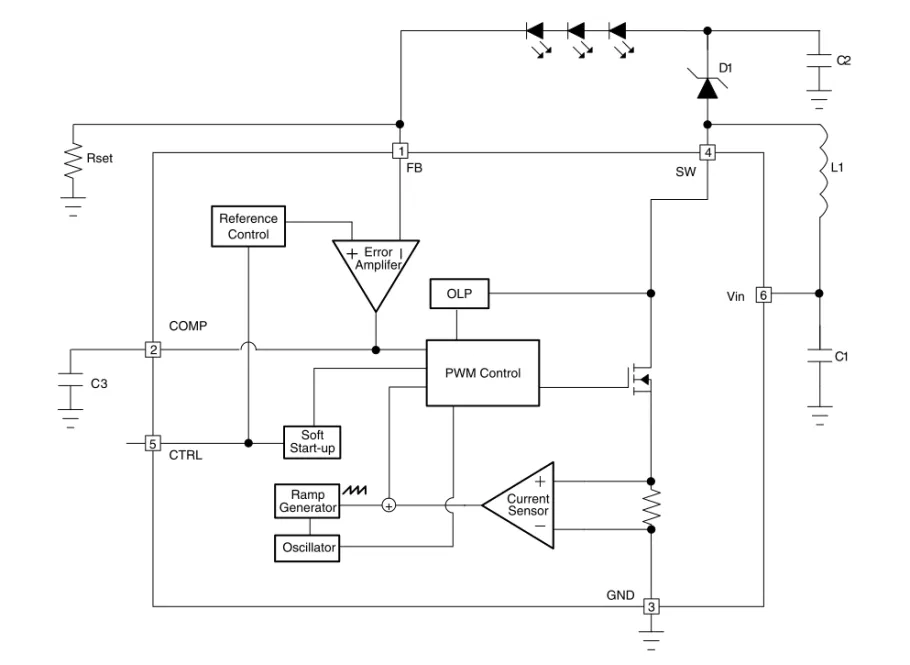

機能ブロック図

SW Ramp Generator Oscillator Current Sensor OLP CTRL GND C3 L1 + FB Reference Control D1 Error Amplifer 2 1 Rset C2 Vin C1 PWM Control 4 6 5 3 COMP Soft Start-up 図Efficiency 3 LEDs (VOUT = 12V); VIN = 3, 5, 8.5V; L = 10µH 図 2 図 3 図 4 図 5 図 6 図 7 図 8 図 9 図 10 図 11 Efficiency 6 LEDs (VOUT = 24V); VIN = 5, 8.5, 12V; L = 10µH

Current limit TA= 25°C

Current limit Easyscale step

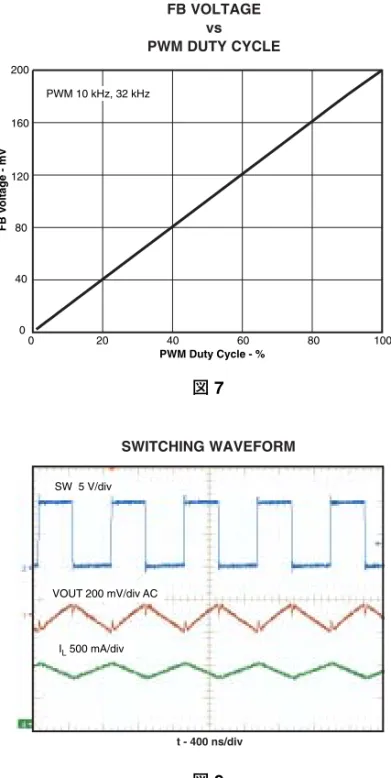

PWM dimming linearity VIN = 3.6 V; PWM Freq = 10 kHz and 32 kHz Output ripple at PWM dimming 3 LEDs; VIN = 5 V; ILOAD= 350 mA; PWM 32 kHz

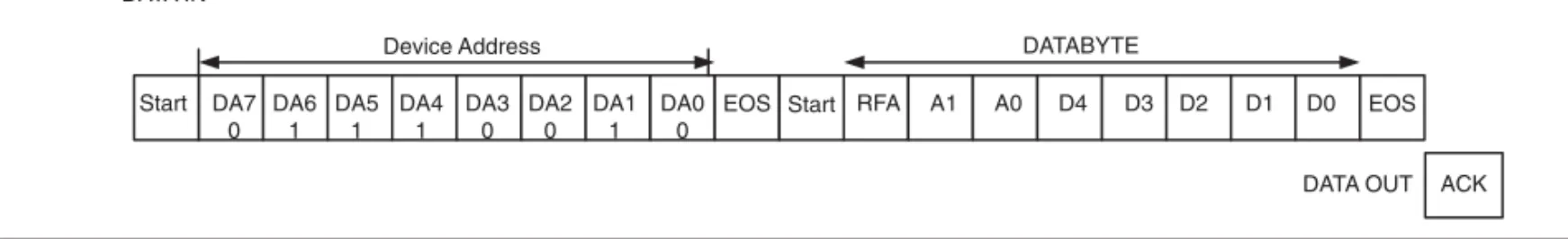

Switching waveform 3 LEDs; VIN = 5 V; ILOAD= 3500 mA; L = 10µH

Start-up 3 LEDs; VIN = 5 V; ILOAD= 350 mA; L = 10µH

Open LED protection 8 LEDs; VIN = 3.6 V; ILOAD= 20 mA

代表的特性

代表的特性

40 50 60 70 80 90 100 0 50 100 150 200 250 300 Output Current - mA3 LEDs ( VOUT = 12 V ) VIN = 8.5 V

VIN = 5 V VIN = 3 V Efficiency -% EFFICIENCY vs OUTPUT CURRENT

図 1

800 900 1000 1100 1200 1300 1400 1500 1600 20 30 40 50 60 70 80 90 Duty Cycle - % Switch Current Limit -ASWITCH CURRENT LIMIT vs DUTY CYCLE

図 3

40 50 60 70 80 90 100 0 50 100 150 200 250 300 VIN = 12 V VIN = 8.5 V VIN = 5 V 6 LEDs ( VOUT = 24 V ) Output Current - mA Efficiency -% EFFICIENCY vs OUTPUT CURRENT図 2

800 900 1000 1100 1200 1300 1400 1500 1600 –40 –20 0 20 40 60 80 100 120 140 Temperature - C° Switch Current Limit -m ASWITCH CURRENT LIMIT vs

TEMPERATURE

代表的特性

CTRL 5 V/div VOUT 5 V/div COMP 500 mV/div I 500 mA/divL t - 2 ms/div START-UP図 10

OPEN LED 5 V/div

FB 200 mV/div

VOUT 10 V/div

I 200 mA/divL

t - 100 s/divµ

OPEN LED PROTECTION

図 11

t - 20 s/divµ

PWM 5 V/div

VOUT 50 mV/div AC

ILED200 mA/div

OUTPUT RIPPLE at PWM DIMMING

図 8

SW 5 V/div t - 400 ns/div VOUT 200 mV/div AC I 500 mA/divL SWITCHING WAVEFORM図 9

0 20 40 60 80 100 120 140 160 180 200 0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 Easy Scale StepFB V oltage -m V FB VOLTAGE vs EASYSCALE STEP

図 6

0 40 80 120 160 200 0 20 40 60 80 100 PWM Duty Cycle - % PWM 10 kHz, 32 kHz FB V oltage -m V FB VOLTAGE vs PWM DUTY CYCLE図 7

詳細説明

動作

TPS61165は高効率で高出力電圧の小型パッケージサイズの 昇圧コンバータです。本製品は10個までの直列接続された白色 LEDの駆動に最適です。直列接続されたLEDには全てのLEDに 同じ電流を流す事により均一な輝度を得ることができるので、 高価となる生産工場でのランク選別が不要となります。このデ バイスは40V/1.2AのFETスイッチを内蔵しており、1.2MHzの スイッチング周波数によるパルス幅変調(PWM)で動作します。 動作はブロック図を参照してください。エラー・アンプの出力 と電流の信号がPWM制御コンパレータに入力されてコンバー タのデューティサイクルが設定されます。制御方式は従来型の 電流モード制御方式を基本としていますので、40%以上のデュー ティサイクルにおける安定動作を確保する為に電流の信号にス ロープ補償が追加されています。負帰還ループ制御はFBピンを 低基準電圧(標準で200mV)に制御するので電流検出抵抗での 損失を低減することができます。ソフトスタート

起動時の大きな突入電流を回避するためICにソフトスタート 回路が内蔵されています。デバイスがイネーブルになった後、 FBピンの基準電圧は各ステップ213µsの32ステップで上昇しま す。このことにより、出力電圧がゆっくり上昇し突入電流が低 減することが確実なものになります。さらに、COMP電圧が上 昇した後の最初の5msでは、スイッチの電流制限値は標準の電 流制限仕様の半分に設定されます。よって、この期間中は、入 力電流は700mA(標準)より低く保たれています。これらの2つ の機能により、スムーズな起動と最小のラッシュ電流を実現し ています。代表的特性の起動波形(図10)を参照してください。LED断線保護

LED断線保護回路により白色LEDでの断線の結果発生するIC へのダメージを防止します。TPS61165はスイッチング中にSW ピンの電圧とFBピンの電圧を監視しています。保護回路はSW ピンの電圧がVovpスレッショルドを超過し、FBピンの電圧が 制御電圧の半分以下まで低下した状態が8クロックの間継続す ると直ちに昇圧スイッチFETをOFFにしてICをシャットダウン 状態にします。この結果出力電圧は入力電圧レベルまで低下し ます。本製品はCTRLピンの論理をトグル(OFF-ON)して再起 動されるまでシャットダウン状態を継続します。TPS61165に は、内部の40V FETが故障するのを防ぐだけでなく、安価な低 電圧出力コンデンサの使用を可能とする、異なったランプ切れ 保護スレショルド電圧の製品も準備可能です。本製品のスレッ ショルド電圧は38Vです。シャットダウン

TPS61165はCTRLの電圧が2.5msより長い時間、論理0が続く とシャットダウン・モードになります。シャットダウン時、デ バイスの電源電流は1µA(最大)より低くなります。 内部FETスイッチがシャットダウンしたとしても。入力から LED列へはインダクタとショットキーダイオードを経由した直 流電流のパスが存在します。シャットダウン時にLED電流を確 実にOFFに保持するにはLEDアレイの順方向電圧の最小値の合 計が入力電圧の最大値を超えている必要があります。電流設定

FBピンの電圧は0.2Vという低い基準電圧に制御されます。 LEDの電流はLED列に直列に接続された電流検出抵抗により外 部で設定されます。RSETの値は式(1)により計算できます。 ここで: ILED= LED出力電流 VFB = FBピンの制御電圧 RSET= 電流検出抵抗の抵抗値 出力電流の公差はFBでの電圧精度と電流検出抵抗の精度に 依存します。I

LED=

V

FBR

SET (1)CTRL low high FB 200mV x duty cycle Insert battery CTRL low high FB Insert battery Programming code

FB ramp Shutdown delay t

Enter ES mode

Timing window Programming code

50mV 50mV Enter ES mode PWM signal Startup delay PWM mode Startup delay FB ramp Programmed value (if not programmed, 200mV default )

Shutdown delay IC Shutdown Startup delay FB ramp ES

mode ES detect delay ES detect time

図 12. Dimming Mode Detection and Soft Start PWM Brightness Dimming

LED輝度調光モードの選択

CTRLピンは、PWM調光と1線式調光の両方の調光モードの 制御入力に使用されます。調光モードはデバイスがイネーブル になるたびに選択されます。デフォルトのモードはPWM調光 です。1線式のモードにするには、ICがシャットダウン・モード から起動するたびに、CTRLピンに以下のデジタル・パターンを 送って、ICで認識されなければなりません。 1. TPS61165をイネーブルにし、1線式モードへの検出ウィン ドウを開始するためCTRLピンを“H”レベルにします。 2. EasyScale検出遅延(tes_delay、100µs)の経過以降に、 EasyScale検出時間(tes_detect、260µs)より長い期間 CTRLを“L”レベルにします。 3. CTRLピンはEasyScale検出ウィンドウ(tes_win、1ms)が 経過する前にEasyScale 検出時間より長い期間“L”レベルになっていなければなり ません。EasyScale検出ウィンドウはCTRLピンが最初に“L” レベルから“H”レベルに遷移した時から開始します。 ICは上記の3つの条件を満足すると直ちに1線式のモードにな ります。EasyScale通信は検出ウィンドウの経過前に始めるこ とができます。一旦1線式調光制御モードがプログラムされる と、別のモード設定方法で再起動させない限り変更することは できません。このことはICのCTRLピンを2.5ms以上の間“L”レ ベルにすることでシャットダウンし、次に再起動させることが必 要であることを意味しています。グラフでの説明としてフィード バック基準電圧プログラムのモード選択の図(図12)を参照し てください。PWM調光モード

CTRLピンが常に“H”レベルの時、FB電圧は標準で200mV にレギュレーションされています。しかしながら、CTRLピン によりPWM信号を供給する事によりこのレギュレーション電 圧を低減することができ、これによりLEDの輝度を調光するこ とができます。デューティ・サイクルとFB電圧の関係は式(2) で求められます。 但し、 Duty = PWM信号のデューティ・サイクル 200mV = 内部基準電圧 図13に示されているように、ICは200mVの内部基準電圧を PWM信号のデューティ比で細かく分割します。次に、このパ ルス信号は内部のローパス・フィルタでフィルタをかけられま す。フィルタの出力はFBピンのレギュレーション用の基準電 圧として誤差増幅器に入力されます。これにより、輝度調光に PWM信号が使われたとしても、白色LEDの直流電流値が変更 されるので、アナログ調光として扱われます。この方式は、 LED電流がPWM制御の周波数とデューティサイクルのコピー となる電流パルスにより、時として発生する可聴域のノイズを 除去することができます。異なった方式によりアナログ調光の ためにPWM信号をフィルタする方式と違って、TPS61165のレ ギュレーション電圧は時として大きなバラツキが生じる原因と なるPWM信号のロジック電圧レベルの変動とは無関係となり ます。V

FB= Duty

× 200 mV

(2) VBG 200 mV CTRL Error Amplifer FB 図 13. PWM信号によるFB電圧の設定のブロック図EasyScale

TM

:1線式デジタル調光

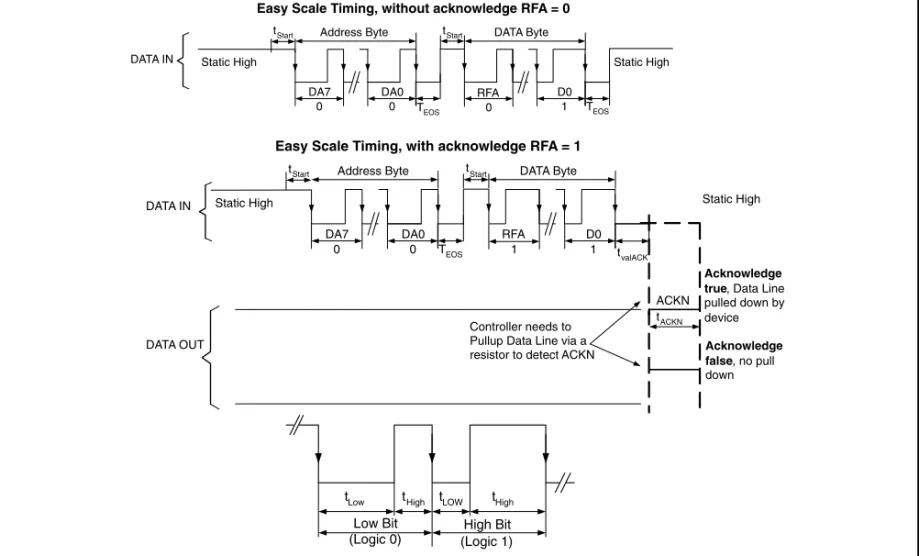

EasyScaleは単純であるにもかかわらず高い柔軟性をもってお り、1ピンのインターフェイスでFB電圧を設定することができま す。このインターフェイスはマスター/スレーブ構成に基づいて おり、マスターがマイクロコントローラやアプリケーション・プ ロセッサであるのが一般的です。図14と表2にプロトコルの概 要を示します。プロトコルはデバイス特有のアドレス・バイトと データ・バイトにより構成されています。デバイス特有のアドレ ス・バイトは72(16進)固定です。データ・バイトは情報用の5ビッ ト、アドレスの2ビット、RFAの1ビットで構成されています。 RFAビットが“H”レベルにセットされていると、“認証”の応 答が要求されます。“認証”の応答は、プロトコルが正しく受 信された場合のみ適用されます。EasyScaleTMの利点は、他の 1ピンのインターフェイスに比べて、そのビット検出がビット転 送レートにほとんど依存していないということです。これは1.7 kビット/秒から160kビット/秒間のビット・レートを自動的に検 出することができます。 9 29 0 1 0 0 1 10 32 0 1 0 1 0 11 35 0 1 0 1 1 12 38 0 1 1 0 0 13 44 0 1 1 0 1 14 50 0 1 1 1 0 15 56 0 1 1 1 1 16 62 1 0 0 0 0 17 68 1 0 0 0 1 18 74 1 0 0 1 0 19 80 1 0 0 1 1 20 86 1 0 1 0 0 21 92 1 0 1 0 1 22 98 1 0 1 1 0 23 104 1 0 1 1 1 24 116 1 1 0 0 0 25 128 1 1 0 0 1 26 140 1 1 0 1 0 27 152 1 1 0 1 1 28 164 1 1 1 0 0 29 176 1 1 1 0 1 FB voltage D4 D3 D2 D1 D0 (mV) 0 0 0 0 0 0 0 1 5 0 0 0 0 1 2 8 0 0 0 1 0 3 11 0 0 0 1 1 4 14 0 0 1 0 0 5 17 0 0 1 0 1 6 20 0 0 1 1 0 7 23 0 0 1 1 1 8 26 0 1 0 0 01線式デジタル制御輝度調光

CTRLピンはデジタル制御で輝度をコントロールする簡素な デジタル・インターフェイス機能をもっています。デジタル調 光は、PWM信号を常に必要とはしないため、プロセッサの電 力を節約することができバッテリーでの稼働時間を延ばしま す。また、プロセッサは可能であればアイドル・モードになる こともできます。 TPS61165は、単一のコマンドを用いてFB電圧を32ステップ のうちのいずれかにプログラムすることができるEasyScaleTM プロトコルを採用しています。ステップの増加に対する電圧増 加は輝度のステップに対応させる為に擬似対数カーブで増加し ます。FBピンの電圧ステップについては表1を参照してくださ い。デバイスが最初にイネーブルになった時のデフォルト値は フル・スケールです(VFB = 1.229V)。電源リセットによりレジ スタ値はクリアされ、デフォルト値にリセットされます。DATA IN

Start

DATA OUT ACK

RFA A1 A0 D4 D3 D2 D1 D0 DA7 0 DA6 1 DA5 1 DA4 1 DA3 0 DA2 0 DA1 1 DA0 0

Device Address DATABYTE

EOS Start EOS

Start

図 14. EasyScaleTM プロトコル概要

7 (MSB) RFA Request for acknowledge. If high, acknowledge is applied by device

6 A1 0 0 Address bit 1 5 A0 Address bit 0 4 D4 Data bit 4 Data byte IN 3 D3 Data bit 3 2 D2 Data bit 2 1 D1 Data bit 1 0 (LSB) D0 Data bit 0

Acknowledge condition active 0, this condition will only be applied in case RFA bit is set. Open drain output, Line needs to be pulled high by the host with a pullup ACK OUT

resistor. This feature can only be used if the master has an open drain output stage. In case of a push pull output stage Acknowledge condition may not be requested!

BIT TRANSMISSION

BYTE NUMBER NAME DIRECTION 説 明

7 DA7 0 MSB device address

6 DA6 1 5 DA5 1 Device 4 DA4 1 Address IN Byte 3 DA3 0 72 hex 2 DA2 0 1 DA1 1

0 DA0 0 LSB device address

Low Bit (Logic 0)

High Bit (Logic 1) tLow tHigh tLOW tHigh

Easy Scale Timing, without acknowledge RFA = 0

DA7 0 tStart

Static High Static High DATA IN tStart TEOS TEOS DA0 0 RFA 0 D0 1 Address Byte DATA Byte

Easy Scale Timing, with acknowledge RFA = 1

Static High

tACKN

Acknowledge true, Data Line

pulled down by device DATA IN

DATA OUT Acknowledge

false, no pull

down Controller needs to

Pullup Data Line via a resistor to detect ACKN

ACKN DA7 0 Static High TEOS tvalACK DA0 0 RFA 1 D0 1 tStart t Start

Address Byte DATA Byte

図 15. EasyScaleTM ビット符号化 全てのビットはMSB先頭/LSB最終で転送されます。図15に 認証要求がない場合のプロトコル(ビットRFA = 0)、図15に認 証要求がある場合のプロトコル(ビットRFA = 1)を示します。 デバイス・アドレス・バイトとデータ・バイトの両方のバイトの 前に、スタート状態を作らなければなりません。このためには、 CTRLピンはビット転送が立下がりエッジで開始する前に少な くともtstart(2µs)の間“H”レベルにしておかなければなりま せん。CTRLピンが既に“H”レベルである場合は、デバイス のアドレス・バイトの前にスタート状態は必要ありません。各 バイトの送信は、少なくともtEOS(2µs)間のエンド・オブ・スト リーム状態で終了します。 ビットの検出はtLOWとtHIGHの関係に基づいた論理検出体系 によって行われます。これは以下のように簡素化することがで きます。

“H”レベル・ビット:tHIGH> tLOWで、tHIGHが tLOWの 2倍より大。図15参照。

“L”レベル・ビット:tHIGH< tLOWで、tLOWがtHIGHの 2倍より大。図15参照。 ビットの検出はCTRLピンの立ち下がりエッジで開始し、次の 立ち下がりエッジで終了します。tHIGHとtLOWの関係により、0 または1が検出されます。 認証は以下の場合にのみ出力されます。 • 認証がRFAビットの設定により要求された。 • 転送されたデバイス・アドレスがデバイスのデバイス・アド レスに一致した。 この認証状態は、内部遅延時間tvalACKの後に有効になります。 このことは、プロトコルの最後の立ち下がりエッジが検出され てからtvalACKの後、内部のACKN-MOSFETがオンになるとい うことを意味しています。マスター・コントローラはこの間ラ インを“L”レベルに保持します。マスター・デバイスはtvalACK 後CTRLピンを解放して入力に設定することによりロジック0を 読み込み、認証状態を検出することができます。CTRLピンは認 証状態が終了した後再び使用可能になります。 認証はマスター・デバイスがオープン・ドレイン出力をもって いる場合にのみ要求することができることに注意してくださ い。プッシュプル出力段については、以下の場合などのために、 電流を500µAに制限するためCTRLラインに直列に抵抗を接続 することを推奨します。 • 誤って認証要求をした、または • 内部のACKN-MOSFETを保護するため

低電圧ロックアウト(UVLO)

低電圧ロックアウトにより入力電圧が標準の2.2Vより低下し た時のデバイスの作動が防止されます。入力電圧が低電圧スレッ ショルドより低い時、デバイスはシャットダウンされ内部のス イッチFETはオフになります。入力電圧が低電圧ロックアウト・ ヒステリシス電圧を超えるまで上昇するとICは再起動します。サーマル・シャットダウン

アプリケーション情報

最大出力電流

昇圧型コンバータの過電流制限により最大入力電流が制限さ れ、これにより入力された電圧における最大入力電力が制限さ れます。最大出力電力は電力変換損失により最大入力電力より 低くなります。従って、設定されている電流制限値、入力電圧、 出力電圧、効率の全てが最大出力電流を変化させます。過電流 制限はインダクタのピーク電流でクランプが動作するため、最 大直流電流を計算するためにはリップル電流を差し引くことが 必要です。リップル電流はスイッチング周波数、インダクタ値、 デューティ・サイクルの関数です。以下の式では最大出力電流 を計算するため上記の因数の全てが考慮されています。 但し、 Ip= インダクタのピーク間リップル電流 L = インダクタ値 Vf= ショットキー・ダイオードの順方向電圧 Fs = スイッチング周波数 Vout= 出力電圧 但し、 Iout_max= 昇圧型コンバータの最大出力電流 Ilim= 過電流制限値 η = 効率 例えば、Vinが3Vで8個のLEDを駆動の場合、Voutは26Vに相 当、インダクタが22µH、ショットキー・ダイオードの順方向電 圧が0.2Vの時、最大出力電流は標準条件で110mAになります。 Vinが5Vで10個のLEDを駆動の場合、Voutは32Vに相当、イン ダクタが22µH、ショットキー・ダイオードの順方向電圧が0.2V の時、最大出力電流は標準条件で150mAになります。インダクタの選択

インダクタの選択は過渡応答時の動作、ループの安定性と同 様に定常状態の動作にも影響を与えます。これらの要因により インダクタは電源レギュレータの設計においてもっとも重要な 部品となります。インダクタにはインダクタ値、直流抵抗、飽 和電流の3つの重要な仕様があります。インダクタ値のみを考 慮することでは不十分です。 インダクタ値によりインダクタのリップル電流が決まりま す。式(3)で求められるピーク・ツー・ピーク・リップル電流の半 分の値を次式で求められるインダクタ直流電流に加算し、ピー ク電流を流しても飽和する事が無いインダクタを選択します。 インダクタ値の公差は直流電流によるバイアスがない場合で ±20%です。インダクタ電流が飽和レベルに近づくと、そのイン ダクタンスはインダクタのベンダーの飽和電流の定義の仕方に もよりますが0Aでの値から20%∼35%程度減少します。小さ なインダクタンス値のインダクタを用いるとインダクタ電流が 各スイッチング・サイクルの終了前にゼロまで下降する不連続 のPWM動作となります。これにより昇圧型コンバータの最大 出力電流が低減し、大きな入力電圧リップルが発生し、効率が 低下します。大きなインダクタンス値では出力電流が増加し、 変換効率が上昇します。これらの理由から10µHから22µHの範 囲のインダクタの使用を推奨します。22µHのインダクタは多 くのアプリケーションに於いて低いピーク・ツー・ピーク・イン ダ ク タ ・ リ ッ プ ル 電 流 に よ り 高 効 率 を 実 現 し ま す 。 表 3 に TPS61165用に推奨するインダクタのリストを挙げます。推奨さ れるインダクタンス値には公称値から–40%から+20%の公差を 考慮してあります。 TPS61165は電流モード・コントロールに特有のサブハーモニッ ク発振の問題を回避するためのスロープ補償を内蔵していま す。インダクタンス値が10µHより小さいと、スロープ補償が 不足する可能性があり、ループは不安定になることがあります。 従って、インダクタンス値が推奨値と異なる場合には、そのア プリケーションとインダクタの組み合わせによる動作安定性を 検証する必要があります。+

–

+

×

×

[

]

=

)

V

1

V

V

V

1

(

F

L

1

I

in in f out s P (3)I

out_max=

Vin

×

(

I

lim– I

P/ 2

)

× η

Vout

(4)L DCR MAX SATURATION CURRENT

PART NUMBER VENDOR

(µH) (mΩ) (A) SIZE (L × W × H mm) A915_Y-100M 10 90 1.3 TOKO VLCF5020T-100M1R1-1 10 237 1.1 TDK CDRH4D22/HP 10 144 1.2 Sumida LQH43PN100MR0 10 247 0.84 5.2 × 5.2 × 3.0 5 × 5 × 2.0 5 × 5 × 2.4 4.5 × 3.2 × 2.0 Murata 表 3. TPS61165の推奨インダクタ

I

in_DC=

Vout

× Iout

ショットキー・ダイオードの選択

TPS61165はスイッチング周波数が高いため効率を最適化する には高速の整流が必要となります。ダイオードの平均及びピー クの電流定格が平均出力電流とインダクタのピーク電流よりも 確実に大きくなるように選択してください。さらに、ダイオー ドの逆降伏電圧はLED断線保護電圧より大きくなければなりま せん。よって、TPS61165用にはONSemi MBR0540やZETEX ZHCS400が推奨されます。補償用コンデンサの選択

COMPピンとGNDの間に接続される補償用コンデンサC3(ブ ロック図を参照)はTPS61165の負帰還ループの安定性を確保する 為に使用します。C3には220nFのセラミックコンデンサを使用し てください。入力/出力コンデンサの選択

出力コンデンサは主に出力リップルとループの安定性の要求 に適合するよう選択されます。このリップル電圧はコンデンサ の容量とその等価直列抵抗(ESR)に関連しています。コンデン サのESRがゼロであると仮定すると、あるリップルに対し必要 とされる最小容量は以下の式で計算することができます。 但し、Vrippleはピーク間出力リップル電圧です。ESRにより生 じる追加の出力リップル成分は以下の式を用いて計算されます。 セ ラ ミ ッ ク ・ コ ン デ ン サ の 場 合 E S R が 低 い こ と に よ り Vripple_ESRは無視することができますが、タンタルまたは電解 コンデンサが用いられる場合にはこれを考慮しなければなりま せん。 セラミック・コンデンサを評価する際には、直流バイアス、経 年変化、交流信号による容量減少に注意を払わなければなりま せん。例えば、大きな寸法のコンデンサ(1206サイズ)では共振 周波数はスイッチング周波数程度です。よって、実効容量はか なり低くなります。また、直流バイアスにより容量は大きく低 下します。セラミック・コンデンサはその定格電圧の直流電圧の 印加で容量が50%以下まで減少することがあります。この為、 必要な出力電圧において充分な容量が確保されるように耐圧に は充分なマージンを見込んでおきます。 図 16. Layout Recommendation CTRL GND C3 L1 Rset Vin CTRL SW FB COMP GND C1 Vin C2 LEDs IN LEDs Out Minimize the area of this trace Place enough VIAs around thermal pad to enhance thermal performance 入力側には1µF∼4.7µFのコンデンサを推奨します。出力には 1µF∼10µFのコンデンサが必要とされます。出力コンデンサは昇 圧型レギュレータのループ安定性に影響を与えます。出力コン デンサ容量がこの範囲より少ないと昇圧型レギュレータは不安 定になる可能性があります。 大容量値セラミック・コンデンサで良く知られているベンダー は以下のとおりです。 TDK(http://www.component.tdk.com/components.php) Murata(http://www.murata.com/cap/index.html)レイアウトについての考察

すべてのスイッチング電源、特に高周波数及び大電流で動作 する製品のレイアウトは電源設計の重要な設計ステップとなり ます。レイアウトが注意深く行われていないと、レギュレータ はノイズの問題はもとより不安定性にも見舞われることがあり ます。効率を最大限にするには、SWピンの立ち上がり/立ち下 がり時間をできるだけ短くします。高周波共振による電磁波放 射(EMI)の問題を防ぐには、高周波のスイッチング・パスを適切 にレイアウトすることが不可欠です。SWピンに接続されるすべ ての配線の長さと配線によるループ面積を最小限にし、内層プ レーンとの結合を最小限に抑えるためスイッチング・レギュレー タの直下に必ずグランド・プレーンを配置してください。PWM スイッチ、ショットキー・ダイオード、出力コンデンサによって 作られる出力側ループでの大電流の立ち上がり/立ち下がり時間 はナノ秒単位なので、パス長はできるだけ短くしておかなけれ ばなりません。ICに供給される電源のリップルを低減するため、 入力コンデンサはVINピンだけでなく、GNDピンにも近づけて 配置する必要があります。図16にレイアウトの実例を示します。C

out=

(

V

out– V

in)

I

outV

out× Fs × V

ripple (6)ADDITIONAL TYPICAL APPLICATIONS

図 17. Drive 3 High Brightness LEDs With External PWM Dimming Network

図 18. Drive 27 LEDs for Media Form Factor Display

VIN 3 V to 6 V D1 VIN SW FB GND CTRL COMP C2 1 Fµ TPS61165

L 1 : TOKO # A915_ Y-100 M C 1 : Murata GRM188 R61A475 K C 2 : Murata GRM188 R61E105 K D 1 : ONsemi MBR0540T 1 3s9p 27LEDs ON /OFF DIMMING CONTROL L1 10 Hµ Rset 1.1Ω C1 4.7 Fµ C3 220 nF VIN 5V D1 VIN SW FB GND CTRL COMP C3 220 nF TPS 61165 L 1 : TOKO #A 915 _Y-100M C1 : Murata GRM188R61 A475K C2 : Murata GRM188R61 E105K D1 : ONsemi MBR 0540 T1 LED : OSRAM LW -W 5SM ON/OFF PWM Signal: 1.8V ; 200 Hz LED current =1.8V x (1-d) / (8x Rset)

10 kΩ L1 10 Hµ C2 1 Fµ Rset 0.64Ω C1 4.7 Fµ 80 kΩ 0.1 Fµ 100 kΩ

熱についての考察

ICの最大接合部温度は標準動作条件下で125°Cに制限されな ければなりません。この制限によりTPS61165の消費電力が制 限されます。最大許容消費電力PD(max)を計算し、実際の消費 電力をPD(max)以下に保持してください。最大消費電力の制限 値は式(8)を用いて決まります。 但し、TAはアプリケーションでの最大周囲温度で、RθJAは消 費電力表で与えられている接合部/周囲間の熱抵抗です。 TPS61165は放熱特性に優れたQFNパッケージで供給されて います。このパッケージにはパッケージの放熱能力を改善する サーマル・パッドが使用されています。QFNパッケージのRθJAは PCBのレイアウトとサーマル・パッドの接続に大きく依存しま す。サーマル・パッドはPCBのアナログ・グランドにはんだ付け しなければなりません。レイアウト例に図示されているように サーマル・パッドの底面にサーマル・ビアを用います。QFN/SON PCB Attachmentアプリケーション・レポート(SLUA271)も参照し てください。P

D(max)=

125

°C – T

AR

θJA (8)D1 Rset 0.57Ω VIN SW FB GND CTRL COMP 350 mA C3 220 nF TPS 61165 L1: TOKO #A915_Y-100M C1: Murata GRM188R61A475K C2: Murata GRM188R61E105K D1: ONsemi MBR0540T1 LED: OSRAM LW-W5SM ON/OFF DIMMING CONTROL VIN 12 V L1 10 Hµ C2 1 Fµ C1 4.7 Fµ

図 19. Drive 6 High Brightness LEDs

図 20. Drive 4 High Brightness LED With SEPIC Topology

VIN 9V to 15V D1 Rset 1.1Ω VIN SW FB GND CTRL COMP VOUT= 12 V C3 220 nF TPS 61165 L1, L2: TOKO #A915_Y-100M C1: Murata GRM188 R61A475 K C2: Murata GRM188 R61E105K C4: Murata GRM188 R61H105 K D1: ONsemi MBR0540T1

*L1,L2 can be replaced by 1:1 transformer ON/OFF DIMMING CONTROL 180 mA L1 10 Hµ C1 4.7 Fµ C2 1 Fµ L2 10 Hµ C4 1 Fµ

Orderable Device Status (1) Package Type Package Drawing

Pins Package Qty Eco Plan (2) Lead/

Ball Finish MSL Peak Temp

(3) Samples (Requires Login) TPS61165DBVR ACTIVE SOT-23 DBV 6 3000 Green (RoHS

& no Sb/Br)

CU NIPDAU Level-1-260C-UNLIM Request Free Samples

TPS61165DBVT ACTIVE SOT-23 DBV 6 250 Green (RoHS & no Sb/Br)

CU NIPDAU Level-1-260C-UNLIM Contact TI Distributor or Sales Office TPS61165DRVR ACTIVE SON DRV 6 3000 Green (RoHS

& no Sb/Br)

CU NIPDAU Level-2-260C-1 YEAR Request Free Samples

TPS61165DRVRG4 ACTIVE SON DRV 6 3000 Green (RoHS & no Sb/Br)

CU NIPDAU Level-2-260C-1 YEAR Request Free Samples

TPS61165DRVT ACTIVE SON DRV 6 250 Green (RoHS & no Sb/Br)

CU NIPDAU Level-2-260C-1 YEAR Contact TI Distributor or Sales Office TPS61165DRVTG4 ACTIVE SON DRV 6 250 Green (RoHS

& no Sb/Br)

CU NIPDAU Level-2-260C-1 YEAR Contact TI Distributor or Sales Office

パッケージ情報

製品情報

(1)マーケティング・ステータスは次のように定義されています。 ACTIVE:製品デバイスが新規設計用に推奨されています。 LIFEBUY:TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。 NRND:新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨 していません。 PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。 OBSOLETE:TIによりデバイスの生産が中止されました。(2)エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free(RoHS)、Pb-Free(RoHS Expert)およびGreen(RoHS & no Sb/Br)があります。最新情報およ び製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD:Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS):TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味しま す。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定 された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt):この部品は、1)ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2)ダイとリードフレーム間に鉛ベースの接着剤を使用、 が除外されています。それ以外は上記の様にPb-Free(RoHS)と考えられます。

Green (RoHS & no Sb/Br):TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質 な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。 (3)MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。 重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者に よって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合 するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部 材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、 CAS番号やその他の制限された情報が公開されない場合があります。 TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金 額を超える責任は負いかねます。

*All dimensions are nominal Device Package Type Package Drawing Pins SPQ Reel Diameter (mm) Reel Width W1 (mm) A0 (mm) B0 (mm) K0 (mm) P1 (mm) W (mm) Pin1 Quadrant TPS61165DBVR SOT-23 DBV 6 3000 179.0 8.4 3.2 3.2 1.4 4.0 8.0 Q3 TPS61165DBVT SOT-23 DBV 6 250 179.0 8.4 3.2 3.2 1.4 4.0 8.0 Q3 TPS61165DRVR SON DRV 6 3000 330.0 12.4 2.2 2.2 1.1 8.0 12.0 Q2 TPS61165DRVR SON DRV 6 3000 179.0 8.4 2.2 2.2 1.2 4.0 8.0 Q2 TPS61165DRVT SON DRV 6 250 180.0 12.4 2.2 2.2 1.1 8.0 12.0 Q2 TPS61165DRVT SON DRV 6 250 179.0 8.4 2.2 2.2 1.2 4.0 8.0 Q2

テープおよびリール・ボックス情報

REEL DIMENSIONS TAPE DIMENSIONS

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Pocket Quadrants

Reel Diameter

Reel Width (W1)

User Direction of Feed

Q1 Q2 Q1 Q2 Q3 Q4 Q3 Q4 K0 A0 B0 P1 Cavity A0 B0 K0 W P1

Dimension designed to accommodate the component width Dimension designed to accommodate the component length Dimension designed to accommodate the component thickness Overall width of the carrier tape

Pitch between successive cavity centers

Sprocket Holes W

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

TPS61165DBVR SOT-23 DBV 6 3000 203.0 203.0 35.0 TPS61165DBVT SOT-23 DBV 6 250 203.0 203.0 35.0 TPS61165DRVR SON DRV 6 3000 346.0 346.0 29.0 TPS61165DRVR SON DRV 6 3000 195.0 200.0 45.0 TPS61165DRVT SON DRV 6 250 190.5 212.7 31.8 TPS61165DRVT SON DRV 6 250 195.0 200.0 45.0

TAPE AND REEL BOX DIMENSIONS

パッケージ・マテリアル情報

A. 寸法はすべてミリメートルです。

B. 本図は予告なく変更することがあります。

C. ボディ寸法には、0.15mmを超えるモールド・フラッシュや突起は含まれません。

D. リード1,2,3は、パッケージ・オプションにより、リード4,5,6より幅が広くなります。 E. 最小リード幅を除き、JEDEC MO178 Variation ABに適合します。

注:

DBV(R-PDSO-G6)

PLASTIC SMALL-OUTLINE PACKAGE

A. 全ての線寸法の単位はミリメートルです。寸法と許容差はASME Y14.5M- 1994に従っています。 B. 図は予告なく変更することがあります。

C. SON(Small Outline No-Lead)パッケージ構成

D. 最良の熱特性および機械的特性を得るには、パッケージのサーマル・パッドを基板に半田付けする必要があります。

露出したサーマル・パッドの寸法に関する詳細は、製品データシートを参照してください。 注:

DRV(S-PDSO-N6)

PLASTIC SMALL OUTLINE

サーマル・パッド寸法図 注:全ての線寸法の単位はミリメートルです。

DRV(S-PWSON-N6)

サーマルパッド・メカニカル・データ

熱特性について

このパッケージには、外部ヒートシンクに直接接続するよう に設計された、露出したサーマル・パッドが装備されています。 このサーマル・パッドは、プリント基板(PCB)をヒートシンク として使用できるように、PCBに直接半田付けする必要があり ます。また、サーマル・ビアを使用して、サーマル・パッドをグ ランド・プレーンまたはPCB内に設計された特別なヒートシン ク構造に直接接続することができます。この設計により、ICか らの熱伝導が最適化されます。QFN(Quad Flatpack No-Lead)パッケージとその利点につい ては、アプリケーション・レポート『Quad Flatpack No-Lead Logic Packages』(Texas Instruments文献番号SLUA271)を参照 してください。このドキュメントは、ホームページwww.ti.com で入手できます。

このパッケージの露出したサーマル・パッドの寸法を次の図 に示します。

A. 直線寸法はすべてミリメートル単位です。 B. 本図は予告なしに変更することがあります。 C. 代替設計には、IPC–7351規格を推奨します。 D. 本パッケージは、サーマルパッドを基板に半田付けするように設計されています。具体的な熱的特性情報、 ヴィア条件、および推奨基板レイアウトについては、アプリケーション・ノート「QFNパッケージ」 テキサス・インスツルメンツ文献番号SLUA271および製品データシートも参照願います。 これらの文献はwww.ti.com < http://www.ti.com> で入手できます。 E. 台形壁面やラウンドコーナーにレーザー・カッティング・アパーチャを行うと、ペーストのリリースが 容易になります。推奨のステンシル設計については、基板組立元に問合せ願います。ステンシル設計の 検討については、IPC7525規格を参照願います。 F. 半田マスク公差については、基板製造元に問合せ願います。 注: