発行日 2007 年 5 月 24 日

MR-SHPC-01

V2-F

アプリケーションマニュアル

改訂履歴

Rev. 日付 番号 概 要 頁 1.00 2003. 3. 3 1 制 定 - 1.01 2003. 8. 12 1 カードスロット側端子、カードデータバス、端子番号 欄に71 番ピン追加 9 1.02 2003.9.2 1 2.1.2 カードスロット側 CARD_PW_GOOD の I,O,B 欄 "I"を"IPUL*"に変更 9 1.03 2003.9.18 1 誤記の為■部分は使用禁止 71、721.04 2004.3.31 1 「7.11 Word to Byte 機能」において MODE1 の場合

は使用禁止 68 1.05 2004.8.30 1 SH3システム AC タイミング内 Write Data タイミン グを改訂 83 1.05 2004.8.30 2 ライトデータ遅延時間(t16a,t16b)をセットアップ時間へ変更 85 1.06 2007.5.24 1 ENDIAN 端子を bit13⇒bit14 へ修正 19

目 次

1.概 要··· 7 1.1 概 要··· 7 1.2 特 徴··· 7 2.端 子··· 8 2.1 端子機能一覧··· 8 2.1.1 システム側端子··· 8 2.1.2 カードスロット側端子··· 9 2.2 端子配置···10 3.回路構成図···15 4.制御レジスタ···16 4.1 制御レジスタ機能一覧表···16 4.2 レジスタ機能 ···17 4.2.1 モードレジスタ···17 4.2.2 オプションレジスタ···18 4.2.3 カードステータスレジスタ···19 4.2.4 割り込み要因レジスタ···20 4.2.5 割り込み制御レジスタ1/2···21 4.2.5 割り込み制御レジスタ2/2···22 4.2.6 カード電源制御レジスタ1/2···23 4.2.6 カード電源制御レジスタ2/2···24 4.2.7 メモリウィンドウ0コントロールレジスタ1···25 4.2.8 メモリウィンドウ1コントロールレジスタ1···26 4.2.9 I/Oウィンドウコントロールレジスタ1···27 4.2.10 メモリウィンドウ0コントロールレジスタ2···28 4.2.11 メモリウィンドウ1コントロールレジスタ2···29 4.2.12 I/Oウィンドウコントロールレジスタ2···30 4.2.13 カードコントロールレジスタ···31 4.2.14 PCIC情報レジスタ···32 5 モード設定···33 5.1 概 要···33 5.2 モードレジスタ設定方法···33 5.3 機能説明···346 システムメモリ空間···36 6.1 レジスタ空間···36 6.1.1 機 能···36 6.1.2 レジスタ空間マッピング例···36 6.2 メモリ,I/O空間···37 6.2.1 機 能···37 6.3 ウィンドウ空間···38 6.3.1 機 能···38 6.3.2 ライト・アクセス···38 6.3.3 リード・アクセス···39 7.機能・動作···40 7.1 SH CPU I/F···40 7.1.1 概 要···40

7.1.2 MODE0 基本4×CKIOサイクル(No WAIT) ···40

7.1.3 MODE1 基本 5×CKIOサイクル(No WAIT) ···41

7.1.4 MODE0 基本 4×CKIOサイクル(1WAIT) ···42 7.1.5 MODE1 基本 5×CKIOサイクル(1WAIT) ···43 7.2 レジスタ機能···44 7.2.1 概 要···44 7.2.2 レジスタ構造···44 7.3 リード バッファ···45 7.3.1 概 要···45 7.3.2 リードバッファ動作···46 7.3.3 リードバッファHit条件···47 7.4 割り込み···48 7.4.1 割り込み要求選択機能···48 7.4.2 割り込み基本動作···51 7.5 カード電源制御···53 7.5.1 概 要···53 7.5.2 カード電源制御回路構成···53 7.5.3 カード電源制御···53 7.5.3 カード電源制御···54 7.5.4 CARD_PW_GOOD端子条件···55 7.6 省電力モード···56 7.6.1 概 要···56 7.6.2 機能制約···56

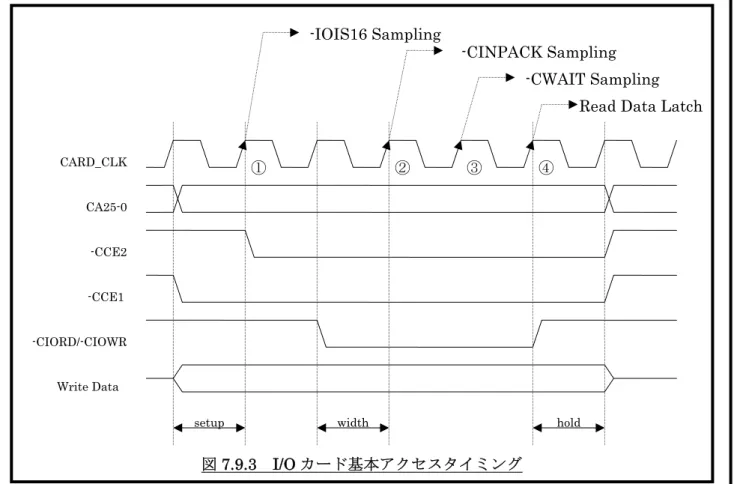

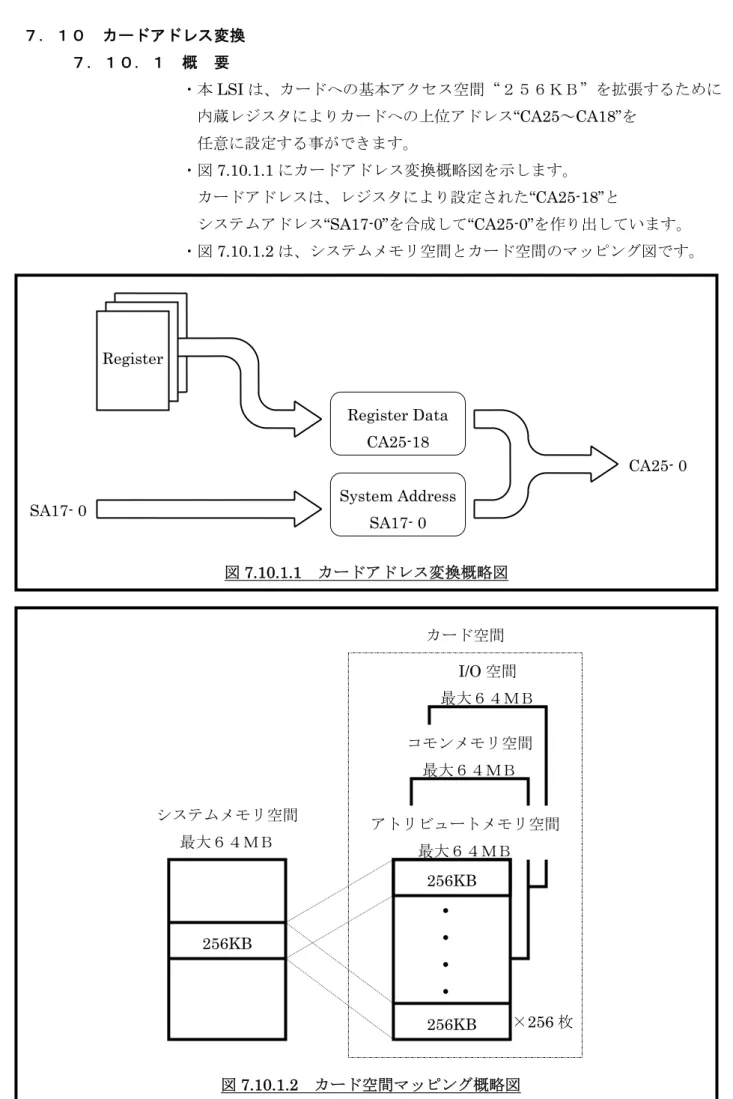

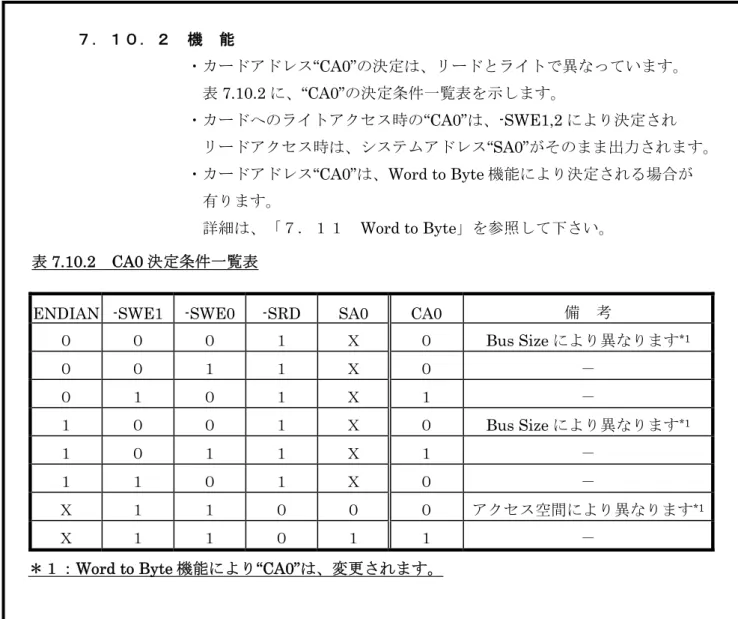

7.7 LED,スピーカー···60 7.7.1 概 要···60 7.7.2 LED ···60 7.7.3 スピーカー···61 7.8 TEST モード···61 7.8.1 概 要···61 7.8.2 モード内容···61 7.9 カード I/F···63 7.9.1 概 要···63 7.9.2 基本メモリサイクル···63 7.9.3 基本I/Oサイクル ···64 7.10 カードアドレス変換···66 7.10.1 概 要···66 7.10.2 機 能···67 7.11 WORD TO BYTE機能···68 7.11.1 概 要···68 7.11.2 メモリカード Word to Byte動作···68

7.11.3 I/Oカード Word to Byte動作 ···69

7.12 カード I/F端子制御 ···70 7.12.1 概 要···70 7.12.2 動 作···70 7.13 データ変換制御···71 7.13.1 システムライトデータ -> カードデータ変換一覧表···71 7.13.2 カードリードデータ -> システムデータ変換一覧表···72 8. DC特性···73 8.1 最大定格···73 8.1.1 入力電圧特性(CVIN)対応端子名···73 8.1.2 入力電圧特性(SVIN)対応端子名···73 8.1.3 出力電圧特性(CVOUT)対応端子名 ···73 8.1.4 出力電圧特性(SVOUT)対応端子名···73 8.2 推奨動作条件1···74 8.3 推奨動作条件2···74

8.2 推奨動作条件1···75 8.2.1 静止電流特性···75 8.2.2 入力リーク···75 8.2.3 入力特性···75 8.2.4 プルアップ抵抗···75 8.2.5 プルダウン抵抗···75 8.2.6 システム側出力特性···76 8.2.7 システム側出力特性(オープンドレイン)···76 8.2.8 カード電源制御出力特性···76 8.2.9 カード側出力特性···76 8.2.10 OFF-STATEリーク···77 8.2.11 入力端子容量···77 8.2.12 出力端子容量···77 8.2.13 入出力端子容量···77 8.3 推奨動作条件2···78 8.3.1 静止電流特性···78 8.3.2 入力リーク···78 8.3.3 入力特性···78 8.3.4 プルアップ抵抗···78 8.3.5 プルダウン抵抗···78 8.3.6 システム側出力特性···79 8.3.7 システム側出力特性(オープンドレイン)···79 8.3.8 カード電源制御出力特性···79 8.3.9 カード側出力特性···79 8.3.10 OFF-STATEリーク···80 8.3.11 入力端子容量···80 8.3.12 出力端子容量···80 8.3.13 入出力端子容量···80 9. AC特性···81 9.1 システムACタイミング···81 9.1.1 クロック・リセットタイミング波形図···81 9.1.2 クロック・リセットタイミングデータ ···81 9.1.3 SH2,SH3 システムACタイミング波形図(MODE0) ···82 9.1.4 SH3 システムACタイミング波形図(MODE1) ···83 9.1.5 SH4 システムACタイミング波形図(MODE1) ···84 9.1.6 システムACタイミングデータ···85

9.2 カードACタイミング···86 9.2.1 メモリカードACタイミング波形図 ···86 9.2.2 I/OカードACタイミング波形図···87 9.2.3 MODE0 カードACタイミングデータ···88 9.2.4 MODE1 カードACタイミングデータ···89 9.3 その他ACタイミング ···90 9.3.1 割り込み出力タイミング( パルス )···90 9.3.2 割り込み出力タイミング( レベル )···90 9.3.3 割り込み出力タイミング( IREQ ) ···90 9.3.4 割り込み出力タイミング( STSCHG )···90 9.3.5 スピーカー出力タイミング( ハード )···91 9.3.6 スピーカー出力タイミング( ソフト )···91 9.3.7 LED出力タイミング( ハード )···91 9.3.8 LED出力タイミング( ソフト )···91 9.3.9 電源制御出力1タイミング···92 9.3.10 電源制御出力2タイミング···92 9.3.11 その他 出力ACタイミングデータ ···93 10. パッケージ外形図···94 注意事項···96

1.概 要

1.1 概 要

・本

LSI は、PC Card Standard97 標準規格に準拠した IC メモリ カード及び

I/O カードとシステムをインターフェイスするコントローラです。

SH バスに本 LSI を接続する事により、PC カード゙対応システム構築する事が

可能です。

・本

LSI は、1個のカードスロットに対応しています。

・パッケージは、

144 ピン薄形フラット パッケージを使用しています。

1.2 特 徴

・PC Card Standard97 標準規格に準拠 した 68 ピン カードスロット一個に対応

・SH2,3,4 バス プロトコル 対応( 16bit Data Bus Mode Only )

・2枚のメモリウィンドウと1枚の I/O ウィンドウを内蔵

・カードアクセスタイミング調整機能内蔵

・1段のリード

/ライトバッファを内蔵

・エンディアン制御回路内蔵

・

5.0V/3.3V カード対応

・外付けバッファ不要

・割り込みステアリング機能内蔵

・パワーダウン機能内蔵

・サスペンド機能内蔵

2.端 子

2.1 端子機能一覧

2.1.1 システム側端子

端子名 I,O,B* 機能・備考 端子番号 リセット時 IOL/IOH ** 電 源 I/F レベル

SA25 ~ SA0 I システム アドレス バス 94,95,96,97,98, 99,100,101,102, 103,104,105,106, 107,108,110,111, 112,113,114,115, 116,117,118,119, 120 - - SVCC LVTTL SD15 ~ SD0 B システム データ バス 122,123,124,125, 126,128,129,130, 132,133,134,135, 136,137,138,139 Hi-Z 6mA/-6mA SVCC LVTTL -BS I バスストローブ 信号 6 - - SVCC LVTTL -CS I チップセレクト信号 7 - - SVCC LVTTL -SRD I リード信号 3 - - SVCC LVTTL -SWE0 I ライト信号0 4 - - SVCC LVTTL -SWE1 I ライト信号1 5 - - SVCC LVTTL

-WAIT/-RDY TO ウエイト要求信号/レディー信号 84 Hi-Z 12mA/-12mA SVCC -

SIRQ3 ~ 0 O 割り込み要求信号 141,142,143,144 Hi-Z 6mA/-6mA SVCC -

SPKR_OUT TO スピーカー信号 82 Hi-Z 6mA/-6mA SVCC -

LED_OUT OD LED 点灯用信号 83 Hi-Z 12mA/ - SVCC -

CKIO I システム クロック 91 - - SVCC LVTTL

-RESET I システム リセット信号 2 - - SVCC LVTTL

・システム側設定端子

端子名 I,O,B 機能・備考 端子番号 リセット時 IOL/IOH ** 電 源 I/F レベル

RA25 ~ RA22 I レジスタ上位アドレス設定信号 86,87,88,89 - - SVCC LVTTL ENDIAN I ENDIAN 設定信号 *詳細は、「7.13 データ変換制御」を 参照して下さい。 93 - - SVCC LVTTL TEST IPD テストピン 85 - - SVCC LVTTL

2.1.2 カードスロット側端子

端子名 I,O,B* 機能・備考 端子番号 リセット時 IOL/IOH 電 源 I/F レベル

CA25 ~ CA0 TO* カード アドレス バス 51,49,47,45,42,

40,38,35,33,44, 46,36,34,48,28, 24,30,32,50,52, 54,58,60,62,65, 67 Hi-Z 8mA/-8mA CVCC - CD15 ~ CD0 B PD* カード データ バス 23,20,17,15,12, 75,72,71,70,19, 16,13,11,9,74,69 Hi-Z 8mA/-8mA CVCC TTL

-CCE2 TO* カード イネーブル 上位バイト 25 Hi-Z 8mA/-8mA CVCC -

-CCE1 TO* カード イネーブル 下位バイト 21 Hi-Z 8mA/-8mA CVCC -

-CIORD TO* カード I/O リード信号 29 Hi-Z 8mA/-8mA CVCC -

-CIOWR TO* カード I/O ライト信号 31 Hi-Z 8mA/-8mA CVCC -

-COE TO* カード アウトプット イネーブル 26 Hi-Z 8mA/-8mA CVCC -

-CWE_PGM TO* カード ライト イネーブル 39 Hi-Z 8mA/-8mA CVCC -

CBVD2_SPKR I PU* バッテリ電圧検出2,スピーカー 66 - - CVCC TTL

CBVD1_STSCHG I PU* バッテリ電圧検出1,ステータス検出 68 - - CVCC TTL

-CCD2 I PUL* カード検出2 77 - - SVCC LVTTL

-CCD1 I PUL* カード検出1 10 - - SVCC LVTTL

CRDY_BSY_IREQ I PU* Ready/Busy,割り込み要求 41 - - CVCC TTL

-CREG TO* メモリエリア選択信号 64 Hi-Z 8mA/-8mA CVCC -

-CWAIT I PU* カード ウエイト 要求 59 - - CVCC TTL

CWP_XIOIS16 I PU* ライトプロテクト,16bit サイクル要求 76 - - CVCC TTL

CRESET TO* カード リセット 57 Hi-Z 8mA/-8mA CVCC -

-CINPACK I PU* リードデータ制御信号 61 - - CVCC TTL

-CVS2 I PUL* カード 電源電圧検出2 53 - - SVCC LVTTL

-CVS1 I PUL* カード 電源電圧検出1 27 - - SVCC LVTTL

・カード電源制御用端子

端子名 I,O,B 機能・備考 端子番号 リセット時 IOL/IOH 電 源 I/F レベル

CARD_PW_GOOD I PUL* カード電源投入終了検出 8 - - SVCC LVTTL

-CVCC3 O カード スロット +3.3V 電源制御 80 1 2mA/-2mA SVCC -

-CVCC5 O カード スロット +5.0V 電源制御 81 1 2mA/-2mA SVCC -

CVPP1 O カード スロット VPP1 電源制御 78 0 2mA/-2mA SVCC -

2.2 端子配置

端子配列一覧表 1/5

PIN No PIN Name I/O/pw 論 理 Input Level Pull Up/Pull Down IOL/IOH(mA)

1 GND PW - - - - 2 -RESET I 負 LVTTL - - 3 -SRD I 負 LVTTL - - 4 -SWE0 I 負 LVTTL - - 5 -SWE1 I 負 LVTTL - - 6 -BS I 負 LVTTL - - 7 -CS I 負 LVTTL - -

8 CARD_PW_GOOD I 正 LVTTL System Vcc Pull Up -

9 CD3 B - TTL Pull Down 8* / -8* 10 -CCD1 I 負 LVTTL System Vcc Pull Up - 11 CD4 B - TTL Pull Down 8* / -8* 12 CD11 B - TTL Pull Down 8* / -8* 13 CD5 B - TTL Pull Down 8* / -8* 14 SYSTEM VCC PW - - - - 15 CD12 B - TTL Pull Down 8* / -8* 16 CD6 B - TTL Pull Down 8* / -8* 17 CD13 B - TTL Pull Down 8* / -8* 18 GND PW - - - - 19 CD7 B - TTL Pull Down 8* / -8* 20 CD14 B - TTL Pull Down 8* / -8* 21 -CCE1 O 負 - - 8* / -8* 22 CARD VCC PW - - - - 23 CD15 B - TTL Pull Down 8* / -8* 24 CA10 O - - - 8* / -8* 25 -CCE2 O 負 - - 8* / -8* 26 -COE O 負 - - 8* / -8* 27 -CVS1 I 負 LVTTL System Vcc Pull Up - 28 CA11 O - - - 8* / -8* 29 -CIORD O 負 - - 8* / -8* 30 CA9 O - - - 8* / -8* 31 -CIOWR O 負 - - 8* / -8*

端子配列一覧表 2/5

PIN No PIN Name I/O/pwr 論 理 Input Level Pull Up/Pull Down IOL/IOH(mA)

34 CA13 O - - - 8* / -8* 35 CA18 O - - - 8* / -8* 36 CA14 O - - - 8* / -8* 37 GND PW - - - - 38 CA19 O - - - 8* / -8* 39 -CWE_PGM O 負 - - 8* / -8* 40 CA20 O - - - 8* / -8*

41 CRDY_XBSY_IREQ I 負 TTL Card Vcc Pull Up -

42 CA21 O - - - 8* / -8* 43 CARD VCC PW - - - - 44 CA16 O - - - 8* / -8* 45 CA22 O - - - 8* / -8* 46 CA15 O - - - 8* / -8* 47 CA23 O - - - 8* / -8* 48 CA12 O - - - 8* / -8* 49 CA24 O - - - 8* / -8* 50 CA7 O - - - 8* / -8* 51 CA25 O - - - 8* / -8* 52 CA6 O - - - 8* / -8* 53 -CVS2 I 負 LVTTL System Vcc Pull Up - 54 CA5 O - - - 8* / -8* 55 SYSTEM VCC PW - - - - 56 GND PW - - - - 57 CRESET O 正 - - 8* / -8* 58 CA4 O - - - 8* / -8*

59 -CWAIT I 負 TTL Card Vcc Pull Up -

60 CA3 O - - - 8* / -8*

61 -CINPACK I 負 TTL Card Vcc Pull Up -

62 CA2 O - - - 8* / -8* 63 CARD VCC PW - - - - 64 -CREG O 負 - - 8* / -8* 65 CA1 O - - - 8* / -8* 66 CBVD2_SPKR I 正 TTL Card Vcc Pull Up - 67 CA0 O - - - 8* / -8*

端子配列一覧表 3/5

PIN No PIN Name I/O/pwr 論 理 Input Level Pull Up/Pull Down IOL/IOH(mA)

68 CBVD1_STSCHG I 正 TTL Card Vcc Pull Up - 69 CD0 B - TTL Pull Down 8* / -8* 70 CD8 B - TTL Pull Down 8* / -8* 71 CD1 B - TTL Pull Down 8* / -8* 72 CD9 B - TTL Pull Down 8* / -8* 73 GND PW - - - - 74 CD2 B - TTL Pull Down 8* / -8* 75 CD10 B - TTL Pull Down 8* / -8*

76 CWP_XIOIS16 I 負 TTL Card Vcc Pull Up -

77 -CCD2 I 負 LVTTL System Vcc Pull Up - 78 CVPP1 O 正 - - 2 / -2 79 CVPP0 O 正 - - 2 / -2 80 -CVCC3 O 負 - - 2 / -2 81 -CVCC5 O 負 - - 2 / -2 82 SPKR_OUT O - - - 6 / -6 83 LED_OUT O - - - 12 / - 84 -WAIT/-RDY O 負 - - 12 / -12

85 TEST I 正 LVTTL Pull Down -

86 RA25 I - LVTTL - - 87 RA24 I - LVTTL - - 88 RA23 I - LVTTL - - 89 RA22 I - LVTTL - - 90 SYSTEM VCC PW - - - - 91 CKIO I - LVTTL - - 92 GND PW - - - - 93 ENDIAN I - LVTTL - - 94 SA25 I - LVTTL - - 95 SA24 I - LVTTL - - 96 SA23 I - LVTTL - - 97 SA22 I - LVTTL - - 98 SA21 I - LVTTL - - 99 SA20 I - LVTTL - - 100 SA19 I - LVTTL - -

端子配列一覧表 4/5

PIN No PIN Name I/O/pwr 論 理 Input Level Pull Up/Pull Down IOL/IOH(mA)

102 SA17 I - LVTTL - - 103 SA16 I - LVTTL - - 104 SA15 I - LVTTL - - 105 SA14 I - LVTTL - - 106 SA13 I - LVTTL - - 107 SA12 I - LVTTL - - 108 SA11 I - LVTTL - - 109 GND PW - - - - 110 SA10 I - LVTTL - - 111 SA9 I - LVTTL - - 112 SA8 I - LVTTL - - 113 SA7 I - LVTTL - - 114 SA6 I - LVTTL - - 115 SA5 I - LVTTL - - 116 SA4 I - LVTTL - - 117 SA3 I - LVTTL - - 118 SA2 I - LVTTL - - 119 SA1 I - LVTTL - - 120 SA0 I - LVTTL - - 121 GND PW - - - - 122 SD15 B - LVTTL - 6 / -6 123 SD14 B - LVTTL - 6 / -6 124 SD13 B - LVTTL - 6 / -6 125 SD12 B - LVTTL - 6 / -6 126 SD11 B - LVTTL - 6 / -6 127 SYSTEM VCC PW - - - - 128 SD10 B - LVTTL - 6 / -6 129 SD9 B - LVTTL - 6 / -6 130 SD8 B - LVTTL - 6 / -6 131 GND PW - - - - 132 SD7 B - LVTTL - 6 / -6 133 SD6 B - LVTTL - 6 / -6 134 SD5 B - LVTTL - 6 / -6 135 SD4 B - LVTTL - 6 / -6

端子配列一覧表 5/5

PIN No PIN Name I/O/pwr 論 理 Input Level Pull Up/Pull Down IOL/IOH(mA)

136 SD3 B - LVTTL - 6 / -6 137 SD2 B - LVTTL - 6 / -6 138 SD1 B - LVTTL - 6 / -6 139 SD0 B - LVTTL - 6 / -6 140 GND PW - - - - 141 SIRQ3 O - - - 6 / -6 142 SIRQ2 O - - - 6 / -6 143 SIRQ1 O - - - 6 / -6 144 SIRQ0 O - - - 6 / -6

3.回路構成図

TEST Mode Decoder TEST Selector TEST Selector TEST チップセレクトTEST IRQ3-1/内部モニター スピーカ/内部モニター IRQ0 LED Address/-CS/-BS System Data Read/Write Command CKIO Mode 内部チップセレクト Card Address 内部Card Address Card Data Card Command Card StatusCard Power Control Card Detect

Card Write Data Card Access Command

Card Read Data Ready/Busy

Card Status Change

Card CLK モニター信号 SH I/F IRQ/SPKR 図3.1 回路構成図 System Wait/Rdy PC Card I/F Card Enable

4.制御レジスタ

4.1 制御レジスタ機能一覧表レジスタ名

アドレス

初期値

機 能

Reserved *E0h 16’hXXXX 使用不可 Reserved *E2h 16’hXXXX 使用不可 モードレジスタ *E4h 16’h0000 PCIC の動作モードを設定します。 オプションレジスタ *E6h 16’h000C オプション機能を制御します。 カードステータスレジスタ *E8h 16’h03BF カードからの入力信号をモニタできます。 割り込み要因レジスタ *EAh 16’h0000 割り込み発生要因を示します。 割り込み制御レジスタ *ECh 16’h0000 割り込み発生条件などを制御します。 カード電源制御レジスタ *EEh 16’h0000 カード電源,低消費電力モードを制御します。 メモリウィンドウ0 コントロールレジスタ1 *E0h 16’h7FC0 メモリアクセス用システムアドレス 空間を制御します。 メモリウィンドウ1 コントロールレジスタ1 *F2h 16’h7FC0 メモリアクセス用システムアドレス 空間を制御します。 I/O ウィンドウ コントロールレジスタ1 *F4h 16’h7FC0 I/Oアクセス用システムアドレス 空間を制御します。 メモリウィンドウ0 コントロールレジスタ2 *F6h 16’h0000 カードへのアクセス条件を制御します。 メモリウィンドウ1 コントロールレジスタ2 *F8h 16’h0000 カードへのアクセス条件を制御します。 I/O ウィンドウ コントロールレジスタ2 *FAh 16’h0000 カードへのアクセス条件を制御します。 カ ー ドコントロールレジス タ *FCh 16’h0000 カードモードを制御します。 チップ情報レジスタ *FEh 16’h5333 Chip Revision 注)*:上位アドレス値は、以下のようになります。 SA25-22 = RA25-22 の設定値 SA21- 8 = 3FFFh 固定値4.2 レジスタ機能

4.2.1 モードレジスタ

オプションレジスタ Address E4h

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R – 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R – 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Scratchpad Bits R/W – 0 Scratchpad Bits R/W - 0 MODE SH4 R/W - 0 MODE66 R/W - 0 Chip No Register R/W – 0 Bit 初期値 Name 説 明 5 0 MODE SH4 ・-RDY/-WAIT 信号の機能を選択します。 0:-WAIT 信号として動作 1:-RDY 信号として動作 4 0 MODE66 ・カードサイクルの基準クロック(CARD_CLK)を選択します。 0: MODE0 CKIO と1:1のクロック (CKIO = 33Mhz 以下時に選択) 1: MODE1 CKIO と1:2のクロック (CKIO = 66Mhz 時に選択) 3-0 0000 Chip No Register ・同一”CS”空間に、本 LSI を最大で16個接続することが可能です。

本LSI を識別するための”Chip No”をソフトウエアにより

自由に設定できる空間です。 (不必要な場合は、設定する必要はありません。) 注) 1.本レジスタは、必ず最初に設定(Write)して下さい。 2.本レジスタの設定前に、データ読み出しを行わないで下さい。 3.動作中又は、本LSI に搭載されている機能設定後に変更した場合誤動作する 場合があります。

4.2.2 オプションレジスタ

オプションレジスタ Address E6h

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 TEST Bit3 R/W - 0 TEST Bit2 R/W - 0 TEST Bit1 R/W - 0 TEST Bit0 R/W - 0

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Scratchpad Bits R/W - 0 Scratchpad Bits R/W - 0 Scratchpad Bits R/W - 0 Scratchpad Bits R/W - 0 SOFT SPKR DATA R/W - 1 SOFT LED DATA R/W - 1 SPKR SELECT R/W - 0 LED SELECT R/W - 0 Bit 初期値 Name 説 明 8-11 0 TEST Bit3-0 ・“TEST” 端子の入力レベルが“High”の時にモードを決定します。 0000:PC Card I/F 内部信号モニターモード SIRQ1-3 と SPKR_OUT 端子にモニター信号が 出力されます。(通常動作との併用ができます。ただしモニ ターピンにリプレスされているピンの機能は使用できません) SIRQ3 = 0: Read Buffer Hit 1:Read Buffer No Hit SIRQ2 = 0: Read Buffer Invalid 1:Read Buffer Valid SIRQ1 = 1: PCIC Start ( 0->1->0 Cycle Start ) SPKR_OUT = 0: PCIC I/F Busy 1: PCIC I/F Ready

1111:CA24-0 に内部ウィンドウの“CS”が出力されます。 (通常動作との併用はできません) 3 1 SOFT SPKR DATA ・SPKR_OUT 端子に出力するレベルを設定します。 0:SPKR_OUT 出力端子レベル “0” 1:SPKR_OUT 出力端子レベル “1” 2 1 SOFT LED DATA ・LED_OUT 端子に出力するレベルを設定します。 0:LED_OUT 出力端子レベル “0” 1:LED_OUT 出力端子レベル “Z” 1 0 SPKR SELECT ・SPKR_OUT 端子に出力する信号を選択します。 0:カード側のCBVD2_SPKR 信号。 1:Bit3:SOFT SPKR DATA。 0 0 LED SELECT ・LED_OUT 端子に出力する信号を選択します。 0:カード側のCBVD2_SPKR 信号

4.2.3 カードステータスレジスタ

カード ステータス レジスタ Address E8h

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 ENDIAN R - 0 RA25 R - 0 RA24 R - 0 RA23 R - 0 RA22 R - 0 PCIC RDY/BSY R - 1 VS2 R - 1

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 VS1 R - 1 PW ON R - 0 RDY/BSY R - 1 WPS R - 1 CD2 R - 1 CD1 R - 1 BVD2 R - 1 BVD1 R - 1 Bit 初期値 Name 説 明 14 0 ENDIAN ・“ENDIAN”端子がそのままリードされます。 0:Big Endian 1:Little Endian 13-10 0000 RA25-22 ・“RA25-22”端子がそのままリードされます。 9 1 PCIC RDY/BSY ・カードへのアクセス実行の有無を示します。 0:カードに対するアクセス実行中。 1:カードに対するアクセスはしていない。 8-7 1 VS2,1 ・“-CVS2,1”端子の値がそのままリードされます。 6 0 PW ON ・カードへの電源供給の有無を示します。 0:カードの電源は供給されていない。 1:カードの電源は供給されている。 5 1 RDY/BSY ・“CRDY_BSY_IREQ”端子がそのままリード できます。ただしI/O カードモード時はこの値は無効です。 4 1 WPS ・“CWP_XIOIS16”端子がそのままリードできます。 ただしI/O カードモード時はこの値は無効です。 3-2 1 CD2,1 ・“-CCD2,1”端子がそのままリードできます。 -CCD2 = 1, -CCD1 = 1:カード無し -CCD2 = 1, -CCD1 = 0:カード無し -CCD2 = 0, -CCD1 = 1:カード無し -CCD2 = 0, -CCD1 = 0:カードあり 1-0 1 BVD2,1 ・“CBVD2_SPKR,CBVD1_STSCHT”端子がリードできます。 CBVD2_SPKR = 1, CBVD1_STSCHT = 1:Battery Good CBVD2_SPKR = 1, CBVD1_STSCHT = 0:Battery Dead CBVD2_SPKR = 0, CBVD1_STSCHT = 1:Battery Warning

4.2.4 割り込み要因レジスタ

割り込み要因レジスタ Address EAh

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Scratchpad Bits R - 0 STSCHG/ RI R - 0 IREQ CHG R - 0 Card Power Good R - 0 CARD DETECT R - 0 RDY CHG R - 0 BAT WARN R - 0 BAT DEAD R - 0 Bit 初期値 Name 説 明 6 0 STSCHG/ RI ・I/O カードモード時に“CBVD1_STSCHG”端子が、“1->0”の 変化で“1”がセットされます。 メモリカードモード時は常に“0” 5 0 IREQ CHG ・I/O カードモード時に“CRDY_BUY_IREQ”端子が、“1->0”の 変化で“1”がセットされます。 メモリカードモード時は常に“0” 4 0 Card Power Good ・“CARD_PW_GOOD”端子が“1->0”変化で “1”がセットされます。 (VCC5,3 端子が、電源供給要求状態で“CARD_PW_GOOD”端子が “High”->“LOW”になった場合に要因をセット) 3 0 CARD DETECT ・“-CCD2,1”端子の変化により“1”がセットされます。 -CCD2,1 が“00”の状態からどちらかの端子が“1”に変化した場合。 -CCD2,1 が共に“00”になった場合 2 0 RDY CHG ・メモリカードモード時に“CRDY_BUY_IREQ”端子が、 “0->1”の変化で“1”がセットされます。 I/O カードモード時は常に“0” 1 0 BAT WARN ・メモリカードモード時に、“CBVD1_STSCHG,CBVD2_SPKR” 端子が、“10”で“1”がセットされます。 I/O カードモード時は常に“0” 0 0 BAT DEAD ・メモリカードモード時に、“CBVD1_STSCHG”端子が、“0”で “1”がセットされます。 I/O カードモード時は常に“0”

4.2.5 割り込み制御レジスタ1/2

割り込み制御 レジスタ 1 Address ECh

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 PULSE SYS IRQ R/W - 0 CARD IRQ R/W - 000 RING IRQ R/W - 000

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 MANAGEMENT IRQ R/W - 000 CPGOOD ENABLE R/W - 0 DETECT ENABLE R/W - 0 RDY ENABLE R/W - 0 BAT WAR ENABLE R/W - 0 BAT DE ENABLE R/W - 0 Bit 初期値 Name 説 明 14 0 PULSE SYS IRQ ・SIRQn 端子の出力方法を決定します。 設定可能な割り込み要因は、“カードの状態変化割り込み”に 有効です。その他の割り込み要因は、設定できません。 0:レベル割り込み 1:エッジ割り込み 13-11 000 CARD IRQ ・カードからの割り込み要求(IREQ)を SIRQ3-0 端子にステアリング します。ただしI/O カードモード時に有効。 0XX:ディセーブル 100:SIRQ0にカードからの割り込み要求を出力 101:SIRQ1にカードからの割り込み要求を出力 110:SIRQ2にカードからの割り込み要求を出力 111:SIRQ3にカードからの割り込み要求を出力 10-8 000 RING IRQ ・カードからのステータスチェンジをSIRQ3-0 端子にステアリング します。ただしI/O カードモード時に有効。 0XX:ディセーブル 100:SIRQ0にカードからの割り込み要求を出力 101:SIRQ1にカードからの割り込み要求を出力 110:SIRQ2にカードからの割り込み要求を出力 111:SIRQ3にカードからの割り込み要求を出力

4.2.5 割り込み制御レジスタ2/2 Bit 初期値 Name 説 明 7-5 000 MANAGE MENT IRQ ・カードの状態変化をSIRQ-3-0 端子にステアリングします。 0XX:ディセーブル 100:SIRQ0にカードの状態変化割り込み要求を出力 101:SIRQ1にカードの状態変化割り込み要求を出力 110:SIRQ2にカードの状態変化割り込み要求を出力 111:SIRQ3にカードの状態変化割り込み要求を出力 4 0 CPGOOD ENABLE ・カード電源変化による割り込みを有効にします。 0:ディセーブル(要因ステータスと割り込み信号をマスク) 1:イネーブル 3 0 DETECT ENABLE ・カードの挿抜割り込みを有効にします。 0:ディセーブル(要因ステータスと割り込み信号をマスク) 1:イネーブル 2 0 RDY ENABLE ・CRDY_BSY_IREQ 端子の割り込みを有効にします。 0:ディセーブル(要因ステータスと割り込み信号をマスク) 1:イネーブル I/O カードモード時は無視され、割り込みは発生しません。 1 0 BAT WAR ENABLE ・バッテリワーニング割り込みを有効にします。 0:ディセーブル(要因ステータスと割り込み信号をマスク) 1:イネーブル I/O カードモード時は無視され、割り込みは発生しません。 0 0 BAT DE ENABLE ・バッテリデッド割り込みを有効にします。 0:ディセーブル(要因ステータスと割り込み信号をマスク) 1:イネーブル I/O カードモード時は無視され、割り込みは発生しません。 ・ Management IRQ は、4.2.4 割り込み要因レジスタ bit4-0 の要因による割り込み出力を

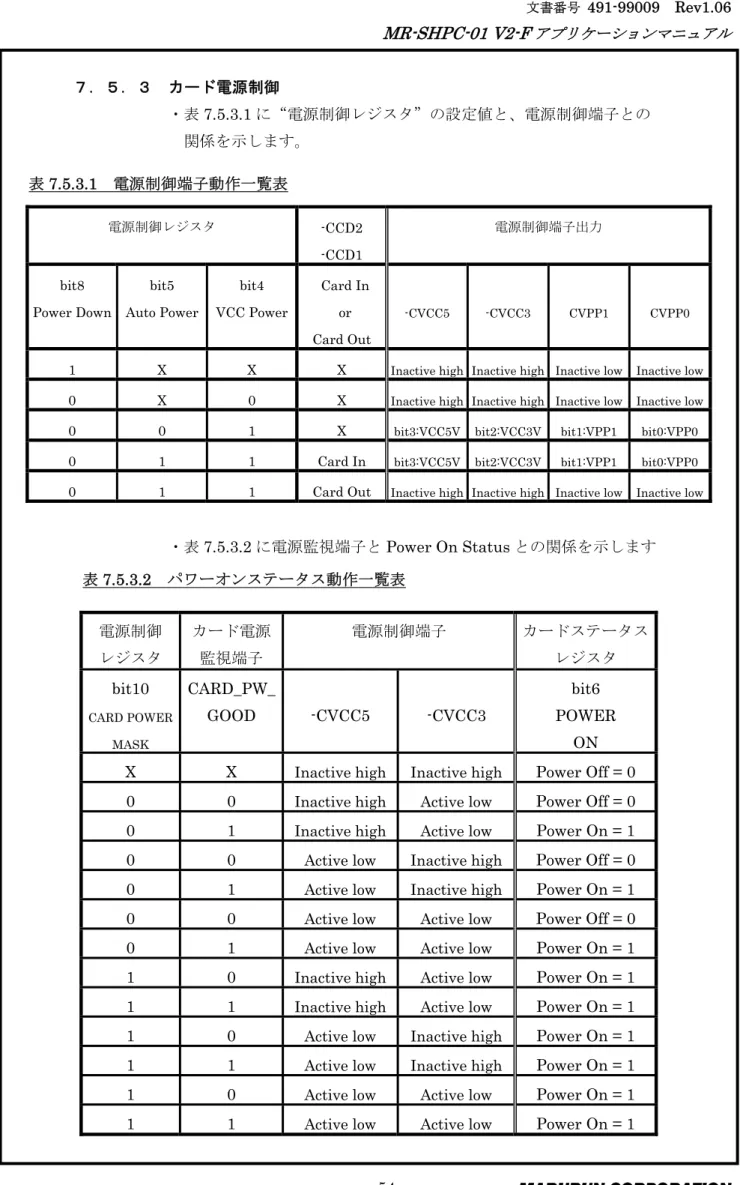

4.2.6 カード電源制御レジスタ1/2

カード 電源制御 レジスタ Address EEh

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 CardPower Mask R/W - 0 CARD RESET R/W - 0 POWER DOWN R/W - 0

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

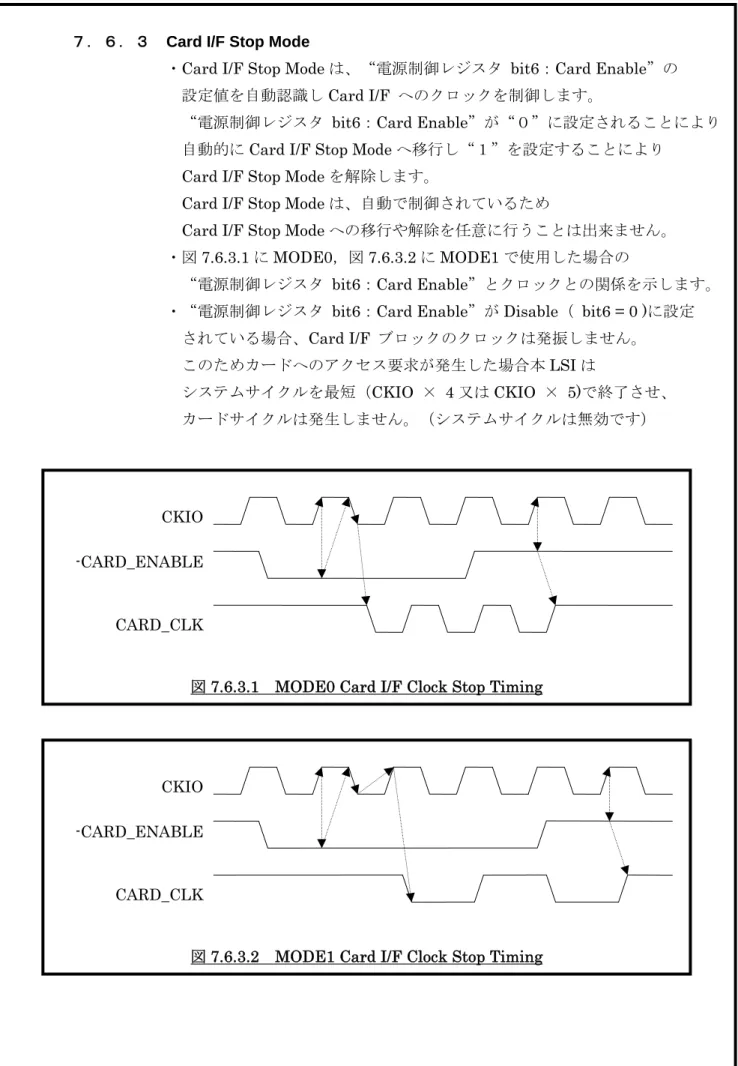

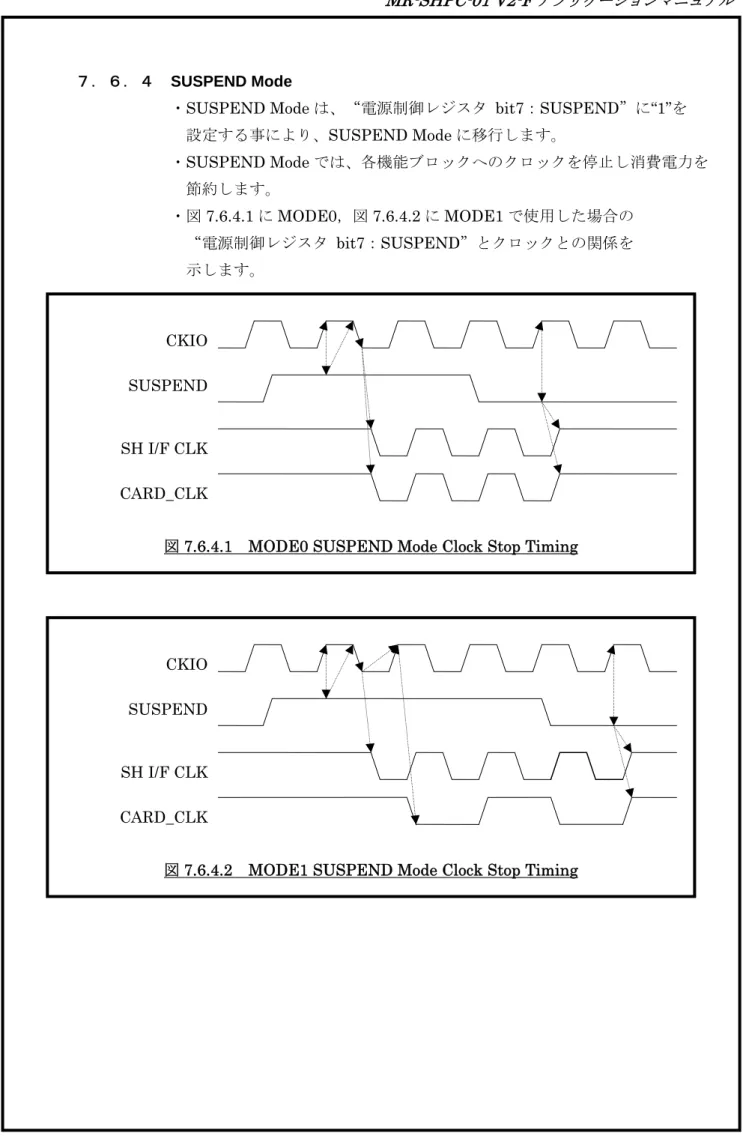

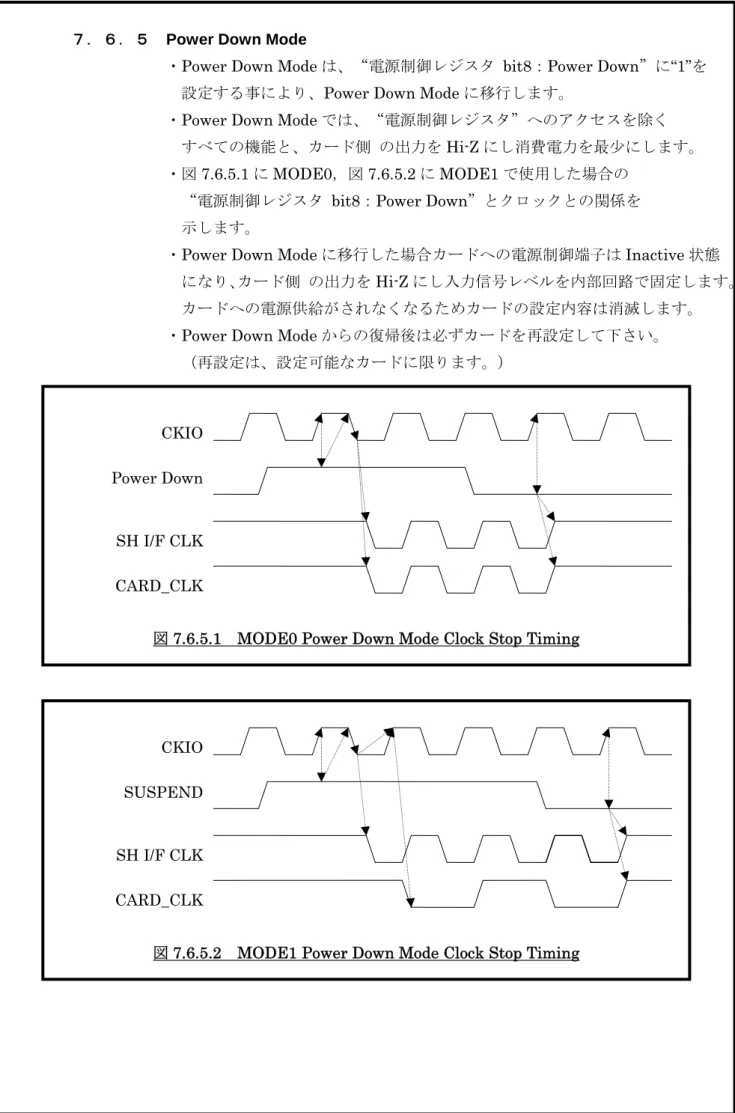

SUSPEND R/W - 0 CARD ENABLE R/W - 0 AUTO POWER R/W - 0 VCC POWER R/W - 0 VCC5V R/W - 0 VCC3V R/W - 0 VPP1 R/W - 0 VPP0 R/W - 0 Bit 初期値 Name 説 明 10 0 Card Power Mask “CARD_PW_GOOD”端子をマスクします。 0:イネーブル 1:マスク(CARD_PW_GOOD 入力信号を High 固定にします。) 9 0 CARD RESET ・カードのリセット信号を制御します。 0:カードリセットアサート 1:カードリセットネゲート カード抜去時は、クリア(初期値)されます。 8 0 POWER Down ・消費電力を最少にします。 0:通常モード 1:パワーダウンモード(内部レジスタの状態は保持されます) ① カードへの電源供給を停止します。 ② カード側出力ポートをディセーブルになります ③ 内部クロックを停止し、全機能動作を停止します。 ただし、電源制御レジスタへのアクセスは可能です 注)パワーダウンモードに移行した場合、カード内部の コンフィギュレーション値は失われます。 7 0 SUSPEND 0:通常モード 1:サスペンドモード(カード出力ポート,カード電源制御は サスペンドモードへの移行前の状態が保持されます) ① 内部クロックを停止し全機能動作を停止します。 ただし、電源制御レジスタへのアクセスは可能です ② IREQ,STSCHG信号をシステムに ステアリングする事は可能です。

4.2.6 カード電源制御レジスタ2/2 Bit 初期値 Name 説 明 6 0 CARD ENABLE ・カードへの出力信号と入力信号を制御します。 0:出力=Hi-z,入力=内部レベル固定 1:出力=出力,入力=内部レベル固定解除 カード抜去時は、クリア(初期値)されます。 5 0 AUTO POWER ・カードの挿抜検出により自動的に電源制御端子を制御します。 0:カード挿抜検出を無視し設定値(bit3-0)を出力 1:カードの挿抜検出で設定値(bit3-0)出力を制御 注1)bit4: Vcc Power が“1”に設定されている場合に カードの挿抜により設定値を出力します。 注2)CARD_PW_GOOD 端子機能を使用していない場合は 挿入検出による自動電源制御機能は使用しないで下さい。 4 0 VCC POWER ・カード電源のON/OFFを設定します。 0:OFF 1:設定値(bit3-0)を出力 注)Auto Power が設定されている場合は、カードが 挿入されている場合に設定値を出力します。 3 0 VCC5V ・“-CVCC5”端子の出力値を設定する。 “-CVCC5”端子には、設定値の反転が出力されます。 0:-CVCC5=1 1:-CVCC5=0 2 0 VCC3V ・“-CVCC3”端子の出力値を設定する。 “-CVCC3”端子には、設定値の反転が出力されます。 0:-CVCC3=1 1:-CVCC3=0 1 0 VPP1 ・“CVPP1”端子の出力値を設定する。 0:CVPP1=0 1:CVPP1=1 0 0 VPP0 ・“CVPP0”端子の出力値を設定する。 0:CVPP0=0 1:CVPP0=1

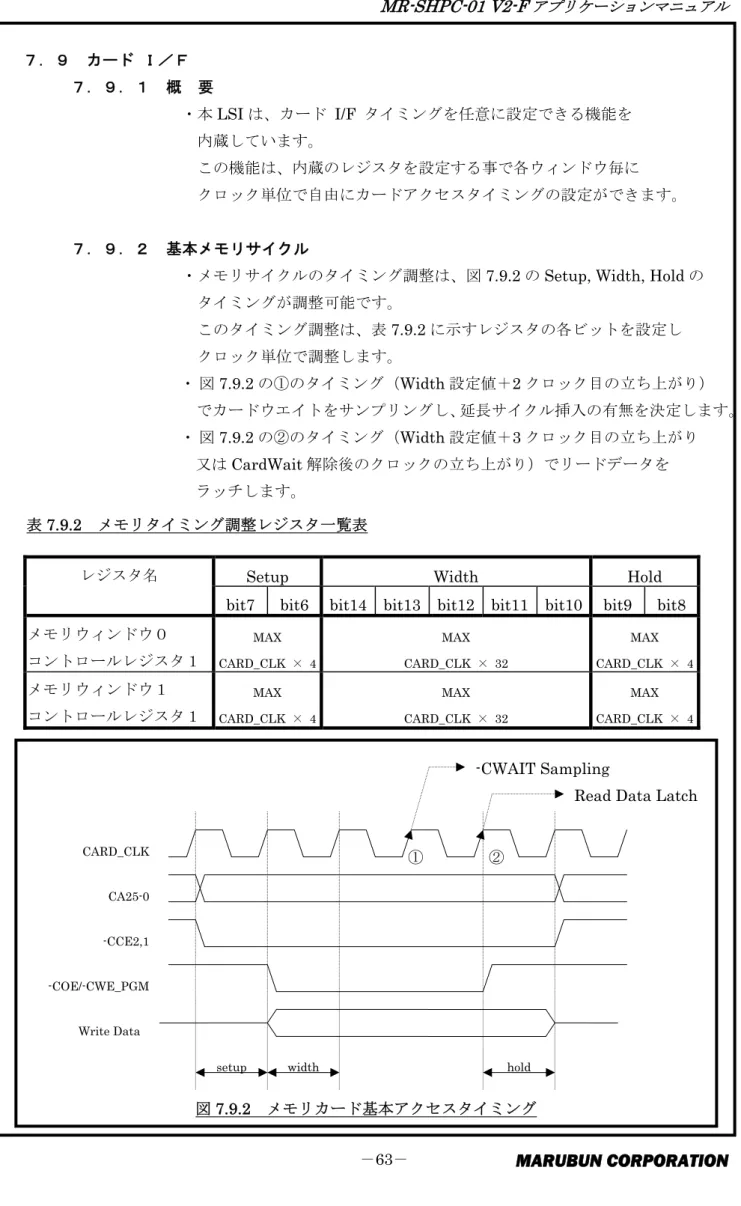

4.2.7 メモリウィンドウ0コントロールレジスタ1

メモリウィンドウ0コントロールレジスタ1 Address F0h

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

WIN EN R/W - 0 WIDTH4 R/W - 1 WIDTH3 R/W - 1 WIDTH2 R/W - 1 WIDTH1 R/W - 1 WIDTH0 R/W - 1 HOLD1 R/W - 1 HOLD0 R/W - 1 bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 SETUP1 R/W - 1 SETUP0 R/W - 1 SA25 R/W - 0 SA24 R/W - 0 SA23 R/W - 0 SA22 R/W - 0 SA21 R/W - 0 SA20 R/W - 0 Bit 初期値 Name 説 明 15 0 WINEN ・ウィンドウをイネーブルにします。 0:ディセーブル 1:イネーブル カード抜去時は、クリア(初期値)されます。 14-10 11111 WIDTH ・コマンドパルス幅時間をクロック単位で設定します。

(WIDTH 値 + 2) × CARD_CLK 周期 + CARD_CLK 周期 = WIDTH 時間

9-8 11 HOLD ・カードアドレス対コマンド立ち下がり時間をクロック単位で

設定します。

HOLD 値 ×CARD_CLK 周期 + CARD_CLK 周期 = HOLD 時間

7-6 11 SETUP ・コマンド立ち上がり対カードアドレス時間をクロック単位で

設定します。

SETUP 値 ×CARD_CLK 周期 + CARD_CLK 周期 = SETUP 時間

5-0 000000 SA25-20 ・ウィンドウ スタート アドレス セット

システムメモリ空間の1MB境界アドレスを設定します。

その他のウィンドウと設定メモリ空間が重なった場合誤動作を しますので注意して下さい。

4.2.8 メモリウィンドウ1コントロールレジスタ1

メモリウィンドウ1コントロールレジスタ1 Address F2h

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

WIN EN R/W - 0 WIDTH4 R/W - 1 WIDTH3 R/W - 1 WIDTH2 R/W - 1 WIDTH1 R/W - 1 WIDTH0 R/W - 1 HOLD1 R/W - 1 HOLD0 R/W - 1 bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 SETUP1 R/W - 1 SETUP0 R/W - 1 SA25 R/W - 0 SA24 R/W - 0 SA23 R/W - 0 SA22 R/W - 0 SA21 R/W - 0 SA20 R/W - 0 Bit 初期値 Name 説 明 15 0 WINEN ・ウィンドウをイネーブルにします。 0:ディセーブル 1:イネーブル カード抜去時は、クリア(初期値)されます。 14-10 11111 WIDTH ・コマンドパルス幅時間をクロック単位で設定します。

(WIDTH 値 + 2) ×CARD_CLK 周期 + CARD_CLK 周期 = WIDTH 時間

9-8 11 HOLD ・カードアドレス対コマンド立ち下がり時間をクロック単位で

設定します。

HOLD 値 ×CARD_CLK 周期 + CARD_CLK 周期 = HOLD 時間

7-6 11 SETUP ・コマンド立ち上がり対カードアドレス時間をクロック単位で

設定します。

SETUP 値 ×CARD_CLK 周期 + CARD_CLK 周期 = SETUP 時間

5-0 000000 SA25-20 ・ウィンドウ スタート アドレス セット

システムメモリ空間の1MB境界アドレスを設定します。

その他のウィンドウと設定メモリ空間が重なった場合誤動作を しますので注意して下さい。

4.2.9 I/Oウィンドウコントロールレジスタ1

I/Oウィンドウ コントロールレジスタ1 Address F4h

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

WIN EN R/W - 0 WIDTH4 R/W - 1 WIDTH3 R/W - 1 WIDTH2 R/W - 1 WIDTH1 R/W - 1 WIDTH0 R/W - 1 HOLD1 R/W - 1 HOLD0 R/W - 1 bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 SETUP1 R/W - 1 SETUP0 R/W - 1 SA25 R/W - 0 SA24 R/W - 0 SA23 R/W - 0 SA22 R/W - 0 SA21 R/W - 0 SA20 R/W - 0 Bit 初期値 Name 説 明 15 0 WINEN ・ウィンドウをイネーブルにします。 0:ディセーブル 1:イネーブル カード抜去時は、クリア(初期値)されます。 14-10 11111 WIDTH ・コマンドパルス幅時間をクロック単位で設定します。

(WIDTH 値 + 2) ×CARD_CLK 周期 + CARD_CLK 周期 = WIDTH 時間

9-8 11 HOLD ・カードアドレス対コマンド立ち下がり時間をクロック単位で

設定します。

HOLD 値 ×CARD_CLK 周期 + CARD_CLK 周期 = HOLD 時間

7-6 11 SETUP ・コマンド立ち上がり対カードアドレス時間をクロック単位で

設定します。

(SETUP 値 + 1) ×CARD_CLK 周期 + CARD_CLK 周期 = SETUP 時間

5-0 000000 SA25-20 ・ウィンドウ スタート アドレス セット

システムメモリ空間の1MB境界アドレスを設定します。

その他のウィンドウと設定メモリ空間が重なった場合誤動作を しますので注意して下さい。

4.2.10 メモリウィンドウ0コントロールレジスタ2

メモリウィンドウ0コントロールレジスタ2 Address F6h

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 SWAP R/W - 0 Write Pro R/W - 0 SIZE R/W - 0 REG R/W - 0 bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 CA25 R/W - 0 CA24 R/W - 0 CA23 R/W - 0 CA22 R/W - 0 CA21 R/W - 0 CA20 R/W - 0 CA19 R/W - 0 CA18 R/W - 0 Bit 初期値 Name 説 明 11 0 SWAP ・カードへの16bit ワードアクセス時のデータスワップを 制御します。 0:SWAPあり 1:SWAP無し *詳細は、「7.13 データ変換一覧表」を参照して下さい。 10 0 Write Pro ・ウィンドウに対するライトアクセスを許可します。 0:ライト許可 1:ライト不可(カードへのライトサイクルは発生しません) 9 0 SIZE ・カードアクセス時のカード側基本データバス幅を設定します。 0: 8bit 1:16bit 8 0 REG ・“-CREG”端子出力信号を設定します。 0:-CREG=0(アトリビュートメモリ)1:-CREG=1(コモンメモリ) 7-0 000000 00 CA25-18 ・カード アドレス セット カードへ出力する上位アドレスを決定します。 下位アドレスは、システム側アドレスがそのまま出力されます。

4.2.11 メモリウィンドウ1コントロールレジスタ2

メモリウィンドウ1コントロールレジスタ2 Address F8h

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 SWAP R/W - 0 Write Pro R/W - 0 SIZE R/W - 0 REG R/W - 0 bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 CA25 R/W - 0 CA24 R/W - 0 CA23 R/W - 0 CA22 R/W - 0 CA21 R/W - 0 CA20 R/W - 0 CA19 R/W - 0 CA18 R/W - 0 Bit 初期値 Name 説 明 11 0 SWAP ・カードへの16bit ワードアクセス時のデータスワップを 制御します。 0:SWAPあり 1:SWAP無し *詳細は、「7.13 データ変換一覧表」を参照して下さい。 10 0 Write Pro ・ウィンドウに対するライトアクセスを許可します。 0:ライト許可 1:ライト不可(カードへのライトサイクルは発生しません) 9 0 SIZE ・カードアクセス時のカード側基本データバス幅を設定します。 0: 8bit 1:16bit 8 0 REG ・“-CREG”端子出力信号を設定します。 0:-CREG=0(アトリビュートメモリ)1:-CREG=1(コモンメモリ) 7-0 000000 00 CA25-18 ・カード アドレス セット カードへ出力する上位アドレスを決定します。 下位アドレスは、システム側アドレスがそのまま出力されます。

4.2.12 I/Oウィンドウコントロールレジスタ2

I/Oウィンドウコントロールレジスタ2 Address FAh

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 SWAP R/W - 0 Write Pro R/W - 0 SIZE R/W - 0 AUTO SIZE R/W - 0 bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 CA25 R/W - 0 CA24 R/W - 0 CA23 R/W - 0 CA22 R/W - 0 CA21 R/W - 0 CA20 R/W - 0 CA19 R/W - 0 CA18 R/W - 0 Bit 初期値 Name 説 明 11 0 SWAP ・カードへの16bit ワードアクセス時のデータスワップを 制御します。 0:SWAPあり 1:SWAP無し *詳細は、「7.13 データ変換一覧表」を参照して下さい。 10 0 Write Pro ・ウィンドウに対するライトアクセスを許可します。 0:ライト許可 1:ライト不可(カードへのライトサイクルは発生しません) 9 0 SIZE ・カードアクセス時のカード側基本データバス幅を設定します。 0: 8bit 1:16bit 8 0 Auto Size ・CWP_XIOIS16 信号によりデータバスサイズを決定します。 0:bit9 - Size によりカードデータバス幅を決定します 1:カードからのXIOIS16 でカードデータバスを決定します 7-0 000000 00 CA25-18 ・カード アドレス セット カードへ出力する上位アドレスを決定します。 下位アドレスは、システム側アドレスがそのまま出力されます。

4.2.13 カードコントロールレジスタ

カードコントロールレジスタ Address FCh

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 Scratchpad Bits R - 0 CARD IS I/O R/W - 0 LED ENABLE R/W - 0 SPKR ENABLE R/W - 0 INPACK ENABE R/W - 0 Bit 初期値 Name 説 明 3 0 CARD IS I/O ・カードモードを選択します。 0:メモリカードI/F

1:I/O カード I/F & メモリカード I/F

注)I/Oカードモードに設定した場合、メモリカードI/Fで 使用する信号の一部がリプレスされます。 2 0 LED ENABLE ・LED_OUT 端子をイネーブルにします。 0:LED_OUT 端子ディセーブル 1:CBVD2_SPKR 信号を LED_OUT 端子に出力します メモリーカード時は無効です カード抜去時は、クリア(初期値)されます。 1 0 SPKR ENABLE ・SPKR_OUT 端子をイネーブルにします。 0:SPKR 端子ディセーブル 1:CBVD2_SPKR 信号を SPKR_OUT 端子に出力します メモリカード時は無効です カード抜去時は、クリア(初期値)されます。 0 0 INPACK ENABE ・-CINPACK 信号の有効無効を設定します。 0:-CINPACK 信号無視 1:-CINPACK 信号有効

4.2.14 PCIC情報レジスタ

PCIC 情報 レジスタ Address FEh

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8 ascll1_7 R - 0 ascll1_6 R - 1 ascll1_5 R - 0 ascll1_4 R - 1 ascll1_3 R - 0 ascll1_2 R - 0 ascll1_1 R - 1 ascll1_0 R - 1

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 ascll2_7 R - 0 ascll2_6 R - 0 ascll2_5 R - 1 ascll2_4 R - 1 ascll2_3 R - 0 ascll2_2 R - 0 ascll2_1 R – 1 ascll2_0 R - 1 Bit 初期値 Name 説 明 15-8 53h ascll word1 ・アスキーコード 1ワード目 “S” 7-0 33h ascll word2 ・アスキーコード 2ワード目 “3”

5 モード設定

5.1 概 要 ・本LSI は、SH2,3 と SH4 のバスサイクルをサポートするため以下の2つの モードとChip No 設定機能を搭載しました。 この機能は、モードレジスタ”E4h”を設定する事により使用可能になります。 1 -WAIT/-RDY 信号機能の選択 2 最大周波数 66Mhz への対応 3 Chip No の設定機能(ソフトウエア用) 5.2 モードレジスタ設定方法 ・モードレジスタは、その他のレジスタとは異なり特殊な意味を持っています。 このため以下の手順により確実に設定する必要があります。 1 システムリセット後、本LSI への最初のアクセス前までに 本LSI が接続されている”CS”空間のソフトウエアウエイト数を 2以上(33Mhz 以下時)又は3以上(66Mhz 以下時)に設定して下さい。 2 モードレジスタの設定が必要な場合 本LSI への最初のアクセスがモードレジスタへのライトアクセスで ある必要があります。 任意の設定値をモードレジスタにライトして下さい。 モードレジスタへのライト後、動作上の制約はありません。 モードレジスタの設定が不必要な場合 動作上の制約はありません。 3 モードレジスタの設定は、ハードウエアリセット後以外に変更しないで下さい。 変更した場合、誤動作の原因になりますのでご注意下さい。5.3 機能説明 5.3.1 -WAIT/-RDY 信号機能選択 ・モードレジスタのBit5:MODE SH4 の設定値と”-WAIT/-RDY”端子の 関係を図5.3.1 に示します。 ・-WAIT/-RDY 端子は3ステート出力となっています。 モードレジスタ Bit5:MODE SH4 の設定により Hi-Z からの遷移状態を 決定することができます。 この設定により、SH2,3 の”-WAIT”信号機能か SH4 の”-RDY”信号機能を 選択する事が可能です。 CKIO -WAIT CKIO -RDY -RDY -WAIT MR-SHPC-01 V2 0 (初期値) 1 タイミング波形図 ハードウエア接続例 MODE SH4 図5.3.1 -WAIT/-RDY 端子動作 MR-SHPC-01 V2

5.3.2 カードアクセス基準クロック(CARD_CLK)の選択 ・モードレジスタのBit4:MODE66 の設定値によりカードアクセス 基準クロック(CARD_CLK)を選択する事ができます。 主にこの機能は、クロック入力最大周波数が33Mhz を越える場合に 必ず設定します。 ・以下にモードレジスタBit4:MODE66 の設定値とカードアクセス 基準クロック(CARD_CLK)の関係を図 5.3.2 に示します。 ・以後“モードレジスタ・Bit4:MODE66”が“0”の場合 MODE0 とし “1”の場合MODE1 とします。 5.3.3 Chip No Rgister ・モードレジスタのBit3-Bit0 に Chip No 設定します。 ・本LSI が、2個以上搭載されるシステムに置いてソフトウエアによる 本LSI の識別を補助する為のレジスタです。 ・ソフトウエアで本Bit を使用しない場合は、初期値のままでご使用下さい。 (任意の値を設定しても動作上問題はありません) CKIO CARD_CLK CKIO CARD_CLK MODE66 0 (初期値) 1 タイミング波形図 図5.3.2 CARD_CLK 基本動作図

6 システムメモリ空間

6.1 レジスタ空間 6.1.1 機 能 ・本LSI は、図 6.1 に示すようにレジスタ空間をシステムのメモリ空間の 4MB 境界に自由にマッピングする事ができます。 ・レジスタ空間のマッピングには、“RA25-22”入力端子を設定する事により 設定されたシステムアドレス境界の上位空間に レジスタ空間がマッピングされます。・レジスタ空間は、16Bit 固定データのため必ず 16Bit 幅で Read/Write を 実行して下さい。 ・レジスタ空間は、32Byte の空間が存在します。 6.1.2 レジスタ空間マッピング例 ・RA25-22を“0000”に設定した場合のレジスタ空間アドレスは 以下のようになります。 マッピング位置(4MB境界)SA25-22 SA25-22 = RA25-22 = 0h レジスタアドレス空間SA21-0 SA21-0 = 3FFFE0h~3FFFFFh レジスタ空間アドレスは、マッピング位置とレジスタアドレスを合成した値 SA25-0 = 03FFFE0h~03FFFFFh になります。 Register 32Byte ・・・・・・・・ 4MB 境界 4MB 境界 4MB 境界 4MB 境界 MSB システム メモリ空間 ・システムアドレス上位“RA25-RA22”を 外部入力ピンで設定する事により、 指定された4MB 空間の上位空間に レジスタ空間をマッピングする事が可能 Register Start Address

6.2 メモリ,I/O空間 6.2.1 機 能 ・本LSI は、図 6.2 に示すようにメモリウィンドウ空間と I/Oウィンドウ空間をシステムのメモリ空間の1MB境界に 自由にマッピングする事ができます。 ・各ウィンドウ空間は、レジスタのスタートアドレスを設定する事により システムのメモリ空間に1MBにウィンドウを自動的に開きます。 I/O 1MB Memory 1MB ・・・・・・・・ 1MB 境界 1MB 境界 1MB 境界 1MB 境界 1MB 境界 1MB 境界 MSB LSB システム メモリ空間 ×2 ・システムアドレスのSA25-SA20 をレジスタに設定 する事により、システムメモリ空間の1MB 境界へ マッピングが可能 図6.2 メモリ・I/Oアクセス空間メモリマップ

6.3 ウィンドウ空間 6.3.1 機 能 ・各ウィンドウは、図6.3 に示すように4つの空間に区別され 各空間のサイズは256KBになっています。 この4つの空間は、リード・アクセス時とライト・アクセス時で 動作が異なって来ます 6.3.2 ライト・アクセス ・カードへのライトアクセス時は、各空間共に同一空間として扱われます。 ライトアクセスでは、256KBの空間がライト空間となり どのWrite 空間0~3にライトアクセスを実行しても、 カード ライトアクセスの結果は同じになります。 ・この機能は、リード・アクセスとライト・アクセスを交互に行うような場合 システムアドレスの移動を、最小限に押さえる事ができます。 1MB 256KB 256KB 256KB 256KB MSB LSB Write 空間0 Write 空間1 Write 空間2 Write 空間3 図6.3.2 各ウィンドウ空間マップ Card 256KB 空間

6.3.3 リード・アクセス ・ “Dummy 空間”と”Real 空間”は、内蔵されているリードバッファを使用 する為の空間です。 リードバッファを使用しない場合は、”Real 空間“を使用した リード・アクセスを行うことでカードデータをリードする事が可能です。 ・SHシリーズでは、リード時に要求データサイズを識別する事ができません。 このため、図6.3.3 に示すように”Byte”空間と”Word”空間を設け アクセスされた空間により要求リードデータサイズを識別します。 ・以下にリード・アクセス時の各空間機能を説明します。 Dummy Byte 空間

カードのEven,Odd Byte Read Data を Read Buffer に

先読みさせる空間です。

Dummy Word 空間

カードのWord Read Data を Read Buffer に先読みさせる空間です。

Real Byte 空間

カードのEven,Odd Byte Read Data を直接リードするための空間です。

Read Buffer で先読みさせたデータもこの空間でリードします。

Real Word 空間

カードのWord Read Data を直接リードするための空間です。

Read Buffer で先読みさせたデータもこの空間でリードします。 1MB 256KB 256KB 256KB 256KB MSB LSB Real Word 空間 Real Byte 空間 Dummy Word 空間 Dummy Byte 空間 図6.3.3 各ウィンドウ空間マップ Card 256KB 空間

7.機能・動作

7.1 SH CPU I/F 7.1.1 概 要 本LSI の基本アクセスサイクルは、“4×CKIO”と“5×CKIO”で 構成されます。(MODE0=4×CKIO,MODE1=5×CKIO) また、サイクルを延長するため本LSI は“-WAIT/-RDY”信号をアサートします。7.1.2 MODE0 基本4×CKIO サイクル(No WAIT)

① “TW1 Cycle”の立ち上がりクロック↑により“-BS”信号を検出し、 システムサイクルの開始を検知します。 ② “TW2 Cycle”の立ち上がりクロック↑により、Address,Command, Data を検出し、本LSI の動作を決定します。 ③ “TW2 Cycle”の立ち下がりクロック↓により、Read Data の出力を 開始します。

④ “-SRD”のネゲートにより、Read Data 出力を Hi-Z にします。

以下に、MODE0 基本 4×CKIO サイクル(No WAIT)波形図を示します。

T1 TW1 TW2 T2 CKIO SA25-0 -CS -SRD Read Data -BS -SWE1,0 -WAIT/-RDY Write Data 図7.1.2 基本サイクル1波形図(NO WAIT) ① ② ③ ④ Hi-Z ④

7.1.3 MODE1 基本 5×CKIO サイクル(No WAIT) ① “TW1 Cycle”の立ち上がりクロック↑により“-BS”信号を検出し、 システムサイクルの開始を検知します。 ② “TW3 Cycle”の立ち上がりクロック↑により、Address,Command, Data を検出し、本LSI の動作を決定します。 ③ “TW3 Cycle”の立ち下がりクロック↓により、Read Data の出力を 開始します。

④ “-SRD”のネゲートにより、Read Data 出力を Hi-Z にします。

以下に、MODE1 基本 5×CKIO(No WAIT)サイクル波形図を示します。

T1 TW1 TW3 T2 SA25-0 -CS -SRD Read Data -BS -SWE1,0 -WAIT/-RDY Write Data 図7.1.3 基本サイクル2波形図(NO WAIT) ① ② ③ ④ Hi-Z CKIO TW2 ④

7.1.4 MODE0 基本 4×CKIO サイクル(1WAIT) ① “TW1 Cycle”の立ち上がりクロック↑により“-BS”信号を検出し、 システムサイクルの開始を検知します。 ② “TW2 Cycle”の立ち上がりクロック↑により、Address,Command, Data を検出し、本LSI の動作を決定します。 このタイミングで“-WAIT/-RDY”信号をアサートします。 ③ “TWn*1 Cycle”の立ち上がりクロック↑により、 “-WAIT/-RDY”信号を ネゲートします。 *1 TWn Cycle は、“-WAIT/-RDY”により挿入された延長サイクルです。 ④ “TWn*1 Cycle”の立ち下がりクロック↓により、Read Data の出力を 開始します。 ⑤ “T2 Cycle”の立ち上がりクロック↑により、“-WAIT/-RDY”信号を Hi-Z にします。

⑥ “-SRD”のネゲートにより、Read Data 出力を Hi-Z にします。

以下に、MODE0 基本 4×CKIO サイクル波形図を示します。 T1 TW1 TW2 T2 CKIO SA25-0 -CS -SRD Read Data -BS -SWE1,0 -WAIT/-RDY Write Data ① ② ③ ④ Twn Hi-Z Hi-Z ⑥ ⑤

7.1.5 MODE1 基本 5×CKIO サイクル(1WAIT) ① “TW1 Cycle”の立ち上がりクロック↑により“-BS”信号を検出し、 システムサイクルの開始を検知します。 ② “TW3 Cycle”の立ち上がりクロック↑により、Address,Command, Data を検出し、本LSI の動作を決定します。 このタイミングで“-WAIT/-RDY”信号をアサートします。 ③ “TWn*1 Cycle”の立ち上がりクロック↑により、 “-WAIT/-RDY”信号を ネゲートします。 *1 TWn Cycle は、“-WAIT/-RDY”により挿入された延長サイクルです。 ④ “TWn*1 Cycle”の立ち下がりクロック↓により、Read Data の出力を 開始します。 ⑤ “T2 Cycle”の立ち上がりクロック↑により、“-WAIT/-RDY”信号を Hi-Z にします。

⑥ “-SRD”のネゲートにより、Read Data 出力を Hi-Z にします。

以下に、MODE1 基本 5×CKIO サイクル波形図を示します。 T1 TW1 TW3 T2 CKIO SA25-0 -CS -SRD Read Data -BS -SWE1,0 -WAIT/-RDY Write Data ① ② ③ ④ Twn Hi-Z Hi-Z ⑥ ⑤

-WAIT/-RDY Hi-Z Hi-Z

7.2 レジスタ機能 7.2.1 概 要 本LSI は内蔵機能を制御するためのレジスタを内蔵しています。 内蔵レジスタへのRead/Write は、16bit ワードアクセス固定になっています。 バックグランドでカードサイクルを実行している場合もレジスタへの Read/Write 動作は可能です。(モードレジスタを除く) レジスタアクセス時は、“-WAIT/-RDY”をアサートしません。 7.2.2 レジスタ構造

・図7.2.2 に示すように1段の“Register Write Buffer”と

1段の“Real Register”で構成されています。(モードレジスタを除く) ・カードサイクル実行中のWrite アクセスは 一旦データをBuffer に貯えておき、カードサイクル終了後に “Real Register”にデータをシフトします。 ・この構造により、カードアクセス中にレジスタの設定値が変更されなくなり 実行中カードサイクルとレジスタ設定値の不整合が 発生しなくなります。 ・リードデータは常に“Real Register”の設定値がリードされます。 カードサイクル発生中にレジスタライトリードを実行した場合は、 ライトデータとリードデータが異なる場合が有ります。 ・カード電源制御レジスタ Bit9:CARD RESET は、例外として カードサイクル実行の有無にかかわらず、常に“Real Register”に Write されます。 これにより、カードがどのような状態であってもリセットをかけることが 可能です。 Register Write Buffer Real Register SD15-0(Input) Register Write

PC Card I/F Ready

CKIO

Buffer Data Register Data Register

Data Selector

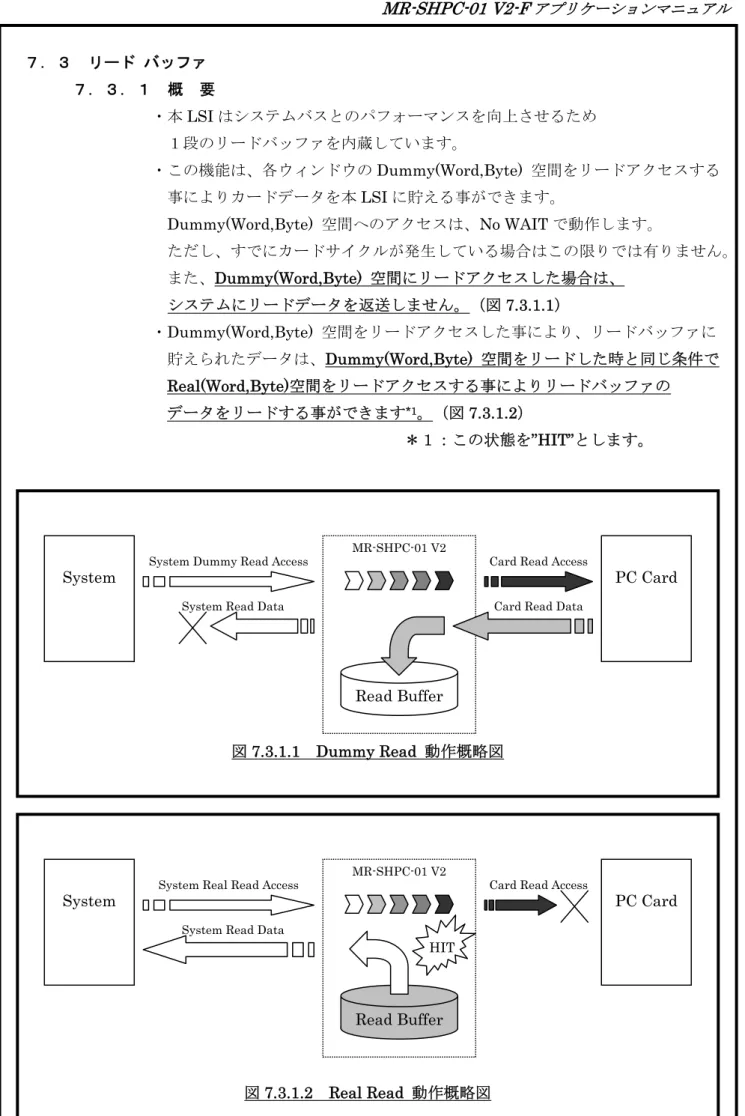

7.3 リード バッファ 7.3.1 概 要 ・本LSI はシステムバスとのパフォーマンスを向上させるため 1段のリードバッファを内蔵しています。 ・この機能は、各ウィンドウのDummy(Word,Byte) 空間をリードアクセスする 事によりカードデータを本LSI に貯える事ができます。

Dummy(Word,Byte) 空間へのアクセスは、No WAIT で動作します。

ただし、すでにカードサイクルが発生している場合はこの限りでは有りません。 また、Dummy(Word,Byte) 空間にリードアクセスした場合は、 システムにリードデータを返送しません。(図7.3.1.1) ・Dummy(Word,Byte) 空間をリードアクセスした事により、リードバッファに 貯えられたデータは、Dummy(Word,Byte) 空間をリードした時と同じ条件で Real(Word,Byte)空間をリードアクセスする事によりリードバッファの データをリードする事ができます*1。(図7.3.1.2) *1:この状態を”HIT”とします。

System Dummy Read Access

System Card Read Access PC Card

Read Buffer

Card Read Data System Read Data

MR-SHPC-01 V2

System Real Read Access

System Card Read Access PC Card

Read Buffer

System Read Data

MR-SHPC-01 V2

HIT

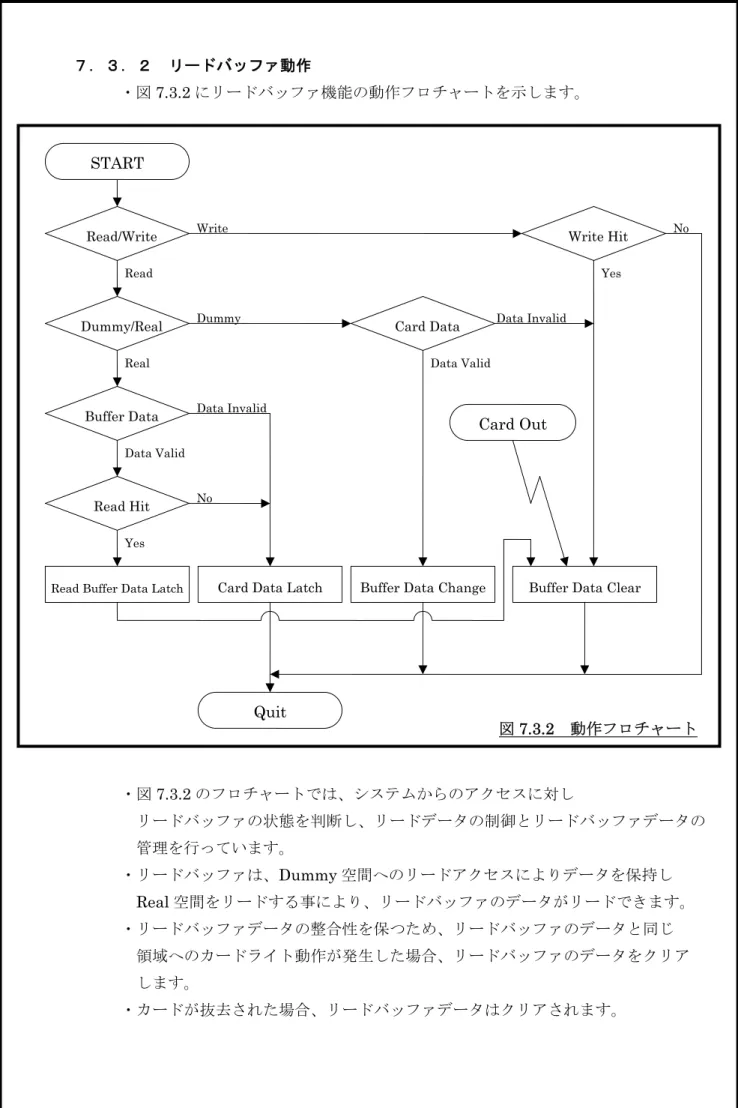

7.3.2 リードバッファ動作 ・図7.3.2 にリードバッファ機能の動作フロチャートを示します。 ・図7.3.2 のフロチャートでは、システムからのアクセスに対し リードバッファの状態を判断し、リードデータの制御とリードバッファデータの 管理を行っています。 ・リードバッファは、Dummy 空間へのリードアクセスによりデータを保持し Real 空間をリードする事により、リードバッファのデータがリードできます。 ・リードバッファデータの整合性を保つため、リードバッファのデータと同じ 領域へのカードライト動作が発生した場合、リードバッファのデータをクリア します。 ・カードが抜去された場合、リードバッファデータはクリアされます。 No Data Invalid Yes Real Read Data Valid START Read/Write Dummy/Real Read Hit Write Card Data No

Read Buffer Data Latch

Buffer Data

Quit Card Data Latch

Data Invalid Dummy

Buffer Data Change

Data Valid

Buffer Data Clear Write Hit

Yes

図7.3.2 動作フロチャート

7.3.3 リードバッファHit条件

・リードバッファのReal Read Access 時と Write Access 時の Hit 条件を

図7.3.3.1 と図 7.3.3.2 に示します。 I/O or Memory Access (1bit) CA25-1 (25bit) REG (1bit)

Read Buffer Condition System Access Condition

I/O or Memory Access (1bit) CA25-1 (25bit) REG (1bit)

Write HIT

・Write Hit

リードバッファのデータをクリアします。 I/O or Memory Access (1bit) CA25-0 (26bit) SWAP (1bit) REG (1bit) 16bit Access (1bit) 8bit Access (1bit)Buffer Data = VALID (1bit)

Read Buffer Condition System Access Condition

I/O or Memory Access (1bit) CA25-0 (26bit) SWAP (1bit) REG (1bit) 16bit Access (1bit) 8bit Access (1bit)

HIT

図7.3.3.1 リアルリードアクセスの Hit 決定比較データ7.4 割り込み

7.4.1 割り込み要求選択機能

・割り込み制御レジスタのBit13-5 の設定値と SIRQ3-0 の関係を

表7.4.1 に示します。

・Card IRQ:Bit13,RING IRQ:Bit10,Management IRQ:Bit7 が

全て“0”に設定されている場合は、SIRQ3-0 がすべて“Hi-Z”になります。 要因3 要因2 要因1 割り込み出力端子 Card IRQ Bit13-11 RING IRQ Bit10-8 Management IRQ Bit7-5

SIRQ3 SIRQ2 SIRQ1 SIRQ0

0 X X 0 X X 0 X X Hi-Z Hi-Z Hi-Z Hi-Z

1 0 0 0 X X 0 X X Hi-Z Hi-Z Hi-Z 要因3

1 0 1 0 X X 0 X X Hi-Z Hi-Z 要因3 Hi-Z

1 1 0 0 X X 0 X X Hi-Z 要因3 Hi-Z Hi-Z

1 1 1 0 X X 0 X X 要因3 Hi-Z Hi-Z Hi-Z

0 X X 1 0 0 0 X X Hi-Z Hi-Z Hi-Z 要因2

0 X X 1 0 1 0 X X Hi-Z Hi-Z 要因2 Hi-Z

0 X X 1 1 0 0 X X Hi-Z 要因2 Hi-Z Hi-Z

0 X X 1 1 1 0 X X 要因2 Hi-Z Hi-Z Hi-Z

0 X X 0 X X 1 0 0 Hi-Z Hi-Z Hi-Z 要因1

0 X X 0 X X 1 0 1 Hi-Z Hi-Z 要因1 Hi-Z

0 X X 0 X X 1 1 0 Hi-Z 要因1 Hi-Z Hi-Z

0 X X 0 X X 1 1 1 要因1 Hi-Z Hi-Z Hi-Z

1 0 0 1 0 0 1 0 0 Hi-Z Hi-Z Hi-Z 要因3&2&1

0 X X 1 0 0 1 0 0 Hi-Z Hi-Z Hi-Z 要因2&1

1 0 1 1 0 0 1 0 0 Hi-Z Hi-Z 要因3 要因2&1

1 1 0 1 0 0 1 0 0 Hi-Z 要因3 Hi-Z 要因2&1

1 1 1 1 0 0 1 0 0 要因3 Hi-Z Hi-Z 要因2&1