© 2007 Xilinx, Inc. All Rights Reserved. XILINX、Xilinx ロ ゴ、 お よびその他本文に含まれる商標名は Xilinx の商標です。本文書に記載 さ れてい る 「Xilinx」、 ザイ リ ン ク スのロ ゴ、 お よびザイ リ ン ク スが所有する製品名等は、 米国 Xilinx Inc. の米国におけ る登録商標です。 その他に記載 さ れてい る会社名お よび製品名等は、 各社の商標または登録商標です。 保証否認の通知 : Xilinx ではデザイ ン、 コ ー ド 、 その他の情報を 「現状有姿の状態」 で提供 し ています。 こ の特徴、 ア プ リ ケーシ ョ ン ま たは規格の一実施例 と し てデザイ ン、 コ ー ド 、 そ の他の情報を提供 し てお り ますが、Xilinx は こ の実施例が権利侵害の ク レ ームを全 く 受けない と い う こ と を表明する も のではあ り ません。 お客様がご自分で実装 さ れる場合には、 必要な 権利の許諾を受け る責任があ り ます。Xilinx は、 実装の妥当性に関するいかな る保証を行な う ものではあ り ません。 こ の保証否認の対象 と な る保証には、 権利侵害の ク レ ームを受けない こ と の保証ま たは表明、 および市場性に対する適合性についての黙示的な保証 も 含まれます。

は じ めに

デジ タ ルデ ィ ス プ レ イ は LCD、 プ ラ ズマ、 リ アプ ロ ジ ェ ク シ ョ ン TV テ ク ノ ロ ジや携帯ハン ド セ ッ ト お よ びオー ト モーテ ィ ブ向けの小型デ ィ ス プ レ イ を含む、 多数のアプ リ ケーシ ョ ン で構成 さ れ、 急成長 を遂げてい る 市場です。デジ タ ル画像処理に よ っ て表示 さ れ る 画像の全体的な画質を向上 さ せ、 製品の 差別化を図 る こ と がで き ます。 ザ イ リ ン ク ス では、 こ の市場向けの製品開発をサポー ト す る ため、デ ィ ス プ レ イパネルアプ リ ケーシ ョ ン用の リ フ ァ レ ン ス デザ イ ン IP コ ア を、 Spartan™-3E デ ィ ス プ レ イ 開発ボー ド に基づいて開発 し ま し た。 FPGA のデ ィ ス プ レ イ ソ リ ュ ーシ ョ ンは、図1に示す よ う に、DVI 入力 イ ン タ ーフ ェ イ ス、 色温度 調整 (CTC)、 正確なガ ン マ補正 (PGC)、 イ メ ージ デ ィ ザ リ ン グ エ ン ジ ン (IDE)、 お よ び低電圧差動信 号送信 (LVDS TX) ま たは DVI TX 出力 イ ン タ ーフ ェ イ ス で構成 さ れます こ のアプ リ ケーシ ョ ン ノ ー ト では、Spartan-3E デ ィ ス プ レ イ 開発ボー ド について説明 し ます。 ま た、DIP ス イ ッ チ設定について詳細に説明 し 、 各 IP ブ ロ ッ ク の リ ソ ース数 も 記載 し てい ます。IP

ブ ロ ッ ク の

サマ リ

表1 で、Spartan-3E デ ィ ス プ レ イ 開発ボー ド の主要な IP ブ ロ ッ ク について説明 し ます。 ア プ リ ケーシ ョ ン ノ ー ト : Spartan-3E FPGA XAPP928 (v1.1) 2007 年 4 月 19 日LVDS/DVI

を使用するデジ タ ル

デ ィ ス プ レ イ

パネル

IP

の リ フ ァ レ ン ス

デザイ ン

Spartan-3E デ ィ ス プ レ イ開発キ ッ ト HW-SPAR3E-DISP-DK-UNI-G 向け 本資料は英語版 (v1.1) を翻訳 し た ものです。 英語の更新バージ ョ ンが リ リ ース さ れている場合には、 最新の英語版を必ずご参照 く だ さ い。 R 図 1 : ザイ リ ン ク ス デ ィ ス プ レ イ パネル IP リ フ ァ レ ン スデザイ ンの フ ロー DVI Interface Color Temperature Correction (CTC) Precise Gamma Correction (PGC) Image Dithering Engine (IDE) LVDS or DVI TX Interface Flat Panel X928_01_040907 表 1 : IP ブ ロ ッ クの概要 ブ ロ ッ ク名 説明 DVI レ シーバ DVI 形式の入力ビデオを受信 CTC (色温度調整) フ レーム全体の入力 RGB 値を ユーザーが設定 し た色温度に調整 PGC (正確なガ ン マ補正) ピ ク セルの ス ト リ ーム を受け取 り 、 必要なガ ン マ値に処理 し た後、 修正 後の ピ ク セル ス ト リ ーム を次のモジ ュ ールに送信 IDE (イ メ ージデ ィ ザ リ ン グ エン ジ ン) PGC モジ ュ ールか ら のガ ン マ補正 さ れた ピ ク セル ス ト リ ーム を 3 x 10 ビ ッ ト で受け取っ て、 ビデオ画質を低下 さ せ る こ と な く 、3 x 8 ビ ッ ト の ピ ク セルス ト リ ームにデ ィ ザ リ ン グす る デ ィ ス プ レ イ イ ン タ ー フ ェ イ ス LVDS イ ン タ ーフ ェ イ ス を介 し て DVI ト ラ ン ス ミ ッ タ が LCD モジ ュ ー ルを直接駆動で き る よ う にす るIP ブ ロ ッ クのサマ リ R

ユーザー

ス イ ッ チおよびプ ッ シ ュ

ボ タ ンの設定

本書での ス イ ッ チ設定は、Spartan-3E デ ィ ス プ レ イ 開発ボー ド 上でユーザー設定の DIP ス イ ッ チブ ロ ッ ク で行い ます (図2)。 イ メ ージ デ ィ ザ リ ン グ エン ジ ンは、 プ ッ シ ュ ボ タ ンの設定で調整 さ れます。 • 0 : プ ッ シ ュ ボ タ ン を押す場合に使用 • 1 : プ ッ シ ュ ボ タ ン を放す場合に使用 DVI 受信 (RX) イ ン タ ー フ ェ イ スブ ロ ッ ク 図 2 : デ ィ ス プ レ イ開発ボー ド のス イ ッ チ設定 表 2 : DIP ス イ ッ チのユーザー設定 DIP ス イ ッ チ 機能 SW4 DVI RX。 常に 「ON」 にす る 。 SW3、SW2 PGC (正確なガ ン マ補正) の制御 • On、On (00) : ガ ン マ 2.2/2.2 (1.00) • On、Off (01) : ガ ン マ 2.4/2.2 (1.09) • Off、On (10) : ガ ン マ 2.6/2.2 (1.18) • On、On (11) : PGC 無効 SW1、SW0 CTC (色温度調整) の制御 • On、On (00) : バ イ パス • On、Off (01) : 6500K • Off、On (10) : 8500K • On、On (11) : 10000KUser Set DIP Switch Block

User Push Button Switch Settings (PSW 2, 1, 0 are above)

CTC IP ブ ロ ッ ク R

CTC IP

ブ ロ ッ ク

色温度について

白色光は色温度で表す こ と がで き ます。 あ る 光源の色温度を特定す る には、 その出力を あ る 温度で理論 的な黒体が放射す る 光 と 比較 し ます (単位はケルビ ン、K)。具体的には、5000K ∼ 5500K が通常の昼白 色、2000K が赤/オ レ ン ジ色、15000K は青みがか っ た色 と な り ます。 た と えば、 空の太陽光が赤、 オ レ ン ジ、 白、 青な ど の よ う に位置に よ っ て異な っ て見え る よ う に、 色温度は、 光源お よ びデ ィ ス プ レ イ テ ク ノ ロ ジに よ っ て異な っ て き ます。 デジ タ ルデ ィ ス プ レ イ におけ る 白色は、 そのデ ィ ス プ レ イ の R、G、 お よ び B セルか ら 出 さ れ る こ れ ら の色の組み合わせで認識 さ れます。 RGB デー タ は CIE x-y 色空間 に合 う よ う に変換で き 、 色空間では、 変換アルゴ リ ズ ムで多数の演算が実行 さ れます。 「ホ ワ イ ト ポ イ ン ト 」 は色温度 と し て大ま かに定義 さ れてい ます。CIE 色度図 (図3) では、5500K での ホ ワ イ ト ポ イ ン ト は、 ほぼ x = y = 0.33 の点です。 こ の図を見 る と 、PDP (プ ラ ズマ デ ィ ス プ レ イ パネル) の色温度が低 く な っ てお り 、 特に CRT (ブ ラ ウ ン管) デ ィ ス プ レ イ と 比較す る と こ れは顕著です。 PDP では基本的に青輝度が低いため、 色温度 も 低 く な り ます。 さ ら に、PDP のセル構造お よ び関連す る 動作回路がいっ たん固定 さ れ る と 、 エン ド カ ス タ マ が色温度を独自に変更す る こ と はで き ません。し たがっ て、PDP な ど のデジ タ ルデ ィ ス プ レ イ 出力は、 よ り 高品質の画像を実現す る よ う に調整 さ れ る 必要があ り ます。 表 3 : LVDS/DVI RX を使用する場合の LVDS DIP ス イ ッ チ設定 DIP ス イ ッ チ ポー ト 名 設定 DIP_SWITCH_0 [ユーザー ス イ ッ チ SW4] DIPS_RX_SELECT 常に 「ON」 にす る 。 図 3 : CIE 色度図に示す色温度 X928_03_040907CTC IP ブ ロ ッ ク R

CTC

アルゴ リ ズム

こ のアルゴ リ ズ ムの イ ンプ リ メ ン テーシ ョ ン では、 フ レームのホ ワ イ ト ポ イ ン ト ま たは色温度が特定の フ レームに求め ら れ る 色温度に変更 さ れます。 最初に、CIE の基準ホ ワ イ ト ポ イ ン ト が、 ユーザーが設 定 し た温度入力か ら x お よ び y 形式で選択 さ れます。入力 さ れ る 全フ レームに対す る ホ ワ イ ト ポ イ ン ト が概算 さ れます。 8 ま たは 10 ビ ッ ト の RGB デー タ の入力フ レームは color-mixing プ ロ グ ラ ム を使用 し て x-y 形式に変換 さ れます。 次に、 入力フ レーム温度お よ び基準温度が同 じ か ど う かが確認 さ れ ます。 再帰演算がデー タ 温度値を制 御 し 、 正確な色温度調整を行 う ため、 基準 と な る ホ ワ イ ト ポ イ ン ト が選択 さ れ ます。色温度が同一 (差 分内) の場合は変更 さ れず、 色温度が異な る と 、 フ レームは適切な色温度に変更 さ れます。 色温度の調整には、 比率法が使用 さ れ ま す。 CIE 温度対入力 フ レ ー ム の温度比率は、 入力 フ レ ー ム の RGB デー タ それぞれに適応 さ れ、 適切な色温度を設定 し ます。こ の時点で、 修正 さ れた色温度の変換が 完了 し た こ と にな り ます。 図 4 : CTC IP ブ ロ ッ ク図 CTC_PGC_R_DATA[7:0] CTC_PGC_G_DATA[7:0] CTC_PGC_B_DATA[7:0] R-Color Correction G-Color Correction B-Color Correction Bypass Logic White Point Calculation Frame White Point Estimation CTC Control Logic VIDEO_RGB Data Bus CIE Reference DIPS_CTC_CNT Frame White Point Bus White Point Bus CLK Cntr Cntr Cntr Cntr Temp CTC_PGC_DATA_RDY VIDEO_CTC_END_FRM RESET_N VIDEO_CTC_STRT_FRM CTC_PGC_DATA_EN X928_04_041907 VIDEO_CTC_DATA_EN VIDEO_CTC_RDY VIDEO_CTC_R_DATA[7:0] VIDEO_CTC_G_DATA[7:0] VIDEO_CTC_B_DATA[7:0]CTC IP ブ ロ ッ ク R 表4に、CTC モジ ュ ールで使用 さ れ る 信号の説明を示 し ます。 色温度の入力レ ジ ス タ 値は、 タ ーゲ ッ ト と す る 色温度 と し て標準温度値 (6500K、8000K、9300K) を示 し ます。こ れ ら の値は外部の DIP ス イ ッ チで選択 さ れます。 そ し て、CIE の基準ホ ワ イ ト ポ イ ン ト 値が 決定 さ れ ます。こ の後の処理では、 ホ ワ イ ト ポ イ ン ト に対す る RGB 値が使用 さ れ ます。デフ ォ ル ト で は、 色温度は変更 さ れず、 入力デー タ を をバ イ パ ス し ます。 次の フ レームの開始点で色温度を選択 し た 後、CTC モジ ュ ールでは、 基準点 と な る ホ ワ イ ト ポ イ ン ト の値が更新 さ れます。 フ レームのホワ イ ト ポ イ ン ト の概算 ホ ワ イ ト ポ イ ン ト を概算す る には、 次のアルゴ リ ズ ム を使用 し ます。まず、RGB の和が最大 と な る ピ ク セルを フ レーム全体か ら 見つけ ます。こ の和を示す RGB 値が、 その フ レームのホ ワ イ ト ポ イ ン ト と みな さ れます。そ し て、 こ のホ ワ イ ト ポ イ ン ト は次の入力フ レームの開始で再び更新 さ れます。 CTC (色温度調整) モ ジ ュ ール CTC モジ ュ ールでは、フ レーム全体の入力 RGB 値が新 し い温度に調整 さ れます。こ のモジ ュ ールでは、 一定の比率を乗算す る 方法に よ っ て、値が調整 さ れます。 た と えば、ピ ク セルの R の調整後の値は等式1 か ら 求め ら れます。 等式 1 説明 : • Rin = 入力ピ ク セルの R 値 • Rwt = 標準温度の CIE ホ ワ イ ト ポ イ ン ト 値 • Rwf = 前の フ レームのホ ワ イ ト ポ イ ン ト におけ る R 値 • Rout = CTC モジ ュ ールで調整 さ れた出力ピ ク セルの R 値 表 4 : CTC モ ジ ュ ールの信号 信号 I/O 説明 RESET_N 入力 シ ス テ ム リ セ ッ ト 。 CTC モジ ュ ール内の全プ ロ セ ス を リ セ ッ ト す る には、 こ の信号を Low にアサー ト す る 。 CLK 入力 シ ス テ ム ク ロ ッ ク 。ビデオ処理に必要な周波数で動作。 DIPS_CTC_CNT 入力 DIP ス イ ッ チか ら の制御信号 (ユーザース イ ッ チ SW1、 SW0)。タ ーゲ ッ ト と す る 色温度を決定。 VIDEO_CTC _STRT_FRM 入力 CTC は こ の信号を アサー ト し て、LVDS レ シーバへ送 信す る 新 し い フ レームの開始を示す。 VIDEO_CTC _END_FRM 入力 CTC は こ の信号を アサー ト し て、LVDS レ シーバへ送 信 し てい る 現在の フ レームの終了を示す。 VIDEO_CTC _DATA_EN 入力 CTC は こ の信号を アサー ト し て、 有効なデー タ が LVDS レ シーバブ ロ ッ ク に与え ら れた こ と を示す。 VIDEO_CTC_RGB_DATA[23:0] 入力 CTC では RGB 形式の入力ピ ク セルデー タ が、 こ の 24 ビ ッ ト のデー タバ ス か ら 入力 さ れ る 。 CTC_PGC_DATA_RDY 出力 CTC は こ の信号を アサー ト し て、 有効なデー タ が次の PGC ブ ロ ッ ク でプ ロ セ ス で き る 状態であ る こ と を示す。 CTC_PGC_DATA_EN 出力 こ の信号がアサート さ れる と 、PGC レ シーバブロ ッ ク の CTC_PGC_RGB_DATA[23:0] のデータ が有効と なる 。 CTC_PGC_RGB_DATA[23:0] 出力 RGB 形式の出力ピ ク セルデー タ が、 こ の 24 ビ ッ ト の デー タ バ ス か ら PGC に出力 さ れ る 。

R

inR

wtR

wf ---× =R

outCTC IP ブ ロ ッ ク R 比率はフ レーム全体の間隔で一定です。 G お よ び B 値に対 し て も 同 じ 方法で、調整後の値が 求め ら れます。 ピ ク セルは ク ロ ッ ク サ イ ク ルご と に同時に乗算 さ れます。 CTC モジ ュ ールが次のモジ ュ ール、PGC (正確なガ ン マ補正) ブ ロ ッ ク にデー タ を送信で き る 状態にな る と 、CTC_PGC_DATA_RDY フ ラ グがアサー ト さ れます。

DIP

ス イ ッ チの設定

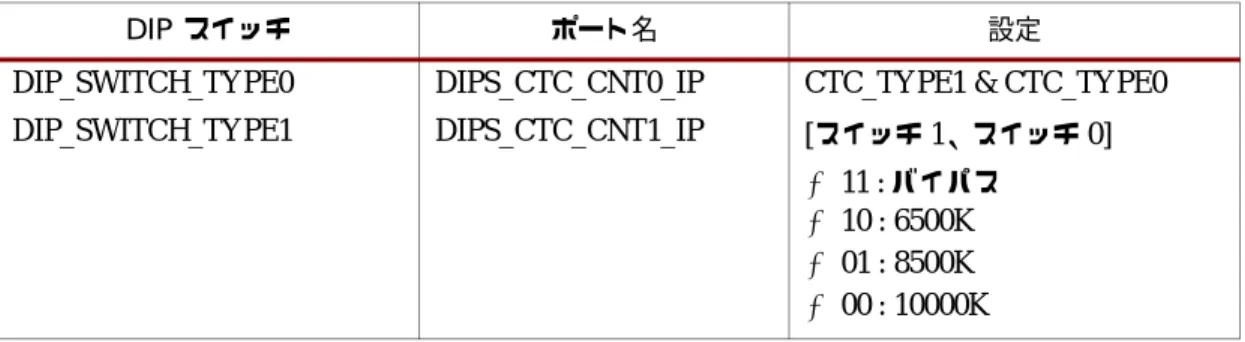

表5に、 色温度を調整す る 際の DIP ス イ ッ チの設定を示 し ます。CTC

モ ジ ュ ールのデバイ ス使用率

表6に、CTC モジ ュ ールが使用す る リ ソ ー ス のサマ リ を示 し ま す。こ れ ら の値は、 デ ィ ス プ レ イ 開発 ボー ド 上の Spartan-3E XC3S1600E FG484 FPGA に基づ く も のです。表 5 : CTC モ ジ ュ ールの DIP ス イ ッ チ設定 DIP ス イ ッ チ ポー ト 名 設定 DIP_SWITCH_TYPE0 DIP_SWITCH_TYPE1 DIPS_CTC_CNT0_IP DIPS_CTC_CNT1_IP

CTC_TYPE1 & CTC_TYPE0 [ス イ ッ チ 1、 ス イ ッ チ 0] • 11 : バ イ パ ス • 10 : 6500K • 01 : 8500K • 00 : 10000K 表 6 : CTC モ ジ ュ ールの リ ソ ース使用率 使用数 利用可能数 使用率 ロ ジ ッ ク使用率 ス ラ イ ス の フ リ ッ プ フ ロ ッ プ数 5,275 29,504 18% 4 入力 LUT 数 3,579 29,504 12% 4 入力 LUT 総数 3,664 29,504 12% ロ ジ ッ ク と し ての使用数 3,579 ルー ト スルー と し ての使用数 1 シ フ ト レ ジ ス タ と し ての使用数 84 ボ ンデ ィ ン グ さ れた IOB 数 58 376 15% ブ ロ ッ ク RAM 数 4 36 11% MULT18X18 数 4 36 11% GCLK 数 1 24 4% ロ ジ ッ ク分散 使用ス ラ イ ス数 3,423 14,752 23% 関連 ロ ジ ッ ク のみを含むス ラ イ ス数 3,423 3,423 100% 関連がない ロ ジ ッ ク のみを含むス ラ イ ス数 0 3,423 0%

R

wtR

⁄ wfPGC (正確なガ ン マ補正) R

PGC (

正確なガ ン

マ補正

)

ガ ン マについて

デ ィ ス プ レ イ シ ス テ ム でエン コ ー ド さ れた輝度 と 表示 さ せたい画像の明度の間には、 ガ ン マ特性 と い う 指数の関係があ り ます。こ の関係は数学的な汎用関数では、 出力 = 入力関数^ (ガ ン マ) と し て表 さ れ、 逆関数に よ っ て、 表示 さ れ る 前のデー タ があ ら か じ め補正で き ます。 入力 と 出力明度は、 多 く のデ ィ ス プ レ イ において非線形関係であ る ため、 ガ ン マ補正が必要 と な り ます。 ま た、 こ の補正に よ っ て知覚 さ れ る 画像の品質を向上 さ せ る こ と がで き ます。 未補正の画像や誤っ たガ ン マ補正を施 し た画像は、 コ ン ト ラ ス ト が不鮮明にな っ た り 、 色バ ラ ン ス が悪 く 、 全体的な光の レベルが不適切にな っ た り し ます。 さ ら に、 こ の よ う な画質の不備を ほかの方法で修 正す る こ と は困難であ る ため、 すべての画像で最初に適切なガ ン マ を エン コ ー ド す る こ と が重要です。 た と えば、図5に示すエン コ ー ド さ れた (未補正の) 線形入力信号 Vsでは、0.1 ~ 0.4 間の知覚明度の差 が大 き く 、0.8 ~ 1.0 間の差は小 さ く な っ てい ます。 基本的にガ ン マ関数は、 こ のデ ィ ス プ レ イ の各入力 ス テ ッ プに対す る 出力明度が、 出力 I で示 よ う に線形 と な る よ う 入力に適用 さ れます。ガ ン マ補正のイ ン プ リ メ ン テーシ ョ ン

10 ビ ッ ト 出力は整数の近似値を求めやすいため、 出力を正確に調整す る には 10 ビ ッ ト 幅のガ ン マ曲線 を選択 し てい ます。 8 ビ ッ ト と 10 ビ ッ ト のガ ン マ曲線を図6 と図7に示 し ます。こ れ ら を比較 し てみて く だ さ い。 曲線には、入力ピ ク セル値に対す る ガ ン マ補正後の輝度値が示 さ れてい ます。 灰色の曲線が 8 ビ ッ ト ま たは 10 ビ ッ ト の精度の場合、 黒色の曲線が実現 し たい レ ス ポ ン ス を表 し てい ます。 図 5 : 未補正 (Vs) およびガ ン マ補正後 (I) の明度 図 6 : 8 ビ ッ ト のガ ン マ曲線 vs 実現 し たい線形レ スポン ス X928_05_040507 X928_06_040407PGC (正確なガ ン マ補正) R こ れ ら の図か ら は、8 ビ ッ ト 出力の場合は階段の よ う な関数 と な り 、10 ビ ッ ト の場合は ス ムーズで、 出 力に一致す る よ う 関数で出力 さ れてい る こ と がわか り ます。 10 ビ ッ ト のガ ン マ補正は等式2を用いて行われま し た。 等式 2 説明 : • X = RGB 入力 (8 ビ ッ ト の R、G、B 値それぞれを整数で表す) • Y = 10 ビ ッ ト のガ ン マ補正 R’、G’、B’ 出力 • ガ ン マ = ガ ン マ係数 (プ ロ グ ラ ム可能) 値の小数部が 0.5 以上の場合、Y は四捨五入 さ れて近似整数値 と な り 、 それ以外の と き は小数部が切 り 捨て ら れます。 出力は 10 ビ ッ ト 形式です。

デー タ パスの詳細説明

外部 DIP ス イ ッ チは、 入力デー タ に適用 さ れ る ガ ン マ値に設定 さ れます。 ガ ン マ関数は一連の LUT (ル ッ ク ア ッ プ テーブル) を用いて R、G、B それぞれに個別に適用 さ れ ます。 出力デー タ は R’G’B’ の 3 x 10 ビ ッ ト デー タ 形式です。 正確なガ ン マ補正が完了す る と 、 次のモジ ュ ール IDE (イ メ ージ デ ィ ザ リ ン グ エン ジ ン) に DATA_EN フ ラ グがアサー ト さ れます。 ま た、 外部 DIP ス イ ッ チを使用 し 、 こ のブ ロ ッ ク をバ イ パ ス さ せ る こ と も 可能です。 図 7 : 10 ビ ッ ト のガ ン マ曲線 vs 実現 し たい線形応答 X928_07_040507Y

ROUND

1023 X 256 ---⎝ ⎠ ⎛ ⎞ 1 Gamma ---⎝ ⎠ ⎛ ⎞ ∧ × =PGC (正確なガ ン マ補正) R 表7 に、PGC モジ ュ ールで使用 さ れ る 信号の説明を示 し ます。 図 8 : PGC のブ ロ ッ ク 図 MUX MUX MUX F/F F/F F/F F/F F/F F/F + + + MUX RED GREEN DUAL PORT_U1 BLUE SINGLE PORT_U1 ADDER_OUT_RED ADDER_OUT_GREEN ADDER_OUT_BLUE REDFF GREENFF BLUEFF REDOUT[7:0] GREENOUT[7:0] BLUEOUT[7:0] ADDRESSA ADDRESSB ADDRESSA RED[7:0] GREEN[7:0] BLUE[7:0] DIPSWITCH_INPUT 10 READY Generation Logic CTC_PGC_RDY PGC_IDE_RDY DATAEN Generation Logic PGC_IDE_DATA_EN CTC_PGC_DATA_EN BYPASSSEL RESET_N CLK X928_08_041907 01 00 表 7 : PGC モ ジ ュ ールの信号 信号 I/O 説明 RESET_N 入力 ア ク テ ィ ブ Low グ ロ ーバル リ セ ッ ト 。 非同期信号。 CLK 入力 グ ロ ーバルク ロ ッ ク 。 CTC_PGC_RDY 入力 CTC モジ ュ ールは こ の信号を アサー ト し て、 ピ ク セル デー タ が有効であ る こ と を PGC モジ ュ ールに伝え る 。 GREEN[7:0] 入力 Green 入力を含む 8 ビ ッ ト バ ス。 BLUE[7:0] 入力 Blue 入力を含む 8 ビ ッ ト バ ス。 RED[7:0] 入力 Red 入力を含む 8 ビ ッ ト バス。 CTC_PGC_DATA_EN 入力 CTC モジ ュ ールは、 フ レームの有効なデー タ ラ イ ン全体に対 し て、 こ の信号を High にアサー ト 。 BYPASSSEL 入力 PGC ブ ロ ッ ク をバ イ パス可能にす る 。 DIPSWITCH_INPUT[1:0] 入力 こ れ ら の信号に求め ら れ る ガ ン マ値を設定。

PGC (正確なガ ン マ補正) R フ リ ッ プ フ ロ ッ プ、 バ ウ ン ダ リ 信号、 レ ジ ス タ の リ セ ッ ト ス テー ト は、 すべてのビ ッ ト で ロ ジ ッ ク 「0」 です。

DIP

ス イ ッ チの設定

表8 に、 正確なガ ン マ補正を行 う 際の DIP ス イ ッ チの設定を示 し ます。PGC

モ ジ ュ ールのデバイ ス使用率

表9に、PGC モジ ュ ールが使用す る リ ソ ース のサマ リ を示 し ます。 REDOUT[9:0] 出力 PGC モジ ュ ールか ら のガ ン マ補正出力を含む 10 ビ ッ ト バ ス。 GREENOUT[9:0] 出力 PGC モジ ュ ールか ら のガ ン マ補正出力を含む 10 ビ ッ ト バ ス。 BLUEOUT[9:0] 出力 PGC モジ ュ ールか ら のガ ン マ補正出力を含む 10 ビ ッ ト バ ス。 PGC_IDE_RDY 出力 PGC モジ ュ ールは こ の信号を アサー ト し て、 ピ ク セルデー タ が有効であ る こ と を IDE モジ ュ ールに伝え る 。 PGC_IDE_DATA_EN 出力 PGC モジュ ールは、 こ の信号を High に アサート し 、 フ レ ーム の データラ イ ン 全体が有効である こ と を IDE モジュ ールに伝える 。 表 8 : PGC モ ジ ュ ールの DIP ス イ ッ チ設定 DIP ス イ ッ チ ポー ト 名 設定 DIP_SWITCH_TYPE0 DIP_SWITCH_TYPE1 ユーザース イ ッ チ SW3、SW2 DIPS_PGC_SEL0_IP DIPS_PGC_SEL1_IPPGC_TYPE1 & PGC_TYPE0 [ス イ ッ チ SW3、 ス イ ッ チ SW2] • 00 : ガ ン マは 2.2 に設定 • 01 : ガ ン マは 2.4 に設定 • 10 : ガ ン マは 2.6 に設定 • 11 : 予約済み 表 9 : PGC モ ジ ュ ールの リ ソ ース 使用数 利用可能数 使用率 ロ ジ ッ ク使用率 ス ラ イ ス の フ リ ッ プ フ ロ ッ プ数 50 29,504 1% 4 入力 LUT 数 31 29,504 1% 4 入力 LUT 総数 31 29,504 1% ボ ンデ ィ ン グ さ れた IOB 数 63 376 17% ブ ロ ッ ク RAM 数 2 36 6% GCLK 数 1 24 4% ロ ジ ッ ク分散 使用ス ラ イ ス数 42 14,752 1% 表 7 : PGC モ ジ ュ ールの信号 (続き) 信号 I/O 説明

IDE (イ メ ージデ ィ ザ リ ン グ エ ン ジ ン) R

IDE (

イ メ ージ

デ ィ ザ リ ン グ

エ ン ジ ン

)

デ ィ ザ リ ングの概要

デ ィ ザ リ ン グ と は、 限 ら れた色深度か ら 見かけ上の色深度を作成す る テ ク ニ ッ ク です。 デ ィ ザ リ ン グ さ れた画像では、 使用不可の色に対 し て、 表示可能な色か ら の ピ ク セルを組み合わせてそれに近い色が作 成 さ れます。 肉眼では、 組み合わせて作成 さ れた色は別の色 と し て認識 さ れます。 た と えば、 白色 と 黒色のみのデ ィ ス プ レ イ を使用 し 、 デ ィ ザ リ ン グに よ っ て灰色の画像が作成で き ます (図9)。 黒お よ び白の ピ ク セルを イ ン タ ーレースす る こ と で、 実際にはない灰色が作成 さ れます。 デ ィ ス プ レ イ デバ イ ス の一部には、 入力デー タ が 8 ビ ッ ト でデ ィ ス プ レ イ 色深度が 6 ビ ッ ト の よ う に、 入力デー タ よ り 小 さ い色深度 し か持た ない も のがあ り ます。入力デー タ は切 り 捨て、 あ る いは四捨五入 さ れますが、 こ の方法では通常細かい情報が失われ、 あ る 1 色の大部分が縞模様に、 オ リ ジナルの色 と は大 き く 異な る 色にな る 可能性があ り ます。デ ィ ザ リ ン グ と は、 こ の よ う な イ メ ージに対 し て行われ る 処理です。イ メ ージ

デ ィ ザ リ ングのアルゴ リ ズムについて

IDE モジ ュ ールは PGC モジ ュ ールか ら 30 ビ ッ ト (10 ビ ッ ト デー タ を R’G’B’ の 3 つ分) の ピ ク セル ス ト リ ーム を受信 し ます。 IDE は有効な ピ ク セルに対 し てのみデ ィ ザ リ ン グ を行い ます。こ のモジ ュ ールでは、10 ~ 8 ビ ッ ト に対 し て 2 x 2 のデ ィ ザ リ ン グ マ ト リ ッ ク ス を用い る 空間デ ィ ザ リ ン グ テ ク ニ ッ ク が使用 さ れます。 た と え ば、3 x 10 ビ ッ ト のデータ がブロ ッ ク に入力さ れる 場合、3 色 (R、G、B) の 2 つの LSB (最下位ビ ッ ト) は最 も 詳 し い色情報を含み、 残 り の 8 ビ ッ ト の MSB と は区別 さ れます。 切 り 捨て ら れた 2 つの LSB は事実上、 エ ラ ーです。 こ れ ら 2 ビ ッ ト は 00 ~ 11 (バ イ ナ リ) の任意の値 で、 残 り の 8 ビ ッ ト の対す る 色の レベルを 4 段階 (0%、25%、50%、75%) で表 し ます。 エ ラ ーは隣接 し た ピ ク セル全体にあ り ます。 次の例では、2 x 2 マ ト リ ッ ク ス を使用 し た ウ ェ イ ト を示 し ます。 次の例では、 上記の ウ ェ イ ト 表がデ ィ ス プ レ イ 空間全体に ど の よ う に適用 さ れ る か を示 し ます。 各 ウ ェ イ ト は実際には し き い値です。入力ピ ク セルの最後 2 ビ ッ ト の値が、 表の該当箇所の値 よ り 大 き い場合、2 つの LSB が示す値が残 り の 8 ビ ッ ト に足 さ れます。 こ の際、 その結果の 8 ビ ッ ト がオーバー フ ロ ー し ない よ う 注意す る 必要があ り ます。 図 9 : デ ィ ザ リ ングによ る新 し い色の作成 0 1 2 3 0 1 0 1 ….. 2 3 2 3 ….. 0 1 0 1 ….. 2 3 2 3 ….. . . . . …..Gray

Black, White

X928_09_040907IDE (イ メ ージデ ィ ザ リ ング エ ン ジ ン) R パ タ ーン を な く し てば ら つかせ る ため、 ウ ェ イ ト 表は 2 行ご と 、 ま たはフ レーム ご と に回転 さ せ る こ と がで き 、 こ れに よ っ て空間デ ィ ザ全体に一時的なデ ィ ザ リ ン グ を追加 し ます。 ま た、 マ ト リ ッ ク ス ウ ェ イ ト は ラ ン ダ ムに回転で き る ため、 デ ィ ザ リ ン グ処理全体が ラ ン ダ ムにな る よ う にで き ます。 こ れは、 ビデオ ス ク リ ーン デ ィ ス プ レ イ に有用な方法です。 入力デー タ の LSB を使用 し てデ ィ ザ リ ン グす る 場合、IDE では 2x2 ピ ク セルブ ロ ッ ク を用いた空間、 一時空間、 お よ び ラ ン ダ ム空間のデ ィ ザ リ ン グが実行 さ れます。 デ ィ ザ リ ン グが完了す る と 、24 ビ ッ ト のデー タ (R、G、B 各 8 ビ ッ ト) が dither_data_ready 信号 と 共 に LVDS/DVI TX イ ン タ ーフ ェ イ ス に送信 さ れます。 表10に、IDE モジ ュ ールで使用 さ れ る 信号の説明を示 し ます。 図 10 : イ メ ージデ ィ ザ リ ングエ ン ジ ンの機能ブ ロ ッ ク 図 (こ こ では 1 色のみを示す) 表 10 : IDE モ ジ ュ ールの信号 ポー ト 名 I/O 説明

RESET_N 入力 Low アサー ト に よ り 、IDE モジ ュ ールを リ セ ッ ト 。

CLK 入力 DCM (デジ タ ル ク ロ ッ ク マネージ ャ) に よ っ て生成 さ れ る シ ス テ ム ク ロ ッ ク 。 BITS_IDE_TYPE0 入力 デ ィ ザ タ イ プの選択。表11 を参照。 BITS_IDE_TYPE1 入力 デ ィ ザタ イ プの選択。表11を参照。 PGC_IDE_DATA_VALID 入力 PGC モジ ュ ールは こ の信号を アサー ト し て、 ピ ク セル デー タ が有効であ る こ と を IDE モジ ュ ールに伝え る 。 ラ イ ン全体が処理 さ れ る ま でアサー ト が維持 さ れ る 。 PGC_IDE_DATA_RDY 入力 PGC モジ ュ ールは、 ガ ン マ補正後のデー タ が使用可能 にな る と 、IDE への こ の信号をパルス さ せ る 。 PGC_IDE_RGB_PIX_DATA[29:0] 入力 PGC モジ ュ ールか ら IDE モジ ュ ールへ入力 さ れ る 、 ガ ン マ補正 さ れた 10 ビ ッ ト の R、G、Bピ ク セル デー タ は こ のバ ス に出 さ れ る 。 VIDEO_FRAME_ACTIVE 入力 High にアサー ト さ れ る と 、 有効な フ レームであ る こ と 10-bit R Bit Extractor LSB Comparator DIther Matrix Adder LSB 2 bit MSB 8 bit Energy level to be added 8-bit Dithered R CLK IDE_PIX_DATA_OP (8 bits of R) FPGA Block RAM DITHER_DATA_RDY RESET_N BITS_IDE_TYPE0 BITS_IDE_TYPE1 PGC_IDE_DATA_VALID PGC_IDE_DATA_RDY PGC_IDE_RGB_PIX_DATA VIDEO_FRAME_ACTIVE X928_10_041007

IDE (イ メ ージデ ィ ザ リ ン グ エ ン ジ ン) R

DIP

ス イ ッ チの設定

IDE モジ ュ ールは、表11に示す よ う にユーザープ ッ シ ュ ボ タ ン を設定 し 、 調整 さ れます。IDE

モ ジ ュ ールのデバイ ス使用率

表12 に、IDE モジ ュ ールが使用す る リ ソ ース のサマ リ を示 し ます。 IDE_PIX_DATA _OP[23:0] 出力 こ の出力バ ス にはデ ィ ザ リ ン グ後の 8 ビ ッ ト の RGB 値が出力 さ れ る 。 DITHER_DATA_RDY 出力 アサー ト さ れ る と 、 デ ィ ザ リ グ さ れたデー タ が使用可 能であ る こ と を示す。 表 11 : IDE モ ジ ュ ールの DIP ス イ ッ チ設定 DIP ス イ ッ チ ポー ト 名 設定 DIP_SWITCH_TYPE0 DIP_SWITCH_TYPE1 [ユーザー プ ッ シ ュ ボ タ ン PSW0、 PSW1] DIPS_IDE_TYPE0_IP DIPS_IDE_TYPE1_IPIDE_TYPE1 & IDE_TYPE0 [PSW1、PSW0] • 00 : IDE 無効 • 01 : 空間的デ ィ ザ リ ン グ • 10 : 一時空間的デ ィ ザ リ ン グ • 11 : ラ ン ダ ム デ ィ ザ リ ン グ 表 12 : IDE モ ジ ュ ールの リ ソ ース (XC3S1600EFG484 の場合) 使用数 利用可能数 使用率 ロ ジ ッ ク使用率 ス ラ イ ス の フ リ ッ プ フ ロ ッ プ数 98 29,504 1% 4 入力 LUT 数 170 29,504 1% ロ ジ ッ ク分散 使用ス ラ イ ス数 119 14,752 1% 関連 ロ ジ ッ ク のみを含むス ラ イ ス数 119 119 100% 関連がない ロ ジ ッ ク のみを含むス ラ イ ス数 0 119 0% 4 入力 LUT 総数 188 29,504 1% ロ ジ ッ ク と し て使用 さ れ る 数 170 ルー ト スルー と し て使用 さ れ る 数 18 ボ ンデ ィ ン グ さ れた IOB 数 62 376 16% GCLK 数 1 24 4% 表 10 : IDE モ ジ ュ ールの信号 (続き) ポー ト 名 I/O 説明

LVDS TX/DVI イ ン タ ー フ ェ イ ス R

LVDS TX/DVI

イ ン タ ー フ ェ イ ス

LVDS ト ラ ン ス ミ ッ タ は、28 ビ ッ ト の LVCMOS/LVTTL デー タ を 4 つの LVDS デー タ ス ト リ ームに 変換 し ます。 位相が同期 し た送信 ク ロ ッ ク が 5 つ目の LVDS リ ン ク と し て、デー タ ス ト リ ーム と 並行 し て入力 さ れ、28 ビ ッ ト の入力デー タ は、 送信 ク ロ ッ ク の各サ イ ク ルでサ ン プル さ れて送信 さ れ ま す。 Spartan-3E デ ィ ス プ レ イ 開発ボー ド には、LVDS お よ び DVI イ ン タ ーフ ェ イ ス は共に備わっ てい ます。 RGB 出力 イ ン タ ーフ ェ イ ス は、24 ビ ッ ト の RGB デー タ と 4 ビ ッ ト の タ イ ミ ン グお よ び制御信号 (ク ロ ッ ク 、HSYNC、VSYNC、 デー タ イ ネーブル) か ら 成 り ます。 LVDS ト ラ ン ス ミ ッ タ の フ ァ ン ク シ ョ ン ブ ロ ッ ク図 LVDS TX モジ ュ ール (図11) は、DCM お よ び serdes_4b_7to1 モジ ュ ールで構成 さ れてい ます。DCM は入力 ク ロ ッ ク を 3.5 逓倍 し た clkx3p5 お よ び clkx3p5not ク ロ ッ ク を生成 し ます。こ れ ら 2 つの ク ロ ッ ク は serdes_4b_7to1 モジ ュ ール内部で、28 ビ ッ ト のデー タ を 4 つの ラ イ ンにす る 7-to-1 のシ リ アル化 に使用 さ れます。 こ こ では clkx3p5 お よ び clkx3p5not ク ロ ッ ク を使用 し 、 デー タ を マルチプ レ ク スす る こ と に よ っ て 28 ビ ッ ト のデー タ ラ イ ン を 4 チ ャ ネルにす る シ リ アル化が実行 さ れます。 表13に、LVDS チ ャ ネルでのデー タ ビ ッ ト のエン コーデ ィ ン グ を示 し ます (デー タ は LSB か ら 送信 さ れます)。ト ッ プ

レ ベルか ら

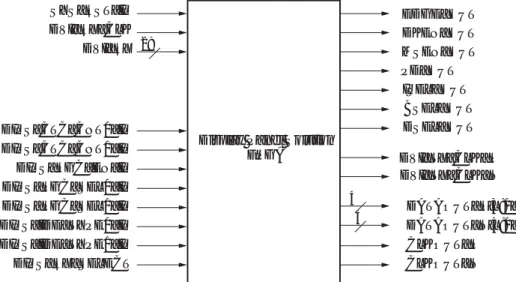

テ ス ト ベンチを含むデザ イ ン フ ァ イ ルは、 次の図に示す よ う な階層で使用 さ れます。 こ れ ら のデザ イ ン 図 11 : LVDS ト ラ ン ス ミ ッ タ のブ ロ ッ ク図 表 13 : LVDS チ ャ ネルでのデー タ ビ ッ ト のエ ン コ ー ド LVDS チ ャ ネル 入力 チ ャ ネル0 0、4、8、12、16、20、24 チ ャ ネル 1 1、5、9、13、17、21、25 チ ャ ネル2 2、6、10、14、18、22、26 チ ャ ネル 3 3、7、11、15、19、23、27 datain LVDS_TX DATAOUT_P[3:0] CLKOUT_P DATAOUT_N[3:0] CLKOUT_N clkin TTL to LVDS Input Buffer Digital Clock Manager Data_Reg._p clkx3P5not Data_Reg._n DDR Registers clkx3P5 DataSync and Mux Selection mux X928_11_041007ト ッ プ レ ベルのデバイ ス使用率 R

ト ッ プ

レ ベルの

デバイ ス使用率

表14 に、 シ ス テ ム全体の合成結果を示 し ます。 図 12 : モ ジ ュ ール階層 X928_12_041007 表 14 : シ ス テム全体の合成結果 使用数 利用可能数 使用率 ロ ジ ッ ク使用率 ス ラ イ ス レ ジ ス タ 総数 5,748 29,504 19% フ リ ッ プ フ ロ ッ プ と し ての使用数 5,743 ラ ッ チ と し ての使用数 5 4 入力 LUT 数 3,878 29,504 13% ロ ジ ッ ク と し ての使用数 3,878 ルー ト スルー と し ての使用数 33 シ フ ト レ ジ ス タ と し ての使用数 88 4 入力 LUT 総数 3,999 29,504 14% ボ ンデ ィ ン グ さ れた IOB 数 93 376 25% ブ ロ ッ ク RAM 数 6 36 17% MULT18X18 数 4 36 11% GCLK 数 7 24 24% DCM 数 3 8 38% RPM マ ク ロ 数 2 ロ ジ ッ ク分散 使用ス ラ イ ス数 3,709 14,752 25% 関連 ロ ジ ッ ク のみを含むス ラ イ ス数 3,709 3,709 100% 関連がない ロ ジ ッ ク を含むス ラ イ ス数 0 3,821 0%シ ス テムレ ベルのI/O 信号 R

シ ス テム

レ ベルの

I/O

信号

図13に、Spartan-3E FPGA を使用 し たデ ィ ス プ レ イ パネルソ リ ュ ーシ ョ ンの I/O 図を示 し ます。

CORE 仕様か ら 次に信号 タ イ プが使用 さ れてい ます。 • I : 入力は標準の入力専用信号 • O : 出力は標準出力 ま た、 次の信号命名規則に従っ てい ます。 • すべてのア ク テ ィ ブ Low 信号に 「_N」 接尾辞が付 く • 接尾辞 「+」 は差動信号の正側であ る こ と を表す • 接尾辞 「-」 は差動信号の負側であ る こ と を表す 表15で Spartan-3E デ ィ ス プ レ イ 開発ボー ド の信号について説明 し ます。 図 13 : FPGA でのデ ィ ス プ レ イ パネル ソ リ ュ ーシ ョ ンの I/O 図 表 15 : デ ィ ス プ レ イ開発ボー ド で使用 さ れる信号 信号 I/O 説明 シ ス テム信号 SYS_RST_IP 入力 こ のシ ス テ ム リ セ ッ ト 信号を アサー ト す る と 、 モジ ュ ール内の 全プ ロ セ ス が リ セ ッ ト さ れ る RGB 信号 DVI_RX_CLK 入力 DVI ク ロ ッ ク 入力

DVI_RX[27:0] 入力 DVI デー タ 入力 (24 ビ ッ ト RGB デー タ 、VSYNC、HSYNC、DE) LVDS デ ィ ス プ レ イ イ ン タ ー フ ェ イ ス信号

EDGE_OUT 出力 TFP410 の DVI_TX チ ッ プ専用信号 (DVI ト ラ ン ス ミ ッ タ)

DKEN_OUT 出力 TFP410 の DVI_TX チ ッ プ専用信号

MSEN_OUT 出力 TFP410 の DVI_TX チ ッ プ専用信号

PD_OUT 出力 TFP410 の DVI_TX チ ッ プ専用信号

Display Panel Solution FPGA SYS_RST_IP DVI_RX_CLK DVI_RX 28 DIPS_CTC_CNT0_IP DIPS_CTC_CNT1_IP DIPS_PGC_EN_IP DIPS_PGC_SEL0_IP DIPS_PGC_SEL1_IP DIPS_IDE_TYPE0_IP DIPS_IDE_TYPE1_IP DIPS_RX_SELECT EDGE_OUT DKEN_OUT MSEN_OUT PD_OUT ISEL_OUT BSEL_OUT DSEL_OUT DVI_TX_CLK_P DVI_TX_CLK_N 4 4 DATAOUT_P[3:0] DATAOUT_N[3:0] CLKOUT_P CLKOUT_N X928_13_041907

ま と め R 図14に、VSYNC、HSYNC、DE 信号間の同期 タ イ ミ ン グ を示 し ます (メ モ : 同期極性は タ ーゲ ッ ト と な る パネルの精度に よ っ て変更で き ます)。

ま と め

こ れ ら のデザ イ ン フ ァ イ ルは、ザ イ リ ン ク ス が提供す る 非常に優れた開発ボー ド での一連のビデオ処理 アルゴ リ ズ ム を表 し 、 デ ィ ス プ レ イ 開発プ ロ グ ラ ムの設計開始をサポー ト し ます。 ど のザ イ リ ン ク ス デ バ イ ス を タ ーゲ ッ ト と し ていて も 、 すべての IP ブ ロ ッ ク が必要に応 じ て カ ス タ マ イ ズ可能です。 こ の シ ス テ ムには、 さ ら に新 し いビデオ処理ブ ロ ッ ク が追加で き 、 ご自身のビデオ拡張アルゴ リ ズ ムが簡単 に確認で き ます。付録

:

LVDS

タ イ ミ ング

詳細は、XAPP486 : 『Spartan-3E FPGA におけ る 最高レー ト 666 Mbps での 7:1 のシ リ アル化』 を参 照 し て く だ さ い。

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。DSEL_OUT 出力 TFP410 の DVI_TX チ ッ プ専用信号

DVI_TX[27:0] 出力 DVI デー タ 出力 (24 ビ ッ ト RGB デー タ 、VSYNC、HSYNC、DE)

DVI_TX_CLK 出力 DVI 出力 ク ロ ッ ク DVI_TX_CLK_N 出力 TFP410 の DVI_TX チ ッ プ専用信号 LVDS TX 信号 DATA_OUT_P[3:0] DATA_OUT_N[3:0] 出力 LVDS 差動出力ペア CLKOUT_P CLKOUT_N 出力 LVDS ク ロ ッ ク 出力ペア 図 14 : リ フ ァ レ ン スデザイ ンにおけ る信号の関係 表 15 : デ ィ ス プ レ イ開発ボー ド で使用 さ れる信号 (続き) 信号 I/O 説明 vsync_b vsync_e VSYNC HSYNC x=0; y=0 DE X928_14_041007 日付 バージ ョ ン 改訂内容 2007/03/23 1.0 初版 リ リ ース 2007/04/19 1.1 文書お よ び図の微調整