Spartan-6 FPGA

PCB

デザイ ンおよび

ピ ン配置ガ イ ド

display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2009–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. 本資料は英語版 (v1.2) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。 日本語版は参考用 と し て ご使用の上、 最新情報につ き ま し ては、 必ず最新英語版を ご参照 く だ さ い。

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。 日付 バージ ョ ン 改訂内容 2009 年 9 月 21日 1.0 初版 リ リ ース 2010 年 4 月 29 日 1.1 こ のユーザーガ イ ド の タ イ ト ルを変更。第 6 章お よ び付録 A を追加。表2-1 を差 し 替え。 2010 年 7 月 15 日 1.2 表2-1に示す値を変更。 脚注 3 を追加。 第 6 章の 「HSWAPEN ピ ンお よ び VREFピ ン」を追加。改訂履歴. . . 2

このユーザー

ガ イ ド について

ユーザーガ イ ド の内容 . . . 7 その他の資料. . . 7 その他の リ ソ ース . . . 8第

1

章

: PCB

技術の基礎知識

PCB の構造 . . . 9 ト レース. . . .9 プ レーン. . . .9 ビ ア. . . .10 パ ッ ド と ア ンチパ ッ ド . . . .10 ラ ン ド. . . .10 寸法. . . .10 伝送 ラ イ ン. . . 11 リ タ ーン電流. . . 12第

2

章

:

電源分配シ ス テム

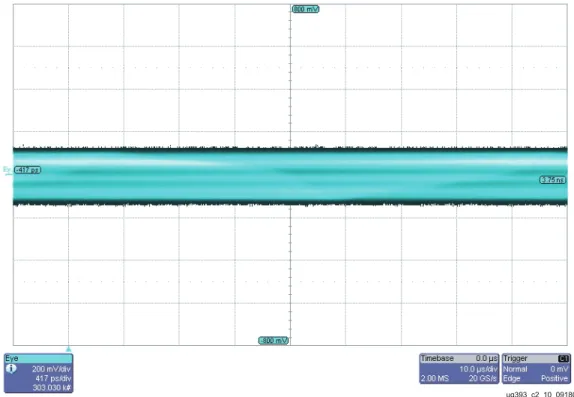

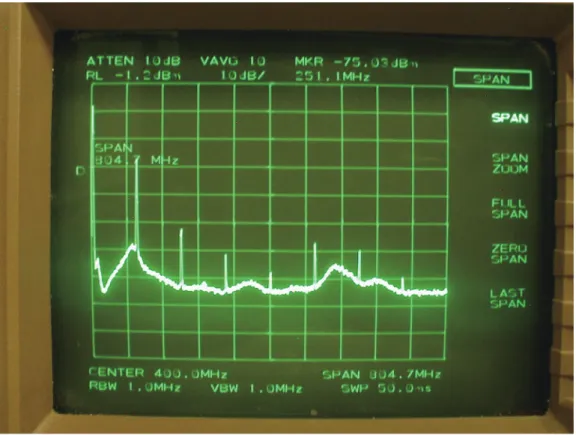

PCB デカ ッ プ リ ン グキ ャ パシ タ . . . 13 各デバ イ ス の推奨キ ャ パシ タ. . . .13 必要な PCB キ ャ パシ タ の数. . . .14 キ ャ パシ タ の仕様. . . .16 PCB バル ク キ ャ パシ タ. . . .16 PCB 高周波キ ャ パシ タ . . . .16 キ ャ パシ タ を ま と め る 場合の条件. . . .17 PCB キ ャ パシ タ の配置 と 実装方法 . . . .17 PCB バル ク キ ャ パシ タ. . . .17 0805 セ ラ ミ ッ ク キ ャ パシ タ. . . .18 0402 セ ラ ミ ッ ク キ ャ パシ タ. . . .19 PDS の基本的な考え方 . . . 20 ノ イ ズの上限 . . . .20 イ ン ダ ク タ ン ス の役割 . . . .22 キ ャ パシ タ の寄生 イ ン ダ ク タ ン ス. . . .22 PCB 電流パ ス の イ ン ダ ク タ ン ス . . . .24 キ ャ パシ タ の実装に よ る イ ン ダ ク タ ン ス . . . .24 プ レーンの イ ン ダ ク タ ン ス . . . .25 FPGA の実装に よ る イ ン ダ ク タ ン ス. . . .26 PCB ス タ ッ ク ア ッ プ と 基板層の順序 . . . .27 キ ャ パシ タ の有効周波数帯域. . . .27 キ ャ パシ タ の反共振. . . .29 キ ャ パシ タ の配置に関す る 基礎. . . .29 VREF 安定化キ ャ パシ タ . . . .30 電源の共通化 . . . .31 未接続の VCCO ピ ン. . . .31 シ ミ ュ レーシ ョ ン方法. . . 31 PDS の計測 . . . 32 ノ イ ズ量の計測 . . . .32 ノ イ ズスペ ク ト ラ ムの計測. . . .34 デカ ッ プ リ ン グネ ッ ト ワー ク の最適化. . . .36目次

例 3 : PCB の I/O 信号の強度が必要以上に大 き い . . . .37 例 4 : I/O 信号の リ タ ーン電流のパ ス が最適でない . . . .37

第

3

章

: SelectIO

のシグナ リ ング

イ ン タ ーフ ェ イ ス の種類. . . 39 シ ン グルエン ド イ ン タ ーフ ェ イ ス と 差動 イ ン タ ーフ ェ イ ス . . . .39 SDR イ ン タ ーフ ェ イ ス と DDR イ ン タ ーフ ェ イ ス. . . .40 シ ン グルエン ド シ グナ リ ン グ. . . 40 モー ド と 属性 . . . .40 入力 し き い値 . . . .40第

4

章

: PCB

材料 と ト レース

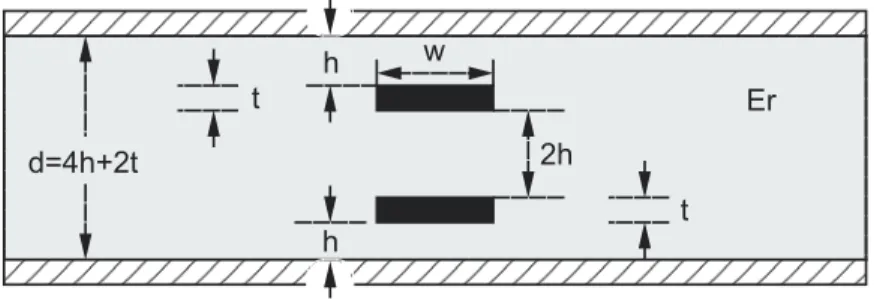

目的の帯域幅. . . 41 誘電損失. . . 41 比誘電率. . . .41 誘電正接. . . .42 表皮効果 と 抵抗損失. . . .42 基板材料の選択 . . . .42 ト レース. . . 43 ト レース の形状 . . . .43 高速 ト ラ ン シーバにおけ る ト レース の特性 イ ン ピーダ ン スデザ イ ン . . . .43 ト レース配線 . . . .45 プ レーン分割 . . . .45 リ タ ーン電流 . . . .45 損失性伝送 ラ イ ンのシ ミ ュ レーシ ョ ン . . . .46 ケーブル. . . 46 コ ネ ク タ . . . .46 導体間の ス キ ュ ー. . . .46第

5

章

:

高速信号 ト ラ ン ジ シ ョ ン を考慮 し たデザイ ン

過剰容量 と イ ン ダ ク タ ン ス. . . 47 TDR (時間領域反射測定) 法 . . . 47 BGA パ ッ ケージ. . . 49 SMT パ ッ ド. . . 49 差動ビ ア. . . 54 P/N ク ロ ス オーバービ ア . . . 56 SMA コ ネ ク タ. . . 56 バ ッ ク プ レーン コ ネ ク タ . . . 56 マ イ ク ロ ス ト リ ッ プ/ス ト リ ッ プ ラ イ ンの曲げ角度 . . . 56第

6

章

: I/O

ピ ンおよび ク ロ ッ クの配置

コ ン フ ィ ギ ュ レーシ ョ ン. . . 61 コ ン フ ィ ギ ュ レーシ ョ ン ピ ンの配置に関す る 考慮事項 . . . .61 多機能 コ ン フ ィ ギ ュ レーシ ョ ン . . . .61 コ ン フ ィ ギ ュ レーシ ョ ン オプシ ョ ン . . . .62 HSWAPEN ピ ンお よ び VREFピ ン. . . .62 メ モ リ コ ン ト ロ ー ラブ ロ ッ ク . . . 63 MCB ピ ンの配置に関す る 考慮事項 . . . .63 MCB ク ロ ッ キ ン グに関す る 考慮事項. . . .63 PCI. . . 64GTP ト ラ ン シーバ. . . 64 GTP ト ラ ン シーバピ ンの配置に関す る 考慮事項. . . .64 GTP ト ラ ン シーバの ク ロ ッ キ ン グに関す る 考慮事項. . . .64 PCI Express . . . .65 その他の GTP ト ラ ン シーバベース のツール. . . .65 グ ロ ーバルク ロ ッ キ ン グ と I/O ク ロ ッ キ ン グ. . . 65 GCLK ピ ンの割 り 当て. . . .65 BUFIO2 I/O ク ロ ッ クバ ッ フ ァ の使用法 . . . .66 イ ン タ ーフ ェ イ ス の種類に応 じ た BUFIO2 リ ソ ース の使用法の概要. . . .66 双方向 I/O . . . .67 イ ン タ ーフ ェ イ ス のシ リ ア ラ イ ズ. . . 67 ピ ン配置に関す る 考慮事項 . . . .67 シ ン グルエン ド SerDes . . . .67 差動 SerDes . . . .67 パ ワーマネージ メ ン ト - Suspend/Awake の使用 . . . 68 I/O 規格 と I/O バン ク の規則. . . 68 同時ス イ ッ チ出力 (SSO) の管理. . . 68 デザ イ ンルールチ ェ ッ ク の実行 . . . 68 集積度の異な る デバ イ スへの移行. . . 69

付録

A :

推奨する

PCB

デザイ ン

ルール

QFP パ ッ ケージでの推奨す る PCB デザ イ ンルール. . . 71 BGA/CSP パ ッ ケージでの推奨す る PCB デザ イ ンルール. . . 72こ のユーザー

ガ イ ド について

こ のユーザーガ イ ド では、PCB お よ び イ ン タ ーフ ェ イ ス レベルのデザ イ ン を決定す る 際の指針を 中心に、Spartan®-6 デバ イ ス の PCB デザ イ ンに関す る 情報を提供 し ます。ユーザー

ガ イ ド の内容

こ のガ イ ド は、 次の章か ら 構成 さ れてい ます。 • 第 1 章 「PCB 技術の基礎知識」 では、 最新の PCB 技術の基礎について、 特に物理的構造物 と 一般的な前提知識を中心に説明 し ます。 • 第 2 章 「電源分配シ ス テ ム」 では、Spartan-6 FPGA の電源分配シ ス テ ムについて、 デカ ッ プ リ ン グキ ャ パシ タ の選択、 電圧レ ギ ュ レー タ の使用 と PCB ジオ メ ト リ 、 シ ミ ュ レーシ ョ ンお よ び計測な ど の内容を詳 し く 説明 し ます。• 第 3 章 「SelectIO のシ グナ リ ン グ」 では、SelectIO™ 規格、I/O ト ポグ ラ フ ィ 、 終端を選択す

る 際の指針、 お よ びシ ミ ュ レーシ ョ ン と 計測の方法について説明 し ます。 • 第 4 章 「PCB 材料 と ト レース」では、 信号劣化を抑えて高周波アプ リ ケーシ ョ ン で最大限の性 能を引 き 出すためのガ イ ド ラ イ ン を紹介 し ます。 • 第 5 章 「高速信号 ト ラ ン ジシ ョ ン を考慮 し たデザ イ ン」 では、 伝送 ラ イ ン終端の イ ン タ ーフ ェ イ ス について説明 し ます。 こ の章に記載 さ れた解析結果や例を参考にす る と 、 デザ イ ン期間を 大幅に短縮で き ます。

その他の資料

次の資料 も 、http://japan.xilinx.com/support/documentation/spartan-6.htmか ら ダ ウ ン ロー ド で き ます。 • 『Spartan-6 フ ァ ミ リ 概要』 Spartan-6 フ ァ ミ リ の特徴 と 製品群の概要を説明 し てい ます。 • 『Spartan-6 FPGA デー タ シー ト: DC 特性お よ びス イ ッ チ特性』 Spartan-6 フ ァ ミ リ の DC 特性お よ びス イ ッ チ特性の仕様が記載 さ れてい ます。 • 『Spartan-6 FPGA パ ッ ケージお よ びピ ン配置仕様』 デバ イ ス/パ ッ ケージの組み合わせお よ び最大 I/O 数の表、 ピ ン定義、 ピ ン配置表、 ピ ン配置図、 機械的図面、 温度仕様が記載 さ れてい ます。• 『Spartan-6 FPGA コ ン フ ィ ギ ュ レーシ ョ ンガ イ ド 』

こ の包括的な コ ン フ ィ ギ ュ レーシ ョ ンガ イ ド は、 コ ン フ ィ ギ ュ レーシ ョ ンイ ン タ ーフ ェ イ ス (シ リ アル と パ ラ レル)、 マルチビ ッ ト ス ト リ ームの管理、 ビ ッ ト ス ト リ ームの暗号化、 バ ウ ン ダ

リ ス キ ャ ンお よ び JTAG コ ン フ ィ ギ ュ レーシ ョ ン、リ コ ン フ ィ ギ ュ レーシ ョ ンテ ク ニ ッ ク の各 章で構成 さ れてい ます。

• 『Spartan-6 FPGA SelectIO リ ソ ースユーザーガ イ ド 』

Spartan-6 の各デバ イ ス で使用可能な SelectIO™ リ ソ ース について説明 し てい ます。 • 『Spartan-6 FPGA ク ロ ッ キ ン グ リ ソ ースユーザーガ イ ド 』 Spartan-6 の各デバ イ ス で使用可能な DCM や PLL な ど の ク ロ ッ キ ン グ リ ソ ース について説 明 し てい ます。 • 『Spartan-6 FPGA コ ン フ ィ ギ ャ ブル ロ ジ ッ クブ ロ ッ ク ユーザーガ イ ド 』 Spartan-6 の各デバ イ ス で使用可能な コ ン フ ィ ギ ャ ブル ロ ジ ッ ク ブ ロ ッ ク (CLB) の機能につ いて説明 し てい ます。

• 『Spartan-6 FPGA ブ ロ ッ ク RAM リ ソ ースユーザーガ イ ド 』

Spartan-6 デバ イ ス のブ ロ ッ ク RAM の機能について説明 し てい ます。 • 『Spartan-6 FPGA DSP48A1 ス ラ イ スユーザーガ イ ド 』

Spartan-6 FPGA の DSP48A1 ス ラ イ ス のアーキ テ ク チ ャ について説明 し 、 コ ン フ ィ ギ ュ レー シ ョ ン例 も 記載 し てい ます。 • 『Spartan-6 FPGA メ モ リ コ ン ト ロ ー ラ ユーザーガ イ ド 』 Spartan-6 FPGA と 一般的な メ モ リ 規格の イ ン タ ーフ ェ イ ス を大幅に簡略化す る 専用の組み込 みマルチポー ト メ モ リ コ ン ト ロ ー ラ 、Spartan-6 FPGA メ モ リ コ ン ト ロ ー ラ ブ ロ ッ ク につい て説明 し てい ます。 • 『Spartan-6 FPGA GTP ト ラ ン シーバユーザーガ イ ド 』 Spartan-6 LXT FPGA で使用可能な GTP ト ラ ン シーバについて説明 し てい ます。

その他の リ ソ ース

シ リ コ ンや ソ フ ト ウ ェ ア、IP に関す る ア ンサーデー タ ベース を検索 し た り 、 テ ク ニ カルサポー ト の ウ ェ ブ ケース を開 く 場合は、 次の Web サ イ ト にア ク セ ス し て く だ さ い。 http://japan.xilinx.com/support/mysupport.htm第

1

章

PCB

技術の基礎知識

プ リ ン ト 回路基板 (PCB) は、そ こ に実装 さ れ る 個別部品やデバ イ ス と 同 じ く ら い複雑な電気的特性 を持つ電気的シ ス テ ム です。PCB の大部分は、PCB 設計者が自由に決定で き ますが、 技術的な理 由に よ っ て形状 (ジ オ メ ト リ) や最終的な電気的特性に制約 を 受け る こ と が あ り ま す。 こ こ では、 FPGA を使用 し た PCB デザ イ ン について、 自由に決定で き る 部分 と 制約を受け る 部分、 デザ イ ン の手法な ど を説明 し ます。 こ の章には、 次のセ ク シ ョ ンがあ り ます。 • 「PCB の構造」 • 「伝送 ラ イ ン」 • 「 リ タ ーン電流」PCB

の構造

PCB の技術は数十年前か ら ほ と ん ど変わ っ てい ません。絶縁体 と な る 基板材料 (通常は FR4 と 呼ば れ る ガ ラ ス エポキ シ基板) の両面に銅めっ き を施 し 、 銅箔の一部を エ ッ チン グで除去 し て導体の配 線を形成 し ます。 めっ き やエ ッ チン グ を施 し た基板層を、 絶縁基板を間に挟んで貼 り 合わせて積層 し ます。そ し て こ の積層基板に ド リ ルで穴を空けた後、 こ れ ら の穴に導電性のめ っ き を施 し 、 エ ッ チン グ さ れた銅箔を選択的に層間接続 し ます。 材料の特性、 使用す る 基板層数、 形状、 ド リ ル加工技術 (一部の基板層のみを貫通す る 穴加工技術 な ど) の よ う に、PCB 技術自体に進歩はあ り ますが、PCB の基本構造は昔か ら 変わっ てい ません。 PCB 技術に よ っ て形成 さ れ る 構造物 と し ては、 その物理的/電気的特徴に よ っ て ト レー ス、 プ レー ン (プ レーン レ ッ ト)、 ビ ア、 パ ッ ド に大 き く 分類 さ れます。ト レース

ト レース と は、PCB の X-Y 座標上の 2 つ以上の点を電気的に接続す る 金属製 (通常は銅) の物理的 な線状パ タ ーン をいい ます。 ト レースは、 こ れ ら 点 と 点の間で信号を伝達す る 役割を果た し ます。プ レーン

プ レーン と は、PCB の基板層全体を連続 し た面状の金属で覆っ た も のをいい ます。 こ れ と 類似 し た も ので、PCB 基板層の一部のみを連続 し た面状の金属で覆っ た も のを プ レーン レ ッ ト と いい ます。 通常、1 つの基板層には複数のプ レーン レ ッ ト があ り ます。 プ レーン と プ レーン レ ッ ト は、PCB 上 の複数の地点に電源を供給す る 役割を果た し ます。 ま た、 こ れ ら は リ タ ーン電流の伝送媒体 と な る ため、 ト レース に よ る 信号伝送に も 非常に重要な意味を持ち ます。ビ ア

ビ アは、PCB の 2 つ以上の点を Z 方向で電気的に接続す る ための金属です。 ビ アは、PCB の層間 で信号や電力を伝達す る 役割を果た し ます。 現在のめ っ き ス ルーホール (PTH) 技術では、PCB を ド リ ルで貫通 し た穴の表面にめっ き を施 し て ビ ア を形成 し ます。HDI (高密度配線接続) と も 呼ばれ る 最新のマ イ ク ロ ビ ア技術では、 レーザーを用いて基板材料を切除 し 、 導電性のめっ き を変形 し て ビ ア を形成 し ます。 マ イ ク ロ ビ アは 1、2 層程度 し か貫通で き ませんが、 ス タ ッ ク ト ビ アやス タ ッ ガー ド ビ アの場合は板厚全体に ま たが る ビ ア を形成で き ます。パ ッ ド と ア ン チパ ッ ド

め っ き ス ルーホール ビ ア は ビ ア の全長にわ た っ て導電性が あ る た め、PCB の特定の基板層の ト レース、 プ レーン、 プ レーン レ ッ ト のみを選択的に電気接続す る には何 ら かの方法が必要 と な り ま す。 こ の役割を果たすのがパ ッ ド と ア ンチパ ッ ド です。 パ ッ ド と は、 あ ら か じ め指定 さ れた形状に配置 し た小 さ な銅箔部分をいい ます。 ア ンチパ ッ ド と は、 あ ら か じ め指定 し た形状に銅箔を取 り 除いた小 さ な部分をいい ます。 パ ッ ド は、 ビ ア と 組み合わせ る こ と で、 基板表面層で表面実装部品を取 り 付け る ための導体 と し て使用す る 場合があ り ます。 ア ンチパ ッ ド は主にビ ア と 組み合わせて使用 し ます。 パ ッ ド は、 ビ ア と ト レース ま たは特定の基板層のプ レーン形状 と を電気的に接続す る ために使用 し ます。 ビ ア と PCB 基板層の ト レー ス を確実に接続す る には、 パ ッ ド を使用 し て機械的安定性を確 保す る 必要があ り ます。 パ ッ ド のサ イ ズは、 ド リ ルの許容公差/位置合わせの制約に合わせ る 必要が あ り ます。 ア ンチパ ッ ド はプ レーンで使用 し ます。 プ レーン と プ レーン レ ッ ト の銅箔は連続 し た面状 と な っ て い る ため、 こ の銅箔を ビ アが貫通す る と 電気的に接続 さ れて し ま い ます。 ビ ア と プ レーン ま たはプ レーン レ ッ ト を電気的に接続 し た く ない場合は、 その層のビ アが貫通す る 部分の周囲に、 銅箔を除 去 し た ア ンチパ ッ ド を設け ます。ラ ン ド

表面実装部品をはんだ付けす る ために表面層に設けたパ ッ ド を、 特に ラ ン ド ま たははんだ ラ ン ド と 呼びます。 通常、 ラ ン ド への電気的な接続にはビ アが必要です。 めっ き スルーホールの場合、 製造 上の制約に よ り ラ ン ド 領域の内部にビ ア を配置す る こ と はほぼ不可能です。 そ こ で、 めっ き スルー ホールの場合は短い ト レ ー ス を 使用 し て表面パ ッ ド と 接続 し ま す。 接続 ト レ ー ス の最小長 さ は、 PCB メ ーカーか ら 提供 さ れ る 最小寸法仕様に よ っ て決定 し ま す。 マ イ ク ロ ビ アには こ の制約はな く 、 はんだ ラ ン ド 領域の内部にビ ア を直接配置で き ます。寸法

PCB の寸法を決め る 大 き な要因 と し ては、 PCB 製造上の制約、FPGA パ ッ ケージの形状、 シ ス テ ム要件な ど があ り ます。 こ れ以外に、DFM (設計容易化設計) や信頼性な ど の要因 も 制約 と な り ま すが、こ れ ら は各アプ リ ケーシ ョ ンに よ っ て異な る ため、こ のユーザーガ イ ド では取 り 上げません。 こ の項 ( 「PCB の構造」 ) で説明す る PCB 構造物の形状は、FPGA パ ッ ケージの寸法 と PCB 製造 上の制約に よ っ て直接的ま たは間接的にほぼ決定 し ます。 し たがっ て、PCB 設計者は数多 く の制約 を受け る こ と にな り ます。ラ ン ドパ ッ ド の レ イ ア ウ ト はパ ッ ケージの ピ ン ま たはボールピ ッ チ (FG パ ッ ケ ージ の場合1.0mm) に よ っ て決定 し ま す。 ま た、 現在の PCB 技術では、 表面実装の最小 フ ィ ーチ ャ ーサ イ ズに よ っ てデバ イ ス直下のビ ア配置が決定 し ます。 最小ビ ア直径、 お よ びビ ア周 囲のキープア ウ ト エ リ アは各 PCB メ ーカーに よ っ て定義 さ れてい ます。 こ れ ら の直径が決定す る と 、 デバ イ ス直下のビ ア配列部分で入出力信号の配線に利用で き る ビ ア間の スペース の大 き さ も 決伝送 ラ イ ン 定 し ます。 ま た、デバ イ ス の引 き 出 し 線の最大 ト レース幅 も こ れ ら の直径に よ っ て決定 し ます。 最 小 ト レース幅 と 最小間隔は PCB 製造上の制約に よ っ て決定 し ます。 FPGA の実装に必要な PCB 基板層の数は、 信号層の数 と プ レーン層の数に よ っ て決定 し ます。 • 信号層の数は、FPGA パ ッ ケージの I/O 信号 ト レース の数に よ っ て決定 し ます (通常、 ア レ イ パ ッ ケージではパ ッ ケージのユーザー I/O の総数に従 う)。 • プ レーン層の数は、FPGA への電源供給に必要な電源プ レーン と グ ラ ン ドプ レーン、 お よ び信 号層の参照電圧 と 絶縁用に必要な電源プ レーン と グ ラ ン ド プ レーンの数に よ っ て決定 し ます。 大規模な FPGA では、4 層~ 22 層程度の PCB を使用 し ます。 通常、 基板全体の厚 さ はシ ス テ ム要件に よ っ て決定 し ます。 使用す る 基板の層数 も 決ま っ てい る た め、 各層の最大厚 さ 、 そ し て信号層やプ レーン層同士の Z 方向の間隔 も 決定 し ます。 信号 ト レース 層同士の Z 方向の間隔は ク ロ ス ト ー ク に影響を与え、信号 ト レース層 と 基準プ レーン層の Z 方向の 間隔は、 信号 ト レース の イ ン ピーダ ン ス に影響を与え ます。 ま た、 プ レーン層同士の Z 方向の間隔 は電源シ ス テ ムの寄生 イ ン ダ ク タ ン ス に影響を与え ます。 信号 ト レー ス層 と 基準プ レーン層の Z 方向の間隔 (板厚 と 基板層数に よ っ て決定) は ト レー ス の イ ン ピーダ ン ス を決定す る 大 き な要因 と な り ます。ト レース幅 (FPGA パ ッ ケージのボール ピ ッ チ と PCB ビ ア メ ー カ ーの制約に よ っ て決定) も ト レ ー ス の イ ン ピ ーダ ン ス に影響 を 与 え ま す。 特に FPGA 直下の ビ ア配列部分では、 設計者が ト レース の イ ン ピーダ ン ス を調整す る 余地はほ と ん ど あ り ま せん。 ビ ア配列の外では、 ト レー ス を太 く し て目標 と す る イ ン ピーダ ン ス (通常はシ ン グルエ ン ド で 50) に調整で き ます。 デカ ッ プ リ ン グ キ ャ パシ タ お よ びデ ィ ス ク リ ー ト 終端抵抗の配置 も ト レ ー ド オ フ で最適化す る 必 要があ り ます。DFM の制約に よ り 、FPGA (デバ イ ス の フ ッ ト プ リ ン ト) の周囲には個別部品を配 置で き ないキープア ウ ト エ リ アが定め ら れてい る こ と があ り ます。 こ のエ リ アは、 組み立てや修正 の際の スペース を確保す る ための も のです。 こ のため、 キープア ウ ト エ リ アの外側には多 く の部品 が密集す る こ と にな り ます。 ど の部品を優先 し て配置す る かは PCB 設計者が決定 し ま す。 デカ ッ プ リ ン グ キ ャ パシ タ の配置制約は、第 2 章 「電源分配シ ス テ ム」 で説明 し ます。 ま た、 終端抵抗の 配置制約は、IBIS や SPICE を使用 し たシ グナル イ ン テ グ リ テ ィ シ ミ ュ レーシ ョ ン を行っ て指定す る 必要があ り ます。

伝送ラ イ ン

信号 ト レース と 基準プ レーン を組み合わせた も のが伝送 ラ イ ン と な り ます。PCB シ ス テ ム内の I/O 信号はすべて伝送 ラ イ ン を通っ て進みます。 シ ン グルエン ド I/O イ ン タ ーフ ェ イ ス の場合、PCB 上の 2 点間で信号を伝送す る には信号 ト レース と 基準プ レーンの両方が必要です。 差動 I/O イ ン タ ーフ ェ イ ス では、2 本の ト レース と 基準プ レー ンで伝送 ラ イ ンが形成 さ れます。差動信号では厳密には基準プ レーンは不要ですが、実際の PCB に 差動 ト レース を実装す る 際には必要にな り ます。 PCB シ ス テ ム で良好な シ グナル イ ン テ グ リ テ ィ を得 る には、 伝送 ラ イ ン の イ ン ピーダ ン ス を制御 す る 必要があ り ます。 イ ン ピーダ ン スは、 ト レース の形状お よ び信号 ト レース周囲の材料や信号 ト レース と 基準プ レーン間の材料の誘電率に よ っ て決定 し ます。 ト レース と 基準プ レーン間の材料の誘電率は、PCB 絶縁層の材料の特性で決定 し ます。 基板表面の ト レース の場合は PCB を取 り 囲む気体ま たは液体の特性で決定 し ます。 一般に、PCB 積層板には FR4 の一種が使用 さ れますが、 それ以外の場合 も あ り ます。絶縁層の誘電率はボー ド に よ っ て異な り ますが、同一ボー ド 内ではほぼ一定です。し たがっ て、PCB の伝送 ラ イ ンの相対 イ ン ピーダ ン ス は ト レース の形状 と 許容値の影響を最 も 強 く 受け る こ と にな り ます。 積層板を使用 し た絶縁層の局所局所にガ ラ ス が存在す る か ど う かに よ っ て イ ン ピーダ ン ス の ば ら つ き が生 じ ますが、 こ れは高速 (>6Gb/s 以上)イ ン タ ーフ ェ イ ス以外ではほ と ん ど問題にな り ません。

リ タ ーン電流

伝送 ラ イ ン と そのシ グナルイ ン テ グ リ テ ィ を考え る 際に見落 と し がち なのが、 リ タ ーン電流です。 信号 ト レース だけで伝送 ラ イ ンが形成 さ れ る わけではあ り ません。 電流が信号 ト レース を流れ る 際 は、 その下の基準プ レーンに も 同量の対 と な る 電流が反対方向に流れます。 ト レース と 基準プ レー ンに よ っ て形成 さ れ る 伝送 ラ イ ンの特性 イ ン ピーダ ン ス は、 ト レース と 基準プ レーンの相対的な電 圧 と 電流の関係に よ っ て決定 し ます。 ト レース の下にあ る 基準プ レーンの連続性が途切れて も 信号 ト レース が分断 さ れ る こ と はあ り ませんが、 伝送 ラ イ ンの性能や基準プ レーン を共用 し てい る すべ てのデバ イ ス の性能に影響が及びます。 基準プ レーンの連続性 と リ タ ーン電流のパ ス には十分な注意が必要です。 穴、 ス ロ ッ ト 、 絶縁分割 な ど に よ っ て基準プ レーンの連続性が妨害 さ れ る と 、 信号 ト レース の イ ン ピーダ ン ス に大 き な不整 合性が生 じ ます。 基準プ レーンの不連続性は ク ロ ス ト ー ク の大 き な要因 と な る ほか、 電源分配シ ス テ ム (PDS) の ノ イ ズ源に も な り ます。 リ タ ーン電流のパ ス は非常に重要なので、 十分に注意 し て く だ さ い。第

2

章

電源分配シ ス テム

こ の章では、Spartan®-6 FPGA の PDS (電源分配シ ス テ ム) について、 デカ ッ プ リ ン グキ ャ パシ タ の選択、 配置、PCB 形状を中心に説明 し ます。 さ ら に、Spartan-6 フ ァ ミ リ の各デバ イ ス について、 シ ンプルなデカ ッ プ リ ン グの方法を紹介す る だけでな く 、 PDS デザ イ ンの基本原則、 お よ びシ ミ ュ レーシ ョ ン と 解析の方法について も 説明 し ます。 こ の章には、 次のセ ク シ ョ ンがあ り ます。 • 「PCB デカ ッ プ リ ン グキ ャ パシ タ 」 • 「PDS の基本的な考え方」 • 「シ ミ ュ レーシ ョ ン方法」 • 「PDS の計測」 • 「 ト ラ ブルシ ュ ーテ ィ ン グ」PCB

デ カ ッ プ リ ング

キ ャパシ タ

各デバイ スの推奨キ ャ パシ タ

Spartan-6 フ ァ ミ リ の各デバ イ ス のシ ンプルな PCB デカ ッ プ リ ン グネ ッ ト ワ ー ク を表2-1に示 し ます。 表2-1に示 し た以外のデカ ッ プ リ ン グ方法 も 可能ですが、 その場合は こ のデカ ッ プ リ ン グ ネ ッ ト ワー ク と 同等以上の性能のデカ ッ プ リ ン グネ ッ ト ワー ク を使用 し て く だ さ い。 別のネ ッ ト ワー ク を 使用する場合、周波数 100kHzか ら 500MHzの範囲で推奨ネ ッ ト ワー ク 以下 と する必要があ り ます。 デバ イ ス のキ ャ パシ タ ン ス要件は CLB お よ び I/O の使用状況に よ っ て異な る ため、PCB のデカ ッ プ リ ン グに関す る ガ イ ド ラ イ ンはデバ イ ス ご と に提供 さ れます。VCCINTと VCCAUXの各キ ャ パシ タ はデバ イ ス当た り の個数、VCCO キ ャ パシ タ は I/O バン ク 当た り の個で指定 さ れてい ます。 こ れ ら の推奨ネ ッ ト ワー ク を使用 し た場合、 デバ イ ス を完全に使用 し た場合の性能はど のデバ イ ス も 等 し く な り ます。必要な

PCB

キ ャパシ タ の数

表2-1に、各 VCC電源レール当た り の PCB デカ ッ プ リ ン グキ ャ パシ タ のガ イ ド ラ イ ン を示 し ます。 表 2-1 : 各デバイ スに必要な PCB キ ャ パシ タ の個数(1) (3) パッケージデバイ ス (XC6S) VCCINT (µF) VCCAUX (µF) VCCO バン ク 0 (µF) VCCO バン ク 1 (µF) VCCO バン ク 2 (µF) VCCO バン ク 3 (µF) VCCO バン ク 4 (µF) VCCO バン ク 5 (µF) 合計(2) 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 TQG144 LX4 0 2 1 0 7 1 0 1 2 0 1 2 0 1 2 0 1 2 23 TQG144 LX9 0 3 1 0 7 1 0 1 2 0 1 2 0 1 2 0 1 2 24 CPG196 LX4 0 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 18 CPG196 LX9 0 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 19 CPG196 LX16 0 5 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 21 CSG225 LX4 0 2 1 1 1 2 1 1 1 1 1 1 1 1 1 1 1 1 19 CSG225 LX9 0 3 1 1 1 2 1 1 1 1 1 1 1 1 1 1 1 1 20 CSG225 LX16 0 5 1 1 1 2 1 1 1 1 1 1 1 1 1 1 1 1 22 CSG324 LX9 1 3 1 1 1 3 1 1 2 1 1 2 1 1 2 1 1 2 26 CSG324 LX16 0 5 1 1 1 3 1 1 2 1 1 2 1 1 2 1 1 2 27 CSG324 LX25 1 1 1 1 1 3 1 1 2 1 1 2 1 1 2 1 1 2 24 CSG324 LX25T 1 1 1 1 1 2 1 1 1 1 1 2 1 1 2 1 1 2 22 CSG324 LX45 1 1 2 1 1 3 1 1 2 1 1 2 1 1 2 1 1 2 25 CSG324 LX45T 1 1 2 1 1 2 1 1 1 1 1 2 1 1 2 1 1 2 23 FT(G)256 LX9 1 3 1 1 1 2 1 1 1 1 1 2 1 1 1 1 1 2 23 FT(G)256 LX16 0 5 1 1 1 2 1 1 1 1 1 2 1 1 1 1 1 2 24 FT(G)256 LX25 1 1 1 1 1 2 1 1 1 1 1 2 1 1 1 1 1 2 21 CSG484 LX45 1 1 2 1 2 4 1 1 2 1 1 4 1 1 2 1 1 4 31 CSG484 LX45T 1 1 2 1 2 4 1 1 1 1 1 3 1 1 2 1 1 4 29 CSG484 LX75 1 2 3 1 2 4 1 1 2 1 1 4 1 1 2 1 1 4 33 CSG484 LX75T 1 2 3 1 2 4 1 1 1 1 1 3 1 1 2 1 1 4 31 CSG484 LX100 1 2 4 1 2 4 1 1 2 1 1 4 1 1 2 1 1 4 34 CSG484 LX100T 1 2 4 1 2 4 1 1 2 1 1 3 1 1 3 1 1 3 33 CSG484 LX150 2 3 6 1 2 4 1 1 2 1 1 4 1 1 2 1 1 4 38 CSG484 LX150T 2 3 6 1 2 4 1 1 1 1 1 3 1 1 2 1 1 4 36 FG(G)484 LX25 1 1 1 1 2 3 1 1 2 1 1 2 1 1 3 1 1 2 26 FG(G)484 LX25T 1 1 1 1 2 3 1 1 2 1 1 2 1 1 3 1 1 2 26 FG(G)484 LX45 1 1 2 1 2 4 1 1 2 1 1 3 1 1 4 1 1 3 31PCB デ カ ッ プ リ ングキ ャパシ タ FG(G)484 LX45T 1 1 2 1 2 4 1 1 2 1 1 3 1 1 3 1 1 3 30 FG(G)484 LX75 1 2 3 1 2 4 1 1 2 1 1 3 1 1 4 1 1 3 33 FG(G)484 LX75T 1 2 3 1 2 4 1 1 2 1 1 3 1 1 3 1 1 3 32 FG(G)484 LX100 1 2 4 1 2 4 1 1 2 1 1 3 1 1 3 1 1 3 33 FG(G)484 LX100T 1 2 4 1 2 4 1 1 2 1 1 3 1 1 3 1 1 3 33 FG(G)484 LX150 2 3 6 1 2 4 1 1 2 1 1 3 1 1 3 1 1 3 37 FG(G)484 LX150T 2 3 6 1 2 4 1 1 2 1 1 3 1 1 3 1 1 3 37 FG(G)676 LX45 1 1 2 1 2 5 1 1 3 1 1 3 1 1 3 1 1 4 33 FG(G)676 LX75 1 2 3 2 3 6 1 1 3 1 1 3 1 1 3 1 1 3 1 1 2 1 1 2 45 FG(G)676 LX75T 1 2 3 1 2 5 1 1 3 1 1 2 1 1 3 1 1 2 1 1 2 1 1 2 40 FG(G)676 LX100 1 2 4 2 3 6 1 1 3 1 1 3 1 1 3 1 1 3 1 1 2 1 1 2 46 FG(G)676 LX100T 1 2 4 1 2 5 1 1 3 1 1 2 1 1 3 1 1 2 1 1 2 1 1 2 41 FG(G)676 LX150 2 3 6 2 3 6 1 1 3 1 1 3 1 1 3 1 1 3 1 1 2 1 1 2 50 FG(G)676 LX150T 2 3 6 1 2 5 1 1 3 1 1 2 1 1 3 1 1 2 1 1 2 1 1 2 45 FG(G)900 LX100T 1 2 4 2 3 6 1 1 3 1 1 3 1 1 3 1 1 4 1 1 2 1 1 2 47 FG(G)900 LX150 2 3 6 2 4 7 1 1 5 1 1 3 1 1 5 1 1 4 1 1 2 1 1 2 57 FG(G)900 LX150T 2 3 6 2 3 7 1 1 4 1 1 3 1 1 4 1 1 4 1 1 2 1 1 2 54 メ モ : 1. PCB キ ャ パシ タ の仕様は表2-2に記載 し てい ます。 2. 合計欄には、 デバ イ ス の I/O バン ク 数 も 考慮に入れた上で、 電源すべてのキ ャ パシ タ の総数を記載 し てい ます。 3. こ のガ イ ド ラ イ ンでは、 旧版にあ っ た 100µFキ ャ パシ タ のい く つかが取 り 除かれてい ます。 ま た、4.7µFキ ャ パシ タ が増え てい る ため、 必要な総個数 も 増え てい る こ と があ り ます。 旧版、 新版の両方 と も 有効であ り 、 ど ち ら を使っ て も か ま い ませんが、 こ こ に示 し た個数に す る こ と に よ り 、 部品 コ ス ト が抑え ら れます。 表 2-1 : 各デバイ スに必要な PCB キ ャ パシ タ の個数(1) (続き) (3) パッケージデバイ ス (XC6S) VCCINT (µF) VCCAUX (µF) VCCO バン ク 0 (µF) VCCO バン ク 1 (µF) VCCO バン ク 2 (µF) VCCO バン ク 3 (µF) VCCO バン ク 4 (µF) VCCO バン ク 5 (µF) 合計(2) 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47 100 4.7 0.47

キ ャパシ タ の仕様

こ こ では、表2-1に示 し た キ ャ パシ タ の電気的特性について説明 し ます。表2-2は PCB バル ク キ ャ パシ タ と 高周波キ ャ パシ タ の特性を一覧に し た も ので、 表の下にはほかのキ ャ パシ タ で代用す る 場 合のガ イ ド ラ イ ン を記載 し てい ます。 各キ ャ パシ タ の欄に記載 し た ESR (等価直列抵抗) の範囲は 変更可能です。 ただ し その場合、 最終的な電源分配シ ス テ ムの イ ン ピーダ ン ス を解析 し て共振 イ ン ピーダ ン ス の ス パ イ ク が発生 し ない よ う 注意す る 必要があ り ます。PCB

バルク

キ ャパシ タ

バル ク キ ャ パシ タ の目的は、 電圧レ ギ ュ レー タ の動作周波数の上限 (~100kHz)か ら 高周波キ ャ パ シ タ の動作周波数の下限 (~2MHz)ま での低周波領域を カバーす る こ と にあ り ます。表2-1に示 し た よ う に、 すべての FPGA 電源にバル ク キ ャ パシ タ が必要です。 レ ギ ュ レー タ メ ーカーが指定す る 電圧レ ギ ュ レー タ 出力キ ャ パシ タ を使用 し てお り 、FPGA と バル ク キ ャ パシ タ の間に イ ン ダ ク タ 、 フ ェ ラ イ ト ビーズ、 チ ョ ー ク 、 その他の フ ィ ル タ がなければ、 表2-1と表2-2のバル ク キ ャ パシ タ は不要です。 ただ し 、FPGA バル ク と レ ギ ュ レー タ 出力の要件 を マージ し た場合、 こ のネ ッ ト ワー ク の総容量は表2-1 と表2-2に記載 し たバル ク の合計値以上で なければな ら ず、 レ ギ ュ レー タ メ ーカーの出力キ ャ パシ タ 要件を満た し ていなければな り ません。 表2-1に記載 し たバル ク PCB キ ャ パシ タ は、 村田製作所のセ ラ ミ ッ ク キ ャ パシ タ です。 こ のキ ャ パシ タ を選んだ理由は、 値、 サ イ ズ、 コ ス ト の面で利点があ る ためです。 ま た、 こ の製品は RoHS 指令に も 準拠 し てい ます。 他社のキ ャ パシ タ や別の種類のキ ャ パシ タ (タ ン タ ルや高性能電解キ ャ パシ タ) も 、表2-2に記載の仕様を満た し ていれば代用で き ます。PCB

高周波キ ャパシ タ

表2-2には、0805 パ ッ ケージの 4.7µFキ ャ パシ タ と 0402 ま たは 0204 パ ッ ケージの 0.47µFキ ャ パシ タ の 2 種類の高周波キ ャ パシ タ を記載 し てい ます。 特性に よ っ て、 代用で き る も の と で き ない も のがあ り ます。 詳細は、表2-2の脚注を参照 し て く だ さ い。 表 2-2 : PCB キ ャパシ タ の仕様 理想 値 値の 範囲(1) ボデ ィ サイ ズ(2) タ イ プ 最大 ESL ESR 範囲(3) 定格電圧 (4) 推奨 製品番号 100µF C > 100µF 1210 2 端子セ ラ ミ ッ ク X7R ま たは X5R 5nH 10m< ESR < 60m 6.3V GRM32ER60J107ME20L 4.7µF C > 4.7µF 0805 2 端子セ ラ ミ ッ ク X7R ま たは X5R 2nH 10m< ESR < 60m 6.3V 0.47µF C > 0.47µF 0204 ま たは 0402 2 端子セ ラ ミ ッ ク X7R ま たは X5R 1.5nH 10m< ESR < 60m 6.3V ほかの PCB キ ャ パシ タ で代用する場合の条件 1. 値が仕様以上であ る こ と 。 2. ボデ ィ サ イ ズが仕様以下であ る こ と 。 3. ESR が仕様の範囲内であ る こ と 。 4. 定格電圧が仕様以上であ る こ と 。PCB デ カ ッ プ リ ングキ ャパシ タ

キ ャパシ タ を ま と める場合の条件

複数の I/O バン ク に 1.8V な ど共通の電圧か ら 電源を供給す る こ と があ り ますが、 推奨ガ イ ド ラ イ ンでは こ の よ う な場合に複数のバル ク キ ャ パシ タ を必要 と し ます。大規模なデバ イ ス の VCCINT と VCCAUXについて も 同様です。こ の よ う な複数のキ ャ パシ タ を値の大 き い少数のバル ク キ ャ パシ タ に ま と め る こ と がで き ますが、 その場合、 代用す る キ ャ パシ タ の電気的特性 (ESR と ESL) が推奨 キ ャ パシ タ を並列に接続 し た場合の電気的特性 と 同 じ でなければな り ません。VCCO、VCCINT、VCCAUXのキ ャ パシ タ を ま と め る 場合、ESL と ESR の値が十分に小 さ い大型の

バル ク キ ャ パシ タ (セ ラ ミ ッ ク 、 タ ン タ ル、 ま たは高性能電解キ ャ パシ タ) は容易に入手で き ます。 高周波キ ャ パシ タ の場合、 ア ク セ スす る PCB ビ アの数に よ っ て キ ャ パシ タ の効果が変化す る ため、 複数のキ ャ パシ タ を 1 つに ま と め る こ と はで き ません。 例 こ こ では、 あ る FPGA の イ ン タ ーフ ェ イ ス が 3 つの I/O バン ク に ま たがっ てお り 、 こ れ ら すべての I/O バン ク が共通の電圧で動作す る 場合を例に説明 し ます。表2-1には、各バン ク に 100µFの PCB キ ャ パシ タ が 1 つ必要 と 記載 さ れてい ます。 こ の場合、330µFのキ ャ パシ タ を使用すれば 100µFの キ ャ パシ タ 3 つを 1 つに ま と め る こ と がで き ます。 こ の と き 、 次の こ と が言え ます。 • 代用キ ャ パシ タ の ESL は指定キ ャ パシ タ の 1/3 でなければな り ません。5nHのキ ャ パシ タ 3 つは 1.7nHのキ ャ パシ タ 1 つに相当 し ます。 つま り 、330µFのキ ャ パシ タ の ESL が 1.7nH 未満な ら 代用可能です。 • 代用キ ャ パシ タ の ESR は指定キ ャ パシ タ の 1/3 でなければな り ません。10m ~ 60m の範 囲 の キ ャ パ シ タ 3 つ は 3.3m ~ 20m の範囲の キ ャ パ シ タ 1 つ に 相当 し ま す。 つ ま り 、 330µFのキ ャ パシ タ の ESL が こ の範囲であれば代用可能です。

• ESL が3nH、ESR が20mの 100µFのキ ャ パシ タ 3 つは、ESL が0.5nH、ESR が15mの 330µFのキ ャ パシ タ 1 つで代用で き ます。

PCB

キ ャパシ タ の配置 と 実装方法

こ こ では、「キ ャ パシ タ の仕様」に記載 し た キ ャ パシ タ の種類ご と に配置 と 実装の方法を説明 し ます。PCB

バルク

キ ャパシ タ

バル ク キ ャ パシ タ はサ イ ズが大 き く FPGA の近 く に配置 し に く い こ と があ り ます。 し か し 、 バル ク キ ャ パシ タ がカバーす る 低周波のエネルギーはキ ャ パシ タ の位置に よ る 影響を受けに く いため、 こ の こ と は大 き な問題にはな り ません。バル ク キ ャ パシ タ は PCB の任意の位置に配置で き ますが、 可能な限 り FPGA の近 く に配置 し て く だ さ い。 キ ャ パシ タ を実装す る 際は、 通常の PCB レ イ ア ウ ト ガ イ ド ラ イ ンに従い、複数のビ ア を使用 し てで き る 限 り 広 く 短い形状で電源プ レーンに接続 し ま す。0805

セ ラ ミ ッ ク

キ ャ パシ タ

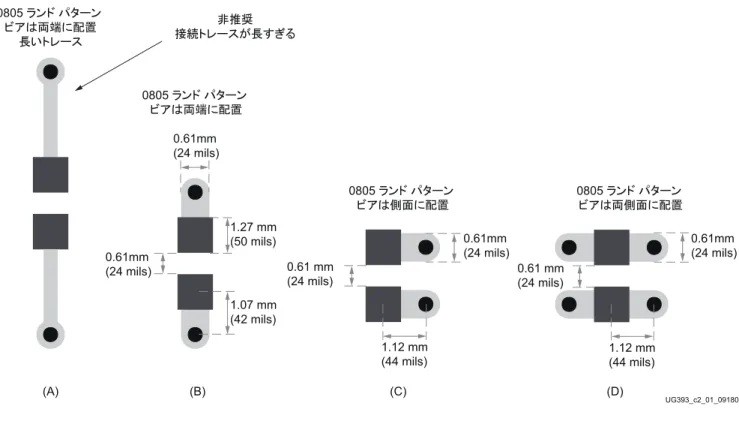

4.7µFの 0805 キ ャ パシ タ は中間の周波数領域を カバー し ます。 こ のキ ャ パシ タ は、 配置す る 位置 に よ っ て性能が変化 し ます。 可能な限 り FPGA の近 く に配置 し て く だ さ い。 デバ イ ス の外縁か ら 2 イ ンチ以内の配置 と し て く だ さ い。 キ ャ パシ タ の実装 (はんだ ラ ン ド 、 ト レース、 ビ ア) は イ ン ダ ク タ ン ス が小 さ く な る よ う に最適化す る 必要があ り ます。 ビ ア と パ ッ ド は直接接す る よ う に配置 し ます。図2-1の (B) に示す よ う にビ ア はパ ッ ド の両端に も 配置で き ますが、図2-1の (C) に示す よ う にパ ッ ド の側面に配置 し た方が良い 結果が得 ら れます。 ビ ア をパ ッ ド の側面に配置す る と ビ ア相互の誘導性結合が大 き く な り 、 実装に よ る 全体的な寄生 イ ン ダ ク タ ン ス が低減 し ます。図2-1の (D) に示す よ う にパ ッ ド の両側面にビ ア を配置す る ダブルビ アにす る と 寄生 イ ン ダ ク タ ン ス を さ ら に抑え る こ と がで き ますが、 リ タ ーン電 流が小 さ く な り ます。X-Ref Target - Figure 2-1

図 2-1 : 0805 キ ャ パシ タ のラ ン ド と 実装の形状例 0805 䊤䊮䊄 䊌䉺䊷䊮 䊎䉝䈲ਔ┵䈮㈩⟎ 㐳䈇䊃䊧䊷䉴 (A) UG393_c2_01_091809 (B) 0805 䊤䊮䊄 䊌䉺䊷䊮 䊎䉝䈲ਔ┵䈮㈩⟎ 㕖ផᅑ ធ⛯䊃䊧䊷䉴䈏㐳䈜䈑䉎 1.27 mm (50 mils) 0.61mm (24 mils) 1.07 mm (42 mils) 0.61mm (24 mils) (C) 0805 䊤䊮䊄 䊌䉺䊷䊮 䊎䉝䈲㕙䈮㈩⟎ 1.12 mm (44 mils) 0.61 mm (24 mils) 0.61mm (24 mils) (D) 0805 䊤䊮䊄 䊌䉺䊷䊮 䊎䉝䈲ਔ㕙䈮㈩⟎ 0.61mm (24 mils) 0.61 mm (24 mils) 1.12 mm (44 mils)

PCB デ カ ッ プ リ ングキ ャパシ タ

0402

セ ラ ミ ッ ク

キ ャ パシ タ

0.47µFの 0402 キ ャ パシ タ は中~高周波数領域を カバー し ます。 こ れ ら のキ ャ パシ タ では、 配置 と 実装が特に重要 と な り ます。 で き る 限 り FPGA の近 く に実装 し て、 寄生 イ ン ダ ク タ ン ス を最小限に抑え る よ う に し て く だ さ い。 板厚 < 1.575mm (62mil)の PCB の場合、 最適な配置場所は PCB 裏面のデバ イ ス フ ッ ト プ リ ン ト 内部 (ビ アのない十字型の領域) と な り ます。 目的の電源に対応 し た VCCビ ア と GND ビ アが ビ ア 配列の中で識別で き る よ う に し ておいて く だ さ い。 スペース に余裕があ る 場合は、0402 実装パ ッ ド を追加 し て こ れ ら のビ アに接続 し ます。 板厚 > 1.575mm (62mil)の PCB の場合、PCB の表面が最適な配置場所 と な る 場合 も あ り ます。 こ の場合、PCB ス タ ッ ク ア ッ プにおけ る 目的の VCCプ レ ーン の深 さ で判断 し ま す。 一方、VCCプ レーンが PCB ス タ ッ ク ア ッ プの上半分にあ る 場合は、 キ ャ パシ タ を PCB 表面に配置す る のが最適 です。VCCプ レーンが PCB ス タ ッ ク ア ッ プの下半分にあ る 場合は、 キ ャ パシ タ を PCB 裏面に配置 す る のが最適です。 0402 キ ャ パシ タ をデバ イ ス フ ッ ト プ リ ン ト の外側に配置す る 場合は、 デバ イ ス の外縁か ら 0.5 イ ンチ以内に配置 し ます (PCB 表面、 裏面いずれの場合 も)。 キ ャ パシ タ の実装 (はんだ ラ ン ド 、 ト レース、 ビ ア) は イ ン ダ ク タ ン ス が小 さ く な る よ う に最適化す る 必要があ り ます。 ビ ア と パ ッ ド は、 間に ト レース を挟まず、 直接接す る よ う に配置 し ます。 こ れ ら の ビ アは、図2-2の (C) に示す よ う に、 可能な限 り パ ッ ド の側面に配置 し て く だ さ い。 ビ ア を パ ッ ド の側面に配置す る と ビ ア相互の誘導性結合が大 き く な り 、 実装に よ る 寄生 イ ン ダ ク タ ン ス が 低減 し ます。図2-2の (D) に示す よ う にパ ッ ド の両側面にビ ア を配置す る ダブルビ アにす る と 寄生 イ ン ダ ク タ ン ス を さ ら に抑え る こ と がで き ますが、 リ タ ーン電流が小 さ く な り ます。 多 く の製造ルールでは、PCB 表面で FPGA か ら 0.1 イ ンチ以内にデバ イ ス を実装す る こ と が禁止 さ れてい ます。 ま た、 製造ルールに よ っ ては裏面の実装が禁止 さ れてい る か、 ビ ア間の狭い スペー ス に実装パ ッ ド を配置す る だけの形状が確保で き ず確実なはんだ付けがで き ない と い っ た理由で、 PCB 裏面のデバ イ ス フ ッ ト プ リ ン ト 内に キ ャ パシ タ を 配置で き な い こ と が あ り ま す。 こ れ ら の ルールがあ る と キ ャ パシ タ 配置の選択肢が狭 く な り ますが、 で き る 限 り ザ イ リ ン ク ス の配置ガ イ ド ラ イ ンに適合す る 方法を検討 し て く だ さ い。 問題があ る 場合は、PCB 製造、 組み立て、 品質管理部 門 と 話 し 合 う よ う に し て く だ さ い。PDS

の基本的な考え方

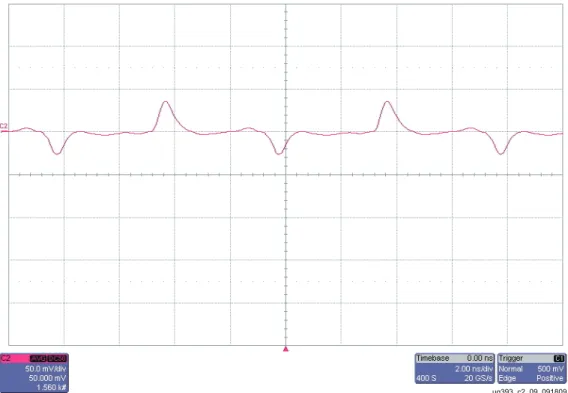

こ こ では、PDS の目的お よ び各部品の特性について説明 し ま す。 キ ャ パシ タ の配置 と 実装、PCB 形状、PCB の推奨ス タ ッ ク ア ッ プな ど の要点について も 説明 し ます。ノ イ ズの上限

シ ス テ ム内のデバ イ ス には電源シ ス テ ム に よ っ て消費 さ れ る 電流量の要件が あ る の と 同様に、 ク リ ーン な電源に関す る 要件 も あ り ます。 ク リ ーン な電源に関す る 要件 と は、 電源に存在す る ノ イ ズ 量を規定 し た も ので、 こ れは通常 リ ッ プル電圧 (VRIPPLE) と 呼ばれます。 ほ と ん ど のデジ タ ルデバ イ ス がそ う ですが、Spartan-6 FPGA で も VCC 電源の変動は標準 VCC値の ±5% 以内でなければ な り ま せん。 つ ま り 、VRIPPLEの Peak-to-Peak 値が標準 VCC の 10% を超え てはな ら ない こ と に な り ま す。以下、VCC と い う 用語は FPGA の電源 VCCINT、VCCO、VCCAUX、VREFの総称 と し て使用 し ま す。 こ こ では、 標準 VCCはデー タ シー ト に記載 さ れてい る 標準値 と 同 じ 値 と 仮定 し ま す。 そ う でない場合は、VRIPPLEを調整 し て 10% 未満に調整す る 必要があ り ます。 デジ タ ルデバ イ ス が消費す る 電力は時間に よ っ て変動 し ますが、 こ の変動はあ ら ゆ る 周波数帯で発 生す る ため、 広帯域の PDS に よ っ て電圧の安定性を維持す る こ と が必要にな り ます。 • 消費電力変動の低周波成分は、 主にデバ イ ス ま たはデバ イ ス の大部分が有効ま たは無効にな る こ と に よ っ て生 じ ます。 こ の大 き さ は短い も ので数 ミ リ 秒、 長い も ので数日の幅があ り ます。 • 消費電力変動の高周波成分は、デバ イ ス内部の個々の ス イ ッ チン グ イ ベン ト に よ っ て発生 し ま す。 こ れは、 ク ロ ッ ク 周波数お よ びその最初の数次高調波 (最大約 1GHz)で発生 し ます。 デバ イ ス の VCCの電圧レベルは一定であ る ため、 必要な電力量の変化は必要な電流量の変化 と し て現れます。PDS では、電源電圧の変化が最小限にな る よ う に電流変動を調整す る 必要があ り ます。 X-Ref Target - Figure 2-2図 2-2 : 0402 キ ャ パシ タ のラ ン ド と 実装の形状例 0402 䊤䊮䊄 䊌䉺䊷䊮 䊎䉝䈲ਔ┵䈮㈩⟎ 㐳䈇䊃䊧䊷䉴 (A) (B) (C) (D) UG393_c2_02_091809 0402 䊤䊮䊄 䊌䉺䊷䊮 䊎䉝䈲ਔ┵䈮㈩⟎ 0.381 mm (15 mils) 0.635 mm (25 mils) 1.07 mm (42 mils) 0.61mm (24 mils) 0402 䊤䊮䊄 䊌䉺䊷䊮 䊎䉝䈲ਔ㕙䈮㈩⟎ 0.762 mm (30 mils) 0.381 mm (15 mils) 0.61mm (24 mils) 0402 䊤䊮䊄 䊌䉺䊷䊮 䊎䉝䈲㕙䈮㈩⟎ 0.762 mm (30 mils) 0.381 mm (15 mils) 0.61mm (24 mils) 㕖ផᅑ ធ⛯䊃䊧䊷䉴䈏㐳䈜䈑䉎

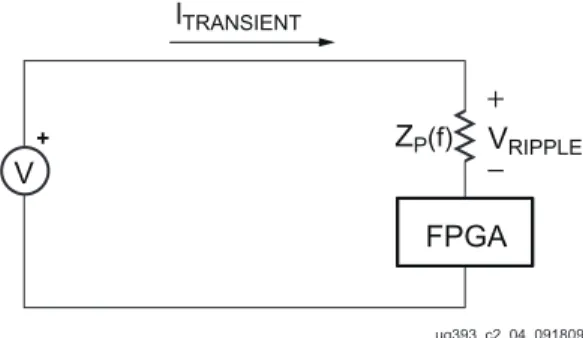

PDS の基本的な考え方 実際にデバ イ ス が要求す る 電流量が変化 し た場合、PDS はその変動に即座には反応で き ません。 こ のため、PDS が反応す る ま での短時間に、 デバ イ ス側での電圧が変化 し ま す。PDS が反応す る ま でに時差が発生す る 主な要因は 2 つあ り 、PDS の 2 つの主要部品であ る 電圧レ ギ ュ レー タ と デカ ッ プ リ ン グ キ ャ パシ タ が こ れ ら に該当 し ます。 PDS を構成す る 中心的な部品 と な る のが電圧レ ギ ュ レー タ です。電圧レ ギ ュ レー タ は出力電圧を監 視 し 、 供給電流量を調整す る こ と に よ っ て出力電圧を一定に保ち ます。 一般的な電圧レ ギ ュ レー タ は、 こ の調整を ミ リ 秒か ら マ イ ク ロ 秒単位で行い ます。 電圧レ ギ ュ レー タ は、 種類に も よ り ますが DC か ら 数百 kHz ま ですべての周波数の イ ベン ト に対 し て出力電圧を一定に維持す る 効果が あ り ます (数 MHz ま で整流効果のあ る レ ギ ュ レー タ も あ り ます)。 こ の範囲を超え る 周波数で発生す る 過渡状態では、 新たに必要 と な っ た電流レベルに対す る 応答に遅延が生 じ ます。 た と えば、 デバ イ ス が要求す る 電流レベルが数百ピ コ 秒の間に増加 し た場合、 電圧レ ギ ュ レー タ に よ っ て必要な レベルの電流が供給 さ れ る ま で、 デバ イ ス の電圧が低下 し ます。 こ の遅延は数マ イ ク ロ 秒か ら 数 ミ リ 秒に及ぶ こ と があ り ます。 そ こ で、 こ の遅延の間、 電圧の降下を防 ぐ ために レ ギ ュ レー タ の役割を果たす部品が別途必要にな り ます。 PDS を構成す る も う 1 つの主要な部品 と な る のが、 デカ ッ プ リ ン グ キ ャ パシ タ (バ イ パ ス キ ャ パ シ タ) です。 デカ ッ プ リ ン グ キ ャ パシ タ はデバ イ ス の近 く でエネルギーを局所的に蓄え る 役割を果 た し ます。 ただ し キ ャ パシ タ が蓄え る エネルギーは少量なので、DC 電力は供給で き ません (DC 電 力は電圧レ ギ ュ レー タ か ら 供給 さ れます)。 局所的にエネルギーを貯蔵す る こ と に よ っ て、 電流要求 レベルの変化にすばや く 反応 し ま す。 キ ャ パシ タ が電源電圧を維持で き る のは、 数百 kHz ~数百 MHz (ミ リ 秒か ら ナ ノ 秒) の範囲です。 こ の範囲外ではデカ ッ プ リ ン グ キ ャ パシ タ は効果があ り ま せん。 た と えば、 デバ イ ス が要求す る 電流レベルが数ピ コ 秒の間に増加 し た場合、 デカ ッ プ リ ン グキ ャ パ シ タ が必要な電流をデバ イ ス に供給で き る ま で、 デバ イ ス の電圧が低下 し ます。 デバ イ ス内の電流 に対す る 要求が変化 し 、 その状態が数 ミ リ 秒続 く 場合は、 バ イ パス キ ャ パシ タ と 同時に機能 し てい る 電圧レ ギ ュ レー タ の出力が変化 し 、 新 し い電流を供給 し ます。 図2-3に、PDS の主な構成要素であ る 電圧レ ギ ュ レー タ 、 デカ ッ プ リ ン グ キ ャ パシ タ 、 電力の供 給を受け る ア ク テ ィ ブなデバ イ ス (FPGA) を示 し ます。 図2-4に、 さ ら に単純化 し た PDS 回路を示 し ます。 こ の図には、 周波数に依存す る 抵抗に分解 し たすべての無効成分を示 し てい ます。

X-Ref Target - Figure 2-3

図 2-3 : PDS 回路の簡略図

+

FPGA

L

REGULATORL

DECOUPLINGC

DECOUPLING㔚

䊧䉩䊠䊧䊷䉺

V

UG393_c2_03_091809イ ン ダ ク タ ン スの役割

キ ャ パシ タ や PCB の電流パス には、電流の流れを妨げ る イ ン ダ ク タ ン ス と い う 特性があ り ます。過 渡電流や、 有効範囲 よ り 高い周波数で発生 し た変化にキ ャ パシ タ が瞬時に反応で き ないのは、 こ の イ ン ダ ク タ ン ス が原因です。 イ ン ダ ク タ ン ス は電荷の運動量 と 考え る こ と がで き ます。 電荷が導体を移動す る と 、 電流が流れま す。 電流レベルが変化す る と 、 電荷の移動速度が変化 し ま す。 こ の電荷には運動量 (蓄え ら れた磁 界エネルギー) があ る ため、 電荷の速度が変化す る には時間 と エネルギーが必要です。 イ ン ダ ク タ ン ス が大 き いほ ど電荷変化に対す る 抵抗が大 き く な り 、電流レベルの変化に時間が必要 と な り ます。 そ し て、 電流レベルが変化す る 際に、 イ ン ダ ク タ ン ス の両端に電圧が発生 し ます。 PDS は、 レ ギ ュ レー タ と 数段のデカ ッ プ リ ン グキ ャ パシ タ で構成 さ れてお り 、 デバ イ ス の要求電 流レベルの変化に可能な限 り すばや く 反応 し ます。 要求 さ れ る レベルの電流を供給で き ない と 、 デ バ イ ス の電源の両端にかか る 電圧が変化 し ます。 こ れが ノ イ ズ と し て観察 さ れます。 キ ャ パシ タ の 電流パ ス に大 き な イ ン ダ ク タ ン ス が あ る と デカ ッ プ リ ン グ キ ャ パシ タ は要求 さ れ る 電流 レ ベルの 変化にすばや く 反応で き な く な る ため、 最小限に抑え る 必要があ り ます。 図2-3に示 し た よ う に、 イ ン ダ ク タ ン ス は FPGA デバ イ ス と キ ャ パシ タ の間、 そ し て キ ャ パシ タ と 電圧 レ ギ ュ レ ー タ の間に発生 し ま す。 こ れ ら の イ ン ダ ク タ ン ス は、 キ ャ パシ タ 内お よ びすべての PCB 電流パ ス に対 し て寄生 イ ン ダ ク タ ン ス と し て発生す る ため、各 イ ン ダ ク タ ン ス を最小にす る こ と が重要です。キ ャパシ タ の寄生イ ン ダ ク タ ン ス

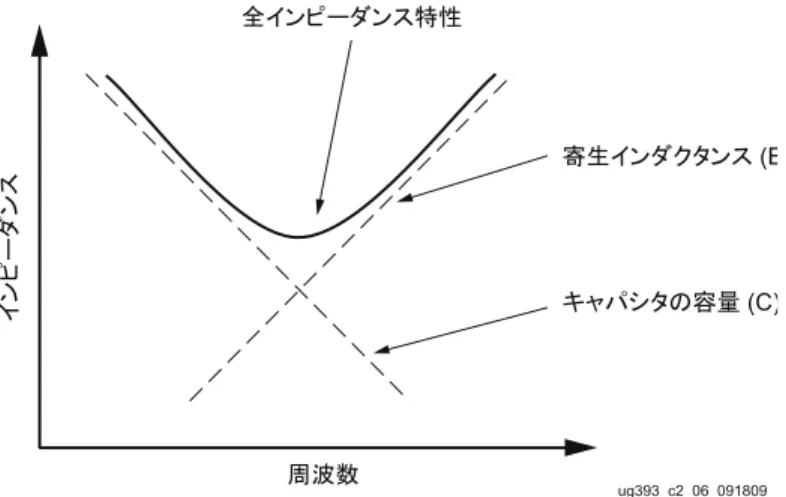

通常、 バ イ パ ス キ ャ パシ タ で最 も 重要な特性 と 考え ら れ る のが容量 (キ ャ パシ タ ン ス) です。 電源 シ ス テ ムアプ リ ケーシ ョ ン では、 寄生 イ ン ダ ク タ ン ス (ESL) も それに劣 ら ず重要な特性 と さ れ ま す。 寄生 イ ン ダ ク タ ン ス の量は、 キ ャ パシ タ のパ ッ ケージ寸法 (ボデ ィ サ イ ズ) に よ っ て決定 し ま す。 一般に、 物理的なサ イ ズが小 さ いキ ャ パシ タ ほ ど寄生 イ ン ダ ク タ ン ス の値が小 さ く な り ます。 デカ ッ プ リ ン グキ ャ パシ タ は、 以下の基準で選択 し ます。 • 容量が決ま っ てい る 場合は、 パ ッ ケージサ イ ズが最小の も のを選択す る 。 ま たは • パ ッ ケージサ イ ズが決ま っ てい る 場合は (すなわち イ ン ダ ク タ ン ス が同 じ)、容量が最大の も の を選択す る 。X-Ref Target - Figure 2-4

図 2-4 : さ ら に簡略化 し た PDS 回路図

l

TRANSIENTFPGA

ug393_c2_04_091809Z

P(f)V

RIPPLE+

−

+V

PDS の基本的な考え方 キ ャ パシ タ の中で最 も 小型なのはチ ッ プ型の表面実装キ ャ パシ タ です。デ ィ ス ク リ ー ト デカ ッ プ リ ン グ キ ャ パシ タ を使用す る 場合は こ の タ イ プの も のを選択す る よ う に し て く だ さ い。 • 0.01µFの き わめて容量の小 さ い も のを含め、100µF以下の容量には、一般に X7R ま たは X5R タ イ プのキ ャ パシ タ を使用 し ます。 こ れ ら のキ ャ パシ タ は寄生 イ ン ダ ク タ ン ス と ESR が小 さ く 、 温度特性 も 条件を満た し ます。 • 100µF~ 1000µFの大 き な容量では、 タ ン タ ルキ ャ パシ タ を使用 し ます。 こ れ ら のキ ャ パシ タ は寄生 イ ン ダ ク タ ン ス が小 さ く 、ESR は中程度です。 こ のため フ ァ ク タ Q が小 さ く 、 き わめ て広範囲の周波数で効果があ り ます。 入手性やその他の理由で タ ン タ ル キ ャ パシ タ を使用で き ない場合は、 低 ESR、 低 イ ン ダ ク タ ン ス の電解キ ャ パシ タ を使用で き ますが、ESR と ESL が タ ン タ ルキ ャ パシ タ と 同等でなければな り ま せん。 特性が同 じ な ら 、 その他の新技術に よ る キ ャ パシ タ (Os-Con、POSCAP、 ポ リ マー電解 SMT な ど) も 利用で き ます。 ど の よ う な種類のキ ャ パシ タ も 、実際には容量以外に イ ン ダ ク タ ン ス と 抵抗 と い う 特性があ り ます。 図2-5に、 実際のキ ャ パシ タ の寄生モデルを示 し ます。 実際のキ ャ パシ タ は、 抵抗 (R)、 イ ン ダ ク タ (L)、 キ ャ パシ タ (C) を直列に接続 し た RLC 回路 と し て扱 う 必要があ り ます。 図2-6は、 実際のキ ャ パシ タ の イ ン ピーダ ン ス特性を示 し た も のです。 グ ラ フ には、 キ ャ パシ タ の 容量 と 寄生 イ ン ダ ク タ ン ス (ESL) も 破線で表 し てい ます。 こ れ ら 2 つの線を組み合わせ る と 、RLC 回路の全 イ ン ピーダ ン ス特性が得 ら れ、 その先端の鋭 さ はキ ャ パシ タ の ESR に よ っ て決定 し ます。 容量が大 き く な る と 容量を表す線は左下方向へ移動 し ます。 一方、 寄生 イ ン ダ ク タ ン ス が小 さ く な る と 、 イ ン ダ ク タ ン ス を表す線は右下方向へ移動 し ます。 パ ッ ケージが同 じ な ら キ ャ パシ タ の寄生 イ ン ダ ク タ ン ス は一定であ る ため、 イ ン ダ ク タ ン ス を表す線は固定 さ れます。

X-Ref Target - Figure 2-5

図 2-5 : 理想ではな く 実際のキ ャ パシ タ の寄生モデル

X-Ref Target - Figure 2-6

図 2-6 : 全イ ン ピーダ ン ス特性に対する寄生成分の影響

C

ESL

ESR

ug393_c2_05_091809 ᵄᢙ 䉟䊮䊏䊷䉻䊮䉴 䉨䊞䊌䉲䉺䈱ኈ㊂ (C) ነ↢䉟䊮䉻䉪䉺䊮䉴 (E ో䉟䊮䊏䊷䉻䊮䉴․ᕈ ug393_c2_06_091809し たがっ て、 同一パ ッ ケージで異な る キ ャ パシ タ を選択す る 場合、 容量を表す線は図2-8に示 し た よ う に固定 さ れた イ ン ダ ク タ ン ス の線に沿っ て上下に移動 し ます。 低周波帯域におけ る キ ャ パシ タ の イ ン ピーダ ン ス を小 さ く す る には、 キ ャ パシ タ を大 き く し ます。 高周波帯域の イ ン ピーダ ン ス を小 さ く す る には、 キ ャ パシ タ の イ ン ダ ク タ ン ス を小 さ く し ます。 同 じ パ ッ ケージで容量の大 き な も のを指定可能な場合があ り ますが、 あ る パ ッ ケージでキ ャ パシ タ の イ ン ダ ク タ ン ス を小 さ く す る には、 キ ャ パシ タ を追加 し て並列に接続す る 必要があ り ます。 キ ャ パ シ タ を並列に接続す る と その分寄生 イ ン ダ ク タ ン ス が分割 さ れ、 同時に容量 も 増加 し ます。 こ う す る と 、 高周波帯域 と 低周波帯域の イ ン ピーダ ン ス を同時に小 さ く で き ます。

PCB

電流パスのイ ン ダ ク タ ン ス

PCB の電流パ ス におけ る 寄生 イ ン ダ ク タ ン ス の原因には、 次の 3 つがあ り ます。 • キ ャ パシ タ の実装 • PCB の電源プ レーン と グ ラ ン ド プ レーン • FPGA の実装キ ャパシ タ の実装によ る イ ン ダ ク タ ン ス

キ ャ パシ タ の実装 と は、PCB 上でのキ ャ パシ タ のはんだ ラ ン ド 、 ラ ン ド と ビ アの間の ト レース (な い こ と も あ る)、 ビ ア をいい ます。 形状に も よ り ますが、2 端子キ ャ パシ タ の場合、 ビ ア、 ト レース、 キ ャ パシ タ 実装パ ッ ド に よ っ て 300pH~ 4nHの イ ン ダ ク タ ン ス が生 じ ます。 電流パス の イ ン ダ ク タ ン スは電流が流れ る ループの面積に比例す る ため、 こ の面積を最小にす る こ と が重要です。図2-7に示す よ う に、 ループは一方の電源プ レーンか ら ビ ア、 接続 ト レース、 ラ ン ド を通っ て キ ャ パシ タ へ至 り 、 そ こ か ら も う 一方の ラ ン ド 、 接続 ト レース、 ビ ア を通っ て も う 一方 のプ レーンに至 る ま でのパ ス で形成 さ れます。X-Ref Target - Figure 2-7

䈲䉖䈣ઃ䈔↪┵ሶ 0402 䉨䊞䊌䉲䉺ᧄ 㕙䊃䊧䊷䉴 䉨䊞䊌䉲䉺䈱䈲䉖䈣䊤䊮䊄 䊎䉝 PCB GND VCC 㔚Ḯ䊒䊧䊷䊮䈫 䉫䊤䊮䊄 䊒䊧䊷䊮 ታⵝᷣ䉂䉨䊞䊌䉲䉺䈱㔚ᵹ䊦䊷䊒 UG393_c2_07_091809

PDS の基本的な考え方 接続 ト レース の長 さ は実装に よ る 寄生 イ ン ダ ク タ ン ス に特に大 き な影響を与え る ため、 使用す る 場 合はで き る 限 り 広 く 短 く し ます。 可能な限 り 、図2-1の (A) の よ う な接続 ト レー ス の使用は避け、 図2-1の (B) の よ う に ビ ア と ラ ン ド を直接接す る よ う に配置 し て く だ さ い。図2-1の (C) の よ う に キ ャ パシ タ の ラ ン ド 側面にビ ア を配置す る か、図2-1の (D) の よ う にビ ア数を倍にす る と 、 実装に よ る 寄生 イ ン ダ ク タ ン ス が さ ら に抑え ら れます。 PCB 製造工程に よ っ ては、寄生 イ ン ダ ク タ ン ス を抑え る 形状 と し てパ ッ ド 内にビ ア を配置で き る 場 合があ り ます。1 つの ラ ン ド に複数のビ ア を使用す る 方法は、 キ ャ パシ タ 本体の端ではな く 側面に 太い端子を配置 し た逆ア スペ ク ト 比のキ ャ パシ タ な ど、 超低 イ ン ダ ク タ ン ス のキ ャ パシ タ で特に重 要にな り ます。 複数のキ ャ パシ タ で 1 つビ ア を共用 し 、狭い面積に多 く の部品を実装 し よ う と する PCB レ イ ア ウ ト を よ く 見かけ ますが、こ う し た手法はいかな る場合において も 使用 し ないで く だ さ い。既にキ ャ パシ タ が接続 さ れてい る ビ アに別のキ ャ パシ タ を接続 し て も 、PDS の特性はほ と ん ど改善 さ れ ません。 キ ャ パシ タ の総数を減 ら し 、 ラ ン ド と ビ アの数を 1:1 の比で使用する方が よ い特性が得 ら れます。 一般に、 キ ャ パシ タ の実装 (ラ ン ド 、 ト レース、 ビ ア) に よ る イ ン ダ ク タ ン ス は、 キ ャ パシ タ 自体の 寄生自己 イ ン ダ ク タ ン ス と 同 じ かそれ以上にな り ます。

プ レーンのイ ン ダ ク タ ン ス

PCB の電源プ レーン と グ ラ ン ド プ レーン か ら も イ ン ダ ク タ ン ス が発生 し ます。 こ の大 き さ は、 プ レーンの形状に よ っ て決定 し ます。 電源お よ びグ ラ ン ド プ レーン では、電流はあ る 1 点か ら 別の 1 点へ と 流れ る 際に広が り なが ら 進み ます (こ れは表皮効果 と 似た特性に よ る も のです)。 こ のため、 プ レーンの イ ン ダ ク タ ン ス は拡散 イ ン ダ ク タ ン ス (単位は H/square) で表 さ れ ます。 こ の イ ン ダ ク タ ン ス の大 き さ はプ レーン のサ イ ズ ではな く 形状に よ っ て決定す る ため、 面積は重要ではあ り ません。 拡散 イ ン ダ ク タ ン ス は通常の イ ン ダ ク タ ン ス と 同 じ よ う に作用 し 、電源プ レーン (導体) の電流量の 変化に抵抗を与え ます。 イ ン ダ ク タ ン ス があ る と デバ イ ス の過渡電流に対す る キ ャ パシ タ の反応が 遅 く な る ため、 こ の値を可能な限 り 小 さ く す る 必要があ り ます。 プ レーン の X-Y 方向の形状は設 計者では調整で き ないため、 拡散 イ ン ダ ク タ ン ス値を調整 し ます。 こ の値は、 電源プ レーン と グ ラ ン ド プ レーン を絶縁 し てい る 誘電体の厚 さ に よ っ て決定 し ます。 高周波の電源分配シ ス テ ムの場合、 電源プ レーン と グ ラ ン ド プ レーンはペア と し て作用 し 、 それぞ れの イ ン ダ ク タ ン ス が一体化 し て存在 し ます。 こ のペアの拡散 イ ン ダ ク タ ン ス は、 電源プ レーン と グ ラ ン ド プ レーン の間隔に よ っ て決定 し ます。 間隔が近い (誘電体の厚 さ が薄い) ほ ど拡散 イ ン ダ ク タ ン ス は小 さ く な り ます。表2-3に、厚 さ の異な る FR4 誘電体の拡散 イ ン ダ ク タ ン ス の概算値を 示 し ます。 表 2-3 : 厚 さ の異な る FR4 誘電体の電源プ レーン と グ ラ ン ド プ レーンの間の容量 と 拡散イ ン ダ ク タ ン ス 誘電体の厚 さ イ ン ダ ク タ ン ス 容量(ミ ク ロ ン) (mil) (pH/square) (pF/in2) (pF/cm2)

102 4 130 225 35

51 2 65 450 70

VCCプ レーン と GND プ レーンの間隔が近いほ ど拡散 イ ン ダ ク タ ン ス の値は小 さ く な る ため、 PCB ス タ ッ ク ア ッ プでは、 可能な限 り VCCプ レーン と GND プ レーン を隣接 さ せて く だ さ い。VCCプ レーン と GND プ レーン を隣接 さ せた構造をサン ド イ ッ チ と 呼ぶ こ と があ り ます。従来の技術 (リ ー ド フ レーム、 ワ イ ヤ ボ ン ド パ ッ ケージ) では VCC と GND のサン ド イ ッ チ構造は必ず し も 必要あ り ませんで し たが、 高速、 高密度のデバ イ ス で要求 さ れ る 速度 と 電力に対応す る ために最近では必 要 と な る ケース が増えてい ます。 電源プ レーン と グ ラ ン ド プ レーン をサン ド イ ッ チ構造にす る と 、電流パ ス の イ ン ダ ク タ ン ス が小 さ く な る だけでな く 、 高周波のデカ ッ プ リ ン グ容量が大 き く な り ます。 こ れは、 プ レーンの面積が大 き く な り 、 電源プ レーン と グ ラ ン ド プ レーンの間隔が狭 く な る ためです。表2-3には、 平方 イ ンチ 当た り の容量の値 も 示 し て あ り ます。

FPGA

の実装によ る イ ン ダ ク タ ン ス

FPGA の電源ピ ン (VCC と GND) を接続す る PCB のはんだ ラ ン ド と ビ ア も 、 全体的な電源回路に おけ る 寄生 イ ン ダ ク タ ン ス の要因 と な り ます。 従来の PCB 技術では、 はんだ ラ ン ド の形状 と ド ッ グボーン形状はほぼ固定 さ れてお り 、 こ れ ら の寄生 イ ン ダ ク タ ン スはほ と ん ど変化 し ません。 ビ ア の寄生 イ ン ダ ク タ ン スは、 ビ アの長 さ と 反対方向の電流パ ス同士の間隔に よ っ て決定 し ます。 こ こ での ビ アの長 さ と は、FPGA のはんだ ラ ン ド か ら VCCま たは GND プ レーン ま で過渡電流を 伝達す る ビ アの長 さ をいい ます。 ビ アのその他の部分 (電源プ レーンか ら PCB 裏面ま で) はビ アの 寄生 イ ン ダ ク タ ン ス には影響 し ません (はんだ ラ ン ド か ら 電源プ レーン ま での ビ アの長 さ が短いほ ど寄生 イ ン ダ ク タ ン スは小 さ く な り ます)。FPGA の実装に よ る ビ アの寄生 イ ン ダ ク タ ン ス を小 さ く す る には、VCCプ レーン と GND プ レーン を で き る 限 り FPGA に近接 (PCB ス タ ッ ク ア ッ プの表 面に近づけ る) さ せます。 反対方向の電流パス同士の間隔は、 デバ イ ス の ピ ン配置に よ っ て決定 し ます。VCCと GND ビ アの ペアに流れ る 電流な ど、 反対方向の電流には常に イ ン ダ ク タ ン ス が発生 し ます 2 つの反対方向のパ ス同士の誘導性結合が大 き いほ ど、 ループの総 イ ン ダ ク タ ン スは小 さ く な り ます。 し たがっ て、 可 能な限 り VCC と GND のビ ア を近 く に配置 し ます。 FPGA 直下の ビ ア領域には多 く の VCCお よ び GND ビ アがあ り 、 総 イ ン ダ ク タ ン ス はビ ア同士の 間隔に よ っ て決定 し ます。 • コ ア電源 (VCCINTおよび VCCAUX) の場合、VCCピ ン と GND ピ ンが反対方向の電流 と な り ます。 • I/O 電源 (VCCO) の場合、 任意の I/O と その リ タ ーン電流のパス (VCCOま たは GND ピ ン) が反対方向の電流 と な り ます。 寄生 イ ン ダ ク タ ン ス を小 さ く す る には、 次の方法があ り ます。 • VCCINTと GND を BGA パ ッ ケージの中心部に格子状に配置す る 。 • VCCOピ ン と GND ピ ン を I/O ピ ンの間に分散 し て配置す る 。 BGA パ ッ ケージでは、FPGA の ピ ン配置に よ っ て PCB ビ アの配置が決定 し ます。PCB 設計者は 反対方向の電流パス の間隔を決定で き ませんが、 キ ャ パシ タ の実装に よ る イ ン ダ ク タ ン ス と FPGA の実装に よ る イ ン ダ ク タ ン ス の ト レー ド オ フ に よ っ て調整で き ます。 • ど ち ら の実装に よ る イ ン ダ ク タ ン ス も 、 電源プ レーン を PCB ス タ ッ ク ア ッ プの上半分に配置 し 、 キ ャ パシ タ を PCB 表面に配置 し て キ ャ パシ タ のビ ア長を短 く す る こ と で小 さ く で き ます。 • 電源プ レーン を PCB ス タ ッ ク ア ッ プの下半分に配置す る 場合は、PCB の裏面にキ ャ パシ タ を 配置す る 必要があ り ます。 こ の場合、FPGA 実装用のビ アが長 く な る ので、 キ ャ パシ タ を PCB 表面に配置 し て キ ャ パシ タ 実装用ビ ア も 長 く す る のは得策ではあ り ません。PCB 裏面 と 電源プ レーンの距離が短いため、 キ ャ パシ タ は裏面に実装す る よ う に し ます。