Arria 10

デバイスのロジック・アレイ・ブロッ

クとアダプティブ・ロジック・モジュール

1

2013.12.02 A10-LAB 署名 フィードバック ロジック・アレイ・ブロック(LAB)は、アダプティブ・ロジック・モジュール(ALM)とし て知られる基本のビルディング・ブロックで構成されています。ロジック・ファンクション、演 算ファンクション、およびレジスタ・ファンクションを実装するために LAB をコンフィギュレ ーションすることができます。また、 Arria® 10 デバイスで使用可能な LAB の 4 分の 1 をメモリ LAB(MLAB)として使用する

ことができます。なお、特定のデバイスにはより高い MLAB 比率を有するものもあります。 Quartus® II ソフトウェアおよびサポートされるサードパーティの合成ツールは、LPM(Library of Parameterized Module)などパラメータ化された機能と併せて使用すると、カウンタ、加算器、 減算器、および演算ファンクションなどの一般的な機能に適切なモードを自動的に選択します。 この章は以下の項で構成されています。 • LAB • ALM 動作モード 関連情報

Arria 10 Device Handbook: Known Issues

Arria 10 Device Handbook の章にて予定される更新をリストします。

LAB

LAB はロジック・リソースのグループで構成されるコンフィギュレーション可能なロジック・ ブロックです。各 LAB には ALM にコントロール信号を駆動するための専用ロジックが含まれ ます。

MLAB は LAB のスーパーセットで、LAB の機能をすべて備えています。

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

ISO 9001:2008

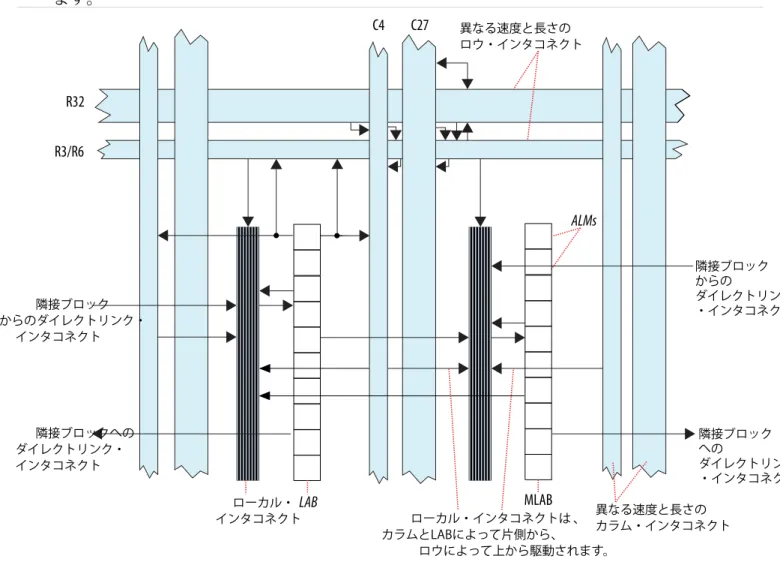

図 1-1: Arria 10 デバイスにおける LAB 構造およびインタコネクトの概要

この図は、LAB インタコネクトを有する Arria® 10 の LAB および MLAB 構造の概要を表してい

ます。 隣接ブロック からの ダイレクトリンク ・インタコネクト 隣接ブロック への ダイレクトリンク ・インタコネクト 異なる速度と長さの ロウ・インタコネクト 異なる速度と長さの カラム・インタコネクト ローカル・インタコネクトは 、 カラムとLABによって片側から、 ロウによって上から駆動されます。 ローカル・ インタコネクトLAB 隣接ブロック からのダイレクトリンク・ インタコネクト 隣接ブロックへの ダイレクトリンク・ インタコネクト ALMs MLAB C4 C27 R32 R3/R6

MLAB

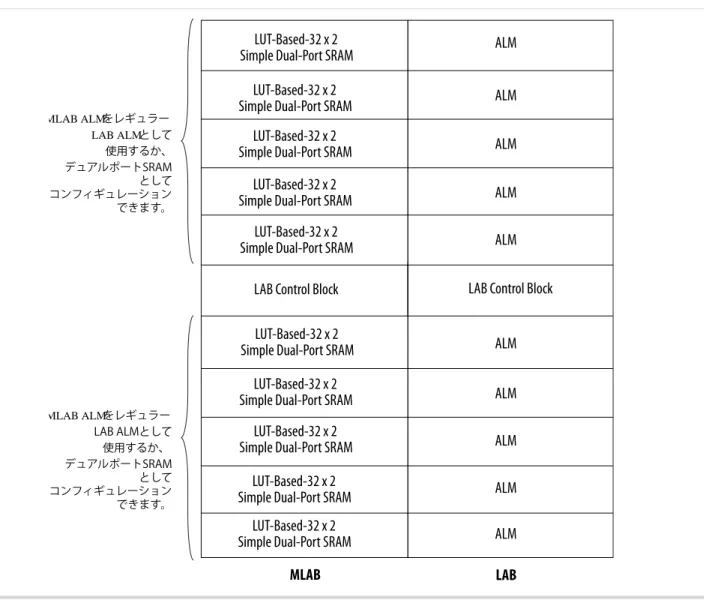

各 MLAB は最大 640 ビットのシンプル・デュアル・ポート SRAM をサポートします。 MLAB の各 ALM は、32(深さ) x 2(幅)のメモリ・ブロックとしてコンフィギュレーション可 能で、32(深さ) x 20(幅)のシンプル・デュアル・ポート SRAM ブロックのコンフィギュレー ションとなります。 MLAB は、Quartus II ソフトウェアを使用するソフト実装で次の 64 ディープ・モードをサポート します。 • 64(深さ)× 8(幅) • 64(深さ)× 9(幅) • 64(深さ)× 10(幅) 1-2 MLAB 2013.12.02A10-LAB図 1-2: Arria 10 デバイスの LAB と MLAB 構造

MLAB LAB

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

LUT-Based-32 x 2 Simple Dual-Port SRAM

ALM ALM ALM ALM ALM ALM ALM ALM ALM ALM LAB Control Block LAB Control Block

MLAB ALMをレギュラー LAB ALMとして 使用するか、 デュアルポートSRAM として コンフィギュレーション できます。 MLAB ALMをレギュラー LAB ALMとして 使用するか、 デュアルポートSRAM として コンフィギュレーション できます。

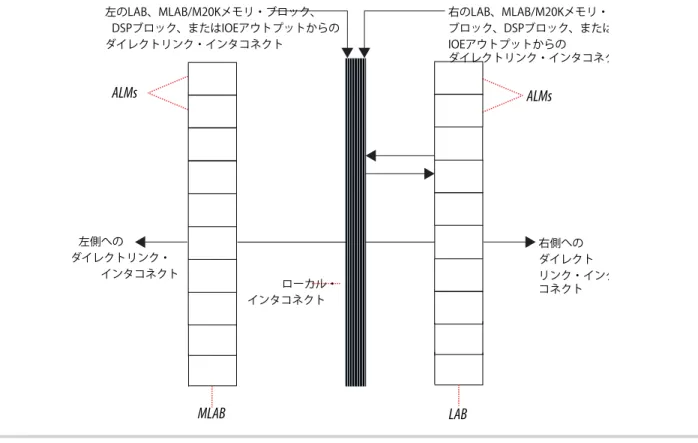

ローカル・インタコネクトおよびダイレクト・リンク・インタコネクト

それぞれの LAB は 40 ALM 出力をドライブ・アウトすることができます。20 ALM 出力の 2 つの グループは、ダイレクト・リンク・インタコネクトを介して隣接する LAB を直接駆動すること ができます。

このダイレクト・リンクによる接続機能は、ロウおよびカラム・インタコネクトの使用が最小限 で済むため、さらに高い性能と柔軟性を提供します。

ローカル・インタコネクトは、カラム・インタコネクトとロウ・インタコネクト、同じ LAB の ALM 出力を使用して、同じ LAB で ALM を駆動します。

左側または右側の隣接する LAB、MLAB、ブロック、あるいは DSP(デジタル信号処理)ブロッ クは、ダイレクト・リンク接続を使用して LAB のローカル・インタコネクトを駆動することが できます。

A10-LAB

図 1-3: Arria 10 デバイスの LAB ローカル・インタコネクトおよびダイレクト・リンク・インタコネ クト ALMs 右側への ダイレクト リンク・インタ コネクト 左のLAB、MLAB/M20Kメモリ・ブロック、 DSPブロック、またはIOEアウトプットからの ダイレクトリンク・インタコネクト ローカル・ インタコネクト LAB ALMs 左側への ダイレクトリンク・ インタコネクト MLAB 右のLAB、MLAB/M20Kメモリ・ ブロック、DSPブロック、または IOEアウトプットからの ダイレクトリンク・インタコネクト

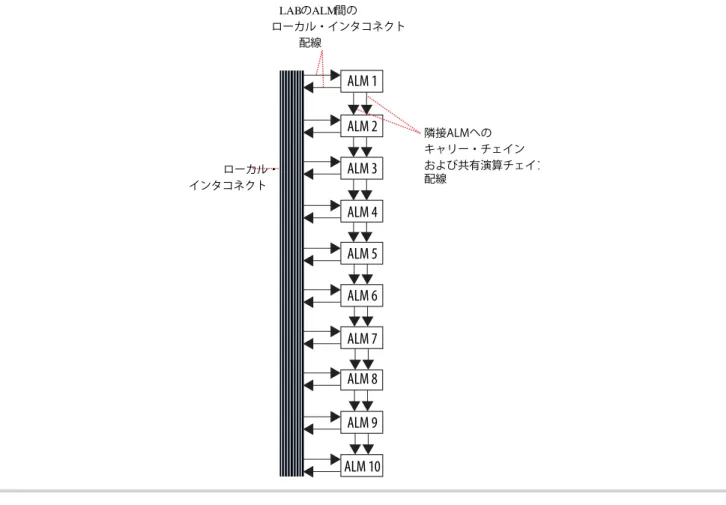

共有演算チェイン・インタコネクトとキャリー・チェイン・インタコネクト

ALM 間にはキャリー・チェインおよび共有演算チェインという 2 つの専用パスがあります。デ バイスは、LAB 内に拡張されたインタコネクト構造を有し、効率的な演算機能のために共有演 算チェインとキャリー・チェインを配線します。こうした ALM 間の接続はローカル・インタコ ネクトをバイパスします。Quartus II コンパイラはこれらのリソースを自動的に利用して使用率 と性能を向上させます。 1-4 共有演算チェイン・インタコネクトとキャリー・チェイン・インタコネクト 2013.12.02A10-LAB図 1-4: 共有演算チェイン・インタコネクトとキャリー・チェイン・インタコネクト 隣接ALMへの キャリー・チェイン および共有演算チェイン 配線 LABのALM間の ローカル・インタコネクト 配線 ローカル・ インタコネクト ALM 1 ALM 2 ALM 3 ALM 4 ALM 5 ALM 6 ALM 7 ALM 8 ALM 9 ALM 10

LAB

コントロール信号

それぞれの LAB は ALM にコントロール信号を駆動するための専用ロジックを含んでおり、2 つ の独立したクロック・ソースと 3 つのクロック・イネーブル信号を有します。 LAB コントロール・ブロックは、2 つのクロック・ソースと 3 つのクロック・イネーブル信号を 使用して最大 3 つのクロックを生成します。各クロックとクロック・イネーブル信号はリンクさ れます。 クロック・イネーブル信号がディアサートされると、対応する LAB ワイドのクロック信号はオ フになります。LAB ロウ・クロック[5..0]と LAB ローカル・インタコネクトは LAB ワイドのコントロール信号を 生成します。MultiTrack インタコネクトに固有の低スキューは、データの他にクロックおよびコ ントロール信号を分配することができます。MultiTrack インタコネクトは、デザイン・ブロック 間およびデザイン・ブロック内の接続に使用される長さと速度が異なる最適性能の連続配線ライ ンで構成されます。 クリアおよびプリセット・ロジック・コントロール レジスタのクリア信号のロジックは、LAB ワイド信号によって制御されます。ALM は非同期の クリア機能を直接サポートします。レジスタ・プリセットは NOT-gate push-back ロジックとし て Quartus II ソフトウェアに実装されています。各 LAB は最大 2 つのクリアをサポートしま す。 A10-LAB 2013.12.02 LABコントロール信号 1-5

Arria® 10 デバイスは、デバイス内のすべてのレジスタをリセットするデバイス・ワイドのリセ

ット・ピン(DEV_CLRn)を提供します。DEV_CLRnピンはコンパイルの前に Quartus II ソフトウェ

アでイネーブルすることができます。このデバイス・ワイドのリセット信号は、他のすべてのコ ントロール信号よりも優先されます。 図 1-5: Arria 10 デバイスの LAB ワイド・コントロール信号 次の図は、LAB 内のクロック・ソースとクロック・イネーブル信号を表しています。 Dedicated Row LAB Clocks Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect labclk2 syncload labclkena0 またはasyncload またはlabpreset

labclk0 labclk1 labclr1

labclkena1 labclkena2 labclr0 synclr

6 6 6 LABごとに2つの固有の クロック信号があります。

ALM

リソース

各 ALM には、2 つの組み合わせアダプティブ LUT(ALUT)と 4 つのレジスタ間で分割できる 多様な LUT ベースのリソースが含まれています。 2 つの組み合わせ ALUT の最大 8 入力を使用して、1 つの ALM に 2 つのファンクションのさま ざまな組み合わせを実装することができます。この適応性により、ALM は 4 入力 LUT アーキテ クチャとの完全な下位互換性を有します。最大 6 入力を有する任意のファンクションや特定の 7 入力ファンクションを 1 つの ALM に実装することも可能です。 1 つの ALM には 4 つのプログラマブル・レジスタが含まれます。各レジスタはそれぞれ、次の ポートを有します。 1-6 ALMリソース 2013.12.02A10-LAB• データ • クロック • 同期および非同期クリア • 同期ロード グローバル信号、汎用 I/O(GPIO)ピン、あるいは任意の内部ロジックで ALM レジスタのクロ ック・イネーブル信号、クロック・コントロール信号、およびクリア・コントロール信号を駆動 することができます。 組み合わせファンクションでは、レジスタがバイパスされ、LUT(ルックアップ・テーブル)の 出力が ALM の出力に直接駆動します。 注: Quartus II ソフトウェアは、最適化されたパフォーマンスを提供するために ALM を自動的に コンフィギュレーションします。 図 1-6: Arria 10 デバイスにおける ALM の上位レベルのブロック図 datac datad datae1 dataf1 adder1 datae0 dataf0 dataa datab carry_in carry_out Combinational/ Memory ALUT0 6-Input LUT 6-Input LUT shared_arith_out shared_arith_in Combinational/ Memory ALUT1 adder0 labclk reg1 一般配線へ reg0 reg3 reg2

ALM

出力

各 ALM における一般配線出力は、ローカル、ロウ、およびカラム配線リソースを駆動します。 2 つの ALM 出力はカラム、ロウ、あるいはダイレクト・リンク配線接続を駆動することができ ます。 LUT、加算器、またはレジスタ出力は ALM 出力を駆動することができます。なお、レジスタが ある出力を駆動している状態で、LUT または加算器は別の出力を駆動することができます。 レジスタ・パッキングは、まったく別のレジスタと組み合わせロジックを 1 つの ALM 内にパッ キングすることによってデバイスの稼働率を向上させます。フィッティングを向上させるため A10-LAB 2013.12.02 ALM出力 1-7の別のメカニズムは、レジスタ出力を同じ ALM の LUT 内にフィード・バックできるようにする ことです。そうすることで、レジスタは自身のファンアウト LUT とパッキングされます。ALM は、加算器または LUT の出力のレジスタされたバージョンとレジスタされていないバージョン をドライブ・アウトすることもできます。 図 1-7: Arria 10 デバイスの ALM 接続の詳細 + carry_in dataf0 datae0 dataa datab datad datae1 dataf1 shared_arith_out carry_out shared_arith_in 4-Input LUT 4-Input LUT 3-Input LUT 3-Input LUT 3-Input LUT 3-Input LUT + datac GND VCC aclr[1:0] sclr syncload clk[2:0] DCLRQ DCLRQ Row, Column Direct Link Routing

DCLRQ

DCLRQ 3

3

Row, Column Direct Link Routing

Row, Column Direct Link Routing

Row, Column Direct Link Routing

ALM

動作モード

Arria® 10 の ALM は、次のいずれかのモードで動作します。 • ノーマル・モード • 拡張 LUT モード • 演算モード • 共有演算モード 1-8 ALM動作モード 2013.12.02A10-LABノーマル・モード

ノーマル・モードでは、2 つのファンクションまたは最大 6 入力の 1 つのファンクションを 1 つ の ALM に実装することができます。 LAB ローカル・インタコネクトからの最大 8 データ入力は、組み合わせロジックの入力になり ます。 ALM は、完全に独立したファンクションの特定の組み合わせや共通の入力を有するファンクシ ョンのさまざまな組み合わせをサポートすることができます。Quartus II のコンパイラは LUT への入力を自動的に選択します。ノーマル・モードの ALM はレ ジスタ・パッキングをサポートします。

A10-LAB

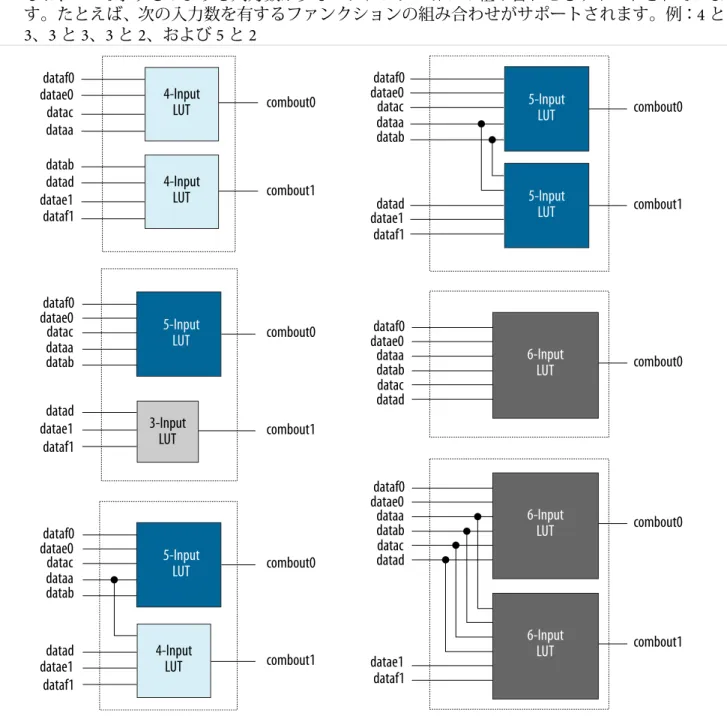

図 1-8: ノーマル・モードの ALM なお、ここで示すものよりも入力数が少ないファンクションの組み合わせもサポートされていま す。たとえば、次の入力数を有するファンクションの組み合わせがサポートされます。例:4 と 3、3 と 3、3 と 2、および 5 と 2 6-Input LUT dataf0 datae0 dataf0 datae0 dataa datab dataa datab datab datac datac dataf0 datae0 dataadatac 6-Input LUT datad datad datae1 combout0 combout1 combout0 combout1 combout0 combout1 dataf1 datae1 dataf1 datad datae1 dataf1 4-Input LUT 4-Input LUT 4-Input LUT 6-Input LUT dataf0 datae0 dataa datab datac datad combout0 5-Input LUT 5-Input LUT dataf0 datae0 dataa datab datac datad combout0 combout1 datae1 dataf1 5-Input LUT dataf0 datae0 dataa datab datac datad combout0 combout1 datae1 dataf1 5-Input LUT 3-Input LUT 2 つの 5 入力ファンクションを 1 つの ALM にパッキングする際、これらのファンクションは少 なくとも 2 つの共通入力を有している必要があります。共通入力はdataaとdatabです。4 入 力ファンクションと 5 入力ファンクションの組み合わせでは、1 つの共通入力(dataaまたは databのいずれか)が必要です。 2 つの 6 入力ファンクションを 1 つの ALM に実装する場合、4 入力を共有する必要があり、組み 合わせファンクションは同じでなければなりません。使用頻度の低いデバイスでは、Quartus II ソフトウェアを使用して 1 つの ALM に配置できるファンクションを別の ALM に実装すること により、最高のパフォーマンスを実現することができます。デバイスの使用率が高くなり始める 1-10 ノーマル・モード 2013.12.02A10-LAB

と、Quartus II ソフトウェアは自動的に Arria® 10 の ALM を最大限に活用します。Quartus II のコ ンパイラは共通入力を使用するファンクションまたは完全に独立したファンクションを自動的 に検索します。これらのファンクションを 1 つの ALM に配置することにより、デバイスのリソ ースを効率的に使用します。なお、ロケーション・アサインメントを設定することによってリソ ース使用量を手動でコントロールすることもできます。 図 1-9: ノーマル・モードの入力ファンクション 6-Input LUT datae0 dataf1 dataa datab datac datad datae1 dataf0 labclk reg1 一般配線へ reg0 reg3 reg2 これらの入力はレジスタ・パッキング で使用できます。 次の入力を使用して任意の 6 入力ファンクションを実装することができます。 • dataa • datab • datac • datad

• datae0とdataf1、またはdatae1とdataf0

datae0およびdataf1入力を使用する場合、次の出力が得られます。

• register0またはバイパスされたregister0に駆動される出力

• register1またはバイパスされたregister1に駆動される出力

register2またはregister3へのパッキングされたレジスタ入力として、使用可能なdatae1入力

またはdataf0入力のいずれかを使用することができます。

datae1およびdataf0入力を使用する場合、次の出力が得られます。

A10-LAB

• register2またはバイパスされたregister2に駆動される出力

• register3またはバイパスされたregister3に駆動される出力

register0またはregister1へのパッキングされたレジスタ入力として、使用可能なdatae0入力

またはdataf1入力のいずれかを使用することができます。

拡張 LUT モード

図 1-10: Arria 10 デバイスの拡張 LUT モードでサポートされる 7 入力ファンクションのテンプレー ト Extended LUT datae0 datae1 dataf0 dataa datab datac datad dataf1 この入力はレジスタ・ パッキングで使用できます。 labclk reg1 一般配線へ reg0 reg3 reg2 次の入力を使用して、7 入力ファンクションを単一の ALM に実装することができます。 • dataa • datab • datac • datad • datae0 • datae1 • dataf0またはdataf1 dataf0入力を使用する場合、次の出力が得られます。 • register0またはバイパスされたregister0に駆動される出力 • register1またはバイパスされたregister1に駆動される出力register2またはregister3へのパッキングされたレジスタ入力として、dataf1入力を使用する

ことができます。

dataf1入力を使用する場合、次の出力が得られます。

• register2またはバイパスされたregister2に駆動される出力

• register3またはバイパスされたregister3に駆動される出力

register0またはregister1へのパッキングされたレジスタ入力として、dataf0入力を使用する

ことができます。

演算モード

演算モードの ALM は、2 つの専用全加算器と共に 2 つの 4 入力 LUT を 2 組使用します。 専用加算器は、LUT がプリ加算ロジックを実行することを可能にします。そのため、各加算器 は 2 つの 4 入力ファンクションの出力を加算することができます。 ALM は組み合わせロジックの出力と加算器のキャリー出力の同時使用をサポートします。加算 器の出力は、この動作では無視されます。 組み合わせロジックの出力と加算器を併用すると、このモードを使用することができるファンク ションのリソースを最大 50%節約します。 また、演算モードではクロック・イネーブル、カウンタ・イネーブル、同期アップ/ダウン・コ ントロール、加算/減算コントロール、同期クリア、および同期ロードを提供します。 クロック・イネーブル、カウンタ・イネーブル、同期アップ/ダウン・コントロール、および加 算/減算コントロールの各信号は、LAB ローカル・インタコネクトのデータ入力によって生成さ れます。これらのコントロール信号は、ALM 内の 4 つの LUT の間で共有される入力に使用でき ます。 同期クリア・オプションと同期ロード・オプションは、LAB 内のすべてのレジスタに影響する LAB ワイド信号です。これらの信号はレジスタごとに個別にディセーブルまたはイネーブルす ることができます。Quartus II ソフトウェアは、カウンタによって使用されていないレジスタを 自動的に他の LAB に配置します。 A10-LAB 2013.12.02 演算モード 1-13図 1-11: Arria 10 デバイスにおける演算モードの ALM datae0 carry_in carry_out dataa databdatac datad datae1 4-Input LUT 4-Input LUT 4-Input LUT 4-Input LUT adder1 dataf0 dataf1 adder0 reg1 一般配線へ reg0 reg3 reg2 キャリー・チェイン キャリー・チェインは、演算モードまたは共有演算モードで、専用加算器間の高速キャリー・フ ァンクションを提供します。 Arria® 10 デバイスの 2 ビット・キャリー選択機能は、ALM 内のキャリー・チェインの伝播遅延

を半減させます。チャリー・チェインは、LAB 内の最初の ALM または 5 番目の ALM のいずれ かで開始することができます。最後のキャリー・アウト信号は ALM に接続され、そこでローカ ル、ロウ、カラムのいずれかのインタコネクトに供給されます。

高ファンイン演算ファンクションが実装される際、デバイス内の 1 つの小さな領域で配線が密集 することを防ぐため、LAB は、次の LAB に接続する前に LAB の上半分また下半分のいずれかの みを使用するキャリー・チェインをサポートすることができます。これにより、LAB 内の ALM の残り半分は、ノーマル・モードでより狭いファンイン・ファンクションを実装する際に使用で きます。最初の LAB 内の上位 5 つの ALM を使用するキャリー・チェインは、カラム内で次の LAB の ALM の上半分に取り込みます。また、最初の LAB 内の下位 5 つの ALM を使用するキャ リー・チェインは、カラム内で次の LAB の ALM の下半分に取り込みます。なお、LAB カラムの 上半分と MLAB カラムの下半分をバイパスすることができます。

Quartus II のコンパイラは、複数の LAB を自動的にリンクさせることにより、20 個以上の ALM (演算モードまたは共有演算モードでは 10 個の ALM)で構成される長いキャリー・チェインを

作成します。フィッティング機能を強化するため、長いキャリー・チェインは垂直に並べ、 TriMatrix メモリおよび DSP ブロックへの水平方向の接続を高速化することができます。キャリ ー・チェインはカラム全体に延長することができます。

共有演算モード

共有演算モードの ALM は、ALM 内に 3 入力加算機能を実装することができます。

このモードでは、ALM は 4 つの 4 入力 LUT で構成されます。各 LUT は、3 入力の合計または 3 入力のキャリーのいずれかを計算します。キャリー計算の出力は、共有演算チェインと呼ばれる 専用の接続を使用して次の加算器に供給されます。 図 1-12: Arria 10 デバイスにおける共有演算モードの ALM datae0 carry_in shared_arith_in shared_arith_out carry_out dataa databdatac datad datae1 4-Input LUT 4-Input LUT 4-Input LUT 4-Input LUT labclk reg1 一般配線へ reg0 reg3 reg2 共有演算チェイン 拡張演算モードで使用可能な共有演算チェインは、ALM による 3 入力加算器の実装を可能にし ます。これにより、大きな加算器ツリーや相関器ファンクションを実装するにあたって必要なリ ソースが大幅に減少します。

共有演算チェインは、LAB 内の最初の ALM または 6 番目の ALM のいずれかで開始することが できます。

キャリー・チェインと同様、代替 LAB カラム内の共有演算チェインの上半分と下半分はバイパ スすることができます。この機能により、共有演算チェインを LAB 内の ALM の半分でカスケー ド接続し、別の半分を幅の狭いファンイン・ファンクションに使用できます。すべての LAB で カラムの上半分はバイパス可能です。また、MLAB ではカラムの下半分がバイパス可能です。 Quartus II のコンパイラは、複数の LAB を自動的にリンクさせることにより、20 個以上の ALM (演算モードまたは共有演算モードでは 10 個の ALM)で構成される長い共有演算チェインを作 成します。フィッティング機能を強化するため、長い共有演算チェインは垂直に並べ、TriMatrix A10-LAB

メモリおよび DSP ブロックへの水平方向の接続を高速化することができます。共有演算チェイ ンはカラム全体に延長することができます。

LAB

消費電力管理方法

以下の方法を使用して、LAB 内のスタティックおよびダイナミック消費電力を管理します。

• Arria® 10 の LAB は高性能モードまたは低消費電力モードで動作します。Quartus II ソフトウ

ェアは、ユーザーのデザインに合わせて LAB の消費電力モードを自動的に最適化します。 • クロック(特に LAB クロック)はダイナミック消費電力の大部分を消費します。各 LAB のク ロックおよびクロック・イネーブル信号はリンクされ、共有されるゲート・クロックで制御 することができます。LAB ワイドのクロック・イネーブル信号を使用すると、クロック・ツ リーの全体をディセーブルせずに LAB ワイド・クロックをゲートすることができます。レジ スタ済みロジックの HDL コードでは、クロック・イネーブル構造を使用します。 関連情報 Quartus II ハンドブック「消費電力の最適化」の章 LAB 内のスタティック消費電力およびダイナミック消費電力の実装に関する詳細を提供しま す。