MAX 10

高速 LVDS I/O ユーザー・ガイド

更新情報 フィードバック

UG-M10LVDS

2016.05.02 101 Innovation DriveSan Jose, CA 95134

目次

MAX 10 高速 LVDS I/O の概要... 1-1

アルテラ・ソフト LVDS 実装の概要...1-2MAX 10 高速 LVDS のアーキテクチャと機能... 2-1

MAX 10 LVDS チャネルのサポート... 2-1 MAX 10 LVDS SERDES I/O 規格のサポート...2-7 MAX 10 高速 LVDS 回路...2-11 MAX 10 高速 LVDS I/O の位置... 2-12 低速領域に位置する差動 I/O ピン...2-15MAX 10LVDS トランスミッタのデザイン... 3-1

高速 I/O トランスミッタ回路...3-1 LVDS トランスミッタのプログラマブル I/O 機能...3-1 プログラマブル・プリエンファシス... 3-1 プログラマブル差動出力電圧... 3-2 LVDS トランスミッタ I/O の終端方式...3-3 エミュレーション LVDS の外部終端...3-3 Sub-LVDS トランスミッタの外部終端... 3-4 SLVS トランスミッタの外部終端...3-4 エミュレーション RSDS、エミュレーション Mini-LVDS、およびエミュレーショ ン PPDS トランスミッタの外部終端... 3-5 LVDS トランスミッタ用 FPGA デザインの実装...3-6 トランスミッタ・モードのアルテラ・ソフト LVDS IP コア... 3-6 高速 I/O のタイミング・バジェット...3-9 ガイドライン:LVDS トランスミッタ・チャネルの配置... 3-9 ガイドライン:LVDS チャネル PLL の配置...3-10 ガイドライン:LVDS トランスミッタ・ロジックの配置... 3-10 ガイドライン:E144 パッケージ向けに LVDS プリエンファシスを有効にする...3-11 LVDS トランスミッタのデバッグとトラブルシューティング ...3-11 ハードウェアのデバッグ前に RTL シミュレーションを行う... 3-11 ジオメトリ・ベースと物理ベースの I/O ルール...3-11MAX 10 LVDS レシーバのデザイン... 4-1

高速 I/O レシーバ回路...4-1 ソフト・デシリアライザ... 4-1 データ・リアラインメント・ブロック(ビット・スリップ)...4-2 目次-2 Altera CorporationLVDS レシーバ I/O の終端方式...4-3 LVDS、mini-LVDS、RSDS およびレシーバの外部終端... 4-3 SLVS レシーバの外部終端...4-3 Sub-LVDS レシーバの外部終端... 4-4 TMDS レシーバの外部終端...4-5 HiSpi レシーバの外部終端...4-5 LVPECL レシーバの外部終端...4-5 LVDS レシーバ用 FPGA デザインの実装... 4-7 レシーバ・モードのアルテラ・ソフト LVDS IP コア...4-7 高速 I/O のタイミング・バジェット... 4-10 ガイドライン:フローティング LVDS 入力ピン...4-13 ガイドライン:LVDS レシーバ・チャネルの配置... 4-13 ガイドライン:LVDS チャネル PLL の配置...4-14 ガイドライン:LVDS レシーバ・ロジックの配置... 4-14 ガイドライン:LVDS レシーバのタイミング制約... 4-14 LVDS レシーバのデバッグとトラブルシューティング...4-15 ハードウェアのデバッグ前に RTL シミュレーションを行う... 4-15 ジオメトリ・ベースと物理ベースの I/O ルール...4-15

MAX 10 LVDS トランスミッタとレシーバのデザイン...5-1

トランスミッタとレシーバのインタフェース...5-1 LVDS トランスミッタとレシーバ用 FPGA デザインの実装...5-3 LVDS トランスミッタとレシーバで PLL を共有する実装...5-3 アルテラ・ソフト LVDS IP コアの初期化... 5-3 LVDS トランスミッタとレシーバのデバッグとトラブルシューティング ...5-4 ハードウェアのデバッグ前に RTL シミュレーションを行う... 5-4 ジオメトリ・ベースと物理ベースの I/O ルール...5-4MAX 10 高速 LVDS ボード・デザインの考慮事項... 6-1

ガイドライン:信号品質の向上...6-1 ガイドライン:チャネル間スキューのコントロール... 6-2 レシーバ入力スキュー・マージン...6-2 LVDS レシーバの RSKM レポート...6-3 ガイドライン:ボード・デザイン制約の決定...6-4 ガイドライン:ボードレベル・シミュレーションの実行...6-5アルテラ・ソフト LVDS IP コアの参考資料... 7-1

アルテラ・ソフト LVDS のパラメータ設定 ...7-1 アルテラ・ソフト LVDS のインタフェース信号...7-7MAX 10 高速 LVDS I/O ユーザー・ガイドのアーカイブ... A-1

MAX 10 高速 LVDS I/O ユーザー・ガイドの改訂履歴... B-1

目次-4

MAX 10

高速 LVDS I/O の概要

1

2016.05.02UG-M10LVDS 更新情報 フィードバック

MAX® 10 デバイス・ファミリは、LVDS I/O バンクおよびアルテラ・ソフト LVDS IP コアを使用

して、高速 LVDS プロトコルをサポートしています。

表 1-1: MAX 10 I/O バンクの LVDS I/O バッファ・サポートのまとめ

I/Oバッファ・タイプ I/Oバンク・サポート 真の LVDS 入力バッファ すべての I/O バンク 真の LVDS 出力バッファ デバイス下側の I/O バンクのみ エミュレーション LVDS 出力バッファ すべての I/O バンク MAX 10 の D バリアントと S バリアントで LVDS I/O 規格のサポートが異なります。詳しくは関 連情報を参照してください。 関連情報 • 2-1 ページの MAX 10 高速 LVDS のアーキテクチャと機能 MAX 10 デバイスがサポートする高速 LVDS アーキテクチャおよび機能について情報を提供 します。 • 3-1 ページの MAX 10LVDS トランスミッタのデザイン MAX 10 デバイスでアルテラ・ソフト LVDS IP コアを使用する LVDS トランスミッタの実装に ついての情報およびガイドラインを提供します。 • 4-1 ページの MAX 10 LVDS レシーバのデザイン MAX 10 デバイスでアルテラ・ソフト LVDS IP コアを使用する LVDS レシーバの実装について の情報およびガイドラインを提供します。 • 5-1 ページの MAX 10 LVDS トランスミッタとレシーバのデザイン 同じ MAX 10 デバイス内に LVDS トランスミッタおよびレシーバの両方を実装するためのデ ザイン・ガイドラインを提供します。 • 7-1 ページの アルテラ・ソフト LVDS IP コアの参考資料 MAX 10 デバイス向けのアルテラ・ソフト LVDS IP コアのパラメータおよび信号をリストしま す。

© 2016 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Megacore, NIOS, Quartus and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008

登録済

• 2-7 ページの MAX 10 LVDS SERDES I/O 規格のサポート サポートされる LVDS I/O 規格およびそれぞれの MAX 10 デバイス・バリアントでのサポート についてリストします。 • 8-1 ページの MAX 10 高速 LVDS I/O ユーザー・ガイドのアーカイブ 前バージョンのアルテラ・ソフト LVDSIP コア向けのユーザー・ガイドのリストを提供しま す。

アルテラ・ソフト LVDS 実装の概要

MAX 10 デバイスに、LVDS アプリケーションをトランスミッタ専用、レシーバ専用、あるいは トランスミッタとレシーバの組み合わせとして実装できます。 図 1-1: MAX 10 LVDS 実装の概要 Altera Soft LVDS LVDS TransmitterImplementation LVDS Transmitterand Receiver

Implementation LVDS Receiver

Implementation

1-2 アルテラ・ソフト LVDS 実装の概要 UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS I/O の概要

MAX 10

高速 LVDS のアーキテクチャと機能

2

2016.05.02UG-M10LVDS 更新情報 フィードバック

MAX 10 デバイスでは、コア・ファブリック内のレジスタおよびロジックを使用して LVDS 入出 力インタフェースを実装します。

• LVDS トランスミッタとレシーバ向けに、 MAX 10 デバイスは、I/O エレメント(IOE)内に あるダブル・データ・レート I/O(DDIO)レジスタを使用する。このアーキテクチャにより、 レシーバの入力スキュー・マージン(RSKM)またはトランスミッタのチャネル間スキュー (TCCS)に関連する性能が向上する • LVDS シリアライザ/デシリアライザ(SERDES)向けには、 MAX 10 デバイスはロジック・エ レメント(LE)レジスタを使用する 関連情報 • 1-1 ページの MAX 10 高速 LVDS I/O の概要

• 2-7 ページの MAX 10 LVDS SERDES I/O 規格のサポート

サポートされる LVDS I/O 規格およびそれぞれの MAX 10 デバイス・バリアントでのサポート についてリストします。

MAX 10 LVDS

チャネルのサポート

LVDS チャネルを各 MAX 10 デバイスで使用できます。 MAX 10 デバイス内の全ての I/O バンク で真の LVDS 入力バッファとエミュレーション LVDS 出力バッファをサポートしています。た だし、真の LVDS 出力バッファはデバイス下側の I/O バンクでのみサポートしています。

表 2-1: MAX 10 デバイスの LVDS バッファ

以下の表に、デバイスの側面にある各 I/O バンクにおける LVDS バッファのサポートを示しま す。

© 2016 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Megacore, NIOS, Quartus and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008

登録済

製品ライン パッケージ 位置 真の LVDS ペア エミュレーション LVDS ペア TX RX 10M02 V36 上側 0 1 1 右側 0 3 3 左側 0 3 3 下側 3 3 3 M153 上側 0 12 12 右側 0 12 12 左側 0 12 12 下側 9 13 13 U169 上側 0 12 12 右側 0 17 17 左側 0 15 15 下側 9 14 14 U324 上側 0 13 13 右側 0 24 24 左側 0 20 20 下側 9 16 16 E144 上側 0 10 10 右側 0 12 12 左側 0 11 11 下側 7 12 12 2-2 MAX 10 LVDSチャネルのサポート UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS のアーキテクチャと機能 フィードバック

製品ライン パッケージ 位置 真の LVDS ペア エミュレーション LVDS ペア TX RX 10M04 M153 上側 0 12 12 右側 0 12 12 左側 0 12 12 下側 9 13 13 U169 上側 0 12 12 右側 0 17 17 左側 0 15 15 下側 9 14 14 U324 上側 0 27 27 右側 0 31 31 左側 0 28 28 下側 15 28 28 F256 上側 0 19 19 右側 0 22 22 左側 0 19 19 下側 13 20 20 E144 上側 0 8 8 右側 0 12 12 左側 0 11 11 下側 10 10 10 UG-M10LVDS 2016.05.02 MAX 10 LVDSチャネルのサポート 2-3

MAX 10高速 LVDS のアーキテクチャと機能 Altera Corporation

製品ライン パッケージ 位置 真の LVDS ペア エミュレーション LVDS ペア TX RX 10M08 V81 上側 0 5 5 右側 0 7 7 左側 0 6 6 下側 7 7 7 M153 上側 0 12 12 右側 0 12 12 左側 0 12 12 下側 9 13 13 U169 上側 0 12 12 右側 0 17 17 左側 0 15 15 下側 9 14 14 U324 上側 0 27 27 右側 0 31 31 左側 0 28 28 下側 15 28 28 F256 上側 0 19 19 右側 0 22 22 左側 0 19 19 下側 13 20 20 E144 上側 0 8 8 右側 0 12 12 左側 0 11 11 下側 10 10 10 F484 上側 0 27 27 右側 0 33 33 左側 0 28 28 下側 15 28 28 2-4 MAX 10 LVDSチャネルのサポート UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS のアーキテクチャと機能 フィードバック

製品ライン パッケージ 位置 真の LVDS ペア エミュレーション LVDS ペア TX RX 10M16 U169 上側 0 12 12 右側 0 17 17 左側 0 15 15 下側 9 14 14 U324 上側 0 27 27 右側 0 31 31 左側 0 28 28 下側 15 28 28 F256 上側 0 19 19 右側 0 22 22 左側 0 19 19 下側 13 20 20 E144 上側 0 8 8 右側 0 12 12 左側 0 11 11 下側 10 10 10 F484 上側 0 39 39 右側 0 38 38 左側 0 32 32 下側 22 42 42 UG-M10LVDS 2016.05.02 MAX 10 LVDSチャネルのサポート 2-5

MAX 10高速 LVDS のアーキテクチャと機能 Altera Corporation

製品ライン パッケージ 位置 真の LVDS ペア エミュレーション LVDS ペア TX RX 10M25 F256 上側 0 19 19 右側 0 22 22 左側 0 19 19 下側 13 20 20 E144 上側 0 8 8 右側 0 12 12 左側 0 11 11 下側 10 10 10 F484 上側 0 41 41 右側 0 48 48 左側 0 36 36 下側 24 46 46 10M40 F256 上側 0 19 19 右側 0 22 22 左側 0 19 19 下側 13 20 20 E144 上側 0 9 9 右側 0 12 12 左側 0 11 11 下側 10 10 10 F484 上側 0 41 41 右側 0 48 48 左側 0 36 36 下側 24 46 46 F672 上側 0 53 53 右側 0 70 70 左側 0 60 60 下側 30 58 58 2-6 MAX 10 LVDSチャネルのサポート UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS のアーキテクチャと機能 フィードバック

製品ライン パッケージ 位置 真の LVDS ペア エミュレーション LVDS ペア TX RX 10M50 F256 上側 0 19 19 右側 0 22 22 左側 0 19 19 下側 13 20 20 E144 上側 0 9 9 右側 0 12 12 左側 0 11 11 下側 10 10 10 F484 上側 0 41 41 右側 0 48 48 左側 0 36 36 下側 24 46 46 F672 上側 0 53 53 右側 0 70 70 左側 0 60 60 下側 30 58 58

MAX 10 LVDS SERDES I/O

規格のサポート

MAX 10 の D バリアントと S バリアントでは、サポートされる LVDS I/O 規格が異なります。 MAX 10 デバイス内の全ての I/O バンクで、真の LVDS 入力バッファとエミュレーション LVDS 出力バッファをサポートしています。ただし、真の LVDS 出力バッファはデバイス下側の I/O バ ンクでのみサポートしています。

表 2-2: MAX 10 LVDS I/O 規格のサポート

シングル電源の MAX 10 デバイスとデュアル電源の MAX 10 デバイスでは、サポートされる I/O 規格が異なります。シングル電源およびデュアル電源のデバイスについて、詳しくは Device Overview を参照してください。

UG-M10LVDS

2016.05.02 MAX 10 LVDS SERDES I/O規格のサポート 2-7

MAX 10高速 LVDS のアーキテクチャと機能 Altera Corporation

I/O規格 I/Oバン ク TX RX MAX 10デバイス・サ ポート 備考 デュアル 電源デバ イス シングル 電源デバ イス 真の LVDS すべて 下側の バンク のみ 使用可 使用可 使用可 • 全ての I/O バッファで 真の LVDS 入力バッフ ァがサポートされる • 下側の I/O バンクでの み真の LVDS 出力バッ ファがサポートされる エミュレーショ ン LVDS(抵抗x 3) すべて 使用可 — 使用可 使用可 全ての I/O バッファでエ ミュレーション LVDS 出 力バッファがサポートさ れる 真の RSDS 下側 使用可 — 使用可 使用可 — エミュレーショ ン RSDS(抵抗x 1) すべて 使用可 — 使用可 — 全ての I/O バッファでエ ミュレーション RSDS 出力 バッファがサポートされ る エミュレーショ ン RSDS(抵抗x 3) すべて 使用可 — 使用可 使用可 全ての I/O バッファでエ ミュレーション RSDS 出力 バッファがサポートされ る 真の Mini-LVDS 下側 使用可 — 使用可 — — エミュレーショ ン Mini-LVDS (抵抗x 3) すべて 使用可 — 使用可 — 全ての I/O バッファでエ ミュレーション Mini-LVDS 出力バッファがサポ ートされる PPDS 下側 使用可 — 使用可 — — エミュレーショ ン PPDS(抵抗x 3) すべて 使用可 — 使用可 — —

2-8 MAX 10 LVDS SERDES I/O規格のサポート UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS のアーキテクチャと機能 フィードバック

I/O規格 I/Oバン ク TX RX MAX 10デバイス・サ ポート 備考 デュアル 電源デバ イス シングル 電源デバ イス Bus LVDS すべて 使用可 使用可 使用可 使用可 • Bus LVDS(BLVDS)出 力は、2 つのシングル・ エンド出力を 2 番目の 出力が反転するように プログラミングして使 用する • BLVDS 入力は、LVDS の 入力バッファを使用す る • BLVDS 出力はトライ・ ステートにできる LVPECL すべて — 使用可 使用可 使用可 兼用クロック入力ピンで のみサポートされる TMDS すべて — 使用可 使用可 — • 外部終端が必要だが、 VREFは不要 • 3.3 V TMDS 入力をサポ ートするには外部レベ ル・シフタが必要。この レベル・シフタは MAX 10 入力バッファに接続 される前に TMDS 信号 を AC 結合から DC 結 合に変換する必要があ る • TMDS レシーバ・サポー トでは専用 2.5 V LVDS 入力バッファを使用す る UG-M10LVDS

2016.05.02 MAX 10 LVDS SERDES I/O規格のサポート 2-9

MAX 10高速 LVDS のアーキテクチャと機能 Altera Corporation

I/O規格 I/Oバン ク TX RX MAX 10デバイス・サ ポート 備考 デュアル 電源デバ イス シングル 電源デバ イス Sub-LVDS すべて 使用可 使用可 使用可 — • トランスミッタは、エミ ュレーションした 1.8 V 差動信号を出力として 使用するエミュレーシ ョン Sub-LVDS のみを サポートする • 外部出力終端が必要 • VREFは不要 • Sub-LVDS レシーバ・サ ポートでは専用 2.5 V LVDS 入力バッファを 使用する SLVS すべて 使用可 使用可 使用可 — • SLVS トランスミッタ・ サポートではエミュレ ーション LVDS 出力を 使用する • 外部終端が必要だが、 VREFは不要 • SLVS レシーバ・サポー トでは専用 2.5 V LVDS 入力バッファを使用す る

HiSpi すべて — 使用可 使用可 — • HiSpi は単方向 I/O 規格

なので入力のみがサポ ートされる • 外部終端が必要だが、 VREFは不要 • HiSpi レシーバ・サポー トでは専用 2.5 V LVDS 入力バッファを使用す る 関連情報

• MAX 10 FPGA Device Overview

• 3-3 ページの エミュレーション LVDS の外部終端

2-10 MAX 10 LVDS SERDES I/O規格のサポート UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS のアーキテクチャと機能 フィードバック

• 3-5 ページの エミュレーション RSDS、エミュレーション Mini-LVDS、およびエミュレーシ ョン PPDS トランスミッタの外部終端 • 4-5 ページの TMDS レシーバの外部終端 • 3-4 ページの Sub-LVDS トランスミッタの外部終端 • 4-4 ページの Sub-LVDS レシーバの外部終端 • 3-4 ページの SLVS トランスミッタの外部終端 • 4-3 ページの SLVS レシーバの外部終端 • 4-5 ページの HiSpi レシーバの外部終端

MAX 10

高速 LVDS 回路

LVDS ソリューションは、 MAX 10 デバイスの I/O エレメントとレジスタを使用します。アルテ ラ・ソフト LVDS IP コアは、コア・ロジックにシリアライザとデシリアライザをソフト SERDES ブロックとして実装します。 MAX 10 デバイスは専用のシリアライゼーションまたはデシリアライゼーション回路を備えて いません。 • デバイスへの高速差動インタフェース実装には I/O ピンおよびコア・ファブリックを使用す る • MAX 10 ソリューションは送受信データのシリアル - パラレルおよびパラレル - シリアル変 換を行うためにシフト・レジスタ、内部 PLL、I/O エレメントを使用する• Quartus® Prime ソフトウェアはコア・ファブリックに自動的に SERDES を構築するためにアル

テラ・ソフト LVDS IP コアのパラメータ設定を使用する

UG-M10LVDS

2016.05.02 MAX 10高速 LVDS 回路 2-11

MAX 10高速 LVDS のアーキテクチャと機能 Altera Corporation

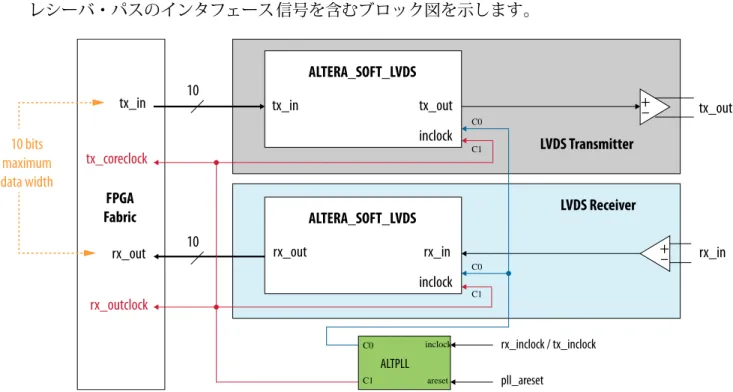

図 2-1: ソフト LVDS SERDES 以下に、ソフト LVDS SERDES 回路のトランスミッタとレシーバ、およびトランシーバ・パスと レシーバ・パスのインタフェース信号を含むブロック図を示します。 FPGA Fabric rx_out tx_in rx_outclock tx_coreclock 10 bits maximum data width +– + – tx_out rx_in 10 10 pll_areset rx_inclock / tx_inclock C0 C0 C0 C1 C1 C1 inclock areset ALTPLL ALTERA_SOFT_LVDS tx_in tx_out inclock ALTERA_SOFT_LVDS rx_out rx_in inclock LVDS Transmitter LVDS Receiver 関連情報

MAX 10 Clocking and PLL User Guide

PLL および PLL 出力カウンタについて詳しい情報を提供します。

MAX 10

高速 LVDS I/O の位置

MAX 10 デバイスの I/O バンクでは、全ての I/O バンクで真の LVDS 入力とエミュレーション LVDS 出力をサポートしています。また、デバイス下側の I/O バンクでのみ真の LVDS 出力をサ ポートしています。

2-12 MAX 10高速 LVDS I/O の位置 UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS のアーキテクチャと機能 フィードバック

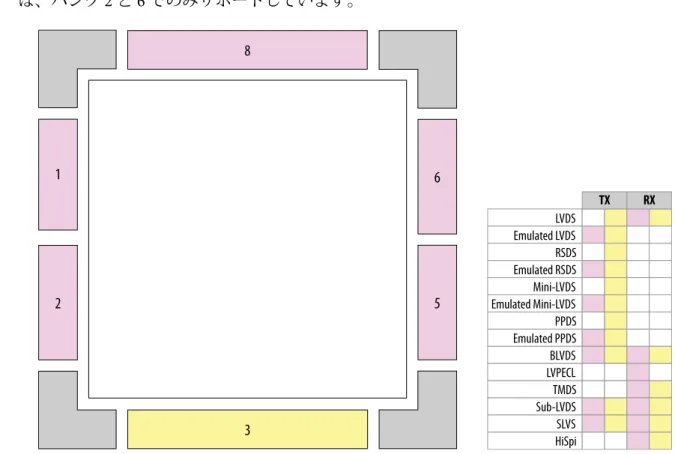

図 2-2: 10M02 デバイスの I/O バンクでの LVDS サポート 以下はシリコン・ダイの概略図です。各バンクに実際のバンク番号を示しています。LVPECL は、バンク 2 と 6 でのみサポートしています。 1 2 5 6 3 8 LVDS Emulated LVDS RSDS Emulated RSDS Mini-LVDS Emulated Mini-LVDS PPDS Emulated PPDS BLVDS LVPECL TMDS Sub-LVDS SLVS HiSpi TX RX UG-M10LVDS 2016.05.02 MAX 10高速 LVDS I/O の位置 2-13

MAX 10高速 LVDS のアーキテクチャと機能 Altera Corporation

図 2-3: 10M04 および 10M08 デバイスの I/O バンクでの LVDS サポート 以下はシリコン・ダイの概略図です。各バンクに実際のバンク番号を示しています。LVPECL は、バンク 2 と 6 でのみサポートしています。 1B 1A 2 5 6 3 4 8 7 LVDS Emulated LVDS RSDS Emulated RSDS Mini-LVDS Emulated Mini-LVDS PPDS Emulated PPDS BLVDS LVPECL TMDS Sub-LVDS SLVS HiSpi TX RX

2-14 MAX 10高速 LVDS I/O の位置 UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS のアーキテクチャと機能 フィードバック

図 2-4: 10M16、10M25、10M40、10M50 デバイスの I/O バンクでの LVDS サポート 以下はシリコン・ダイの概略図です。各バンクに実際のバンク番号を示しています。LVPECL は、バンク 2、3、6、8 でのみサポートしています。 1B 1A 2 3 4 8 7 OCT 5 6 LVDS Emulated LVDS RSDS Emulated RSDS Mini-LVDS Emulated Mini-LVDS PPDS Emulated PPDS BLVDS LVPECL TMDS Sub-LVDS SLVS HiSpi TX RX 関連情報 • PLL Specifications MAX 10 デバイス向けの PLL 性能について詳しい情報を提供します。 • High-Speed I/O Specifications

MAX 10 デバイスでのさまざまなデータ幅向けに最小および最大データ・レートを提供しま す。

低速領域に位置する差動 I/O ピン

一部の差動 I/O ピンは、 MAX 10 デバイスの低速領域に配置されています。

• ユーザーが低速領域に配置した、コンフィギュレーション・ピンを除く各 I/O ピンに対して、 Quartus Prime ソフトウェアが Informational Warning メッセージを表示する

• 低速 I/O ピンを見分けるには、デバイスの Pin-Out File を参照する • 低速 I/O ピンの性能情報は Device Datasheet を参照する

関連情報

• MAX 10 Device Pin-Out Files

各 MAX 10 向けにピンアウト・ファイルを提供します。

UG-M10LVDS

2016.05.02 低速領域に位置する差動 I/O ピン 2-15

MAX 10高速 LVDS のアーキテクチャと機能 Altera Corporation

• MAX 10 Device Datasheet

• MAX 10 I/O Banks Locations, MAX 10 General Purpose I/O User Guide

高速および低速の I/O バンクの位置を確認することができます。

2-16 低速領域に位置する差動 I/O ピン UG-M10LVDS2016.05.02

Altera Corporation MAX 10高速 LVDS のアーキテクチャと機能 フィードバック

MAX 10LVDS

トランスミッタのデザイン

3

2016.05.02 UG-M10LVDS 更新情報 フィードバック MAX 10 LVDS ソリューションを使用して、トランスミッタ専用アプリケーションを実装するこ とができます。 アルテラ・ソフト LVDS IP コアを使用して、ソフト SERDES 回路をインスタン ス化します。ソフト SERDES 回路はクロックおよび差動 I/O ピンとともに動作し、高速差動トラ ンスミッタ回路を作成します。 関連情報 • 1-1 ページの MAX 10 高速 LVDS I/O の概要• 2-7 ページの MAX 10 LVDS SERDES I/O 規格のサポート

サポートされる LVDS I/O 規格およびそれぞれの MAX 10 デバイス・バリアントでのサポート についてリストします。

高速 I/O トランスミッタ回路

LVDS トランスミッタ回路は、 MAX 10 デバイスの I/O エレメントとレジスタを使用します。ア ルテラ・ソフト LVDS IP コアは、コア・ロジックにシリアライザをソフト SERDES ブロックとし て実装します。 関連情報 2-11 ページの MAX 10 高速 LVDS 回路LVDS

トランスミッタのプログラマブル I/O 機能

MAX 10 デバイスの I/O バッファおよびピンの機能のいくつかは、デザイン要件に応じてプログ ラミングが可能です。高速 LVDS トランスミッタ・アプリケーション向けに、プリエンファシス 設定をプログラミングできます。プログラマブル・プリエンファシス

高速伝送信号の出力電流は、差動出力電圧(VOD)設定およびドライバの出力インピーダンスに より制限されます。高い周波数では、次のエッジの前にフル・レベルの VODに達するためにス ルー・レートの速度が十分ではないことがあり、これがパターン依存ジッタを生じさせます。 プリエンファシスは、スイッチング時に出力電圧を瞬間的に増幅し、出力スルー・レートを向上 します。© 2016 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Megacore, NIOS, Quartus and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008

登録済

プリエンファシスは、出力信号の高周波数成分の振幅を増幅させます。この増幅により伝送ライ ンにおける周波数依存の減衰を補償します。 余剰の電流によるオーバーシュートは、ステート・スイッチングの遷移中にのみ生じます。この オーバーシュートは信号の反射によるオーバーシュートとは異なり、出力スルー・レートを高め ますがリンギングはしません。必要なプリエンファシスの量は、伝送ラインにおける高周波数成 分の減衰に依存し ます。 図 3-1: プログラマブル・プリエンファシスを用いた LVDS 出力 OUT OUT VOD VP VP Voltage boost from pre-emphasis Differential output voltage (peak–peak) 表 3-1: プログラマブル・プリエンファシス向け Quartus Prime ソフトウェアのアサインメント フィールド アサインメント To tx_out

Assignment name Programmable Pre-emphasis

Allowed values 0(無効)、1(有効)。デフォルトは 1 です。

プログラマブル差動出力電圧

プログラマブル VOD設定により出力のアイ開口を調整し、トレース長と消費電力を最適化する ことができます。強い VODスイングはレシーバ端における電圧マージンを改善し、低い VODス イングは消費電力を削減します。 3-2 プログラマブル差動出力電圧 UG-M10LVDS2016.05.02Altera Corporation MAX 10LVDSトランスミッタのデザイン

図 3-2: 差動 VOD 以下の図に、差動 LVDS 出力の VODを示します。 Single-Ended Waveform Positive Channel (p) Negative Channel (n) Ground Differential Waveform p - n = 0 V VCM VOD VOD VOD

VOD (diff peak - peak) = 2 x VOD (single-ended)

差動信号の VODは、 Quartus Prime ソフトウェアの Assignment Editor で VOD設定を変更するこ

とによって静的に調整できます。

表 3-2: Quartus Prime ソフトウェア Assignment Editor — プログラマブル VOD

フィールド アサインメント

To tx_out

Assignment name Programmable Differential Output Voltage (VOD)

Allowed values 0(低)、1(中)、2(高)。デフォルトは 2 です。

LVDS

トランスミッタ I/O の終端方式

MAX 10 デバイスのトランスミッタ・アプリケーションでは、外部終端が必要な I/O 規格がいく つかあります。エミュレーション LVDS の外部終端

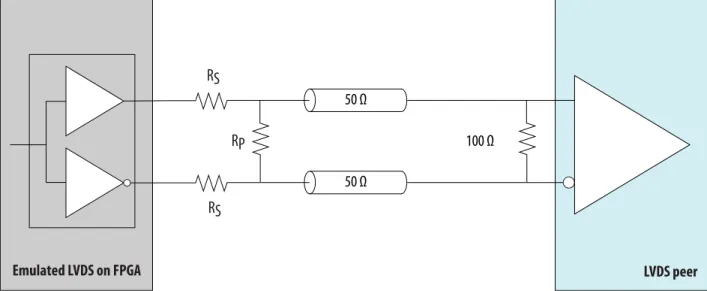

エミュレーション LVDS トランスミッタ向けには、抵抗を 3 つ使用する外部終端方式が必要で す。 UG-M10LVDS 2016.05.02 LVDSトランスミッタ I/O の終端方式 3-3MAX 10LVDSトランスミッタのデザイン Altera Corporation

図 3-3: エミュレーション LVDS トランスミッタの外部終端 この図では、RS = 120 Ω、RP = 170 Ω です。 RS RP RS LVDS peer 50 Ω 50 Ω 100 Ω Emulated LVDS on FPGA

Sub-LVDS

トランスミッタの外部終端

Sub-LVDS トランスミッタ向けには、抵抗を 3 つ使用する外部終端方式が必要です。 図 3-4: Sub-LVDS トランスミッタの外部終端 TX RX Sub-LVDS on FPGA 1.8 V Sub-LVDS peer Z0 = 50 Ω Z0 = 50 Ω 267 Ω 267 Ω 100 Ω 121 ΩSLVS

トランスミッタの外部終端

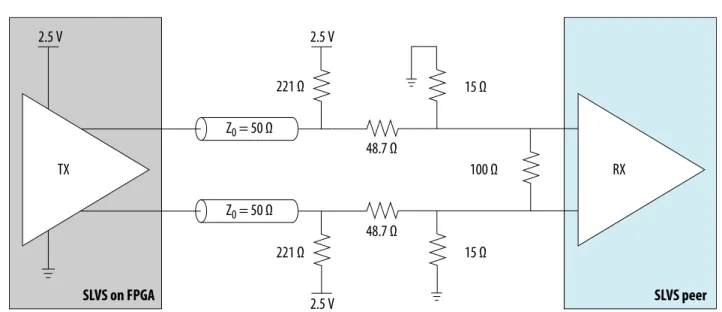

SLVS トランスミッタ向けには、抵抗を 3 つ使用する外部終端方式が必要です。 3-4 Sub-LVDSトランスミッタの外部終端 UG-M10LVDS2016.05.02Altera Corporation MAX 10LVDSトランスミッタのデザイン

図 3-5: SLVS トランスミッタの外部終端 TX RX SLVS on FPGA 2.5 V 2.5 V 2.5 V SLVS peer Z0 = 50 Ω Z0 = 50 Ω 48.7 Ω 48.7 Ω 221 Ω 221 Ω 15 Ω 100 Ω 15 Ω

エミュレーション RSDS、エミュレーション Mini-LVDS、およびエミュレーション

PPDS

トランスミッタの外部終端

エミュレーション RSDS、エミュレーション Mini-LVDS、およびエミュレーション PPDS トラン スミッタ向けには、抵抗を 3 つ使用する外部終端方式が必要です。エミュレーション PPDS トラ ンスミッタ向けには抵抗を 1 つ使用する外部終端も使用できます。 図 3-6: エミレーション RSDS、Mini-LVDS、または PPDS トランスミッタの外部終端 この図では、RS = 120 Ω、RP = 170 Ω です。 RS RP RS RSDS, Mini-LVDS, or PPDS peer 50 Ω 50 Ω 100 Ω Emulated RSDS, Mini-LVDS, or PPDS on FPGA UG-M10LVDS 2016.05.02 エミュレーション RSDS、エミュレーション Mini-LVDS、およびエミュレーション PPDSトランスミッタの外部終端 3-5MAX 10LVDSトランスミッタのデザイン Altera Corporation

図 3-7: エミュレーション RSDS トランスミッタ向けの抵抗 1 つの外部終端 RSDS peer 50 Ω 50 Ω 100 Ω 100 Ω Emulated RSDS on FPGA

LVDS

トランスミッタ用 FPGA デザインの実装

MAX 10 デバイスでは、高速 I/O インタフェースをサポートするためにソフト SERDES アーキテ クチャを使用しています。 Quartus Prime ソフトウェアが、アルテラ・ソフト LVDS IP コアを使 用してコア・ファブリックに SERDES 回路を作成します。タイミング性能を向上させ、SERDES をサポートするために、 MAX 10 デバイスではコア・ファブリックの I/O レジスタと LE レジス タを使用します。

トランスミッタ・モードのアルテラ・ソフト LVDS IP コア

Quartus Prime ソフトウェアで、アルテラ・ソフト LVDSIP コアを使用して高速トランスミッタ・ インタフェースをデザインすることができます 。この IP コアは、高速 I/O インタフェースを作 成するために MAX 10 デバイス内のリソースを最も有利に活用します。 • デザイン要件に応じてシリアライザをカスタマイズするためにアルテラ・ソフト LVDS パラ メータ・エディタを使用可能 • アルテラ・ソフト LVDS IP コアを使用して作成された高速 I/O インタフェースは、常にパラ レル・データの最上位ビット(MSB)から先に送信する 関連情報 • 7-1 ページの アルテラ・ソフト LVDS のパラメータ設定

• Introduction to Altera IP Cores

すべてのアルテラ IP コアについて、パラメータ化、アップグレード、IP のシミュレーション といった基本的な情報を提供します。

• Creating Version-Independent IP and Qsys Simulation Scripts

ソフトウェアあるいは IP のバージョンのアップグレードのためのマニュアルでの更新を必 要としないシミュレーション・スクリプトの作成について詳しい情報を提供します。

3-6 LVDSトランスミッタ用 FPGA デザインの実装 UG-M10LVDS2016.05.02

Altera Corporation MAX 10LVDSトランスミッタのデザイン

• Project Management Best Practices プロジェクトおよび IP ファイルの効果的な管理および移植性のためのガイドラインを提供 します。

アルテラ・ソフト LVDS IP コアでの PLL ソースの選択

アルテラ・ソフト LVDS IP コアを、内部 PLL または外部 PLL と併せてインスタンス化すること により、LVDS インタフェース・コンポーネントを作成できます。 内部 PLL を使用するアルテラ・ソフト LVDS IP コアのインスタンス化 アルテラ・ソフト LVDS IP コアを、SERDES コンポーネントを構築し、PLL を内部にインスタン ス化するように設定できます。• この手法を使用するには、PLL Settings タブの Use external PLL オプションをオフにし、PLL

Settings タブおよび Transmitter Settings タブで必要な設定をセットする

• アルテラ・ソフト LVDS IP コアは、PLL を LVDS ブロックに統合する

• この手法の欠点は、この PLL をこの LVDS インタフェース向けにしか使用できないこと

外部 PLL を使用するアルテラ・ソフト LVDS IP コアのインスタンス化

アルテラ・ソフト LVDS IP コアは、SERDES コンポーネントだけを構築し、外部 PLL ソースを使 用するように設定可能です。

• この手法を使用するには、PLL Settings タブの Use external PLL オプションをオンにする • 通知が表示されるパネルにリストされているとおりに入力ポートに必要なクロック設定を行

う

• ALTPLL IP コアを使用して、独自のクロック・ソースを作成できる

• PLL の使用方法をコアの他の機能とあわせて最適化するためにこの手法を使用する 関連情報

• MAX 10 Clocking and PLL User Guide

PLL および PLL 出力カウンタについて詳しい情報を提供します。 • MAX 10 Clocking and PLL User Guide

PLL および PLL 出力カウンタについて詳しい情報を提供します。

ガイドライン:外部 PLL を使用する LVDS TX インタフェース

Use External PLL オプションを用いるアルテラ・ソフト LVDSIP コアをインスタンス化すること

ができます。外部 PLL を使用することにより、PLL 設定を制御できます。たとえば、多様なデー タ・レートと動的な位相シフトをサポートするために、PLL を動的にリコンフィギュレーション できます。このオプションを用いるためには、ALTPLLIP コアをインスタンス化して、さまざま なクロック信号を生成する必要があります。 アルテラ・ソフト LVDS のトランスミッタ向けに Use External PLL オプションをオンにした場 合、ALTPLLIP コアからの以下の信号が必要になります。 • アルテラ・ソフト LVDS トランスミッタのtx_inclockポートへのシリアル・クロッ入力 • FPGA ファブリックのトランスミッタ・ロジックをクロック駆動するために使用する、 tx_syncclockポートに接続されているパラレル・クロック UG-M10LVDS 2016.05.02 アルテラ・ソフト LVDS IP コアでの PLL ソースの選択 3-7

MAX 10LVDSトランスミッタのデザイン Altera Corporation

関連情報

MAX 10 Clocking and PLL User Guide

PLL および PLL 出力カウンタについて詳しい情報を提供します。 アルテラ・ソフト LVDS トランスミッタに用いる ALTPLL 信号インタフェース LVDS インタフェース・クロックを生成するために、あらゆる PLL 出力クロック・ポートを選択 できます。 ALTPLL トランスミッタの外部 PLL ソースとしてアルテラ・ソフト LVDS IP コアを使用する場合 は、ソース・シンクロナス・コンペンセーション・モードを使用します。 表 3-3: ALTPLL とアルテラ・ソフト LVDS トランスミッタの間の信号インタフェースの例 ALTPLL IPコアより アルテラ・ソフト LVDS トランスミッタへ 高速クロック出力(c0) 高速クロック出力(c0)は、アルテ ラ・ソフト LVDS トランスミッタの tx_inclockのみ駆動できます。 tx_inclock 低速クロック出力(c1) tx_syncclock アルテラ・ソフト LVDS のトランスミッタ向けに外部 PLL クロックのパラメータを決定する ALTPLL IP コアのトランスミッタ向けにアルテラ・ソフト LVDS IP コア・クロックのパラメータ を決定するために、デザインで以下の手順を実行します。 1. 内部 PLL を使用するアルテラ・ソフト LVDSIP コアのトランスミッタをインスタンス化しま す。 2. デザインを TimeQuest タイミング解析までコンパイルします。

3. Compilation Report ウィンドウの Table of Contents セクションで、TimeQuest Timing Analyzer > Clocks に移動します。 4. アルテラ・ソフト LVDS IP コア・トランスミッタの内部 PLL に使用されるクロック・パラメ ータを書きとめておきます。 クロックのリストのclk0が高速クロックです。 図 3-8: アルテラ・ソフト LVDS トランスミッタのクロック・パラメータの例 3-8 アルテラ・ソフト LVDS トランスミッタに用いる ALTPLL 信号インタフェース UG-M10LVDS2016.05.02

Altera Corporation MAX 10LVDSトランスミッタのデザイン

上記の手順で書きとめておいたパラメータで ALTPLL 出力クロックをコンフィギュレーション し、適切なアルテラ・ソフト LVDS クロック入力ポートにクロック出力を接続します。

アルテラ・ソフト LVDS IP コアの初期化

PLL は、アルテラ・ソフト LVDS IP コアがデータ転送向け SERDES ブロックを実装する前にリフ ァレンス・クロックにロックします。 デバイスの初期化時に、PLL はリファレンス・クロックへのロックを開始し、ロックを達成する とユーザー・モード時に動作可能になります。クロックのリファレンスが安定していなければ、 PLL 出力クロックの位相シフトに乱れが生じます。この位相シフトの乱れが、高速 LVDS ドメイ ンと低速パラレル・ドメイン間のデータ転送の不具合や破損の原因になります。 データの破損を避けるために、アルテラ・ソフト LVDS IP コアの初期化時に以下のステップを実 行します。 1. pll_areset信号を少なくとも 10 ns 以上アサートします。 2. 10 ns 以上経過してから、pll_areset信号をディアサートします。 3. PLL ロックが安定するまで待機します。 PLL ロック・ポートがアサートし、安定すると、SERDES ブロックの動作準備が整います。高速 I/O のタイミング・バジェット

LVDS I/O 規格は、データの高速伝送を可能にし、システム全体の性能向上を実現します。 高速 のシステム性能を活用するには、この高速信号のタイミングを解析する必要があります。差動ブ ロックのタイミング解析は、従来の同期タイミング解析手法とは異なります。 ソース・シンクロナス・タイミング解析は、クロック - 出力のセットアップ時間ではなく、デー タとクロック信号間のスキューに基づきます。高速差動データ伝送には、IC ベンダによって提 供されるタイミング・パラメータを使用する必要があり、ボード・スキュー、ケーブル・スキュ ー、およびクロック・ジッタによる強い影響を受けます。トランスミッタのチャネル間スキュー

レシーバ入力スキュー・マージン(RSKM)の計算には、トランスミッタのチャネル間スキュー (TCCS)を使用します。TCCS は、ソース・シンクロナス差動インタフェースの MAX 10 トラン スミッタに基づいた重要なパラメータです。TCCS 値は Device Datasheet で入手可能です。 関連情報MAX 10 Device Datasheet

ガイドライン:LVDS トランスミッタ・チャネルの配置

VCCIO電源で許容ノイズ・レベルを維持するには、差動パッドに対するシングル・エンド I/O ピ

ンの配置に関する制約に従う必要があります。

アルテラは、 Quartus Prime デザインを作成し、デバイスの I/O 割り当てを指定し、デザインを コンパイルしてピン配置の妥当性を確認することを推奨しています。 Quartus Prime ソフトウェ アは、デバイスの正常動作を確保するために、I/O 割り当ておよび配置ルールを基準にピン接続 を検証します。

Quartus Prime の Pin Planner Package ビューを使用すると、差動 I/O 割り当ての計画が簡単になり ます。

UG-M10LVDS

2016.05.02 アルテラ・ソフト LVDS IP コアの初期化 3-9

MAX 10LVDSトランスミッタのデザイン Altera Corporation

• View メニューで Show Differential Pin Pair Connections をクリックし、差動ピン・ペアをハイ ライト表示する。差動ピン・ペアは赤い線で結び付けられている • 差動ピンに関しては、割り当てが必要なのは正のピンへの信号のみ。 Quartus Prime ソフトウ ェアは、正のピンが差動 I/O 規格に割り当てられると自動的に負のピンへの割り当てを行う MAX 10 デバイスでは、各差動ピン・ペアの配線を一致させています。したがって、正と負のピ ン間のスキューは最小です。差動ペアの両方のピンの内部配線は、ピンが隣接していない場合で も一致しています。 MAX 10 は、x18 バンドル・モードをサポートしています。スキューを制御するためには、同じ バンドル内の全ての LVDS チャネルを隣り合わせに配置し、また、チャネルが I/O バンクをクロ スしないようにします。スキューを最小に、性能を最大にするために、PCB デザインでパッケ ージ・スキューを補償することを推奨します。

ガイドライン:LVDS チャネル PLL の配置

MAX 10 デバイスの各 PLL は、PLL と同じ側にある I/O バンク内の LVDS チャネルのみを駆動で きます。 表 3-4: MAX 10 デバイスで I/O バンクの駆動に使用可能な PLL の例I/Oバンクの位置 入力refclk GCLK mux 使用可能な PLL

左側 左側 左側 左上または左下

下側 下側 下側 左下または右下

右側 右側 右側 右上または右下

上側 上側 上側 左上または右上

ガイドライン:LVDS トランスミッタ・ロジックの配置

Quartus Prime ソフトウェアは、タイミング要件を満たすように SERDES ロジックの配置を自動 的に最適化します。このため、ユーザーがアルテラ・ソフト LVDSIP コア・ロジックで配置の制 約を行う必要がありません。

Quartus Prime Fitter の性能を向上させるには、デバイスのフロアプランに LogicLock™領域を作成

し、トランスミッタ SERDES ロジックの配置を制限します。 • TCCS パラメータは、同じサイドに配置された差動 I/O バンク全体に対してデータシートの仕 様のように保証されている。この保証は、トランスミッタの SERDES ロジックが出力ピンに 隣接する LAB に配置されている場合に適用される • TCCS 性能を向上させるために、トランスミッタ SERDES ロジックをデータ出力ピンとクロッ ク出力ピンに隣接する LAB に制限する 関連情報

Quartus Prime Incremental Compilation for Hierarchical and Team-Based Design chapter, Volume 1: Design and Synthesis, Quartus Prime Handbook

LogicLock ロケーション・アサインメントによるデザイン・フロアプランの作成について段階ご との手順を提供します。

3-10 ガイドライン:LVDS チャネル PLL の配置 UG-M10LVDS2016.05.02

Altera Corporation MAX 10LVDSトランスミッタのデザイン

ガイドライン:E144 パッケージ向けに LVDS プリエンファシスを有効にする

アルテラは、E144 パッケージの MAX 10 デバイスでは、最良のシグナル・インテグリティ(SI) 性能を得るために LVDS プリエンファシスを有効にすることを推奨します。プリエンファシス を有効にしないと、デバイスで引き起こされる可能性がある望ましくない SI 状態により、LVDS のアイの高さが影響を受けます。LVDS

トランスミッタのデバッグとトラブルシューティング

FPGA プロトタイプを使用したボードレベルの検証により、LVDS インタフェース性能に関して 役立つ情報を得ることができます。 ボードレベルの検証の主要な目的は FPGA の機能をエンド・システムで検証することにあります が、手順を追加することによりマージンについて調べることが可能になります。オシロスコープ を使用してマージンについて調べることにより、予測されるデータ有効ウィンドウのサイズ、な らびに I/O インタフェースのセットアップおよびホールド・マージンを検証することができま す。 アルテラの SignalTap® II ロジック・アナライザを使用してシステム・レベルの検証を行い、デザ イン・ターゲットに対するシステムの相関を確認することもできます。 関連情報In-System Debugging Using External Logic Analyzers chapter, Volume 3: Verification, Quartus Prime Handbook

ハードウェアのデバッグ前に RTL シミュレーションを行う

アルテラは、ハードウェアでデバッグを行う前に RTL シミュレーションを行うことを推奨しま す。RTL シミュレーションの活用により、実際のハードウェアをテストする前にコードの機能性 を確認できます。 たとえば、RTL シミュレーションを使用して、リモート・トランスミッタからトレーニング・パ ターンを送信した際の LVDS レシーバのビット・スリップ・メカニズムの機能を検証することが できます。ジオメトリ・ベースと物理ベースの I/O ルール

LVDS に関する I/O 配置のルールについて考慮する必要があります。 Quartus Prime ソフトウェ アは、I/O 配置のルールに違反があるとクリティカル・ワーニングやエラー・メッセージを表示 します。

詳しくは、関連情報を参照してください。 関連情報

MAX 10 General Purpose I/O User Guide

UG-M10LVDS

2016.05.02 ガイドライン:E144 パッケージ向けに LVDS プリエンファシスを有効にする 3-11

MAX 10LVDSトランスミッタのデザイン Altera Corporation

MAX 10 LVDS

レシーバのデザイン

4

2016.05.02 UG-M10LVDS 更新情報 フィードバック MAX 10 LVDS ソリューションを使用して、レシーバ専用アプリケーションを実装することがで きます。 アルテラ・ソフト LVDS IP コアを使用して、ソフト SERDES 回路をインスタンス化し ます。ソフト SERDES 回路はクロックおよび差動 I/O ピンとともに動作し、高速差動レシーバ回 路を作成します。 関連情報 • 1-1 ページの MAX 10 高速 LVDS I/O の概要• 2-7 ページの MAX 10 LVDS SERDES I/O 規格のサポート

サポートされる LVDS I/O 規格およびそれぞれの MAX 10 デバイス・バリアントでのサポート についてリストします。

高速 I/O レシーバ回路

LVDS レシーバ回路は、 MAX 10 デバイスの I/O エレメントとレジスタを使用します。デシリア ライザは、コア・ロジックにソフト SERDES ブロックとして実装されます。 レシーバ・モードでは、差動レシーバのデータパスで以下のブロックが使用可能です。 • デシリアライザ • データ・リアラインメント・ブロック(ビット・スリップ) 関連情報 2-11 ページの MAX 10 高速 LVDS 回路ソフト・デシリアライザ

ソフト・デシリアライザは、デシリアライゼーション・ファクタに基づいて、1 ビットのシリア ル・データ・ストリームをパラレル・データ・ストリームに変換します。© 2016 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Megacore, NIOS, Quartus and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008

登録済

www.altera.com

図 4-1: LVDS x8 デシリアライザの波形 7 6 5 4 3 2 1 0 a b c d e f g h A B C D E F G H X X X X X X X X ABCDEFGH abcdefgh 76543210 XXXXXXXX RX_IN FCLK RX_OUT[9:0] 信号 説明 rx_in アルテラ・ソフト LVDS チャネルに入力される LVDS データ・ストリーム fclk レシーバに使用されるクロック loaden アルテラ・ソフト LVDS IP コアによって生成されるデシリアライゼーション 向けの信号をイネーブルする rx_out[9:0] デシリアライゼーションされた信号

データ・リアラインメント・ブロック(ビット・スリップ)

送信されたデータ内のスキューおよび送信リンクによって追加されたスキューにより、受信した シリアル・データ・ストリームにチャネル間スキューが生じます。 チャネル間スキューを補償 し、各チャネルに正しい受信ワード境界を確立するために、各レシーバ・チャネルにはデータ・ リアライメント回路が含まれています。データ・リアライメント回路は、シリアル・ストリーム にビット・レイテンシを挿入することにより、データを再アライメントします。 データを手動でアラインメントするには、データ・リアライメント回路を使用して、RxFCLKで の 1 サイクルのレイテンシを挿入します。データ・リアライメント回路は、RX_DATA_ALIGNのパ ルスごとにデータを 1 ビット スリップします。データがアラインメントされているかを確認す る前に、コア・クロックで 2 サイクル以上待機する必要があります。破損したデータのパージに 少なくともコア・クロックでの 2 サイクルを必要とするために、この待機時間が必要になりま す。 オプションのRX_CHANNEL_DATA_ALIGNポートは、内部ロジックから独立して各レシーバのビット 挿入を制御します。データは、RX_CHANNEL_DATA_ALIGNの立ち上がりエッジで 1 ビット スリップ します。 RX_CHANNEL_DATA_ALIGN信号には以下の要件があります。 • 最小パルス幅は、ロジック・アレイのパラレル・クロックでの 1 周期である • パルス間の最小 Low 時間は、パラレル・クロックでの 1 周期である • 信号はエッジ・トリガである • 有効なデータは、RX_CHANNEL_DATA_ALIGNの立ち上がりエッジからパラレル・クロックでの 2 サイクルが経過した後に得られる 4-2 データ・リアラインメント・ブロック(ビット・スリップ) UG-M10LVDS2016.05.02図 4-2: データ・リアラインメントのタイミング 以下の図に、デシリアライゼーション・ファクタを4に設定した状態での、1 ビット・スリッ プ・パルスの後のレシーバ出力(RX_OUT)を示します。 rx_inclock rx_in rx_outclock rx_channel_data_align rx_out 3 2 1 0 3 2 1 0 3 2 1 0 3210 321x xx21 0321

LVDS

レシーバ I/O の終端方式

信号品質を向上し、伝送経路およびドライバとのインピーダンス・マッチングを保障するため に、すべての LVDS レシーバ・チャネルに終端処理が求められます。LVDS

、mini-LVDS、RSDS およびレシーバの外部終端

LVDS、mini-LVDS、または RSDS のレシーバ向けには、抵抗を 1 つ用いる外部終端方式が必要で す。 図 4-3: LVDSI/O 規格の外部終端 TX RX Differential Inputs Differential Outputs 50 Ω 50 Ω 100 ΩSLVS

レシーバの外部終端

SLVS レシーバ向けには、抵抗を 1 つ使用する外部終端方式が必要です。 UG-M10LVDS 2016.05.02 LVDSレシーバ I/O の終端方式 4-3MAX 10 LVDSレシーバのデザイン Altera Corporation

図 4-4: SLVS レシーバの外部終端 TX RX SLVS on FPGA 2.5 V SLVS peer Z0 = 50 Ω Z0 = 50 Ω 100 Ω

Sub-LVDS

レシーバの外部終端

Sub-LVDS レシーバ向けには、抵抗を 1 つ使用する外部終端方式が必要です。 図 4-5: Sub-LVDS レシーバの外部終端 TX RX Sub-LVDS on FPGA 2.5 V Sub-LVDS peer Z0 = 50 Ω Z0 = 50 Ω 100 Ω 4-4 Sub-LVDSレシーバの外部終端 UG-M10LVDS2016.05.02TMDS

レシーバの外部終端

図 4-6: TMDS レシーバの外部終端 以下の図は、 MAX 10 デバイスで TMDS 入力規格をサポートするために必要な外部レベル・シ フタを示しています。 TX RX TMDS on FPGA 2.5 V 1.8 V TMDS peer Z0 = 50 Ω Z0 = 50 Ω 50 Ω 50 Ω 0.1 µF 0.1 µFHiSpi

レシーバの外部終端

HiSpi レシーバ向けには、抵抗を 1 つ使用する外部終端方式が必要です。 図 4-7: HiSpi レシーバの外部終端 TX RX HiSpi on FPGA 2.5 V HiSpi peer Z0 = 50 Ω Z0 = 50 Ω 100 ΩLVPECL

レシーバの外部終端

MAX 10 デバイスでは、LVPECL I/O 規格は入力クロック・ピンでのみサポートします。

UG-M10LVDS

2016.05.02 TMDSレシーバの外部終端 4-5

MAX 10 LVDSレシーバのデザイン Altera Corporation

• LVDS 入力バッファは、LVPECL 入力動作をサポートする • LVPECL 出力動作はサポートされない 出力バッファの LVPECL コモン・モード電圧が LVPECL 入力コモン・モード電圧と整合しない場 合、AC 結合を使用します。 注意: アルテラは、LVPECL AC / DC 結合終端を検証するために IBIS モデルを使用することを推 奨します。 図 4-8: LVPECL AC 結合終端

LVPECL Input Buffer LVPECL Output Buffer

0.1 µF 0.1 µF Z0 = 50 Ω Z0 = 50 Ω VICM 50 Ω 50 Ω

DC 結合 LVPECL のサポートは、LVPECL 出力コモン・モード電圧が MAX 10 LVPECL 入力バッフ ァ仕様の範囲内である場合に可能です。

図 4-9: LVPECL DC 結合終端

LVPECL Input Buffer LVPECL Output Buffer

Z0 = 50 Ω Z0 = 50 Ω

100 Ω

4-6 LVPECLレシーバの外部終端 UG-M10LVDS2016.05.02

VICM仕様についての詳細は、Device Datasheet を参照してください。 関連情報

MAX 10 Device Datasheet

LVDS

レシーバ用 FPGA デザインの実装

MAX 10 デバイスでは、高速 I/O インタフェースをサポートするためにソフト SERDES アーキテ クチャを使用しています。 Quartus Prime ソフトウェアが、アルテラ・ソフト LVDS IP コアを使 用してコア・ファブリックに SERDES 回路を作成します。タイミング性能を向上させ、SERDES をサポートするために、 MAX 10 デバイスではコア・ファブリックの I/O レジスタと LE レジス タを使用します。

レシーバ・モードのアルテラ・ソフト LVDS IP コア

Quartus Prime ソフトウェアで、アルテラ・ソフト LVDSIP コアを使用して高速レシーバ・インタ フェースをデザインすることができます。この IP コアは、高速 I/O インタフェースを作成する ために MAX 10 デバイス内のリソースを最も有効に活用します。 • デザイン要件に応じてデシリアライザをカスタマイズするためにアルテラ・ソフト LVDS パ ラメータ・エディタを使用可能 • アルテラ・ソフト LVDS IP コアは、高速デシリアライザをコア・ファブリックに実装する 関連情報 • 7-1 ページの アルテラ・ソフト LVDS のパラメータ設定

• Introduction to Altera IP Cores

すべてのアルテラ IP コアについて、パラメータ化、アップグレード、IP のシミュレーション といった基本的な情報を提供します。

• Creating Version-Independent IP and Qsys Simulation Scripts

ソフトウェアあるいは IP のバージョンのアップグレードのためのマニュアルでの更新を必 要としないシミュレーション・スクリプトの作成について詳しい情報を提供します。 • Project Management Best Practices

プロジェクトおよび IP ファイルの効果的な管理および移植性のためのガイドラインを提供 します。

アルテラ・ソフト LVDS IP コアでの PLL ソースの選択

アルテラ・ソフト LVDS IP コアを、内部 PLL または外部 PLL と併せてインスタンス化すること により、LVDS インタフェース・コンポーネントを作成できます。 内部 PLL を使用するアルテラ・ソフト LVDS IP コアのインスタンス化 アルテラ・ソフト LVDS IP コアを、SERDES コンポーネントを構築し、PLL を内部にインスタン ス化するように設定できます。• この手法を使用するには、PLL Settings タブの Use external PLL オプションをオフにする • アルテラ・ソフト LVDS IP コアは、PLL を LVDS ブロックに統合する

• この手法の欠点は、この PLL をこの LVDS インタフェース向けにしか使用できないこと

UG-M10LVDS

2016.05.02 LVDSレシーバ用 FPGA デザインの実装 4-7

MAX 10 LVDSレシーバのデザイン Altera Corporation

外部 PLL を使用するアルテラ・ソフト LVDS IP コアのインスタンス化

アルテラ・ソフト LVDS IP コアは、SERDES コンポーネントだけを構築し、外部 PLL ソースを使 用するように設定可能です。

• この手法を使用するには、PLL Settings タブの Use external PLL オプションをオンにする • 通知が表示されるパネルにリストされているとおりに入力ポートに必要なクロック設定を行

う

• ALTPLL IP コアを使用して、独自のクロック・ソースを作成できる

• PLL の使用方法をコアの他の機能とあわせて最適化するためにこの手法を使用する 関連情報

• MAX 10 Clocking and PLL User Guide

PLL および PLL 出力カウンタについて詳しい情報を提供します。 • MAX 10 Clocking and PLL User Guide

PLL および PLL 出力カウンタについて詳しい情報を提供します。

ガイドライン:外部 PLL を使用する LVDS RX インタフェース

Use External PLL オプションを用いるアルテラ・ソフト LVDSIP コアをインスタンス化すること

ができます。外部 PLL を使用することにより、PLL 設定を制御できます。たとえば、多様なデー タ・レートと動的な位相シフトをサポートするために、PLL を動的にリコンフィギュレーション できます。このオプションを用いるためには、ALTPLLIP コアをインスタンス化して、さまざま なクロック信号を生成する必要があります。 アルテラ・ソフト LVDS のレシーバ向けに Use External PLL オプションをオンにした場合、 ALTPLLIP コアからの以下の信号が必要になります。 • アルテラ・ソフト LVDS レシーバのrx_inclockポートへのシリアル・クロッ入力 • レシーバの FPGA ファブリック・ロジックのクロッキングに使用したパラレル・クロック • アルテラ・ソフト LVDS PLL リセット・ポート向けlocked信号 関連情報

MAX 10 Clocking and PLL User Guide

PLL および PLL 出力カウンタについて詳しい情報を提供します。 アルテラ・ソフト LVDS レシーバに用いる ALTPLL 信号インタフェース LVDS インタフェース・クロックを生成するために、あらゆる PLL 出力クロック・ポートを選択 できます。 ALTPLL レシーバの外部 PLL ソースとしてアルテラ・ソフト LVDS IP コアを使用する場合は、ソ ース・シンクロナス・コンペンセーション・モードを使用します。 4-8 外部 PLL を使用するアルテラ・ソフト LVDS IP コアのインスタンス化 UG-M10LVDS2016.05.02

表 4-1: デシリアライゼーション・ファクタが偶数の ALTPLL およびアルテラ・ソフト LVDS レシーバ間 の信号インタフェースの例 ALTPLL IPコアより アルテラ・ソフト LVDS レシーバへ 高速クロック出力(c0) シリアル・クロック出力(c0)は、 アルテラ・ソフト LVDS レシーバの rx_inclockのみ駆動できます。 rx_inclock 低速クロック出力(c1) rx_syncclock 表 4-2: デシリアライゼーション・ファクタが奇数の ALTPLL およびアルテラ・ソフト LVDS レシーバ間 の信号インタフェースの例 ALTPLL IPコアより アルテラ・ソフト LVDS レシーバへ 高速クロック出力(c0) シリアル・クロック出力(c0)は、 アルテラ・ソフト LVDS レシーバの rx_inclockのみ駆動できます。 rx_inclock 低速クロック出力(c1) rx_syncclock PLL からの読み出しクロック(c2)出 力 rx_readclock (RAM バッファおよび読み出しカウンタからの読み出し動作 向けクロック入力ポート) アルテラ・ソフト LVDS のレシーバ向けに外部 PLL クロックのパラメータを決定する ALTPLL IP コアのレシーバ向けアルテラ・ソフト LVDS IP コア・クロックのパラメータを決定す るために、デザインで以下の手順を実行します。 1. 内部 PLL を使用するアルテラ・ソフト LVDS IP コアのレシーバをインスタンス化します。 2. デザインを TimeQuest タイミング解析までコンパイルします。

3. Compilation Report ウィンドウの Table of Contents セクションで、TimeQuest Timing Analyzer > Clocks に移動します。 4. アルテラ・ソフト LVDS IP コア・レシーバの内部 PLL に使用されるクロック・パラメータを 書きとめておきます。 クロックのリストで、clk[0]が高速クロック、clk[1]が低速クロック、clk[2]が読み出しク ロックです。 UG-M10LVDS 2016.05.02 アルテラ・ソフト LVDS のレシーバ向けに外部 PLL クロックのパラメータを決定す る 4-9

MAX 10 LVDSレシーバのデザイン Altera Corporation

![図 4-1: LVDS x8 デシリアライザの波形 7 6 5 4 3 2 1 0 a b c d e f g h A B C D E F G H X X X X X X X X ABCDEFGHabcdefgh76543210XXXXXXXXRX_INFCLKRX_OUT[9:0] 信号 説明 rx_in アルテラ・ソフト LVDS チャネルに入力される LVDS データ・ストリーム fclk レシーバに使用されるクロック loaden アルテラ・ソフト LVDS IP コアによって生成されるデシリアライ](https://thumb-ap.123doks.com/thumbv2/123deta/6442088.647124/35.918.72.846.99.491/デシリアライザアルテラソフトデータストリームアルテラソフト.webp)