Spartan-6 FPGA

ブ ロ ッ ク

RAM

リ ソ ース

ユーザー

ガ イ ド

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2009-2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

改訂履歴

本書の改訂履歴は以下の と お り です。 本資料は英語版 (v1.2) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。 日本語版は参考用 と し て ご使用の上、 最新情報につ き ま し ては、 必ず最新英語版を ご参照 く だ さ い。 日付 バージ ョ ン 変更内容 2009 年 6 月 24 日 1.0 初期 リ リ ース 2009 年 10 月 29 日 1.1 「非同期 ク ロ ッ ク 」 に項目を追加。「未使用の入力」 の接続を Low に修正。 2010 年 2 月 23 日 1.2 「 コ ン フ ィ ギ ュ レーシ ョ ンの種類」 を変更 ( 「18Kb ブ ロ ッ ク RAM - シ ンプルデュ ア ルポー ト 」 セ ク シ ョ ンの削除を含む)。 ガ イ ド 全体で こ の情報を削除。表2

~表3

にポー ト 名を追加。「非同期 ク ロ ッ ク 」 の説明を ア ッ プデー ト 。「デー タ お よ びア ド レ ス幅 - DATA_WIDTH_A、DATA_WIDTH_B」 を変更。図 14を ア ッ プデー ト 。改訂履歴. . . 2

こ のマニ ュ アルについて

その他の資料. . . 5 その他の リ ソ ース . . . 6ブ ロ ッ ク

RAM

リ ソ ース

概要 . . . 7 コ ン フ ィ ギ ュ レーシ ョ ンの種類. . . .7 9Kb ブ ロ ッ ク RAM - シ ンプルデ ュ アルポー ト . . . .8 9Kb ブ ロ ッ ク RAM - 完全デュ アルポー ト . . . .8 18Kb ブ ロ ッ ク RAM - 完全デ ュ アルポー ト . . . .9Spartan-6 FPGA のブ ロ ッ ク RAM の機能 . . . .11

Spartan-6 FPGA のブ ロ ッ ク RAM の使用規則. . . .11

同期デュ アルポー ト お よ びシ ンプルデ ュ アルポー ト RAM . . . 12 デー タ フ ロー. . . .12 読み出 し 動作 . . . .13 書 き 込み動作 . . . .13 書 き 込みモー ド . . . .13 WRITE_FIRST (透過) モー ド (デフ ォ ル ト) . . . .14 READ_FIRST (書 き 込み前に読み出 し) モー ド . . . .14 NO_CHANGE (変化な し) モー ド. . . .15 競合の回避 . . . .15 非同期 ク ロ ッ ク . . . .15 同期 ク ロ ッ ク . . . .16 出力レ ジ ス タ (オプシ ョ ン) . . . .16 シ ンプルデ ュ アルポー ト ブ ロ ッ ク RAM . . . .16 バ イ ト 幅書 き 込み イ ネーブル. . . .18 ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ. . . 18 ブ ロ ッ ク RAM のポー ト 信号 . . . 20 ク ロ ッ ク - CLKA、CLKB (CLKAWRCLK、CLKBRDCLK) . . . .20

イ ネーブル - ENA、ENB (ENAWREN、ENBRDEN) . . . .20

バ イ ト 幅書 き 込み イ ネーブル - WEA、WEB (WEAWEL、WEBWEU) . . . .20

レ ジ ス タ イ ネーブル - REGCEA、REGCEB (REGCEA、REGCEBREGCE) . . . .21

セ ッ ト/リ セ ッ ト - RSTA、RSTB (RSTA、RSTBRST) . . . .21

ア ド レ スバ ス - ADDRA、ADDRB (ADDRAWRADDR、ADDRBRDADDR) . . . .21

デー タ 入力バ ス - DIA、DIB (DIADI、DIBDI) . . . .22

デー タ 入力パ リ テ ィ - DIPA、DIPB (DIPADIP、DIPBDIP) . . . .22

デー タ 出力バ ス - DOA、DOB (DOADO、DOBDO) . . . .22

デー タ 出力パ リ テ ィ - DOPA、DOPB (DOPADOP、DOPBDOP) . . . .22

GSR . . . .22

未使用の入力 . . . .22

ブ ロ ッ ク RAM のア ド レ ス マ ッ プ. . . 23

目次

デー タ ラ ッ チ リ セ ッ ト - EN_RSTRAM_A、EN_RSTRAM_B . . . .25

リ セ ッ ト タ イ プ - RSTTYPE . . . .25

オプシ ョ ンの出力レ ジ ス タ 切 り 替え - DO[A|B]_REG . . . .25

書 き 込みモー ド - WRITE MODE_A、WRITE_MODE_B . . . .25

ブ ロ ッ ク RAM の ロ ケーシ ョ ン制約 . . . .26 ブ ロ ッ ク RAM の初期化. . . 26 ブ ロ ッ ク RAM プ リ ミ テ ィ ブの設計上の追加注意事項 . . . 26 出力レ ジ ス タ (オプシ ョ ン) . . . .26 RAMB16BWER お よ び RAMB8BWER ポー ト のマ ッ プ規則. . . .26 リ セ ッ ト の動作 . . . .27 バ イ ト 幅書 き 込み イ ネーブル. . . .27 ブ ロ ッ ク RAM のアプ リ ケーシ ョ ン. . . 27 大型 RAM 構造の作成. . . .27 レ ジ ス タ モー ド のブ ロ ッ ク RAM の RST . . . .28 ブ ロ ッ ク RAM の タ イ ミ ン グモデル . . . 30 ブ ロ ッ ク RAM の タ イ ミ ン グパ ラ メ ー タ. . . .30 ブ ロ ッ ク RAM の タ イ ミ ン グ特性. . . .31 ク ロ ッ ク イ ベン ト 1 . . . .31 ク ロ ッ ク イ ベン ト 2 . . . .32 ク ロ ッ ク イ ベン ト 4 . . . .32 ク ロ ッ ク イ ベン ト 5 . . . .32 ブ ロ ッ ク RAM の タ イ ミ ン グモデル. . . .33

こ のマニ ュ アルについて

こ のマニ ュ アルでは、 すべての Spartan®-6 FPGA で使用可能なブ ロ ッ ク RAM について説明 し ま す。ブ ロ ッ ク RAM は、 効率的なデー タ 格納ま たはバ ッ フ ァ 、 パフ ォーマン ス の優れた ス テー ト マ シ ン ま たは FIFO バ ッ フ ァ 、 大型シ フ ト レ ジ ス タ 、 大型ル ッ ク ア ッ プテーブル、ROM な ど に使用 さ れます。

その他の資料

Spartan-6 に関す る その他の情報は、http://japan.xilinx.com/support/documentation/spartan-6.htm か ら 次を参照 し て く だ さ い。 • 『Spartan-6 フ ァ ミ リ 概要』 Spartan-6 フ ァ ミ リ の機能 と デバ イ ス の概要を示 し ます。 • 『Spartan-6 FPGA デー タ シー ト : DC 特性お よ びス イ ッ チ特性』 Spartan-6 フ ァ ミ リ の DC 特性お よ びス イ ッ チ特性が記載 さ れてい ます。 • 『Spartan-6 FPGA パ ッ ケージお よ びピ ン配列の仕様』 デバ イ ス/ピ ンの組み合わせ と 最大 I/O 数、 ピ ン定義、 ピ ン配置図、 機械的図面、 熱仕様が記載 さ れてい ます。 • 『Spartan-6 FPGA コ ン フ ィ ギ ュ レーシ ョ ンユーザーガ イ ド 』 コ ン フ ィ ギ ュ レーシ ョ ン イ ン タ ーフ ェ イ ス (シ リ アルお よ びパ ラ レル)、複数の ビ ッ ト ス ト リ ー ムの管理、 ビ ッ ト ス ト リ ームの暗号化、 バ ウ ン ダ リ ス キ ャ ンお よ び JTAG コ ン フ ィ ギ ュ レー シ ョ ン、 リ コ ン フ ィ ギ ュ レーシ ョ ン手法な ど、 コ ン フ ィ ギ ュ レーシ ョ ンについて詳細に説明 し ます。• 『Spartan-6 FPGA SelectIO リ ソ ースユーザーガ イ ド 』

すべての Spartan-6 デバ イ ス に含まれてい る SelectIO™ について説明 し ます。 • 『Spartan-6 FPGA ク ロ ッ ク リ ソ ース ユーザーガ イ ド 』

DCM お よ び PLL を含め、Spartan-6 デバ イ ス の ク ロ ッ ク リ ソ ース について説明 し ます。 • 『Spartan-6 FPGA コ ン フ ィ ギ ャ ブル ロ ジ ッ ク ブ ロ ッ クユーザーガ イ ド 』

こ のマニ ュ アルについて

• 『Spartan-6 FPGA DSP48A1 Slice User Guide』

Spartan-6 FPGA の DSP48A1 ス ラ イ ス のアーキ テ ク チ ャ について説明 し 、 コ ン フ ィ ギ ュ レー シ ョ ン例を示 し ます。

• 『Spartan-6 FPGA Memory Controller User Guide』

Spartan-6 FPGA の メ モ リ コ ン ト ロ ー ラブ ロ ッ ク について説明 し ます。メ モ リ コ ン ト ロ ー ラブ ロ ッ ク は、Spartan-6 FPGA を よ く 使用 さ れ る メ モ リ 規格に接続す る 際の イ ン タ ーフ ェ イ ス を 簡略化す る エンベデ ッ ド マルチポー ト メ モ リ コ ン ト ロ ー ラ です。

• 『Spartan-6 FPGA PCB Design Guide』

PCB お よ び イ ン タ ーフ ェ イ ス レベルでデザ イ ン を決定す る ための ス ト ラ テジに焦点を置い て、Spartan-6 デバ イ ス の PCB デザ イ ンに関す る 情報を示 し ます。

その他の リ ソ ース

シ リ コ ン、 ソ フ ト ウ ェ ア、IP に関する ア ンサーデー タ ベース を検索 し た り 、 テ ク ニ カルサポー ト の ウ ェ ブケース を開 く 場合は、 次の Web サ イ ト にア ク セ ス し て く だ さ い。 http://japan.xilinx.com/supportブ ロ ッ ク

RAM

リ ソ ース

概要

Spartan®-6 FPGA のブ ロ ッ ク RAM は、最大 18K ビ ッ ト のデー タ を格納で き 、2 つの独立 し た 9Kb RAM ま たは 1 つの 18Kb RAM と し て コ ン フ ィ ギ ュ レーシ ョ ンで き ます。各 RAM は 2 つのポー ト を使用 し てア ク セ ス で き ますが、 シ ン グル ポー ト RAM と し て も コ ン フ ィ ギ ュ レーシ ョ ンで き ま す。ブ ロ ッ ク RAM リ ソ ース には、 パ イ プ ラ イ ンパフ ォーマン ス を向上す る ため出力レ ジ ス タ が含 まれています。ブ ロ ッ ク RAM は列に配置 さ れます。ブ ロ ッ ク RAM の合計数は、Spartan-6 デバ イ ス のサ イ ズに よ っ て異な り ます。 その他のザ イ リ ン ク ス FPGA のブ ロ ッ ク RAM と 同様に、 書 き 込み と 読み出 し は同期動作で、2 つ のポー ト は対称でそれぞれ完全に独立 し てお り 、格納 さ れたデー タ のみを共有 し ます。各ポー ト は、 設定可能な幅のいずれかに個別に指定で き ます。 メ モ リ の内容は、 コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ームで初期化ま たは ク リ アで き ます。書 き 込み処理中、デー タ 出力を その ま ま保持す る か、書 き 込まれてい る 新規デー タ を出力す る か、 上書 き さ れ よ う と し てい る 以前のデー タ を出力す る か を 指定で き ます。 デ ュ アルポー ト ま たはシ ン グルポー ト のエンベデ ッ ド RAM モジ ュ ール、ROM モジ ュ ール、 同期

FIFO、デー タ 幅 コ ンバー タ は、CORE Generator のブ ロ ッ ク メ モ リ モジ ュ ールを使用す る と 簡単に イ ンプ リ メ ン ト で き ます。デ ュ アル ク ロ ッ ク FIFO は、CORE Generator の FIFO Generator モ ジ ュ ールを使用 し て作成で き ます。

コ ン フ ィ ギ ュ レーシ ョ ンの種類

完全デ ュ アルポー ト モー ド の場合、両方のポー ト を個別に書 き 込みま たは読み出 し ポー ト に設定で き ます。9Kb RAM では、シ ンプルデュ アルポー ト モー ド の場合を除 き 、デー タ の最大幅は 18 ビ ッ ト です。 シ ンプルデ ュ アルポー ト モー ド の場合、 ポー ト A は書 き 込みのみ、 ポー ト B は読み出 し のみに し か設定で き ませんが、 デー タ 幅は 36 ビ ッ ト に拡張 さ れます。 完全デ ュ アルポー ト モー ド では、 両方のブ ロ ッ ク RAM サ イ ズで、2 つのポー ト の幅を個別に設定 で き ます。シ ンプルデ ュ アルポー ト モー ド では、表 1~表 3に示す よ う に、9Kb RAM で x36 デー タ 幅の コ ン フ ィ ギ ュ レーシ ョ ンが可能です。概要

9Kb

ブ ロ ッ ク

RAM -

シ ン プル

デ ュ アル

ポー ト

9Kb ブ ロ ッ ク RAM に コ ン フ ィ ギ ュ レーシ ョ ン可能なシ ンプルデ ュ アルポー ト モー ド のポー ト 幅 の組み合わせは、表 1の と お り です。9Kb

ブ ロ ッ ク

RAM -

完全デ ュ アル

ポー ト

9Kb ブ ロ ッ ク RAM に コ ン フ ィ ギ ュ レーシ ョ ン可能な完全デ ュ アルポー ト モー ド のポー ト 幅の組 み合わせは、表 2の と お り です。 表 1 :9Kb

ブ ロ ッ クRAM

に コ ン フ ィ ギ ュ レーシ ョ ン可能なシ ン プルデ ュ アルポー ト モー ド ポー ト A パ リ テ ィ ビ ッ ト な し パ リ テ ィ ビ ッ ト あ り 8K x 1 4K x 2 2K x 4 1K x 8 512 x 16 256 x 32 1K x 9 512 x 18 256 x 36 ポー ト B パ リ テ ィ ビ ッ ト な し 8K x 1 完全デ ュ アルポー ト モー ド を使用 不可 不可 4K x 2 2K x 4 1K x 8 512 x 16 256 x 32 不可 可能 パ リ テ ィ ビ ッ ト あ り 1K x 9 不可 完全デ ュ アル ポー ト モー ド を 使用 不可 512 x 18 256 x 36 不可 可能 表 2 : 9Kb ブ ロ ッ ク RAM に コ ン フ ィ ギ ュ レーシ ョ ン可能な完全デ ュ アルポー ト モー ド ポー ト A パ リ テ ィ ビ ッ ト な し パ リ テ ィ ビ ッ ト あ り 8K x 1 4K x 2 2K x 4 1K x 8 512 x 16 1K x 9 512 x 18 ポー ト B 8K x 1 すべて可能 すべて不可 4K x 2 2K x 4 1K x 8 512 x 16 1K x 9 すべて不可 すべて可能 512 x 18概要

18Kb

ブ ロ ッ ク

RAM -

完全デ ュ アル

ポー ト

18Kb ブ ロ ッ ク RAM に コ ン フ ィ ギ ュ レーシ ョ ン可能な完全デ ュ アル ポー ト モー ド のポー ト 幅の 組み合わせは、表 3の と お り です。 表 3 : 18Kb ブ ロ ッ ク RAM に コ ン フ ィ ギ ュ レーシ ョ ン可能な完全デ ュ アルポー ト モー ド ポー ト A パ リ テ ィ ビ ッ ト な し パ リ テ ィ ビ ッ ト あ り 16K x 1 8K x 2 4K x 4 2K x 8 1K x 16 512 x 32 2K x 9 1K x 18 512 x 36 ポー ト B 16K x 1 すべて可能 すべて不可 8K x 2 4K x 4 2K x 8 1K x 16 512 x 32 2K x 9 すべて不可 すべて可能 1K x 18 512 x 36概要 表 4は、 その他のブ ロ ッ ク RAM の組み合わせ と ADDR ポー ト 幅を示 し てい ます。 表 4 : ブ ロ ッ ク RAM デー タ の組み合わせ と ADDR の位置 組み合わせ ワー ド 数 デー タ 幅 パ リ テ ィ 幅 デー タ 入力 および出力 ADDR RAM 合計 (Kb) パ リ テ ィ あ り と パ リ テ ィ な し の場合の 9Kb ブ ロ ッ ク RAM 256 x 32(1) 256 32 な し [31:0] [12:5] 8 256 x 36(1) 256 32 4 [35:0] [12:5] 9 512 x16 512 16 な し [15:0] [12:4] 8 512 x18 512 16 2 [17:0] [12:4] 9 1K x 8 1024 8 な し [7:0] [12:3] 8 1K x 9 1024 8 1 [8:0] [12:3] 9 2K x 4 2048 4 な し [3:0] [12:2] 8 4K x 2 4096 2 な し [1:0] [12:1] 8 8K x 1 8192 1 な し [0:0] [12:0] 8 パ リ テ ィ あ り と パ リ テ ィ な し の場合の 18Kb ブ ロ ッ ク RAM 512 x 32 512 32 な し [31:0] [13:5] 16 512 x 36 512 32 4 [35:0] [13:5] 18 1K x16 1024 16 な し [15:0] [13:4] 16 1K x18 1024 16 2 [17:0] [13:4] 18 2K x 8 2045 8 な し [7:0] [13:3] 16 2K x 9 2048 8 1 [8:0] [13:3] 18 4K x 4 4096 4 な し [3:0] [13:2] 16 8K x 2 8192 2 な し [1:0] [13:1] 16 16K x 1 16384 1 な し [0:0] [13:0] 16 メ モ : 1. x32 お よ び x36 のデー タ 幅はシ ン プルデ ュ アルポー ト (SDP) モー ド でのみ使用可能

概要

Spartan-6 FPGA

のブ ロ ッ ク

RAM

の機能

• ブ ロ ッ ク ご と の メ モ リ 格納機能に よ り 、 各ブ ロ ッ ク RAM に最大で 18Kb のデー タ を格納で き ます。 • 2 つの独立 し た 9Kb ま たは 1 つの 18Kb ブ ロ ッ ク RAM がサポー ト さ れます。 • 各 9Kb ブ ロ ッ ク RAM を シ ンプルデ ュ アルポー ト モー ド に し 、ブ ロ ッ ク RAM のデー タ 幅を 最大 36 ビ ッ ト に ま で設定で き ます。 シ ンプルデ ュ アルポー ト モー ド では、読み出 し 専用ポー ト と 書 き 込み専用ポー ト が 1 つずつあ り 、 それぞれが独立 し た ク ロ ッ ク で動作 し ます。 • 同期セ ッ ト ピ ン と 同期 リ セ ッ ト ピ ン を分離す る こ と に よ り 、 オプシ ョ ン の出力 レ ジ ス タ の セ ッ ト/リ セ ッ ト と ブ ロ ッ ク RAM の出力 ラ ッ チ段階を個別に制御で き ま す。 こ れに よ り 、

Spartan-6FPGA ブ ロ ッ ク RAM がその他の FPGA フ ァ ミ リ と さ ら に一致す る よ う にな り 、

FPGA ロ ジ ッ ク レ ジ ス タ を ブ ロ ッ ク RAM ブ ロ ッ ク にマ ッ プ し やす く な り ま す。 • 18 ま たは 36 ビ ッ ト 幅のポー ト には、 バ イ ト ご と に個別の書 き 込み イ ネーブルを含め る こ と が で き ます。 こ れは、 オンチ ッ プのマ イ ク ロ プ ロ セ ッ サ と イ ン タ ーフ ェ イ スす る 際に頻繁に使用 さ れ る 機能です。 • すべての入力はポー ト ク ロ ッ ク に同期 し て取 り 込まれ、setup-to-clock タ イ ミ ン グ仕様に従い ます。 • すべての出力の機能は、書き込みイ ネーブル (WE) ピ ンの状態に よ っ て、「読み出 し 」 ま たは 「書 き 込み中読み出 し 」 にな り ます。こ れ ら の出力は、clock-to-out タ イ ミ ン グの後に有効にな り ま す。書 き 込み中読み出 し の出力には、WRITE_FIRST、READ_FIRST、NO_CHANGE と い う

3 つの動作モー ド があ り ます。 • 書き込みには、 ク ロ ッ ク エ ッ ジが 1 つ必要です。 • 読み出し には、 ク ロ ッ ク エ ッ ジが 1 つ必要です。 • すべての出力ポー ト には ラ ッ チが付いています。出力ポー ト の値は、 そのポー ト で別の読み込 みま たは書 き 込みが行われない限 り 変化 し ません。 デフ ォル ト では、 ブ ロ ッ ク RAM 出力は ラ ッ チモー ド です。 • 出力データ パ ス にはオプシ ョ ンの内部パ イ プ ラ イ ン レ ジ ス タ があ り ます。レ ジ ス タ モー ド の 使用を強 く 推奨 し ます。こ れに よ り 、高 ク ロ ッ ク レー ト での動作が可能にな り ますが、1 ク ロ ッ クサ イ ク ルの レ イ テ ン シが追加 さ れます。

Spartan-6 FPGA

のブ ロ ッ ク

RAM

の使用規則

• ブ ロ ッ ク RAM の同期出力レ ジ ス タ (オプシ ョ ン) は、DO_REG = 1 の と き に RST を使用 し て セ ッ ト ま たは リ セ ッ ト (SRVAL) さ れます。同期出力 ラ ッ チは EN_RSTRAM = TRUE の と き に RST を使用 し てセ ッ ト ま たは リ セ ッ ト (SRVAL) さ れます。こ の場合、 ブ ロ ッ ク RAM は イ ネーブル (EN = 1) にな っ てい る 必要があ り ます。

• ブ ロ ッ ク RAM のア ド レ ス ピ ンお よ び書 き 込み イ ネーブルピ ンのセ ッ ト ア ッ プ タ イ ムに違反 し ない よ う に し ます。ア ド レ ス セ ッ ト ア ッ プ タ イ ムに違反す る と 、 書 き 込みネーブルが Low

同期デ ュ アルポー ト およびシ ン プルデ ュ アルポー ト RAM

同期デ ュ アル

ポー ト お よびシ ン プル

デ ュ アル

ポー ト

RAM

デー タ

フ ロー

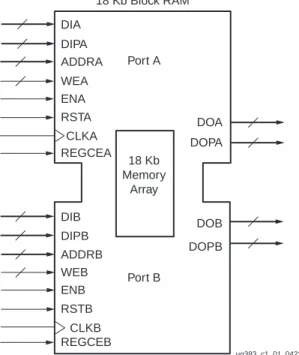

完全デ ュ アルポー ト の 18Kb ブ ロ ッ ク RAM デュ アルポー ト メ モ リ は、18Kb の記憶領域 と 、完全 に独立 し た 2 つのア ク セ ス ポー ト (A お よ び B) で構成 さ れてい ます。同様に、 各 9Kb ブ ロ ッ ク RAM デ ュ アルポー ト メ モ リ は、9Kb の記憶領域 と 、完全に独立 し た 2 つのア ク セ ス ポー ト (A お よ び B) で構成 さ れてい ます。構造は完全に対称で、両ポー ト は交換可能です。図 1にデ ュ アルポー ト のデー タ フ ローを示 し 、表 5にポー ト 名 と その説明を示 し ます。 デー タ の書 き 込み/読み出 し は、 ど ち ら か 1 つのポー ト ま たは両方のポー ト で実行で き ます。書 き 込 みは同期動作であ り 、 各ポー ト にそれぞれア ド レ ス、 デー タ 入力、 デー タ 出力、 ク ロ ッ ク 、 ク ロ ッ ク イ ネーブル、書 き 込み イ ネーブルがあ り ます。読み出 し お よ び書 き 込みは同期動作であ り 、ク ロ ッ ク エ ッ ジが 1 つ必要です。 両方のポー ト で同 じ ア ド レ ス にア ク セ ス し た場合に、それを調整す る 専用モニ タ はあ り ません。 2 つ の ク ロ ッ ク の タ イ ミ ン グは、 ユーザーの責任で調整 し て く だ さ い。同 じ ア ド レ ス に同時に書 き 込み を実行 し た場合、 物理的な破損はあ り ませんが、 書 き 込まれたデー タ は不確定にな り ます。X-Ref Target - Figure 1

図

1 :

完全デ ュ アルポー ト デー タ フ ロー ADDRA WEA ENA CLKA RSTA REGCEA REGCEB ADDRB WEB ENB RSTB CLKB 18 Kb Block RAM ug383_c1_01_042209 DOB DOA DIA DIB 18 Kb Memory Array Port A Port B DIPA DOPA DOPB DIPB同期デ ュ アルポー ト およびシ ン プルデ ュ アルポー ト RAM

読み出 し 動作

ラ ッ チモー ド の読み出 し には、1 つの ク ロ ッ ク エ ッ ジが使用 さ れます。読み出 し ア ド レ ス が読み出 し ポー ト に取 り 込まれてか ら 、RAM ア ク セ ス時間の後に、格納 さ れたデー タ が出力 ラ ッ チに読み込 まれます。出力レ ジ ス タ を使用 し てい る 場合、 出力で レ イ テ ン シが 1 サ イ ク ル追加 さ れます。書き込み動作

書 き 込み動作は、1 つの ク ロ ッ ク エ ッ ジで行われます。書 き 込みア ド レ ス が書 き 込みポー ト に取 り 込まれ、 入力デー タ が メ モ リ に格納 さ れます。書き込みモー ド

書 き 込み ク ロ ッ ク エ ッ ジ後に出力 ラ ッ チに現れ る デー タ は、 書き 込みモー ド を 3 つの値(WRITE_FIRST、READ_FIRST、NO_CHANGE) のいずれかに設定する こ と で制御 し ます。各ポー ト で書 き 込みモー ド を個別に設定で き ます。デフ ォル ト では、WRITE_FIRST に設定 さ れてい ます。 WRITE_FIRST では、出力バ ス に新たに書 き 込まれたデー タ が出力 さ れます。READ_FIRST では、 新 し く デー タ が書 き 込まれ る 前に、格納 さ れていたデー タ が出力 さ れます。 NO_CHANGE では、前 回の読み出 し での出力がその ま ま保持 さ れます。 表 5 : 完全デ ュ アルポー ト の名前 と 説明 ポー ト 名 説明 DI[A|B](1) デー タ 入力バ ス DIP[A|B](1) デー タ 入力パ リ テ ィ バ ス ADDR[A|B] ア ド レ スバ ス WE[A|B] バ イ ト 幅書き 込み イ ネーブル EN[A|B] 非ア ク テ ィ ブの場合、ブ ロ ッ ク RAM にデー タ は書 き 込まれず、 出力バ ス が以前の状態に保持 さ れます。 RST[A|B] 出力レ ジ ス タ を同期セ ッ ト/リ セ ッ ト (DO_REG = 1) CLK[A|B] ク ロ ッ ク 入力 DO[A|B](1) デー タ 出力バ ス DOP[A|B](1) デー タ 出力パ リ テ ィ バ ス REGCE[A|B] 出力レ ジ ス タ ク ロ ッ ク イ ネーブル メ モ :

同期デ ュ アルポー ト およびシ ン プルデ ュ アルポー ト RAM

WRITE_FIRST (

透過

)

モー ド

(

デ フ ォ ル ト

)

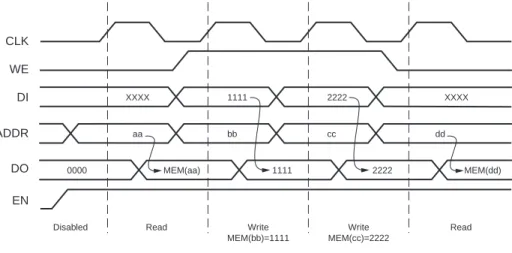

WRITE_FIRST モー ド では、図 2に示す よ う に、 入力デー タ が メ モ リ に書 き 込まれ る と 同時にデー タ 出力に送信 さ れます (透過書 き 込み)。こ こ に示す波形は、 オプシ ョ ンの出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ていない ラ ッ チモー ド の場合の も のです。READ_FIRST (

書き込み前に読み出 し

)

モー ド

READ_FIRST モー ド では、 以前に書 き 込みア ド レ ス に格納 さ れていたデー タ が出力 ラ ッ チに送信 さ れ、 それ と 同時に入力デー タ が メ モ リ に格納 さ れます (書 き 込み前に読み出 し)。図 3に示す波形 は、 オプシ ョ ンの出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ていない ラ ッ チモー ド の場合の も のです。X-Ref Target - Figure 2

図

2 : WRITE_FIRST

モー ド の タ イ ミ ン グ CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 XXXX aa bb cc dd 0000 MEM(aa) 1111 2222 MEM(dd) Read Write MEM(bb)=1111 Write MEM(cc)=2222 ug383_c1_02_042209X-Ref Target - Figure 3

図

3 : READ_FIRST

モー ド の タ イ ミ ン グ CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 XXXX aa bb cc dd0000 MEM(aa) old MEM(bb) old MEM(cc) MEM(dd)

Read Write MEM(bb)=1111 Write MEM(cc)=2222 ug383_c1_03_042209

同期デ ュ アルポー ト およびシ ン プルデ ュ アルポー ト RAM

NO_CHANGE (

変化な し

)

モー ド

NO_CHANGE モー ド では、 書き 込み中出力 ラ ッ チは変化 し ません。図 4に示す よ う に、 データ出力 には最後に読み込まれたデータ がその ま ま保持 さ れ、同 じ ポー ト での書き込みに影響 さ れません。こ こ に示す波形は、オプシ ョ ンの出力パ イ プ ラ イ ンレ ジ ス タ を使用 し ていない ラ ッ チモー ド の場合の も のです。競合の回避

Spartan-6 FPGA のブ ロ ッ ク RAM メ モ リ は、両方のポー ト が任意の メ モ リ 位置に随時ア ク セ ス で き る 完全デ ュ アルポー ト RAM です。ただ し 、2 つのポー ト か ら 1 つの メ モ リ 位置へア ク セ スす る 際 には、 制限があ り ます。こ の よ う なア ク セ ス には、 両ポー ト で共通の ク ロ ッ ク を使用 し てい る 場合 (同期 ク ロ ッ ク) と 、 両ポー ト の ク ロ ッ ク 周波数 と 位相が異な る 場合 (非同期 ク ロ ッ ク) があ り ます。

非同期 ク ロ ッ ク

非同期 ク ロ ッ ク は、 よ り 一般的な状況で、 両 ク ロ ッ ク のア ク テ ィ ブエ ッ ジは同時に発生 し ません。 • 両ポー ト で読み出し を実行する場合、 タ イ ミ ングの制限はあ り ません。 • 1 つのポー ト で書き 込みを実行 し てい る と き に、 も う 1 つのポー ト で同 じ メ モ リ 位置への読み 出 し ま たは書 き 込みは実行で き ません。こ れに反す る と 、 シ ミ ュ レーシ ョ ンモデルでエ ラ ーが 発生 し ます。 こ の制限を無視す る と 、 読み出 し ま たは書 き 込み動作の結果が予測 さ れない も の にな り ます。ただ し 、デバ イ ス が物理的に破損する こ と はあ り ません。読み出 し と 書 き 込みが実 行 さ れ る と 、 書 き 込み位置に有効なデー タ が格納 さ れます。 • READ_FIRST モー ド では、 デュ アルポー ト ブ ロ ッ ク RAM を使用す る 場合にポー ト A と B のア ド レ ス が競合 し ない よ う にす る 必要があ り ます。こ の制限は、TDP お よ び SDP モー ド の両 方に適用 さ れます。1 つのポー ト での読み出 し/書 き 込み と 、 も う 1 つのポー ト での同 じ ア ド レ スへの書 き 込みを同時に実行す る こ と はで き ません。 ブ ロ ッ ク RAM の動作におけ る こ の制限 を無視す る こ と はで き ません。X-Ref Target - Figure 4

図

4 : NO_CHANGE

モー ド の タ イ ミ ン グ CLK WE DI ADDR DO EN Disable Read XXXX 1111 2222 XXXX aa bb cc dd 0000 MEM(aa) MEM(dd) Read Write MEM(bb)=1111 Write MEM(cc)=2222 ug383_c1_04_042209同期デ ュ アルポー ト およびシ ン プルデ ュ アルポー ト RAM

同期 ク ロ ッ ク

同期 ク ロ ッ ク は、両ポー ト の ク ロ ッ ク のア ク テ ィ ブエ ッ ジが同時に発生する と い う 特殊な状況です。 • 両ポー ト で読み出し を実行する場合、 タ イ ミ ングの制限はあ り ません。 • 1 つのポー ト で書き 込みを実行 し てい る と き 、 も う 1 つのポー ト を使用 し て同 じ メ モ リ 位置に 書 き 込みを実行す る こ と で き ません。 ただ し 、 両ポー ト で書 き 込むデー タ が同一の場合は例外 です。 • 1 つのポー ト で書 き 込みを実行 し てい る と き 、 書 き 込みポー ト が READ_FIRST モー ド にな っ ていれば、 も う 1 つのポー ト で同 じ メ モ リ 位置か ら 正 し く デー タ を読み出す こ と がで き ます。 その場合、 両ポー ト の DATA_OUT は以前に格納 さ れていたデー タ にな り ます。 書 き 込みポー ト が WRITE_FIRST ま たは NO_CHANGE モー ド にな っ てい る と き は、 読み出 し ポー ト の DATA_OUT が無効 (不確定) にな り ます。読み出 し ポー ト のモー ド 設定は、 こ の動 作には影響を与え ません。出力レ ジ ス タ

(

オプ シ ョ ン

)

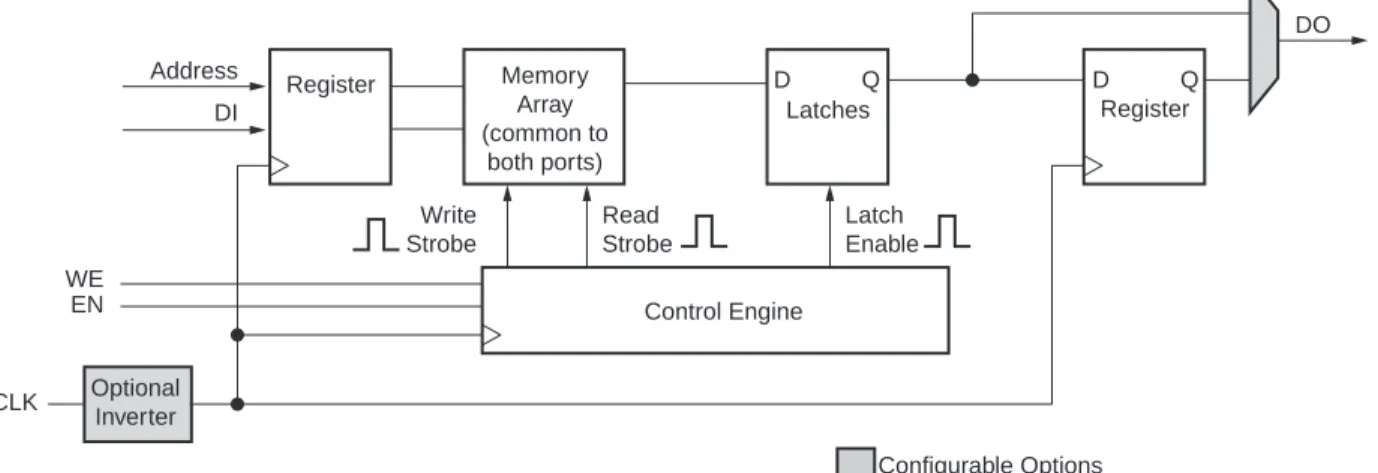

オプシ ョ ンの出力レ ジ ス タ は、 パ イ プ ラ イ ン処理用に CLB フ リ ッ プ フ ロ ッ プへの配線遅延を削除 す る こ と で、 デザ イ ンのパフ ォーマン ス を向上 し ます。 こ れ ら の出力レ ジ ス タ には独立 し た ク ロ ッ ク イ ネーブル入力が供給 さ れ る ため、入力レ ジ ス タ と は別の値が保持 さ れます。図 5にオプシ ョ ン の出力レ ジ ス タ を示 し ます。シ ン プル

デ ュ アル

ポー ト

ブ ロ ッ ク

RAM

各 9Kb ブ ロ ッ ク は、 シ ンプルデ ュ アルポー ト (SDP) RAM モー ド に も コ ン フ ィ ギ ュ レーシ ョ ンで き ます。こ のモー ド では、9Kb ブ ロ ッ ク RAM のポー ト 幅が 2 倍の 36 ビ ッ ト と な り ます。シ ンプル デ ュ アルポー ト モー ド では、 ポー ト A を主な書 き 込みポー ト 、 ポー ト B を主な読み出 し ポー ト とX-Ref Target - Figure 5

図

5 :

ブ ロ ッ クRAM

の論理図(

ポー ト は1

つ)

Register Optional Inverter Latches Register Address DI WE EN CLK Write Strobe Read Strobe Q D D Q DO Control Engine Configurable Options ug383_c1_05_042209 Memory Array (common to both ports) Latch Enable同期デ ュ アルポー ト およびシ ン プルデ ュ アルポー ト RAM

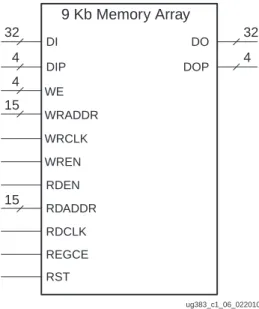

X-Ref Target - Figure 6

図

6 :

シ ン プルデ ュ アルポー ト モー ド でのデー タ フ ロー 表 6 : シ ン プルデ ュ アルポー ト RAM のポー ト 名および説明 ポー ト 名 説明 DO デー タ 出力バ ス DOP デー タ 出力パ リ テ ィ バ ス DI デー タ 入力バ ス DIP デー タ 入力パ リ テ ィ バ ス RDADDR 読み出 し デー タ ア ド レ スバ ス RDCLK 読み出 し デー タ ク ロ ッ ク RDEN 読み出 し ポー ト イ ネーブル REGCE 出力レ ジ ス タ ク ロ ッ ク イ ネーブル RST デー タ 出力レ ジ ス タ/ラ ッ チの同期セ ッ ト/リ セ ッ ト WE バ イ ト 幅書き 込み イ ネーブル WRADDR 書き 込みデー タ ア ド レ スバ ス WRCLK 書き 込みデー タ ク ロ ッ ク WREN 書き 込みポー ト イ ネーブル9 Kb Memory Array

RDEN RDADDR RDCLK REGCE WRADDR WE WRCLK WREN DO DI ug383_c1_06_022010 32 4 15 15 32 DOP DIP 4 4 RSTブ ロ ッ ク RAM のラ イ ブ ラ リ プ リ ミ テ ィ ブ

バイ ト 幅書き込みイ ネーブル

ブ ロ ッ ク RAM にはバ イ ト 幅の書 き 込み イ ネーブル機能があ り 、8 ビ ッ ト (1 バ イ ト) 単位で入力 デー タ を書 き 込む こ と がで き ます。完全デ ュ アルポー ト RAM へのバ イ ト 幅書 き 込み イ ネーブル入 力は、最高で 4 つあ り ます。各バ イ ト 幅書き 込み イ ネーブルは、入力デー タ の 1 バ イ ト と 1 パ リ テ ィ ビ ッ ト に対応 し てい ます。こ の機能は、 ブ ロ ッ ク RAM を使用 し てマ イ ク ロ プ ロ セ ッ サ と 通信す る 場合に有用です。バ イ ト 幅書 き 込み イ ネーブルの詳細は、「ブ ロ ッ ク RAM プ リ ミ テ ィ ブの設計上の 追加注意事項」 を参照 し て く だ さ い。図 7に、 ブ ロ ッ ク RAM のバ イ ト 幅書 き 込み イ ネーブルの タ イ ミ ン グ図を示 し ます。 ブ ロ ッ ク RAM を 18 ビ ッ ト 幅ま たは 9 ビ ッ ト 幅のデー タ パ ス用に コ ン フ ィ ギ ュ レーシ ョ ンす る と 、 デー タ ワー ド 内で指定 し たバ イ ト 位置への書き 込みを任意のポー ト で制御で き ます。 READ_FIRST モー ド の場合、DO バ ス には指定 さ れた ア ド レ ス の以前の ワ ー ド 全体が出力 さ れま す。WRITE_FIRST モー ド の場合、DO には新 し く 書 き 込まれた イ ネーブルにな っ てい る バ イ ト の みが出力 さ れます。 NO_CHANGE モー ド の場合、DO には前の ク ロ ッ ク サ イ ク ルか ら の値が保持 さ れます。ブ ロ ッ ク

RAM

のラ イ ブ ラ リ

プ リ ミ テ ィ ブ

Spartan-6 FPGA ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ RAMB16BWER および RAMB8BWER

は、 すべてのブ ロ ッ ク RAM コ ン フ ィ ギ ュ レーシ ョ ンの基本ブ ロ ッ ク です。その他のブ ロ ッ ク RAM

プ リ ミ テ ィ ブおよびマ ク ロ は、 こ れ ら のプ リ ミ テ ィ ブを基に し てい ます。 ブ ロ ッ ク RAM の属性に よ っ ては、 これ ら の中の 1 つのプ リ ミ テ ィ ブを使用する だけで コ ン フ ィ ギ ュ レーシ ョ ンで き ます。詳 細は、「ブ ロ ッ ク RAM の属性」 を参照し て く だ さ い。

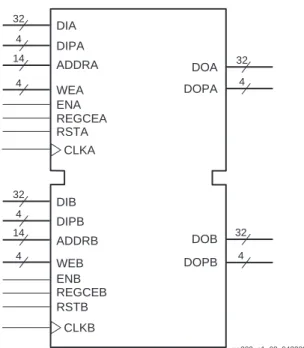

図 8に 18Kb の完全デュ アルポー ト の RAM プ リ ミ テ ィ ブ (RAMB16BWER) の I/O ポー ト を、図 9に 9Kb のデ ュ アルポー ト ブ ロ ッ ク RAM プ リ ミ テ ィ ブ (RAMB8BWER) を示 し ます。表 7には、

お よ び プ リ ミ テ ィ ブを リ ス ト し ます。

X-Ref Target - Figure 7

図

7 :

バイ ト 書き込み動作の波形(x36 WRITE_FIRST)

CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 1111 0011 XXXX aa bb bb cc 0000 MEM(aa) 1111 xx22 MEM(cc) Read Write MEM(bb)=1111 Byte Write MEM(bb)=1122 ug383_c1_07_052909ブ ロ ッ ク RAM のラ イ ブ ラ リ プ リ ミ テ ィ ブ

X-Ref Target - Figure 8

図

8 :

ブ ロ ッ クRAM

ポー ト 信号(RAMB16BWER)

X-Ref Target - Figure 9図

9 :

ブ ロ ッ クRAM

ポー ト 信号(RAMB8BWER)

DIA ADDRA WEA ENA RSTA CLKA DOA DOB REGCEA DIB ADDRB WEB ENB RSTB REGCEB CLKB ug383_c1_08_042209 32 14 4 32 32 32 14 4 DIPA 4 DIPB 4 DOPB 4 DOPA 4 DIADI ADDRAWRADDR WEAWEL ENAWREN RSTA CLKAWRCLK DOADO DOBDO REGCEA DIBDI ADDRBRDADDR WEAWEU ENBRDEN RSTBRST REGCEBREGCE CLKBRDCLK ug383_c1_09_042309 16 13 2 16 16 16 13 2 DIPADIP 2 DIPBDIP 2 DOPBDOP 2 DOPADOP 2ブ ロ ッ ク RAM のポー ト 信号

ブ ロ ッ ク

RAM

のポー ト 信号

ブ ロ ッ ク RAM の各ポー ト は、同 じ 9Kb ま たは 18Kb メ モ リ セルのセ ッ ト にア ク セ ス し ますが、動 作はそれぞれ独立 し てい ます。 RAMB16BWER と RAMB8BWER プ リ ミ テ ィ ブのポー ト 名は異な り ます。 次のセ ク シ ョ ンでは、RAMB16BWER のポー ト 名を最初に、RAMB8BWER のポー ト 名 を かっ こ 内に し ます。ク ロ ッ ク

- CLKA

、

CLKB (CLKAWRCLK

、

CLKBRDCLK)

各ポー ト は、 それぞれの ク ロ ッ ク ピ ンに完全に同期 し ます。すべてのポー ト 入力ピ ンのセ ッ ト ア ッ プ タ イ ムは、CLK ピ ンのポー ト を基準 と し てい ます。ま た、出力デー タ バ ス の clock-to-out タ イ ム も CLK ピ ン を基準 と し ます。ク ロ ッ ク の極性は コ ン フ ィ ギ ュ レーシ ョ ン可能で、デフ ォ ル ト は立ち 上が り エ ッ ジに設定 さ れてい ます。 完全デ ュ アルポー ト (TDP) モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、 CLKAWRCLK と CLKBRDCLK がそれぞれのポー ト の ク ロ ッ ク 入力にな り ます。 SDP モー ド (RAM_MODE = SDP) の場合、CLKAWRCLK が書 き 込み ク ロ ッ ク 入力、CLKBRDCLK が読み出 し ク ロ ッ ク 入力にな り ます。イ ネーブル

- ENA

、

ENB (ENAWREN

、

ENBRDEN)

ポー ト の読み出 し 、 書き 込み、 お よ びセ ッ ト/リ セ ッ ト 機能を制御 し ます。ポー ト の イ ネーブルピ ン が非ア ク テ ィ ブの と き は、出力ピ ンは前の状態を保持 し 、デー タ は メ モ リ セルに書 き 込まれません。 イ ネーブルの極性は コ ン フ ィ ギ ュ レーシ ョ ン可能で、 デフ ォ ル ト ではア ク テ ィ ブ High に設定 さ れ てい ます。

TDP モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、ENAWREN と ENBRDEN がそれ ぞれのポー ト の イ ネーブル入力にな り ます。 SDP モー ド の場合は、ENAWREN が書 き 込み イ ネー ブル、ENBRDEN が読み出 し イ ネーブルにな り ます。

バイ ト 幅書き込みイ ネーブル

- WEA

、

WEB (WEAWEL

、

WEBWEU)

デー タ 入力バ ス の内容を指定 し た メ モ リ 位置に書 き 込むには、 ク ロ ッ ク の立ち上が り エ ッ ジのセ ッ 表 7 : Spartan-6 FPGA のブ ロ ッ ク RAM プ リ ミ テ ィ ブ

プ リ ミ テ ィ ブ 説明 RAMB8BWER サポー ト さ れ る デー タ 幅 : x1、x2、x4、x8、x16、x32 (お よ びパ リ テ ィ ビ ッ ト 付 き の x9、x18、x36) RAMB16BWER サポー ト さ れ る デー タ 幅 : x1、x2、x4、x8、x16、x32 (お よ びパ リ テ ィ ビ ッ ト 付 き の x9、x18、x36) メ モ : 1. プ リ ミ テ ィ ブについては、 ソ フ ト ウ ェ アの ラ イ ブ ラ リ ガ イ ド お よ び言語テ ンプ レー ト で説明 さ れてい ます。

ブ ロ ッ ク RAM のポー ト 信号

TDP モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、WEAWEL と WEBWEU がそれぞ れのポー ト のバ イ ト イ ネーブル入力にな り ます。 SDP モー ド の場合、WEAWEL が下位 2 バ イ ト の 書 き 込み イ ネーブルで、WEBWEU が上位バ イ ト の書 き 込み イ ネーブルにな り ます。

レ ジス タ

イ ネーブル

- REGCEA

、

REGCEB (REGCEA

、

REGCEBREGCE)

オプシ ョ ンの出力レ ジ ス タ を制御 し ます。 RAM が レ ジ ス タ モー ド の場合、REGCE = 1 と 指定す ると 、 ク ロ ッ ク エ ッ ジで出力が レ ジ ス タ に取 り 込まれます。 REGCE の極性は コ ン フ ィ ギ ュ レーシ ョ ン可能で、 デフ ォ ル ト ではア ク テ ィ ブ High に設定 さ れてい ます。

TDP モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、REGCEA と REGCEBREGCE が それぞれのポー ト の レ ジ ス タ ク ロ ッ ク イ ネーブル入力にな り ます。 SDP モー ド の場合、REGCEA は未使用なので、ロ ジ ッ ク 0 に接続 さ れてい る 必要があ り ます。REGCEBREGCE は、読み出 し ポー ト の レ ジ ス タ イ ネーブルにな り ます。

セ ッ ト

/

リ セ ッ ト

- RSTA

、

RSTB (RSTA

、

RSTBRST)

ラ ッ チモー ド では、RST ピ ンがア ク テ ィ ブにな る と 、デー タ 出力 ラ ッ チの値が SRVAL の値にな り ます。こ の動作は、RSTTYPE 属性の値に よ っ て同期ま たは非同期にな り ます。詳細は、23 ページ の 「ブ ロ ッ ク RAM の属性」 を参照 し て く だ さ い。オプシ ョ ンの出力レ ジ ス タ が イ ネーブルの場合 (DO_REG = 1)、RST 信号に よ り デー タ 出力レ ジ ス タ の値が SRVAL の値にな り ます。 RST_PRIORITY 属性を使用す る と 、RST と REGCE の ど ち ら を優先す る かを指定で き ます。デー タ 出力レ ジ ス タ は、 パ リ テ ィ ビ ッ ト を含めて、0 ま たは 1 にアサー ト さ れます。EN_RSTRAM 属 性の設定に よ っ ては、 デー タ 出力 ラ ッ チが RST ポー ト で も リ セ ッ ト さ れます。各ポー ト には、 それ ぞれ 36 ビ ッ ト の SRVAL[A|B] 属性が指定 さ れます。こ の動作に よ り RAM メ モ リ セルが変化す る こ と はな く 、 も う 1 つのポー ト での書 き 込みに も 影響 し ません。 セ ッ ト/リ セ ッ ト 機能 も 、 読み込み /書 き 込み と 同様に、そのポー ト の イ ネーブルピ ンがア ク テ ィ ブな場合にのみ有効 と な り ます。両方 の信号の極性は コ ン フ ィ ギ ュ レーシ ョ ン可能で、 デフ ォ ル ト ではア ク テ ィ ブ High に設定 さ れてい ます。TDP モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、RSTA と RSTBRST がそれぞれの ポー ト のセ ッ ト/リ セ ッ ト 入力にな り ます。 SDP モー ド の場合、RSTA は未使用なので、 ロ ジ ッ ク 0

に接続 さ れてい る 必要があ り ます。RSTBRST は、 読み出 し ポー ト のセ ッ ト/リ セ ッ ト にな り ます。

ア ド レ ス

バス

- ADDRA

、

ADDRB (ADDRAWRADDR

、

ADDRBRDADDR)

読み込みま たは書 き 込みを行 う メ モ リ セルを選択 し ます。表 4に示す よ う に、1つのブ ロ ッ ク RAMに必要なア ド レ ス バ ス幅は、 ポー ト のデー タ ビ ッ ト 幅に よ っ て決ま り ます。 デー タ幅は、

DATA_WIDTH_[A|B] 属性に よ っ て定義 さ れます。

TDP モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、ADDRAWRADDR と

ADDRBRDADDR がそれぞれのポー ト の イ ネーブル入力にな り ます。 SDP モー ド

(RAM_MODE=SDP) の場合、ADDRBRDADDR が書 き 込みポー ト のア ド レ ス入力、

ブ ロ ッ ク RAM のポー ト 信号

デー タ 入力バス

- DIA

、

DIB (DIADI

、

DIBDI)

RAM に書き 込むデー タ 値を供給 し ます。パ リ テ ィデー タ 入力バ ス (使用可能な場合) を含む通常の デー タ 入力バ ス (DI) の幅を合計す る と 、ポー ト 幅にな り ます。た と えば、表 4に示す よ う に、36 ビ ッ ト ポー ト のデー タ 幅は DI[31:0] と そのパ リ テ ィ ビ ッ ト の DIP[3:0] で表 さ れます。デー タ幅は、

DATA_WIDTH_[A|B] 属性に よ っ て定義 さ れます。

TDP モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、DIADI と DIBDI がそれぞれのポー ト のデー タ 入力にな り ます。 SDP モー ド (RAM_MODE=SDP) の場合は、DIADI が下位ビ ッ ト 、

DIBDI が上位ビ ッ ト を示 し ます (デー タ 幅が 16 ビ ッ ト を超え る 場合)。

デー タ 入力パ リ テ ィ

- DIPA

、

DIPB (DIPADIP

、

DIPBDIP)

RAM のパ リ テ ィ ビ ッ ト に書 き 込むデー タ 値を供給 し ます。メ モ リ の こ の部分は、 パ リ テ ィ ビ ッ ト を格納す る ための も のですが、 必要に応 じ て追加デー タ に も 使用で き ます。 パ リ テ ィ ビ ッ ト を計算 し た り 、検証する ための ロ ジ ッ ク は、ブ ロ ッ ク RAM にはあ り ません。 TDP モー ド の場合、DIPADIP

と DIPBDIP がそれぞれのポー ト のパ リ テ ィ デー タ 入力にな り ます。 SDP モー ド の場合、DIPADIP

が下位 2 ビ ッ ト のパ リ テ ィ で、DIPBDIP が上位 2 ビ ッ ト のパ リ テ ィ にな り ます。

デー タ 出力バス

- DOA

、

DOB (DOADO

、

DOBDO)

読み出 し では、 最後のア ク テ ィ ブな ク ロ ッ ク エ ッ ジでア ド レ ス バ ス に よ り 指定 さ れた メ モ リ セル の内容が、 デー タ 出力バス に送信 さ れます。 WRITE_FIRST ま たは READ_FIRST モー ド の書 き込 みでは、 書 き 込み中の値 ま たは書 き 込み前に保存 さ れていた値がデー タ 出力バ ス に送信 さ れ ます。

NO_CHANGE モー ド の書 き 込みでは、 デー タ 出力バ ス は変化 し ません。

TDP モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、DOADO と DOBDO がそれぞれの ポー ト の出力にな り ます。 SDP モー ド (RAM_MODE=SDP) の場合は、DOADO が下位ビ ッ ト 、

DOBDO が上位ビ ッ ト を示 し ます (デー タ幅が 16 ビ ッ ト を超え る 場合)。

デー タ 出力パ リ テ ィ

- DOPA

、

DOPB (DOPADOP

、

DOPBDOP)

パ リ テ ィ デー タ に割 り 当て ら れた メ モ リ セルの内容が出力 さ れます。デー タ は、デー タ 出力バ ス と 同様にバ ス に出力 さ れます。

TDP モー ド (RAM_MODE = TDP) の RAMB8BWER の場合、DOPADOP と DOPBDOP がそれぞ れのポー ト の出力にな り ます。 SDP モー ド の場合、DOPADOP が下位バ イ ト のパ リ テ ィ ビ ッ ト 、 DOPBDOP が上位バ イ ト のパ リ テ ィ ビ ッ ト にな り ます。

GSR

Spartan-6 デバ イ ス のグ ロ ーバルセ ッ ト/リ セ ッ ト (GSR) 信号は、デバ イ ス の コ ン フ ィ ギ ュ レーシ ョ ン終了時にア ク テ ィ ブにな る 非同期のグ ロ ーバル信号です。 GSR を使用す る と 、Spartan-6 デバ イ ス の初期状態を いつで も 復元で き ます。 GSR に よ り 、 出力 ラ ッ チは INIT (シ ンプルデ ュ アルポー ト) ま たは INIT_A お よ び INIT_B の値 (完全デ ュ アルポー ト) に初期化 さ れます。詳細は、「ブ ロ ッブ ロ ッ ク RAM のア ド レ スマ ッ プ

ブ ロ ッ ク

RAM

のア ド レ ス

マ ッ プ

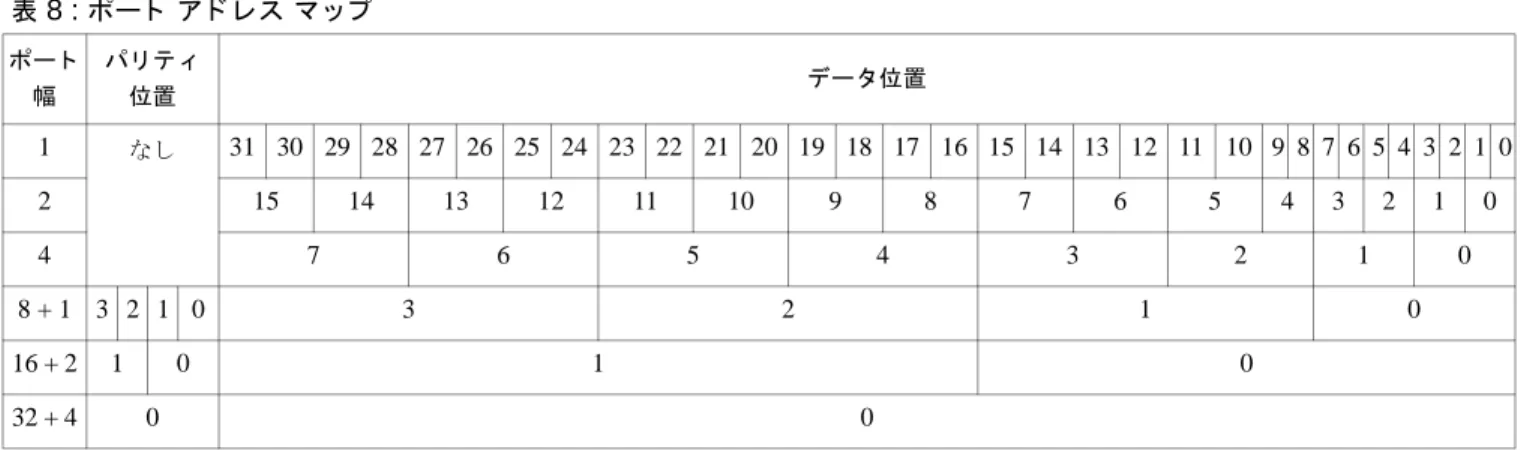

各ポー ト は、9Kb RAM であ る か 18Kb RAM であ る かに よ っ て異な る ア ド レ ス指定方法を使用 し て、同 じ 9,216 個ま たは 18,432 個の メ モ リ セルにア ク セ ス し ます。特定のポー ト 幅で指定 さ れ る 物 理的な RAM の位置は、次の式に よ っ て決定 さ れます (2 つのポー ト が異な る 比率の場合のみ参照)。

END = ((ADDR + 1) × Width)

-

1 START = ADDR × Width表 8に、 各ポー ト 幅の下位のア ド レ スマ ッ プを示 し ます。

ブ ロ ッ ク

RAM

の属性

すべての属性 コ ー ド 例は、「ブ ロ ッ ク RAM の初期化」に記載 さ れてい ます。こ れ ら の属性の使用に ついては、「ブ ロ ッ ク RAM プ リ ミ テ ィ ブの設計上の追加注意事項」で詳細に説明 し てい ます。デー タ お よびア ド レ ス幅

- DATA_WIDTH_A

、

DATA_WIDTH_B

各ポー ト のデー タ バ ス と ア ド レ ス バ ス の幅を定義 し ます。 リ ス ト さ れてい る デー タ 幅の有効な組 み合わせは、0 (デフ ォル ト)、1、2、4、9、18 お よ び 36 で、9、18、36 にはパ リ テ ィ ビ ッ ト が含 まれます。シ ンプルデ ュ アルポー ト モー ド の 9Kb ブ ロ ッ ク RAM では、DATA_WIDTH に設定可 能な値は 36 のみです。 シ ンプルま たは完全デ ュ アルポー ト モー ド の 18Kb ブ ロ ッ ク RAM、 あ る いは完全デ ュ アルポー ト モー ド の 9Kb ブ ロ ッ ク RAM では、DATA_WIDTH を任意の組み合わせ に設定で き ます。 デー タ 幅に基づ く ア ド レ ス幅は、表 4の よ う にな り ます。メ モ リ 内容の初期化

- INIT_xx

メ モ リ の初期内容を定義 し ます。 デフ ォ ル ト では、 ブ ロ ッ ク RAM メ モ リ はデバ イ ス の コ ン フ ィ ギ ュ レーシ ョ ン シーケ ン ス中にすべて 0 に初期化 さ れます。 9Kb ブ ロ ッ ク RAM の INIT_00 ~INIT_1F 初期化属性、18Kb ブ ロ ッ ク RAM の INIT_00 ~ INIT_3F 初期化属性は、 通常の メ モ リ 内容を指定 し ます。パ リ テ ィ メ モ リ の内容は、INITP 属性を使用 し て初期化 し ます。各 INIT_xx は、 16 進数で表 し た 64 桁の ビ ッ ト ベ ク タ です。メ モ リ は一部だけ を初期化す る こ と も 可能です。 こ の 表 8 : ポー ト ア ド レ スマ ッ プ ポー ト 幅 パ リ テ ィ 位置 デー タ 位置 1 な し 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 2 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 4 7 6 5 4 3 2 1 0 8 + 1 3 2 1 0 3 2 1 0 16 + 2 1 0 1 0 32 + 4 0 0

ブ ロ ッ ク RAM の属性 た と えば、 属性 INIT_1F の場合は次の よ う にな り ます。 • yy = 16 進数 (xx) 1F を 10 進数に変換 し た値 = 31 • 開始セル : [(31+1)× 256] – 1 = 8191 • 終了セル : 31× 256 = 7936 その他の例を表 9に示 し ます。

パ リ テ ィ

メ モ リ 内容の初期化

- INITP_xx

パ リ テ ィ ビ ッ ト に対応す る メ モ リ セルの初期内容を定義 し ます。デフ ォ ル ト では、 こ れ ら の メ モ リ セル も すべて 0 に初期化 さ れます。初期化属性で、 パ リ テ ィ ビ ッ ト の メ モ リ 内容を指定 し ます。初 期化属性は、9Kb ブ ロ ッ ク RAM では INITP_00 ~ INITP_03、18Kb ブ ロ ッ ク RAM では INIT_00~ INITP_07 です。各 INITP_xx は、16 進数で表 し た 64 桁のビ ッ ト ベ ク タ で、INIT_xx 属性 と 同 様に機能 し ます。特定の INITP_xx 属性で初期化す る ビ ッ ト 位置 も 、 同 じ 式で計算 さ れます。 表 9 : ブ ロ ッ ク RAM の初期化属性 属性 メ モ リ 位置 開始位置 終了位置 INIT_00 255 0 INIT_01 511 256 INIT_02 767 512 … … … INIT_0E 3839 3584 INIT_0F 4095 3840 INIT_10 4351 4096 … … … INIT_1F 8191 7936 INIT_20 8447 8192 … … … INIT_2F 12287 12032 INIT_30 12543 12288 … … … INIT_3F 16383 16128

ブ ロ ッ ク RAM の属性

出力 ラ ッ チ

/

レ ジ ス タ の同期セ ッ ト

/

リ セ ッ ト

- SRVAL_A

、

SRVAL_B

RST 入力がアサー ト さ れた際の出力 ラ ッ チの値を定義 し ます。こ れ ら の属性の幅がポー ト 幅にな り ます。こ れ ら の属性は 16 進数のビ ッ ト ベ ク タ で、デフ ォル ト 値は 0 です。オプシ ョ ンの出力レ ジ ス タ 属性が設定 さ れてい る 場合は、出力レ ジ ス タ 値を指定 し ます。レ ジ ス タ が未使用の と き は、ラ ッ チ が SRVAL に指定 さ れます。パ リ テ ィ を使用す る 場合は、最上位ビ ッ ト (MSB) がそのパ リ テ ィ ビ ッ ト にな り ます。 TDP モー ド の場合、SRVAL_A がポー ト A に、SRVAL_B がポー ト B にな り ます。 SDP モー ド の 場合、SRVAL_A が下位 18 ビ ッ ト (パ リ テ ィ 2 ビ ッ ト を含む) に、SRVAL_B が上位ビ ッ ト (パ リ テ ィ 2 ビ ッ ト を含む) にな り ます。RAM

モー ド

- RAM_MODE

こ の属性は RAMB8BWER に対 し てのみ必要で、 ブ ロ ッ ク RAM を完全デ ュ アルポー ト RAM (読み出 し お よ び書 き 込み用にバ ス が 2 つ) ま たはシ ンプルデュ アルポー ト RAM (ポー ト B が読み 出 し 専用、 ポー ト A は書 き 込み用) の ど ち ら と し て使用す る かを指定 し ます。 有効な値は TDP (デ フ ォ ル ト) ま たは SDP です。

リ セ ッ ト と

CE

の優先度

- RST_PRIORITY_A

、

RST_PRIORITY_B

出力レ ジ ス タ を使用す る 場合は、 こ の属性で RST と REGCE の ど ち ら を優先す る かを指定で き ま す。レ ジ ス タ の代わ り に出力 ラ ッ チを使用す る 場合は、RST と EN の ど ち ら を優先す る かを指定で き ます。 有効な値は SR (デフ ォ ル ト) ま たは CE です。デー タ

ラ ッ チ

リ セ ッ ト

- EN_RSTRAM_A

、

EN_RSTRAM_B

RST ポー ト でブ ロ ッ ク RAM 出力の ラ ッ チを リ セ ッ ト す る か ど う かを指定 し ます。 有効な値は TRUE ま たは FALSE (デフ ォ ル ト) です。リ セ ッ ト

タ イ プ

- RSTTYPE

ブ ロ ッ ク RAM 出力を同期で リ セ ッ ト す る か、 非同期で リ セ ッ ト す る かを指定 し ます。値は SYNC (デフ ォ ル ト) ま たは ASYNC に設定で き ますが、非同期 リ セ ッ ト よ り も 同期 リ セ ッ ト を使用す る こ と をお勧め し ます。詳細は、「 リ セ ッ ト の動作」 を参照 し て く だ さ い。オ プ シ ョ ンの出力レ ジ ス タ 切 り 替え

- DO[A|B]_REG

ブ ロ ッ ク RAM の A/B 出力でのパ イ プ ラ イ ンレ ジ ス タ を イ ネーブルにす る かど う かを指定 し ます。 有効な値は 0 (デフ ォル ト) ま たは 1 です。書き込みモー ド

- WRITE MODE_A

、

WRITE_MODE_B

ブ ロ ッ ク RAM の初期化

ブ ロ ッ ク

RAM

のロ ケーシ ョ ン制約

ブ ロ ッ ク RAM の イ ン ス タ ン ス に LOC プ ロ パテ ィ を指定す る と 、 配置を制約で き ます。ブ ロ ッ ク RAM の配置位置の表記方法は、CLB 位置の表記方法 と は異な り 、LOC プ ロ パテ ィ を別の配列で も 容易に使用で き る よ う にな っ てい ます。 18Kb ブ ロ ッ ク RAM では、RAMB16 の ロ ケーシ ョ ン識別 を使用 し て、 パ リ テ ィ ビ ッ ト を含ま ない RAM の容量を示 し ます。 9Kb ブ ロ ッ ク RAM では、 次の よ う な RAMB8 の表記を使用 し ます。 LOC プ ロ パテ ィ は、 次の形式で指定 し ます。 LOC = RAMB16_X#Y#; LOC = RAMB8_X#Y#;RAMB16_X0Y0 は、 デバ イ ス の左下にあ る 18 Kb ブ ロ ッ ク RAM の位置です。 18 Kb RAM が

RAMB16_X0Y0 に制約 さ れ る 場合、9 Kb RAM は こ れ と 位置を共有す る ので、RAMB8_X0Y0 ま たは RAMB8_X0Y1 に制約で き ません。

ブ ロ ッ ク

RAM

の初期化

ブ ロ ッ ク RAM メ モ リ の属性お よ び内容は、イ ン ス タ ン シエー ト さ れた コ ン ポーネ ン ト 内で generic map (VHDL) ま たは defparam (Verilog) を使用 し て、合成お よ びシ ミ ュ レーシ ョ ン用に VHDL ま た は Verilog コ ー ド で初期化で き ます。 generic map ま たは defparam の値を変更す る と 、 シ ミ ュ レー シ ョ ン ビヘ イ ビ ア と イ ンプ リ メ ン テーシ ョ ン結果に影響 し ます。 Spartan-6 の ラ イ ブ ラ リ ガ イ ド に は、18Kb お よ び 9Kb ブ ロ ッ ク RAM を初期化する ための コ ー ド が記載 さ れてい ます。

ブ ロ ッ ク

RAM

プ リ ミ テ ィ ブの設計上の追加注意事項

出力レ ジ ス タ

(

オプ シ ョ ン

)

オプシ ョ ンの出力レ ジ ス タ は、RAMB16BWER お よ び RAMB8BWER の A|B 出力ポー ト のいずれ か、 ま たは両方に使用で き ます。使用ポー ト は DO[A|B]_REG 属性を使用 し て指定 し ます。独立 し た 2 つの ク ロ ッ ク イ ネーブルピ ンは REGCE[A|B] です。ポー ト [A|B] でオプシ ョ ンの出力レ ジ ス タ を使用す る 場合、ポー ト [A|B] の同期セ ッ ト/リ セ ッ ト (RST) ピ ン を アサー ト す る と 、属性 SRVAL

で指定 さ れた値が レ ジ ス タ を介 し て出力 さ れます。図 5にオプシ ョ ンの出力レ ジ ス タ を示 し ます。

RAMB16BWER

お よび

RAMB8BWER

ポー ト のマ ッ プ規則

Spartan-6 FPGA ブ ロ ッ ク RAM は、さ ま ざ ま なポー ト 幅 と サ イ ズに コ ン フ ィ ギ ュ レーシ ョ ンで き ま す。コ ン フ ィ ギ ュ レーシ ョ ンに よ っ ては、 一部のデー タ ピ ン と ア ド レ ス ピ ンが未使用 と な り ます。

表 4は、さ ま ざ ま な コ ン フ ィ ギ ュ レーシ ョ ンで使用 さ れ る ピ ン を示 し てい ます。表 4の情報に加え、 次の規則に基づいてブ ロ ッ ク RAM のポー ト 接続を決定 し ます。

• RAMB16BWER を使用 し ていて DI[A|B] ピ ンの幅が 32 ビ ッ ト 未満の場合、

ブ ロ ッ ク RAM のア プ リ ケーシ ョ ン • RAMB16BWER を使用す る 場合、DO[A|B] ピ ンの幅は 32 ビ ッ ト にする 必要があ り ます。ただ し 、(DO_BIT_WIDTH - 1) か ら 0 ま での ピ ンのデー タ のみが有効です。 • RAMB16BWER を使用する 場合、DOP[A|B] ピ ンの幅は 4 ビ ッ ト にす る 必要があ り ます。 RAMB8BWER を使用す る 場合、DOP[A|B] ピ ンの幅は 2 ビ ッ ト にす る 必要があ り ます。ただ し 、(DOP_BIT_WIDTH - 1) か ら 0 ま でのピ ンのデー タ のみが有効です。 DOP[A|B] を使用 し ていない場合は、 未接続の ま ま にで き ます。 • RAMB16BWER を使用する 場合、ADDR[A|B] ピ ンの幅は 14 ビ ッ ト にす る 必要があ り ます。 RAMB8BWER を使用す る 場合、ADDR[A|B] ピ ンの幅は 13 ビ ッ ト にす る 必要があ り ます。ア ド レ ス幅は、表 4に記載 さ れてい ます。

リ セ ッ ト の動作

ブ ロ ッ ク RAM の ラ ッ チ ま たはレ ジ ス タ の初期値は、RSTTYPE = ASYNC の場合は SR_VAL で、

RSTTYPE = SYNC の場合は INIT で定義 さ れます。 リ セ ッ ト タ イ プが ASYNC で INIT 値が使用 さ れてい る 場合、 コ ン フ ィ ギ ュ レーシ ョ ン後に GSR を適用す る 必要があ り ます。

バイ ト 幅書き込みイ ネーブル

バ イ ト 幅書 き 込み イ ネーブルを使用す る 場合は、 次の規則に従っ て く だ さ い。 • x36 モー ド の場合、WE[3:0] を 4 つのユーザー WE 入力に接続 し ます。

• x18 モー ド の場合、WE[0] お よ び WE[2] はユーザー WE[0] で駆動 し 、WE[1] お よ び WE[3]

はユーザー WE[1] で駆動 し ます。

• x9、x4、x2、x1 モー ド の場合、WE[3:0] はすべて 1 つのユーザー WE に接続 さ れます。

ブ ロ ッ ク

RAM

のア プ リ ケーシ ョ ン

大型

RAM

構造の作成

CORE Generator では、 複数のブ ロ ッ ク RAM イ ン ス タ ン ス を使用 し て、 ビ ッ ト 数お よ びワ ー ド 数 の多い メ モ リ 構造を簡単に生成で き ます。こ の ツールでは、VHDL ま たは Verilog の イ ン ス タ ン シ エーシ ョ ン テ ンプ レー ト やシ ミ ュ レーシ ョ ンモデル、デザ イ ンに含め る EDIF フ ァ イ ルが出力 さ れ ます。

ブ ロ ッ ク RAM のア プ リ ケーシ ョ ン

レ ジ ス タ

モー ド のブ ロ ッ ク

RAM

の

RST

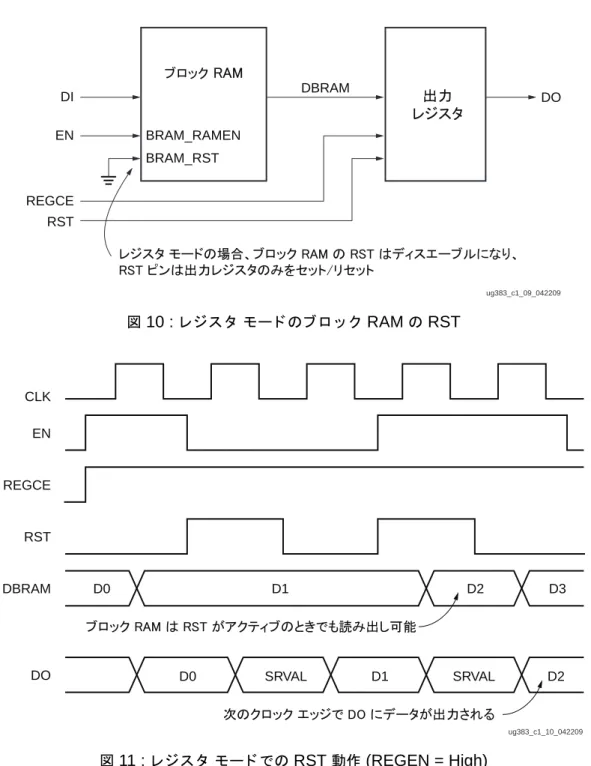

ブ ロ ッ ク RAM の RST を レ ジ ス タモー ド で使用す る と 、 出力レ ジ ス タ を ブ ロ ッ ク RAM か ら 独立 し たパ イ プ ラ イ ンレ ジ ス タ と し て制御で き ます。図 10は、ブ ロ ッ ク RAM の読み出 し お よ び書 き 込 みが、 レ ジ ス タ イ ネーブルま たはセ ッ ト/リ セ ッ ト と は独立 し て実行 さ れてい る と こ ろ を示 し てい ます。レ ジ ス タ モー ド では、RST に よ り DO が SRVAL に設定 さ れ、ブ ロ ッ ク RAM か ら DBRAM

へのデー タ 読み出 し が可能です。 DBRAM でのデー タ は、 次のサ イ ク ルで ク ロ ッ ク 出力 (DO) に送 信で き ます。図 11お よ び図 12の タ イ ミ ン グ図は、 別の RST の例を示 し てい ます。

X-Ref Target - Figure 10

図

10 :

レ ジ ス タ モー ド のブ ロ ッ クRAM

のRST

䊑䊨䉾䉪㩷㪩㪘㪤

ജ

䊧䉳䉴䉺

BRAM_RST DO BRAM_RAMEN 䊧䉳䉴䉺㩷䊝䊷䊄䈱႐ว䇮䊑䊨䉾䉪㩷㪩㪘㪤㩷䈱㩷㪩㪪㪫㩷䈲䊂䉞䉴䉣䊷䊑䊦䈮䈭䉍䇮 㪩㪪㪫㩷䊏䊮䈲ജ䊧䉳䉴䉺䈱䉂䉕䉶䉾䊃㪆䊥䉶䉾䊃 EN REGCE RST DI DBRAM ug383_c1_09_042209X-Ref Target - Figure 11

CLK EN REGCE RST DBRAM 䊑䊨䉾䉪㩷㪩㪘㪤㩷䈲㩷㪩㪪㪫㩷䈏䉝䉪䊁䉞䊑䈱䈫䈐䈪䉅⺒䉂䈚น⢻ D0 D1 D2 D3 D0 SRVAL D1 SRVAL D2 DO

ブ ロ ッ ク RAM のア プ リ ケーシ ョ ン

X-Ref Target - Figure 12

図

12 :

レ ジ ス タ モー ド でのRST

動作(REGEN =

変数)

CLK EN REGCE RST DBRAM D0 D1 D2 D3 D0 SRVAL D1 D2 DO ug383_c1_11_042209 㪩㪪㪫㩷䈲㩷㪩㪜㪞㪚㪜㩷䉅㩷㪟㫀㪾㪿㩷䈱䈫䈐䈮䈱䉂㩷㪛㪦㩷䉕䉶䉾䊃㪆䊥䉶䉾䊃ブ ロ ッ ク RAM の タ イ ミ ングモデル

ブ ロ ッ ク

RAM

の タ イ ミ ング

モデル

こ こ では、Spartan-6 デバ イ ス のブ ロ ッ ク RAM に関連す る タ イ ミ ン グパ ラ メ ー タ について説明 し ます (図 13を参照)。 Spartan-6 FPGA デー タ シー ト の ス イ ッ チ特性のセ ク シ ョ ンや、 ザ イ リ ン ク ス ソ フ ト ウ ェ アの Timing Analyzer (TRACE) か ら 出力 さ れ る レ ポー ト も 参考に し て く だ さ い。

ブ ロ ッ ク

RAM

の タ イ ミ ング

パ ラ メ ー タ

表 10は、Spartan-6 FPGA のブ ロ ッ ク RAM の タ イ ミ ン グパ ラ メ ー タ を示 し てい ます。

表 10 : ブ ロ ッ ク RAM の タ イ ミ ングパラ メ ー タ パラ メ ー タ フ ァ ン ク シ ョ ン 制御信号 説明 ク ロ ッ ク (CLK) に対する セ ッ ト ア ッ プ と ホール ド TRxCK_x = セ ッ ト ア ッ プ タ イ ム (ク ロ ッ ク エ ッ ジ前) お よ び TRCKx_x = ホール ド タ イ ム (ク ロ ッ ク エ ッ ジ後) TRCCK_ADDR ア ド レ ス入力 ADDR ク ロ ッ ク 前ま でに、 ブ ロ ッ ク RAM の ADDR 入力で、 ア ド レ ス信号が 安定 し てい る 必要のあ る 時間(1)

TRCKC_ADDR ク ロ ッ ク 後に、 ブ ロ ッ ク RAM の ADDR 入力で、 ア ド レ ス信号が安定 し てい る 必要のあ る 時間(1) TRDCK_DI デー タ 入力 DI ク ロ ッ ク 前に、 ブ ロ ッ ク RAM の DI 入力で、 デー タ が安定 し てい る 必 要のあ る 時間 TRCKD_DI ク ロ ッ ク 後に、 ブ ロ ッ ク RAM の DI 入力でデー タ が安定 し てい る 必要 のあ る 時間 TRCCK_EN イ ネーブル EN ク ロ ッ ク 前に、 ブ ロ ッ ク RAM の EN 入力で、 イ ネーブル信号が安定 し てい る 必要のあ る 時間 TRCKC_EN ク ロ ッ ク 後に、ブ ロ ッ ク RAM の EN 入力で イ ネーブル信号が安定 し て い る 必要のあ る 時間 TRCCK_RST 同期セ ッ ト/ リ セ ッ ト RST ク ロ ッ ク 前に、 ブ ロ ッ ク RAM の RST 入力で、 同期セ ッ ト/リ セ ッ ト 信 号が安定 し てい る 必要のあ る 時間。 TRCKC_RST ク ロ ッ ク 後に、ブ ロ ッ ク RAM の RST 入力で同期セ ッ ト/リ セ ッ ト 信号 が安定 し てい る 必要のあ る 時間 TRCCK_WE 書 き 込み イ ネーブル WE ク ロ ッ ク 前に、ブ ロ ッ ク RAM の WE 入力で、書 き 込み イ ネーブル信号 が安定 し てい る 必要のあ る 時間 TRCKC_WE ク ロ ッ ク 後に、ブ ロ ッ ク RAM の WE 入力で書 き 込み イ ネーブル信号が 安定 し てい る 必要のあ る 時間 TRCCK_REGCE 出力レ ジ ス タ ク ロ ッ ク 前ま でに、 ブ ロ ッ ク RAM の REGCE 入力で レ ジ ス タ イ ネー ブル信号が安定 し てい る 必要のあ る 時間

ブ ロ ッ ク RAM の タ イ ミ ングモデル

ブ ロ ッ ク

RAM

の タ イ ミ ング特性

図 13の タ イ ミ ン グ図は、 オプシ ョ ンの出力レ ジ ス タ を使用 し ない、WRITE_FIRST モー ド のシ ン グルポー ト ブ ロ ッ ク RAM を示 し てい ます。 READ_FIRST モー ド と NO_CHANGE モー ド の タ イ ミ ン グは、WRITE_FIRST モー ド と 類似 し てい ます。オプシ ョ ンの出力レ ジ ス タ を使用す る と 、 DO ピ ンで ク ロ ッ ク レ イ テ ン シが追加 さ れます。こ こ に示す波形は、 オプシ ョ ンの出力パ イ プ ラ イ ンレ ジ ス タ を使用 し ない ラ ッ チモー ド の場合の も のです。 0 の時点では、EN (イ ネーブル) は Low であ る ため、 ブ ロ ッ ク RAM はデ ィ ス エーブルです。

ク ロ ッ ク

イ ベ ン ト

1

読み出 し 読み出 し では、ADDR 入力のア ド レ ス位置の メ モ リ 内容は変更 し ません。 TRCKO_DO_REG (レ ジ ス タモー ド) ク ロ ッ ク か ら 出力 CLK か ら DO ク ロ ッ ク 後に、ブ ロ ッ ク RAM の DO 出力で出力デー タ が安定す る ま で の時間 (出力レ ジ ス タ を使用 し た場合) メ モ : 1. WE が非ア ク テ ィ ブで も EN がア ク テ ィ ブの場合は、 セ ッ ト ア ッ プ/ホール ド タ イ ム中は ADDR 入力が安定 し てい る 必要があ り ま す。こ の要件に違反す る と 、 ブ ロ ッ ク RAM でデー タ が破損す る 可能性があ り ま す。 ADDR タ イ ミ ン グが指定 し た要件に反す る 場合、EN は非 ア ク テ ィ ブ (デ ィ ス エーブル) にす る 必要があ り ます。 表 10 : ブ ロ ッ ク RAM の タ イ ミ ングパラ メ ー タ (続き) パラ メ ー タ フ ァ ン ク シ ョ ン 制御信号 説明X-Ref Target - Figure 13

図

13 :

ブ ロ ッ クRAM

の タ イ ミ ン グ図 ADDR DI DO EN RST WE CLK 00 DDDD TRCCK_ADDR TRDCK_DI TRCKO_DO MEM (00) TRCCK_EN TRCCK_WEDisabled Read Write Read Reset Disabled Note 1: Write Mode = WRITE_FIRST

Note 2: SRVAL = 0101 0F 7E 8F 20 CCCC BBBB AAAA 0000 CCCC(1) MEM (7E) 0101(2) ug383_c1_12_042209 1 2 3 4 5 TRCCK_RST

ブ ロ ッ ク RAM の タ イ ミ ングモデル • EN がアサー ト さ れてい る 場合は常に、 すべてのア ド レ ス変更が指定のセ ッ ト ア ッ プお よ び ホール ド 仕様を満たす必要があ り ます。非同期でのア ド レ ス変更は、 メ モ リ 内容お よ びブ ロ ッ ク RAM の機能に予想外の影響を与え る 可能性があ り ます。

ク ロ ッ ク

イ ベ ン ト

2

書き込み書 き 込みでは、 書 き 込み イ ネーブル (WE) が High にな る と 、ADDR 入力のア ド レ ス で指定 さ れた 位置の メ モ リ 内容が DI ピ ンの値に置 き 換え ら れ、 すぐ に出力 ラ ッ チに反映 さ れます

(WRITE_FIRST モー ド)。

• ク ロ ッ ク イ ベン ト 2 よ り TRCCK_ADDR時間前に、ア ド レ ス0Fがブ ロ ッ ク RAM の ADDR 入 力で有効にな り ます。 • ク ロ ッ ク イ ベン ト 2 よ り TRDCK_DI時間前に、 デー タCCCCがブ ロ ッ ク RAM の DI 入力で有 効にな り ます。 • ク ロ ッ ク イ ベン ト 2 よ り TRCCK_WE時間前に、書 き 込み イ ネーブルが WE で有効にな り ます。 • ク ロ ッ ク イ ベン ト 2 よ り TRCKO_DO 時間後に、デー タCCCCがブ ロ ッ ク RAM の DO 出力で 有効にな り ます。

ク ロ ッ ク

イ ベ ン ト

4

RST (同期セ ッ ト/リ セ ッ ト) 同期セ ッ ト/リ セ ッ ト では、初期化パ ラ メ ー タ の値 SRVAL がブ ロ ッ ク RAM の出力 ラ ッ チに読み込 まれます。 RST は メ モ リ の内容を変更 し ません。ま た、ADDR お よ び DI 入力の影響 も 受け ません。 • ク ロ ッ ク イ ベン ト 4 よ り TRCCK_RST時間前に、同期セ ッ ト/リ セ ッ ト 信号がブ ロ ッ ク RAM の RST 入力で有効 (High) にな り ます。• ク ロ ッ ク イ ベン ト 4 よ り TRCKO_DO時間後に、SRVAL の0101がブ ロ ッ ク RAM の DO 出力 で有効にな り ます。

ク ロ ッ ク

イ ベ ン ト

5

デ ィ スエーブル イ ネーブル信号 EN をデ ィ アサー ト す る と 、 書き 込み、 読み出 し 、 ま たは RST が実行で き な く な り ます。デ ィ ス エーブルに し て も 、 メ モ リ の内容、 お よ び出力 ラ ッ チの値は変わ り ません。 • ク ロ ッ ク イ ベン ト 5 よ り TRCCK_EN時間前に、イ ネーブル信号がブ ロ ッ ク RAM の EN 入力で 無効 (Low) にな り ます。 • ク ロ ッ ク イ ベン ト 5 後は、 ブ ロ ッ ク RAM の DO 出力のデー タ は変化 し ません。ブ ロ ッ ク RAM の タ イ ミ ングモデル

ブ ロ ッ ク

RAM

の タ イ ミ ング

モデル

図 14は、 ブ ロ ッ ク RAM の イ ンプ リ メ ン テーシ ョ ンに関連 し た遅延パス を示 し ています。記述 さ れ てい る のは、オン/オフチ ッ プの最 も シンプルなパス です (パスはデザ イ ンに よ り 大き く 異な り ます)。 こ の タ イ ミ ン グモデルは、 ブ ロ ッ ク RAM の タ イ ミ ン グパ ラ メ ータ の使用法お よび使用場所を示 し ています。 • NET = 可変 イ ン タ ー コ ネ ク ト 遅延 • TIOPI = パ ッ ド か ら IOB の I 出力ま での遅延 • TIOOP = IOB の O 入力か ら パ ッ ド ま での遅延 • TBUFG = BUFG 遅延X-Ref Target - Figure 14

図

14 :

ブ ロ ッ クRAM

の タ イ ミ ン グモデル Block RAMug383_c1_13_012610

FPGA

[TIOPI + NET] + TRCCK_WE

Write Enable

[TIOPI + NET] + TRCCK_EN

Enable

[TIOPI + NET] + TRCCK_ADDR

Address

[TIOPI + NET] + TRDCK_DI

Data

[TBUFG + NET]

Clock

[TIOPI + NET]

BUFG

TRCKO_DO + [NET + TIOOP]

Data [TIOPI + NET] + TRCCK_RST Set/Reset DO DI ADDR WE EN RST CLK