本資料ご利用に際しての注意事項 (「本資料」には、この注意事項が記載されたドキュメント、及び、このドキュメントに添付して配布されるプログラムソースコード 一式が含まれます。) 1. 本資料の内容は、全て本資料発行時点のものであり、予告なく変更することがあります。ご利用の際は、弊社からの最新情報をご 確認ください。 2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。 3. 本資料に掲載されるアルゴリズム、プログラム、応用回路、使用方法、製品データ、図、表等の技術情報はあくまでも参考情報で あり、これらに起因するあらゆる損害、第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社はいかなる責任も 負いません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。 4. 本資料に掲載されている情報は、人命にかかわるような状況下で使用される等の、高い信頼性、安全性が要求される製品やシステ ムに用いられることを想定していません。よって、弊社は本資料に掲載されている情報をこれらの用途に用いた場合のいかなる責 任も負いません。 5. 本資料に掲載されている情報をお客様の製品に応用する場合は、システム全体で十分に機能評価及び信頼性評価を行い、お客様の 責任においてご利用ください。 6. 本資料に掲載されている情報は、誤りを含まないように慎重に製作しておりますが、万一誤りがあった場合は、弊社にご連絡をお 願いします。また、この誤りに起因する損害について、弊社はいかなる責任も負いません。 7. その他、本資料に関するお問い合わせ、お気づきの点がございましたら、弊社にご連絡ください。

目次

1 特長... 1

2 パッケージ構成品 ... 3

3 各部の名称と機能 ... 4

3.1 各部の名称... 4

3.1.1

全体の外観 ... 4

3.1.2

CPUボード(LCDボード、Audioボードなし) ... 5

3.1.3

ICDボード ... 6

3.1.4

LCDボード ... 7

3.1.5

Audioボード ... 8

3.2 ジャンパー、ディップスイッチの機能と設定 ... 9

3.2.1

CPUボード ... 9

3.2.1.1 JP1 の機能と設定... 9

3.2.1.2 JP2、JP3 の機能と設定 ... 9

3.2.1.3 ディップスイッチ(DSW1)の機能と設定... 10

3.2.2

Audioボード ... 11

3.2.2.1 JP1 の機能と設定... 11

3.3 主要部品 ... 12

3.4 各部の機能... 14

3.4.1

ICDボード ... 14

3.4.2

CPUボード ... 15

3.4.2.1 電源 ... 15

3.4.2.2 CPUクロック ... 15

3.4.2.3 CPUボードリセットスイッチ ... 15

3.4.3

LCDボード ... 15

3.4.4

Audioボード ... 15

4 ブロック図 ... 16

5 動作環境と起動手順... 17

5.1 ソフトウェア簡易開発環境... 17

5.2 SVT33L17 の単独動作... 21

5.3 ICDボードファームウエアアップデート手順 ... 21

6 ICDボードとICD33 の相違点... 22

7 搭載メモリー ... 23

7.1 NOR Flash回路... 24

7.2 SDRAM回路 ... 24

7.3 NAND Flash回路... 25

7.4 Serial Flash回路 ... 25

8 CPUのキー入力回路 ... 26

9 MMCカードインターフェース回路... 27

10 UART(RS-232C)インターフェース回路 ... 28

11 USBインターフェース回路... 29

12 LCD回路 ... 30

13 Audio回路... 31

14 拡張インターフェースコネクタ... 32

14.1 CPUボード ... 32

14.1.1

デバッグ用コネクタ ... 32

14.1.2

USBインターフェース ... 34

14.1.3

MMCインターフェース ... 35

14.1.4

UART(RS-232C)インターフェース ... 36

14.1.5

LCDボードインターフェース... 37

14.1.6

Audioボードインターフェース... 39

14.1.7

外部拡張インターフェース ... 40

14.2 LCDボード... 42

14.3 Audioボード... 44

Appendix A 基板寸法図... 45

A.1 外観図(CPUボード/ICDボード/LCDボード/Audioボード)... 45

A.2 CPUボードの寸法図... 46

A.3 ICDボードの寸法図 ... 46

A.4 LCDボードの寸法図 ... 47

A.5 Audioボードの寸法図 ... 48

1 特長

S5U1C33L17T1100(Software eValuation Tool for S1C33L17、以下 SVT33L17)は、SEIKO EPSON 製 MCU S1C33L17 の評

価用ボードです。

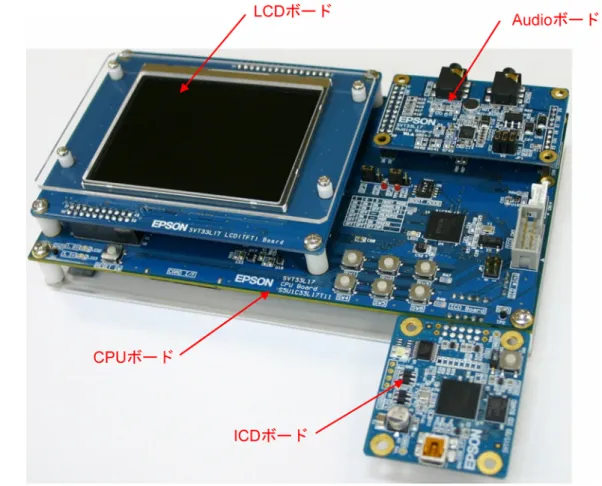

SVT33L17 は、CPU ボード、ICD ボード、LCD ボード、Audio ボードの4つのボードで構成され、ICD ボードと CPU ボー

ドを接続することにより、他の

ICD などのデバッグツールを介すことなくソフトウェアのデバッグを行うことができま

す。また、

LCD ボード、及び Audio ボードを装着して、LCD パネル表示や Audio 入出力の簡易評価を行うことができま

す。

<CPU ボード>

CPU S1C33L17

入力電源電圧

+5.0V ±5% DC

レギュレータ出力電圧 +3.3V

DC(I/O)、+1.8V DC(CPU Core)

CPU 入力クロック OSC1:32.768kHz(リアルタイムクロック用)

OSC3:48MHz

搭載機能/デバイス

• NOR Flash (64Mbit)

• SDRAM

(128Mbit)

• NAND Flash (2Gbit)

• Serial Flash (8Mbit)

• MMC カードソケット

• USBminiB コネクタ

• UART(RS-232C)コネクタ

• キースイッチ(6 キー)

• 拡張インターフェース(LCD ボード)コネクタ

• 拡張インターフェース(Audio ボード)コネクタ

• 外部拡張コネクタ(未実装)

• ICD ボードコネクタ

• ICD33 コネクタ

• ICDmini コネクタ

• BOOT

MODE 設定スイッチ

• リセットスイッチ

• 電源スイッチ

<ICD ボード>

PC とのインターフェース USB

1.1

電源電圧 USB バスパワー(オンボードレギュレータ出力電圧 3.3V)

搭載機能

/デバイス

• ステータス表示 LED(3 色発光)

• リセットスイッチ

• CPU ボードコネクタ

<LCD ボード>

搭載機能/デバイス

• 3.5inch TFT QVGA 320(xRGB)×240 ドットパネル

• LED バックライト

• バックライト駆動用 DC コンバータ

<Audio ボード>

搭載機能

/デバイス

• Audio IC(CS42L51 CIRRUS LOGIC)

• Audio 入力ジャック

• Audio 出力ジャック

• マイク

2 パッケージ構成品

S5U1C33L17T1100 パッケージ構成品を以下に示します。

(1) SVT33L17

CPU ボード(本体) ... 1

(2) SVT33L17

ICD ボード... 1

(3) SVT33L17

LCD ボード... 1

(4) SVT33L17

Audio ボード... 1

(5) USB ケーブル(A-miniB コネクタ) ... 1

(6) AC アダプタ ... 1

(7) 保証書 ... 和/英各 1

(8) ご使用上の注意... 和/英各 1

(9) マニュアルダウンロードのご案内 ... 和/英各 1

3 各部の名称と機能

各部の名称と機能は以下のとおりです。

3.1 各部の名称

3.1.1

全体の外観

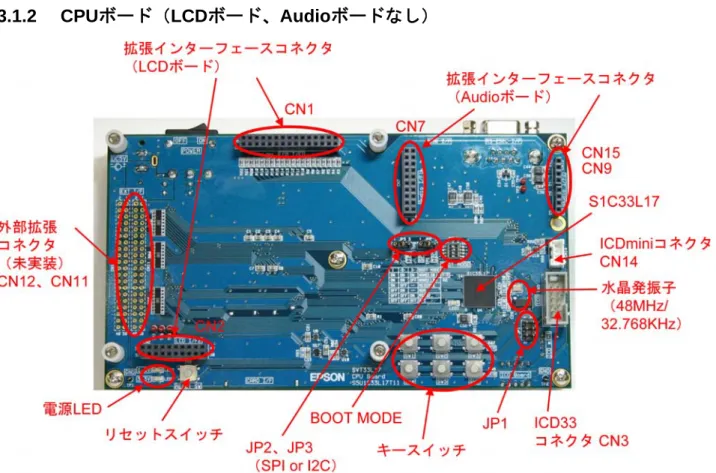

3.1.2 CPUボード(LCDボード、Audioボードなし)

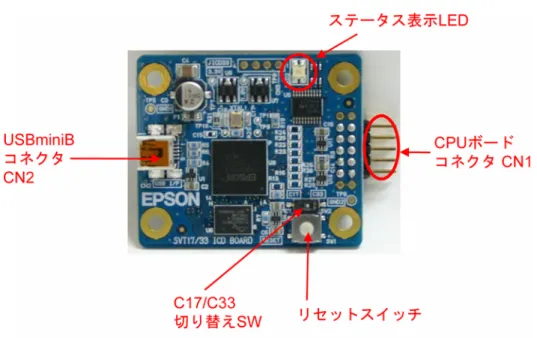

3.1.3 ICDボード

図 3.4 ICD ボード表面各部の名称

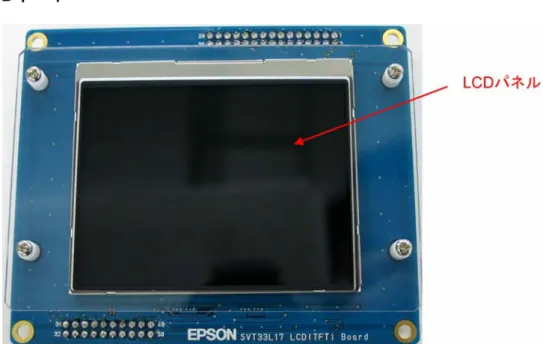

3.1.4 LCDボード

図 3.6 LCD ボード表面各部の名称

3.1.5 Audioボード

図 3.8 Audio ボード表面各部の名称

3.2 ジャンパー、ディップスイッチの機能と設定

3.2.1 CPUボード

3.2.1.1 JP1 の機能と設定

JP1 は CPU の DST0,DST1,DPCO 信号をマルチファンクション機能で LCD ボードコントロール信号として使用する場合

に接続してください。この場合、

DST0,DST1,DPCO 信号はデバッグに使用できなくなります。

通常は

JP1 を OPEN で使用します。(出荷時、OPEN です。)

表 3.1 JP1 の設定 JP1 状態 全端子 Open 状態 (出荷時) DST0, DST1,DPCO 信号は ICD33 によるデバッグ端子として 使用可能です。 全端子 Short 状態 TFT_CTL0,2,3 端子として使用できます。 DST0, DST1,DPCO と重複するので ICD33 との接続はできま せん。3.2.1.2 JP2、JP3 の機能と設定

JP2,JP3 は Audio ボードの制御信号として SPI を使用するか I2C を使用するかを選択します。

出荷時は

SPI 側に接続されています。

表 3.2 JP2、JP3 の設定 JP2、JP3 状態 SPI 選択 (出荷時) SPI 機能(P65,P66,P67)を使用 I2C 選択 I2C 機能(P41,P50)を使用※

付属の Audio ボードは SPI でご使用ください。

SPI

I2C

SPI

I2C

SPI I2C SPI I2C

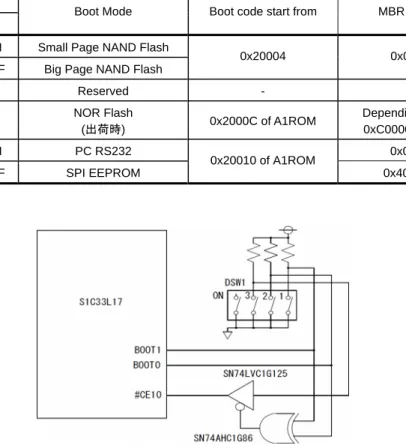

3.2.1.3

ディップスイッチ(DSW1)の機能と設定

DSW1 は CPU(S1C33L17)の BOOT MODE を設定します。

スイッチの設定により以下のような

BOOT MODE が選択できます。

出荷時の

BOOT MODE は NOR Flash に設定されています。

表 3.3 DSW1 の設定 SW1

1 2 3

Boot Mode Boot code start from MBR Execute from ON ON ON Small Page NAND Flash

ON ON OFF Big Page NAND Flash

0x20004 0x0 of A0RAM

ON OFF -- Reserved - -

OFF ON -- NOR Flash

(出荷時) 0x2000C of A1ROM

Depending on Content in 0xC00000 of NOR Flash

OFF OFF ON PC RS232 0x0 of A0RAM

OFF OFF OFF SPI EEPROM

0x20010 of A1ROM

0x400 of A0RAM

3.2.2 Audioボード

3.2.2.1 JP1 の機能と設定

JP1 は I2S インターフェースの SCKI、WSI、MCLKI を接続するかどうかを選択します。

接続することにより

Audio IC より CPU に Audio データを入力することができるようになります。

回路上、SCKO、WSO、MCLKO (CPU からの出力)と接続されることとなりますので、ソフトウェア上での対応が必要

です。出荷時は接続状態です。

表 3.4 JP1 の設定 JP1 状態 全端子 Open 状態 CPU からはデータ出力のみです。 全端子 Short 状態 (出荷時) SCKI、WSI、MCLKI がそれぞれ SCKO、WSO、MCLKO と接 続されます。 データを CPU に転送することができます。3.3 主要部品

表 3.5 CPU ボード主要部品

品名 ロケーション 型名 メーカー名

CPU U4 S1C33L17 SEIKO EPSON CORP.

水晶振動子(48MHz) Y1 FA-238 EPSON TOYOCOM CORP.

水晶振動子(32.768kHz) Y2 MC-306 EPSON TOYOCOM CORP.

SDRAM U2 MT48LC8M16A2P MICRON

NOR Flash U1 SST39VF6401B-70-4I SST

NAND Flash U6 K9F2G08U0A-PCB0 SAMSUNG

Serial Flash U11 M45PE80-VMP6G ST-Micro

RS-232C ドライバ U12 SP3220EBEY Sipex

電源 SW SW7 D501J12S2AHQF C&K

リセットスイッチ(RESET SW) SW8 SKRAAKE010 ALPS

拡張コネクタ(LCD ボード) CN1 SSW-115-01-G-D SAMTEC 拡張コネクタ(LCD ボード) CN2 SSW-110-01-G-D SAMTEC 拡張コネクタ(Audio ボード) CN7 SSW-110-01-G-D SAMTEC 拡張コネクタ(Audio ボード) CN9,CN15 SSW-104-01-G-S SAMTEC ICD ボードコネクタ CN6 PS-10SD-D4T1-1 JAE ICD33 コネクタ CN3 7610-6002PL 3M ICDmini 電源コネクタ CN14 B04B-PASK-1(LF)(SN) JST

ICDmini コネクタ CN13 A2-4PA-2.54DS(71) HIROSE

UART(RS-232C DSUB)コネクタ CN4 DELC-J9SAF-23L9E JAE

MMC カードコネクタ CN5 DM1B-DSF-PEJ(82) HIROSE

電源 DC ジャック CN8 PJ-037AH CUI

USBminiB コネクタ CN10 54819-0572 molex

キースイッチ SW1-SW6 SKRAAKE010 ALPS

電源 LED(緑) (1.8V,3.3V) LED2,LED3 SML-210PT ROHM

表 3.6 ICD ボード主要部品

品名 ロケーション 型名 メーカー名

USBminiB コネクタ CN2 54819-0572 molex

LED(RGB) LED2 598-9920-307F Dialight

リセットスイッチ(RESET SW) SW1 SKRAAKE010 ALPS

デバッグ用コネクタ CN1 9-103801-0 Tyco

表 3.7 LCD ボード主要部品

品名 ロケーション 型名 メーカー名

LCD パネル - L5S30739 EPSON IMAGING DEVICES

コネクタ(CPU ボード接続用) CN1 TSW-115-26-G-D SAMTEC コネクタ(CPU ボード接続用) CN2 TSW-110-26-G-D SAMTEC

コネクタ(LCD パネル接続用) LCD1 FH12A-40S-0.5SH(55) HIROSE

電源 IC U4,U5 MIC3289-16YD6 MICREL

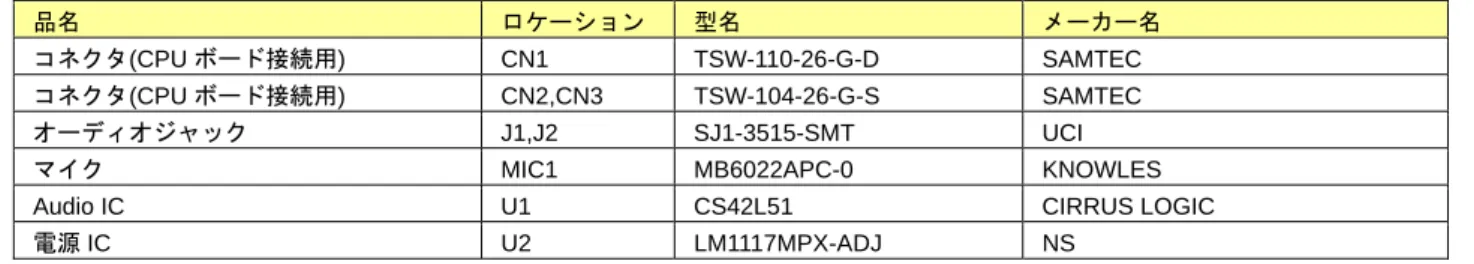

表 3.8 Audio ボード主要部品

品名 ロケーション 型名 メーカー名

コネクタ(CPU ボード接続用) CN1 TSW-110-26-G-D SAMTEC

コネクタ(CPU ボード接続用) CN2,CN3 TSW-104-26-G-S SAMTEC

オーディオジャック J1,J2 SJ1-3515-SMT UCI

マイク MIC1 MB6022APC-0 KNOWLES

Audio IC U1 CS42L51 CIRRUS LOGIC

電源 IC U2 LM1117MPX-ADJ NS

表 3.9 その他部品

品名 ロケーション 型名 メーカー名

3.4 各部の機能

3.4.1 ICDボード

ICD ボードは、S1C33L17 のソフトウェア開発を効率よく行うためのハードウェアツール(エミュレータ)です。PC と、

CPU ボード上のターゲット IC(S1C33L17)間の通信を制御し、S1C33L17 の簡易ソフトウェア開発環境を提供します。

S1C33 コア製品機種すべてに対応する開発ツール ICD33(S5U1C33001H)との機能的な違いについては、6 章を参照くださ

い。

※

図 3.11 の C17/C33 切り替えスイッチ(SW2)は、C33 側(シルクに「C33」と記載のある側。)固定でご使用くださ

い。C17 側に切り替えると動作できませんのでご注意ください。

図 3.11 C17/C33 切り替えスイッチICD ボードリセットスイッチ

ICD ボードリセットスイッチ(SW1)を押すと、ICD ボード上のファームウェアが再起動し、ターゲットリセット信号

(XRESET_OUT)が CPU ボードに対して出力されます。CPU ボードと ICD ボードがハード的に接続されている場合は、

通信接続が完了します。

CPU ボードと ICD ボードがハード的に接続されていない場合は、通信接続待ち状態となります。

ICD ボード LED

この

LED は、ICD ボードとターゲットの状態を色別に示します。

●

(青)

電源オン(ターゲットと初期接続が確立する前)

●

(緑) ターゲットがデバッグモード中

●

(赤)

ターゲットが接続されていない、または正しく接続されていない

ターゲットがユーザプログラムを実行中

C17/C33 切り替えスイッチ

(SW2)

3.4.2 CPUボード

CPU ボードは、ターゲット CPU(S1C33L17)を搭載した簡易ターゲット評価ボードです。周辺機器として、各種メモ

リ

(SDRAM、NAND FLASH、NOR FLASH、SERIAL FLASH)、UART(RS-232C)、MMC カード、USB などの各周辺機能

や回路が搭載されており、これらの制御ソフトウェアの開発、評価に使用することができます。また、同梱される

LCD

ボードや

Audio ボードと接続可能な拡張インターフェースコネクタも搭載しており、パネル表示や音声入出力の制御ソ

フトウェア開発、評価に使用することができます。

3.4.2.1

電源

本ボードの電源は電源コネクタ(CN8)に外部から 5V を供給します。(付属の AC アダプタをお使い下さい。)

また、USB 端子からの電源供給も可能です。(USB から電源を供給する場合、消費電流にご注意ください。)

基板内部のレギュレータにより

3.3V と 1.8V を作り I/O 等周辺回路に 3.3V を、CPU の Core に 1.8V を供給しています。

(周辺の

I/O インターフェース電圧は 3.3V です。)電源スイッチ(SW7)を ON にすると電源モニタ用の LED(1.8V、3.3V)

が点灯します。

3.4.2.2 CPUクロック

CPU クロックは OSC3 用に 48MHz、OSC1 用(リアルタイムクロック)に 32.768KHz の水晶発振子を搭載しています。

3.4.2.3 CPUボードリセットスイッチ

CPU ボードリセットスイッチ(SW6)を押すと、CPU ボードがリセットされます。

3.4.3 LCDボード

LCD ボードは、CPU ボードの LCD ボードインターフェースコネクタに接続して使用します。LCD ボード上には、LCD

パネル

(L5S30739 EPSON IMAGING DEVICES)が搭載されており、LCD パネルへの表示評価が可能です。

LCD パネルは 320(×RGB)×240dots の表示と LED バックライトを備えた汎用 TFT パネルです。

CPU(S1C33L17)内蔵の LCD コントローラと SPI シリアル通信により制御することで画像表示の簡易評価を

行うことが出来ます。

LCD パネル L5S30739 の主な仕様を示します。

• Dot 数:960(320×RGB)×240

• Dot

pitch:0.074×0.222mm

• MPU Serial I/F:SPI

• RGB

I/F:18bit(RED 6bit,GREEN 6bit,BLUE 6bit) or 16bit(RED 5bit,GREEN 6bit,BLUE 5bit)

• DCKcycle:8.25MHz(TYP) HSYNC 周期:512CLK VSYNC 周期:263H

• Backlight:6 LED

3.4.4 Audioボード

Audio ボードは、CPU ボードの Audio ボードインターフェースコネクタに接続して使用します。Audio ボード上には、

AudioIC(CS42L51 CIRRUS LOGIC)と、マイク、及びオーディオジャック(入出力用)が搭載されいます。CPU(S1C33L17)

は、内蔵の

I2S モジュールを使用して PCM データを I2S フォーマットで入出力できるため、Audio ボード上の AudioIC

を通して容易に音声入出力の機能評価を行うことが可能です。

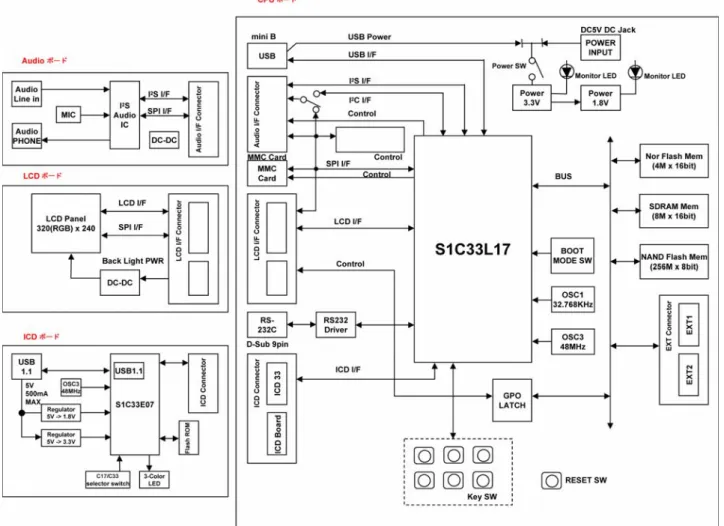

4 ブロック図

SVT33L17 の全体のブロック図は以下のとおりです。

(

CPU ボード、ICD ボード、LCD ボード、Audio ボードを表します。)

5 動作環境と起動手順

SVT33L17 では ICD ボードを介して PC に接続することで、PC 上のデバッガで実行したコマンドに従って動作可能です。

また、

ICD ボードや PC を使用せずに、CPU ボードを単独で動作させることもできます。以下、それぞれの動作を行う

ための接続や起動方法について説明します。

5.1 ソフトウェア簡易開発環境

SVT33L17 は ICD ボードを介して PC に接続し、PC 上の S1C33 開発ツール(S5U1C33001C パッケージに含まれる GNU33

IDE、コンパイラ、デバッガなど)と共に使用することで、CPU ボードをターゲットとする S1C33L17 ソフトウェアの簡

易開発環境を提供します。

図 5.1 ソフトウェア簡易開発環境ソフトウェア簡易開発環境下の動作

この動作環境の場合、ターゲット

CPU(S1C33L17)は、ICD ボードと接続された PC 上のデバッガで実行するコマンドに

従って動作します。デバッガで実行したコマンドは

USB 経由で ICD ボードに送られ、そこで解析された後に S1C33L17

のデバッグ信号に変換されて

CPU ボードに送られます。PC 上のデバッガからプログラムやデータを CPU ボードにダウ

ンロードしたり、プログラムの実行や停止を制御して、デバッグを行うことができます。

CPU の動作モード

ターゲット

CPU(S1C33L17)は、brk 命令や ICD ボードからのデバッグ割り込み(デバッガ上での強制ブレーク操作など)

によりターゲットプログラムの実行を中断してデバッグモード(ブレーク状態)になります。この状態で、PC 上のデバッ

ガからコマンドを実行することができます。デバッグモード時は、

ICD ボードの LED が緑に点灯します。一方、ターゲッ

ト

CPU がターゲットプログラムを実行している状態をノーマルモードといいます。ノーマルモードでは、ICD ボードの

LED が赤く点灯します。

接続と起動

ソフトウェア簡易開発環境を実現するための接続と起動方法を以下に示します。

(1) ICD ボードと CPU ボードを接続します。10 ピンコネクタ同士を接続します。

(2) PC の電源をオンします。(オフの場合のみ)

(3) CPU ボードの電源をオンし、ICD ボードと PC を USB ケーブルで接続します。

(4) PC 上に USB ドライバのインストール画面が現れますので、適切なドライバをインストールします。(この操作は最

初の接続時にのみ必要です。2 回目以降の接続時は不要です。)インストール方法は、後述の“USB ドライバのイン

ストール

”を参照してください。

(5) ICD ボードの LED が青→緑(ターゲットがデバッグモード)となることを確認します。

(6) PC 上でデバッガを起動し、プログラムを実行させます。プログラム実行中に ICD ボードの LED が赤(ターゲット

がノーマルモード

)になることを確認します。

デバッガの操作方法やデバッグコマンドの詳細については、

「S5U1C33001C Manual (S1C33 Family C/C++コンパイラパッ

ケージ)」を参照してください。

注

:デバッガが動作中は、絶対に PC~ICD ボード間の USB ケーブルを抜かないでください。

USB ドライバのインストール

(2) ウィザードに従って USB ドライバをインストールしてください。

USB ドライバの参照ディレクトリには、“C:¥EPSON¥GNU33¥utility¥drv_usb¥Icd33v60”を指定してください。

※ 上記のパスは、IDE がインストールされているパスを指定します。

USB ドライバのインストールが正常に終了すると、デバイスマネージャに以下のように表示されます。

5.2 SVT33L17 の単独動作

SVT33L17 では、ICD ボードや PC を使用せずに CPU ボード単体で動作させることができます。

単独動作

この動作環境の場合、CPU ボード上の S1C33L17 はノーマルモードで動作し、ボード上に搭載されている Flash メモリ

などに書き込まれたプログラムを実行します。このため、

CPU ボード上に搭載されている Flash メモリなどにあらかじ

めユーザプログラムをダウンロードしておく必要があります。

(SVT33L17 は Flash メモリにデモプログラムを書き込んだ状態で出荷されます。)

メモリへのユーザプログラムのダウンロード方法については、「

S5U1C33001C Manual (S1C33Family C/C++コンパイラ

パッケージ

)」を参照してください。

接続と起動

SVT33L17 を単独動作させる方法を以下に示します。

(1) PC の電源をオンします。(オフの場合のみ)

(2) ICD ボードと CPU ボードを接続した状態で、PC と ICD ボードを USB ケーブルで接続し、CPU ボードの電源をオ

ンします。

(3) PC 上のデバッガを起動し、メモリにユーザプログラムをダウンロードします。プログラムのダウンロード方法に

ついては、「S5U1C33001C Manual (S1C33 Family C/C++コンパイラパッケージ)」を参照してください。

(4) デバッガを終了後、CPU ボードの電源を切り、USB ケーブルと ICD ボードを取り外します。

(5) CPU ボードの電源を再投入すると CPU ボード上の S1C33L17 は、Flash メモリにダウンロードされたユーザプログ

ラムの実行を開始します。

5.3 ICDボードファームウエアアップデート手順

SVT33L17 は、PC 上のデバッガを使用して ICD ボードのファームウェアをアップデートすることができます。ICD ボー

ドのファームウェアは、必要に応じて弊社より提供いたします。

(アップデート用ファイルの拡張子は“.sa”です。)

以下にファームウェアをアップデートする手順を示します。

注

:

ファームウェアのアップデート作業は、

USB

ドライバをインストールした後で行ってください。

(1) ICD ボードと CPU ボードを接続した状態で、CPU ボードの電源をオンします。

PC と ICD ボードを USB ケーブルで接続します。

(2) ICD ボードの RESET スイッチ(SW1)を押します。

(3) デバッガをコマンドプロンプトから起動します。

>cd c:¥EPSON¥gnu33 (gnu33 ツールがインストールされているパスを指定します。)

>gdb

(4) デバッガが起動したら、以下のコマンドを入力してください。

(gdb) target icd6 usb

(gdb) c33 firmupdate path¥filename.sa

(“path¥filename.sa”にはアップデートするファイル名を指定します。)

(5) ICD ボードの LED が緑(

●

)に点灯すれば完了です。

6 ICD ボードと ICD33 の相違点

S1C33 Family 用の開発ツール S5U1C33001H(ICD33)と SVT33L17 ICD ボードとの仕様上の比較を表 6.1 に示します。なお、

SVT33L17 では、ICD33 インターフェースも実装されておりますが、ICD ボードと ICD33 を同時に接続することはでき

ません。ICD33 のご使用に関しては、S5U1C33001H1400 マニュアルを参照ください。

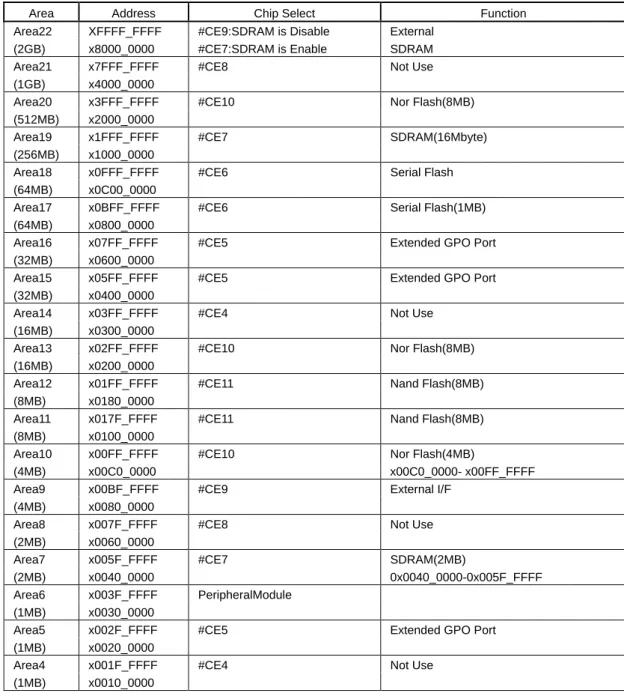

表 6.1 ICD ボードと ICD33 の機能比較 製品名 S5U1C33001H1400 (ICD33V6) S5U1C33L17T1100(SVT33L17) ICD ボード 対応コア S1C33 コア ホストインターフェース USB1.1 データダウンロード最大速度 約 27KB/s DCLK=12MHz 時 *1*3 約 21KB/s DCLK=12MHz 時 *1 *3 ターゲットとの通信周波数 (DCLK 周波数) 4kHz~40MHz 単体フラッシュライタ機能 あり なし ファームウエアアップデート機能 あり Flash 書き込み用電源供給 あり なし トレース機能 あり なし 実行サイクル計測機能 あり なし ターゲットへのリセット信号出力 あり ターゲットシステム I/O 対応電圧 3.3V, 1.8V,ターゲットから 入力した電圧(1.0~5.0V) 3.3V ターゲット接続用コネクタ 10 ピン、4 ピン *4 10 ピン *2 *4 *1 I/O インターフェース電圧=3.3V 時の対応周波数です。周辺ノイズ、温度条件、製品の種類やばらつき等によって上限周波数がス ペック値より低くなる場合があります。 *2 CPU ボード以外には接続しないでください。 *3 SVT33L17 では、動作周波数 48MHz(DCLK=12MHz)です。 *4 ICD33 の 10 ピンコネクタと、ICD ボードの 10 ピンコネクタは、ピン配置、形状など異なりますのでご注意ください. (ICD ボードのコネクタ形状、ピン配置は 14.1.1 章を参照ください。)7 搭載メモリー

CPU ボードは以下のメモリーを搭載しています。

NOR Flash

SST39VF6401B-70-4I(SST)(64Mbit)

SDRAM

MT48LC8M16A2P (MICRON) (128Mbit)

NAND Flash

K9F2G08U0A-PCBO (Samsung) (2Gbit)

Serial Flash

M45PE80-VMP6G (ST) (8Mbit)

以下にメモリーマップを示します。

表 7.1 メモリーマップ

Area Address Chip Select Function

Area22 XFFFF_FFFF #CE9:SDRAM is Disable External

(2GB) x8000_0000 #CE7:SDRAM is Enable SDRAM

Area21 x7FFF_FFFF #CE8 Not Use

(1GB) x4000_0000

Area20 x3FFF_FFFF #CE10 Nor Flash(8MB)

(512MB) x2000_0000

Area19 x1FFF_FFFF #CE7 SDRAM(16Mbyte)

(256MB) x1000_0000

Area18 x0FFF_FFFF #CE6 Serial Flash

(64MB) x0C00_0000

Area17 x0BFF_FFFF #CE6 Serial Flash(1MB)

(64MB) x0800_0000

Area16 x07FF_FFFF #CE5 Extended GPO Port

(32MB) x0600_0000

Area15 x05FF_FFFF #CE5 Extended GPO Port

(32MB) x0400_0000

Area14 x03FF_FFFF #CE4 Not Use

(16MB) x0300_0000

Area13 x02FF_FFFF #CE10 Nor Flash(8MB)

(16MB) x0200_0000

Area12 x01FF_FFFF #CE11 Nand Flash(8MB)

(8MB) x0180_0000

Area11 x017F_FFFF #CE11 Nand Flash(8MB)

(8MB) x0100_0000

Area10 x00FF_FFFF #CE10 Nor Flash(4MB)

(4MB) x00C0_0000 x00C0_0000- x00FF_FFFF

Area9 x00BF_FFFF #CE9 External I/F

(4MB) x0080_0000

Area8 x007F_FFFF #CE8 Not Use

(2MB) x0060_0000

Area7 x005F_FFFF #CE7 SDRAM(2MB)

(2MB) x0040_0000 0x0040_0000-0x005F_FFFF

Area6 x003F_FFFF PeripheralModule (1MB) x0030_0000

Area5 x002F_FFFF #CE5 Extended GPO Port

(1MB) x0020_0000

Area4 x001F_FFFF #CE4 Not Use

7.1 NOR

Flash回路

SST39VF6401B-70-4I(SST)(64Mbit)

図 7.1 NOR Falsh 回路図

7.2 SDRAM回路

7.3 NAND Flash回路

K9F2G08U0A-PCB0 (Samsung) (2Gbit)

図 7.3 NAND Flash 回路図

7.4 Serial

Flash回路

M45PE80-VMP6G (ST) (8Mbit)

8 CPU のキー入力回路

SVT33L17 は CPU ボード上に 6 個のキースイッチを搭載しています。

キーマトリックスとして

CPU のポートからキーの状態を読み取ります。

キースイッチの回路を示します。

9 MMC カードインターフェース回路

SVT33L17 は CPU ボード上に MMC カードとのインターフェースを搭載しています。

CPU と MMC カードは SPI インターフェースで通信を行います。

MMC カード周辺の回路を示します。

10 UART(RS-232C)インターフェース回路

SVT33L17 は CPU ボード上に RS-232C インターフェースを搭載しています。

PC との接続にはストレートケーブルをご使用ください。

RS-232C インターフェース周辺の回路を示します。

11 USB インターフェース回路

SVT33L17 は CPU ボード上に USB インターフェースを搭載しています。

USB インターフェース周辺の回路を示します。

CPU ボードの電源は USB コネクタからも供給可能です。

(USB から供給可能な電流値にご注意ください。)

CPU(S1C33L17)は FS(12Mbps)の転送モードに対応しています。

図 11.1 USB インターフェース回路図12 LCD 回路

LCD 機能の回路構成を示します。

13 Audio 回路

Audio 機能の回路図を示します。

14 拡張インターフェースコネクタ

14.1 CPUボード

14.1.1 デバッグ用コネクタ

本ボードは

ICD ボード、ICD33、ICDmini の接続用コネクタを持っています。

デバッグ方法等は

“S5U1C33001C Manual (S1C33 Family C/C++コンパイラパッケージ)”を参照してください。

表 14.1 ICD ボード インターフェース ICD ボードインターフェース(CN6) メーカ: JAE 型番: PS-10SD-D4T1-1(メス) (ICD ボード側) メーカ: Tyco Electronics 型番: 9-103801-0(オス)

No. Name I/O 機能

1 DCLK O オンチップデバッガクロック出力ポート 2 GND - 電源グランド(全端子とも接続することを推奨) 3 GND - 電源グランド(全端子とも接続することを推奨) 4 XRESET I ターゲットリセット信号入力ポート 5 DSIO I/O オンチップデバッガデータ入出力ポート 6 TGT_EN - N.C(ターゲットイネーブル信号) 7 DST2 O オンチップデバッガステータス信号出力ポート 8 N.C - N.C 9 VCC - N.C 10 VCC - N.C ※ このコネクタを逆差しすると、双方のボードが破損してしまうことがありますのでご注意ください。CPU ボードと ICD ボードを 接続した状態の図は、3 章を参照ください。(ICD ボードのリセットスイッチが表面となるように接続してください。) <CPU ボード上側側面図>

1

2

9

10

<ICD ボード側面図>1

2

9

10

表 14.2 ICD33 インターフェース

ICD33 インターフェース(CN3)

メーカ: 3M

型番: 7610-6002PL

No. Name I/O 機能

1 DCLK O オンチップデバッガクロック出力ポート 2 GND - 電源グランド(全端子とも接続することを推奨) 3 DSIO I/O オンチップデバッガデータ入出力ポート 4 GND - 電源グランド(全端子とも接続することを推奨) 5 DST2 O オンチップデバッガステータス信号出力ポート 6 GND - 電源グランド(全端子とも接続することを推奨) 7 DST1 O オンチップデバッガ用信号出力ポート 8 GND - 電源グランド(全端子とも接続することを推奨) 9 DST0 O オンチップデバッガ用信号出力ポート 10 DPCO O オンチップデバッガ用信号出力ポート ※ DST0、DST1、DPCO 信号は JP1 を通して LCD 用コネクタ(CN2)に接続されています。本信号を LCD コントロールとして使用 した場合は、ICD33 によるデバッグはできませんのでご注意ください。 <CPU ボード(表面)コネクタ>

表 14.3 ICDmini インターフェース ICDmini インターフェース(CN13,CN14) CN13 メーカ: HIROSE 型番: A2-4PA-2.54DS(71) CN14 メーカ: JST 型番: B04B-PASK-1(LF)(SN) CN13

No. Name I/O 機能

1 DCLK O オンチップデバッガクロック出力ポート

2 GND - 電源グランド

3 DSIO I/O オンチップデバッガデータ入出力ポート

4 DST2 O オンチップデバッガステータス信号出力ポート

CN14

No. Name I/O 機能

1 N.C - - 2 GND - 電源グランド 3 XRESET I ターゲットリセット信号入力ポート 4 VCC (+3.3V) -I +3.3V 電源端子 ※ ICD33 に対応した ICDmini は 2009 年 1 月現在リリースされていません。 ※ CN13 にケーブルを接続する場合、青色のケーブルが 1 番ピンとなる方向に接続してください。

14.1.2 USBインターフェース

SVT33L17 は USB インターフェースを備えており USBminiB コネクタが搭載されています。

表 14.4 USB インターフェース USB インターフェース(CN10) メーカ: Molex 型番: 54819-0572No. Name I/O 機能

1 VBUS Power USB BUS Power

2 D- I/O D-

<CPU ボード(表面)コネクタ>

<CPU ボード(裏面)コネクタ <CPU ボード(裏面)コネクタ>

14.1.3 MMCインターフェース

SVT33L17 は MMC カードインターフェースを備えており MMC カードコネクタが搭載されています。

SPI により MMC カードの制御を行います。

表 14.5 MMC カードインターフェース MMC カードインターフェース(CN5) メーカ: HIROSE 型番: DM1B-DSF-PEJ(82)No. Name I/O 機能

1 CD/DAT3 O XSCD_CS チップセレクト信号 2 CMD O SPI_SDO シリアルデータ出力 3 GND - 電源グランド 4 VDD - +3.3V 電源供給 5 CLK O SPI_CLK 6 VSS2 - 電源グランド 7 DAT0 I SPI_SDI シリアルデータ入力 8 DAT1 - 抵抗でプルアップ 9 DAT2 - 抵抗でプルアップ 10 nCD I XSDC_CD カード検出信号 11 WP I XSDC_WP ライトプロテクト信号 12 GND - 電源グランド <CPU ボード(裏面)コネクタ>

14.1.4 UART(RS-232C)インターフェース

SVT33L17 は RS-232C インターフェースを備えており D-Sub(9Pin)コネクタが搭載されています。

表 14.6 RS-232C インターフェース RS-232C インターフェース(CN4) メーカ: JAE 型番: DELC-J9SAF-23L9E(メス)No. Name I/O 機能

1 DCD - N.C 2 TxD O シリアルデータ出力 3 RxD I シリアルデータ入力 4 DTR - DSR と接続されています 5 GND - 電源グランド 6 DSR - DTR と接続されています 7 RTS - CTS と接続されています 8 CTS - RTS と接続されています 9 RI - N.C ※ パソコンなどと接続する場合はストレートケーブルをご使用ください。 <CPU ボード(裏面)コネクタ>

14.1.5 LCDボードインターフェース

SVT33L17 の LCD ボードとの接続信号を示します。

CPU(S1C33L17)は 4/8 ビットモノクロ/カラーLCD パネルと 16 ビット汎用 TFT パネルに対応した LCD コントローラを内

蔵しています。本ボードでは対応する

LCD 制御用信号をコネクタに接続しています。

表 14.7 LCD ボードインターフェース LCD ボードインターフェース(CN1,CN2) CN1 メーカ: samtec 型番: SSW-115-01-G-D(メス 30 ピン) CN2 メーカ: samtec 型番: SSW-110-01-G-D(メス 20 ピン) CN1No. Name I/O 機能

1 +5V - 5V 電源端子 LCD ボードに供給します。 2 +3.3V - 3.3V 電源端子 LCD ボードに供給します。 3 FPDAT0 O LCD 表示データ出力 4 FPDAT1 O LCD 表示データ出力 5 FPDAT2 O LCD 表示データ出力 6 GND - 電源グランド(全端子とも接続することを推奨) 7 FPDAT3 O LCD 表示データ出力 8 FPDAT4 O LCD 表示データ出力 9 FPDAT5 O LCD 表示データ出力 10 GND - 電源グランド(全端子とも接続することを推奨) 11 FPDAT6 O LCD 表示データ出力 12 FPDAT7 O LCD 表示データ出力 13 FPDAT8 O LCD 表示データ出力 14 GND - 電源グランド(全端子とも接続することを推奨) 15 FPDAT9 O LCD 表示データ出力 16 FPDAT10 O LCD 表示データ出力 17 FPDAT11 O LCD 表示データ出力 18 GND - 電源グランド(全端子とも接続することを推奨) 19 FPDAT12 O LCD 表示データ出力 20 FPDAT13 O LCD 表示データ出力 21 FPDAT14 O LCD 表示データ出力 22 FPDAT15 O LCD 表示データ出力 23 GND - 電源グランド(全端子とも接続することを推奨) 24 FPFRAME O LCD フレームクロック出力 <CPU ボード(表面)コネクタ>

26 GND - 電源グランド(全端子とも接続することを推奨) 27 FPSHIFT O LCD シフトクロック出力 28 GND - 電源グランド(全端子とも接続することを推奨) 29 FPDRDY O LCD DRDY/MOD 信号出力 30 GND - 電源グランド(全端子とも接続することを推奨) CN2 31 TFT_CTL0 O TFT インターフェース制御信号 ※1 32 TFT_CTL2 O TFT インターフェース制御信号 ※1 33 TFT_CTL3 O TFT インターフェース制御信号 ※1 34 GND - 電源グランド(全端子とも接続することを推奨)

35 SDO O SPI インターフェース SDO 信号

36 SDI I SPI インターフェース SDI 信号

37 SPICLK O SPI インターフェース CLK 信号 38 XLCD_CS O LCD コントローラセレクト信号(汎用ポート出力) 39 XLCD_RST O LCD コントローラリセット信号(汎用ポート出力) 40 LCD_PWR O LCD コントローラ電源制御信号(汎用ポート出力) 41 LCD_BL O LCD コントローラバックライト制御信号(汎用ポート出力) 42 GND - 電源グランド(全端子とも接続することを推奨) 43 GND - 電源グランド(全端子とも接続することを推奨) 44 P70/AIN0 I/O 45 P71/AIN1 I/O 46 - - 47 - - 48 - - 49 - - 50 - - ※1 TFT_CTL0、TFT_CTL2、TFT_CTL3 は JP1 を接続した場合に有効です。この場合 ICD33 のデバッグ用信号と併用となるため ICD33 は使用できません。

14.1.6 Audioボードインターフェース

SVT33L17 の Audio ボードとの接続信号を示します。

CPU(S1C33L17)は PCM データを I2S フォーマットで制御するモジュールを内蔵しています。これを使用してオーディオ

機能を実現できるよう関連する信号をコネクタに接続しています。

表 14.8 Audio ボードインターフェース Audio ボードインターフェース(CN7,CN9,CN15) CN7 メーカ: samtec 型番: SSW-110-01-G-D(メス 20 ピン) CN9 メーカ: samtec 型番: SSW-104-01-G-S(メス 4 ピン) CN15 メーカ: samtec 型番: SSW-104-01-G-S(メス 4 ピン) CN7No. Name I/O 機能

1 GND - 電源グランド(全端子とも接続することを推奨)

2 +3.3V - 3.3V 電源端子 Audio ボードに供給します。

3 GND - 電源グランド(全端子とも接続することを推奨)

4 GND - 電源グランド(全端子とも接続することを推奨)

5 SDO /SCL O SPI SDO /I2C SCL JP3 で切り替えます。

6 SDI /SDA I SPI SDI /I2C SDA JP2 で切り替えます。

7 XCORDEC_CS O Audio IC セレクト信号 8 SPI_SCK O SPI インターフェース CLK 信号 9 GND - 電源グランド(全端子とも接続することを推奨) 10 GND - 電源グランド(全端子とも接続することを推奨) 11 OPEN - N.C 12 XCORDEC_RST O Audio IC リセット信号 13 GND - 電源グランド(全端子とも接続することを推奨)

14 I2S_MCLKO O I2S MCLKO 信号

15 I2S_WSO O I2S WSO 信号

16 GND - 電源グランド(全端子とも接続することを推奨)

17 GND - 電源グランド(全端子とも接続することを推奨)

18 GND - 電源グランド(全端子とも接続することを推奨)

19 I2S_SCKO O I2S SCKO 信号

20 I2S SDO O I2S SDO 信号

CN15 21 GND - 電源グランド(全端子とも接続することを推奨) 22 +3.3V - 3.3V 電源端子 Audio ボードに供給します。 23 +5V - 5V 電源端子 Audio ボードに供給します。 24 GND - 電源グランド(全端子とも接続することを推奨) CN9

25 I2S SDI I I2S SDI 信号

26 I2S_SCKI I I2S SCKI 信号

27 I2S_WSI I I2S WSI 信号

28 I2S_MCLKI I I2S MCLKI 信号

<CPU ボード表面図>

CN7

CN15

14.1.7 外部拡張インターフェース

外部拡張用に以下の信号が外部拡張用コネクタに引き出されています。

ただし、出荷時には外部拡張コネクタは実装されていません。

ボード上のスルーホールは

2.54mm ピッチ 穴径φ1.0 です。

表 14.9 外部拡張インターフェース 外部拡張インターフェース(CN11,CN12) CN11No. Name I/O 機能

1 +3.3V - 3.3V 電源端子 2 +3.3V - 3.3V 電源端子 3 EXT_A0 O アドレスバス 4 EXT_A1 O アドレスバス 5 EXT_A2 O アドレスバス 6 EXT_A3 O アドレスバス 7 EXT_A4 O アドレスバス 8 EXT_A5 O アドレスバス 9 EXT_A6 O アドレスバス 10 EXT_A7 O アドレスバス 11 EXT_A8 O アドレスバス 12 EXT_A9 O アドレスバス 13 EXT_A10 O アドレスバス 14 EXT_A11 O アドレスバス 15 EXT_A12 O アドレスバス 16 EXT_A13 O アドレスバス 17 EXT_A14 O アドレスバス 18 EXT_A15 O アドレスバス 19 EXT_A16 O アドレスバス 20 EXT_A17 O アドレスバス 21 EXT_A18 O アドレスバス 22 EXT_A19 O アドレスバス 23 EXT_A20 O アドレスバス 24 EXT_A21 O アドレスバス 25 EXT_A22 O アドレスバス 26 OPEN - N.C 27 GND - 電源グランド 28 GND - 電源グランド 29 EXT_XRD O リード信号

37 EX_XRST I 外部リセット入力 0:リセット有効 47KΩPullUp 抵抗

38 XNMI I 外部 NMI 入力信号 0:有効 100KΩPullUp 抵抗

39 GND - 電源グランド 40 GND - 電源グランド CN12 1 +3.3V - 3.3V 電源端子 2 +3.3V - 3.3V 電源端子 3 EXT_D0 I/O データバス 4 EXT_D1 I/O データバス 5 EXT_D2 I/O データバス 6 EXT_D3 I/O データバス 7 EXT_D4 I/O データバス 8 EXT_D5 I/O データバス 9 EXT_D6 I/O データバス 10 EXT_D7 I/O データバス 11 GND - 電源グランド 12 GND - 電源グランド 13 EXT_D8 I/O データバス 14 EXT_D9 I/O データバス 15 EXT_D10 I/O データバス 16 EXT_D11 I/O データバス 17 EXT_D12 I/O データバス 18 EXT_D13 I/O データバス 19 EXT_D14 I/O データバス 20 EXT_D15 I/O データバス 21 GND - 電源グランド 22 GND - 電源グランド

23 EXT_SPI_SDI I SPI SDI 信号

24 EXT_SPI_SDO O SPI SDO 信号

25 OPEN - N.C

26 EXT_SPI_CLK O SPI CLK 信号

27 GND - 電源グランド

28 GND - 電源グランド

29 EXT_I2S_MCLKI I I2S MCLKI 信号

30 EXT_I2S_WSI I I2S WSI 信号

31 EXT_I2S_SCKI I I2S SCKI 信号

32 EXT_I2S_SDI I I2S SDI 信号

33 EXT_I2S_MCLKO O I2S MCLKO 信号

34 EXT_I2S_WSO O I2S WSO 信号

35 EXT_I2S_SCKO O I2S SCKO 信号

36 EXT_I2S_SDO O I2S SDO 信号

37 +5V - 5V 電源端子

38 +5V - 5V 電源端子

39 GND - 電源グランド

14.2 LCDボード

SVT33L17 に付属の LCD ボードは LCD パネルとして L5S30739(EPSON IMAGING DEVICES)を搭載しており

16BitRGB(5Bit RED,6Bit GREEN,5Bit Blue) 320(×RGB)×240 Dot の表示が可能です。また、LED タイプのバックライト

を装備しています。

表 14.10 LCD ボードインターフェース LCD ボードインターフェース(CN1,CN2) CN1 メーカ: samtec 型番: TSW-115-26-G-D(オス 30 ピン) CN2 メーカ: samtec 型番: TSW-110-26-G-D(オス 20 ピン) CN1No. Name I/O 機能

1 +5V - 5V 電源端子 2 +3.3V - 3.3V 電源端子 3 FPDAT0 I LCD 表示データ入力 4 FPDAT1 I LCD 表示データ入力 5 FPDAT2 I LCD 表示データ入力 6 GND - 電源グランド(全端子とも接続することを推奨) 7 FPDAT3 I LCD 表示データ入力 8 FPDAT4 I LCD 表示データ入力 9 FPDAT5 I LCD 表示データ入力 10 GND - 電源グランド(全端子とも接続することを推奨) 11 FPDAT6 I LCD 表示データ入力 12 FPDAT7 I LCD 表示データ入力 13 FPDAT8 I LCD 表示データ入力 14 GND - 電源グランド(全端子とも接続することを推奨) 15 FPDAT9 I LCD 表示データ入力 16 FPDAT10 I LCD 表示データ入力 17 FPDAT11 I LCD 表示データ入力 18 GND - 電源グランド(全端子とも接続することを推奨) 19 FPDAT12 I LCD 表示データ入力 20 FPDAT13 I LCD 表示データ入力 21 FPDAT14 I LCD 表示データ入力 22 FPDAT15 I LCD 表示データ入力 23 GND - 電源グランド(全端子とも接続することを推奨) <LCD ボード コネクタ> <LCD ボード コネクタ>

CN2 31 N.C - TFT インターフェース制御信号は使用していません 32 N.C - TFT インターフェース制御信号は使用していません 33 N.C - TFT インターフェース制御信号は使用していません 34 GND - 電源グランド(全端子とも接続することを推奨) 35 SPISDI I SPI インタフェース データ入力信号 36 SPISDO O SPI インタフェース データ出力信号 37 SPICLK I SPI インタフェース CLK 信号 38 XLCD_CS I LCD コントローラセレクト信号 39 XLCD_RST I LCD コントローラリセット信号 0:リセット 40 LCD_PWR I LCD パネル電源を ON/OFF します 1: ON 41 LCD_BL I LCD パネルバックライトを ON/OFF します 1:ON 42 GND - 電源グランド(全端子とも接続することを推奨) 43 GND - 電源グランド(全端子とも接続することを推奨) 44 - - 未使用 45 - - 未使用 46 - - 未使用 47 - - 未使用 48 - - 未使用 49 - - 未使用 50 - - 未使用

14.3 Audioボード

SVT33L17 に付属の Audio ボードは AudioIC として CS42L51(CIRRUS LOGIC)を搭載し LINE IN、LINE OUT、マイク入

力を備えています。

CPU とのデータ転送は I2S インターフェースにより行いまた、SPI インターフェースによりコマン

ド通信を行います。

表 14.11 Audio ボードインターフェース Audio ボードインターフェース(CN1,CN2,CN3) CN2 メーカ : samtec 型番 : TSW-110-26-G-D(オス 20 ピン) CN3 メーカ : samtec 型番 : TSW-104-26-G-S(オス 4 ピン) CN1 メーカ : samtec 型番 : TSW-104-26-G-S(オス 4 ピン) CN2No. Name I/O 機能

1 GND - 電源グランド(全端子とも接続することを推奨)

2 +3.3V - 3.3V 電源端子

3 GND - 電源グランド(全端子とも接続することを推奨)

4 GND - 電源グランド(全端子とも接続することを推奨)

5 DO I AudioIC の SPI SDI に接続されています。

6 N.C - SPI SDO に相当しますが AudioIC からの出力はありません。

7 XCORDEC_CS I AudioIC のチップセレクト信号 8 SPI_SCK I SPI インターフェース CLK 信号 9 GND - 電源グランド(全端子とも接続することを推奨) 10 GND - 電源グランド(全端子とも接続することを推奨) 11 OPEN - N.C 12 XCORDEC_RST O AudioIC リセット信号 0:リセット 13 GND - 電源グランド(全端子とも接続することを推奨)

14 I2S_MCLKO I I2S MCLKO 信号(CPU からの出力)

15 I2S_WSO I I2S WSO 信号(CPU からの出力)

16 GND - 電源グランド(全端子とも接続することを推奨)

17 GND - 電源グランド(全端子とも接続することを推奨)

18 GND - 電源グランド(全端子とも接続することを推奨)

19 I2S_SCKO I I2S SCKO 信号(CPU からの出力)

20 I2S SDO I I2S SDO 信号(CPU からの出力)

CN3 21 GND - 電源グランド(全端子とも接続することを推奨) 22 +3.3V - 3.3V 電源端子 AudioIC の I/O 電源です。 23 +5V - 5V 電源端子 内部で AudioIC 用 2.5V を作ります。 24 GND - 電源グランド(全端子とも接続することを推奨) <Audio ボードコネクタ>

CN3

CN1

CN2

Appendix A 基板寸法図

A.1 外観図(CPUボード/ICDボード/LCDボード/Audioボード)

基板の外観図(CPU ボード/ICD ボード/LCD ボード/Audio ボード)は以下のとおりです。

図 A.1 外観寸法図(全体 表面)

A.2 CPUボードの寸法図

CPU ボードの寸法図は以下のとおりです。

図 A.4 CPU ボード寸法図(表面から見た場合)

A.3 ICDボードの寸法図

ICD ボードの寸法図は以下のとおりです。

A.4 LCDボードの寸法図

LCD ボードの寸法図は以下のとおりです。

A.5 Audioボードの寸法図

Audio ボードの寸法図は以下のとおりです。

RESET SW USB I/F GND1 GND2 3.3V 1.8V OPEN 注意 1.+3V3,+1V8,USBVCC,USB_VBUS,CN2.1-F1は電源ラインなので太くする。 +3.3V,+1.8Vは内層 一点鎖線部分はUSBバスラインなので並走、等長とし 差動特性インピーダンスは90Ωとする。 また、最短で配線し周囲をGNDで他の信号と分離すること。 2.GNDはベタGNDとする。内層と接続するための適当数のビアがあること。 XRESETはGNDでガードする。 また、最短配線とする。 VBUSON C33DCLK XRESET_OUT C33DSIO TGT_EN C33DST2 XRESET LED01_0 LED01_1 LED01_2 USB_DM USB_DP +3V3 USBVCC USBVCC +3V3 +3V3 +1V8 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 R3 0 FET1 2 3 4 5 DD G S D D Q1 RN1104F 3 1 2 R9 120 R2 47K TP3 TH R10 30 C1 0.1uF TP4 TH R11 30 C6 0.1uF R7 470K U5 74LVC244 1 20 2 4 6 8 19 17 15 13 11 18 16 14 12 3 5 7 9 10 OE1 VCC I0 I1 I2 I3 OE2 I4 I5 I6 I7 O0 O1 O2 O3 O4 O5 O6 O7 GND LED2 598-9920-307F 1 2 3 4 G R B AN C8 4.7uF LED1 HBMGFRT825 1 2 3 4 5 6 R G B B G R TP8 PAD C2 0.1uF U3 S-1000N28 1 2 3 4 OUT VDD NC VSS U4 SN74LVC1G97 1 2 3 4 5 6 IN1 GND IN0 Y VCC IN2 U2 SN65240 1 2 3 4 5 6 7 8 GND C GND D GND B GND A U7 S-1170B18UC 1 2 3 4 5 ON VSS NC VIN VOUT SW1 SKRAAKE010 1 2 3 4 + C3 100uF R5 22 C7 0.1uF CN1 PEC36DBAN 1 2 3 4 5 6 7 8 9 10 DCLK GND GND XRESET DSIO TGT_EN DST2 NC VCC VCC C12 4.7uF C10 0.1uF TP5 TH CN2 54819-0572 1 2 3 4 5 6 7 8 9 VBUS D-D+ ID GND FGND FGND FGND FGND TP6 TH R6 22 C11 4.7uF F1 BLM21PG600SN1D F2 BLM21PG600SN1D R4 1.5K TP7 PAD C4 22uF R8 100K C5 0.1uF C9 4.7uF U6 S-1170B33UC 1 2 3 4 5 ON VSS NC VIN VOUT U1 SN74LVC1G125 2 4 1 3 5

JICD33 OPEN PFBGA(180Pin) 一点鎖線内は発振回路なので最短配線、GNDでガード。 実装裏面での他のパターンの横断を行わないこと。 C19-C29,C30-C40はU9用バイパスコンデンサ。 BGA裏面等に最短で配置すること。 最短配線、GNDでガード D6 D6 D10 D5 D7 D2 D14 D15 A21 D14 A20 D4 A12 A15 D1 A9 D0 D3 D13 A18 D2 A17 A3 A5 D9 A8 A6 A19 A16 D8 A2 D11 D10 D3 A7 D4 D7 D11 D8 A10 A11 A14 D1 D12 D15 A13 D12 A4 D13 A22 D5 D9 XRESET LED01_0 LED01_1 LED01_2 TIMER C33DST2 C33DSIO SIO SIO P81 P81 TGT_EN C33DST2 XRESET P10 P30 XRESET_OUT C33DCLK P12 TIMER P31 P13 P32 P14 P11 USB_DM USB_DP VBUSON +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 USB_VBUS +3V3 R21 0 XTAL1 FA-238 1 2 3 4 IN GND OUT GND C18 9pF R28 OPEN C14 0.1uF C15 0.22uF U10 SN74LVC1G97 1 2 3 4 5 6 IN1 GND IN0 Y VCC IN2 R22 OPEN U11 TS5A3159A 1 2 3 4 5 6 NO GND NC COM V+ IN R29 OPEN R15 4.7K TP10 PAD R23 OPEN R14 4.7K R17 4.7K R13 4.7K R12 100K C17 9pF R24 OPEN R25 OPEN E1 D1 C1 A1 B1 D2 C2 A2 B5 A5 C5 D5 B6 A6 C6 D6 E6 B2 C3 D4 D3 C4 F1 G1 A4 A3 B3 B4 F6 H6 H1 G4 E2 H2 E3 H3 H4 E4 H5 E5 F2 G2 F3 G3 F4 G5 F5 G6 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 XCE XOE XWE RY/XBY WP/ACC XRESET NC VSS VSS VCC D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 S1C33E07 E2 F2 E3 F1 G2 F3 G1 G3 H1 H2 J4 J2 H3 D13 D14 C14 C13 B14 B13 A13 B12 D1 D3 E4 E1 L13 K12 J12 K14 K3 M2 M3 N1 N6 M6 N7 M5 N5 P7 L6 L7 M7 L8 M8 N13 M13

K13 L5 N4 K1 L1 K4 J1 J3 K2 P8 P9 P2 P3 M4 M9 P1 P14 A14 A1 P4 D11 D6 D5 D4 N9 N3 E11 E10 E5 J11 J10 J5 K11 K10 K6 K5

M14 N14 L14 M1 L3 L4 L2 P13 P12 L12 N11 P11 M12 N12 N10 M11 M10 P10 L11 L10 A5 B4 C5 A4 B5 B2 A2 A10 C4 B3 A3 E14 C12 D12 E13 F12 E12 F13 F14 G13 G14 G12 H14 H13 H12 J14 J13 C6 A6 C1 C3 C2 D2 B1 B10 C11 A11 A12 B6 C7 A7 B7 C8 A8 D9 B8 D10 A9 C9 B9 C10 B11 D7 N8 N2 E7 E6 F11 F10 H5 H4 K7 G11 G4 P5 P6 L9 D8 F5 F4 H11 H10 K9 K8 G10 G5 E9 E8 P00/SIN0/#DMAACK2 P01/SOUT0/#DMAACK3 P02/#SCLK0/#DMAEND2 P03/#SRDY0/#DMAEND3 P04/SIN1/I2S_SDO P05/SOUT1/I2S_WS P06/#SCLK1/I2S_SCK P07/#SRDY1/I2S_MCLK P10/TM0/SIN0/#DMAEND0 P11/TM1/SOUT0/#DMAEND1 P12/TM2/#SCLK0/#DMAACK0 P13/TM3/#SRDY0/#DMAACK1 P14/TM4/SIN1 P20/SDCKE P21/SDCLK P22/#SDCS P23/#SDRAS/TFT_CTL1 P24/#SDCAS P25/#SDWE P26/DQML P27/DQMH P30/CARD2/#DMAREQ0 P31/CARD3/#DMAREQ1 P32/CARD4/#DMAREQ2 P33/CARD5/#DMAREQ3 P60/SIN2/DCSIO0/EXCL0 P61/SOUT2/DCSIO1/EXCL1 P62/#SCLK2/#ADTRG/CMU_CLK P63/#SRDY2/WDT_CLK/#WDT_NMI P64/#WAIT/EXCL2 P65/SDI/FPDAT8 P66/SDO/FPDAT9 P67/SPICLK/FPDAT10 P70/AIN0 P71/AIN1 P72/AIN2 P73/AIN3 P74/AIN4/EXCL5 P80/FPFRAME P81/FPLINE P82/FPSHIFT P83/FPDRDY/TFT_CTL1/BCLK P84/DCSIO0/FPDAT11 P85/DCSIO1 #RESET #NMI

BOOT0 BOOT1 VCP DSIO/P3

4

DCLK/P35 DST2/P36 DST0/P15/TM5/SOUT1/TFT_CTL0 DST1/P16/DCSIO0/#SCLK1/TFT_CTL3 DPCO/P17/DCSIO1/#SRDY1/TFT_CTL2 MCLKI MCLKO RTCCLK1 RTCCLKO TEST0 BURNIN NC NC NC NC PLL VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

USBDP USBDM USBVBUS PB3/FPDAT11/I2S_MCLK/CARD5 PB2/FPDAT10/I2S_SCK/CARD4 PB1/FPDAT9/I2S_WS/CARD3 PB0/FPDAT8/I2S_SDO/CARD2 PA4/FPDAT11/TFT_CTL3/CARD1 PA3/FPDAT10/TFT_CTL2/CARD0 PA2FPDAT9/TFT_CTL1 PA1/FPDAT8/TFT_CTL0 PA0/TFT_CTL0 P97/FPDAT7 P96/FPDAT6 P95/FPDAT5 P94/FPDAT4 P93/FPDAT3 P92/FPDAT2 P91/FPDAT1 P90/FPDAT0 #RD #WRH/#BSH #WRL #CE11/P56 #CE10/P57 #CE9/P55/CARD0 #CE8/P54/CARD1 #CE7/P53/SDA10 P52/BCLK/#CE6/CMU_CLK #CE5/P51/CARD1 #CE4/P50/CARD0 D15/PC7 D14/PC6 D13/PC5 D12/PC4 D11/PC3 D10/PC2 D9/PC1 D8/PC0 D7 D6 D5 D4 D3 D2 D1 D0 A24/ P40/ EXCL4/ #SDCAS A23/ P41/ EXCL3/ #SDRAS A22/ P42/ FPDAT8 A21/ P43/ FPDAT9 A20/ P44/ FPDAT10 A19/ P45/ FPDAT11 A18/P46/TFT_CTL2 A17/ DQMH A16/ DQML A15 A14 A13 A12 A11/ P47 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0/#BSL VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD PLLVDD AVDD VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH R16 OPEN CN3 PBC36SGAN 1 2 3 4 C13 0.1uF SW2 CHS-01B1 1 2 R26 OPEN C16 0.1uF R19 33 TP9 PAD TP11 PAD R27 OPEN R18 0 R20 1M

BOOT MODE LCD I/F1 LCD I/F2 1 2 3 ON ON ON ON OFF BOOT MODE NAND(SB) NAND(LB) RESERVE NOR RS232 SPI ON ON ON OFF -OFF OFF OFF OFF OFF OFF

ON ICD ICDBoard CARD I/F RS-232C I/F SW1 SW5 SW6 SW3 SW2 SW4 SPI I2C I2C SPI Audio I/F1 Audio I/F2 For Debug For Debug ICD mini クロック部分は最短で配線し他の部分とGNDで分離する。 また、他の配線が横切らないこと。 一点鎖線以内は最短で配線し、他の部分とGNDで分離する。 DCLK,DSIO,DST2の配線長は5cm以内を目標とする。 DCLK、DSIOはそれぞれGNDでガードする。 R33はIC U4端子の近くに配置する。 XRST,XNMIはそれぞれGNDでガードする。 U2用パスコン USBVBUSは電源ライン(パターン幅1mm目標) USBDM,USBDPは差動特性インピーダンス90Ω 等長配線とすること。他の信号とGNDで 分離すること。 配線長が短いこと。 PAD1-8はφ1.5のパッドとし 裏面にあってもよい。 IC U4に近く DSW1の近くにこの表を シルクで記入する。 FPDAT15 FPDAT14 FPDAT13 FPDAT12 FPDAT11 FPDAT10 FPDAT9 FPDAT8 FPDAT7 FPDAT6 FPDAT5 FPDAT4 FPDAT3 FPDAT2 FPDAT1 FPDAT0 FPDAT0 FPDAT2 FPDAT3 FPDAT5 FPDAT6 FPDAT8 FPDAT9 FPDAT11 FPDAT12 FPDAT14 FPDAT15 FPDAT13 FPDAT10 FPDAT7 FPDAT4 FPDAT1 D0 D1 D2 D3 D4 D5 D6 D7 D5 D4 D13 D2 D9 D7 D7 D9 D4 D1 D14 D0 D2 D8 D11 D10 D11 D1 D3 D1 D10 D7 D4 D0 D7 D14 D12 D6 D5 D11 D3 D1 D3 D6 D14 D8 D0 D15 D3 D10 D13 D2 D15 D5 D5 D12 D2 D8 D6 D9 D4 D12 D0 D6 D15 D13 A12 A20 A8 A2 A15 A15 A13 A12 A1 A10 A22 A17 A14 A21 A2 A13 A4 A2 A19 A15 A6 A5 A1 A7 A8 A13 A9 A10

A17 A20 A21

A6 A18 A3 A3 A14 A14 A10 A9 A19 A6 A3 A5 A4 A11 A16 A18 A11 A9 A12 A7 A4 A5 A1 A7 A8 A16 A22 SOUT0 CLE ALE I2S_SDO I2S_WSO I2S_SCKO I2S_MCLKO P14 SDCKE SDCLK XSDCS XSDRAS XSDCAS XSDWE DQML DQMH XSMRD XSMWR XSMWP XCODEC_RST KEYO0 KEYO1 KEYO2 XSDC_CD XSDC_WP SPI_SDO SPI_CLK TP_INT FPFRAME FPLINE FPSHIFT FPDRDY XSDC_CS XCODEC_CS XCE10 DSIO DCL K DST2 DST0 DST1 DPCO USBDP USBDM FPDRDY FPSHIFT FPLINE FPFRAME SPI_SDO XLCD_CS LCD_PWR TP_INT TP_XH TP_YH XRD XBSH XWR XCE11 XCE10 XCE9 SDA10 XCE6 XCE5 I2C_SCL XCE5 XWR TP_XL TP_XH TP_YL TP_YH XLCD_RST XLCD_CS LCD_PWR LCD_BL XCE10 XRD XWR XRST XCE11 XSMRD XSMWR CLE ALE XSMWP XSMRY DQML XSDWE XSDCS XSDRAS SDCKE DQMH XSDCAS SDCLK LCD_BL XCE6 TP_YL SPI_CLK XRST XLCD_RST SPI_SDI SPI_SDO SPI_CLK TP_XL D[0..15] SDA10 DST0 DST1 DPCO SPI_SDI TP_AD0 TP_AD1 DSIO DPCO DST1 DCLK DST0 DST2 XSDC_CD SPI_CLK SPI_SDI XSDC_WP XSDC_CS SPI_SDO SOUT0 SIN0 KEYO0 KEYI0 KEYO1 KEYI1 KEYO2 I2C_SDA SPI_SDO I2S_WSO SPI_SDI I2C_SCL XCODEC_CS XCODEC_RST SIN0 I2S_WSI I2S_SCKI I2S_MCLKI I2S_SDI SPI_SDI TP_AD0 TP_AD1 KEYI0 KEYI1 XRST XNMI USBVBUS P14 FPDAT[0..15] I2S_SDI I2S_WSI I2S_SCKI I2S_MCLKI I2S_MCLKO I2S_SDO SPI_CLK I2C_SDA I2C_SCL I2S_SCKO +1V8 +3V3 +3V3 +5V0 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +3V3 +5V0 +3V3 R21 0 R34 100K R13 0 R9 0 C11 0.1uF C36 0.1uF C22 0.1uF R36 100K C35 47pF R22 0 SW2 SKRAAKE010 1 2 3 4 R49 0 C15 0.1uF R23 100K U13 SN74LVC1G125 2 4 1 3 5 R27 0 R11 0 C1 0.1uF + C52 10uF R20 0 C6 0.1uF R10 0 R38 100K C31 0.1uF R4 0 R12 0 JP3 TP3 TH R61 33 C8 0.1uF SW3 SKRAAKE010 1 2 3 4 + C38 10uF TP4 TH CN7 SSW-110-01-G-D 1 3 5 7 9 11 13 15 17 19 2 4 6 8 10 12 14 16 18 20 GND GND DO XCS GND NC GND WSO GND SCKO 3V GND DI CLK GND XRST MCKO GND GND SDO CN3 7610-6002PL 1 2 3 4 5 6 7 8 9 10 R45 0 R14 0 U12 SP3220E 2 4 5 6 11 9 1 8 13 7 3 16 10 12 15 14 C1+ C1-C2+ C2-T1IN R1OUT EN R1IN T1OUT V-V+ SHDN NC NC VCC GND C12 0.1uF R7 0 R29 0 C4 0.1uF C25 10pF U11 M45PE80 1 2 3 4 8 7 6 5 D C #RESET3 #S Q VSS VCC #W R24 100K CN13 A2-4PA-2.54DS(71) 1 2 3 4 U1 SST39VF6401B 25 24 23 22 21 20 19 18 8 7 6 5 4 3 2 1 45 43 41 39 36 34 32 30 44 42 40 38 35 33 31 29 48 17 16 9 10 13 15 47 46 27 37 14 12 11 28 26 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 DQ15 DQ14 DQ13 DQ12 DQ11 DQ10 DQ9 DQ8 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0 A16 A17 A18 A19 A20 A21 NC NC VSS VSS VDD #WP #RST #WE #OE #CE CN6 PS-10SD-D4T1-1 1 2 3 4 5 6 7 8 9 10 DCLK GND GND XRESET DSIO TGT_EN DST2 NC VCC VCC R15 0 U4 S1C33L17 E2 F2 E3 F1 G2 F3 G1 G3 H1 H2 J4 J2 H3 D13 D14 C14 C13 B14 B13 A13 B12 D1 D3 E4 E1 L13 K12 J12 K14 K3 M2 M3 N1 N6 M6 N7 M5 N5 P7 L6 L7 M7 L8 M8 N13 M13 K13 L5 N4 K1 L1 K4 J1 J3 K2 P8 P9 P2 P3 M4 M9 P1 P14 A14 A1 P4 D1 1 D6 D5 D4 N9 N3 E11 E10 E5 J1 1 J1 0 J5 K11 K10 K6 K5 M14 N14 L14 M1 L3 L4 L2 P13 P12 L12 N11 P11 M12 N12 N10 M11 M10 P10 L11 L10 A5 B4 C5 A4 B5 B2 A2 A10 C4 B3 A3 E14 C12 D12 E13 F12 E12 F13 F14 G13 G14 G12 H14 H13 H12 J14 J13 C6 A6 C1 C3 C2 D2 B1 B10 C1 1 A11 A12 B6 C7 A7 B7 C8 A8 D9 B8 D1 0 A9 C9 B9 C1 0 B11 D7 N8 N2 E7 E6 F11 F10 H5 H4 K7 G1 1 G4 P5 P6 L9 D8 F5 F4 H1 1 H1 0 K9 K8 G1 0 G5 E9 E8 P00/SIN0/#DMAACK2 P01/SOUT0/#DMAACK3 P02/#SCLK0/#DMAEND2 P03/#SRDY0/#DMAEND3 P04/SIN1/I2S_SDO P05/SOUT1/I2S_WS_O/I2S_WS_I P06/#SCLK1/I2S_SCK_O/I2S_SCK_I P07/#SRDY1/I2S_MCLK_O P10/I2S_SDI/SIN0/#DMAEND0 P11/I2S_WS_I/SOUT0/#DMAEND1 P12/I2S_SCK_I/#SCLK0/#DMAACK0 P13/I2S_MCLK_I/#SRDY0/#DMAACK1 P14/TM2/SIN1 P20/SDCKE P21/SDCLK P22/#SDCS P23/#SDRAS/TFT_CTL1 P24/#SDCAS P25/#SDWE P26/DQML P27/DQMH P30/CARD2/#DMAREQ0/FPDAT12 P31/CARD3/#DMAREQ1/FPDAT13 P32/CARD4/#DMAREQ2/FPDAT14 P33/CARD5/#DMAREQ3/FPDAT15 P60/SIN2/FPDAT15/EXCL0 P61/SOUT2/FPDAT14/EXCL1 P62/FPDAT12/#ADTRG/CMU_CLK P63/FPDAT13/WDT_CLK/#WDT_NMI P64/#WAIT/EXCL2 P65/SDI/FPDAT8 P66/SDO/FPDAT9 P67/SPICLK/FPDAT10 P70/AIN0 P71/AIN1 P72/AIN2 P73/AIN3/I2S_MCLK_EXT P74/AIN4/EXCL3 P80/FPFRAME P81/FPLINE P82/FPSHIFT P83/FPDRDY/TFT_CTL1/BCLK P84/TM0/FPDAT11 P85/TM1 #RESET #NMI BOOT 0 BOOT 1 VCP DSIO /P34 DCLK/P35 DST2 /P3 6 DST1/P16/CARD0/#SCLK1/TFT_CTL3 DST0/P15/TM 3/SO UT1/TFT_CTL0 DPCO /P17/CARD1/#SRDY1/TFT_CTL2 MCL K I MCL D O RTCCL KI RTCCL KO TEST0 BURNIN NC NC NC NC PLL VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS USBDP USBDM USBVBUS PB3/FPDAT15/I2S_MCLK/CARD5 PB2/FPDAT14/I2S_SCK/CARD4 PB1/FPDAT13/I2S_WS/CARD3 PB0/FPDAT12/I2S_SDO/CARD2 PA4/FPDAT11/TFT_CTL3/I2S_MCLK_EXT PA3/FPDAT10/TFT_CTL2/I2S_MCLK_I PA2FPDAT9/TFT_CTL1/I2S_SCK_I PA1/FPDAT8/TFT_CTL0/I2S_WS_I PA0/TFT_CTL0//I2S_SDI P97/FPDAT7 P96/FPDAT6 P95/FPDAT5 P94/FPDAT4 P93/FPDAT3 P92/FPDAT2/SPICLK P91/FPDAT1/SDO P90/FPDAT0/SDI #RD #WRH/#BSH #WRL #CE11/P56 #CE10/P57 #CE9/P55/CARD0/FPDAT14 #CE8/P54/CARD1/FPDAT15 #CE7/P53/SDA10 P52/BCLK/#CE6/CMU_CLK #CE5/P51/CARD1 #CE4/P50/CARD0 D15/PC7 D14/PC6 D13/PC5 D12/PC4 D11/PC3 D10/PC2 D9/PC1 D8/PC0 D7 D6 D5 D4 D3 D2 D1 D0 A24/P40/FPD A T12/#SD C A S A23/P41/FPD A T13/#SD R A S A22/P42/FPD A T8 A21/P43/FPD A T9 A20/P44/FPD A T10 A19/P45/FPD A T11 A18/P46/TFT_CTL2 A17/D Q M H A16/D Q M L A15 A14 A13 A12 A11/P47 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0/#BSL VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD PLLVD D AVDD VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH VDDH CN5 DM1B-DSF-PEJ 11 10 4 8 7 6 5 2 1 9 12 3 WP nCD VDD DAT1 DAT0 VSS2 CLK CMD CD/DAT3 DAT2 GND GND + C44 10uF CN9 SSW-104-01 -G-S 25 26 27 28 SDI SCKI WSI MCLKI C21 0.1uF CN15 SSW-104-01 -G-S 21 22 23 24 GND 3V3 5V GND CN4 DSub-9 1 6 2 7 3 8 4 9 5 C28 0.1uF R17 0 C27 10pF C33 0.1uF U8 SN74LVC1G125 2 4 1 3 5 D1 PESDXL2BT 3 2 1 SW5 SKRAAKE010 1 2 3 4 C9 0.1uF R1 0 C2 0.1uF C19 0.1uF R30 1M R25 100K C17 0.1uF C7 0.1uF JP2 U5 SN74AHC1G02 1 2 4 5 3 C13 0.1uF R2 33 C20 0.1uF SW4 SKRAAKE010 1 2 3 4 PAD8 C29 0.1uF PAD1 TP7 R43 0 R35 100K C30 0.1uF TP8 U6 K9F2G08U0M 1 2 3 4 5 6 10 11 14 15 20 21 22 23 24 9 8 18 16 17 19 7 38 29 30 31 32 41 42 43 44 48 47 46 45 40 39 35 34 33 28 27 26 25 12 37 13 36 NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC #CE #RE #WE CLE ALE #WP RY/#BY PRE I/O0 I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 NC NC NC NC NC NC NC NC NC NC NC NC NC VCC VCC VSS VSS R59 220 R60 47K C18 0.1uF R26 100K R28 0 R33 33 R18 0 TP9 C5 0.1uF R37 100K R5 0 U3 74ALVC373A 3 4 7 8 13 14 17 18 11 1 10 20 19 16 15 12 9 6 5 2 D0 D1 D2 D3 D4 D5 D6 D7 LE #OE GND VCC Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 R48 Y2 32.768KHz PAD5 C10 0.1uF TP5 TH C24 10pF PAD2 R31 10M PAD6 U9 SN74AHC1G86 1 2 4 5 3 TP6 TH R69 10K R19 0 PAD3 C14 0.1uF R41 0 PAD7 DSW1 CHS-04B1 1 2 3 4 8 7 6 5 LED1 SML-210PT R6 0 SW1 SKRAAKE010 1 2 3 4 R16 0 C32 0.1uF C39 0.1uF CN1 SSW-115-01-G-D 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 5V0 3V3 DAT0 DAT1 DAT2 GND DAT3 DAT4 DAT5 GND DAT6 DAT7 DAT8 GND DAT9 DAT10 DAT11 GND DAT12 DAT13 DAT14 DAT15 GND FRAM LINE GND SFT GND RDY GND C34 47pF R46 4.7K C37 0.1uF R3 0 C26 10pF U2 MT48LC8M16A2TG 23 24 25 26 29 30 31 32 33 34 22 35 36 20 21 19 38 37 16 17 18 15 39 2 4 5 7 8 10 11 13 42 44 45 47 48 50 51 53 40 1 14 27 3 9 43 49 28 41 54 6 12 46 52 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 NC/A12 BA0 BA1 #CS CLK CKE #WE #CAS #RAS DQML DQMH DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 NC VDD VDD VDD VDDQ VDDQ VDDQ VDDQ VSS VSS VSS VSSQ VSSQ VSSQ VSSQ JP1 WLW-1 -6 Y1 TSX3225 1 3 2 4 R47 4.7K C3 0.1uF SW6 SKRAAKE010 1 2 3 4 R8 0 U10 SN74LVC1G125 2 4 1 3 5 C16 0.1uF CN2 SSW-110-01-G-D 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 CTL0 CTL2 CTL3 GND SDO SDI CLK XCS RST PWR BL GND GND AD0 AD1 INT XL XH YL YH C23 0.1uF PAD4