高知工科大学

修士論文

In-Ga-Zn-O 薄膜トランジスタの

低温形成および特性・信頼性制御

Electrical properties and reliability of low-temperature

processed In-Ga-Zn-O thin-film transistors

平成 29 年 3 月 21 日

工学研究科基盤工学専攻

物質生命システム工学コース

氏名: 辰岡 玄悟

指 導 教 員

古田 守 教授

目次

第 1 章 序論

1.1 はじめに ... 1 1.2 TFT 構造および伝達特性の導出方法 ... 1 1.3 研究背景 ... 3 1.3.1 FPD 応用へ向けた TFT の要求性能 ... 3 1.3.2 フレキシブルディスプレイ実現に向けた課題 ... 3 1.3.3 TFT の種類と特徴 ... 4 1.3.4 IGZO TFT の課題 ... 5 1.4 研究目的 ... 6 1.5 本論文の構成 ... 7 参考文献 ... 8第 2 章 フッ素含有絶縁膜を用いた高性能・高信頼性 IGZO TFT 形成

2.1 高信頼性 IGZO TFT 実現への試み ... 9 2.2 フッ素による欠陥補償メカニズム ... 9 2.3 フッ素含有絶縁膜を用いた TFT 作製プロセス ... 10 2.4 フッ素含有絶縁膜を用いた TFT の特性および信頼性評価 ... 12 2.4.1 TFT 初期特性のポストアニール時間依存性 ... 12 2.4.2 ポジティブゲートバイアス熱ストレス試験による信頼性評価 ... 13 2.5 各種 TFT の膜中フッ素濃度 ... 15 2.6 TFT 特性・信頼性と膜中フッ素濃度の相関関係の考察 ... 17 参考文献 ... 18第 3 章 フッ素含有絶縁膜のエッチングストッパー層(ESL)応用

3.1 エッチングストッパー層(ESL)応用の目的 ... 19 3.2 評価方法・装置概要 ... 193.2.1 Van der Pauw 法概要 ... 19

3.2.2 測定装置構成 ... 21

3.3 SiOx:F 成膜が IGZO に与える影響の評価 ... 22

3.4 TFT の ESL 応用 ... 24

3.5 考察および今後の展望 ... 26

第 4 章 有機絶縁膜を用いた IGZO TFT の低温形成

4.1 フレキシブル TFT への要求 ... 28 4.2 塗布型有機絶縁膜および TFT 構造の選定理由 ... 28 4.3 セルフアライン型・トップゲート(SA-TG)構造 TFT の低温形成 ... 29 4.3.1 SA-TG 構造 IGZO TFT 作製プロセス ... 29 4.3.2 TFT 初期特性および PL 導入の意義 ... 31 4.3.3 大気環境および真空環境下における信頼性評価 ... 32 4.4 大気安定性向上への試み ... 33 4.4.1 パッシベーション層形成 ... 33 4.4.2 層間絶縁層材料の変更 ... 34 4.5 特性・信頼性向上への取り組み ... 35 4.6 今後の展望 ... 38 4.7 フレキシブル IGZO TFT 作製 ... 38 参考文献 ... 40第 5 章 総括と展望

... 41研究業績

... 43謝辞

... 441

第1章

序論

1.1 はじめに

近年の情報化社会の発展において、表現手法の幅を広げることや、より多くの情報を伝達する ことに向けた視聴覚技術の進歩は必要不可欠である。中でも視覚情報は、人間が情報を摂取する 上で特に重要な役割を果たすため、人と情報との繋がりを強めていく上でディスプレイデバイス の技術発展は非常に大きな意味を持つと言える。 現在普及されているディスプレイデバイスには、主に液晶ディスプレイ(LCD: Liquid Crystal Display)や有機 EL(OLED: Organic Light Emitting Diode)ディスプレイ等のフラットパネルディ スプレイ(FPD: Flat Panel Display)が用いられている。これら FPD の駆動には薄膜トランジスタ (TFT: Thin-Film Transistor)と呼ばれる電子デバイスが用いられており、TFT の特性はディスプ レイの表示機能に大きな影響を与える。したがって、ディスプレイの高精細化・大画面化・高効 率化等の改良の背景には TFT 作製技術の発展があり、TFT に用いられている半導体材料に応じ た研究開発が進められてきた。中でも、TFT の半導体活性層に非晶質酸化インジウム・ガリウム・ 亜鉛(In-Ga-Zn-O, IGZO)を用いた IGZO TFT は、従来用いられてきた水素化非晶質シリコン TFT と比較し高い電界効果移動度を有し、スパッタ法による室温形成が可能であることから、高精細 や大画面、フレキシブルディスプレイといった次世代ディスプレイ応用に向けた技術として期待 され活発な研究が行われている[1]。1.2 TFT 構造および伝達特性の導出方法[2]

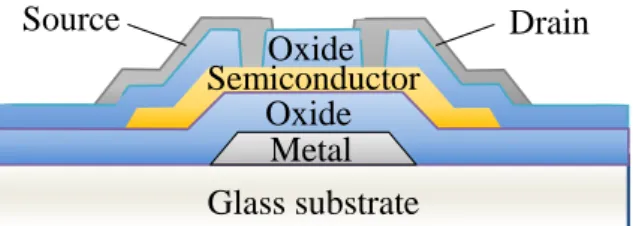

TFT は電界効果トランジスタの一種であり、金属/酸化膜(絶縁体)/半導体(MOS: Metal/Oxide/ Semiconductor)の積層構造によって構成される。それぞれの膜厚がナノスケールによって形成さ れるため、厚みが薄いことから薄膜トランジスタと呼ばれる。また、半導体と金属電極の位置関 係により TFT 構造が大きく分類されるが、本研究グループでは主に図 1.1 に示すようなエッチン グストッパー層を有するボトムゲート構造 TFT を用いている。このような TFT では、半導体層 (チャネル層)は通常時高い絶縁性(オフ状態)を示すが、金属電極(ゲート電極)にゲート電 圧(Vg)を印加することでチャネル層に蓄積層を形成し抵抗率が減少する。その後、ソース・ド レイン(S/D)電極間にドレイン電圧(Vd)を印加することで、ドレイン電流(Id)が指数関数的 に上昇しスイッチング動作(オン状態)を示す。2

図 1.1 エッチングストッパー層を有するボトムゲート構造 TFT の断面模式図

次に、TFT 特性値の算出方法に関して述べる。本研究では主に、電界効果移動度(μFE: Field

Effect mobility)、閾値電圧(Vth: Threshold Voltage)、サブスレッショルドスイング値(S 値)、ヒ

ステリシス(ΔVH)に関して議論を行う。 まず、電界効果移動度に関して導く。Vd<(Vg-Vth)となる領域(線形領域)では Idは Vdと比 例関係にあり、線形領域における線形移動度をμlin.、チャネル幅を W、チャネル長を L、単位面 積あたりのゲート絶縁膜のキャパシタンスを Ciで表すと、線形領域の Idは(1.1)式により与え られる。 𝐼𝑑= 𝜇𝐿𝑖𝑛.𝑊𝐶𝑖 𝐿 [(𝑉𝑔− 𝑉𝑡ℎ)𝑉𝑑− 1 2𝑉𝑑 2] (1.1) 尚、Vdが小さいとき(1.1)式中の Vd2の項は無視できる。(1.1)式とチャネルの相互コンダクタ ンス(gm, (1.2)式)を用いることにより、μlin.は(1.3)式で求められる 𝑔𝑚= 𝛿𝐼𝑑 𝛿𝑉𝑔 = 𝜇𝑙𝑖𝑛. 𝑊 𝐿 𝐶𝑖𝑉𝑑 (1.2) 𝜇𝑙𝑖𝑛. = 𝐿 𝑊 𝑔𝑚 𝐶𝑖𝑉𝑑 (cm2/Vs) (1.3) また、Vd>(Vg-Vth)となる領域(飽和領域)では Idは飽和して Vdによらずほぼ一定の値となる。

この時の Idは(1.4)式で与えられ、飽和移動度 μsat.は(1.6)式で導かれる。尚、μlin.およびμsat.は

Vg依存性を示すが、本研究では最大値を用いた。 𝐼𝑑= 𝜇𝑠𝑎𝑡. 𝑊 2𝐿𝐶𝑖(𝑉𝑔− 𝑉𝑡ℎ) 2 (A) (1.4) 𝛿√𝐼𝑑 𝛿𝑉𝑔 = √𝜇𝑆𝑎𝑡.𝑊𝐶𝑖 2𝐿 (1.5) 𝜇𝑠𝑎𝑡.= 2𝐿 𝑊𝐶𝑖 (𝛿√𝐼𝑑 𝛿𝑉𝑔 ) 2 (cm2/Vs) (1.6) その他のパラメータに関し、Vthは Idが 1.0×10-9 A に達した際の Vgの値、S 値は Idが 10 pA か ら 100 pA に変化するのに要した Vg、ΔVHは順方向掃引(Vg<0 V → 0 V<Vg)と逆方向掃引(Vg >0 V → 0 V>Vg)における Vthの差と定義した。

Glass substrate

Metal

Oxide

Semiconductor

Oxide

Source

Drain

3

1.3 研究背景[2-4]

1.3.1 FPD 応用へ向けた TFT の要求性能

現在普及している FPD には一般的に、アクティブマトリクス(AM: Active Matrix)駆動方式が 採用されている。基本的な AM 駆動方式の LCD ディスプレイの一画素は 1 つの TFT と 1 つの保 持容量で構成され、一定の周期(フレームレート)で TFT が選択しオン状態にすることで画素 への充電を行い、次の周期まで電位を保持する。よって、AM 駆動方式に用いられる TFT には TFT が選択された僅かな時間内に画素電位を充電する性能が求められ、フレームレートや画素数 の向上のためには、高い電界効果移動度を有する TFT が求められ(1.7)式にて説明される。 𝜇𝐹𝐸 ≫ (𝐶𝐿𝐶+ 𝐶𝑆) 𝑊 𝐿 𝐶𝑖(𝑉𝑔− 𝑉𝑡ℎ) 60 × 𝑚 × 𝑛 (1.7) 上式より、液晶容量 CLC、フレームレート比 m、走査線数 n の増大に伴い電界効果移動度が要求 されることがわかる。 また、OLED ディスプレイの一画素には、有機 EL 素子を駆動する駆動用 TFT と、駆動用 TFT スイッチングする選択用 TFT の 2 つの TFT が用いられている。この駆動用 TFT により有機 EL 素子の発光輝度 Lmが制御され、Lmは駆動用 TFT を流れる電流 Ipixel、OLED 発光効率 η、発光面 積 a を用いて(1.8)式により与えられる。(A: 定数) 𝐿𝑚= 𝐼𝑝𝑖𝑥𝑒𝑙× 𝜂 𝐴 × 𝑎 (1.8) したがって、十分な輝度を得るためには高いドレイン電流が必要とされ、TFT には高い電界効果 移動度が求められると共に、輝度バラツキを抑制するために駆動用 TFT の特性均一性が求めら れる。また、選択用 TFT には LCD 駆動用の TFT と比較し高いゲート電圧が印加されるため、ゲ ートバイアスストレスに対する高い信頼性が要求される。

1.3.2 フレキシブルディスプレイ実現に向けた課題

次世代ディスプレイとして、フレキシブルディスプレイは薄く、軽く、折り曲げられるといっ た特徴を有することから、携帯端末や大型ディスプレイへの応用が期待されている。フレキシブ ルディスプレイ用の表示デバイスとしては LCD や OLED ディスプレイが有力候補であり、特に OLED はバックライトが不要であることから薄型化、柔軟化が可能であるためフレキシブルディ スプレイへの応用に適している。 フレキシブルディスプレイに用いられる基板の種類を表 1.1 に示す。薄板ガラスは耐熱性や平 坦性、ガスバリア性に優れることから基板上への高品質な素子形成が可能であるが、割れやすい ためにフレキシブルデバイス用途としては不完全である。メタルホイルは、耐熱性や柔軟性が良 好であるものの、表面が粗く、導電性を有することから浮遊容量が大きいといった問題があるた め実用化は困難である。対して、プラスチックフィルムは低コスト且つ柔軟性、平坦性に優れる4

ことからフレキシブルデバイス用の基板材料として有力な候補である。しかし、一般的なプラス チック材料は耐熱性が低く、代表的な材料である PET(polyethylene terephthalate)や PEN (polyethylene naphthalate)の耐熱温度はそれぞれ 110 ºC、155 ºC である[5]。PI(polyimide)フ ィルムに代表される耐熱性に優れる材料もあるが、一般的なフィルムと比較し高価であり透明性 にも課題がある。よって、実用的には PET や PEN フィルムをフレキシブルディスプレイの基板 材料として用いることが望まれ、そのためには TFT 作製プロセス温度を基板の耐熱温度以下に 抑制することが求められる。 表 1.1 各フレキシブル基板の特徴 プラスチック 耐熱フィルム 薄板ガラス メタルホイル 代表材料 PET, PEN PI - ステンレス 最高プロセス温度 180 ºC > 300 ºC 600 ºC > 600 ºC 平坦性 ◯ ○ ○ △ 導電性 無 無 無 有 ガスバリア性 ✕ ✕ ○ △~○ 柔軟性 ○ ○ ✕ ○

1.3.3 TFT の種類と特徴

以上を踏まえ TFT の現行技術について考える。TFT の電気的特性や作製プロセスは、TFT の チャネル層に用いる半導体材料によって大きく異なり、主に非晶質シリコン(a-Si: Amorphous Silicon)、低温多結晶シリコン(LTPS: Low Temperature Poly-Silicon)、酸化物半導体等が挙げられ る。それぞれの半導体材料に応じた TFT の特徴を表 1.2 にまとめる[6]。a-Si は、プラズマ化学気相堆積(PE-CVD: Plasma-Enhanced Chemical Vapor Deposition)法によ り成膜され、低コスト且つ大面積均一性に優れることから、現在の大型ディスプレイ用 TFT の 主流技術である。しかし、電界効果移動度は 1 cm2/Vs 程度と低く、ディスプレイの表示機能の高 精細化には限界がある。また、非晶質である a-Si は近接数原子間での短距離秩序しか持たず長距 離秩序が維持でき難いため、バンドギャップ中に裾状準位が広がっていることが知られており、 デバイス応用の際には信頼性や作製再現性が問題となる[7]。 LTPS は、a-Si 膜をエキシマレーザーアニールにより結晶化させることで形成する。電界効果 移動度が 100 cm2/Vs 以上と高く、画素内の TFT だけでなく周辺回路も同時に形成することが可 能であることから、ディスプレイの小型化・低コスト化に有効である。しかし、製造装置が大型 になることや、結晶粒界の影響により閾値電圧バラツキが大きいことから大型ディスプレイ用途 には不向きである[8]。 酸化物半導体は、a-Si と同様に大面積均一性に優れる非晶質半導体ある。中でも代表的なイン ジウム、ガリウム、亜鉛の酸化物である In-Ga-Zn-O(IGZO)は、a-Si と比較し 10 cm2/Vs を超え る高い電界効果移動度を有し、信頼性にも優れる[9]。また、非晶質であるために LTPS と比較し

5 特性バラツキが良好であるという特徴があることから、ディスプレイ用 TFT 用途として一部実 用化もされている。加えて、スパッタ法による室温形成が可能であり、前述の耐熱性に劣るプラ スチックフィルム上への直接形成が可能であることも大きな特徴の一つである。 表 1.2 各種半導体材料を用いた TFT の特徴比較 a-Si TFT LTPS TFT 酸化物半導体 TFT 電界効果移動度(cm2/Vs) < 0.5 > 100 (n 型) 10 < 信頼性 △ ◎ ◯ 閾値電圧均一性 ◎ △ ◯ チャネル成膜方法 PE-CVD PE-CVD+ELA SPT プロセス温度 150-350 °C 250-550 °C RT-350 °C

基板材料 Glass, Metal Glass, Metal Glass, Metal, Plastic

製造コスト Low High Low

1.3.4 IGZO TFT の課題

前項にて、IGZO TFT は従来用いられてきた a-Si TFT と比較し電界効果移動度と信頼性に優れ、 LTPS と比較し特性均一性が高く、さらに室温形成が可能である特徴を有することを述べた。こ れらの理由より、高精細や大画面、フレキシブル等の次世代ディスプレイ実現に向けた TFT と して特に有望であると言える[1]。しかし、次世代ディスプレイの実現には TFT 特性の更なる改 善が求められ、特にバイアスストレス信頼性の向上は実用化の上で重要な課題である。特に、バ イアスストレスによる特性劣化として TFT の閾値電圧が変動することが報告されており、チャ ネル膜中やチャネル/絶縁膜界面への電子トラップがゲートバイアスをスクリーニングすること に起因する閾値電圧の正シフトが主に報告されている[10,11]。また IGZO における電子トラップ は、IGZO 膜中や IGZO/絶縁膜界面の酸素欠損(未結合手)や配位数が不十分な酸素によりバン ドギャップ中にサブギャップ欠陥準位が形成されることが要因であると報告されている[12,13]。 したがって、サブギャップ欠陥準位の低減が IGZO TFT 実用化に向けた課題であり、酸素や水素、 フッ素等を用いた酸素欠損補償による欠陥準位の抑制がこれまでに研究されている[13-16]。 また、IGZO は室温形成が可能であるものの、十分な電気的特性を得るためには通常 300 °C 以 上によるポストアニール処理が必要であり、ポストアニール処理を行っていない TFT はヒステ リシスやバイアスストレス信頼性に劣ることが報告されている[6,11]。加えて、一般的に IGZO TFT のゲート絶縁膜には PE-CVD 法により成膜した酸化シリコンが用いられているが、PE-CVD 法では成膜温度(基板温度)の低下に伴い膜質(サブギャップ準位密度、絶縁耐圧)が劣化する。 したがって、ゲート絶縁膜として十分な膜質を得るためには 300 °C で成膜を行う必要がある。 これらの理由から、フレキシブル TFT 作製に際してフレキシブル基板上へ直接 IGZO TFT の形 成を行うことは困難であり、低温にて高品質な IGZO 膜およびゲート絶縁膜を形成することが課 題とされる。6

1.4 研究目的

以上をまとめると、次世代ディスプレイ応用に向けた IGZO TFT の課題として、I) IGZO TFT のサブギャップ欠陥準位の抑制による TFT 特性・信頼性の制御と II) プラスチックフィルムの耐 熱温度(150 °C)以下による高性能・高信頼性 IGZO TFT の実現が要求されるといえる。そこで 本研究では、これら課題の解決に向け以下の研究を行った。 I) フッ素を用いた欠陥補償による IGZO TFT 特性・信頼性の制御 本研究グループでは、IGZO TFT のパッシベーション層としてフッ素含窒化シリコン膜を成 膜し、長時間のポストアニール処理を行うことで絶縁膜中に含まれたフッ素が熱拡散し、酸素欠 損を補償することで TFT 特性や信頼性が向上することを報告している[15]。そこで本研究では、 フッ素導入による IGZO TFT の更なる伝達特性・信頼性の向上を目指し、フッ素源となるフッ素 含有絶縁膜の変更による特性制御・改善を試みると同時に、フッ素濃度と TFT 特性の相関関係 について評価を行った。また、パッシベーション層からの熱拡散ではなくチャネル上へ直にフッ 素含有絶縁膜を成膜することで、より直接的な IGZO TFT の特性・信頼性制御手法の確立を試み た。 II) 有機絶縁膜を用いた 150 °C 以下プロセスによる高性能・高信頼性 IGZO TFT の実現 フレキシブルディスプレイ応用を目指した IGZO TFT の低温形成に関する研究として、本研 究グループではこれまでに塗布型有機絶縁膜を TFT のゲート絶縁膜およびチャネル保護膜、層 間絶縁層として用いた無機/有機ハイブリット IGZO TFT の作製を行い、フロントチャネル界面 形成プロセスを改善することにより最高プロセス温度 150 ºC にて良好な TFT 特性を実現した ことを報告している[17]。この成果を踏まえ、本研究では塗布型有機絶縁膜を用いた無機/有機ハ イブリット IGZO TFT の信頼性評価および特性・信頼性の更なる改善に向けた制御技術に関して 研究を行った。 以上を主な研究指針とし、研究活動に取り組んだ。

7

1.5 本論文の構成

第 1 章 序論

本研究の背景と次世代ディスプレイ応用に向けた IGZO TFT の課題について述べ、本研究の目 的を示した。第 2 章 フッ素含有絶縁膜を用いた高性能・高信頼性 IGZO TFT 形成

IGZO TFT 上へフッ素含有酸化シリコンおよびフッ素を含有しない酸化シリコンによるパッシ ベーション層を形成することにより、フッ素導入の有無による特性・信頼性の比較を行った。ま た、フッ素含有量が TFT の特性に与える影響に関しても検討した。第 3 章 フッ素含有絶縁膜のエッチングストッパー層(ESL)応用

より効率的な特性・信頼性制御手法として、パッシベーション層やエッチングストッパー層か らの熱拡散による間接的なフッ素導入ではなく、エッチングストッパー層にフッ素含有絶縁膜を 用いることによる直接的なフッ素導入を試みた。第 4 章 有機絶縁膜を用いた IGZO TFT の低温形成

有機絶縁膜を用いた最高プロセス温度 150 °C にて作製した IGZO TFT の信頼性評価および特 性・信頼性の更なる改善に向けた制御技術に関して研究を行った。第 5 章 総括と展望

本論文を総括し、本研究で得られた結果や今後の展望について述べる。8

参考文献

[1] K. Nomura et al., “Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors”, Nature, 432 (2004) 488.

[2] 薄膜材料デバイス研究会 編, “薄膜トランジスタ”, コロナ社, (2008). [3] 山本 敏裕, “フレキシブルディスプレー用薄膜トランジスターの研究動向”, NHK 技研 R&D No.145 (2014) 28. [4] 栗田 泰市郎, “フレキシブルディスプレーの研究・開発動向 ”, NHK 技研 R&D No.145 (2014) 4. [5] 帝人デュポンフィルム株式会社, テオネックス®, https://www.teijindupontfilms.jp/product/name/pen/pen_teo.html, (2017 年 3 月 9 日).

[6] T. Kamiya et al., “Present status of amorphous In-Ga-Zn-O thin-film transistors”, Sci. Technol. Adv. Mater. 11 (2010) 044305.

[7] F. Yonezawa 編, “Fundamental Physics of Amorphous Semiconductors”, p.119, Springer, (1980). [8] S. Higashi et al., “High-quality SiO2/Si interface formation and its application to fabrication of

low-temperature-processed polycrystalline Si thin-film transistor”, Jpn. J. Appl. Phys., 41 (2002) 3646. [9] T. Kamiya and H. Hosono, “Material characteristics and application of transparent amorphous oxide

semiconductors”, NPG Asia Mater, 2 (2010) 15.

[10] J.-M. Lee et al., “Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors”, Appl. Phys. Lett., 93 (2008) 093504.

[11] K. Nomura et al., “Origins of threshold voltage shifts in roomtemperature deposited and annealed a -In – Ga – Zn – O thin-film transistors”, Appl. Phys. Lett., 95 (2009) 013502.

[12] T. Kamiya et al., “Subgap states, doping and defect formation energies in amorphous oxide semiconductor a-InGaZnO4 studied by density functional theory”, Phys. Stat. Sol. (a), 207 (2010) 1698. [13] W. Körner et al., “Origin of Subgap states in amorphous In-Ga-Zn-O”, Appl. Phys. Lett., 114 (2013)

163704.

[14] K. Nomura et al., “Depth analysis of subgap electronic states in amorphous oxide semiconductor, a-In-Ga-Zn-O, studied by hard x-ray photoelectron spectroscopy”, J. Appl. Phys., 109 (2012) 073726. [15] J. Jiang et al., “Highly stable fluorine-passivated In-Ga-Zn-O thin-film transistors under positive gate

bias and temperature stress”, Appl. Phys. Express, 7 (2014) 114103.

[16] H. Yamazaki et al., “The influence of fluorinated silicon nitride gate insulator on positive bias stability toward highly reliable amorphous InGaZnO thin-film transistors,” J. Solid State Sci. and Technol., 3 (2014) Q20.

[17] T. Toda et al., “High performance top-gate and self-aligned In-Ga-Zn-O thin-film transistor using coatable organic insulators fabricated at 150 °C”, IEEE Electron Device Lett., 37 (2016) 1006.

9

第 2 章

フッ素含有絶縁膜を用いた高性能・高信頼性

IGZO TFT 形成

2.1 高信頼性 IGZO TFT 実現への試み

IGZO 膜中や IGZO/GI 界面の酸素欠陥(未結合手)由来のサブギャップ欠陥準位への電子トラ ップは、TFT 特性や信頼性に悪影響を及ぼすことが知られている[1,2]。従って、これらの欠陥の 補償を行うことは良好な TFT 特性・信頼性を得るために必要不可欠であり、従来研究にて様々 な手法が提案されている。主な欠陥補償手法として、水素や酸素、フッ素を導入することで欠陥 の終端を行う方法が研究されている[2-5]。フッ素による欠陥補償として、プラズマ処理やイオン 注入等の方法により酸化物半導体への導入することによる電気的特性の向上や、フッ素含有絶縁 膜を TFT のゲート絶縁膜(GI: Gate Insulator)に用いることによる信頼性の向上が報告されてい る[6-8]。本研究グループでも、IGZO TFT のパッシベーション層(PSL: Passivation Layer)にフッ 素含有絶縁膜を用いることで TFT 特性や信頼性が向上することを報告している[9]。そこで本研 究では、フッ素導入による IGZO TFT の更なる伝達特性・信頼性の向上を目指し、フッ素源とな るフッ素含有絶縁膜の変更による特性制御・改善を試みると同時に、フッ素濃度と TFT 特性の 相関関係について評価を行った。2.2 フッ素による欠陥補償メカニズム[9,10]

フッ素イオンと酸素イオンはイオン半径が近いために IGZO 中に拡散したフッ素イオンは(2.1) 式に示す酸素欠損(VO)の補償と、(2.2)式に示す弱結合酸素の置換の 2 つの役割を持つ[11]。𝑉

𝑜⦁⦁+ 2𝑒

−+ 𝐹 → 𝐹

𝑜⦁+ 𝑒

− (2.1)𝑂

𝑜𝑋+ 𝐹 → 𝐹

𝑜⦁+ 𝑒

− (2.2) (2.1)式により、IGZO/ゲート絶縁膜界面や IGZO 膜中に存在する酸素欠損に対してフッ素が 結合することで欠陥終端した場合、酸素欠損により生成された自由電子(キャリア)の内 1 つの 電子が消費されキャリア濃度が減少する。一方で(2.2)式に示すように酸素イオン(O2-)をフ10

ッ素イオン(F-)で置換すると、価数の差により自由電子が生成され、IGZO のキャリア濃度が

増大する。これは、TFT 特性における閾値電圧(Vth)の負シフトや導電膜化の原因となる。よっ

て、フッ素による酸素欠損補償を行うと同時に過剰なフッ素拡散を抑制することが求められる。 この問題に対して、本研究グループではエッチングストッパー層(ESL: Etching Stopper Layer) を有するコンタクトホール(CH)型・ボトムゲート(BG)構造 TFT のパッシベーション層とし てフッ素含有窒化シリコン(SiNx:F)を成膜し、ESL を介してフッ素拡散を行うことで良好な TFT 特性・信頼性が得られることを報告している。また、IGZO 中の金属とフッ素の結合は、金属と 酸素の結合と比較し結合エネルギーにおいて安定である(表 2.1)[12]。したがって、熱的安定性 に優れることもフッ素を用いることの利点の 1 つと言える。 表 2.1 結合エネルギー一覧[12] 酸素 フッ素 In 346 kJ/mol 516 kJ/mol Ga 374 kJ/mol 584 kJ/mol Zn 250 kJ/mol 364 kJ/mol Si 444 kJ/mol 595 kJ/mol

2.3 フッ素含有絶縁膜を用いた TFT 作製プロセス

本研究では、本グループにて一般的に用いられる ESL を有するコンタクトホール型・ボトム ゲート構造を採用した。本研究で作製したフッ素含有絶縁膜を PSL に用いたボトムゲート構造 TFT の作製プロセス工程を図 2.1 に示す。尚、本研究における TFT の基板材料には無アルカリガ ラス基板(Corning® EAGLE XG®、直径 4 インチ、厚さ 0.7 mm)を用い、各層のパターニングに はポジ型フォトレジストとフォトマスク、Deep UV 露光装置を用いたフォトリソグラフィーによ り行った。 初めに①ガラス基板上へ Cr 膜(50 nm)を DC スパッタ法により成膜し、ウェットエッチング によってゲート電極パターニングを行った。次に、②GI として酸化シリコン(SiOx)膜(150 nm) をプラズマ化学気相堆積(PE-CVD)法により設定温度 500 ºC(基板温度 350 ºC)にて成膜した。 このとき、原料ガスにはモノシラン(SiH4)と N2O ガス、窒素をそれぞれ 2/100/120 sccm 流入し、 電力 50 w、圧力 110 Pa にて成膜を行った。その後直ちに③IGZO 膜(45 nm)を DC マグネトロ ンスパッタ法により成膜した。また、IGZO 成膜には元素比 In: Ga: Zn = 1: 1: 1 の IGZO ターゲットを用い表 2.2 に示す条件にて成膜を行った。IGZO 膜成膜後、CH4/Ar ガスを用いたドライエッ

チングにてチャネルパターニング(チャネル幅 W = 50 μm, チャネル長 L = 20 μm)を行った。ま た、本研究におけるドライエッチングは誘導結合プラズマ(ICP: Inductively Coupled Plasma)エ

11 より設定温度 250 ºC(基板温度 170 ºC)、成膜ガス流量および電力、圧力は GI 成膜と等しい条 件にて行った。ESL 形成後、CF4/O2ガスを用いたドライエッチングによってチャネルとソース・ ドレイン(S/D: Source/Drain)電極間および、ゲート電極と測定用パッド間のコンタクトホール の形成を行った。その後、⑤InSnO(ITO、50 nm)の成膜を DC マグネトロンスパッタ法により 行い、更に CH4/Ar ガスを用いたドライエッチングにより S/D 電極パターニングを行った。最後 に、⑥PSL の成膜を PE-CVD 法にて行い、その後測定用バッド上のコンタクトホール形成をドラ イエッチングによって行った。 本研究では PSL におけるフッ素の有無および材料の違いによる比較を行うため、フッ素フリ ーPSL として SiH4を主な原料ガスとするフッ素フリー酸化シリコン(SiOx:H)膜およびフッ素含

有 PSL として SiF4を主な原料ガスとするフッ素含有酸化シリコン(SiOx:F)膜、SiOx:F とフッ素

含有窒化シリコン(SiNx:F)膜の積層膜(下層/上層=SiOx:F/SiNx:F)を用い、合計 3 種類の TFT

の比較を行った。各種 PSL の成膜条件については表 2.3 に示す。

TFT 作製後、RTA(Rapid Thermal Annealing)を用いて 350 ºC、窒素雰囲気によるポストアニ ール処理を行い、TFT 初期特性および信頼性のポストアニール処理時間依存性の評価を行った。 図 2.1 コンタクトホール型・ボトムゲート構造 TFT の作製プロセス工程 ② ゲート絶縁膜形成 SiOxGI(150 nm) ① ゲート電極形成 ガラス基板 Cr Gate(50 nm) ウェットエッチング PR ※PR:フォトレジスト ③ チャネル層形成(W = 50 μm, L = 20 μm) IGZO チャネル(45 nm) PR ドライエッチング ④ ESLおよびコンタクトホール形成 SiOxESL(200 nm) ⑤ S/D電極形成 ITO S/D(50 nm) ⑥ PSL形成およびパッドコンタクトホール形成 各種PSL(200 nm)

12 表 2.2 IGZO チャネル成膜条件 成膜ガス流量 [sccm] O2/Ar = 0.6/29.4(P[O2]=2%) 成膜圧力(背圧)[Pa] 1.0(約 3.0×10-5) 成膜電力 [W] DC 80 成膜温度 [ºC] 設定温度 260(基板温度 ~160) 基板-ターゲット間距離 [mm] 88 表 2.3 各種 PSL の成膜条件 PSL 材料 SiOx:H SiOx:F SiOx:F/SiNx:F (下層/上層) 成膜温度 [ºC] 170 350 350/350 膜厚 [nm] 200 ← 20/180

成膜ガス SiH4 + N2O SiF4 + N2O SiH4 + N2O/ SiF4 + N2O

成膜装置 CCP※ CVD ICP CVD ←

※CCP:Capacitively Coupled Plasma(容量結合プラズマ)

2.4 フッ素含有絶縁膜を用いた TFT の特性および信頼性評価

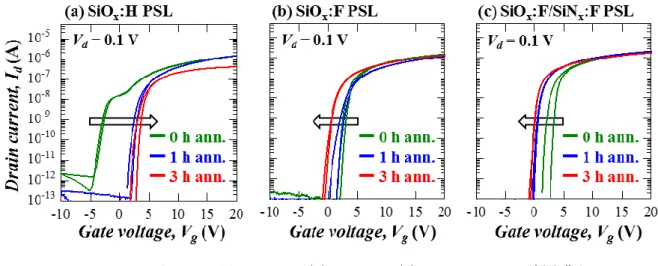

2.4.1 TFT 初期特性のポストアニール時間依存性

各種 PSL を用いた IGZO TFT のポストアニール処理無しおよび 1 時間、3 時間行った後の、ド レイン電圧 Vd = 0.1 V の際の測定結果を図 2.2 に示す。この時、測定はすべて同一素子で行い、 1 時間アニール処理後に測定を行った後、追加で 2 時間のアニール処理を行うことで 3 時間アニ ールとした。また、表 2.4 は同一素子の電界効果移動度(μFE)、サブスレッショルドスイング値 (S 値)、閾値電圧(Vth)、ヒステリシス(ΔVH)である。尚、本研究における S 値はドレイン電 流(Id )が 10 pA から 100 pA まで増大するのに要したゲート電圧 Vg、Vthは Idが 1 nA に達した 際の Vgと定義した。また、TFT 初期特性評価には半導体パラメータアナライザ(Agilent 4156C) を用い、プローブボックス内で大気雰囲気中、室温で行った。 図 2.2(a-c)に示すように、SiOx:H PSL を用いた TFT ではポストアニール処理時間の延長に伴う Vthの正シフトが見られ、これに対し SiOx:F および SiOx:F/SiNx:F 積層 PSL を用いた TFT では

処理時間の増大に伴う Vthの負シフトが見られた。また、VHに関し、SiOx:H と SiOx:F サンプル

では 1 時間アニール処理後の数値はそれぞれ 0.51 V と 0.63 V と大きな差は見られなかったが、 3 時間アニール処理後 SiOx:F にのみ ΔVHの減少(改善)が見られた。また、SiOx:F/SiNx:F 積層

13

図 2.2 PSL として(a)SiOx:H,(b)SiOx:F,(c)SiOx:F/SiNx:F 積層膜を

用いた IGZO TFT の伝達特性 表 2.4 図 2.2 中の TFT の特性値

Passivation layer (a) SiOx:H PSL (b) SiOx:F PSL

Annealing time 0 h ann. 1 h ann. 3 h ann. 0 h ann. 1 h ann. 3 h ann. μFE [cm2/Vs] 12.2 14.8 7.6 17.5 15.6 14.9

S 値(Id: 10-100 pA) [V/dec.] 0.52 0.38 0.40 0.25 0.55 0.41

Vth (Vg at Id = 1 nA) [V] -2.91 2.52 3.12 2.50 2.09 0.52

ΔVH (Vg at Id = 1 nA) [V] 0.29 0.51 0.57 0.57 0.63 0.17

Passivation layer (c) SiOx:F/SiNx:F PSL

Annealing time 0 h ann. 1 h ann. 3 h ann. μFE [cm2/Vs] 15.2 20.8 16.6

S 値(Id: 10-100 pA) [V/dec.] 0.22 0.21 0.27

Vth (Vg at Id = 1 nA) [V] 2.12 0.51 0.06

ΔVH (Vg at Id = 1 nA) [V] 1.27 0.13 0.07

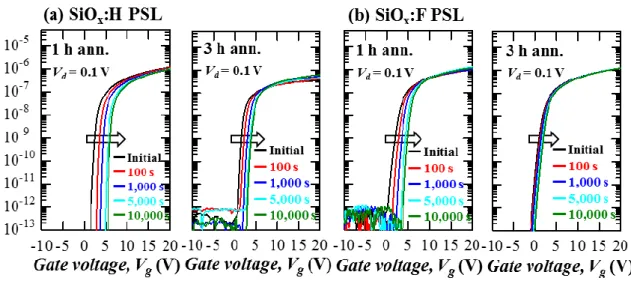

2.4.2 ポジティブゲートバイアス熱ストレス試験による信頼性評価

次に、信頼性評価としてポジティブゲートバイアス熱ストレス(PBTS: Positive Bias Temperature Stress)試験を行った。本研究における PBTS 試験では、加熱ステージにより 100 °C の基板加熱 を行いつつゲート電極に 20 V のストレス電圧を合計 10,000 秒印加し、ストレス印加前後の閾値 電圧のシフト量(ΔVth)の評価を行った。 図 2.3(a-c)は、各種 PSL を用いた IGZO TFT のポストアニール処理(窒素雰囲気、350 °C) 1 時間および 3 時間後の PBTS 試験の測定結果である。また、表 2.5 は同測定におけるストレス 印加 10,000 秒後の ΔVthの値である。測定結果より、アニール処理 1 時間後の ΔVthは SiOx:H PSL

14

(図 2.3(a))と SiOx:F PSL(図 2.3(b))を用いた TFT ではいずれも約 3 V と同等であった。しか

し、アニール処理時間を 3 時間に延長した結果、SiOx:H では 2.26 V、SiOx:F では 1.01 V を示し、

SiOx:F PSL ではアニール時間の延長に伴う ΔVthの改善を示した。また、SiOx:F/SiNx:F 積層 PSL

(図 2.3(c))ではアニール処理 1 時間にて 0.72 V の良好な値を示し、更にアニール時間を 3 時間 に延長することで 0.11 V の最も良好な信頼性を示した。

図 2.3 PSL として(a)SiOx:H,(b)SiOx:F,(c)SiOx:F/SiNx:F 積層膜を用いた IGZO TFT

のポストアニール処理 1 時間および 3 時間後の PBTS(100 °C, Vg=20 V)測定結果

表 2.5 PBTS 試験下における 10,000 秒後の閾値電圧シフト量(ΔVth)

Passivation layer (a) SiOx:H (b) SiOx:F (b) SiOx:F/SiNx:F

Annealing time 1 h ann. 3 h ann. 1 h ann. 3 h ann. 1 h ann. 3 h ann.

15

2.5 各種 TFT の膜中フッ素濃度

2 次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により、IGZO TFT に含まれる 成分濃度の評価を行った。SIMS 評価には、Si 基板上に SiOx:H/IGZO/SiOx:H/各種 PSL 材料(SiOx:H,

SiOx:F, SiOx:F/SiNx:F 積層膜)を積層したサンプルを用いた(図 2.4)。この時、各層の成膜条件は

TFT と同一条件を用い、膜厚は SiOx:H/IGZO/SiOx:H/各種 PSL=50/50/200/200 nm とした。また、 SIMS 測定は表 2.6 に示す条件にて行い、PSL に含まれるフッ素が検出器の飽和濃度に達してい たため、測定の手順を i) PSL 測定中はフッ素(19F)の検出を行わず代用として19F+16O の質量数 35 に関して測定、ii) 19F+16O の検出量が減少し始めた時点を PSL と SiO x:H の境界とし測定を一 時中断、iii) 19F の検出を追加して測定を再開、の順で行った。 図 2.4 SIMS 測定サンプル構造模式図 表 2.6 SIMS 測定条件 1 次イオン Cesium 加速電圧 [kV] 3 照射電流 [nA] 200 イオンビーム照射面積(Raster)[μm] 600 分析範囲(Aperture)[%] 9 各種 PSL を用いたサンプルに関し、アニール処理(窒素雰囲気、350 °C、1 時間)前後での SIMS 測定を行い、得られたフッ素(m/z=19)と水素(m/z=1.2)の信号強度を酸素(m/z=18)の強 度により規格化し強度比を求めた。フッ素および水素の強度比をそれぞれ図 2.5 および図 2.6 に 示す。 SiOx:H サンプルに関して、アニール処理後に IGZO 中における m/z=19 の強度比の増大が見ら れた(図 2.5)。m/z=19 の検出の際、SIMS 測定では19F と同時に18O と1H で構成される OH も 検出されため、m/z=19 の信号強度はフッ素と OH の和を表す。したがって、SiOx:H における m/z =19 の強度比の増大は OH 起因であると考えられる。また、図 2.6 より SiOx:H ではアニール処 理後に IGZO 中の水素(m/z=1.2)の強度比が増大していることから、水素が拡散していることが 確認できる。よって、SiOx:H サンプルではアニール処理により水素が拡散し、OH が生成されて いることが考えられる。

一方、SiOx:F および SiOx:F/SiNx:F 積層サンプルでは、アニール処理前における IGZO 中での

Si基板 SiOx:H(50 nm) IGZO(50 nm) SiOx:H(200 nm) 各種PSL材料 1. SiOx:H(200 nm) 2. SiOx:F(200 nm) 3. SiOx:F/SiNx:F(100/100 nm)

16

m/z= 19 の強度比は SiOx:H サンプルと比較し高い値を示し、アニール処理後に上層 SiOx:H と

IGZO 中において m/z=19 強度比の更なる増大が見られた(図 2.5)。図 2.6 より、アニール処理

前後での IGZO 中における水素(m/z=1.2)の強度比に大きな変化は見られないことから、OH の生 成される量は SiOx;H サンプル以下であると考えられる。したがって、SiOx:F および SiOx:F/SiNx:F

サンプルにおける m/z= 19 の強度比の増大より、アニール処理により IGZO 中へフッ素が拡散し ていることが明らかとなり、フッ素の含有量は SiOx:F/SiNx:F 積層サンプルがより多いことが確 認できた。 図 2.5 各種 PSL 材料を用いたサンプルのアニール処理前後の SIMS 測定結果 (フッ素(m/z=19)を酸素(m/z=18)で規格化した強度比) 図 2.6 各種 PSL 材料を用いたサンプルのアニール処理(窒素雰囲気、350 °C、1 時間)前後の SIMS 測定結果(水素(m/z=1.2)を酸素(m/z=18)で規格化した強度比)

17

2.6 TFT 特性・信頼性と膜中フッ素濃度の相関関係の考察

TFT 特性評価より、SiOx:H PSL サンプルではアニール処理時間の増大に伴う Vthの正シフトと

ΔVHの増大(悪化)傾向が見られた。対して、SiOx:F および SiOx:F/SiNx:F 積層 PSL を用いた TFT

では、アニール処理時間の増大に伴う Vthの負シフトとΔVHの改善が見られた。また、PBTS 信

頼性評価では SiOx:F/SiNx:F 積層 PSL にて最も良好な結果を示し、SiOx:F PSL では 3 時間アニー

ル処理後に SiOx:H PSL と比較し改善する傾向が見られた。Vthはチャネル中のキャリア濃度に強

く依存し、ΔVHと PBTS 信頼性はチャネル/GI 界面欠陥に特に依存するため、測定結果より SiOx:F

および SiOx:F/SiNx:F 積層 PSL を用いた TFT では、ポストアニール処理時間の延長に伴う IGZO

のキャリア濃度の増大および、IGZO/GI 界面欠陥が補償されたと考えられる[1,2]。

2 章 2 節で述べたように、フッ素は酸素欠損を補償することでキャリアを増大させることから、

TFT 特性・信頼性評価の結果はフッ素による IGZO 膜中や IGZO/GI 界面の酸素欠損(未結合手)

由来の欠陥が補償されていることを示唆している。また、SIMS 評価より SiOx:H ESL を介した

IGZO 膜中へのフッ素拡散が確認され、膜中フッ素濃度は SiOx:F/SiNx:F 積層 PSL にて最大値を

示した。積層 PSL にて最も良好な PBTS 信頼性を示したことから、IGZO 膜中フッ素濃度の増大 と信頼性の改善に相関関係が確認でき、フッ素が TFT の欠陥補償に重要な役割を果たしている と考えられる。

しかし、フッ素濃度と特性・信頼性の量的関係性、窒化膜や酸化膜による材料の影響に関して は評価が不十分であり、今後は定量的な分析を行っていくことが求められる。

18

参考文献

[1] K. Nomura et al., “Origins of threshold voltage shifts in roomtemperature deposited and annealed a -In – Ga – Zn – O thin-film transistors”, Appl. Phys. Lett., 95 (2009) 013502.

[2] W. Körner et al., “Origin of Subgap states in amorphous In-Ga-Zn-O”, Appl. Phys. Lett., 114 (2013) 163704.

[3] K. Nomura et al., “Depth analysis of subgap electronic states in amorphous oxide semiconductor, a-In-Ga-Zn-O, studied by hard x-ray photoelectron spectroscopy”, J. Appl. Phys., 109 (2012) 073726. [4] J. Jiang et al., “Highly stable fluorine-passivated In-Ga-Zn-O thin-film transistors under positive gate

bias and temperature stress”, Appl. Phys. Express, 7 (2014) 114103.

[5] H. Yamazaki et al., “The influence of fluorinated silicon nitride gate insulator on positive bias stability toward highly reliable amorphous InGaZnO thin-film transistors,” J. Solid State Sci. and Technol., 3 (2014) Q20.

[6] Z. Ye, and M. Wong, “Characteristics of plasma-fluorinated zinc oxide thin-film transistors,” IEEE Electron Device Lett., 33 (2012) 1147.

[7] L. X. Qian and P. T. Lai, “Fluorinated InGaZnO thin-film transistor with HfLaO gate dielectric,” IEEE Elec. Dev. Lett., 35 (2014) 363.

[8] H. Yamazaki et al., “The influence of fluorinated silicon nitride gate insulator on positive bias stability toward highly reliable amorphous InGaZnO thin-film transistors,” J. Solid State Sci. and Technol., 3 (2014) Q20.

[9] J. Jiang et al., “Highly stable fluorine-passivated In-Ga-Zn-O thin-film transistors under positive gate bias and temperature stress”, Appl. Phys. Express, 7 (2014) 114103.

[10] J. Jiang, “Study on density of states in In-X-Zn-O (X=Sn, Ga) semiconductors and defect passivation methods for highly reliable thin-film transistors”, 高知工科大学大学院博士論文 (2015).

[11] J. Seo et al., “Solution-processed flexible fluorine-doped indium zinc oxide thin-film transistors fabricated on plastic film at low temperature,” Sci. Rep., 3 (2013) 1.

[12] Das Periodensystem der Elemente online, http://www.periodensystem-online.de/index.php, (2017 年 3 月 9 日).

19

第 3 章

フッ素含有絶縁膜の

エッチングストッパー層応用

3.1 エッチングストッパー層(ESL)応用の目的

前章では、フッ素含有絶縁膜を TFT のパッシベーション層(PSL)として用いた IGZO TFT は フッ素を含有しない PSL を用いた TFT と比較し良好な伝達特性・信頼性を示し、フッ素による IGZO 膜中や IGZO/絶縁膜界面の欠陥補償に有効であることを述べた。しかしながら、この手法 ではエッチングストッパー層(ESL)を介してフッ素拡散を行うため、高温かつ長時間のポスト アニール処理を必要とする。したがって、より効率的にフッ素による欠陥補償を行うためには、 ESL として直接フッ素含有絶縁膜を用いることが望まれるが、フッ素は基本的に酸化物半導体に 対してキャリア濃度を増大させるドナーとして働くために、IGZO 上にフッ素含有窒化シリコン (SiNx:F)を直接積層させた場合、IGZO が導電膜化することが確認されている[1-3]。 そこで本研究では、フッ素による欠陥補償と、酸素によるキャリア補償を同時に行うことを目的に、IGZO 上へのフッ素含有酸化シリコン(SiOx:F)成膜を行い、SiOx:F 成膜が IGZO 電気特性

に与える影響を評価し、SiOx:F 膜の ESL 応用とフッ素による TFT 特性・信頼性制御を試みた。

3.2 評価方法・装置概要[4,5]

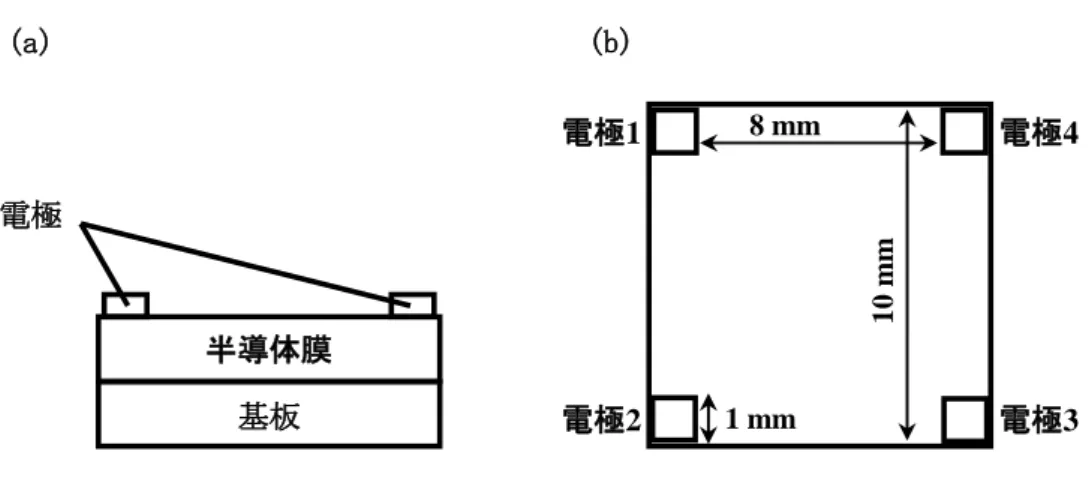

3.2.1 Van der Pauw 法概要

IGZO 膜を TFT のチャネル層として用いる場合、IGZO 膜のキャリア濃度は 1012 ~1015 cm-3、体

積抵抗率は 103 ~106 Ω∙cm 程度に制御される必要がある[6]。一方、本研究グループにて従来用い

られてきた測定器で測定可能なキャリア濃度下限はおよそ 1018 cm-3であり、TFT 動作が可能な

領域付近に関する測定を行うことが困難であった。しかし、キャリア濃度や体積抵抗率は半導体 の電気的特性に関して議論する上で重要な指標であり、より低い濃度領域(高い抵抗率)の測定 を可能にすることが望まれた。そこで、より広範囲の測定のため van der Pauw 法に基づいたホー ル効果測定装置のシステム構築を行った。Van der Pauw 法はホール効果を利用し薄膜の抵抗率、 キャリア濃度、移動度の測定を行う。特に任意の形状のサンプルのホール効果測定に対して用い られ、本研究では図 3.1 に示す形状のサンプルを用いた。

20

図 3.1 Van Der Pauw 法に用いるサンプルの(a)断面図、(b)平面図

Van der Pauw 法における対辺抵抗値とホール抵抗値の測定手順を示す。対辺抵抗値は、図 3.1 (b)に示す構造のサンプルの 1 辺を電流印加端子とし、その対辺を電圧測定端子として測定(測 定 a)を行い、得られた値より対辺抵抗値を求める。次に、電極配置を変えず逆方向に電流を印 加して同様の測定(測定 b)を行う。その後、電流印加端子と電圧測定端子を逆に入れ替えて測 定 a, b と同様の測定(測定 c, d)を行う。更に、測定 a ~ d と直交する方向の辺に関しても同様の 測定(測定 e ~ h)を行う。 ホール抵抗値は、サンプル面に垂直に磁場を印加し測定を行う。まず、サンプルの 1 対角を電 流印加端子とし、その直交対角を電圧測定端子として測定(測定 i)を行い、得られた値よりホ ール抵抗値を求める。次に、電極配置を変えず逆方向に電流を印加して同様の測定(測定 j)を 行い、更に、電流印加端子と電圧測定端子を逆に入れ替え測定 i, j と同様の測定(測定 k, l)を行 う。その後、磁場を反転させて、測定 i ~ l と同様の測定(測定 m ~ p)を行う。

次に、算出方法に関して述べる。Van der Pauw 法における体積抵抗率 ρ、キャリア濃度 NC、ホ

ール移動度μHallはそれぞれ(3.1)式、(3.2)式、(3.3)式で求められる。このとき、半導体膜の 膜厚を t [cm]、ホール係数を RH、電気素量を e [C]と置く。また、測定 a ~ p より得られた抵抗値 をそれぞれ Ra ~ Rp と置く。 𝜌 =𝜋 ∙ 𝑡 𝑙𝑛 2∙ 1 8(𝑅𝑎+ 𝑅𝑏+ 𝑅𝑐+ 𝑅𝑑+ 𝑅𝑒+ 𝑅𝑓+ 𝑅𝑔+ 𝑅ℎ) ∙ 𝑓(𝑟) [Ω ∙ cm] (3.1) 𝑁𝐶 = 1 𝑅𝐻∙ 𝑒

[cm−3] (3.2) 𝜇𝐻𝑎𝑙𝑙 = 𝑅𝐻 𝜌

[cm 2/V ∙ s] (3.3) ここで、(3.1)式におけるバランスファクター f(r)は(3.4)式で表される方向比 r を用いて、 (3.5)式が成立するように回帰的に求められる。このとき、方向比 r を 1 より大きくなるように 求める。サンプル各辺および電極の対称性が理想的である場合 r=1, f(r)=1 となり、f(r)=1 が成 立しない場合は 0 ≤ f(r) ≤1 の範囲で f(r)を求める。 半導体膜 基板 電極 (a) 電極1 (b) 電極2 電極4 電極3 8 mm 1 0 m m 1 mm

21 𝑟 = |(𝑅𝑎+ 𝑅𝑏+ 𝑅𝑐+ 𝑅𝑑) (𝑅𝑒+ 𝑅𝑓+ 𝑅𝑔+ 𝑅ℎ) | または |(𝑅𝑒+ 𝑅𝑓+ 𝑅𝑔+ 𝑅ℎ) (𝑅𝑎+ 𝑅𝑏+ 𝑅𝑐+ 𝑅𝑑) | (3.4) cosh (𝑟 − 1 𝑟 + 1∙ ln 2 𝑓(𝑟)) = 1 2∙ 𝑒𝑥𝑝 ( ln 2 𝑓(𝑟)) (3.5) また、ホール係数 RHは(3.6)式で表される。このとき、磁場の強度を B [T]と置く。 𝑅𝐻 = 𝑡 𝐵∙ 1 8|𝑅𝑖− 𝑅𝑚+ 𝑅𝑗−𝑅𝑛+ 𝑅𝑘−𝑅𝑜+𝑅𝑙− 𝑅𝑝| × 10 4 (3.6)

3.2.2 測定装置構成

抵抗値測定には半導体パラメータアナライザ Agilent 4156C を用い、測定 a ~ p における電流 印加端子や電圧測定端子の切り替えにはスイッチメインフレーム KEYSIGHT E5250A、電磁石に は TAMAKAWA TM-YS3FA’ 02 型、電磁石用電源には Matsusada POKF20-20 を使用した。また、 本装置は環境試験としての冷却測定が可能であり、結露防止用の真空ポンプとして Pfeiffer Vacuum D-35614 Asslar を用い、排気性能は 1 時間後におよそ 2×10-2 Pa、24 時間後におよそ 4×10-4 Pa であった。真空ポンプを除く各種装置の操作は Agilent VEE Pro 9.2 で作製したプログラム

により半自動的に行い、 I) オーミック接触確認、II) 対辺抵抗値測定、III) ホール抵抗値測定の 手順で行った。 I) オーミック接触確認では、半導体層と金属電極間にオーミック接触が取れていることを確 認する。図 3.1(b)に示したサンプルの一辺に対して、スイープモードにより電流値を任意の範 囲で印加し、対応する電圧値を計測する。得られた電流値と電圧値が比例関係にない場合は、電 圧・電流値の変動による抵抗値の不安定性を招くため本評価には適さない。この測定を 4 辺全て で行いすべての辺でオーミック接触が取れていることを確認し、また各辺のバラツキに問題が見 られない場合は測定可能と見なした。 II) 対辺抵抗値測定では、上記した対辺抵抗値測定(測定 a ~ h)を行った。実際の測定ではサ ンプリングモードにより 1 秒間隔で計 15 回測定を行い、得られた抵抗値の平均値を計算で用い る。したがって、サンプリング電流が非常に小さい(抵抗値が高い)場合は電流が安定するまで の待機時間(ホールドタイム)を設けた。ホールドタイムの目安としては、サンプリング電流 10 nA では 30 秒、100 nA では 15 秒、1 μA 以上では 3 秒を用いており、測定初期のノイズ対策とし て最低でも 3 秒は待機した。 III) ホール抵抗値測定では上記の測定 h ~ p を行い、II)と同様にサンプリング測定を行った。 ホールドタイムに関しても同様の基準を用いた。また、本測定器における測定磁場は 0.4 T であ り、この時の磁極間距離は 40 mm、電磁石の駆動電流は 14.2 A である[7]。 最後に主な装置仕様を表 3.1 にまとめる。尚、測定可能値は一辺 10 mm の正方形をした IGZO 膜(45 nm)測定時の値である。キャリア濃度の測定可能値は 1016 cm-3以上であり従来本研究グ ループで用いてきた装置と比較し 2 桁低いキャリア濃度の測定が可能となった。しかし、TFT 動作が可能なキャリア濃度領域(1012 ~1015 cm-3)の測定は依然として困難である。一方、体積

22 抵抗率に関しては 105 Ω∙cm まで測定可能であり、TFT 動作が可能な領域付近の測定が可能であ った。したがって本研究では主に体積抵抗率に関して議論を行っていくが、本来はキャリア濃 度やホール効果移動度に関して同時に議論されることが望ましい。より低いキャリア濃度を得 るための方法としては、磁極間距離の短縮、電磁石印加電流の増大により磁場の強度を上げる ことが挙げられる。本測定器使用の電磁石の最大駆動電流は 15 A であり、磁極間距離は工夫す ることで 36 mm ~30 mm 程度まで近づけられると見られ、以上の変更により磁場は 0.5 T 程度ま で増大が見込めるがその効果に関しては不明である。また、抵抗率測定に関し、サンプルの一 辺の短縮や半導体層の膜厚を厚くすることにより抵抗値を低下させることで、各辺のバラツキ を抑制し信憑性の高い数値を取ることに有効と考えられる。また、より高い抵抗率の測定を可 能にすると考えられる。 表 3.1 主な装置仕様 測定パラメータ 最大印加電圧 100 V 常用測定電流 10 nA ~100 mA スイッチフレーム リーク電流(入力ポート1-2) 約40 fA(10 V 印加) リーク電流(入力ポート3-6) 約4 nA(10 V 印加) 電磁石 磁極間隔 40 mm 電流値 14.2 A 磁場 0.4 T 排気性能 圧力(1 時間排気後) ~2×10 -2 Pa 圧力(24 時間排気後) ~4×10-4 Pa 測定可能値 測定抵抗値 105 Ω∙cm 未満 測定キャリア濃度 1016 cm-3以上

3.3 SiO

x:F 成膜が IGZO に与える影響の評価

SiOx:F 膜の IGZO 膜上への直接成膜が IGZO の電気特性に及ぼす影響を評価するため、Van der

Pauw 法による電気特性評価を行った。先にも述べたように、TFT のチャネル層として用いる場 合、IGZO 膜の抵抗率は 103 ~106 Ω∙cm の範囲が適切である[6]。したがって、本研究ではこの値を ターゲットに評価を行った。 抵抗率評価用素子として図 3.2 に示すような構造の IGZO 膜/絶縁膜積層サンプルの作製を行 った。まず、ガラス基板上へ IGZO 膜(45 nm)を DC マグネトロンスパッタ法により 2 章 3 節 中の表 2.2 に示した条件と同様に成膜し、続いて SiOx:F 膜(150 nm)を ICP-CVD により成膜温 度 350 °C にて積層した。加えて、酸素によるキャリア補償の効果に関して比較するため、SiNx:F 膜(150 nm)を基板温度 350 °C にて成膜したサンプルの作製も行った。各種絶縁膜の成膜条件

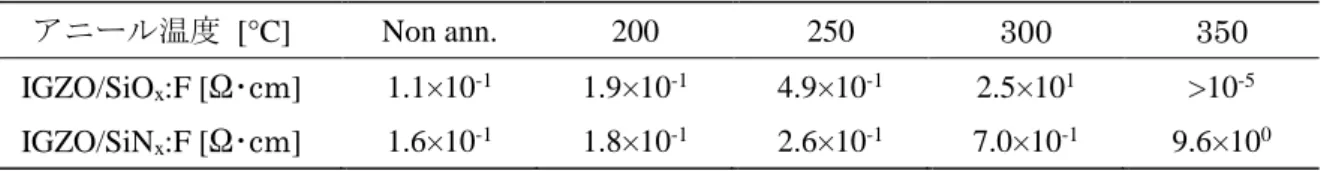

23 を表 3.2 に示す。尚、成膜条件は前章で述べた SiOx:F 膜成膜条件と異なる。絶縁膜成膜後、フォ トリソグラフィーと CF4/O2ガスを用いたドライエッチングによりコンタクトホール形成を行い、 最後に電極として Mo/Al/Mo(50/50/20 nm)成膜およびフォトリソグラフィーによる電極形成を 行った。 図 3.2 抵抗率評価用素子構造図 表 3.2 SiOx:F および SiNx:F 成膜条件 絶縁膜 SiOx:F SiNx:F 成膜温度 [ºC] 350 350 膜厚 [nm] 150 150 成膜ガス SiF4/O2 SiF4/X/N2 成膜装置 ICP-CVD ICP-CVD 図 3.3 および表 3.3 に、測定した IGZO 膜の体積抵抗率のポストアニール(大気雰囲気、1 時 間)温度依存性とその値を示す。結果より、いずれのサンプルでもポストアニール処理前ではお よそ 10-1Ω・cm の低抵抗率を示した。しかし、300 °C 以上のアニール処理後に SiO x:F サンプルで のみ抵抗率の増大が見られ、350 °C アニール後には本測定器では測定不可の高い抵抗率(>1×105 Ω・cm)を示し、SiNx:F サンプルと比較し 4 桁以上高い値を示した。

図 3.3 SiOx:F 膜および SiNx:F 膜を成膜した後の IGZO の体積抵抗率 SiOx:F, SiNx:F

IGZO(45 nm, 260 °C)

ガラス基板

24 表 3.3 図 3.3 中の IGZO 体積抵抗率値 アニール温度 [°C] Non ann. 200 250 300 350 IGZO/SiOx:F [Ω・cm] 1.1×10-1 1.9×10-1 4.9×10-1 2.5×101 >10-5 IGZO/SiNx:F [Ω・cm] 1.6×10-1 1.8×10-1 2.6×10-1 7.0×10-1 9.6×100 以上より、SiNx:F 膜を積層させた場合と比較し、SiOx:F 膜を積層させた場合はアニール処理後

に IGZO の抵抗率が増大することが確認された。この結果より、SiOx:F 膜に含まれる酸素が IGZO

膜中の酸素欠損を埋めることでキャリア生成を抑制したこと、または SiNx:F 成膜ではアニール

処理後にフッ素が IGZO 膜中へ拡散しドナーとして働くことで多量のキャリアが生成され低抵 抗率が維持されたことの 2 つの要因が推察できる。2 章 5 節で示した PSL にフッ素含有絶縁膜を

用いた際の SIMS によるフッ素濃度評価(図 2.5)では、SiOx:F PSL を用いた際のフッ素濃度に

比較し、SiOx:F/SiNx:F 積層 PSL 成膜した際により多量のフッ素が拡散していた。よって、今回

SiOx:F 膜にて IGZO 抵抗率の増大が確認された理由としては、SiNx:F と比較しフッ素拡散量が少

ないために過剰なキャリア生成が起こらなかったことが主要因であると考えられる。また本評価 により、SiOx:F 膜を成膜した IGZO の抵抗率は 103 Ω・cm 以上を示したことから、SiOx:F 膜は TFT

の ESL として適用可能であることが確かめられた。

3.4 TFT の ESL 応用

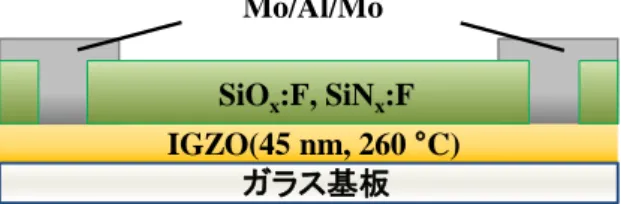

抵抗率評価の結果 SiOx:F 膜は TFT の ESL として適用可能であることが確認されたため、実際 に IGZO TFT への応用を試みた。図 3.4 に作製した IGZO TFT の構造を示す。TFT 作製は 2 章 3 節で述べたプロセス手順と同様に行い、IGZO 膜上へのフッ素含有絶縁膜形成が TFT 特性に及ぼ す影響を評価するため、ESL 材料を SiOx:F 膜に変更した。また、本サンプルではパッシベーシ ョン層(PSL)の形成は行わなかった。TFT 作製後、350 °C、1 時間のポストアニール処理を窒素 雰囲気と大気雰囲気中にて行った後、伝達特性および信頼性の評価を行った。図 3.4 ESL に SiOx:F 膜を用いた IGZO TFT の断面模式図

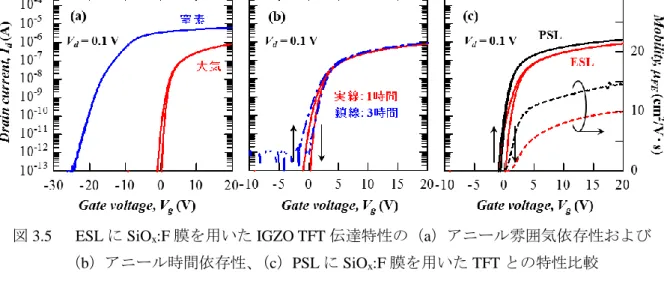

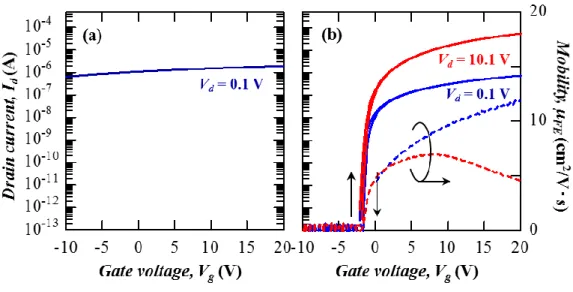

図 3.5(a-c)および表 3.4 に ESL に SiOx:F 膜を用いた IGZO TFT の伝達特性およびその特性値

を示す。図 3.5(a)に示すように、窒素雰囲気でアニール処理を行った TFT の閾値電圧(Vth) ガラス基板Cr (50 nm) SiOx:H (150 nm) IGZO (45 nm) ITO (50 nm) SiOx:F 膜厚: 200 nm 成膜温度: 350 °C 成膜装置: ICP-CVD

25 は非常に負側での立ち上がりを見せた。この結果より、SiOx:F 膜の IGZO チャネル上へ直接形成 は、IGZO 膜中の過剰なキャリア生成を引き起こしている可能性が考えられる。大気雰囲気によ るアニール処理により IGZO 膜への酸素補償を行った結果 Vth=0 V 付近での正常な立ち上がり を示したことからも、SiOx:F 成膜により IGZO 膜中キャリア濃度が増大していると考えられる。 また、アニール処理時間延長によるフッ素拡散の影響に関して評価を行った結果、図 3.5(b) に示すようにサブスレッショルドスイング値(S 値)やヒステリシス(ΔVH)の増大が見られ、 加えて図 3.5(c)に示すように PSL に SiOx:F 膜を用いた TFT との比較においても S 値、ΔVHの 増大が見られ、伝達特性の改善は得られなかった。

図 3.5 ESL に SiOx:F 膜を用いた IGZO TFT 伝達特性の(a)アニール雰囲気依存性および

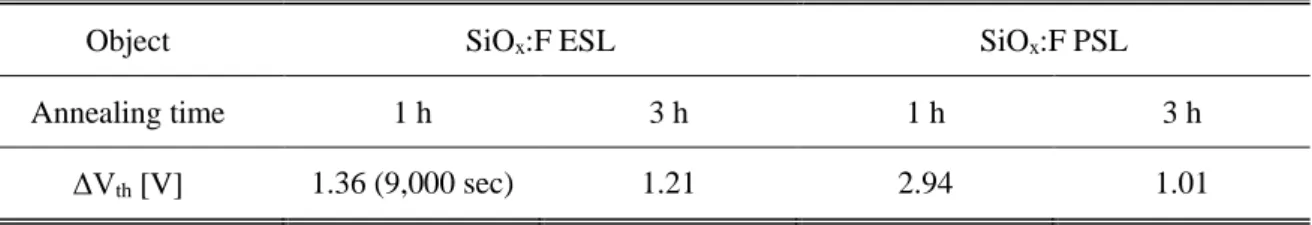

(b)アニール時間依存性、(c)PSL に SiOx:F 膜を用いた TFT との特性比較 表3.4 図 3.5(a, b)中の特性値 Annealing condition 窒素(1 h) 大気(1 h) 大気(3 h) μFE [cm2/Vs] - 10.0 10.9 S 値 (Id: 10-100 pA) [V/dec.] 1.56 0.59 0.88 Vth (Vg at Id = 1 nA) [V] -18.71 1.31 0.97 ΔVH (Vg at Id = 1 nA) [V] - 0.49 1.09 次に、ポジティブゲートバイアス熱ストレス(PBTS)試験を行った。PBTS として、加熱ステ ージにより 100 °C の基板加熱を行いつつゲート電極に 20 V のストレス電圧を合計 10,000 秒印 加し、ストレス印加前後の閾値電圧のシフト量(ΔVth)の評価を行った。 図 3.6(a, b)に、大気雰囲気中 350 °C のアニール処理をそれぞれ 1 時間、3 時間行った後の PBTS 試験結果を示す。また、SiOx:F ESL および SiOx:F PSL を用いた際の PBTS 試験後の ΔVthの

比較を表 3.5 にまとめた。尚、1 時間アニール後の SiOx:F ESL の結果のみ測定が途中で中断され

ていたため 9,000 秒後の測定結果を示す。結果より、SiOx:F ESL を用いた IGZO TFT では 1 時間

アニール後に 1.36 V の ΔVthを示し、SiOx:F PSL を用いた TFT の 3 時間アニール後と同等の値を

示した。しかし SiOx:F ESL を用いた TFT における 3 時間アニール後の ΔVthは 1.21 V であり、1

26

図 3.6 ESL に SiOx:F 膜を用いた IGZO TFT の(a)1 時間アニール処理後および

(b)3 時間アニール処理後の PBTS(100 °C, Vg=20 V)信頼性

表 3.5 PBTS 試験後の閾値電圧シフト量(ΔVth)の比較

Object SiOx:F ESL SiOx:F PSL

Annealing time 1 h 3 h 1 h 3 h

ΔVth [V] 1.36 (9,000 sec) 1.21 2.94 1.01

3.5 考察および今後の展望

以上をまとめると、PBTS 試験よりアニール処理時間に関わらず SiOx:F ESL を用いた IGZO

TFT では比較的良好な PBTS 信頼性が得られたものの、アニール時間の延長による更なる改善は 見られなかった。フッ素含有 PSL で見られたアニール時間の延長による特性・信頼性向上が得 られなかった理由としては、ESL 中におけるフッ素はある程度安定な結合を形成しているために 熱拡散が起きなかったことが原因の一つと考えられる。また、フッ素含有 PSL の場合は、ESL に SiOx:H 膜を用いていたことから、ESL に含まれる水素が欠陥を補償することによる信頼性改善 も同時に生じていると考えられる[8]。加えて初期特性評価より、過剰なキャリア供給や S 値、ヒ ステリシスの劣化が確認されたことから、フッ素含有絶縁膜形成が IGZO TFT に与える影響はフ ッ素拡散に伴う欠陥補償のみとは言えない。したがって、今後は水素やフッ素の単一系と共存系 の特性比較や、SiOx:F の直接成膜を行った際の界面品質評価(酸素欠損、金属-フッ素結合)や絶 縁膜中のフッ素の状態(イオン、分子)等の分析を行い、IGZO 単膜特性や TFT 特性との相関関 係の理解を深めていくことがフッ素含有絶縁膜による IGZO TFT の特性・信頼性制御技術を達成 するためには必須といえる。

27

参考文献

[1] Z. Ye, and M. Wong, “Characteristics of plasma-fluorinated zinc oxide thin-film transistors,” IEEE Electron Device Lett., 33 (2012) 1147.

[2] L. X. Qian and P. T. Lai, “Fluorinated InGaZnO thin-film transistor with HfLaO gate dielectric,” IEEE Elec. Dev. Lett., 35 (2014) 363.

[3] J. Jiang et al., “Self-aligned bottom-gate In–Ga–Zn–O thin-film transistor with source/drain regions formed by direct deposition of fluorinated silicon nitride”, IEEE Electron Device Lett., 35 (2014) 933. [4] 薄膜材料デバイス研究会 編, “薄膜トランジスタ”, コロナ社, (2008).

[5] 日新電機㈱提供資料, 測定データの処理と評価の方法

[6] T. Kamiya, and H. Hosono, “Roles of Hydrogen in Amorphous Oxide Semiconductor”, ECS Transactions, 54 (2013) 103.

[7] 玉川製作所㈱, “TM-YS3FA’02 型電磁石検査報告書”, (2015)

[8] Y. Hanyu et al., “Hydrogen passivation of electron trap in amorphous In-Ga-Zn-O thin-film transistors”, Appl. Phys. Lett., 103 (2013) 202114.

28

第 4 章

塗布型有機絶縁膜を用いた IGZO TFT の

低温形成

4.1 フレキシブル TFT への要求

1 章 3 節 2 項で述べたように、TFT を直接フレキシブル基板上に形成する場合には、プロセス 温度をフレキシブル基板の耐熱温度以下に抑える必要がある。フレキシブル TFT 用の基板とし て PEN(polyethylene naphthalate)フィルムは低コスト、柔軟性に富む、壊れにくいなどの特徴が あり、実用性の面で有望な素材であるが、一方で耐熱温度が低い(~155 °C)という課題がある。 一般的な IGZO TFT のゲート絶縁膜(GI)にはプラズマ化学気相堆積(PE-CVD)法により 成膜した酸化シリコン(SiOx)膜が用いられるが、GI として十分な絶縁耐圧、欠陥密度を得 るためには通常 300 ºC 以上で成膜を行う必要があり、PEN フィルム上に直接 SiOx膜を形成 することは困難と言える。故に、PEN フィルム上へ直接 IGZO TFT を形成するためには、150 ºC 程度のプロセス温度にて高品質な GI を形成する必要がある。加えて、実際のフレキシブ ル TFT の柔軟性は基板のみならず TFT を構成する材料によっても制限されるため、SiOxを 含む無機材料は柔軟性に劣りフレキシブル TFT 応用には適さない[1]。 以上の問題に対して本研究グループでは、塗布型有機絶縁膜を TFT の GI およびチャネル保護 膜(PL: Protection Layer)、層間絶縁層(IL: Inter Layer)として用いた無機/有機ハイブリット IGZO TFT の作製を行い、フロントチャネル界面形成プロセスを改善することにより、実用性の高い自 己整合(SA: Self-align)型・トップゲート(TG: Top-gate)構造を採用しながら、最高プロセス温度 150 ºC にて良好な TFT 特性を実現したことを報告している[2]。この成果を踏まえ、本研究 では塗布型有機絶縁膜を用いた無機/有機ハイブリット IGZO TFT の信頼性評価および特性・信 頼性の更なる改善に向けた制御技術に関して研究を行った。

4.2 塗布型有機絶縁膜および TFT 構造の選定理由

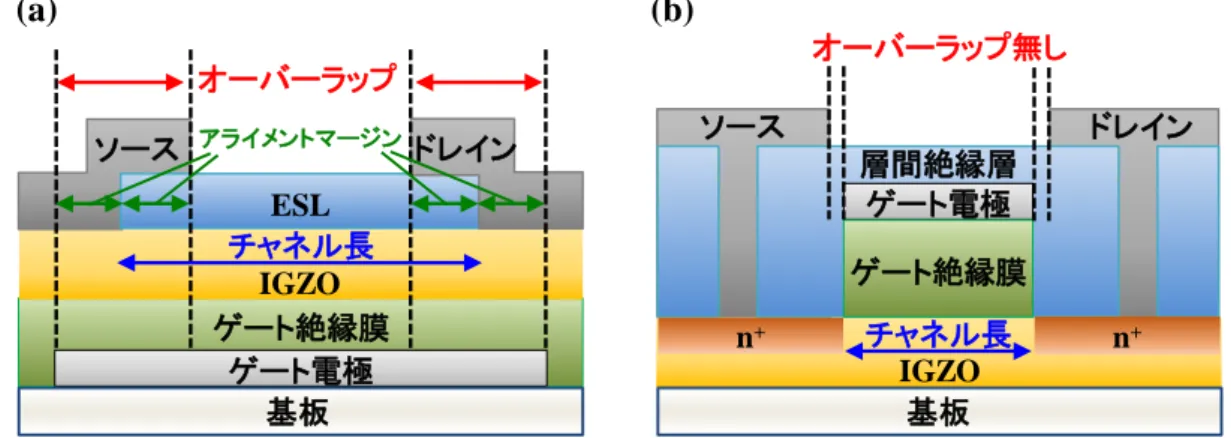

IGZO TFT の PL および GI、IL として塗布型有機絶縁膜を採用した理由として、200 °C 以下の 硬化処理により十分な絶縁耐圧が得られる点、スピンコート法による簡便かつプラズマダメージ レスなプロセスが可能である点、無機材料と比較し高いフレキシビリティを有する点が挙げられ る。29 また、SA-TG 構造の長所は、ソース・ドレイン(S/D)電極とゲート電極間のオーバーラップ により形成される寄生容量(Cp)の抑制およびチャネル長の短縮ができる点にある。一般的な IGZO TFT では、図 4.1(a)に示すエッチングストッパー層(ESL)を有するボトムゲート構造 が用いられている。しかし、この構造の TFT 作製におけるフォトリソグラフィー工程には、ESL とゲート電極間、ESL と S/D 電極間とで 2 つのアライメントマージンを設ける必要がある。これ らのアライメントマージンによって、ゲート電極と S/D 電極が重なる領域で Cpが生じ、回路の 高速駆動や大面積化を困難にする他、アライメントマージンの分だけチャネル長が長くなること から TFT の高精細化を困難にする[3]。対して図 4.1(b)に示すセルフアライン型は、ゲート電 極をマスクにしてゲート絶縁膜をエッチングし、半導体層を選択的に低抵抗化することで S/D(n+) 領域として用いる。したがって、アライメントマージンを必要とせず、電極間の重なりをなくす ことができるため、Cpの低減、チャネル長の縮小が可能となる。

図 4.1 (a)ESL を有するボトムゲート構造および(b)SA-TG 構造 IGZO TFT の断面模式図

4.3 セルフアライン型・トップゲート(SA-TG)構造 TFT の

低温形成

4.3.1 SA-TG 構造 IGZO TFT 作製プロセス

本研究では、SA-TG 構造 IGZO TFT の PL および GI、IL として Zeocoat®(ES2110、日本ゼオ

ン株式会社)を用いた。Zeocoat®は、150 °C での熱硬化が可能なシクロオレフィンポリマーであ

り、ポリマー中の極性官能基が少なく、吸水性が低いことから、フレキシブル TFT の GI に求め

られる要求を満たす有機絶縁膜材料であると言える[4]。尚、本研究における Zeocoat®の硬化処理

にはホットプレートを用い、1 次硬化処理後直ちに 2 次硬化処理を実施した。また、C-V 測定よ り算出された Zeocoat®の比誘電率は 3.3 である。

図 4.2 に Zeocoat®を用いた SA-TG 構造 IGZO TFT の通常作製プロセスを示す。初めに①ガラ

ゲート電極 ゲート絶縁膜 ソース ドレイン ESL チャネル長 オーバーラップ 基板 アライメントマージン IGZO