2012 年 6 月 Altera Corporation

CV-51001-2.0 Device Overview

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

101 Innovation Drive San Jose, CA 95134 www.altera.com Feedback Subscribe ISO 9001:2008 Registered Cyclone®V デバイスは、消費電力、コスト、「time-to-market」の要件を削減すること、 および量産かつコスト重視のアプリケーション用の帯域幅の要件を向上させること に同時に対応するためにデザインされています。 統合トランシーバおよびハード・メモリ・コントローラで強化された Cyclone V デバ イスは、工業用、ワイヤレスとワイヤライン、軍用および自動車市場でのアプリ ケーションに適しています。

重要な利点

表 1に、Cyclone V デバイス・ファミリの重要な利点を示します。 表 1. Cyclone V デバイス・ファミリの重要な利点 利点 サポートする機能 低消費電力化 ■ TSMC の 28 nm 低消費電力(28LP)プロセス上で構築されて、さまざまな ハード IP(intellectual property)ブロックを含む ■ 前世代のデバイスよりも最大 40% の低消費電力化 改良されたロジック統合およ び差動機能 ■ 8 入力のアダプティブ・ロジック・モジュール(ALM) ■ 最大 13.59 メガビット(Mb)のエンベデッド・メモリ ■ 可変精度ディジタル信号処理(DSP)ブロック 向上された帯域幅の容量 ■ 3.125 Gbps および 5 Gbps のトランシーバ ■ ハード・メモリ・コントローラ 統合された ARM® Cortex™-A9 MPCore プロセッサを持ってい るハード・プロセッサ・シス テム(HPS) ■ シングルの Cyclone V SoC(system-on-a-chip)FPGA 内で、シングル・コアまたはデュアル・コア ARMCortex-A9 MPCore プロセッサ、ハード IP、および FPGA を緊密に統合 ■ プロセッサおよび FPGA ファブリックの間の統合されたデータ・コヒーレ ンシを持っている 128 Gbps 以上のピーク帯域幅をサポート 最低のシステム・コスト ■ 動作するコア電圧を 2 つのみ必要 ■ 低コストのワイヤボンド・パッケージに使用可能 ■ プロトコルを介するコンフィギュレーション(CvP)およびパーシャル・ コンフィギュレーションなどの革新的なコスト節約機能を含む

機能の概要

表 2に、Cyclone V の機能の概要を示します。 表 2. Cyclone V デバイスの機能の概要(その 1) 機能 説明 テクノロジ ■ TSMC の 28 nm の低消費電力(28LP)プロセス・テクノロジ ■ 1.1 V のコア電圧 パッケージ ■ ワイヤボンドの低ハロゲン・パッケージ ■ 異なるデバイス集積度の間でのシームレスなマイグレーション用の高い互換性のパッ ケージ・フットプリントを持っている複数のデバイス集積度 ■ RoHS 対応のオプション 高性能の FPGA ファブリック 4 つのレジスタで拡張された 8 入力の AML 内部メモリ・ブ ロック ■ M10K— ソフト誤りコード(ECC)を持っている 10 Kb のメモリ・ブロック ■ メモリ・ロジック・アレイ・ブロック(MLAB)—MLAB メモリとして最大 25% の ALM を使用できる LUTRAM に分配される 640 ビット エンベデッド・ ハード IP ブロッ ク 可変精度 DSP ■ 同じ可変精度 DSP ブロックでの 3 つの信号処理精度レベル(3 つの 9 x 9、2 つの 18 x 18、または 1 つの 27 x 27 のマルチプライヤ)用 のネイティブ・サポート ■ 64 ビットのアキュムレータおよびカスケード ■ エンベデッド内部の係数メモリ ■ 効率を向上させるプリ加算器 / 減算器 メモリ・コント ローラ 16 ビットおよび 32 ビットの ECC を持っている DDR3、DDR2、および LPDDR2 エンベデッド・ トランシーバ I/O マルチファンクション・サポート、エンドポイント、およびルート・ポートを持っている PCI Express®(PCIe®)Gen2 および Gen1(x1、

x2、または x4)のハード IP クロック・ネット ワーク ■ 550 MHz のグローバル・クロック・ネットワーク ■ グローバル、エリアおよびペリフェラル・クロック・ネットワーク ■ ダイナミックな消費電力を低減するためにパワー・ダウンできる未使用のクロック・ ネットワーク PLL(Phase-locked loops) ■ クロック合成の精度、クロック遅延補償、およびゼロ遅延バッファ(ZDB) ■ 整数モードおよび小数モード FPGA 汎用 I/O (GPIO) ■ 875 Mbps の LVDS レシーバおよび 840 Mbps の LVDS トランシーバ ■ 400 MHz/800 Mbps の外部メモリ・インタフェース ■ すべての主要なシングル・エンドおよび差動 I/O 規格のサポート ■ On-chip termination(OCT) ■ 最大 16 mA のドライブ強度までの 3.3 V のサポート 低消費電力で高速 のシリアル・イン タフェース ■ 614 Mbps ~ 5.0 Gbps の統合トランシーバ速度 ■ トランスミッタ・プリエンファシスおよびレシーバ・イコライゼーション ■ 個々のチャネルのダイナミック・パーシャル・リコンフィギュレーション

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation HPS (Cyclone V SE、 SX、および ST デ バイスのみ)

■ シングル・コアまたはデュアル・コア ARM Cortex-A9 MPCore プロセッサ — 対称および

非対称のマルチ処理のサポートを持っている最大 800 MHz の最大周波数 ■ インタフェース・ペリフェラル —10/100/1000 のイーサネット MAC(EMAC)、USB 2.0、 On-The-GO(OTG)コントローラ、クワッド・シリアル・ペリフェラル・インタフェー ス(QSPI)フラッシュ・コントローラ、NAND フラッシュ・コントローラ、Secure Digital/MultiMediaCard(SD/MMC)コントローラ、UART、コントローラ・エリア・ネッ トワーク(CAN)、シリアル・ペリフェラル・インタフェース(SPI)、I2C インタ フェース、および最大 85 HPS の GPIO インタフェース ■ システム・ペリフェラル — 汎用タイマ、ウォッチドッグ・タイマ、ダイレクト・メモ リ・アクセス(DMA)コントローラ、FPGA コンフィギュレーション・マネージャ、お よびクロック・マネージャとリセット・マネージャ ■ オンチップ RAM およびブート ROM ■ HPS–FPGA ブリッジ —FPGA ファブリックが HPS 内のスレーブに(あるいはその逆に)ト ランザクションを発行できるようにする FPGA-to-HPS、to-FPGA、および軽量 HPS-to-FPGA ブリッジを含む

■ FPGA-to-HPS SDRAM コントローラ・サブシステム —HPS SDRAM コントローラのマルチ

ポート・フロント・エンド(MPFE)に対してコンフィギュレーション可能なインタ フェースを提供

■ ARM CoreSight™ JTAG デバッグ・アクセス・ポート、トレース・ポート、およびオン

チップ・トレース・ストレージ コンフィギュレー ション ■ 改ざん保護 — 貴重な IP 投資を保護するための包括的なデザイン保護 ■ 拡張度暗号化標準(AES)デザイン・セキュリティ機能 ■ CvP ■ FPGA のパーシャルおよびダイナミック・リコンフィギュレーション ■ アクティブ・シリアル(AS)x1 および x4、ファースト・パッシブ・パラレル(FPP) x8 および x16、パッシブ・シリアル(PS)、および JTAG オプション 表 2. Cyclone V デバイスの機能の概要(その 2) 機能 説明

デバイスのバリアントおよびパッケージ

Cyclone V デバイス・ファミリは、表 3に示すように、6 つのバリアントで使用可能 です。Cyclone V E

このセクションでは、Cyclone V E デバイスに使用可能なオプション、最大リソース 数、およびパッケージ・プランを説明します。使用可能なオプション

図 1に、サンプル・オーダリング・コードおよび Cyclone V E デバイスに使用可能な オプションを示します。 表 3. Cyclone V デバイス・ファミリのデバイス・バリアント バリアント 説明 Cyclone V E 幅広い汎用ロジックおよび DSP アプリケーション用にシステム・コ ストおよび消費電力の要件を最小限に抑えるように最適化されてい ます。 Cyclone V GX 614 Mbps ~ 3.125 Gbps のトランシーバ・アプリケーション用にシス テム・コストおよび消費電力の要件を最小限に抑えるように最適化 されています。 Cyclone V GT 5 Gbps のトランシーバ・アプリケーション用としてコストおよび消 費電力の要件が FPGA 業界で最小です。Cyclone V SE 統合 ARM ベースの HPS を持っている SoC FPGA です。

Cyclone V SX 統合 ARM ベースの HPS および 3.125 Gbps のトランシーバを持ってい る SoC FPGA です。 Cyclone V ST 統合 ARM ベースの HPS および 5 Gbps のトランシーバを持っている SoC FPGA です。 図 1. サンプル・オーダリング・コードおよび Cyclone V E デバイスに使用可能なオプ ション ̶ 暫定仕様 Family Signature

Embedded Hard IPs

Package Type

Package Code

Operating Temperature

FPGA Fabric Speed Grade Optional Suffix

Indicates specific device options or shipment method

E : Enhanced logic/memory

B : No hard PCIe or hard memory controller F : No hard PCIe and maximum

2 hard memory controllers

5C : Cyclone V

F : FineLine BGA (FBGA) U : Ultra FineLine BGA (UBGA)

FBGA Package Type 17 : 256 pins 23 : 484 pins 27 : 672 pins 31 : 896 pins UBGA Package Type 15 : 324 pins 19 : 484 pins C : Commercial (TJ = 0° C to 85° C) I : Industrial (TJ = -40° C to 100° C) A : Automotive (TJ = -40° C to 125° C) 6 (fastest) 7 8 N : Lead-free packaging ES : Engineering sample 5C E F A9 F 31 C 7 N Member Code Family Variant A2 : 25K logic elements A4 : 49K logic elements A5 : 77K logic elements A7 : 149.5K logic elements A9 : 301K logic elements

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

最大リソース

表 4に、Cyclone V E の最大リソース数を示します。パッケージ・プラン

表 5に、Cyclone V SE のパッケージ・プランを示します。 表 4. Cyclone V E の最大リソース数 ̶ 暫定仕様 リソース e 各コード A2 A4 A5 A7 A9 ロジック・エレメント(LE)(K) 25 49 77 149.5 301 ALM 9,434 18,480 29,080 56,480 113,560 レジスタ 37,736 73,920 116,320 225,920 454,240 メモリ(Kb) M10K 1,760 3,080 4,460 6,860 12,200 MLAB 196 303 424 836 1,717 可変精度 DSP ブロック 25 66 150 156 342 18 x 18 乗算器 50 132 300 312 684 PLL 4 4 6 7 8 GPIO 224 224 240 480 480 LVDS 56 56 84 120 140 ハード・メモリ・コントローラ 1 1 2 2 2 表 5. Cyclone V E デバイスのパッケージ・プラン ̶ 暫定仕様 各コード F256 (17 mm) U324 (15 mm) U484 (19 mm) F484 (23 mm) F672 (27 mm) F896 (31 mm)GPIO GPIO GPIO GPIO GPIO GPIO

A2 128 176 224 224 — —

A4 128 176 224 224 — —

A5 — — 224 240 — —

A7 — — 240 240 336 480

Cyclone V GX

このセクションでは、Cyclone V GX デバイスに使用可能なオプション、最大リソース 数、およびパッケージ・プランを説明します。使用可能なオプション

図 2に、サンプル・オーダリング・コードおよび Cyclone V GX デバイスに使用可能な オプションを示します。最大リソース

表 6に、Cyclone V GX の最大リソース数を示します。 図 2. サンプル・オーダリング・コードおよび Cyclone V GX デバイスに使用可能なオプ ション ̶ 暫定仕様 表 6. Cyclone V GX デバイスの最大リソース数 ̶ 暫定仕様(その 1) リソース 各コード C3 C4 C5 C7 C9 LE (K) 31.5 50 77 149.5 301 ALM 11,900 18,868 29,080 56,480 113,560 レジスタ 47,600 75,472 116,320 225,920 454,240 メモリ(Kb) M10K 1,190 2,500 4,460 6,860 12,200 MLAB 159 295 424 836 1,717 可変精度 DSP ブロック 51 70 150 156 342 18 x 18 乗算器 102 140 300 312 684 PLL(1) 4 6 6 7 8 3 Gbps のトランシーバ 3 6 6 9 12 GPIO 208 336 336 480 560 Family Signature Embedded Hard IPsTransceiver Count Transceiver Speed Grade Package Type Package Code Operating Temperature FPGA Fabric Speed Grade Optional Suffix

Indicates specific device options or shipment method GX : 3-Gbps transceivers

B : No hard PCIe or hard memory controller F : Maximum 2 hard PCIe and

maximum 2 hard memory controllers 5C : Cyclone V C3 : 31.5K logic elements C4 : 50K logic elements C5 : 77K logic elements C7 : 149.5K logic elements C9 : 301K logic elements B : 3 C : 6 D : 9 E : 12 6 : 3.125 Gbps 7 : 2.5 Gbps

F : FineLine BGA (FBGA) U : Ultra FineLine BGA (UBGA)

FBGA Package Type 23 : 484 pins 27 : 672 pins 31 : 896 pins 35 : 1,152 pins UBGA Package Type 15 : 324 pins 19 : 484 pins C : Commercial (TJ = 0° C to 85° C) I : Industrial (TJ = -40° C to 100° C) A : Automotive (TJ = -40° C to 125° C) 6 (fastest) 7 8 N : Lead-free packaging ES : Engineering sample 5C GX F C9 E 6 F 35 C 7 N Member Code Family Variant

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

パッケージ・プラン

表 7に、Cyclone V GX のパッケージ・プランを示します。 LVDS 52 84 84 120 140 PCIe ハード IP ブロック 1 2 2 2 2 ハード・メモリ・コント ローラ 1 2 2 2 2 表 6の注: (1) PLL カウント数には、汎用小数 PLL およびトランシーバ小数 PLL が含まれています。 表 7. Cyclone V GX デバイスのパッケージ・プラン ̶ 暫定仕様 各コード U324 (15 mm) U484 (19 mm) F484 (23 mm) F672 (27 mm) F896 (31 mm) F1152 (35 mm)GPIO XCVR GPIO XCVR GPIO XCVR GPIO XCVR GPIO XCVR GPIO XCVR

C3 112 3 208 3 208 3 — — — — — — C4 — — 224 6 240 6 336 6 — — — — C5 — — 224 6 240 6 336 6 — — — — C7 — — 240 6 240 6 336 9 480 9 — — C9 — — — — 224 6 336 9 480 12 560 12 表 6. Cyclone V GX デバイスの最大リソース数 ̶ 暫定仕様(その 2) リソース 各コード C3 C4 C5 C7 C9

Cyclone V GT

このセクションでは、Cyclone V GT デバイスに使用可能なオプション、最大リソース 数、およびパッケージ・プランを説明します。使用可能なオプション

図 3に、サンプル・オーダリング・コードおよび Cyclone V GT デバイスに使用可能な オプションを示します。最大リソース

表 8に、Cyclone V GT の最大リソース数を示します。 図 3. サンプル・オーダリング・コードおよび Cyclone V GT デバイスに使用可能なオプ ション ̶ 暫定仕様 表 8. Cyclone V GT デバイスの最大リソース数 ̶ 暫定仕様(その 1) リソース 各コード D5 D7 D9 LE (K) 77 149.5 301 ALM 29,080 56,480 113,560 レジスタ 116,320 225,920 454,240 メモリ(Kb) M10K 4,460 6,860 12,200 MLAB 424 836 1,717 可変精度 DSP ブロック 150 156 342 18 x 18 乗算器 300 312 684 PLL(1) 6 7 8 5 Gbps のトランシーバ 6 9 12 GPIO 336 480 560 Family Signature Embedded Hard IPsTransceiver Count Transceiver Speed Grade Package Type Package Code Operating Temperature FPGA Fabric Speed Grade Optional Suffix

Indicates specific device options or shipment method GT : 5-Gbps transceivers

F : 2 hard PCIe and 2 hard memory controllers 5C : Cyclone V D5 : 77K logic elements D7 : 149.5K logic elements D9 : 301K logic elements C : 6 D : 9 E : 12 5 : 5 Gbps

F : FineLine BGA (FBGA) U : Ultra FineLine BGA (UBGA)

FBGA Package Type 23 : 484 pins 27 : 672 pins 31 : 896 pins 35 : 1,152 pins UBGA Package Type 19 : 484 pins C : Commercial (TJ = 0° C to 85° C) I : Industrial (TJ = -40° C to 100° C) A : Automotive (TJ = -40° C to 125° C) 6 (fastest) 7 8 N : Lead-free packaging ES : Engineering sample 5C GT F D9 E 5 F 35 C 7 N Member Code Family Variant

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

パッケージ・プラン

表 9に、Cyclone V GT のパッケージ・プランを示します。 LVDS 84 120 140 PCIe ハード IP ブロック 2 2 2 ハード・メモリ・コント ローラ 2 2 2 表 8の注: (1) PLL 数には、汎用小数 PLL およびトランシーバ小数 PLL が含まれています。 表 9. Cyclone V GT デバイスのパッケージ・プラン ̶ 暫定仕様 各コード U484 (19 mm) F484 (23 mm) F672 (27 mm) F896 (31 mm) F1152 (35 mm)GPIO XCVR GPIO XCVR GPIO XCVR GPIO XCVR GPIO XCVR

D5 224 6 240 6 336 6 — — — — D7 240 6 240 6 336 9 480 9 — — D9 — — 224 6 336 9 480 12 560 12 表 8. Cyclone V GT デバイスの最大リソース数 ̶ 暫定仕様(その 2) リソース 各コード D5 D7 D9

Cyclone V SE

このセクションでは、Cyclone V SE デバイスに使用可能なオプション、最大リソース 数、およびパッケージ・プランを説明します。使用可能なオプション

図 4に、サンプル・オーダリング・コードおよび Cyclone V SE デバイスに使用可能な オプションを示します 。 ‘最大リソース

表 10に、Cyclone V SE の最大リソース数を示します。 図 4. サンプル・オーダリング・コードおよび Cyclone V SE デバイスに使用可能なオプ ション ̶ 暫定仕様 表 10. Cyclone V SE デバイスの最大リソース数 ̶ 暫定仕様(その 1) リソース 各コード A2 A4 A5 A6 LE (K) 25 40 85 110 ALM 9,434 15,094 32,075 41,509 レジスタ 37,736 60,376 128,300 166,036 メモリ (Kb) M10K 1,400 2,240 3,970 5,140 MLAB 138 220 480 621 可変精度 DSP ブ ロック 36 58 87 112 18 x 18 乗算器 72 116 174 224 FPGA PLL 4 5 6 6 HPS PLL 3 3 3 3 FPGA GPIO 145 145 288 288 Family Signature Embedded Hard IPsPackage Type Package Code Operating Temperature FPGA Fabric Speed Grade Optional Suffix

Indicates specific device options or shipment method

SE : SoC FPGA with enhanced logic/memory 5C : Cyclone V

F : FineLine BGA (FBGA) U : Ultra FineLine BGA (UBGA)

FBGA Package Type 31 : 896 pins UBGA Package Type 19 : 484 pins 23 : 672 pins C : Commercial (TJ = 0° C to 85° C) I : Industrial (TJ = -40° C to 100° C) A : Automotive (TJ = -40° C to 125° C) 6 (fastest) 7 8 Processor Cores

Omit for dual-core S : Single-core N : Lead-free packaging ES : Engineering sample 5C SE M A6 F 31 C 6 S N Member Code Family Variant A2 : 25K logic elements A4 : 40K logic elements A5 : 85K logic elements A6 : 110K logic elements B : No hard PCIe or hard

memory controller M : No hard PCIe and 1 hard

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

パッケージ・プラン

表 11に、Cyclone V SE のパッケージ・プランを示します。 HPS I/O 188 188 188 188 LVDS 31 31 72 72 FPGA ハード・メモ リ・コントローラ 1 1 1 1 HPS ハード・メモ リ・コントローラ 1 1 1 1 ARM Cortex-A9 MPCore プロセッサ シングルまたは デュアル・コア シングルまたは デュアル・コア シングルまたは デュアル・コア シングルまたは デュアル・コア 表 11. Cyclone V SE デバイスのパッケージ・プラン ̶ 暫定仕様 各コード U484 (19 mm) U672 (23 mm) F896 (31 mm)FPGA GPIO HPS I/O FPGA GPIO HPS I/O FPGA GPIO HPS I/O

A2 66 161 145 188 — — A4 66 161 145 188 — — A5 66 161 145 188 288 188 A6 66 161 145 188 288 188 表 10. Cyclone V SE デバイスの最大リソース数 ̶ 暫定仕様(その 2) リソース 各コード A2 A4 A5 A6

Cyclone V SX

このセクションでは、Cyclone V SX デバイスに使用可能なオプション、最大リソース 数、およびパッケージ・プランを説明します。使用可能なオプション

図 5に、サンプル・オーダリング・コードおよび Cyclone V SX デバイスに使用可能な オプションを示します。最大リソース

表 12に、Cyclone V SX の最大カウント数を示します。 図 5. サンプル・オーダリング・コードおよび Cyclone V SX デバイスに使用可能なオプ ション ̶ 暫定仕様 表 12. Cyclone V SX の最大カウント数 ̶ 暫定仕様(その 1) リソース 各コード C2 C4 C5 C6 LE (K) 25 40 85 110 ALM 9,434 15,094 32,075 41,509 レジスタ 37,736 60,376 128,300 166,036 メモリ(Kb) M10K 1,400 2,240 3,970 5,140 MLAB 138 220 480 621 可変精度 DSP ブロック 36 58 87 112 18 x 18 乗算器 72 116 174 224 FPGA PLL(1) 4 5 6 6 HPS PLL 3 3 3 3 3 Gbps のトランシーバ 6 6 9 9 FPGA GPIO 145 145 288 288 Family Signature Embedded Hard IPsTransceiver Count Transceiver Speed Grade Package Type Package Code Operating Temperature FPGA Fabric Speed Grade Optional Suffix

Indicates specific device options or shipment method SX : SoC FPGA with 3-Gbps transceivers

F : Maximum 2 hard PCIe controllers and 1 hard memory controller 5C : Cyclone V C2 : 25K logic elements C4 : 40K logic elements C5 : 85K logic elements C6 : 110K logic elements C : 6 D : 9 6 : 3.125 Gbps

F : FineLine BGA (FBGA) U : Ultra FineLine BGA (UBGA)

FBGA Package Type 31 : 896 pins UBGA Package Type 23 : 672 pins C : Commercial (TJ = 0° C to 85° C) I : Industrial (TJ = -40° C to 100° C) A : Automotive (TJ = -40° C to 125° C) 6 (fastest) 7 8 N : Lead-free packaging ES : Engineering sample 5C SX F C6 D 6 F 31 C 6 N Member Code Family Variant

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

パッケージ・プラン

表 13に、Cyclone V SX のパッケージ・プランを示します。 HPS I/O 188 188 188 188 LVDS 31 31 72 72 PCIe ハード IP ブロック 2 2 2 2 FPGA ハード・メモリ・コン トローラ 1 1 1 1 HPS ハード・メモリ・コン トローラ 1 1 1 1ARM Cortex-A9 MPCore プロ セッサ デュアル・ コア デュアル・ コア デュアル・ コア デュアル・ コア 表 12の注: (1) PLL には、汎用小数 PLL およびトランシーバ小数 PLL が含まれています。 表 13. Cyclone V SX デバイスのパッケージ・プラン ̶ 暫定仕様 各コード U672 (23 mm) F896 (31 mm)

FPGA GPIO HPS I/O XCVR FPGA GPIO HPS I/O XCVR

C2 145 188 6 — — — C4 145 188 6 — — — C5 145 188 9 288 188 9 C6 145 188 9 288 188 9 表 12. Cyclone V SX の最大カウント数 ̶ 暫定仕様(その 2) リソース 各コード C2 C4 C5 C6

Cyclone V ST

使用可能なオプション

図 6に、サンプル・オーダリング・コードおよび Cyclone V ST デバイスに使用可能な オプションを示します。最大リソース

表 14に、Cyclone V ST の最大リソース数を示します。 図 6. サンプル・オーダリング・コードおよび Cyclone V ST デバイスに使用可能なオプ ション ̶ 暫定仕様 表 14. Cyclone V ST デバイスの最大リソース数 ̶ 暫定仕様(その 1) リソース 各コード D5 D6 LE (K) 85 110 ALM 32,075 41,509 レジスタ 128,300 166,036 メモリ(Kb) M10K 3,970 5,140 MLAB 480 621 可変精度 DSP ブロック 87 112 18 x 18 乗算器 174 224 FPGA PLL(1) 6 6 HPS PLL 3 3 5 Gbps のトランシーバ 9 9 FPGA GPIO 288 288 HPS I/O 188 188 LVDS 72 72 Family Signature Embedded Hard IPsTransceiver Count Transceiver Speed Grade Package Type Package Code Operating Temperature FPGA Fabric Speed Grade Optional Suffix

Indicates specific device options or shipment method ST : SoC FPGA with 5-Gbps transceivers

F : Maximum 2 hard PCIe controllers and 1 hard memory controller 5C : Cyclone V D5 : 85K logic elements D6 : 110K logic elements D : 9 4 : 5 Gbps

F : FineLine BGA (FBGA)

31 : 896 pins C : Commercial (TJ = 0° C to 85° C) I : Industrial (TJ = -40° C to 100° C) A : Automotive (TJ = -40° C to 125° C) 6 (fastest) 7 8 N : Lead-free packaging ES : Engineering sample 5C ST F D6 D 4 F 31 C 6 N Member Code Family Variant

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

パッケージ・プラン

表 15に、Cyclone V ST のパッケージ・プランを示します。 PCIe ハード IP ブロック 2 2 FPGA ハード・メモリ・コン トローラ 1 1 HPS ハード・メモリ・コン トローラ 1 1ARM Cortex-A9 MPCore プロ

セッサ デュアル・コア デュアル・コア 表 14の注: (1) PLL には、汎用小数 PLL およびトランシーバ小数 PLL が含まれています。 表 15. Cyclone V ST デバイスのパッケージ・プラン ̶ 暫定仕様 各コード F896 (31 mm)

FPGA GPIO HPS I/O XCVR

D5 288 188 9 D6 288 188 9 表 14. Cyclone V ST デバイスの最大リソース数 ̶ 暫定仕様(その 2) リソース 各コード D5 D6

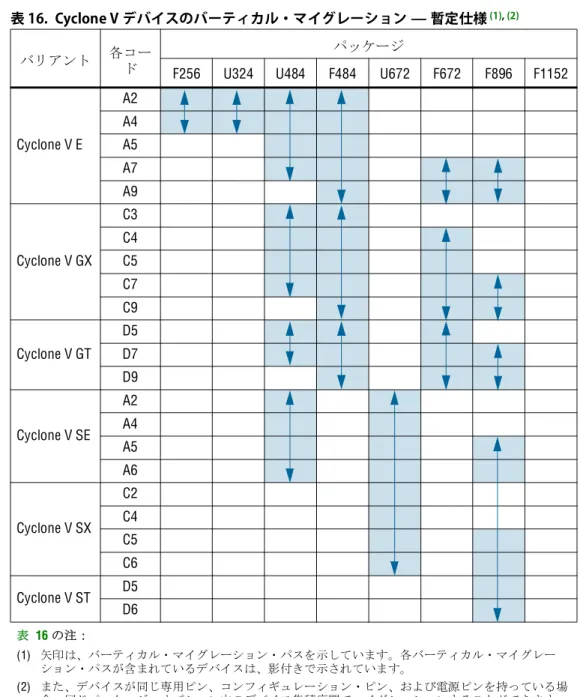

バーティカル・マイグレーション

表 16に、Cyclone V デバイスのパッケージおよび集積度間のバーティカル・マイグ

レーション機能を示します。

1 ピン・マイグレーションの互換性を確認するには、Quartus®II ソフトウェアの Pin

Planner 内にある Pin Migration View ウィンドウを使用します。

f ピン・マイグレーションの互換性の確認について詳しくは、Quartus II Handbook の

“I/O Management”の章を参照してください。

表 16. Cyclone V デバイスのバーティカル・マイグレーション ̶ 暫定仕様(1),(2)

バリアント 各コード

パッケージ

F256 U324 U484 F484 U672 F672 F896 F1152

Cyclone V E A2 A4 A5 A7 A9 Cyclone V GX C3 C4 C5 C7 C9 Cyclone V GT D5 D7 D9 Cyclone V SE A2 A4 A5 A6 Cyclone V SX C2 C4 C5 C6 Cyclone V ST D5 D6 表 16の注: (1) 矢印は、バーティカル・マイグレーション・パスを示しています。各バーティカル・マイグレー ション・パスが含まれているデバイスは、影付きで示されています。 (2) また、デバイスが同じ専用ピン、コンフィギュレーション・ピン、および電源ピンを持っている場 合、同じパッケージ・オプション内のデバイス集積度間でマイグレーションすることができます。

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

アダプティブ・ロジック・モジュール

Cyclone V デバイスは、28 nm ALM をロジック・ファブリックの基本的なビルディン グ・ブロックとして使用します。 図 7に示すように、ALM は、レジスタを多用するデザインでタイミング・クロー ジャを向上しやすくするために、また、前世代よりも高いデザイン・パッキング機 能を実現しやすくするために、4 つの専用レジスタを持っている 8 入力フラクチャブ ル・ルック・アップ・テーブル(LUT)を使用します。ユーザーは、MLAB を使用して分配されるメモリとして Cyclone V デバイス内の ALM

の最大 25% をコンフィギュレーションすることができます。詳しくは、20 ページの 「エンベデッド・メモリの容量」を参照してください。

可変精度 DSP ブロック

Cyclone V デバイスは、これらの機能をサポートする可変精度 DSP ブロックを機能さ せます。 ■ ネイティブで 9 x 9、18 x 18、および 27 x 27 ビットの範囲の信号処理精度をサポー トするようにコンフィギュレーション可能 ■ 64 ビットのアキュムレータ ■ 18 ビットおよび 27 ビット・モードの両方で使用可能なハード・プリ加算器 ■ 効率的でシストリックな有限インパルス応答(FIR)フィルタ用のカスケードさ れた出力加算器 ■ 18 ビットまたは 27 ビット・モードでの各乗算器用の深度 8 の内部係数レジスタ・ バンク ■ 完全に独立している乗算器の動作 ■ 複雑な積和ファンクションに対応するためのセカンド・アキュムレータのフィー ドバック・レジスタ 図 7. Cyclone V デバイス用の ALM Cyclone V Device 1 2 3 4 5 6 7 8 Adaptive LUT Full Adder Reg Reg Full Adder Reg Reg■ シングル精度またはダブル精度の浮動小数点演算用の効率的なサポート ■ Quartus II デザイン・ソフトウェアによるすべてのモードのインフェラビリティ 表 17に、いくつかの使用方法の例として、関連する DSP ブロック・コンフィギュ レーションを示します。 ユーザーは、独立している 3 つの 9 x 9、2 つの 18 x 18、または 1 つの 27 x 27 の乗算 器としてのコンパイル中に各 DSP ブロックをコンフィギュレーションすることがで きます。専用の 64 ビットのカスケード・バスを使用して、より高精度の DSP ファン クションを効率的に実装するために複数の可変精度 DSP ブロックをカスケードする ことができます。 表 18に、各 Cyclone V デバイスのビット精度によって可変精度 DSP リソースを示し ます。 表 17. Cyclone V デバイス用の可変精度 DSP ブロック・コンフィギュレーション 使用方法 乗算器のサイズ (ビット) DSP ブロック・ リソース ビデオ・アプリケーション用の低精度の固定小 数点 3 つの 9 x 9 1 FIR フィルタの中精度の固定小数点 2 つの 18 x 18 1 FIR フィルタおよび一般的な DSP の使用方法 累積付きの 2 つの18 x 18 1 高精度の固定小数点または浮動小数点の実装 累積付きの 1 つの 27 x 27 1 表 18. Cyclone V デバイスでの乗算器数(その 1) バリアント 各コー ド 可変精度 DSP ブ ロック 独立した入力および出力乗算演 算子 18 x 18 乗算器・ 加算器 モード 36 ビッ ト入力に 加算する 18 x 18 乗算器・ 加算器 9 x 9 乗 算器 18 x 18 乗算器 27 x 27 乗算器 Cyclone V E A2 25 75 50 25 25 25 A4 66 198 132 66 66 66 A5 150 450 300 150 150 150 A7 156 468 312 156 156 156 A9 342 1,026 684 342 342 342 Cyclone V GX C3 51 153 102 51 51 51 C4 70 210 140 70 70 70 C5 150 450 300 150 150 150 C7 156 468 312 156 156 156 C9 342 1,026 684 342 342 342 Cyclone V GT D5 150 450 300 150 150 150 D7 156 468 312 156 156 156 D9 342 1,026 684 342 342 342

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

エンベデッド・メモリ・ブロック

Cyclone V エンベデッド・メモリ・ブロックは、柔軟性が高く、小規模および大規模 メモリ・アレイの最適な量を提供するようにデザインされています。エンベデッド・メモリ・ブロックのタイプ

Cyclone V デバイスには、2 つのタイプのエンベデッド・メモリ・ブロックが含まれ ています。 ■ 10 Kb の M10K ブロック — 専用メモリ・リソースのブロックです。M10K ブロック は、多数の独立したポートを提供している間では、より大規模なメモリ・アレイ にとって理想的です。 ■ 640 ビットの MLAB— 兼用ロジック・アレイ・ブロック(LAB)からコンフィギュ レーションされる拡張されたメモリ・ブロックです。MLAB は、幅広く深度の浅 いメモリ・アレイにとって理想的です。 Cyclone V SE A2 36 108 72 36 36 36 A4 58 174 116 58 58 58 A5 87 261 174 87 87 87 A6 112 336 224 112 112 112 Cyclone V SX C2 36 108 72 36 36 36 C4 58 174 116 58 58 58 C5 87 261 174 87 87 87 C6 112 336 224 112 112 112 Cyclone V ST D5 87 261 174 87 87 87 D6 112 336 224 112 112 112 表 18. Cyclone V デバイスでの乗算器数(その 2) バリアント 各コ ード 可変精度 DSP ブ ロック 独立した入力および出力乗算演 算子 18 x 18 乗算器・ 加算器 モード 36 ビッ ト入力に 加算する 18 x 18 乗算器・ 加算器 9 x 9 乗 算器 18 x 18 乗算器 27 x 27 乗算器エンベデッド・メモリの容量

表 19に、各 Cyclone V デバイスのメモリ・ブロックの容量と分配を示します。 表 19. Cyclone V デバイスでのメモリの容量および分配 バリアント 各コード M10K MLAB トータル RAM ビッ ト数 (ビット) ブロック RAM ビット 数(Kb) ブロック RAM ビット 数(Kb) Cyclone V E A2 176 1,760 314 196 1,956 A4 308 3,080 485 303 3,383 A5 446 4,460 679 424 4,884 A7 686 6,860 1338 836 7,696 A9 1,220 12,200 2748 1,717 13,917 Cyclone V GX C3 119 1,190 255 159 1,349 C4 250 2,500 472 295 2,795 C5 446 4,460 679 424 4,884 C7 686 6,860 1338 836 7,696 C9 1,220 12,200 2748 1,717 13,917 Cyclone V GT D5 446 4,460 679 424 4,884 D7 686 6,860 1338 836 7,696 D9 1,220 12,200 2748 1,717 13,917 Cyclone V SE A2 140 1,400 221 138 1,538 A4 224 2,240 352 220 2,460 A5 397 3,970 768 480 4,450 A6 514 5,140 994 621 5,761 Cyclone V SX C2 140 1,400 221 138 1,538 C4 224 2,240 352 220 2,460 C5 397 3,970 768 480 4,450 C6 514 5,140 994 621 5,761 Cyclone V ST D5 397 3,970 768 480 4,450 D6 514 5,140 994 621 5,761Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

エンベデッド・メモリのコンフィギュレーション

表 20に、Cyclone V デバイス用にサポートされているメモリのコンフィギュレーショ ンを示します。クロック・ネットワークおよび PLL クロック・ソース

Cyclone V デバイスは、最大 550 MHz での動作が可能な 16 個のグローバル・クロッ ク・ネットワークを持っています。クロック・ネットワークのアーキテクチャは、 アルテラのグローバル、エリア、およびペリフェラル・クロック・ネットワークに 基づいています。このクロックの構造は、専用クロック入力ピンおよび小数 PLL に よってサポートされています。 1 消費電力を低減させるために、Quartus II ソフトウェアは、クロック・ネットワーク のすべての未使用セクションを識別して、それらをパワー・ダウンします。PLL の機能

Cyclone V デバイスの PLL は、以下の機能をサポートします。 ■ 周波数合成 ■ オンチップ・クロック・デスキュー ■ ジッタ減衰 ■ カウンタ・リコンフィギュレーション ■ プログラマブル出力クロック・デューティ・サイクル ■ PLL カスケード接続 ■ 基準クロック・スイッチオーバー ■ プログラマブル帯域幅 ■ PLL のユーザー・モード・リコンフィギュレーション ■ 各小数 PLL 用の低消費電力モード ■ ダイナミック・フェーズ・シフト ■ ダイレクト・モード、ソース・シンクロナス・モード、ゼロ遅延バッファ・モー ド、外部フィードバック・モード、および LVDS 補償モード 表 20. Cyclone V デバイス用のエンベデッド・メモリ・ブロックのコンフィギュレー ション メモリ・ブロック 容量(ビット) プログラマブルな幅 MLAB 32 x1, x2, x4, x8, x9, x10, x16, x18, or x20 M10K 256 x40 または x32 512 x20 または x16 1K x10 または x8 2K x5 または x4 4K x2 8K x1小数 PLL

整数 PLL だけでなく、Cyclone V デバイスは、小数 PLL アーキテクチャを使用します。 デバイスには、それぞれ 9 個の出力カウンタを持っている PLL が最大 8 個あります。 PLL の使用を低減させるために、2 つの方法によって出力カウンタを使用することが できます。 ■ 小数 PLL を使用することによって、ボード上で必要とされるオシレータの数を低 減させます。 ■ シングルの基準クロック・ソースからの複数のクロック周波数を合成することに よって、デバイス内で使用されるクロック・ピンの数を低減させます。 小数 PLL モードを使用する場合、精度小数 N 周波数合成用の PLL を使用することが できます(デザイン内のオフチップ基準クロック・ソースの必要性を削除します)。. トランシーバの I/O に使用されないトランシーバ小数 PLL は、FPGA ファブリックに よって汎用小数 PLL として使用することができます。FPGA の汎用 I/O

Cyclone V デバイスは、高度にコンフィギュレーション可能な GPIO を提供します。以 下のリストは、GPIO の機能を示しています。 ■ プログラマブル・バス・ホールドおよびウィーク・プルアップ ■ プログラマブル差動出力電圧(VOD)およびプログラマブル・プリエンファシス を持っている LVDS 出力バッファ ■ 終端でのインピーダンス変化を制限するための OCT キャリブレーションを持って いるすべての I/O バンク用のオンチップ並列終端(RT OCT) ■ シグナル・インテグリティ用の共通バス上にリードまたはライトのどちらがある かということに応じて、シリアルおよび並列終端の間をスワップできるオンチッ プ・ダイナミック終端 ■ ユーザーのI/Oとしてコンフィギュレーションすることができる未使用電圧リファ レンス(VREF)ピン ■ 細かいアーキテクチャおよび荒いアーキテクチャを持っている遅延ロック・ルー プ(DLL)遅延チェイン、および入力レジスタ・パス内のハード・リード FIFO を 使用して、タイミング・クロージャを容易に実現するためのサポートPCIe Gen1 および Gen2 のハード IP

Cyclone V GX、GT、SX、および ST デバイスには、パフォーマンス、使いやすさ、お よび機能向上のためにデザインされている PCIe ハード IP が含まれています。PCIe ハード IP は、MAC、データ・リンク、およびトランザクション・レイヤから構成さ れています。

PCIe ハード IP は、 最大のレーン・コンフィギュレーション用の PCIe Gen2 および

Gen1 のエンド・ポイントをサポートします。PCIe Gen2 x4 のサポートには、PCIe と の互換性があります。

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation 図 8に示すように、PCIe のエンドポイント・サポートには、最大 8 つのファンク ションのためのマルチファンクション・サポートが含まれています。統合マルチ ファンクション・サポートは、複数のペリフェラルが必要な PCIe デザインの最大 20,000 の LE による FPGA ロジック要件を低減させます。 Cyclone V の PCIe ハード IP は、コア・ロジックから独立して動作します。この独立 した動作によって、Cyclone V デバイスが他の FPGA の部分でプログラミング・ファ イルをロードしている間に、PCIe リンクは、100 ms 以内にウェイクアップおよびリ ンク・トレーニングを完成することができます。 更に、Cyclone V デバイス内の PCIe ハード IP は、改善されたエンド・ツー・エンド のデータパス保護を ECC を使用して提供します。

外部メモリ・インタフェース

このセクションでは、Cyclone V デバイス内の外部メモリ・インタフェースの概要を 説明します。ハードおよびソフト・メモリ・コントローラ

Cyclone V デバイスは、DDR3、DDR2、および LPDDR2 SDRAM デバイス用の最大 2 個 のハード・メモリ・コントローラをサポートします。 各コントローラは、2 つのチッ プ選択およびオプションの ECC を持っている最大集積度 4 Gb の 8 ビット~ 32 ビッ トのコンポーネントをサポートします。Cyclone V SoC FPGA では、HPS 内のハード・ メモリ・コントローラは、DDR3、DDR2、および LPDDR2 SDRAM デバイスをサポー トします。 また、Cyclone V デバイスは、最大の柔軟性を確保するための DDR3、DDR2、および LPDDR2 SDRAM デバイス用のソフト・メモリ・コントローラもサポートします。 図 8. Cyclone V デバイスの PCIe マルチファンクション PCIe LinkExternal System Cyclone V Device Host CPU Memor y Controller Root Complex Local Peripheral 1 Local Peripheral 2 PCIe RP PCIe EP

CAN GbE ATA

Br

idge

to PCIe

SPI GPIO 2IC

外部メモリのパフォーマンス

表 21に、Cyclone V デバイスの外部メモリ・インタフェースのパフォーマンスを示し ます。 表 21. Cyclone V デバイスの外部メモリ・インタフェースのパフォーマンス インタフェース 電圧(V) ハード・コントローラ(MHz) ソフト・コントローラ(MHz) DDR3 SDRAM 1.5 400 300 DDR3L SDRAM 1.35 400 300 DDR3U SDRAM 1.25 333 300 DDR2 SDRAM 1.8 400 300 1.5 400 300 LPDDR2 SDRAM 1.2 333 300Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

低消費電力のシリアル・トランシーバ

Cyclone V デバイスは、各チャネルで最大 88 mW の消費電力と見積もられる、業界で 最も低い消費電力の 5 Gbps のトランシーバを提供します。Cyclone V トランシーバ は、幅広いプロトコルおよびデータ・レートに対応するようにデザインされていま す。トランシーバ・チャネル

図 9に示すように、トランシーバは、デバイスの左の外側端に配置されています。 トランシーバ・チャネルは、フィジカル・メディア・アタッチメント(PMA)、フィ ジカル・コーディング・サブレイヤ(PCS)、およびクロック・ネットワークで構成 されています。 図 9. Cyclone V GX および GT デバイスでのデバイス・チップの概要(1) 図 9の注:(1) この図は、トランシーバを持っている Cyclone V FPGA を表しています。他の Cyclone V デバイスは、こ こで示すものとは異なるフロア・プランを持っている可能性があります。

I/O, LVDS, and Memory Interface I/O, LVDS, and Memory Interface

I/O , L VDS , and Memor y Interf ace Tr ansceiv er PMA Bloc ks Fr actional PLLs Hard PCS Bloc ks Fractional PLL Fr actional PLLs

PCIe Hard IP Bloc

ks

Hard Memory Controller Hard Memory Controller

Core Logic Fabric and MLABs

Variable-Precision DSP Blocks M10K Internal Memory Blocks Distributed Memory Transceiver PMA Transceiver PMA Transceiver PMA Hard PCS Hard PCS Hard PCS Clock Networks Transceiver Individual Channels

PMA の機能

トランシーバへのカップリングからコアおよび I/O ノイズを防止するために、PMA ブロックは、チップの残りの部分から分離されています(最適なシグナル・インテ グリティを確保するためです)。トランシーバでは、未使用レシーバ PMA のチャネ ル PLL を追加の送信 PLL として使用することができます。 表 22に、トランシーバの PMA 機能を示します。PCS の機能

Cyclone V のコア・ロジックは、トランシーバのデータ・レートおよびプロトコルに 応じて、8 ビット、10 ビット、16 ビット、20 ビット、32 ビット、または 40 ビット のインタフェースを経由して PCS に接続します。Cyclone V デバイスには、PCIe Genおよび Gen2、XAUI、ギガビット・イーサネット(GbE)、Serial RapidIO®(SRIO)、お

よび CPRI(Common Public Radio Interface)をサポートする PCS ハード IP が含まれて います。614 Mbps ~ 5.0 Gbps のほとんどの標準および独自のプロトコルは、サポー トされます。 表 22. Cyclone V デバイスのトランシーバの PMA 機能 機能 機能の説明 バックプレーン・サポート 最大 5 Gbps の機能の駆動 PLL ベースのクロック・リカバ リ 優れたジッタ許容値 プログラマブル・デシリアライ ゼーションおよびワード・アラ インメント 高い柔軟性のデシリアライゼーション幅およびコン フィギュレーション可能なワード・アラインメント・ パターン イコライゼーションおよびプリ エンファシス 最大 6 dB のプリエンファシス、最大 4 dB のイコライ ゼーション、およびデシジョン・フィードバック・ イコライザ(DFE)なし リング・オシレータの送信 PLL 614 Mbps ~ 5 Gbps 入力基準クロックの範囲 20 MHz ~ 400 MHz トランシーバ・ダイナミック・ リコンフィギュレーション 他のチャネルの動作に影響されずにシングル・チャ ネルのリコンフィギュレーションを可能にします。

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation 表 23に、トランシーバの PCS 機能を示します。 表 23. Cyclone V デバイスのトランシーバの PCS 機能(その 1) PCS サポート データ・ レート (Gbps) トランスミッタ・データパス レシーバ・データパス 3 Gbps および 5 Gbps 基本 0.614 ~ 5.0 ■ フェーズ補償 FIFO ■ バイト・シリアライザ ■ 8B/10B エンコーダ ■ トランスミッタ・ビットス リップ ■ ワード・アライナ ■ デスキュー FIFO ■ レート・マッチ FIFO ■ 8B/10B デコーダ ■ バイト・デシリアライザ ■ バイト・オーダリング ■ レシーバ位相補償 FIFO PCIe Gen1:x1、x2、 x4 PCIe Gen2:x1、x2、 x4(1) 2.5 および 5.0 ■ 専用 PCIe PHY IP コア ■ PIPE 2.0 インタフェースから コア・ロジックへ ■ 専用 PCIe PHY IP コア ■ PIPE 2.0 インタフェースからコア・ロ ジックへ GbE 1.25 ■ プリセット機能を持っている カスタム PHY IP コア ■ GbE トランスミッタ同期ス テート・マシーン ■ プリセット機能を持っているカスタ ム PHY IP コア ■ GbE レシーバ同期ステート・マシー ン

XAUI 3.125 ■ 専用 XAUI PHY IP コア

■ 4 つのチャネルを結合するた めの XAUI 同期ステート・マ シーン ■ 専用 XAUI PHY IP コア ■ 4つのチャネルをリアライメントする ための XAUI 同期ステート・マシーン HiGig 3.75 SRIO 1.3 および 2.1 1.25 ~3.125 ■ プリセット機能を持っている カスタム PHY IP コア ■ SRIO バージョン 2.1 対応の x2 および x4 のチャネル結合 ■ プリセット機能を持っているカスタ ム PHY IP コア ■ SRIOバージョン 2.1対応の x2および x4 のデスキュー・ステート・マシーン SDI、SD/HD、およ び 3G-SDI 0.27(2)、 1.485、およ び 2.97 プリセット機能を持っているカ スタム PHY IP コア プリセット機能を持っているカスタム PHY IP コア JESD204A 0.3125(2)~ 3.125 シリアル ATA Gen1 および Gen2 1.5 および 3.0 ■ プリセット機能を持っている カスタム PHY IP コア ■ 電気的アイドル ■ プリセット機能を持っているカスタ ム PHY IP コア ■ 信号検出 ■ 非同期 SSC の広範囲拡散 CPRI 4.1(3) 0.6144 ~ 4.9152 ■ 専用確定的レイテンシ PHY IP コア ■ トランスミッタ(TX)マニュ アル・ビット・スリップ・ モード ■ 専用確定的レイテンシ PHY IP コア ■ レシーバ(RX)確定的レイテンシ・ ステート・マシーン OBSAI RP3 0.768 ~ 3.072

V-by-One HS 3.75(最大) カスタム PHY IP コア ■ カスタム PHY IP コア ■ 非同期 SSC の広範囲拡散 DisplayPort 1.2(4) 1.62 および 2.7 表 23の注:

(1) PCIe Gen2 は、Cyclone V GT デバイス用のみにサポートされています。PCIe Gen2 x4 サポートは、PCIe と互換性があります。 (2) 0.27 Gbps および 0.3125 Gbps のデータ・レートは、FPGA ファブリック内に実装する必要があるオーバサンプリングのユー ザー・ロジックを使用してサポートされます。 (3) 高電圧の出力モード(1000-BASE-CX)は、サポートされません。 (4) 特性評価待ちです。 表 23. Cyclone V デバイスのトランシーバの PCS 機能(その 2) PCS サポート データ・ レート (Gbps) トランスミッタ・データパス レシーバ・データパス

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

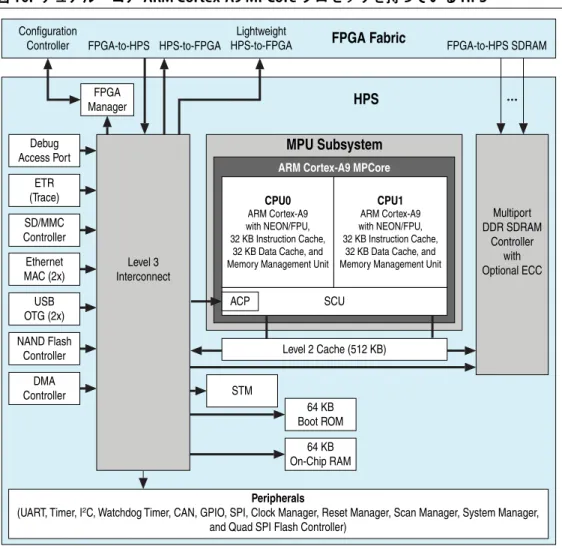

HPS を持っている SoC FPGA

各 SoC FPGA は、シングル・デバイス内で FPGA ファブリックおよびの HPS を組み合 わせます。この組み合わせは、3 つの方法によって、ハード IP の消費電力およびコ ストの節約と共にプログラマブル・ロジックの高い柔軟性を提供します。 ■ ディスクリート・エンベデッド・プロセッサを解消することによって、ボード・ スペース、システムの消費電力、および部品コストを削減します。 ■ ハードウェアおよびソフトウェアの両方の最終製品の差別化を可能にして、実質 的にどのインタフェース規格もサポートできるようにします。 ■ 製品寿命を長くして、ハードウェアおよびソフトウェアのインフィールド・アッ プデートを通して収益を拡張します。

HPS の機能

図 10に示すように、HPS は、デュアル・コア ARM Cortex-A9 MPCore プロセッサ、ペ

リフェラルの豊富なセット、および共有マルチポート SDRAM メモリ・コントローラ から構成されています。

図 10. デュアル・コア ARM Cortex-A9 MPCore プロセッサを持っている HPS

FPGA Fabric

HPS

HPS-to-FPGA

Lightweight HPS-to-FPGA

FPGA-to-HPS FPGA-to-HPS SDRAM

Configuration Controller FPGA Manager 64 KB On-Chip RAM 64 KB Boot ROM Level 3 Interconnect Ethernet MAC (2x) USB OTG (2x) NAND Flash Controller SD/MMC Controller DMA Controller STM ETR (Trace) Debug Access Port

ARM Cortex-A9 MPCore

MPU Subsystem

CPU0 ARM Cortex-A9 with NEON/FPU, 32 KB Instruction Cache,

32 KB Data Cache, and Memory Management Unit

CPU1 ARM Cortex-A9 with NEON/FPU, 32 KB Instruction Cache,

32 KB Data Cache, and Memory Management Unit

SCU ACP Level 2 Cache (512 KB) Multiport DDR SDRAM Controller with Optional ECC Peripherals

(UART, Timer, I2C, Watchdog Timer, CAN, GPIO, SPI, Clock Manager, Reset Manager, Scan Manager, System Manager,

システム・ペリフェラル

各イーサネット MAC、USB OTG、NAND フラッシュ・コントローラ、および SD/MMC コントローラ・モジュールは、それぞれ統合 DMA コントローラを持っています。オ フチップと通信するペリフェラルは、他のペリフェラルと共に HPS ピン・レベルで マルチプレクサ化されます。これによって、PCB 上の他のデバイスにインタフェー スするペリフェラルを選択できるようになります。 統合 DMA コントローラを持っていないモジュールでは、追加の DMA コントローラ・ モジュールが、広帯域幅データ転送の最大 8 個のチャネルを提供します。デバッグ・ アクセス・ポートは、インタフェースから業界標準 JTAG デバッグ・プローブに至る まで提供し、ソフトウェア開発を容易に行うために ARM CoreSight デバッグおよびコ ア・トレースをサポートします。HPS‒FPGA AXI ブリッジ

AMBA®(Advanced Microcontroller Bus Architecture)の AXI™(Advanced eXtensible Interface)仕様をサポートする HPS–FPGA ブリッジは、以下のブリッジから構成され ています。

■ FPGA-to-HPS AXI ブリッジ —FPGA ファブリックが HPS内のスレーブに対してトラン

ザクションを発行できるようにする 32 ビット、64 ビット、および 128 ビットの データ幅をサポートする高いパフォーマンスのバスです。

■ HPS-to-FPGA AXI ブリッジ —HPS が FPGA ファブリック内のスレーブに対してトラン

ザクションを発行できるようにする 32 ビット、64 ビット、および 128 ビットの データ幅をサポートする高いパフォーマンスのバスです。 ■ 軽量HPS-to-FPGA AXIブリッジ—HPSがFPGAファブリック内のスレーブに対してト ランザクションを発行できるようにする低いパフォーマンスの 32 ビット幅バス です。このブリッジは、基本的に、FPGA ファブリック内のペリフェラルへのコ ントロールおよびステータス・レジスタ(CSR)アクセス用に使用されます。 また、HPS–FPGA AXI ブリッジは、FPGA ファブリック内に実装されたマスタが HPS 内の 1 つまたは両方のマイクロプロセッサと共にメモリを共有できるようにします。 また、各ブリッジは、FPGA ファブリックおよび HPS の間で転送されるデータ用に非 同期クロック・クロッシングを提供します。

HPS SDRAM コントローラ・サブシステム

HPS SDRAM コントローラ・サブシステムには、FPGA ファブリック(FPGA-to-HPS

SDRAM インタフェースを経由して)、レベル 2(L2)キャッシュ、およびレベル 3

(L3)システム・インタコネクトの間で共有されるマルチポート SDRAM コントロー ラおよび DDR PHY が含まれています。FPGA-to-HPS SDRAM インタフェースは、

AMBA AXI および Avalon® Memory-Mapped(Avalon-MM)インタフェース規格をサポー

トして、FPGA ファブリック内に実装されたマスタによるアクセス用として最大 6 個 の個別のポートを提供します。 メモリのパフォーマンスを最大にするために、SDRAM コントローラ・サブシステム は、コマンドおよびデータ・リオーダリングの機能、エージング付きのラウンド・ ロビン・アービトレーション機能、および高優先度のバイパス機能をサポートしま す。SDRAM コントローラ・サブシステムは、最大 400 MHz(800 Mbps のデータ・ レート)での動作で最大 4 Gb の DDR2、DDR3、または LPDDR2 をサポートします。

Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

FPGA コンフィギュレーションおよびプロセッサのブート

FPGA ファブリックおよび SoC FPGA 内の HPS は、個別に電源が供給されます。ダイ ナミック消費電力を低減させるために、クロック周波数を低減させるまたはクロッ クをゲートすることができます。または、トータル・システム消費電力を削減する ために FPGA ファブリック全体をシャット・ダウンすることができます。 ユーザーは、デザインの高い柔軟性によって、任意の順序で別々に、FPGA ファブ リックのコンフィギュレーションおよび HPS のブートをすることができます。 ■ ユーザーは、別々に HPS をブートすることができます。HPS の実行後、HPS は、ソ フトウェアの制御下でいつでも完全にまたは部分的に FPGA ファブリックをリコ ンフィギュレーションすることができます。また、HPS は、FPGA コンフィギュ レーション・コントローラを経由して、ボード上の他の FPGA をコンフィギュ レーションすることもできます。 ■ HPS および FPGA ファブリックを一緒にパワー・アップして、まず FPGA ファブリッ クをコンフィギュレーションし、その後、FPGA ファブリックにアクセス可能な メモリから HPS をブートすることができます。 1 FPGA ファブリックおよび HPS が個別のパワー・ドメイン上であるにもかかわらず、 FPGA ファブリックが必要に応じたパワー・アップまたはパワー・ダウンの動作中 に、HPS はパワー・アップの状態である必要があります。

ハードウェアおよびソフトウェアの開発

ハードウェア開発では、Quartus II ソフトウェア内の Qsys システム統合ツールを使用 して、HPS をコンフィギュレーションして FPGA ファブリック内のソフト・ロジック を HPS インタフェースに接続することができます。ソフトウェア開発では、ARM ベースの SoC FPGA デバイスは、ARM Cortex-A9 MPCore プロセッサに使用可能な豊富なソフトウェア開発エコシステムを継承しています。 アルテラの SoC FPGA 用のソフトウェア開発プロセスは、他のメーカによる他の SoC

デバイスのプロセスと同じステップに従います。Linux、VxWorks®、および他のオペ

レーティング・システムのサポートは、SoC FPGA に使用可能です。オペレーティン

グ・システム・サポートの可用性について詳しくは、 Altera sales teamにお問い合わせ

ください。

ユーザーは、アルテラの SoC FPGA Virtual Target 上でデバイス固有ファームウェアお よびソフトウェア開発を開始することができます。Virtual Target は、ターゲット開発 システムの高速 PC ベースの機能シミュレーションです(PC 上で実行する完全な開 発ボードのモデルです)。Virtual Target は、未変更の実際のハードウェア上で実行で きるデバイス固有製品のソフトウェアの開発を可能にします。

ダイナミックおよびパーシャル・リコンフィギュレーション

Cyclone V デバイスは、ダイナミック・リコンフィギュレーションおよびパーシャ ル・リコンフィギュレーションをサポートします。ダイナミック・リコンフィギュレーション

ダイナミック・リコンフィギュレーション機能によって、隣接するチャネル上の データ転送に影響を与えることなく、トランシーバのデータ・レート、PMA 設定、 またはチャネルのプロトコルをダイナミックに変更することができるようになりま す。この機能は、実行時のマルチプロトコルまたはマルチレートのサポートを必要 とするアプリケーションにとって理想的です。ダイナミック・リコンフィギュレー ションを使用して、PMA および PCS のブロックをリコンフィギュレーションするこ とができます。パーシャル・リコンフィギュレーション

パーシャル・リコンフィギュレーションによって、デバイスのほかのセクションの 動作中にデバイスの一部をコンフィギュレーションできるようになります。この機 能は、サービスを停止することなく機能を更新または調整できるようにするため、 クリティカルなアップタイム要件を持っているシステムにとって重要です。 コストおよび消費電力の低減とは別に、パーシャル・リコンフィギュレーションは、 同時に動作しないデバイス・ファンクションを配置する必要がないため、デバイス の効率的なロジック集積度を向上させます。そのかわり、これらのファンクション を外部メモリに格納し、ファンクションが必要な時にいつでもそれらをロードする ことができます。この機能は、シングル・デバイス上の複数のアプリケーションの ボード・スペースの節約および消費電力の節約を可能にするため、デバイスのサイ ズを低減させます。 アルテラは、Quartus II デザイン・ソフトウェアで提供されるインクリメンタル・コ ンパイルおよびデザイン・フローの上にこの機能を構築することによって、パー シャル・コンフィギュレーションの時間のかかるタスクを容易にします。Altera®ソ リューションを使用すれば、パーシャル・リコンフィギュレーションを実行するた めに、すべての複雑なデバイス・アーキテクチャの詳細を理解する必要はありませ ん。 パーシャル・リコンフィギュレーションは、FPP x16 のコンフィギュレーション・イ ンタフェースを経由してサポートされます。デバイス・コアおよびトランシーバの 両方で同時にパーシャル・リコンフィギュレーションを可能にするために、ダイナ ミック・リコンフィギュレーションを持っているタンデムでパーシャル・リコン フィギュレーションをシームレスに使用することができます。Cyclone V デバイスの概要 2012 年 6 月 Altera Corporation

エンハンスト・コンフィギュレーションおよびプロトコルを介する

コンフィギュレーション

Cyclone V デバイスは、1.8 V、2.5 V、3.0 V、および 3.3 V のプログラミング電圧および いくつかのコンフィギュレーション・モードをサポートします。表 24に、Cyclone V デバイスにサポートされるコンフィギュレーション・モードおよび機能を示します。 外部フラッシュまたは ROM を使用するかわりに、CvP を使用して PCIe を経由して Cyclone V デバイスをコンフィギュレーションすることができます。CvP モードは、 使いやすい PCIe ハード IP ブロック・インタフェースを使用して、最速のコンフィ ギュレーション・レートおよび柔軟性を提供します。Cyclone V CvP 実装は、PCIe 100 ms のパワー・アップ・ツー・アクティブ時間要件に準拠します。f CvPについて詳しくは、 Configuration via Protocol (CvP) Implementation in Altera FPGAs User

Guideを参照してください。

消費電力管理

FPGA アーキテクチャ機能、プロセス技術、および電力効率用にデザインされたトラ ンシーバを活用することにより、Cyclone V デバイスは、前世代の Cyclone FPGA より も少ない消費電力で済みます。 ■ 全デバイス・コア消費電力 — 最大 40% 未満です。 ■ トランシーバ・チャネル消費電力 — 最大 50% 未満です。 更に、Cyclone V には、ロジック・リソースを低減して同等のソフト実装よりも最大 25% の大幅な電力節約を実現するいくつかのハード IP ブロックが含まれています。 表 24. Cyclone V デバイスのコンフィギュレーション・モードおよび機能 モード データ幅 最大ク ロック・ レート (MHz) 最大デー タ・レート (Mbps) 圧縮復元 デザイン・ セキュリ ティ パーシャル・リ コンフィギュ レーション リモート・シ ステム・アッ プデート EPCS および EPCQ シリアル・コン フィギュレーショ ン・デバイスを経 由する AS 1 ビット、 4 ビット 80 — 使用可 使用可 — 使用可 CPLD または外部 マイクロコント ローラを経由する PS 1 ビット 125 125 使用可 使用可 — — FPP 8 ビット 125 — 使用可 使用可 — パラレル・ フラッシュ・ ローダ 16 ビット 125 — 使用可 使用可 使用可 CvP(PCIe) x1、x2、 および x4 レーン — — — 使用可 使用可 使用可 JTAG 1 ビット 33 33 — — — —

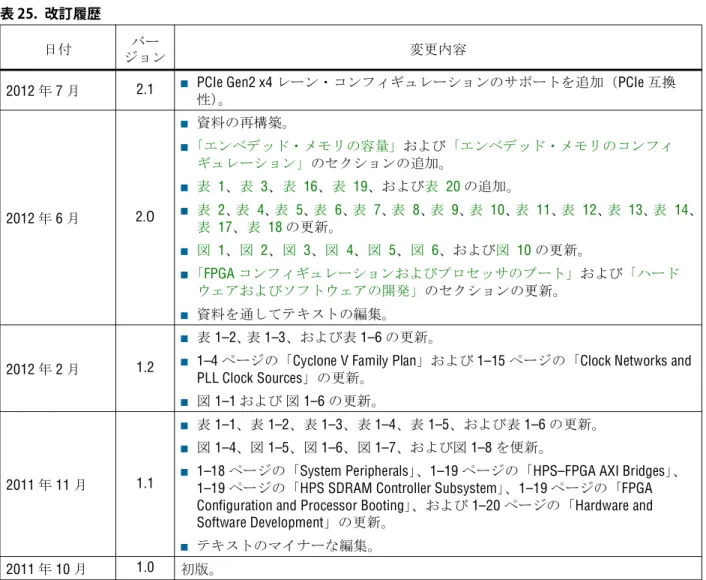

改訂履歴

表 25に、本資料の改訂履歴を示します。

表 25. 改訂履歴

日付 バー

ジョン 変更内容

2012 年 7 月 2.1 ■ PCIe Gen2 x4 レーン・コンフィギュレーションのサポートを追加(PCIe 互換

性)。 2012 年 6 月 2.O ■ 資料の再構築。 ■「エンベデッド・メモリの容量」および「エンベデッド・メモリのコンフィ ギュレーション」のセクションの追加。 ■ 表 1、表 3、表 16、表 19、および表 20の追加。 ■ 表 2、表 4、表 5、表 6、表 7、表 8、表 9、表 10、表 11、表 12、表 13、表 14、 表 17、表 18の更新。 ■ 図 1、図 2、図 3、図 4、図 5、図 6、および図 10の更新。 ■「FPGA コンフィギュレーションおよびプロセッサのブート」および「ハード ウェアおよびソフトウェアの開発」のセクションの更新。 ■ 資料を通してテキストの編集。 2012 年 2 月 1.2 ■ 表 1–2、 表 1–3、および表 1–6 の更新。

■ 1–4 ページの「Cyclone V Family Plan」および 1–15 ページの「Clock Networks and

PLL Clock Sources」の更新。

■ 図 1–1 および 図 1–6 の更新。

2011 年 11 月 1.1

■ 表 1–1、表 1–2、表 1–3、表 1–4、表 1–5、および表 1–6 の更新。

■ 図 1–4、図 1–5、図 1–6、図 1–7、および図 1–8 を便新。

■ 1–18 ページの「System Peripherals」、1–19 ページの「HPS–FPGA AXI Bridges」、

1–19 ページの「HPS SDRAM Controller Subsystem」、1–19 ページの「FPGA

Configuration and Processor Booting」、および 1–20 ページの「Hardware and

Software Development」の更新。

■ テキストのマイナーな編集。