Agilent

E2960B シリーズ

PCI EXPRESS

®

2.0 対応

Data Sheet

最高速のテスト

優れたプロービング機能を備えた包括的な

PCI Express

®

x1 ∼ x16

テスト・ソリューション

P2L ゲートウェイ

拡張 P2L ゲートウェイに

よるフル・システム表示

x1 ∼ x16 アナライザに

よる信頼性の高い

トラフィック捕捉

柔軟な GUI による優れた

プロトコル表示

製品ニーズに

対応したさまざまな

プロービング・

ソリューション

プロトコル・

アナライザ

x1 ∼ x16

エクセサイザによる

詳細な製品テスト

テスト・サイクルを

高速化する

コンプライアンス・

テスト・パッケージ

実システムでの

エラー挿入テスト

解決法

スケーラブルなスティミュラス・

レスポンス用のモジュラ・

ツーインワン・ソリューション

スティミュラス・

ツール

単一

ソリューション

で独自のロジック

解析機能と

プロトコル

解析機能を搭載

概要 ...2

E2960B の主な特長 ...2

システム・アーキテクチャの概要 ...3

代表的な構成 ...4

PCI Express Gen 2 Ready

プログラム ...5

概要 ...6

N5306A アナライザ ...8

N5322A 拡張インタフェース・

モジュール ...10

N5309A エクセサイザ、

プロトコル・テスト・カード 2.0、

コンプライアンス・テスト ...11

N5323A ジャマー ...16

N4241A/2A/3A ミッドバス・

プローブ ...18

N4241F フライング・リード・

プローブ ...20

N5315A スロット・

インタポーザ・プローブ ...22

N5316A パッシブ・

バックプレーン...24

N5313A P2L ゲートウェイ・

ケーブル ...26

N5319A P2L ゲートウェイ・

ケーブル、フラグ・サポート付き ...27

関連製品 ...28

関連 Agilent カタログ ...29

オーダ情報 ...30

目次

E2960B シリーズは、業界で最も機能

が充実した統合テスト・システムで

す。x1 ∼ x16 プロトコル・アナライザ、

エクセサイザ、コンプライアンス・

テスト・パッケージ、さまざまなプ

ロービング・ソリューションから構

成され、テスト・ニーズに対応でき

ます。

■

アナライザは、回路に影響を与え

ることなく、正確な信号を捕捉で

き、信頼性の高いシステム表示が

得られます。

■

エクセサイザは、x1 ∼ x16 のリン

クの詳細なテストを実行します。

自動 LTSSM エクセサイザと定義

済みのコンプライアンス・テスト

により、テスト・サイクルが高速

化されます。

■

プロトコル・ロジック・ゲートウェ

イ(P2L ゲ ー ト ウ ェ イ ) に よ り、

Agilent のロジック・アナライザ

と相関測定が行え、システム全体

を解析できます。

■

スティミュラス(エクセサイザ)

/レスポンス(アナライザ)用の

統合ソリューションにより、DUT

の動作を詳細に表示して、理解で

きるようになります。

このような機能により、解析時間が

短縮され、デザインのデバッグに使

える時間が増え、商品化にかかる時

間を短縮できます。

概要

■

信頼性の高いトラフィックの捕捉

/解析

■

業 界 最 速 の ロ ッ ク 時 間(3 ∼ 5

FTS、 代 表 値 ) に よ る 効 率 的 な

ASPM(アクティブ・ステート・

パワー・マネージメント)テスト

■

イージー・フロー/コンテキスト

依存表示によるプロトコル表示

■

高度なトリガ、検索、フィルタリ

ング機能

■

レーン・ビュー、高速 ASPM 同期

時間、オーダード・セットでのト

リガなど、独自のロジック機能を

装備

■

ミッドバス 2.0 プローブ、フライ

ング・リード 2.0 プローブ、スロッ

ト・インタポーザ・プローブなど

のプロービング・ソリューション

■

定義済みテストを使用した独自の

LTSSM テスト

■

最新ジャマー・ツールによるエラー

挿入テスト

■

PTC 2.0、PCI Express Gen1 用と

Gen2 用のコンプライアンス・テス

トを同じテスト・カードで可能

■

ハードウェア・アップグレードが

可 能。PTC 2.0 用、180 種 類 の 追

加テストを搭載したコンプライア

ンス・テスト用、またはフル・エ

クセサイザ機能にアップグレード

が可能

■

ロジック・アナライザとプロトコ

ル・アナライザのクロス・トリガ

■

フラグ付きのピンポン・トリガを

サポート

■

エクセサイザとアナライザの緊密

な統合により、アナライザがデバ

イス動作の主要セグメントのみを

捕捉可能

■

プロトコル・アナライザで記録し

たトラフィックをエクセサイザで

再生可能

E2960B の主な特長

P2L

ゲートウェイ

プロトコル・

アナライザ

解決法

スティ

ミュラス・

ツール

システム・アーキテクチャの概要

システム管理用 PC コントローラ。コントロー

ラには、複数の接続オプションがあります。

− PC コントローラとシャーシを直接接続す

る 100 Mbps イーサネット LAN

− USB インタフェースに使用可能な

USB-LAN ドングル

シャーシ(2 スロットまたは 4 スロットを使

用可能)

PC コントローラから LAN または USB 2.0

で制御される N5306A プロトコル・アナライ

ザ・モジュール

N5316A テスト・バックプレーン。ベンダ・

システムなしでエンド・ポイントのテストが

可能

PC コントローラから LAN または USB 2.0

で 制 御 さ れ る N5309A エ ク セ サ イ ザ・ モ

ジュール

N5315A スロット・インタポーザ・プローブ

2 1 3 4 5 6 2 1 3 4 5 6プラットフォーム ● Agilent E2960Bシリーズは、既存のN2Xプラットフォームをベースにしているので、E2960Aシャー シとプローブをPCIeTM 2.0にも再利用できます。

● GUIを含めたソフトウェアは、両方の製品で同じなので、投資を保護でき、これまでのノウハ ウを活用してPCIe 2.0テストをすぐに開始できます。

● E2960BシリーズのAPIは、既存のE2960A(Gen 1)のAPIと互換性があり、Gen 1用に開発され たスクリプトをGen2テストに再利用できます。

Gen 2 Readyプログラム ● PCI Express Gen 1テスト用のE2960B機器を、将来PCI Express Gen 2テストを開始するときに、簡 単なライセンス・アップデートによりGen 2テストにも使用できます。 独自のロジック解析機能と プロトコル解析機能を搭載 ● 物理層からトランザクション層までを効率的に解析できます。また、レーン毎のLEDにより、 I/OモジュールとGUIの両方でレーンのステータス情報が瞬時にわかります。 ● チャネル・ボンディングが完了する前でも、8b、10b、K/Dシンボルなどをレーン毎に表示でき ます。 ● 選択したレーン上での2つの“Trigger-down-the-lane”パターン ● 手動および自動での速度設定 TCLまたはWindows® DCOMによるテストの カスタマイズと自動化 ● テストを自動化できます。 ● テストを反復できます。 ● 専用のテスト手順を作成し、自動化できます。 ● 連続テストができます。

軽量で持ち運び可能なシステムから大規模な検証環境まで

E2960B シリーズは、軽量で持ち運びができ、ラボでも場所をとりません。また、

多くのアナライザやエクセサイザが必要な場合でも、これに対応できるアーキ

テクチャになっています。複数のシャーシを互いに接続して、大規模な時間同

期テスト・システムを構築できます。

図 3. N5541A N2X 4 スロット・シャーシ 図 2. E2960B プロトコル・アナライザ代表的な構成

E2960B シリーズは、エクセサイザと

プロトコル・アナライザ、ジャマーの、

3 つ の 主 要 ア プ リ ケ ー シ ョ ン を サ

ポートしています。

エクセサイザの主な特長は、被試験

デバイス(DUT)へのスティミュラ

スの作成です。アドイン・カードを

テストしている場合は、ルート・コ

ンプレックスをエミュレートするよ

うにエクセサイザをプログラムでき

ます。ルート・コンプレックスのテ

ストを実行している場合は、エンド・

ポイントをエミュレートするように

エクセサイザをプログラムできます。

エクセサイザでは、物理層、データ・

リンク層、トランザクション層の動

作をプログラムし、製品をリリース

する前に DUT の動作を包括的に検

証できます。エクセサイザの動作を

自 分 で プ ロ グ ラ ム す る こ と も、

Agilent のコンプライアンス保証テス

ト・パッケージを購入してテストす

ることもできます。このパッケージ

には 180 種類を超える自動テストが

含まれていて、デバイスの適切な動

作を検証できます。

テスト中に問題が検出された場合は、

プロトコル・アナライザを使用して

目の前にある問題をさらにデバッグ

/トラブルシューティングできます。

PCI Express Gen 2 でのデバッグの

際の問題として、信号へのアクセス

があります。E2960B シリーズ・アナ

ライザはこの問題を解決するために、

さまざまなプロービング・ソリュー

ション(ミッドバス・プローブ、スロッ

ト・インタポーザ・プローブ、フラ

イング・リード・プローブ)を提供し

ています。

E2960B シリーズ・プロトコル・アナ

ライザには、ステートベース・トリガ、

イージー・フロー、コンテキストに

よるカラム解析などの、解析時間の

短縮に役立つ高度な機能も含まれて

います。

エクセサイザのサンプル構成

テスト・カード N5309A-E04 エクセサイザおよびLTSSMボードx4、PCIe 5 Gb/s用 テスト・ バックプレーン N5316A テスト・バックプレーン ソフトウェア N5309A-EX2 N5309A-COM N5309A-PTC エクセサイザSWライセンス、エクセサイザおよびLTSSM、5 Gb/s エクセサイザSWライセンス、コンプライアンス保証テスト・パッ ケージ:180種類を超える追加PCI-SIG推奨コンプライアンス・テ ストが付属 PTC用エクセサイザSWライセンス(エクセサイザの購入時に無料 で付属):13種類のPCI-SIG必須コンプライアンス・テストが付属 図 4. アナライザとエクセサイザのサンプル構成アナライザのサンプル構成

シャーシ N5540A 2スロット・シャーシ テスト・カード N5306A アナライザ・モジュール、PCIe 5 Gb/s用 ソフトウェア N5306A-A04 アナライザSWライセンスx4、PCIe 5 Gb/s用 プローブ N5315A-A04 スロット・インタポーザx4、PCIe 5 Gb/s用PCI Express Gen 2 Ready プログラム

業界では PCI Express Gen 2 デザイ

ン の 検 証 を 開 始 し た た め、PCI

Express Gen 1 用のテスト機器への

投資を続けるか、Gen 2 への投資に

切り替えるかを決断するための議論

がさかんに行われています。Gen 2

Ready プログラムは、この決断を容

アナ

ライザ・

リンク

Gen2 Ready

構成

概要

Gen2

へのアップグレード

x1 N5306A アナライザ・モジュール、PCIe 5 Gb/s用(x16用には2個必要) N5310U-U21

N5306A-G01 アナライザSWライセンスx4、PCIe 2.5 Gb/s用 アップグレードx1、Gen2 ReadyからGen2へ

N5315A-A01 スロット・インタポーザx1、PCIe 5 Gb/s用

N5540A N2X 2スロット・ポータブル・シャーシ

x4 N5306A アナライザ・モジュール、PCIe 5 Gb/s用(x16用には2個必要) N5310U-U24

N5306A-G04 アナライザSWライセンスx4、PCIe 2.5 Gb/s用 アップグレードx4、Gen2 ReadyからGen2へ

N5315A-A04 スロット・インタポーザx4、PCIe 5 Gb/s用

N5540A N2X 2スロット・ポータブル・シャーシ

x8 N5306A アナライザ・モジュール、PCIe 5 Gb/s用(x16用には2個必要) N5310U-U28

N5306A-G08 アナライザSWライセンスx8、PCIe 2.5 Gb/s用 アップグレードx8、Gen2 ReadyからGen2へ

N5315A-A08 スロット・インタポーザx8、PCIe 5 Gb/s用

N5540A N2X 2スロット・ポータブル・シャーシ

x16 N5306A アナライザ・モジュール、PCIe 5 Gb/s用(x16用には2個必要) N5310U-U26

N5306A アナライザ・モジュール、PCIe 5 Gb/s用(x16用には2個必要) アップグレードx16、Gen2 ReadyからGen2へ

N5306A-G16 アナライザSWライセンスx16、PCIe 2.5 Gb/s用 N5306A-G16 アナライザSWライセンスx16、PCIe 2.5 Gb/s用 N5315A-A16 スロット・インタポーザx16、PCIe 5 Gb/s用 N5540A N2X 2スロット・ポータブル・シャーシ

エクセ

サイザ・

リンク

Gen2 Ready

構成

概要

Gen2

へのアップグレード

x1 N5309A-E01 ハーフ・サイズ・エクセサイザおよびLTSSMボードx1、PCIe 5 Gb/s用 N5310U-E12

N5309A-EX1 エクセサイザSWライセンスおよびLTSSM、PCIe 2.5 Gb/s用 Gen2 ReadyからGen2へのアップグレード

x4 N5309A-E04 ハーフ・サイズ・エクセサイザおよびLTSSMボードx4、PCIe 5 Gb/s用 N5310U-E12

N5309A-EX1 エクセサイザSWライセンスおよびLTSSM、PCIe 2.5 Gb/s用 Gen2 ReadyからGen2へのアップグレード

x8 N5309A-E08 ハーフ・サイズ・エクセサイザおよびLTSSMボードx8、PCIe 5 Gb/s用 N5310U-E12

N5309A-EX1 エクセサイザSWライセンスおよびLTSSM、PCIe 2.5 Gb/s用 Gen2 ReadyからGen2へのアップグレード

x16 N5309A-E16 ハーフ・サイズ・エクセサイザおよびLTSSMボードx16、PCIe 5 Gb/s用 N5310U-E12

N5309A-EX1 エクセサイザSWライセンスおよびLTSSM、PCIe 2.5 Gb/s用 Gen2 ReadyからGen2へのアップグレード

ジャ

マー・

リンク

Gen2 Ready

構成

概要

Gen2

へのアップグレード

x1 N5323A-J01 ジャマー・モジュールx1、PCIe 5 Gb/s用 N5310U-J12

N5323A-JM1 ジャマーSWライセンス:2.5 Gb/s Gen2 ReadyからGen2へのアップグレード

x4 N5323A-J04 ジャマー・モジュールx4、PCIe 5 Gb/s用 N5310U-J12

易にするために作成され、現在のテ

スト・ツールへの投資を保護します。

E2960B シリーズは、PCI Express 2.0

アナライザ/エクセサイザで、必要

なレーン幅

(x1 ∼ x16)に関係なく、2.5

Gb/s または 5 Gb/s で使用できます。

当面は E2960B を Gen 1 アプリケー

ションのみに使用し、将来 Gen 2 テ

ストに移行できます。Gen2 へのアッ

プグレードは、簡単なソフトウェア・

アップグレードで、ハードウェアの

交換や取り外しは不要です。

概要

プ

ロ

ト

コ

ル

・

ア

ナ

ラ

イ

ザ

信頼性の高いトラフィックの 捕捉/解析 x1∼x16に対応したアナライザを使用して、システム・トラフィックを容易に理解できます。 ● 2.5 Gビット/s、5 Gビット/s PCI Expressトラフィックの捕捉 ● 見つけるのが困難なエラーでも検出できる高度なトリガ機能 ● 3∼5倍(代表値)高速なトレーニング・シーケンスの業界最速ロック時間により、L0sから抜け るときでも信頼性の高いデータ捕捉 ● コンテキストベースのカラム解析とイージー・フロー表示によるわかりやすいデータ表示 ● SR-IOVおよびMR-IOVデコードで、PCI-SIGの最新仕様に対してもデバッグと解析をサポートアプリケーション・ニーズに対応する 優れたプロービング・ソリューション プロトコル・アナライザには、x1∼x16の、ミッドバス・プローブ、スロット・インタポーザ・プロー ブ、フライング・リード・プローブなどの、さまざまなプロービング・ソリューションがあります。 ● ミッドバス・プローブとフライング・リード・プローブは、容量性負荷が小さいので、信号の歪 みが最小にできます。 ● スロット・インタポーザ・プローブは、優れたアナログ信号再現テクノロジーと機械的に頑丈な 構造を備え、シグナル・インテグリティが不十分な場所をプロービングできます。

P

2

L

ゲ

I

ト

ウ

ェ

イ

フル・システム表示 P2Lゲートウェイの採用により、クロス・バス解析が行えます。 ● 複数のプロトコル(例えば、PCI ExpressとDDR)を同時にモニタ可能。 ● ロジック・アナライザとプロトコル・アナライザの時間相関表示を提供。 ● ロジック・アナライザとプロトコル・アナライザ間でクロス・トリガが可能。 ● フラグ・サポートにより、ロジック・アナライザとプロトコル・アナライザ間でピンポン・トリ ガが可能。 P2L ゲートウェイ プロトコル・ アナライザ 解決法 スティ ミュラス・ ツール概要

P2L ゲートウェイ プロトコル・ アナライザ 解決法 スティ ミュラス・ ツールス

テ

ィ

ミ

ュ

ラ

ス

DUT(被試験デバイス)の検証 エクセサイザ: ● ルート・コンプレックスとエンド・ポイントのエミュレーションにより、あらゆるタイプのPCI Express 2.0用DUTをテストできます。 ● エクセサイザとテスト・バックプレーンを使用して、実際のシステムなしでエンド・ポイントを テストできます。 ● 内蔵APIインタフェースによりテストを自動化できます。 ジャマー: ● インライン・エラーを挿入して限界条件を作成し、DUTとソフトウェアを極端条件で検証できます。 ● さまざまなOS、ドライバ、アプリケーションを搭載した実際のシステムにエラーを挿入できます。 ● 設定が簡単なジャマーは、PCI Express階層に対してトランスペアレントです。ジャマーを作業用 システムに挿入するだけで、テストを開始できます。 詳細なリンク・テスト ● 定義済みのLTSSMテストを使って、テストが難しいDUTのLTSSMの状態遷移を簡単に検証でき ます。 ● レーン幅の動的変更、リンク・ネゴシエーションなどの、2.0仕様への新しい追加機能を簡単に検 証できます。 コンプライアンス・テスト ● 180種類を超える(PCI-SIGにより定義された)コンプライアンス・テスト・スクリプトを使って、 トランザクション層、データ・リンク層、コンフィギュレーション・スペースでPCI Express 2.0仕 様への準拠をすばやくテストできます。 ● エクセサイザは使いやすいGUIを装備しています。1回のクリックで、すべてのテスト、または テスト・ケースのサブセクションを実行できます。 ● 正確なレポートで、合格、不合格、警告結果を明確に識別できます。解

決

法

スティミュラス・レスポンス用の ツーインワン・ソリューション ● スティミュラス(アナライザ)/レスポンス(エクセサイザ)ソリューションにより、エクセサイ ザとアナライザが完全に統合され、一貫した操作でDUTの詳細な表示が可能です。 ● エクセサイザとアナライザの統合により、記録と再生が簡単に行えます。アナライザのパケット を保存し、エクセサイザで再生できます。N5306A アナライザ

特長

表示 ● 表形式ビューに基づいた、高度な設定が可能なGUI ● 色のカスタマイズ ● コンテキストベースのカラムを使用した要約データ表示 ● イージー・フローによるアップストリーム/ダウンストリーム・データの「ピンポン」表示 ● 捕捉トレースの簡単なナビゲーション ● トラフィック・オーバビュー(ポスト・キャプチャ) ● 個別レーン・データを表示可能 ● レコード・デコード・ビュー、シングル・ライン・デコード・ビュー、ペイロード・ビュー、レーン・ビューなど パケット・デコードの複数のビューによるデバッグが可能 ● エラー強調表示とパケットの表示/非表示 ● 各トラフィックを簡単に識別できる、色分けされたトランザクション・タイプ ● コメント機能を持つ複数のマーカ ● 絶対タイムスタンプ、相対タイムスタンプ、任意の位置を時間ゼロとして設定する機能を備えた表示 ● 独立したレイアウトによる複数のリスト表示 ● 関連トランザクション指標付きのトランザクション・ビュー ● リンク幅の変更を動的にトラッキングする機能 トリガ ● グラフィカル・トリガ ● マルチステート、マルチレベル・トリガ・シーケンサ: −最大8個のステート −最大2個のカウンタ/タイマ −最大4個のパターン −別のアナライザからのトリガ・シーケンサが可能なクロス・モジュール・アーム入力/出力内蔵 ● 外部トリガ入力/出力 ● プロトコル・エラー・トリガ ● マルチ分岐 ● フィルタリング(リアルタイム): −アイドル −トリガ・シーケンサによるパケット −ストア条件 ● フィルタ条件は、各トリガ・シーケンサ・ステートに対して個別に定義可能 ● ペイロードでトリガ(最大128ビット) ● 1ビット単位のユーザ指定トレーニング・シーケンス・オーダード・セットでトリガ 検索/フィルタ ● 高速なハードウェア・ベースの検索とフィルタリング ● ドラッグ・アンド・ドロップ・インタフェースによる検索/フィルタリングのグラフィカル設定 ● プロトコル・エラーでの検索/フィルタ ● 複数の並列検索/フィルタ条件 −同時に最大6パターン ● 定義済みのパターン(TLP、DLLP、オーダード・セット、トレーニング・シーケンス、プロトコル・エラー)リスト ● ユーザ定義データ・パターン トラフィック捕捉 ● x1、x2、x4、x8、x16のリンク幅、2.5 GT/sと5 GT/sでの捕捉をサポート ● 信号に影響を与えないトラフィック捕捉 ● トレーニング・シーケンス、オーダード・セット、データ・リンク層パケット、トランザクション層パケットを双 方向で同時に捕捉 ● 2.5 GT/sと5 GT/s(±300 ppm)のデータ・レートをサポート ● エラー検出 ● ハードウェア内のディスパリティ・エラーと不正な10bシンボル ● ソフトウェア内のLCRC、シンボル、ディスパリティ、EDB、フレーミング、アイドル・データ不正パケット・チェッ ク(CRCエラー、不正なフィールド・コンテンツ、長さの不整合)プログラミング言語 ● Windows DCOM API

● 完全なAPIマニュアル その他 ● アナライザとエクセサイザ間のトラフィックの記録と再生 ● 8 ns分解能のタイムスタンプ(絶対値と相対値) ● 自動レーン極性検出 ● x1∼x8アナライザには2 GBのトレース・メモリ、x16アナライザには4 GBのトレース・メモリ ● レイテンシ測定(マーカを使用)

N5306A アナライザ

仕様

システム

N5306A解析モジュールは、N2Xシャーシ(N5540AまたはN5541A)に適合するI/Oブレードです。

N5306Aモジュールを制御するソフトウェアは、PCコントローラで動作します。 N2XシャーシまたはPCコントローラの詳細については、データ・シートの関連製品セクションを参照してください。

環境

温度(AT-ETM757) 動作時:0 ℃∼+55 ℃ 保管時:−40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時:15∼95% 動作時水浸:90%(24時間)安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2 環境定格:標準

一般仕様

メモリ 2 GB ディスプレイ ステータス情報用4桁LEDディスプレイ ステータスLED 16個のレーン毎LEDによる個別レーンのステータス表示 2個のステータスLEDによるモジュールのグローバル・ステータス表示 ● グレー:システムが設定されていません ● 赤:速度が検出されないか、システムが設定されていません ● 黄:システムが2.5 Gb/sの速度に設定されています ● 緑:システムが5 Gb/sの速度に設定されています コネクタ ● アナライザ・プローブ・コネクタ ● モジュール間コネクタ(N5319Aフラグ・サポート付きP2Lゲートウェイ経由でロジック・アナライザに接 続する場合に使用します) ● セルフテスト・コネクタ ● REFクロック出力 ● 10 MHzクロック出力 ● P2L用の同期ポート 図 5. N5306A アナライザN5322A 拡張インタフェース・モジュール

特長および仕様

システム

N5322A拡張インタフェース・モジュールは、解析機能を拡張するためにN5306AアナライザI/Oモジュールと一緒に使用する必要があります。

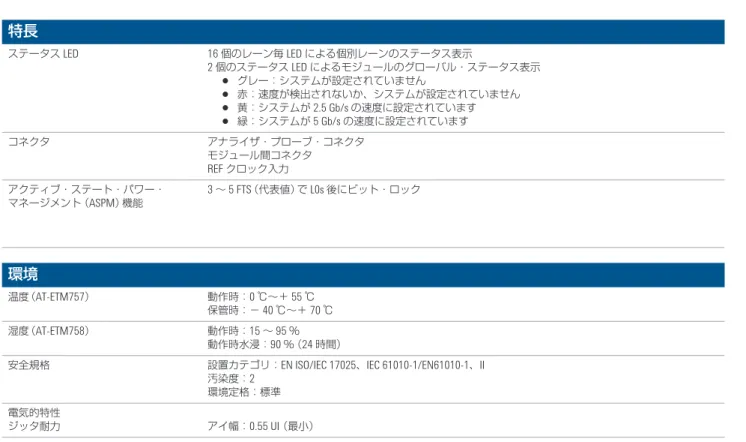

特長

ステータスLED 16個のレーン毎LEDによる個別レーンのステータス表示 2個のステータスLEDによるモジュールのグローバル・ステータス表示 ● グレー:システムが設定されていません ● 赤:速度が検出されないか、システムが設定されていません ● 黄:システムが2.5 Gb/sの速度に設定されています ● 緑:システムが5 Gb/sの速度に設定されています コネクタ アナライザ・プローブ・コネクタ モジュール間コネクタ REFクロック入力 アクティブ・ステート・パワー・ マネージメント(ASPM)機能 3∼5 FTS(代表値)でL0s後にビット・ロック環境

温度(AT-ETM757) 動作時:0 ℃∼+55 ℃ 保管時:−40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時:15∼95 % 動作時水浸:90 %(24時間)安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2

環境定格:標準 電気的特性

ジッタ耐力 アイ幅:0.55 UI(最小)

N5309A エクセサイザ

コンプライアンス・テスト

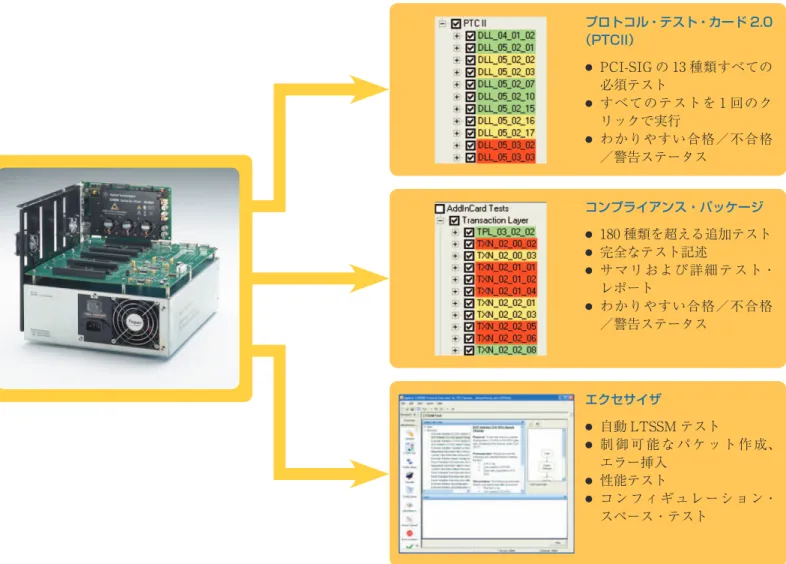

図 7. エクセサイザとコンプライアンス・テスト:1 つのハードウェアで複数のアプリケーション

一般 ● コンプライアンス・テストを既存のN5309Aエクセサイザ・ハードウェアで実行可能 ● PCI Express Gen 1とGen 2をサポート

● 使いやすいGUI − N5309AエクセサイザGUIに統合 −単一テストを実行、または複数のテストを選択してシーケンシャルに実行 −すべてのテストでテストの開始と終了をタグ付けでき、Agilentプロトコル・アナライザによる捕捉/解析が容易 テスト・サポート ● 2個のテスト・パッケージが使用可能 − E2969B PTC2 ● 13種類のPCI-SIG必須テスト・ケースをすべてサポート − 180種類の推奨テストが付属するN5309A-COMコンプライアンス保証テスト・パッケージ ● 94種類のトランザクション層テスト ● 31種類のリンク層テスト ● 57種類のコンフィギュレーション・スペース・テスト ● 1種類の電気テスト

プロトコル・テスト・カード 2.0

(PTCII)

●PCI-SIG の 13 種類すべての

必須テスト

●すべてのテストを 1 回のク

リックで実行

●わかりやすい合格/不合格

/警告ステータス

コンプライアンス・パッケージ

●180 種類を超える追加テスト

●完全なテスト記述

●サ マ リ お よ び 詳 細 テ ス ト・

レポート

●わかりやすい合格/不合格

/警告ステータス

エクセサイザ

●自動 LTSSM テスト

●制 御 可 能 な パ ケ ッ ト 作 成、

エラー挿入

●性能テスト

●コ ン フ ィ ギ ュ レ ー シ ョ ン・

スペース・テスト

N5309A エクセサイザ

エクセサイザの特長

物理層 ● シンボルのエンコード/デコード、パケット・フレーミングの生成と検証、フレーミング・エラー・レポート機能 ● スクランブルのオン/オフが可能 ● 以下の自動リンク初期化およびトレーニングを設定可能: −自動レーン極性検出(RX)、各レーン毎 −プログラマブル・レーン極性反転(TX)、各レーン毎 −自動リンク幅ネゴシエーション、リンク幅x1、x4、x8、x16をサポート、リンクのトレーニング中にリンク幅を 設定可能 −プログラマブルTXレーン反転(RX自動) −プログラマブル・レーン・スキュー:(±7シンボル、分解能:1シンボル時間)● LTSSM(Link Training and Status State Machine): Detect、Polling、Configuration、Recovery、L1、L0s、L0ステートをフル・サポー ト ● スキップOS単位でプログラマブル・スキップ・レートとSKP数 パワー・マネージメントに関する注記:L0またはL1から出るときに、エクセサイザのレシーバが2番目のSKPオーダード・ セットまでデータを受信できない場合があります。この場合パケットの損失により、PCI Expressリンクのリトレーニング が発生する可能性があります。 データ・リンク層 ● データ・リンク制御と管理ステート・マシン ● フロー制御の自動初期化、プログラマブル・クレジットとフロー制御更新レート ● データ・リンク層パケット(DLLP)の自動生成:ACK/NAK、Init/Update-FC ● LCRCとシーケンス番号の自動生成とチェック、不正なLCRCをTLPに挿入可能、自動リトライ機能 トランザクション層 ● ユーザ・ソフトウェアでトランザクションの任意シーケンスを定義可能

● 単純なパケット伝送では“Send single packet”、仮想チャネルあたり1個のブロック・トランザクション用メモリ ● RXパターン・マッチャ、外部トリガ入力、動作完了ステータスでの条件付き開始 ● 最大帯域幅でのパケットの生成と受信(ストレス・テスト)、5 GT/sでリンク幅x8まで ● 無限ループ ● コンプリータ待ち行列で動作完了パケットの送信方法(長さ、エラー挿入、パーティションなど)を定義 −動作完了を個別パケットに分割可能 ● 最大32個の未処理リクエストを「保留」可能(拡張モードでは256個)(動作完了なしのリクエスト) ● デコーダ(6 BARS+拡張ROMデコーダ) ● データ・メモリに対するペイロードの生成と受信 図 8. N5309A エクセサイザ /LTSSM エクセサイザ

N5309A エクセサイザ

エクセサイザの特長

パケット生成 ● 送信モード −単一パケットの送信 −ブロック転送 −捕捉されたアナライザ・トレースからパケットをインポート可能 ● 単一パケットの送信 −すべてのフィールドが制御された状態で、任意のタイプのTLPを送信可能 −送信パケットでエラーを作成可能 ● ブロック転送 −大容量転送(読み取りまたは書き込み)を作成、リクエスト・サイズを設定可能 −自動データ・コンパレータにより、データの破損がないことを確認可能 −性能テストにより、最大データ・レートを保証 ● 動作完了待ち行列 −任意の種類の動作完了ステータスをプログラム可能 エラーの生成と解析 物理層、データ・リンク層、トランザクション層でのエラー挿入機能 ● 物理層: −トランスミッタの極性反転 −トランスミッタのレーン反転 −最大7シンボルのレーン・スキュー − x1、x4、x8、x16デバイスをエミュレートする、リンク幅とレーン・シーケンス・ネゴシエーション −不正な「ランニング・ディスパリティ」を持つパケットの送信 − TLPでのTXフレーミング・エラー ● データ・リンク層: −不正なLCRCを持つパケットの送信 − ACKではなくNAK応答(リトライ・バッファ・テストの場合) −間違ったシーケンス数 −任意のビットを変更した自由フォーマットのDLLPを作成 ● トランザクション層: −任意のヘッダ・フィールド −“Nullified TLP”の送信 −“Poisoned TLP”の送信 −通知されたパケット長(TLPヘッダ内)が実際のパケット長と(1ワードだけ)異なる −トランスミッタがフロー制御クレジットを無視 −動作完了損失/遅延 コンフィギュレーション・ スペース ● さまざまなPCI Expressデバイスの設定をエミュレート可能 ● 最大6個の基準アドレス・レジスタと拡張ROMデコーダをサポート ● PCIヘッダ・タイプ0のコンフィギュレーション・スペースをフル・サポート ● サポートされる構造: − PCIパワー・マネージメント構造 − MSI構造 − PCI Express構造 − Virtual Channel構造 −高度なエラー・レポート構造 表示 ツリー構造によるテストの選択 GUIでのテスト・ログの表示 実行された状態遷移のフィードバック すべてのステートのタイムスタンプ、[ns]単位 リンク・ステータス・インジケータ リンク幅x1、x4、x8、x16 デバッグ・サポート L0から抜けるときに外部トリガ可能 LTSSMエクセサイザの状態遷移とタイムスタンプのログ・ファイル出力 無限のクレジットによるフロー制御の自動初期化 サポートされるステート Detect Polling Configuration L0、LOs、L1 Recovery 簡単なソフトウェア・ アップグレード PTC IIライセンスから、コンプライアンス保証テスト・パッケージ・ライセンス、フル・エクセサイザ/LTSSMソフトウェア・ ライセンスへのアップグレードN5309A エクセサイザ

仕様

システム要件

N5309Aは、PTCII、コンプライアンス保証テスト・パッケージ、エクセサイザ・アプリケーションに使用できるスタンドアロンPCIeカードです。

N5309Aカードを制御するソフトウェアは、USB 2.0で接続されたPCコントローラで動作します。 PCコントローラの詳細については、データ・シートの関連製品セクションを参照してください。

環境

温度(AT-ETM757) 動作時:0 ℃∼+55 ℃ 保管時:−40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時:15∼95% 動作時水浸:90%(24時間)安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2 環境定格:標準

一般仕様

電源要件 100∼240 Vac 130∼160 VA 1.5 A(最大) 47∼63 Hz 外形 PCI Express規格の高さ、ハーフサイズ・カード 長さ:168 mm 高さ:111 mm ヒートシンクを含むトップサイド上のコンポーネントの高さ:19 mm コネクタ フロント・ブラケット: ● USBタイプB ● Vin(18 Vdc、3.5 A) ● PCIe解析出力、独自 トップ・コネクタ: ● PCIe、コネクタx16、x1レーン接続のみ ボトム・コネクタ: ● PCIe、x1、x4、x8、x16(バージョンに依存) トリガ入力/出力: ● LVCMOS 2.5 V、ユーザ・ガイドを参照 ● Vin(最大3.0 V) 電源入力: ● トップ・コネクタに電源を供給するATX電源コネクタ SSC SSCのサポートなし データ・メモリ 128 kBN5309A エクセサイザ

仕様

電気的特性

データ入力 入力レベル: ● 最小:100 mV ● 最大:1.2 V ジッタ耐力:● PCIe Specification 2.0 Rev 0.9に準拠 周波数: ● 最小: 2.5 GHz −300 ppm*UI 5 GHz −300 ppm ● 最大: 2.5 GHz +300 ppm 5 GHz +300 ppm SSCのサポート: ● なし データ出力 出力レベル: ● 最小:800 mV(フル・スイング) ● 代表値:1000 mV ● 最大:1.2 V ディエンファシス3.5 dB: ● 代表値:3.5 dB ディエンファシス6 dB: ● 代表値:6.0 dB UIインターバル: ● 最小:−300 ppm*UI ● 最大:+300 ppm*UI 全ジッタ: ● 代表値:0.3 UI 電気的アイドル: ● 代表値:20 mV 外部クロック入力 レベル: ● 最小:800 mVdiff ● 最大:1200 mVdiff AC結合 周波数:100 MHz 基準クロック入力 PCIe仕様2.0に準拠

N5323A PCIe ジャマー

特長

一般的な機能

● スキュー、レーン極性、レーン・オーダリングなどの、デバイスの物理層特性を設定可能 ● 付属のプロトコル・チェッカにより、テスト中にプロトコル違反のフラグ付けが可能 ● テスト中にいつエラーが挿入されたかを統計表とグラフで表示 ● 外部トリガ入力/出力により、アナライザに対するトリガとアナライザからのトリガが可能ジャミング・オプション

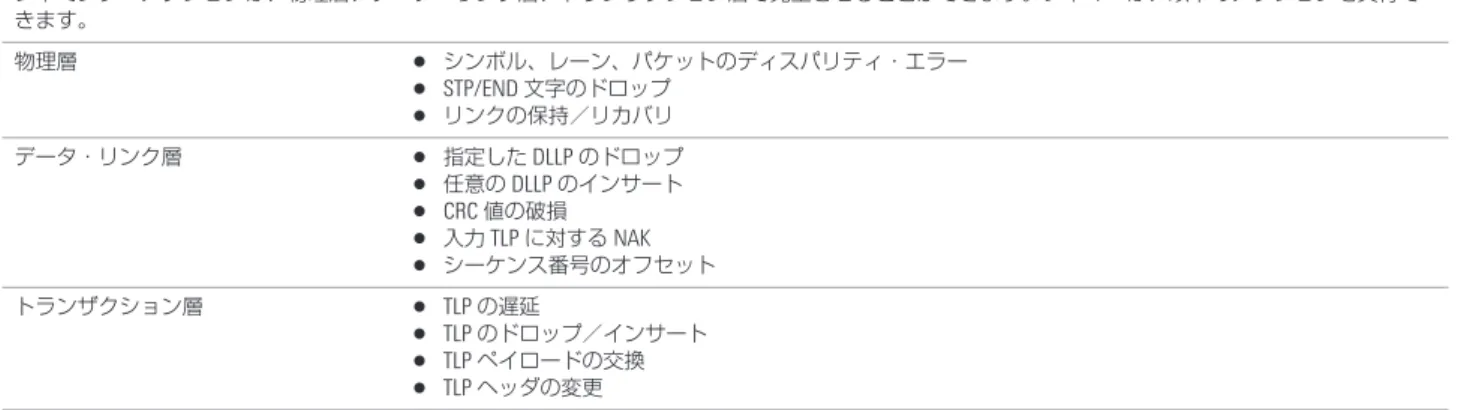

ジャミング・アクションは、物理層、データ・リンク層、トランザクション層で発生させることができます。ジャマーは、以下のアクションを実行で きます。 物理層 ● シンボル、レーン、パケットのディスパリティ・エラー ● STP/END文字のドロップ ● リンクの保持/リカバリ データ・リンク層 ● 指定したDLLPのドロップ ● 任意のDLLPのインサート ● CRC値の破損 ● 入力TLPに対するNAK ● シーケンス番号のオフセット トランザクション層 ● TLPの遅延 ● TLPのドロップ/インサート ● TLPペイロードの交換 ● TLPヘッダの変更自動テスト

ジャマーは、Agilentのその他のPCI Express製品と同様に、ジャマーのすべての機能を自動化できるAPIを提供します。これにより、連続テストが容易に なります。定義済みテスト・ケースのスイートも用意されていて、すぐにテストを開始できます。

● フル・オンライン・マニュアル付きのTCL API

● 5種類のサンプル・テスト・シナリオ・スクリプト(QuickTestフレームワークの一部) ● 追加で25種類のテスト・スクリプトを購入可能(QuickTestフレームワークの一部)

N5323A PCIe ジャマー

仕様

システム要件

N5323Aは、スタンドアロンのPCI Expressカードです。N5323Aカードを制御するソフトウェアは、USB 2.0で接続されたPCコントローラで動作します。

環境

温度(AT-ETM757) 動作時:0 ℃∼+55 ℃ 保管時:−40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時:15∼95 %

動作時水浸:90 %(24時間)

安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2 環境定格:標準

一般仕様

電源要件 100∼240 Vac 130∼160 VA 1.5 A(最大) 47∼63 Hz 外形 PCI Expressハーフサイズ・カード(長さ:168 mm、高さ:181 mm) ヒートシンクを含む上面のコンポーネントの高さ:19 mm コネクタ フロント・ ブラケット ● USBタイプB ● Vin(18 Vdc、 3.5 A) ● PCIe解析出力、 独自 トップ・コネクタ ● PCIe、コネクタ x16、最大x8 レーン接続 ボトム・コネクタ ● PCIe x1、x4、x8(バー ジョンに依存) トリガ入出力 ● LVCMOS 3.3 V、 ユーザ・ガイド を参照 ● Vin(最大4.6 V) 電源入力 ● トップ・コネ クタに電源を 供給するATX 電源コネクタ SSC SSCのサポートあり データ・メモリ 128 KB電気的特性

データ入力 入力レベル ● 最小:100 mV ● 最大:1.2 V ジッタ耐力 ● PCIe Specification 2.0 Rev 0.9に準拠 周波数 ● 最小: 2.5 GHz ±300 ppm 5 GHz ±300 ppm ● 最大: 2.5 GHz +300 ppm; 5 GHz +300 ppm SSCのサポート ● あり データ出力 出力レベル ● 最小:800 mV(フル・スイング) ● 代表値:1000 mV ● 最大:1.2 V UIインターバル ● 最小:−300 ppm*UI ● 最大:+300 ppm*UI ディエンファシス 3.5 dB ● 代表値:3.5 dB 全ジッタ ● 代表値:0.3 UI ディエンファシス 6 dB ● 代表値:6.0 dB 電気的アイドル ● 代表値:20 mV 外部クロック入力 最小レベル:800 mVdiff 最大レベル:1200 mVdiff AC結合 周波数:100 MHz 基準クロック入力 PCIe Specification 2.0に準拠N4241A/2A/3A/N5328A ミッドバス・プローブ

特長

ソフトタッチ・テクノロジーを使用したAgilentミッドバス2.0シリーズのプローブは、最大16チャネルをサポートし、システムに影響を与えることな くシステムを解析できます。

一般 ● 4種類のミッドバス・プローブ:ストレート(N4241A)、スウィズルx16(N4242A)、スプリットx4(N4243A)、 ハーフ(N5328A) ● すべてのリンク幅とリンク・タイプに使用可能なミッドバス・インタポーザ ● 約1.5 mのケーブル長により、アナライザとテスト・システム間で柔軟なセットアップが可能 図 10. N4241A/2A/3A ミッドバス・プローブ 図 12. ミッドバス・インタポーザ 図 11. ミッドバス・プローブ・ヘッド

N4241A/2A/3A/N5328A ミッドバス・プローブ

仕様

詳細については、ミッドバス・プローブのマニュアルを参照してください。

環境

温度(AT-ETM757) 動作時:0 ℃∼+40 ℃ 保管時:−40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時:15∼95% 動作時水浸:90%(24時間)安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2 環境定格:標準 通気 毎分140リニア・フィート(1本のプローブ、1インチ(約2.5 cm)の距離内に熱源がない場合) 毎分200リニア・フィート(2本のプローブを最小間隔で並べた場合)

一般仕様

物理特性 幅:19.70 cm 奥行:14.50 cm 高さ:2.80 cm 質量:0.75 kg プローブ・ケーブル長 1.5 m電気的特性

絶対最大定格 振幅データ信号:2 Vppdiff 振幅基準クロック:5 Vppdiff ジッタ耐力 アイ幅:0.6 UI(最小) トレース長(トランスミッタ):9 インチ(ワーストケース・シナリオでの最大値) 容量性負荷 150fF データ信号 周波数: ● 最小:2.5 GHz −300 ppm 5 GHz −300 ppm ● 最大:2.5 GHz +300 ppm 5 GHz +300 ppm 最小アイ開口:60 mV(0.6 UIのアイ幅) 最大入力振幅:1600 mVppdiff(0.85 UIのアイ幅) 基準クロック* 振幅: ● 最小:800 mVppdiff ● 最大:2000 mVppdiff DCオフセット: ● 最小:0 mV ● 最大:500 mV 周波数: ● 最小:100 MHz −300 ppm ● 最大:100 MHz +300 ppm SSC: ● 最小:−0.5% ● 最大:0%N4241F フライング・リード・プローブ

特長

N4241F フライング・リード・プローブ

仕様

詳細については、フライング・リード・プローブのマニュアルを参照してください。

環境

温度(AT-ETM757) 動作時:0 ℃∼+40 ℃ 保管時:−40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時: 15∼95 % 動作時水浸:90 %(24時間)安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2 環境定格:標準 通気 毎分140リニア・フィート(1本のプローブ、2.5cmの距離内に熱源がない場合) 毎分200リニア・フィート(2本のプローブを最小間隔で並べた場合) 図 13. フライング・リード・プローブ Agilentフライング・リード・プローブ2.0は、検出しにくい信号を表示できるモバイル/エンベディッド・システム用のプローブです。予めコネクタを デザインしなくても5 Gb/sの速度でPCIeリンクにアクセスできます。 一般 ● 各プローブでx8 PCI Expressリンクまでモニタ可能、2本のプローブを組み合わせるとx16リンクまでモニ タ可能 ● 約1.5 mのケーブル長により、アナライザとテスト・システム間で柔軟なセットアップが可能 プローブ・チップ ● ソケット付きのプローブ・チップにより、抵抗への信頼性の高い接続が可能 ● プローブ・チップ外で増幅が行われるので、小型化でき、温度の問題が減少

一般仕様

物理特性 幅:19.70 cm 奥行:14.50 cm 高さ:2.80 cm 質量:0.75 kg プローブ長 アナライザのケーブル長:1.5 m プローブ・チップ特性 ソケット付きの差動チップ 寸法 ● フライング・リード長:15 cm ● チップ幅:4.71 mm ● チップ長:3.33 mm電気的特性

絶対最大定格 振幅データ信号:2 Vppdiff 振幅基準クロック:5 Vppdiff ジッタ耐力 アイ幅:0.65 UI(最小) トレース長トランスミッタ:23 cm(ワーストケースでの最大値) 容量性負荷 200 fF データ信号 注記:これらの測定値は、Agilent が提供する抵抗(E5381-82101)を 使用した場合にだけ有効です。 周波数 ● 最小:2.5 GHz −300 ppm 5 GHz −300 ppm ● 最大:2.5 GHz +300 ppm 5 GHz +300 ppm 最小アイ開口:75 mV(0.65 UIのアイ幅) 最大入力振幅:1600 mVppdiff(0.85 UIのアイ幅) 基準クロック 振幅 ● 最小:800 mVppdiff ● 最大:2000 mVppdiff DCオフセット ● 最小:0 mV ● 最大:500 mV 周波数 ● 最小:100 MHz −300 ppm ● 最大:100 MHz +300 ppm SSC ● 最小:−0.5 % ● 最大:0 %N4241F フライング・リード・プローブ

仕様

N5315A スロット・インタポーザ・プローブ

特長

インタポーザ ● アナログ・リピーティング・スロット・インタポーザ ● 物理リンク幅:x1 x4 x8 x16 ● 電気アイドル条件も伝搬 ● 被試験デバイスに対して機械的に安定 ● ケーブル・ホルダを装備 ● バックプレーンとの機械的な安定性により、PCIeスロットとの緊密な接続が可能 ● パワー・マネージメント機能(15-35 FTS) 図 14. N5315A インタポーザ・プローブN5315A スロット・インタポーザ

仕様

環境

温度(AT-ETM757) 動作時:0 ℃∼+55 ℃ 保管時:40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時:15∼95% 動作時水浸:90%(24時間)安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2 環境定格:標準

一般仕様

ディスプレイ 4桁LEDディスプレイ・ステータス LED 2個のステータスLED 電源要件 100∼240 Vac 130∼160 VA 1.5 A(最大) 47∼63 Hz 外形 長さ:195.8 mm 高さ:169.5 mm プローブ・ケーブル長 1.0 m コネクタ フロント・ブラケット:Vin(18 Vdc、3 A) トップ・コネクタ:PCIe、コネクタx16 ボトム・コネクタ:PCIe、x1、x4、x8、x16(バージョンに依存)電気的特性

絶対最大定格 振幅データ信号:2 V ppdiff 振幅基準クロック:5 V ppdiff ジッタ耐力 アイ幅:0.6 UI(最小) トレース長(トランスミッタ):9 インチ(ワーストケース・シナリオの最大) DUTパス 追加ジッタ:0.1U未満 出力電圧レベル:入力信号の100∼110% 遅延:1200 ps レーン間スキュー:30 ps未満 外部クロック・レベル 最小:800 mV diff 最大:2000 mV diff AC結合周波数:100 MHzN5316A パッシブ・バックプレーン

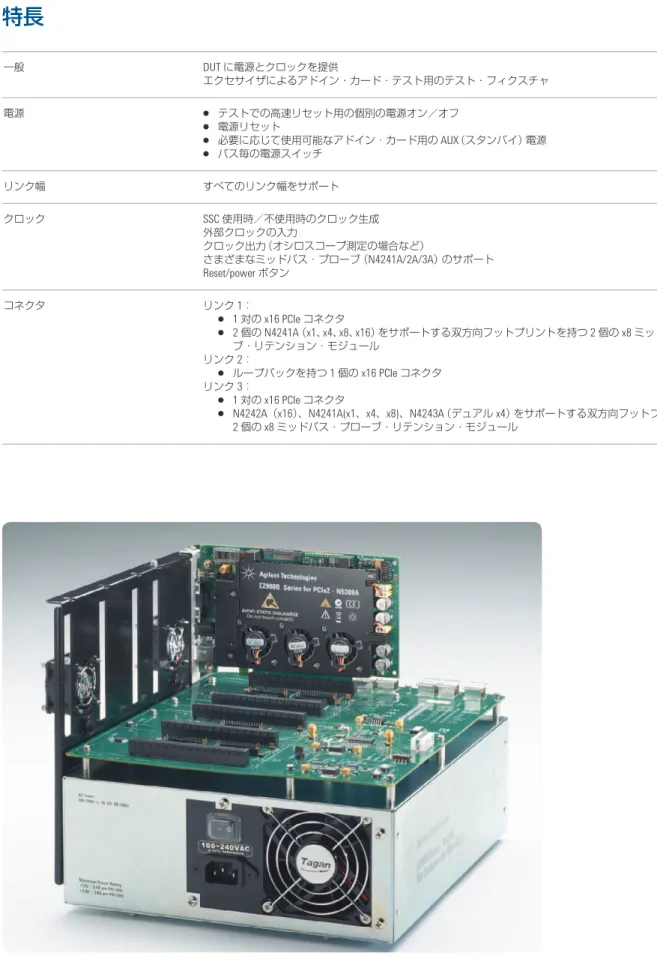

特長

一般 DUTに電源とクロックを提供 エクセサイザによるアドイン・カード・テスト用のテスト・フィクスチャ 電源 ● テストでの高速リセット用の個別の電源オン/オフ ● 電源リセット ● 必要に応じて使用可能なアドイン・カード用のAUX(スタンバイ)電源 ● バス毎の電源スイッチ リンク幅 すべてのリンク幅をサポート クロック SSC使用時/不使用時のクロック生成 外部クロックの入力 クロック出力(オシロスコープ測定の場合など) さまざまなミッドバス・プローブ(N4241A/2A/3A)のサポート Reset/powerボタン コネクタ リンク1: ● 1対のx16 PCIeコネクタ ● 2個のN4241A(x1、x4、x8、x16)をサポートする双方向フットプリントを持つ2個のx8ミッドバス・プロー ブ・リテンション・モジュール リンク2: ● ループバックを持つ1個のx16 PCIeコネクタ リンク3: ● 1対のx16 PCIeコネクタ● N4242A(x16)、N4241A(x1、x4、x8)、N4243A(デュアルx4)をサポートする双方向フットプリントを持つ

2個のx8ミッドバス・プローブ・リテンション・モジュール

N5316A パッシブ・バックプレーン

仕様

環境

温度(AT-ETM757) 動作時:0 ℃∼+55 ℃ 保管時:−40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時:15∼95%安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2 環境定格:標準

一般仕様

電源要件 100-240 Vac 10/6A 47∼63 Hz コネクタ 5x PCI Express x16物理コネクタ N4241A/2A/3Aミッドバス・プローブを保持するための5個のミッドバス・プローブ・リテーナ DUT電源コネクタ 寸法 長さ:30.5 cm 幅:24.5 cm 高さ:13.5 cm、リア・カバーを除く 質量:約5 kg電気的特性

スロット電源電圧 最大電源定格: ● +12 V/5.5 A、PCIスロットあたり ● +3.3 V/3.0 A、PCIスロットあたり コネクタ 電源出力コネクタ ディスク・ドライブ電源コネクタ: ● 12 V 5.5 A(最大) ● 5 V 3 A(最大) クロック SMA外部クロック入力: ● 800 mVpp、AC結合オンボード SMAクロック出力: ● 50 Ωに終端 ● レベル: 800 mVpp(代表値) PCIコネクタでの基準クロック:● PCI Express Specification 2.0 Rev 0.9に準拠 ● 周波数100 MHz±300 ppm

サポートされるSSC:

N5313A P2L ゲートウェイ・ケーブル

仕様

図 18. P2L のシステム表示 16900 ロジック・ アナライザ DDR/FBD、FPGA、FSB P2L ゲートウェイ クロス・トリガ 相関マーカ PCI Express一般 ● Agilentロジック・アナライザとE2960B PCI Expressプロトコル・アナライザから、オールインワンのツール を構築 ● ロジック・アナライザでモニタされるバスとPCI Expressバス間の相互作用をフル表示 GUI ● ロジック・アナライザとプロトコル・アナライザ間の時間相関表示 ● 両方の測定器間でマーカを共有 トリガ ● ロジック・アナライザとプロトコル・アナライザ間のクロス・トリガ コネクタ ● PCI Expressモジュールに接続 ● 3個のBNCコネクタを16900ロジック・アナライザ・モジュールに接続 図 16. PCI Express- ロジック・アナライザ間の相関システム 図 17. N5313A P2L ゲートウェイ・ケーブル

N5319A P2L ゲートウェイ・ケーブル(フラグ・サポート付き)

仕様

一般 ● Agilentロジック・アナライザとE2960B PCI Expressプロトコル・アナライザから、オールインワンのツール を構築 ● ロジック・アナライザでモニタされるバスとPCI Expressバス間の相互作用をフル表示 GUI ● ロジック・アナライザとプロトコル・アナライザ間の時間相関表示 ● 両方の測定器間でマーカを共有 トリガ ● ロジック・アナライザとプロトコル・アナライザ間のクロス・トリガ ● フラグ・サポートによるロジック・アナライザとプロトコル・アナライザ間のピンポン・トリガ。4つの フラグをサポート コネクタ ● PCI Expressプロトコル・アナライザに接続 ● 16900ロジック・アナライザ・モジュールに接続 16900 ロジック・ アナライザ DDR/FBD、 FPGA、FSB P2L ゲートウェイ 相関マーカ PCI Express 図 20. N5319A P2L ゲートウェイ・ケーブル (フラグ・サポート付き) フラグによる ピンポン・トリガ 図 19. PCI Express 図 21. P2L のシステム表示

関連製品

N5540A(2 スロット)または N5541A(4 スロット)シャーシ

環境

温度(AT-ETM757) 動作時:0 ℃∼+55 ℃ 保管時:−40 ℃∼+70 ℃ 湿度(AT-ETM758) 動作時:15∼95 % 動作時水浸:90 %(24時間)安全規格 設置カテゴリ:EN ISO/IEC 17025、IEC 61010-1/EN61010-1、II

汚染度:2 環境定格:標準

一般仕様

電源要件 100∼120 Vac 200∼250 Vac 550 VA(最大) 47∼63 Hz物理特性

2スロット・シャーシ 幅:30 cm 奥行:49.0 cm 高さ:11 cm 質量(スロットが空の場合):5.1 kg 4スロット・シャーシ 幅:45.4 cm、EIA標準48.3 cmラックに搭載可能 奥行:49.0 cm 高さ:2U(8.89 cm) 質量(スロットが空の場合):9.1 kgコネクタ

MDI RJ-45、100 Mb/sイーサネット(PCコントローラへ) MDI-X RJ-455、100 Mb/sイーサネット(次のシャーシへ) ATハードドライブ電源 プローブ・ボード上のコネクタ(12 Vのみを使用可能) 外部トリガ入力 BNC(メス)、外部デバイスからのトリガ入力 外部トリガ出力 BNC(メス)、外部デバイスへのトリガ出力関連製品

N5543E PC コントローラ

最小システム要件

アナライザまたはエクセサイザ・モジュールを制御するために PC コントローラが必要です。コントローラは、Agilent

N5543E として購入できます。または、同等の仕様の PC を使用できます。

ハードウェア Intel Core Duoプロセッサ 2.26 GHzまたは同等品

2 GBのRAM DVD/CD-R/Wドライブ(オプション) 14.1" LCDディスプレー N2Xシャーシ接続用LANポート エクセサイザとN2Xシャーシ用のUSB 2.0(USBベース)

タイトル

カタログ番号

PCI Express 2.0におけるフル ・ テスト・ソリューション Brochure 5989-5594JAJP PCI Express Gen 2対応Agilentのテスト・ツール Photo Card 5989-6395JAJP E2969B PCI Express 2.0 用プロトコル・テスト・カードII 5989-7594JAJP Agilent E2969A Protocol Test Card for PCI Express Photo card 5989-9520EN Agilent PCIeジャマー Brochure 5990-3222JAJP

オーダ情報

プロトコル・アナライザ

ハードウェア

概要

N5306A アナライザ・モジュール、PCIe 5 Gb/s用 N5322A 拡張インタフェース・モジュール、PCIe 5 Gb/s用ソフトウェア

概要

Gen2アナライザ・ソフトウェア N5306A-A01 アナライザSWライセンスx1、PCIe 5 Gb/s用

N5306A-A04 アナライザSWライセンスx4、PCIe 5 Gb/s用

N5306A-A08 アナライザSWライセンスx8、PCIe 5 Gb/s用

N5306A-A16 アナライザSWライセンスx16、PCIe 5 Gb/s用

Gen2 Readyアナライザ・ソフトウェア N5306A-G01 Gen2 ReadyアナライザSWライセンスx1、PCIe 2.5 Gb/s用

N5306A-G04 Gen2 ReadyアナライザSWライセンスx4、PCIe 2.5 Gb/s用

N5306A-G08 Gen2 ReadyアナライザSWライセンスx8、PCIe 2.5 Gb/s用

N5306A-G16 Gen2 ReadyアナライザSWライセンスx16、PCIe 2.5 Gb/s用

プローブ

概要

Gen2プローブ N4241A ミッドバス・プローブ2.0双方向x8、PCIe 5 Gb/s用

N4242A ミッドバス・プローブ2.0スウィズルx16、PCIe 5 Gb/s用 N4243A ミッドバス・プローブ2.0キット・スプリットx4、PCIe 5 Gb/s用 N4241F フライング・リード・セット2.0双方向x8、PCIe 5 Gb/s用 N5315A-A01 スロット・インタポーザ、PCIe 5 Gb/sリンク幅x1用 N5315A-A04 スロット・インタポーザ、PCIe 5 Gb/sリンク幅x4用 N5315A-A08 スロット・インタポーザ、PCIe 5 Gb/sリンク幅x8用 N5315A-A16 スロット・インタポーザ、PCIe 5 Gb/sリンク幅x16用

Gen1プローブ E2960B-MEC Expressカード・アダプタ、PCIe 2.5 Gb/s用(N4241Aの場合)

E2945A PCI Express x1パッシブ・プローブ・ボード

E2946A PCI Express x4パッシブ・プローブ・ボード

E2947A PCI Express x8パッシブ・プローブ・ボード

E2941B EXCH AVAILソフト・タッチ・ミッドバス・プローブ、PCI-Express用

N4221A ミッドバス・プローブ1.0 双方向x8、PCIe 2.5 Gb/s用

N4221F フライング・リード・セット1.0双方向 x8、PCIe 2.5 Gb/s用

N4228A ハーフサイズ圧縮ケーブル・セット、PCI Express 2.5 Gb/s用

N5317A PCIeプローブ接続ケーブル(Gen1プローブをGen2システムに接続)

アクセサリ

概要

N5540A N2X 2スロット・ポータブル・シャーシ N5541A N2X 4スロット・シャーシ N5543D N2X PCコントローラ E2960B-LAN シャーシ-コントローラ・インタフェース用USB-LANアダプタ E2960B-RET-05 リテンション・モジュール、ミッドバス・プローブ2.0 - 5 pcs用 E2960B-RET-50 リテンション・モジュール、ミッドバス・プローブ2.0 - 50 pcs用 ロジック・アナライザとプロトコル・ アナライザの相関アクセサリN5313A 16900AとE2960Bアナライザの接続用のP2Lゲートウェイ・ケーブル

オーダ情報

エクセサイザ

ハードウェア

概要

N5309A-E01 ハーフ・サイズ・エクセサイザおよびLTSSMモジュールx1、PCIe 5 Gb/s用 N5309A-E04 ハーフ・サイズ・エクセサイザおよびLTSSMモジュールx4、PCIe 5 Gb/s用 N5309A-E08 ハーフ・サイズ・エクセサイザおよびLTSSMモジュールx8、PCIe 5 Gb/s用 N5309A-E16 ハーフ・サイズ・エクセサイザおよびLTSSMモジュールx16、PCIe 5 Gb/s用ソフトウェア

概要

Gen2エクセサイザ・ソフトウェア N5309A-EX2 エクセサイザSWライセンス:エクセサイザおよびLTSSM、5 Gb/s Gen2 Readyエクセサイザ・ ソフトウェアN5309A-EX1 Gen2 ReadyエクセサイザSWライセンス:エクセサイザおよびLTSSM、2.5 Gb/s

コンプライアンス・テスト N5309A-PTC エクセサイザSWライセンス:プロトコル・テスト・カード・ソフトウェア (エクセサイザの購入時に付属) N5309A-COM エクセサイザSWライセンス:コンプライアンス保証テスト・パッケージ (180種類の定義済みテスト)

アクセサリ

概要

N5543D N2X PCコントローラ N5316A PCIe2用テスト・バックプレーンプロトコル・テスト・

カード

概要

PTC1 E2969A PCI Express Gen 1用プロトコル・テスト・カード(ソフトウェアとハードウェアを含む)

PTC2 E2969B PCI Express Gen 2用プロトコル・テスト・カード(ソフトウェアとハードウェアを含む)

ジャマー

ハードウェア

概要

N5323A-J01 ジャマー・モジュールx1、PCIe 5Gb/s 用 N5323A-J04 ジャマー・モジュールx4、PCIe 5Gb/s 用 N5323A-J08 ジャマー・モジュールx8、PCIe 5Gb/s 用ソフトウェア

概要

N5323A-JM1 Gen2 Ready ジャマーSW ライセンス:2.5 Gb/s N5323A-JM2 ジャマーのSW ライセンス:5Gb/s

N5323A-SCR ジャマーのSW ライセンス:ジャマー・スクリプト

アクセサリ

概要

Remove all doubt

アジレント・テクノロジーでは、柔軟性の高い 高品質な校正サービスと、お客様のニーズに応 じた修理サービスを提供することで、お使いの 測定機器を最高標準に保つお手伝いをしていま す。お預かりした機器をお約束どおりのパフォ ーマンスにすることはもちろん、そのサービス をお約束した期日までに確実にお届けします。 熟練した技術者、最新の校正試験プログラム、 自動化された故障診断、純正部品によるサポー トなど、アジレント・テクノロジーの校正・修 理サービスは、いつも安心で信頼できる測定結 果をお客様に提供します。 また、お客様それぞれの技術的なご要望やビジ ネスのご要望に応じて、 ● アプリケーション・サポート ● システム・インテグレーション ● 導入時のスタート・アップ・サービス ● 教育サービス など、専門的なテストおよび測定サービスも提 供しております。 世界各地の経験豊富なアジレント・テクノロジ ーのエンジニアが、お客様の生産性の向上、設 備投資の回収率の最大化、測定器のメインテナ ンスをサポートいたします。詳しくは:www.agilent.co.jp/find/removealldoubt

電子計測UPDATEwww.agilent.co.jp/find/emailupdates-Japan

Agilent からの最新情報を記載した電子メー ルを無料でお送りします。Agilent Direct

www.agilent.co.jp/find/agilentdirect

測定器ソリューションを迅速に選択して、使用 できます。PCI Express および PCIe は、PCI-SIG®の登

録商標です。

Windows は、Microsoft Corporation の登 録商標です。

Pentium は、Intel Corporation の登録商標で す。