Virtex-6 FPGA

メ モ リ

リ ソ ース

ユーザー

ガ イ ド

display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2009–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. 本資料は英語版 (v1.5) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。

資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。

改訂履歴

本書の改訂履歴は以下の と お り です。 日付 バージ ョ ン 変更内容 2009 年 6 月 24 日 1.0 初版 リ リ ース 2009 年 9 月 16 日 1.1 ま えが き の 「 こ のユーザーガ イ ド について」 を更新。「非同期 ク ロ ッ ク 」 で、 READ_FIRST モー ド に関す る 箇条書 き 項目を追加。「書 き 込みモー ド 」 で、SDP モー ド のブ ロ ッ ク RAM の READ_FIRST モー ド に関す る 説明を明確化。22 ページの図 1-9 と23 ページの表 1-6で WEBWE ピ ンの記述を変更。「未使用の入力」 で、 未使用デー タ入力の接続先を Low に変更。35 ページの 「RAMB18E1 お よ び RAMB36E1 のポー ト

マ ッ プ設計ルール」を変更。49 ページの 「FIFO の動作」 で、RESET の説明を変更。

2009 年 11 月 9 日 1.2 図 1-1の見出 し を変更。図 1-6 と表 1-3を加筆訂正。26 ページの 「セ ッ ト/リ セ ッ ト 」を

変更。表 1-15と表 1-16を追加 し 、 その直前の説明文を変更。表 2-5で SRVAL の説明

を変更 し 、INIT 属性 と 注 3 を追加。53 ページの表 2-6を追加。

2010 年 1 月 18 日 1.3 「 リ セ ッ ト 」 の記述を明確化。表 2-3で WREN と RDEN の説明を加筆。「FIFO

ALMOST FULL/EMPTY フ ラ グのオ フ セ ッ ト 範囲」 で最大オ フ セ ッ ト 値に関す る 式 と 例を追加。 2010 年 1 月 19 日 1.3.1 誤植を訂正。 2010 年 5 月 20 日 1.4 17 ページの 「非同期 ク ロ ッ ク 」の説明を変更。 「概要」お よ び 「ECC の動作モー ド 」の ECCPARITY に関す る 説明を変更。表 3-1お よ び表 3-2の ECCPARITY に関す る 説明を変更。79 ページの 「標準モー ド の ECC」お よ び81 ページの 「ECC タ イ ミ ン グ特性」の ECCPARITY の使用法を変更。表 3-5よ り TRCKO_PARITY_ECCを削除。 2010 年 8 月 3 日 1.5 SDP ブ ロ ッ ク RAM の WRITE_FIRST モー ド を説明す る ために 「書 き 込みモー ド 」の セ ク シ ョ ン を変更。34 ページの 「ブ ロ ッ ク RAM の ロ ケーシ ョ ン制約」を変更。

改訂履歴. . . 3

このユーザー

ガ イ ド について

ユーザーガ イ ド の内容 . . . 9 その他の資料. . . 9 その他の リ ソ ース . . . 10第

1

章

:

ブ ロ ッ ク

RAM

リ ソ ース

概要 . . . 11 ブ ロ ッ ク RAM の説明. . . 13 同期デ ュ アルポー ト お よ びシ ン グルポー ト RAM . . . 14 デー タ フ ロ ー. . . .14 読み出 し. . . .15 書 き 込み. . . .15 書 き 込みモー ド . . . .15 WRITE_FIRST ま たは透過モー ド (デフ ォ ル ト) . . . .16 READ_FIRST ま たは書 き 込み前読み出 し モー ド . . . .16 NO_CHANGE モー ド. . . .17 競合の回避 . . . .17 非同期 ク ロ ッ ク . . . .17 同期 ク ロ ッ ク . . . .18 Virtex-6 デバ イ ス のブ ロ ッ ク RAM のその他の機能. . . 18 出力レ ジ ス タ (オプシ ョ ン) . . . .18 個別に選択可能な読み出 し ポー ト と 書 き 込みポー ト の幅. . . .18 シ ンプルデ ュ アルポー ト ブ ロ ッ ク RAM . . . .19 カ ス ケー ド 接続可能なブ ロ ッ ク RAM . . . .20 バ イ ト ラ イ ト イ ネーブル . . . .21 ブ ロ ッ ク RAM の ECC (エ ラ ー訂正 コ ー ド) . . . .21 ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ. . . 22 ブ ロ ッ ク RAM のポー ト 信号 . . . 26 ク ロ ッ ク - CLKARDCLK、CLKBWRCLK . . . .26 イ ネーブル - ENARDEN、ENBWREN . . . .26 バ イ ト ラ イ ト イ ネーブル - WEA、WEBWE . . . .26レ ジ ス タ イ ネーブル - REGCEA、REGCE、REGCEB . . . .26

セ ッ ト/リ セ ッ ト . . . .26

RSTREGARSTREG、RSTREGB、RSTRAMARSTRAM、RSTRAMB . . . .26

ア ド レ スバ ス - ADDRARDADDR、ADDRBWRADDR . . . .27

デー タ 入力バス - DIADI、DIPADIP、DIBDI、DIPBDIP . . . .29

デー タ 出力バス - DOADO、DOPADOP、DOBDO、DOPBDOP . . . .29

カ ス ケー ド 入力 . . . .29

CASCADEINA、CASCADEINB、CASCADEOUTA、CASCADEOUTB . . . .29

制御ピ ンの反転 . . . .30 GSR . . . .30 未使用の入力 . . . .30 ブ ロ ッ ク RAM のア ド レ スマ ッ プ. . . 30 ブ ロ ッ ク RAM の属性. . . 31 メ モ リ 内容の初期化 - INIT_xx . . . .31 パ リ テ ィ メ モ リ 内容の初期化 - INITP_xx . . . .32

出力 ラ ッ チの初期化 - INIT (INIT_A ま たは INIT_B) . . . .32

出力 ラ ッ チ/レ ジ ス タ の同期セ ッ ト/リ セ ッ ト (SRVAL_[A|B]) . . . .32

リ セ ッ ト ま たは CE の優先度 - RSTREG_PRIORITY_[A|B]. . . .33

書 き 込み幅 - WRITE_WIDTH_[A|B] . . . .33 モー ド 選択 - RAM_MODE . . . .34 書 き 込みモー ド - WRITE_MODE_[A|B] . . . .34 ブ ロ ッ ク RAM の ロ ケーシ ョ ン制約 . . . .34 VHDL ま たは Verilog コ ー ド でのブ ロ ッ ク RAM の初期化. . . 34 RAMB18E1 お よ び RAMB36E1 プ リ ミ テ ィ ブの設計上のその他の注意事項 . . . 34 出力レ ジ ス タ (オプシ ョ ン) . . . .35 独立 し た読み出 し ポー ト と 書 き 込みポー ト の幅を選択. . . .35 RAMB18E1 お よ び RAMB36E1 のポー ト マ ッ プ設計ルール. . . .35 カ ス ケー ド 接続可能なブ ロ ッ ク RAM . . . .36 バ イ ト ラ イ ト イ ネーブル . . . .36 ブ ロ ッ ク RAM のアプ リ ケーシ ョ ン. . . 36 大規模な RAM 構造の作成 . . . .36 レ ジ ス タ モー ド のブ ロ ッ ク RAM の RSTREG . . . .37 ブ ロ ッ ク RAM の タ イ ミ ン グモデル . . . 38 ブ ロ ッ ク RAM の タ イ ミ ン グパ ラ メ ー タ. . . .39 ブ ロ ッ ク RAM の タ イ ミ ン グ特性. . . .40 ク ロ ッ ク イ ベン ト 1 . . . .40 ク ロ ッ ク イ ベン ト 2 . . . .41 ク ロ ッ ク イ ベン ト 4 . . . .41 ク ロ ッ ク イ ベン ト 5 . . . .41 ブ ロ ッ ク RAM の タ イ ミ ン グモデル. . . .42

第

2

章

:

ビル ト イ ン

FIFO

のサポー ト

概要 . . . 43 デ ュ アルク ロ ッ ク FIFO . . . 43 同期 FIFO . . . 44 同期 FIFO イ ンプ リ メ ン テーシ ョ ン . . . .45 FIFO アーキ テ ク チ ャ の概略図. . . 46 FIFO プ リ ミ テ ィ ブ . . . 46 FIFO ポー ト の説明 . . . 47 FIFO の動作. . . 49 リ セ ッ ト . . . .49 動作モー ド . . . .49 標準モー ド. . . .49FWFT (First Word Fall Through) モー ド . . . .49

ス テー タ ス フ ラ グ . . . .49 EMPTY フ ラ グ . . . .50 ALMOST EMPTY フ ラ グ . . . .50 READ ERROR フ ラ グ . . . .50 FULL フ ラ グ. . . .51 WRITE ERROR フ ラ グ . . . .51 ALMOST FULL フ ラ グ . . . .51 FIFO の属性. . . 51

FIFO ALMOST FULL/EMPTY フ ラ グのオ フ セ ッ ト 範囲. . . .53

VHDL お よ び Verilog の FIFO テ ンプ レー ト . . . 55 FIFO の タ イ ミ ン グモデル と パ ラ メ ー タ . . . 55 FIFO の タ イ ミ ン グ特性. . . .57 ケース 1 : 空の FIFO への書 き 込み . . . .57 ケース 2 : フルま たはほぼフルの FIFO への書 き 込み . . . .59 ケース 3 : フルの FIFO か ら の読み出 し . . . .60 ケース 4 : 空ま たはほぼ空の FIFO か ら の読み出 し . . . .61 ケース 5 : すべてのフ ラ グ を リ セ ッ ト . . . .63

ケース 6 : デ ュ アルク ロ ッ ク FIFO に対す る 読み出 し と 書 き 込みの同時実行. . . .63 FIFO のアプ リ ケーシ ョ ン. . . 64 FIFO のカ ス ケー ド 接続に よ る ワー ド 数の拡張. . . .64 FIFO の並列接続に よ る ビ ッ ト 数の拡張 . . . .65 ブ ロ ッ ク RAM と FIFO の有効な組み合わせ . . . 66

第

3

章

:

ビル ト イ ン

エ ラ ー訂正

概要 . . . 67 ECC の動作モー ド. . . 68 ブ ロ ッ ク RAM ECC アーキ テ ク チ ャ の概略図. . . 69ブ ロ ッ ク RAM お よ び FIFO ECC プ リ ミ テ ィ ブ . . . .70

ブ ロ ッ ク RAM お よ び FIFO ECC のポー ト. . . 71

ブ ロ ッ ク RAM お よ び FIFO ECC の属性 . . . 75

ECC モー ド の動作. . . 76 標準モー ド の ECC . . . .79 属性での設定 . . . .79 標準 ECC の書 き 込み (図 3-4) . . . .79 標準 ECC の読み出 し (図 3-5) . . . .79 エン コ ー ド 専用モー ド の ECC . . . .80 属性での設定 . . . .80 エン コ ー ド 専用 ECC での書 き 込み . . . .80 エン コ ー ド 専用 ECC での読み出 し . . . .80 デ コ ー ド 専用モー ド の ECC . . . .80 属性での設定 . . . .80 デ コ ー ド 専用 ECC でのシ ン グルビ ッ ト エ ラ ーの挿入. . . .80 デ コ ー ド 専用 ECC でのダブルビ ッ ト エ ラ ーの挿入. . . .81 ECC タ イ ミ ン グ特性. . . 81 標準 ECC の書 き 込み タ イ ミ ン グ (図 3-4) . . . .81 標準 ECC の読み出 し タ イ ミ ン グ (図 3-5) . . . .81 DO_REG = 0 の場合. . . .81 DO_REG = 1 の場合. . . .82 エン コ ー ド 専用 ECC の書 き 込み タ イ ミ ン グ (図 3-4). . . .82 エン コ ー ド 専用 ECC の読み出 し タ イ ミ ン グ . . . .82 デ コ ー ド 専用 ECC の書 き 込み タ イ ミ ン グ . . . .82 デ コ ー ド 専用 ECC の読み出 し タ イ ミ ン グ . . . .82 ブ ロ ッ ク RAM ECC モー ド の タ イ ミ ン グパ ラ メ ー タ. . . 83 64 ビ ッ ト ワー ド 用 8 ビ ッ ト パ リ テ ィ の作成 . . . 84

こ のユーザー

ガ イ ド について

こ のユーザーガ イ ド は、Virtex®-6 FPGA のブ ロ ッ ク RAM について説明 し たテ ク ニ カル リ フ ァ レ

ン ス です。 ブ ロ ッ ク RAM は、 効率的なデー タ の格納やバ ッ フ ァ に活用 し 、 高性能な ス テー ト マシ ン ま たは FIFO バ ッ フ ァ 、 大規模シ フ ト レ ジ ス タ 、 大規模なル ッ ク ア ッ プテーブル、ROM な ど に 使用 さ れます。

ユーザー

ガ イ ド の内容

こ のユーザーガ イ ド は、 次の各章か ら 構成 さ れてい ます。 • 第 1 章 「ブ ロ ッ ク RAM リ ソ ース」 • 第 2 章 「ビル ト イ ン FIFO のサポー ト 」 • 第 3 章 「ビル ト イ ンエ ラ ー訂正」その他の資料

次の資料 も 、http://japan.xilinx.com/support/documentation/virtex-6.htmか ら ダ ウ ン ロー ド で き ます。 • 『Virtex-6 フ ァ ミ リ 概要』 Virtex-6 フ ァ ミ リ の特徴 と 製品群の概要を説明 し てい ます。 • 『Virtex-6 デー タ シー ト : DC 特性お よ びス イ ッ チ特性』 Virtex-6 フ ァ ミ リ の DC お よ びス イ ッ チ特性を含むデー タ シー ト です。 • 『Virtex-6 FPGA パ ッ ケージお よ びピ ン配置仕様』 デバ イ ス/パ ッ ケージの組み合わせ と 最大 I/O 数、 ピ ン定義、 ピ ン配置表、 ピ ン配置図、 回路図、 熱仕様について明記 し てい ます。 • 『Virtex-6 FPGA コ ン フ ィ ギ ュ レーシ ョ ンガ イ ド 』 こ の包括的な コ ン フ ィ ギ ュ レーシ ョ ンガ イ ド は、 コ ン フ ィ ギ ュ レーシ ョ ンイ ン タ ーフ ェ イ ス (シ リ アル と SelectMAP)、 ビ ッ ト ス ト リ ームの暗号化、 バ ウ ン ダ リ ス キ ャ ンお よ び JTAG コ ン フ ィ ギ ュ レーシ ョ ン、 リ コ ン フ ィ ギ ュ レーシ ョ ンテ ク ニ ッ ク 、SelectMAP イ ン タ ーフ ェ イ スお よ び JTAG イ ン タ ーフ ェ イ ス での リ ー ド バ ッ ク の各章で構成 さ れてい ます。• 『Virtex-6 FPGA SelectIO リ ソ ースユーザーガ イ ド 』

Virtex-6 の各デバ イ ス で使用可能な SelectIO™ リ ソ ース について説明 し てい ます。 • 『Virtex-6 FPGA ク ロ ッ キ ン グ リ ソ ースユーザーガ イ ド 』

Virtex-6 の各デバ イ ス で使用可能な MMCM や PLL な ど の ク ロ ッ キ ン グ リ ソ ース について説 明 し てい ます。

• 『Virtex-6 FPGA コ ン フ ィ ギ ャ ブル ロ ジ ッ クブ ロ ッ ク ユーザーガ イ ド 』 すべての Virtex-6 デバ イ ス で使用可能な コ ン フ ィ ギ ャ ブルロ ジ ッ クブ ロ ッ ク (CLB) の機能に ついて説明 し てい ます。 • 『Virtex-6 FPGA GTH ト ラ ン シーバユーザーガ イ ド 』 FF1154 パ ッ ケージの XC6VHX250T と XC6VHX380T を除 く すべての Virtex-6 HXT FPGA で使用可能な GTH ト ラ ン シーバについて説明 し てい ます。 • 『Virtex-6 FPGA GTX ト ラ ン シーバユーザーガ イ ド 』 XC6VLX760 を除 く すべての Virtex-6 FPGA で使用可能な GTX ト ラ ン シーバについて説明 し てい ます。

• 『Virtex-6 FPGA エンベデ ッ ド ト ラ イ モー ド イ ーサネ ッ ト MAC ユーザーガ イ ド 』

XC6VLX760 を除 く すべての Virtex-6 で使用可能な専用 ト ラ イ モー ド イ ーサネ ッ トMAC (メ デ ィ アア ク セ ス コ ン ト ロ ー ラ) について説明 し てい ます。

• 『Virtex-6 FPGA DSP48E1 ス ラ イ スユーザーガ イ ド 』

Virtex-6 FPGAのDSP48E1 ス ラ イ ス の ア ー キ テ ク チ ャ につい て説明 し 、 コ ン フ ィ ギ ュ レ ー シ ョ ン例 も 記載 し てい ます。

• 『Virtex-6 FPGA シ ス テ ム モニ タユーザーガ イ ド 』

すべての Virtex-6 デバ イ ス で使用可能な System Monitor 機能の概要について説明 し てい ます。 • 『Virtex-6 FPGA PCB デザ イ ンガ イ ド 』 PCBお よ び イ ン タ ー フ ェ イ ス レ ベルでデザ イ ン を 決定す る た めの ス ト ラ テ ジ に焦点 を 置い て、Virtex-6 デバ イ ス の PCB デザ イ ンに関す る 情報を提供 し てい ます。

その他の リ ソ ース

シ リ コ ンお よ び ソ フ ト ウ ェ アに関す る ア ンサーデー タ ベース を検索 し た り 、テ ク ニ カルサポー ト の ウ ェ ブケース を開 く 場合は、 次の Web サ イ ト にア ク セ ス し て く だ さ い。 http://japan.xilinx.com/support第

1

章

ブ ロ ッ ク

RAM

リ ソ ース

概要

Virtex®-6 FPGA のブ ロ ッ ク RAM は 2 つの独立 し た 18Kb RAM ま たは 1 つの 36Kb RAM と し

て構成可能で、 いずれ も 最大 36Kbのデー タ を格納で き ます。36Kbの各ブ ロ ッ ク RAM は、SDP (Simple Dual-Port) モー ド では 64K x 1 (隣接す る 36Kbブ ロ ッ ク RAM と カ ス ケー ド 接続)、 32K x 1、16K x 2、8K x 4、4K x 9、2K x 18、1K x 36、512 x 72 と し て構成で き ます。18Kbの 各ブ ロ ッ ク RAM は、SDP モー ド では 16K x 1、8K x 2、4K x 4、2K x 9、1K x 18、512 x 36 と し て構成で き ます。

Virtex-5 FPGA のブ ロ ッ ク RAM と 同様に、書き込み と 読み出 し は ク ロ ッ ク に同期 し て行われます。 ま た、2 つのポー ト は対称でそれぞれ完全に独立 し てお り 、 保存 し たデー タ のみを共有 し ます。 各 ポー ト は、 設定可能な幅のいずれかに指定で き 、 も う 一方のポー ト か ら は独立 し てい ます。 さ ら に、 1 つのポー ト の読み出 し ポー ト と 書 き 込みポー ト には別々の幅を設定可能です。メ モ リ 内容は、コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ームで初期化ま たは ク リ アで き ます。書 き 込み実行中のデー タ 出 力は、 以前の出力を その ま ま維持す る か、 書 き 込まれてい る デー タ を出力す る か、 上書 き さ れ る 以 前のデー タ を出力す る か を設定で き ます。

Virtex-6 FPGA のブ ロ ッ ク RAM には、 次の よ う な拡張機能があ り ます。

• 同期セ ッ ト ピ ン と 同期 リ セ ッ ト ピ ン を分離す る こ と に よ り 、オプシ ョ ンの出力レ ジ ス タ のセ ッ ト/ リ セ ッ ト と ブ ロ ッ ク RAM の出力 ラ ッ チ段階を個別に制御で き ます。 こ れに よ り 、Virtex-6 の FPGA ブ ロ ッ ク RAM がその他の FPGA フ ァ ミ リ と さ ら に一致す る よ う にな り 、FPGA ロ ジ ッ ク レ ジ ス タ をブ ロ ッ ク RAM のブ ロ ッ ク にマ ッ プ し やす く な り ます。

• シ ンプルデ ュ アルポー ト (SDP) 幅の新 し い組み合わせが追加 さ れます。 • ECC モー ド でエ ラ ー挿入機能が追加 さ れます。

• SDP モー ド のデー タ と 共に読み出 し ア ド レ ス を リ ー ド バ ッ ク する機能がオプシ ョ ンでサポー ト さ れます。

Virtex-6 FPGA のブ ロ ッ ク RAM には次の特長があ り ます。

• ブ ロ ッ ク ご と の メ モ リ 格納機能に よ り 、 各ブ ロ ッ ク RAM に最大で 36Kb のデー タ を格納で き ます。 • 2 つの独立 し た 18K ブ ロ ッ ク ま たは 1 つの 36K ブ ロ ッ ク RAM をサポー ト し ます。 • 各 36K ブ ロ ッ ク RAM を シ ンプル デ ュ アルポー ト (SDP) モー ド に設定す る 場合、 最大 72 ビ ッ ト のデー タ 幅が可能で、18K ブ ロ ッ ク RAM を こ のモー ド に設定す る 場合は最大 36 ビ ッ ト ま でのデー タ 幅が可能です。 こ こ で、 シ ンプルデ ュ アルポー ト モー ド と は、 読み出 し 専用 ポー ト と 書 き 込み専用ポー ト が 1 つずつあ り 、 それぞれが独立 し た ク ロ ッ ク で動作 し てい る も の と 定義 し ます。 • SDP モー ド のブ ロ ッ ク RAM では、一方のデー タ ポー ト を固定幅 と し 、 も う 一方を可変幅にで き ます。

• 2 つの隣接 し たブ ロ ッ ク RAM を組み合わせ る こ と で、 外部 ロ ジ ッ ク を使用せずに 1 つの 64K x 1 メ モ リ を作成で き ます。

• 36Kbブ ロ ッ ク RAM ま たは 36Kb FIFO は 64 ビ ッ ト の ECC (Error Correction Coding) ブ ロ ッ ク を備えてい ます。 エン コ ー ド/デ コ ー ド 機能が別々に使用可能です。

• 初期値に対す る 、 出力の同期セ ッ ト/リ セ ッ ト は、 ブ ロ ッ ク RAM 出力の ラ ッ チお よ びレ ジ ス タ モー ド の両方で使用で き ます。

• ブ ロ ッ ク RAM を同期 FIFO と し て構成す る と 、 フ ラ グの レ イ テ ン シは安定 し ます。 • Virtex-6 FPGA の FIFO には FULL フ ラ グのアサー ト レ イ テ ン シがあ り ません。

• 18、36、72 ビ ッ ト 幅のポー ト には、バ イ ト ご と に個別の ラ イ ト イ ネーブルを含め る こ と がで き ます。 こ れは、 オンチ ッ プのマ イ ク ロ プ ロ セ ッ サ と イ ン タ ーフ ェ イ スす る 際に頻繁に使用 さ れ る 機能です。 • 各ブ ロ ッ ク RAM には、ビル ト イ ンデ ュ アル ク ロ ッ ク FIFO メ モ リ と し て動作す る ためのオプ シ ョ ンのア ド レ スシーケ ン ス処理お よ び制御回路が含まれてい ます。Virtex-6 アーキ テ ク チ ャ の場合、 ブ ロ ッ ク RAM は 18Kb ま たは 36Kb FIFO と し て構成で き ます。 • すべての入力はポー ト ク ロ ッ ク に同期 し て取 り 込ま れ、Setup-to-Clock タ イ ミ ン グ仕様に従い ます。 • すべての出力は、 書 き 込み イ ネーブル (WE) ピ ンの状態に よ っ て、 読み出 し ま たは書 き 込み中 に読み出 し にな り ます。 こ れ ら の出力は、Clock-to-Out タ イ ム後に有効にな り ます。 書 き 込み 中に読み出 し の出力には、WRITE_FIRST、READ_FIRST、NO_CHANGE と い う 3 つの動作 モー ド があ り ます。 • 書 き 込みには、 ク ロ ッ ク エ ッ ジが 1 つ必要です。 • 読み出 し には、 ク ロ ッ ク エ ッ ジが 1 つ必要です。 • すべての出力ポー ト には ラ ッ チが付いてい ます。 ま た、 別の読み出 し/書 き 込みを実行す る ま で は、 出力ポー ト の値は一定です。 デフ ォ ル ト では、 ブ ロ ッ ク RAM 出力は ラ ッ チモー ド です。 • 出力デー タ パス にはオプシ ョ ンの内部パ イ プ ラ イ ン レ ジ ス タ があ り ます。 レ ジ ス タ モー ド の 使用を強 く 推奨 し ます。こ れに よ り 、高 ク ロ ッ ク レー ト での動作が可能にな り ますが、1 ク ロ ッ ク サ イ ク ルの レ イ テ ン シが追加 さ れます。

Virtex-6 FPGA のブ ロ ッ ク RAM には次の使用規則があ り ます。

• ECC デ コ ーダの有効時 (EN_ECC_READ = TRUE)、同期セ ッ ト/リ セ ッ ト (RSTRAM) ポー ト は使用で き ません。

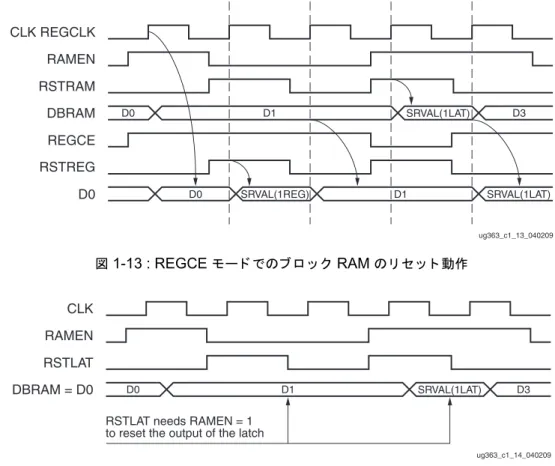

• ブ ロ ッ ク RAM の同期出力レ ジ ス タ (オプシ ョ ン) は、D0_REG = 1 の と き に RSTREG を使用 し てセ ッ ト ま たは リ セ ッ ト (SRVAL) さ れます。RSTREG と REGCE の ど ち ら が優先 さ れ る か は、RSTREG_PRIORITY 属性で指定 し ます。同期出力 ラ ッ チは D0_REG = 0 ま たは 1 の と き に RSTRAM を使用 し てセ ッ ト ま たは リ セ ッ ト (SRVAL) さ れます。 • ブ ロ ッ ク RAM のア ド レ ス ピ ンお よ び書 き 込み イ ネーブル ピ ンのセ ッ ト ア ッ プタ イ ムは違反 し ない よ う に し ます。 ア ド レ ス セ ッ ト ア ッ プ タ イ ムに違反す る と 、 書 き 込みネーブルが Low であ っ て も 、 ブ ロ ッ ク RAM のデー タ 内容が破損 し ます。 • ブ ロ ッ ク RAM の レ ジ ス タモー ド が RSTREG の場合、 出力 DO レ ジ ス タ 値を リ セ ッ ト す る に は、REGCE = 1 と す る 必要があ り ます。 こ のモー ド では、 ブ ロ ッ ク RAM ア レ イデー タ 出力 ラ ッ チは リ セ ッ ト さ れません。 ブ ロ ッ ク RAM の ラ ッ チ モー ド SRTRAM の場合、 出力 DO ラ ッ チ値を リ セ ッ ト す る にはブ ロ ッ ク RAM は イ ネーブル (EN = 1) にな っ てい る 必要があ り ます。

ブ ロ ッ ク RAM の説明

• ブ ロ ッ ク RAM プ リ ミ テ ィ ブには RAMB36E1 と RAMB18E1 の 2 つがあ り ます。 ブ ロ ッ ク RAM のモー ド は、RAMB_MODE 属性で SDP (Simple Dual-Port) モー ド ま たは TDP (True Dual-Port) モー ド のいずれかに設定 し ます。 • 特定のブ ロ ッ ク RAM プ リ ミ テ ィ ブ を使用す る と 、 読み出 し お よ び書 き 込みポー ト に異な る 幅 が選択可能です。 パ リ テ ィ ビ ッ ト はポー ト 幅が x9、x18、x36 の場合のみ利用で き ます。 読み 出 し 幅が x1、x2、x4 の と き は使用 し ないで く だ さ い。 読み出 し 幅が x1、x2、 ま たは x4 の場 合、 有効な書 き 込み幅は x1、x2、x4、x8、x16、x32 です。 同様に、 書 き 込み幅が x1、x2、 ま たは x4 の場合、 プ リ ミ テ ィ ブの属性は 1、2、4、9、18、 あ る いは 36 に設定 さ れますが、 実 際に使用可能な読み出 し 幅はそれぞれ x1、x2、x4、x8、x16、 ま たは x32 と な り ます。表 1-1 に、 ポー ト 幅の組み合わせを示 し ます。 • 非同期 リ セ ッ ト に よ っ て EN 信号が非同期にデ ィ アサー ト さ れ る と 、EN 信号のセ ッ ト ア ッ プ/ ホール ド タ イ ム違反 と な る こ と があ り ます。 こ の場合、 最初の読み出 し ま たは書 き 込みは正 し い結果 と な り ません。 リ セ ッ ト をデ ィ アサー ト し てか ら 最初の読み出 し ま たは書 き 込みの前に ク ロ ッ ク の 1 サ イ ク ル間、EN 信号を再度アサー ト す る 必要があ り ます。

ブ ロ ッ ク

RAM

の説明

Virtex-6 デバ イ ス には、分散 RAM メ モ リ お よ び高速 SelectIO™ メ モ リ イ ン タ ーフ ェ イ ス だけでな く 、 多数の 36Kbブ ロ ッ ク RAM が備わっ てい ます。 各 36Kbブ ロ ッ ク RAM には、 独立 し て制御 さ れ る 2 つの 18Kb RAM があ り ます。 ブ ロ ッ ク RAM は列に配置 さ れ、 ブ ロ ッ ク RAM メ モ リ の 総数は Virtex-6 デバ イ ス のサ イ ズに よ っ て決ま り ます。36Kbブ ロ ッ ク を カ ス ケー ド 接続す る と 、タ

イ ミ ン グ遅延を最小限に抑えて、 ビ ッ ト 数 と ワー ド 数の多い メ モ リ を イ ンプ リ メ ン ト で き ます。 デ ュ アルポー ト ま たはシ ン グルポー ト のエンベデ ッ ド RAM モジ ュ ール、ROM モジ ュ ール、 同期 FIFO、 デー タ 幅 コ ンバー タ は、ザ イ リ ン ク ス CORE Generator™ のブ ロ ッ ク メ モ リ モジ ュ ールを 使用す る と 容易に イ ンプ リ メ ン ト で き ます。デ ュ アルク ロ ッ ク FIFO は、CORE Generator の FIFO Generator モジ ュ ールを使用 し て作成で き ます。 同期ま たは非同期 (デ ュ アル ク ロ ッ ク) FIFO の イ ンプ リ メ ン テーシ ョ ンには、専用のハー ド ウ ェ ア リ ソ ース が使用 さ れ る ため、FIFO 制御 ロ ジ ッ ク に 追加の CLB リ ソ ース を使用す る 必要はあ り ません。 表 1-1 : パ リ テ ィ ビ ッ ト の使用法 プ リ ミ テ ィ ブ 設定 有効な読み出 し 幅 有効な書き込み幅 読み出 し 幅 書き込み幅 RAMB18E1 1、2、4 9、18 設定幅 と 同一 8、16 RAMB18E1 9、18 1、2、4 8、16 設定幅 と 同一 RAMB18E1 1、2、4 1、2、4 設定幅 と 同一 設定幅 と 同一 RAMB18E1 9、18 9、18 設定幅 と 同一 設定幅 と 同一 RAMB36E1 1、2、4 9、18、36 設定幅 と 同一 8、16、32 RAMB36E1 9、18、36 1、2、4 8、16、32 設定幅 と 同一 RAMB36E1 1、2、4 1、2、4 設定幅 と 同一 設定幅 と 同一 RAMB36E1 9、18、36 9、18、36 設定幅 と 同一 設定幅 と 同一 メ モ : 1. 一方のポー ト 幅が 9 よ り 小 さ く 、 も う 一方が 9 以上の場合、 パ リ テ ィ ビ ッ ト DIP/DOP は使用 し ないで く だ さ い。

同期デ ュ アル

ポー ト およびシ ン グル

ポー ト

RAM

デー タ

フ ロー

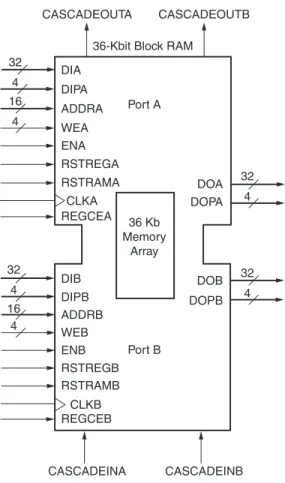

36Kbの完全デ ュ アルポー ト ブ ロ ッ ク RAM は、36Kbの記憶領域 と 完全に独立 し た 2 つのア ク セ ス ポー ト (A お よ び B) で構成 さ れてい ます。 同様に、 各 18Kbブ ロ ッ ク RAM のデ ュ アルポー ト メ モ リ は、18Kbの記憶領域 と 完全に独立 し た 2 つのア ク セ ス ポー ト (A お よ び B) で構成 さ れてい ます。 構造は完全に対称で、 両ポー ト は交換可能です。図 1-1に RAMB36 の完全デ ュ アルポー ト のデー タ フ ロ ーを示 し 、表 1-2にポー ト の機能 と その説明を示 し ます。 デー タ の書 き 込み/読み出 し は、 ど ち ら か 1 つのポー ト ま たは両方のポー ト で実行で き ます。 書 き 込 みは、 それぞれ ク ロ ッ ク に同期 し て行われ、 各ポー ト には、 ア ド レ ス、 デー タ 入力、 デー タ 出力、 ク ロ ッ ク 、 ク ロ ッ ク イ ネーブル、 書 き 込み イ ネーブルが含まれます。 読み出 し お よ び書 き 込みは同期 で実行 さ れます。 そのため、1 つの ク ロ ッ ク エ ッ ジが必要です。 両方のポー ト で同 じ ア ド レ ス にア ク セ ス し た際に、その調整を行 う 専用モニ タ はあ り ません。2 つの ク ロ ッ ク の タ イ ミ ン グは、 ユーザーの責任で調整 し て く だ さ い。 同 じ ア ド レ ス に同時に書 き 込みを 実行 し た場合、 物理的な破損はあ り ませんが、 書 き 込まれたデー タ は不確定にな り ます。X-Ref Target - Figure 1-1

図 1-1 : RAMB36 の完全デ ュ アルポー ト デー タ フ ロー DOPA DIPA ADDRA WEA ENA CASCADEOUTB RSTRAMA CLKA RSTREGA REGCEA REGCEB DIPB ADDRB WEB ENB RSTRAMB RSTREGB CLKB

36-Kbit Block RAM

ug363_c1_01_011509 DOPB DOB DOA DIA DIB 36 Kb Memory Array Port A 32 4 32 4 16 4 32 4 16 4 32 4 Port B CASCADEOUTA CASCADEINB CASCADEINA

同期デ ュ アルポー ト お よびシ ングルポー ト RAM

読み出 し

ラ ッ チモー ド の読み出 し は、 ク ロ ッ ク エ ッ ジに同期 し て行われます。読み出 し ア ド レ ス が読み出 し ポー ト に取 り 込まれてか ら 、RAM ア ク セ ス時間の後に、格納 さ れたデー タ が出力 ラ ッ チに読み込ま れます。 オプシ ョ ンの出力レ ジ ス タ を使用 し た場合は、 読み出 し の レ イ テ ン シが 1 ク ロ ッ クサ イ ク ル増加 し ます。書き込み

書 き 込みは、 ク ロ ッ ク エ ッ ジに同期 し て行われます。 書 き 込みア ド レ スは書 き 込みポー ト に取 り 込 まれ、 入力デー タ が メ モ リ に格納 さ れます。書き込みモー ド

書 き 込み ク ロ ッ ク エ ッ ジ後の出力 ラ ッ チのデー タ は、3 つの書 き 込みモー ド (WRITE_FIRST、 READ_FIRST、NO_CHANGE) のいずれを設定す る かで決定 さ れます。 こ のモー ド は、 コ ン フ ィ ギ ュ レーシ ョ ンで設定 し ます。 各ポー ト に対 し て別々の書 き 込みモー ド を設定で き 、 デフ ォ ル ト は WRITE_FIRST です。WRITE_FIRST では新た なデー タ が書 き 込まれ る と 同時に、その新規デー タ が出力バス に送信 さ れ、READ_FIRST ではあ ら か じ め保存 さ れてい る デー タ が出力 さ れます。 NO_CHANGE では、 前回の読み出 し 処理の出力がその ま ま送信 さ れます。 表 1-2 : 完全デ ュ アルポー ト の名前 と 説明 ポー ト 名 内容 DI[A|B] デー タ 入力バ ス DIP[A|B] (1) デー タ 入力パ リ テ ィ バ ス で、 追加デー タ 入力に使用可能 ADDR[A|B] ア ド レ スバ ス WE[A|B] バ イ ト ラ イ ト イ ネーブル EN[A|B] 非ア ク テ ィ ブの場合、ブ ロ ッ ク RAM にデー タ は書 き 込まれず、 出力バ ス が以前の状態に保持 さ れ るRSTREG[A|B] 出力レ ジ ス タ を同期セ ッ ト/リ セ ッ ト (D0_REG = 1)。REGCE よ り も 優先す る か ど う かは、RSTREG_PRIORITY 属性で設定 RSTRAM[A|B] 出力デー タ ラ ッ チの同期セ ッ ト/リ セ ッ ト CLK[A|B] ク ロ ッ ク 入力 DO[A|B] デー タ 出力バ ス DOP[A|B] (1) デー タ 出力パ リ テ ィ バ ス で、 追加デー タ 出力に使用可能 REGCE[A|B] 出力レ ジ ス タ ク ロ ッ ク イ ネーブル CASCADEIN[A|B] 64K x 1 モー ド のカ ス ケー ド 入力 CASCADEOUT[A|B] 64K x 1 モー ド のカ ス ケー ド 出力 メ モ :

1. デー タパ リ テ ィ ピ ンの詳細は、「デー タ 入力バ ス - DIADI、DIPADIP、DIBDI、DIPBDIP」 を参照 し て く だ さ い。

ISE Design Suite 12.2 以降を使用 し た場合、SDP モー ド のブ ロ ッ ク RAM は WRITE_FIRST モー ド も サポー ト し ます。12.2 よ り も 前の ISE では、SDP ブ ロ ッ ク RAM は必ず READ_FIRST モー ド と な り 、「競合の回避」セ ク シ ョ ンで詳述する ア ド レ ス競合に関する制約が常に適用 さ れます。

WRITE_FIRST

または透過モー ド

(

デ フ ォル ト

)

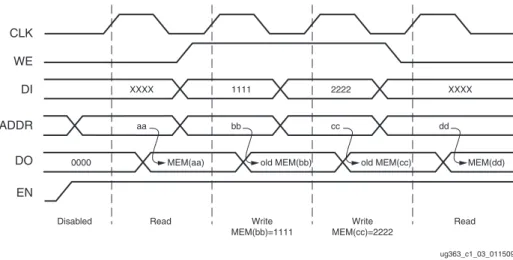

図 1-2に示す よ う に、WRITE_FIRST モー ド では入力デー タ を メ モ リ に書 き 込む と 同時にデー タ 出 力に も 格納 さ れます (透過書 き 込み)。 こ こ に示す波形は、 オプシ ョ ンの出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ない ラ ッ チモー ド の場合です。ISE Design Suite 12.2 以降を使用す る 場合、SDP ブ ロ ッ ク RAM は WRITE_FIRST モー ド も サポー ト し ます。

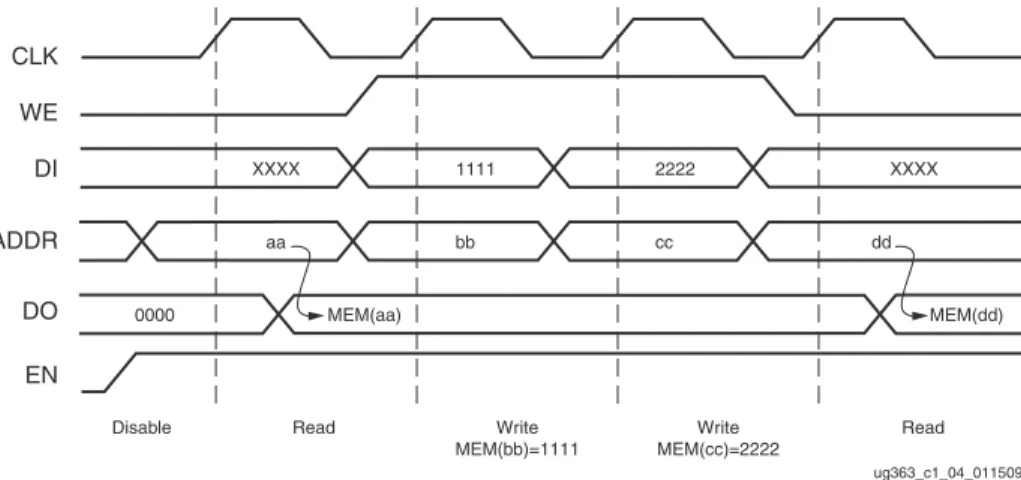

READ_FIRST

または書き込み前読み出 し モー ド

SDP モー ド のブ ロ ッ ク RAM は READ_FIRST ま たは WRITE_FIRST モー ド のいずれか と な り ま す。READ_FIRST モー ド では、書 き 込み先ア ド レ ス に格納 さ れていたデー タ が出力 ラ ッ チに送信 さ れ、それ と 同時に入力デー タ が メ モ リ に格納 さ れます (書 き 込み前に読み込み)。図 1-3の波形は、オ プシ ョ ンの出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ない ラ ッ チモー ド の場合を示 し てい ます。

X-Ref Target - Figure 1-2

図 1-2 : WRITE_FIRST モー ド での波形 CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 XXXX aa bb cc dd 0000 MEM(aa) 1111 2222 MEM(dd) Read Write MEM(bb)=1111 Write MEM(cc)=2222 ug363_c1_02_033009

X-Ref Target - Figure 1-3

図 1-3 : READ_FIRST モー ド での波形 CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 XXXX aa bb cc dd

0000 MEM(aa) old MEM(bb) old MEM(cc) MEM(dd)

Read Write MEM(bb)=1111 Write MEM(cc)=2222 ug363_c1_03_011509

同期デ ュ アルポー ト お よびシ ングルポー ト RAM

NO_CHANGE

モー ド

NO_CHANGE モー ド では、 書 き 込み中、 出力 ラ ッ チは変化 し ません。図 1-4に示す よ う に、 デー タ 出力には最後に読み込まれたデー タ がその ま ま維持 さ れ、 同 じ ポー ト での書 き 込みに影響 さ れま せん。 こ こ に示す波形は、オプシ ョ ンの出力パ イ プ ラ イ ンレ ジ ス タ を使用 し ない ラ ッ チモー ド の場 合です。競合の回避

Virtex-6 FPGA のブ ロ ッ ク RAM メ モ リ は、 両方のポー ト が任意の メ モ リ 位置に随時ア ク セ ス で き る 完全デ ュ アルポー ト RAM です。 ただ し 、2 つのポー ト か ら 同 じ メ モ リ 位置へア ク セ スす る 際に は、 制限があ り ます。 こ の よ う な ア ク セ ス には、 両ポー ト で共通の ク ロ ッ ク を使用 し てい る 場合 (同 期 ク ロ ッ ク) と 、 両ポー ト の ク ロ ッ ク 周波数ま たは位相が異な る 場合 (非同期 ク ロ ッ ク) と い う 2 つ の場合があ り ます。

非同期ク ロ ッ ク

一般的には、 ク ロ ッ ク は非同期であ る こ と が多 く 、 両 ク ロ ッ ク のア ク テ ィ ブエ ッ ジが同時に発生す る こ と はあ り ません。 • 両ポー ト で読み出 し を実行す る 場合、 タ イ ミ ン グに制約はあ り ません。 • 1 つのポー ト で書 き 込みを実行 し てい る 間は、 も う 1 つのポー ト か ら 同 じ メ モ リ 位置に対 し て 読み出 し ま たは書 き 込みは実行で き ません。 こ れは、 すべてのア ド レ ス ビ ッ ト が同一であ る た めです。 こ れに違反す る と 、 シ ミ ュ レーシ ョ ンモデルでエ ラ ーが発生 し ます。 こ の制約を無視 す る と 、 出力読み出 し デー タ は不明 (予測不可) と な り ます。 ただ し 、 デバ イ ス が物理的に破損 す る こ と はあ り ません。 読み出 し と 書 き 込みを実行す る と 、 書 き 込み位置に有効なデー タ が格 納 さ れます。• TDP/SDP/ECC モー ド のブ ロ ッ ク RAM を READ_FIRST モー ド で使用す る 場合、 ブ ロ ッ ク RAM のポー ト A と B のア ド レ ス (RAMB18E1 の場合はビ ッ ト A13 - A7、RAMB36E1 の場 合はビ ッ ト A14 - A8) が競合 し ない よ う にす る 必要があ り ます。 こ の制限は、TDP お よ び SDP モー ド の両方に適用 さ れます。1 つのポー ト での読み出 し/書 き 込み と 、 も う 1 つのポー ト での 同 じ ア ド レ スへの書 き 込みを同時に実行す る こ と はで き ません。こ の制約を無視す る と 、ブ ロ ッ ク RAM の動作が保証 さ れず、 メ モ リ セルが破損す る 恐れがあ り ます。 同時ア ク セ ス を避け る には、 イ ネーブルピ ン (EN) を使用 し ます。

X-Ref Target - Figure 1-4

図 1-4 : NO_CHANGE モー ド での波形 CLK WE DI ADDR DO EN Disable Read XXXX 1111 2222 XXXX aa bb cc dd 0000 MEM(aa) MEM(dd) Read Write MEM(bb)=1111 Write MEM(cc)=2222 ug363_c1_04_011509

同期ク ロ ッ ク

同期 ク ロ ッ ク は、両ポー ト の ク ロ ッ ク のア ク テ ィ ブエ ッ ジが同時に発生する と い う 特殊な状況です。 • 両ポー ト で読み出 し を実行す る 場合、 タ イ ミ ン グに制約はあ り ません。 • 1 つのポー ト で書 き 込みを実行中に、 も う 1 つのポー ト を使用 し て同 じ メ モ リ 位置に書 き 込み はで き ません。 ただ し 、 両ポー ト で書 き 込むデー タ が同一の場合は例外です。 • 1 つのポー ト で書 き 込みを実行中、書 き 込みポー ト が READ_FIRST モー ド であれば、も う 1 つ のポー ト で同 じ メ モ リ 位置か ら デー タ を正 し く 読み出す こ と がで き ます。 その場合、 両ポー ト の DATA_OUT は書 き 込み前に格納 さ れていたデー タ にな り ます。 書 き 込みポー ト が WRITE_FIRST ま たは NO_CHANGE モー ド の場合は、 読み出 し ポー ト の DATA_OUT が無効 (不確定) にな り ます。 読み出 し ポー ト のモー ド 設定は、 こ の動作には影響 を与え ません。Virtex-6

デバイ スのブ ロ ッ ク

RAM

のその他の機能

出力レ ジ ス タ

(

オプ シ ョ ン

)

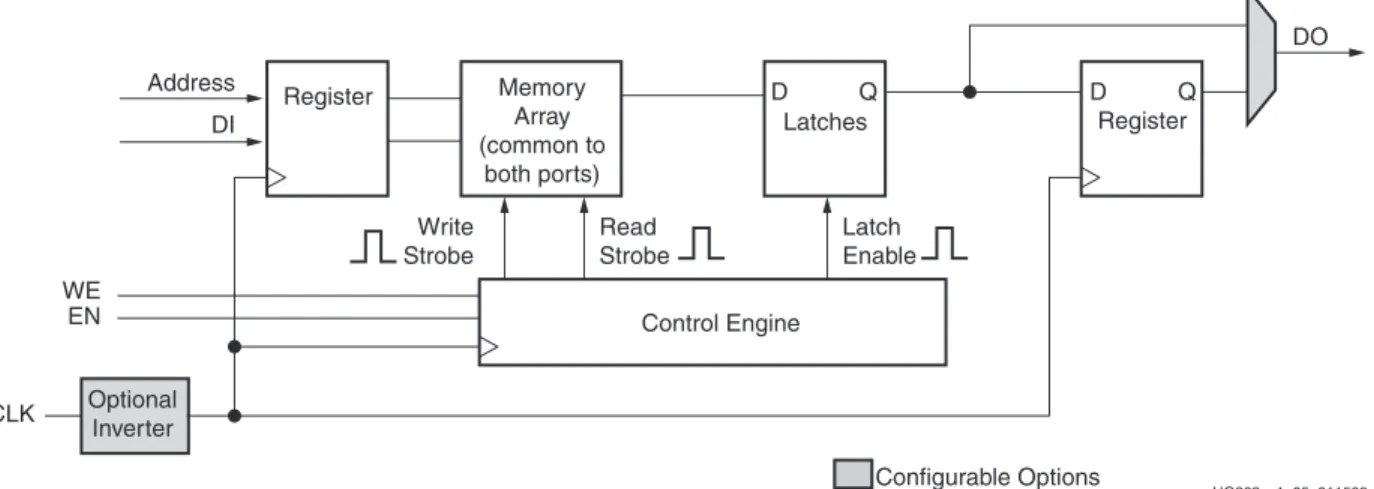

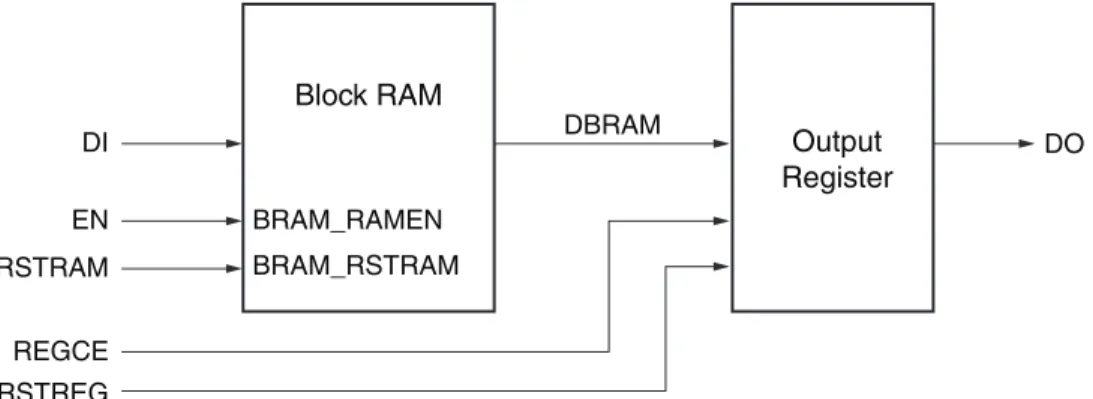

オプシ ョ ンの出力レ ジ ス タ を使用す る と 、 パ イ プ ラ イ ン処理におけ る CLB フ リ ッ プ フ ロ ッ プへの 配線遅延が削減 さ れ、 デザ イ ンのパフ ォーマ ン ス が向上 し ます。 こ れ ら の出力レ ジ ス タ には、 独立 し た ク ロ ッ ク お よ び ク ロ ッ ク イ ネーブルの入力が供給 さ れ る ため入力レ ジ ス タ の動作か ら 独立 し た値が保持で き ます。図 1-5にオプシ ョ ンの出力レ ジ ス タ を示 し ます。個別に選択可能な読み出 し ポー ト と 書き込みポー ト の幅

各ブ ロ ッ ク RAM ポー ト では、 デー タ 幅 と ア ド レ ス幅 (ア スペ ク ト 比) を制御で き ます。Virtex-6 FPGA の TDP モー ド のブ ロ ッ ク RAM では こ の機能が拡張 さ れ、各ポー ト での読み出 し お よ び書 き 込みに異な る デー タ 幅を設定で き る よ う にな っ てい ます。 た と えば、 ポー ト A が 36 ビ ッ ト の読み 出 し 幅 と 9 ビ ッ ト の書 き 込み幅を持ち、ポー ト B が 18 ビ ッ ト の読み出 し 幅 と 36 ビ ッ ト の書 き 込み 幅を持つ よ う 設定可能です。 詳細は、31 ページの 「ブ ロ ッ ク RAM の属性」 を参照 し て く だ さ い。 読み出 し ポー ト と 書き込みポー ト の幅が異な っ ていて、WRITE_FIRST モー ド が設定 さ れてい る場 合、 有効なすべての書き込みバ イ ト に対 し て、DO には有効な新規デー タ が現れます。 有効 と な っ て いないすべてのバ イ ト に対 し ては、 メ モ リ に保存 さ れた以前のデー タ が DO ポー ト に出力 さ れます。 X-Ref Target - Figure 1-5図 1-5 : ブ ロ ッ ク RAM の論理図 (1 ポー ト のみ表示) Register Optional Inverter Latches Register Address DI WE EN CLK Write Strobe Read Strobe Q D D Q DO Control Engine Configurable Options UG363_c1_05_011509 Memory Array (common to both ports) Latch Enable

Virtex-6 デバイ スのブ ロ ッ ク RAM のその他の機能

読み出 し ポー ト と 書 き 込みポー ト の幅を個別に設定で き る こ と に よ り 、 ブ ロ ッ ク RAM に CAM (Content Addressable Memory) を効率的に イ ンプ リ メ ン ト で き ます。 こ のオプシ ョ ンは、Virtex-6 FPGA のブ ロ ッ ク RAM を TDP モー ド と し た場合、すべてのポー ト サ イ ズ と モー ド で使用可能です。

シ ン プル

デ ュ アル

ポー ト

ブ ロ ッ ク

RAM

18Kbブ ロ ッ ク お よび 36Kbブ ロ ッ ク はそれぞれ、シ ンプルデュ アルポー ト RAM モー ド と し て も 構 成で き ます。 こ のモー ド では、 ブ ロ ッ ク RAM のポー ト 幅が 2 倍にな り 、18Kbブ ロ ッ ク RAM では 36ビ ッ ト 、36Kbブ ロ ッ ク RAM では 72ビ ッ ト と な り ます。 シ ンプルデュ アルポー ト モー ド のブ ロ ッ ク RAM は、 ポー ト A を読み出 し ポー ト 、 ポー ト B を書き込みポー ト と し 、 読み出 し と 書き込 みを同時に独立 し て実行で き ます。 読み出 し ポー ト と 書 き 込みポー ト が同 じ デー タ 位置に同時にア ク セ スする と 、 完全デュ アルポー ト モー ド のポー ト 競合 と 同様に競合が発生 し ます。 シ ンプルデュ アルポー ト モー ド のブ ロ ッ ク RAM では、コ ン フ ィ ギ ュ レーシ ョ ンポー ト か ら の リ ー ド バ ッ ク がサ ポー ト さ れてい ます。図 1-6に、 シ ンプルデュ アルポー ト RAMB18SDP およ び RAMB36SDP の デー タ フ ローを示 し ます。X-Ref Target - Figure 1-6

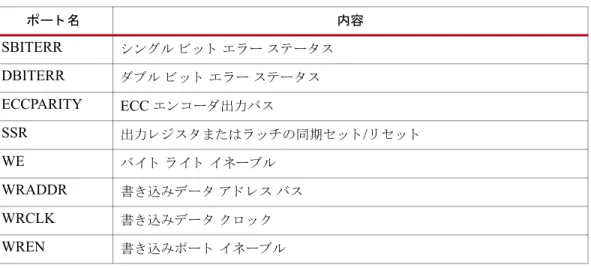

図 1-6 : シ ン プルデ ュ アルポー ト RAMB18SDP および RAMB36SDP のデー タ フ ロー 表 1-3 : シ ン プルデ ュ アルポー ト の名前 と 説明 ポー ト 名 内容 DO デー タ 出力バ ス DOP デー タ 出力パ リ テ ィ バ ス DI デー タ 入力バ ス DIP デー タ 入力パ リ テ ィ バ ス RDADDR 読み出 し デー タ ア ド レ スバス RDCLK 読み出 し デー タ ク ロ ッ ク RDEN 読み出 し ポー ト イ ネーブル REGCE 出力レ ジ ス タ ク ロ ッ ク イ ネーブル

36 Kb Memory Array

DO RDEN RDADDR RDCLK REGCE DIP WRADDR WE WRCLK WREN DBITERR DI ug363_c1_06_092509 64 8 8 15 15 SBITERR 64 ECCPARITY DOP 8 8 SSRカ スケー ド 接続可能な ブ ロ ッ ク

RAM

Virtex-6 のブ ロ ッ ク RAM アーキ テ ク チ ャ では、2 つの 32K x 1 RAM を組み合わせて 1 つの 64K x 1 RAM を作成で き ます。 こ の際に、 ロ ーカルイ ン タ ー コ ネ ク ト や追加の CLB ロ ジ ッ ク の使 用は不要です。隣接す る 2 つのブ ロ ッ ク RAM を カ ス ケー ド 接続す る と 、64K x 1 ブ ロ ッ ク RAM を 作成で き ます。 ただ し 、 ブ ロ ッ ク RAM を 2 つカ ス ケー ド 接続 し て、 ブ ロ ッ ク RAM の ワー ド 数を 増やす こ と がで き る のは、64K x 1 モー ド のみです。カ ス ケー ド 接続可能なブ ロ ッ ク RAM について は、「RAMB18E1 お よ び RAMB36E1 プ リ ミ テ ィ ブの設計上のその他の注意事項」で詳 し く 説明 し てい ます。 こ れ以外の方法に よ る ビ ッ ト 数 と ワ ー ド 数の拡張については、「大規模な RAM 構造の作 成」を参照 し て く だ さ い。図 1-7に、 カ ス ケー ド モー ド でポー ト を接続 し たブ ロ ッ ク RAM を示 し ます。 SBITERR シ ン グルビ ッ ト エ ラ ース テー タ ス DBITERR ダブルビ ッ ト エ ラ ース テー タ ス ECCPARITY ECC エン コ ーダ出力バ ス SSR 出力レ ジ ス タ ま たは ラ ッ チの同期セ ッ ト/リ セ ッ ト WE バ イ ト ラ イ ト イ ネーブル WRADDR 書 き 込みデー タ ア ド レ スバス WRCLK 書 き 込みデー タ ク ロ ッ ク WREN 書 き 込みポー ト イ ネーブル メ モ : 1. ブ ロ ッ ク RAM プ リ ミ テ ィ ブのポー ト 名 と ポー ト 機能名は異な る こ と があ り ます。 表 1-3 : シ ン プルデ ュ アルポー ト の名前 と 説明 (続き) ポー ト 名 内容

X-Ref Target - Figure 1-7

図 1-7 : カ スケー ド 接続可能な ブ ロ ッ ク RAM

D0 Not Used

DI DI

CASCADEIN Connect to logic High or Low

CASCADEOUT (No Connect) A[14:0] WE D0 A15 A15 A[14:0] D0 DI DI A[14:0] WE D0 D Q D Q D Q D Q D Q D Q D Q D Q A15 A15 A[14:0] WE[3:0] WE[3:0]

Interconnect Block RAM RAM_EXTENSION = UPPER(0) RAM_EXTENSION = LOWER(1) 0 1 0 1 0 1 0 1 ug363_c1_07_011509 CASCADEIN of Top CASCADEOUT of Bottom Optional Output FF Optional Output FF

Virtex-6 デバイ スのブ ロ ッ ク RAM のその他の機能

バイ ト

ラ イ ト

イ ネーブル

ブ ロ ッ ク RAM にはバ イ ト ラ イ ト イ ネーブル機能があ り 、8 ビ ッ ト (1 バ イ ト) 単位で入力デー タ を 書 き 込む こ と がで き ます。TDP モー ド の RAMB36E1 には、4 つの独立 し たバ イ ト ラ イ ト イ ネーブ ル入力があ り ます。 ま た、SDP モー ド (RAMB36SDP) では、8 つの独立 し たバ イ ト ラ イ ト イ ネー ブル入力があ り ます。表 1-4に、36K お よ び 18K ブ ロ ッ ク RAM で利用で き る バ イ ト ラ イ ト イ ネー ブルの数を示 し ます。各バ イ ト ラ イ ト イ ネーブルは、1 バ イ ト の入力デー タ と 1 パ リ テ ィ ビ ッ ト に 対応 し てい ます。すべてのデー タ 幅の コ ン フ ィ ギ ュ レーシ ョ ンで、すべてのバ イ ト ラ イ ト イ ネーブ ル入力を駆動す る 必要があ り ます。 こ の機能は、 ブ ロ ッ ク RAM を使用 し てマ イ ク ロ プ ロ セ ッ サ と 通信す る 場合に有用です。 バ イ ト ラ イ ト イ ネーブル機能は、 デ ュ アルク ロ ッ ク FIFO や ECC モー ド では使用で き ません。 バ イ ト ラ イ ト イ ネーブルの詳細は、「RAMB18E1 お よ び RAMB36E1 プ リ ミ テ ィ ブの設計上のその他の注意事項」を参照 し て く だ さ い。図 1-8に、RAMB36E1 のバ イ ト ラ イ ト イ ネーブルの タ イ ミ ン グ図を示 し ます。 RAMB36E1 で 36 ビ ッ ト 幅ま たは 18 ビ ッ ト 幅のデー タパ ス を設定す る と 、デー タ ワー ド 内で指定 し たバ イ ト 位置への書 き 込みを任意のポー ト で制御で き ます。READ_FIRST モー ド の場合、DO バ ス にはア ド レ ス指定 し た ワー ド 全体が書 き 込み前の内容で現れます。WRITE_FIRST の場合は、DO には新たに書 き 込まれた有効なバ イ ト と 未書 き 込みバ イ ト の メ モ リ の初期内容の組み合わせが出力 さ れます。ブ ロ ッ ク

RAM

の

ECC (

エ ラ ー訂正 コ ー ド

)

36Kbブ ロ ッ ク RAM でのブ ロ ッ ク RAM お よ び FIFO イ ンプ リ メ ン テーシ ョ ンでは、64 ビ ッ ト の ECC (エ ラ ー訂正 コ ー ド) を備え る こ と がで き ます。 こ の機能を使用す る と 、 ブ ロ ッ ク RAM の読み 出 し デー タ のシ ン グルビ ッ ト お よ びダブルビ ッ ト エ ラ ーが検知で き ます。シ ン グルビ ッ ト エ ラ ー は出力デー タ で修正 さ れます。 表 1-4 : 使用可能なバイ ト ラ イ ト イ ネーブル プ リ ミ テ ィ ブ 最大ビ ッ ト 幅 バイ ト ラ イ ト イ ネーブル数 RAMB36E1 TDP モー ド 36 4 RAMB36E1 SDP モー ド 72 8 RAMB18E1 TDP モー ド 18 2 RAMB18E1 SDP モー ド 36 4

X-Ref Target - Figure 1-8

図 1-8 : バイ ト ラ イ ト 動作の波形 (x36 WRITE_FIRST) CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 1111 0011 XXXX aa bb bb cc 0000 MEM(aa) 1111 1122 MEM(cc) Read Write MEM(bb)=1111 Byte Write MEM(bb)=1122 ug363_c1_08_011509

ブ ロ ッ ク

RAM

のラ イ ブ ラ リ

プ リ ミ テ ィ ブ

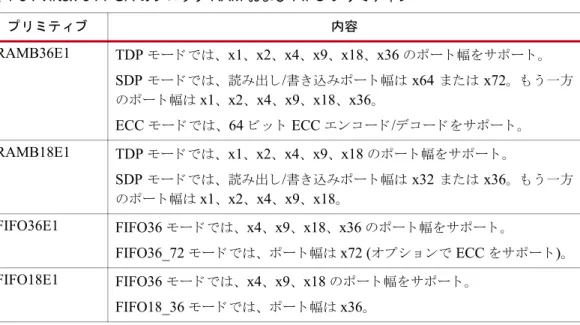

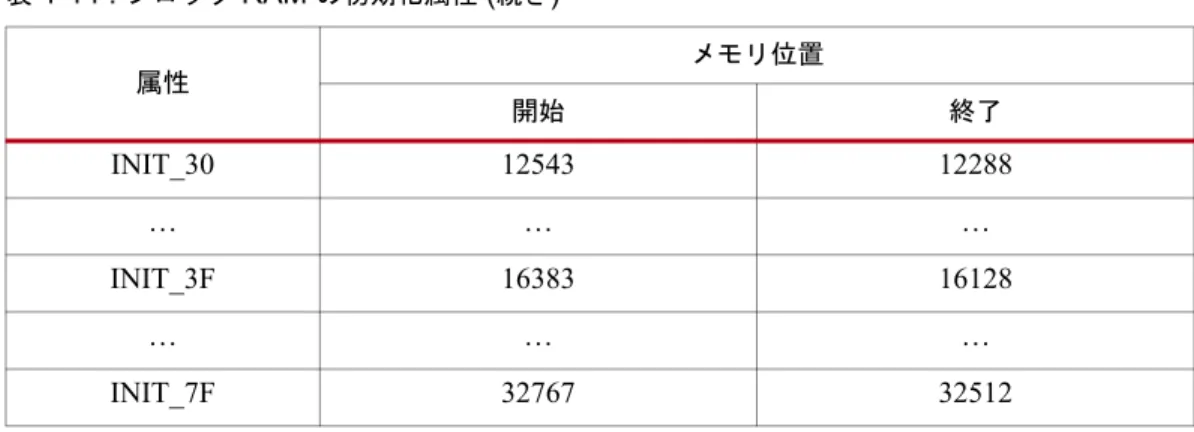

Virtex-6 FPGA のブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ、RAMB18E1 お よび RAMB36E1 はす べてのブ ロ ッ ク RAM コ ン フ ィ ギ ュ レーシ ョ ンの基本構築ブ ロ ッ ク です。その他のブ ロ ッ ク RAM の プ リ ミ テ ィ ブお よ びマ ク ロ は、 こ のプ リ ミ テ ィ ブ を基に し てい ます。 ブ ロ ッ ク RAM の属性に よ っ ては、1 つのプ リ ミ テ ィ ブでのみ設定で き ます (パ イ プ ラ イ ン レ ジ ス タ 、 カ ス ケー ド な ど)。 詳細は、 「ブ ロ ッ ク RAM の属性」 を参照 し て く だ さ い。 9 ビ ッ ト 幅 (8 + 1)、18 ビ ッ ト 幅 (16 + 2)、36 ビ ッ ト 幅 (32 + 4) の コ ン フ ィ ギ ュ レーシ ョ ンでは、入 力お よ び出力デー タバ ス は 2 つのバ ス で表 さ れます。各バ イ ト に関連付け ら れてい る 9 番目のビ ッ ト にはパ リ テ ィ ビ ッ ト (エ ラ ー訂正ビ ッ ト) を保存す る か、 追加のデー タ ビ ッ ト と し て使用で き ま す。 こ の 9 番目のビ ッ ト には、 特定の機能はあ り ません。 パ リ テ ィ ビ ッ ト 用に別のバ ス を使用 し た 方が良いデザ イ ン も あ り ますが、 たいていの場合は、通常のデー タバス と パ リ テ ィ バ ス を一緒に し て、9 ビ ッ ト 、18 ビ ッ ト 、 ま たは 36 ビ ッ ト のバス を使用 し て も 問題あ り ません。 読み込み/書 き 込 みお よ び保存は、 パ リ テ ィ ビ ッ ト も 含めてすべてのビ ッ ト で同 じ よ う に行われます。

図 1-9に、TDP モー ド の 36Kbブ ロ ッ ク RAM プ リ ミ テ ィ ブ (RAMB36) の I/O ポー ト を示 し ます。

表 1-5に、 プ リ ミ テ ィ ブの一覧を示 し ます。 X-Ref Target - Figure 1-9

図 1-9 : ブ ロ ッ ク RAM ポー ト 信号 (RAMB36E1) DOPADOP DOPBDOP DIADI DIPADIP ADDRARDADDR WEA ENARDEN RSTREGARSTREG CLKARDCLK DOADO DOBDO RSTRAMARSTRAM REGCEAREGCE DIBDI DIPBDIP ADDRBWRADDR WEBWE ENBWREN RSTREGB RSTRAMB REGCEB CLKBWRCLK ug363_c1_09_071409 32 4 16 4 32 4 32 4 32 4 16 8 CASCADEOUTA CASCADEOUTB CASCADEINA CASCADEINB

ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ

表 1-6 と表 1-7に、表 1-5で示 し たプ リ ミ テ ィ ブの各ポー ト の名称 と 説明を示 し ます。ECC ポー ト については、第 3 章 「ビル ト イ ンエ ラ ー訂正」 で説明 し ます。

表 1-5 : Virtex-6 FPGA のブ ロ ッ ク RAM お よび FIFO プ リ ミ テ ィ ブ

プ リ ミ テ ィ ブ 内容 RAMB36E1 TDP モー ド では、x1、x2、x4、x9、x18、x36 のポー ト 幅をサポー ト 。 SDP モー ド では、 読み出 し/書 き 込みポー ト 幅は x64 ま たは x72。 も う 一方 のポー ト 幅は x1、x2、x4、x9、x18、x36。 ECC モー ド では、64 ビ ッ ト ECC エン コ ー ド/デコ ー ド をサポー ト 。 RAMB18E1 TDP モー ド では、x1、x2、x4、x9、x18 のポー ト 幅をサポー ト 。 SDP モー ド では、 読み出 し/書 き 込みポー ト 幅は x32 ま たは x36。 も う 一方 のポー ト 幅は x1、x2、x4、x9、x18。 FIFO36E1 FIFO36 モー ド では、x4、x9、x18、x36 のポー ト 幅をサポー ト 。 FIFO36_72 モー ド では、 ポー ト 幅は x72 (オプシ ョ ンで ECC をサポー ト)。 FIFO18E1 FIFO36 モー ド では、x4、x9、x18 のポー ト 幅をサポー ト 。 FIFO18_36 モー ド では、 ポー ト 幅は x36。 表 1-6 : RAMB36E1 のポー ト 名 と 説明 ポー ト 名 内容 DIADI[31:0] ポー ト A デー タ 入力。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名 マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DIPADIP[3:0] ポー ト A デー タ パ リ テ ィ 入力。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド で のポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DIBDI[31:0] ポー ト B デー タ 入力。ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名 マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DIPBDIP[3:0] ポー ト A デー タパ リ テ ィ 入力。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド で のポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。

ADDRARDADDR[15:0] ポー ト A ア ド レ ス入力バス。RAM_MODE = SDP の場合、RDADDR バ ス と な り ます。 ADDRBWRADDR[15:0] ポー ト B ア ド レ ス入力バス。RAM_MODE = SDP の場合、WRADDR バ ス と な り ます。 WEA[3:0] ポー ト A バ イ ト ラ イ ト イ ネーブル。RAM_MODE = SDP の場合は使用 し ません。

WEBWE[7:0] ポー ト B バ イ ト ラ イ ト イ ネーブル。RAM_MODE = SDP の場合、 バ イ ト ラ イ ト イ ネーブル と な り ます。

ENARDEN ポー ト A イ ネーブル。RAM_MODE = SDP の場合、RDEN と な り ます。 ENBWREN ポー ト B イ ネーブル。RAM_MODE = SDP の場合、WREN と な り ます。

RSTREGARSTREG 同期出力レ ジ ス タ のセ ッ ト/リ セ ッ ト 。SRVAL_A (DOA_REG = 1) で初期化 し ます。REGCE よ り も 優先す る か ど う かは RSTREG_PRIORITY_A で設定 し ます。RAM_MODE = SDP の場 合、RSTREG と な り ます。

RSTREGB 同期出力レ ジ ス タ のセ ッ ト/リ セ ッ ト 。SRVAL_B (DOA_REG = 1) で初期化 し ます。REGCE よ り も 優先す る か ど う かは、RSTREG_PRIORITY_B で設定 し ます。

RSTRAMARSTRAM 同期出力 ラ ッ チのセ ッ ト/リ セ ッ ト 。SRVAL_A (DOB_REG = 0) で初期化 し ます。 RAM_MODE = SDP の場合、RSTRAM と な り ます。

RSTRAMB 同期出力 ラ ッ チのセ ッ ト/リ セ ッ ト 。SRVAL_B (DOB_REG = 0) で初期化 し ます。 CLKARDCLK ポー ト A ク ロ ッ ク 入力。RAM_MODE = SDP の場合、RDCLK と な り ます。 CLKBWRCLK ポー ト B ク ロ ッ ク 入力。RAM_MODE = SDP の場合、WRCLK と な り ます。

REGCEAREGCE ポー ト A 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOA_REG = 1)。RAM_MODE = SDP の場合、 REGCE と な り ます。 REGCEB ポー ト B 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOB_REG = 1)。 CASCADEINA ポー ト A カ ス ケー ド 入力。RAM_MODE = TDP の場合のみ使用 し ます。 CASCADEINB ポー ト B カ ス ケー ド 入力。RAM_MODE = TDP の場合のみ使用 し ます。 CASCADEOUTA ポー ト A カ ス ケー ド 出力。RAM_MODE = TDP の場合のみ使用 し ます。 CASCADEOUTB ポー ト B カ ス ケー ド 出力。RAM_MODE = TDP の場合のみ使用 し ます。 DOADO[31:0] ポー ト A デー タ 出力バス。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DOPADOP[3:0] ポー ト A パ リ テ ィ 出力バ ス。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド での ポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DOBDO[31:0] ポー ト B デー タ 出力バス。ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DOPBDOP[3:0] ポー ト A パ リ テ ィ 出力バ ス。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド での ポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 表 1-7 : RAMB18E1 のポー ト 名 と 説明 ポー ト 名 内容 DIADI[15:0] ポー ト A デー タ 入力。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名 マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DIPADIP[1:0] ポー ト A デー タ パ リ テ ィ 入力。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド で のポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DIBDI[15:0] ポー ト B デー タ 入力。ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名 マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DIPBDIP[1:0] ポー ト A デー タパ リ テ ィ 入力。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド で のポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。

ADDRARDADDR[13:0] ポー ト A ア ド レ ス入力バス。RAM_MODE = SDP の場合、RDADDR バ ス と な り ます。 ADDRBWRADDR[13:0] ポー ト B ア ド レ ス入力バス。RAM_MODE = SDP の場合、WRADDR バ ス と な り ます。 WEA[1:0] ポー ト A バ イ ト ラ イ ト イ ネーブル。RAM_MODE = SDP の場合は使用 し ません。 表 1-6 : RAMB36E1 のポー ト 名 と 説明 (続き)

ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ

WEBWE[3:0] ポー ト B バ イ ト ラ イ ト イ ネーブル (WEBBE[1:0])。RAM_MODE = SDP の場合、 バ イ ト ラ イ ト イ ネーブル と な り ます。

ENARDEN ポー ト A イ ネーブル。RAM_MODE = SDP の場合、RDEN と な り ます。 ENBWREN ポー ト B イ ネーブル。RAM_MODE = SDP の場合、WREN と な り ます。

RSTREGARSTREG 同期出力レ ジ ス タ のセ ッ ト/リ セ ッ ト 。SRVAL_A (DOA_REG = 1) で初期化 し ます。REGCE よ り も 優先す る か ど う かは RSTREG_PRIORITY_A で設定 し ます。RAM_MODE = SDP の場 合、RSTREG と な り ます。

RSTREGB 同期出力レ ジ ス タ のセ ッ ト/リ セ ッ ト 。SRVAL_B (DOA_REG = 1) で初期化 し ます。REGCE よ り も 優先す る か ど う かは、RSTREG_PRIORITY_B で設定 し ます。

RSTRAMARSTRAM 同期出力 ラ ッ チのセ ッ ト/リ セ ッ ト 。SRVAL_A (DOB_REG = 0) で初期化 し ます。 RAM_MODE = SDP の場合、RSTRAM と な り ます。

RSTRAMB 同期出力 ラ ッ チのセ ッ ト/リ セ ッ ト 。SRVAL_B (DOB_REG = 0) で初期化 し ます。 CLKARDCLK ポー ト A ク ロ ッ ク 入力。RAM_MODE = SDP の場合、RDCLK と な り ます。 CLKBWRCLK ポー ト B ク ロ ッ ク 入力。RAM_MODE = SDP の場合、WRCLK と な り ます。

REGCEAREGCE ポー ト A 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOA_REG = 1)。RAM_MODE = SDP の場合、 REGCE と な り ます。 REGCEB ポー ト B 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOB_REG = 1)。 DOADO[15:0] ポー ト A デー タ 出力バス。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DOPADOP[1:0] ポー ト A パ リ テ ィ 出力バス。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド での ポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DOBDO[15:0] ポー ト B デー タ 出力バス。ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 DOPBDOP[1:0] ポー ト A パ リ テ ィ 出力バス。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド での ポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。 表 1-7 : RAMB18E1 のポー ト 名 と 説明 (続き) ポー ト 名 内容

ブ ロ ッ ク

RAM

のポー ト 信号

ブ ロ ッ ク RAM の各ポー ト は、 同 じ 36Kb メ モ リ セルのセ ッ ト にア ク セ ス し ますが、 動作はそれぞ れ独立 し てい ます。ク ロ ッ ク

- CLKARDCLK

、

CLKBWRCLK

各ポー ト は、 それぞれの ク ロ ッ ク ピ ンに完全に同期 し ます。 すべてのポー ト の入力ピ ンにはセ ッ ト ア ッ プ タ イ ムがあ り 、CLK ピ ン を基準 と し ます。 ま た、 出力デー タ バ ス の Clock-to-Out も CLK ピ ン を基準 と し ます。 ク ロ ッ ク の極性は コ ン フ ィ ギ ュ レーシ ョ ン可能で、 デフ ォ ル ト では立ち上が り エ ッ ジに設定 さ れてい ます。SDP モー ド では、CLKA ポー ト が RDCLK と な り 、CLKB ポー ト が WRCLK と な り ます。イ ネーブル

- ENARDEN

、

ENBWREN

イ ネーブルピ ンは、 ポー ト の読み出 し 、 書 き 込み、 お よ びセ ッ ト/リ セ ッ ト 機能を制御 し ます。 ポー ト の イ ネーブルピ ンが非ア ク テ ィ ブの と き 、出力ピ ンは前の状態を維持 し 、デー タ は メ モ リ セルに 書き 込まれません。 イ ネーブルの極性は コ ン フ ィ ギ ュ レーシ ョ ン可能で、 デフ ォ ル ト ではア ク テ ィ ブ High に設定 さ れてい ます。SDP モー ド では、ENA ポー ト が RDEN と な り 、ENB ポー ト が WREN と な り ます。バイ ト

ラ イ ト

イ ネーブル

- WEA

、

WEBWE

デー タ 入力バ ス の内容を指定 し た メ モ リ 位置に書 き 込むには、 ク ロ ッ ク の立ち上が り エ ッ ジ前の セ ッ ト ア ッ プ タ イ ム中に EN と WE の両方がア ク テ ィ ブにな る 必要があ り ます。デー タ が出力 ラ ッ チに読み込まれ る か ど う かは、 書 き 込みモー ド (WRITE_FIRST、READ_FIRST、NO_CHANGE) の設定に よ っ て決ま り ます。 非ア ク テ ィ ブの場合は、 読み出 し 処理が行われ、 書 き 込みモー ド の設 定にかかわ ら ず、 ア ド レ スバス で指定 さ れた メ モ リ セルの内容がデー タ 出力バ ス に送信 さ れます。

ラ イ ト イ ネーブルピ ンの極性は変更で き ず、 常にア ク テ ィ ブ High です。SDP モー ド では、 WEBWE[7:0] ポー ト がバ イ ト ラ イ ト イ ネーブル と な り ます。TDP モー ド では、WEA[3:0] と WEB[3:0] がそれぞれポー ト A と ポー ト B のバ イ ト ラ イ ト イ ネーブル と な り ます。

レ ジ ス タ

イ ネーブル

- REGCEA

、

REGCE

、

REGCEB

レ ジ ス タ イ ネーブルピ ン (REGCE) は、 オプシ ョ ンの出力レ ジ ス タ を制御 し ます。RAM が レ ジ ス タ モー ド の場合、REGCE = 1 と 指定す る と 、 ク ロ ッ ク エ ッ ジで出力が レ ジ ス タ に取 り 込まれます。 REGCE の極性は変更で き ず、 常にア ク テ ィ ブ High です。SDP モー ド では、REGCEA ポー ト が REGCE と な り ます。

セ ッ ト

/

リ セ ッ ト

RSTREGARSTREG

、

RSTREGB

、

RSTRAMARSTRAM

、

RSTRAMB

ラ ッ チモー ド では、RSTRAM ピ ンに よ っ てデー タ 出力 ラ ッ チに SRVAL の値が同期で格納 さ れま す。 詳細は、31 ページの 「ブ ロ ッ ク RAM の属性」 を参照 し て く だ さ い。 オプシ ョ ンの出力レ ジ ス タ が イ ネーブルの場合 (DO_REG = 1)、RSTREG 信号に よ っ てデー タ 出力レ ジ ス タ に SRVAL の値 が同期的に格納 さ れます。RSTREG と REGCE の ど ち ら を優先す る かは、RSTREG_PRIORITY 属 性で指定 し ます。 デー タ 出力 ラ ッ チ ま たは出力レ ジ ス タ は、 パ リ テ ィ ビ ッ ト を含め同期で 0 ま たは 1にアサー ト さ れます。 各ポー ト には、 それぞれ 36 ビ ッ ト の SRVAL[A|B] 属性が指定 さ れます。 こ の初期化に よ っ て RAM メ モ リ セルが変化す る こ と はな く 、も う 1 つのポー ト での書 き 込みに も 影

ブ ロ ッ ク RAM のポー ト 信号

響を与え ません。 ど ち ら の信号 も 極性は コ ン フ ィ ギ ュ レーシ ョ ン可能で、 デフ ォ ル ト ではア ク テ ィ ブ High に設定 さ れてい ます。SDP モー ド では、RSTREGA ポー ト が RSTREG と な り 、RSTRAMA ポー ト が RSTRAM と な り ます。

ア ド レ ス

バス

- ADDRARDADDR

、

ADDRBWRADDR

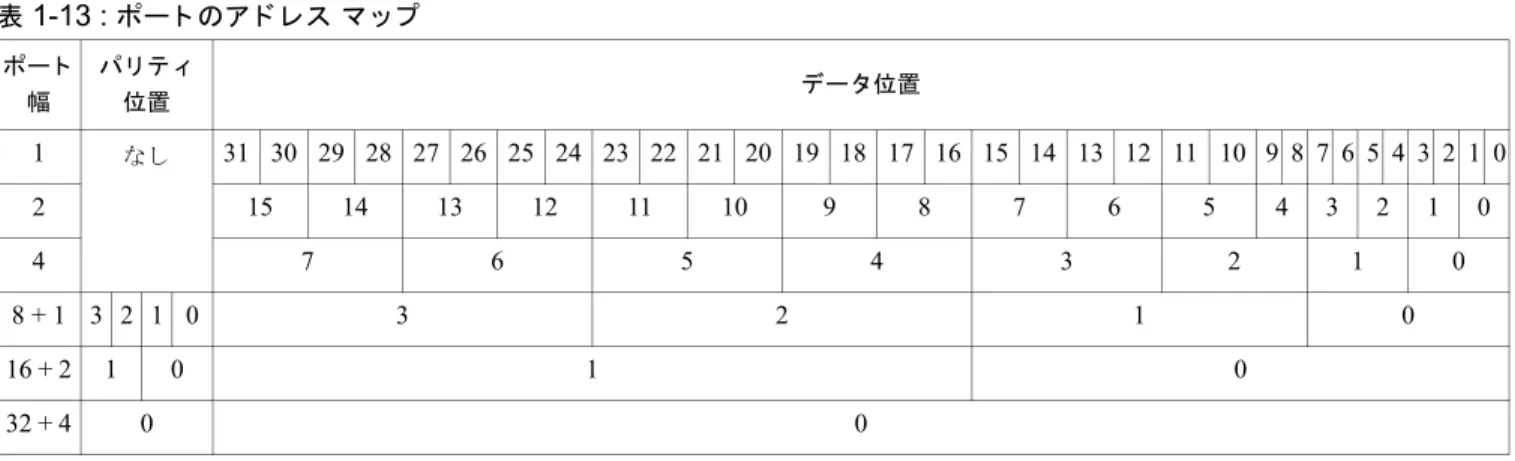

ア ド レ スバ ス は、 読み出 し ま たは書 き 込みを実行す る メ モ リ セルを選択 し ます。SDP モー ド では、 ADDRA ポー ト が RDADDR と な り 、ADDRB ポー ト が WRADDR と な り ます。表 1-8、表 1-9、

表 1-10、表 1-11に示す よ う に、RAMB18E1 ま たは RAMB36E1 のア ド レ スバ ス幅は、 ポー ト の デー タ ビ ッ ト 幅に よ っ て決ま り ます。 表 1-8 : RAMB18E1 のポー ト 比 (TDP モー ド) ポー ト のデー タ 幅 ポー ト のア ド レ ス幅 ワー ド 数 ADDR バス DI バス DO バス DIP バス DOP バス 1 14 16,384 [13:0] [0] NA 2 13 8,192 [13:1] [1:0] NA 4 12 4,096 [13:2] [3:0] NA 9 11 2,048 [13:3] [7:0] [0] 18 10 1,024 [13:4] [15:0] [1:0] 表 1-9 : RAMB18E1 のポー ト 比 (SDP モー ド) ポー ト のデー タ 幅 も う 一方のポー ト 幅 ポー ト のア ド レ ス幅 ワー ド 数 ADDR バス DI バス DO バス DIP バス DOP バス 32 1 14 16,384 [13:0] [0] NA 32 2 13 8,192 [13:1] [1:0] NA 32 4 12 4,096 [13:2] [3:0] NA 36 9 11 2,048 [13:3] [7:0] [0] 36 18 10 1,024 [13:4] [15:0] [1:0] 36 36 9 512 [13:5] [31:0] [3:0] メ モ : 1. 読み出 し ま たは書 き 込みポー ト の幅は x32 ま たは x36 で固定です。 表 1-10 : RAMB36E1 のポー ト 比 (TDP モー ド) ポー ト のデー タ 幅 ポー ト のア ド レ ス幅 ワー ド 数 ADDR バス DI バス DO バス DIP バス DOP バス 1 15 32,768 [14:0] [0] NA 2 14 16,384 [14:1] [1:0] NA 4 13 8,192 [14:2] [3:0] NA 9 12 4,096 [14:3] [7:0] [0]

RAMB36E1 を使用す る カ ス ケー ド 接続可能なブ ロ ッ ク RAM の場合、 デー タ 幅は 1 ビ ッ ト で、 ア ド レ スバ ス幅は 16 ビ ッ ト[15:0] にな り ます。ア ド レ ス ビ ッ ト 15 は、カ ス ケー ド 接続可能なブ ロ ッ ク RAM でのみ使用 さ れます。 それ以外のブ ロ ッ ク RAM では High に接続 し て く だ さ い。 デー タ お よ びア ド レ スピ ンのマ ッ ピ ン グについては、「RAMB18E1 お よ び RAMB36E1 プ リ ミ テ ィ ブの設計上のその他の注意事項」 で詳 し く 説明 し ます。 表 1-12に、SDP モー ド におけ る ポー ト 名のマ ッ ピ ン グ を示 し ます。SDP モー ド におけ る デー タ フ ロ ーについては、19 ページの図 1-6に示 し てい ます。 18 11 2,048 [14:4] [15:0] [1:0] 36 10 1,024 [14:5] [31:0] [3:0] 1 (カ ス ケー ド) 16 65,536 [15:0] [0] NA 表 1-10 : RAMB36E1 のポー ト 比 (TDP モー ド) (続き) ポー ト のデー タ 幅 ポー ト のア ド レ ス幅 ワー ド 数 ADDR バス DI バス DO バス DIP バス DOP バス 表 1-11 : RAMB36E1 のポー ト 比 (SDP モー ド) ポー ト のデー タ 幅(1) も う 一方のポー ト 幅 ポー ト のア ド レ ス幅 ワー ド 数 ADDR バス DI バス DO バス DIP バス DOP バス 64 1 15 32,768 [14:0] [0] NA 64 2 14 16,384 [14:1] [1:0] NA 64 4 13 8,192 [14:2] [3:0] NA 72 9 12 4,096 [14:3] [7:0] [0] 72 18 11 2,048 [14:4] [15:0] [1:0] 72 36 10 1,024 [14:5] [31:0] [3:0] 72 72 9 512 [14:6] [63:0] [7:0] メ モ : 1. 読み出 し ま たは書 き 込みポー ト の幅は x64 ま たは x72 で固定です。 表 1-12 : SDP モー ド におけるポー ト 名のマ ッ ピ ング SDP モー ド 時の RAMB18E1 SDP モー ド 時の RAMB36E1 X36 モー ド (幅= 36) X18 モー ド (幅18) X72 モー ド (幅= 72) X36 モー ド (幅36) DI[15:0] = DIADI[15:0] DI[15:0] = DIBDI[15:0] DI[31:0] = DIADI[31:0] DI[31:0] = DIBDI[31:0] DIP[1:0] = DIPADI[1:0] DIP[1:0] = DIPBDIP[1:0] DIP[3:0] = DIPADI[3:0] DIP[3:0] = DIPBDIP[3:0] DI[31:16] = DIBDI[15:0] DI[63:32] = DIBDI[31:0]

DIP[3:2] = DIPBDIP[1:0] DIP[7:4] = DIPBDIP[3:0]

DO[15:0] = DOADO[15:0] DO[15:0] = DOADO[15:0] DO[31:0] = DOADO[31:0] DO[31:0] = DOADO[31:0] DOP[1:0] = DOPADOP[1:0] DOP[1:0] = DOPADOP[1:0] DOP[3:0] = DOPADOP[3:0] DOP[3:0] = DOPADOP[3:0]

ブ ロ ッ ク RAM のポー ト 信号

デー タ 入力バス

- DIADI

、

DIPADIP

、

DIBDI

、

DIPBDIP

デー タ 入力バス は、RAM に書 き 込むデー タ 値を供給 し ます。 通常のデー タ 入力バス (DI) と パ リ テ ィ デー タ 入力バ ス (DIP) (使用可能な場合) の幅を合計 し た も のがポー ト 幅にな り ます。 た と え

ば、表 1-8~表 1-11に示す よ う に、36 ビ ッ ト のポー ト デー タ 幅は DI[31:0] と DIP[3:0] で表 さ れ

ます。SDP モー ド でのポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。

デー タ 出力バス

- DOADO

、

DOPADOP

、

DOBDO

、

DOPBDOP

読み出 し では、 最後のア ク テ ィ ブな ク ロ ッ ク エ ッ ジでア ド レ ス バ ス に よ り 指定 さ れた メ モ リ セル の内容が、 デー タ 出力バス に送信 さ れます。WRITE_FIRST ま たは READ_FIRST モー ド の書 き 込 みでは、 書 き 込み中の値 ま たは書 き 込み前に保存 さ れていた値がデー タ 出力バ ス に送信 さ れ ます。 NO_CHANGE モー ド の書 き 込みでは、デー タ 出力バス は変化 し ません。表 1-8~表 1-11に示す よ う に、通常のデー タ 出力バ ス (DO) と パ リ テ ィ デー タ 出力バス (DOP) (使用可能な場合) の幅を合計 し た も のがポー ト 幅にな り ます。SDP モー ド でのポー ト 名マ ッ ピ ン グについては、表 1-12を参照 し て く だ さ い。

カ スケー ド 入力

CASCADEINA

、

CASCADEINB

、

CASCADEOUTA

、

CASCADEOUTB

CASCADEIN ピ ンは、2 つのブ ロ ッ ク RAM を接続 し て 64K x 1 メ モ リ を作成す る 場合に使用 し ま

す (図 1-10)。UPPER に設定 し たブ ロ ッ ク RAM の こ の ピ ン を、同一ポー ト の LOWER に設定 し た

ブ ロ ッ ク RAM の CASCADEOUT ピ ンに接続 し ます。 カ ス ケー ド モー ド を使用 し ない場合、 こ の ピ ン を接続す る 必要はあ り ません。 詳細は、「カ ス ケー ド 接続可能なブ ロ ッ ク RAM」を参照 し て く だ さ い。 カ ス ケー ド 接続を利用で き る のは、TDP モー ド の場合のみです。

DO[31:16] = DOBDO[15:0] DO[63:32] = DOBDO[31:0] DOP[3:2] = DOPBDOP[1:0] DOP[7:4] = DOPBDOP[3:0] 表 1-12 : SDP モー ド におけるポー ト 名のマ ッ ピ ング (続き)

SDP モー ド 時の RAMB18E1 SDP モー ド 時の RAMB36E1

X36 モー ド (幅= 36) X18 モー ド (幅18) X72 モー ド (幅= 72) X36 モー ド (幅36)

X-Ref Target - Figure 1-10

図 1-10 : カ スケー ド 接続 し た 2 つの RAMB36 ug363_c1_10_011509