RL78/F13, F14

割り込み要因判別方法

対象デバイス(RL78/F13, F14)では、複数の割り込み要因を一つの割り込みベクタ・テーブル・アドレス に兼用しています(表1-1 参照)。複数の割り込み要因を共に使用する場合、割り込み処理内でどちらの割 り込みが発生したか、または両方の割り込みが発生したかを判定する必要があります。 本アプリケーションノートでは、デフォルト・プライオリティ6, 7, 8, 19 の割り込みについて、割り込み 要因を共に使用する場合の割り込み要因判別方法について説明します。 表1-1. 複数の割り込み要因を一つの割り込みベクタ・テーブル・アドレスに兼用した割り込み要因 デフォルト・ プライオリティ 割り込み要因注3 名称 トリガ 6 INTP4 端子入力エッジ検出4 INTSPM スタック・ポインタオーバーフロー/アンダーフロー 7 INTP5 端子入力エッジ検出5 INTCMP0 コンパレータ検出0 8 INTP13 端子入力エッジ検出13 INTCLM PLL クロックの停止 19 INTP8 端子入力エッジ検出8 INTRTC RTC 定周期信号/アラーム一致検出 25注1 INTP6 端子入力エッジ検出6 INTTM11H TAU1 チャネル 1 の上位 8 ビット・インターバル・タイマ割り込み (8 ビット・タイマ機能選択時) 26注1 INTP7 端子入力エッジ検出7 INTTM13H TAU1 チャネル 3 の上位 8 ビット・インターバル・タイマ割り込み (8 ビット・タイマ機能選択時) 27注1 INTP9 端子入力エッジ検出9 INTTM01H TAU0 チャネル 1 の上位 8 ビット・インターバル・タイマ割り込み (8 ビット・タイマ機能選択時) 28注1 INTP10 端子入力エッジ検出10 INTTM03H TAU0 チャネル 3 の上位 8 ビット・インターバル・タイマ割り込み (8 ビット・タイマ機能選択時) 35注2 INTP11 端子入力エッジ検出11 INTLIN0WUP LIN0 受信端子入力 48注2 INTP12 端子入力エッジ検出12 INTLIN1WUP LIN1 受信端子入力 注1:デフォルト・プライオリティ 25, 26, 27, 28 の端子入力エッジ検出と TAU の上位 8 ビット・インター バル・タイマ割り込みは、割り込み要因を判別することができません。 注2:デフォルト・プライオリティ 35, 48 の端子入力エッジ検出と LIN 受信端子入力割り込みは、ISC レジ スタのISC2, ISC3 ビットで機能を選択して使用するため、同時に使用することはできません。 注3:製品により存在しない場合があります。詳細はユーザーズマニュアルをご確認ください。 R01AN3343JJ0100 Rev.1.00 2017.06.30目次

1. 兼用割り込みの判別方法 ... 3 1.1 INTP4/INTSPM 判別方法 ... 3 1.2 INTP5/INTCMP0 判別方法 ... 4 1.3 INTP13/INTCLM 判別方法 ... 5 1.4 INTP8/INTRTC 判別方法 ... 6 2. 兼用割り込み使用時の注意点 ... 7 2.1 INTFLG0 レジスタ ビットクリア時の注意点 ... 7 2.2 INTFLG00 ビットを使用時の要因判別処理例 ... 8INTSPM 割り込み発生判定

1. 兼用割り込みの判別方法

1.1

INTP4/INTSPM 判別方法

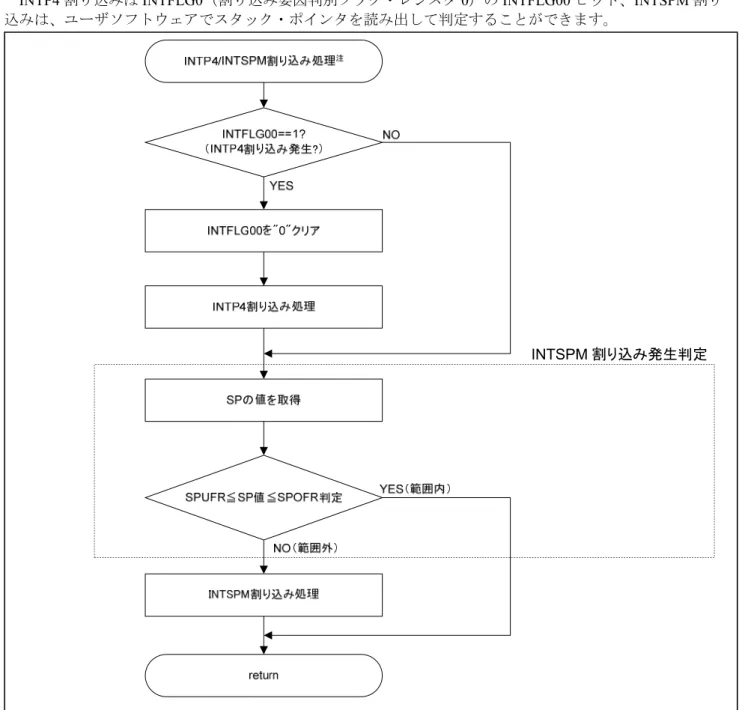

INTP4(端子入力エッジ検出 4)と INTSPM(スタック・ポインタオーバーフロー/アンダーフロー)の 2 つの割り込みを許可した時の割り込み処理例を図 1-1 に示します。

INTP4 割り込みは INTFLG0(割り込み要因判別フラグ・レジスタ 0)の INTFLG00 ビット、INTSPM 割り 込みは、ユーザソフトウェアでスタック・ポインタを読み出して判定することができます。

注:INTP4 と INTSPM の 2 つの割り込みを許可する場合、多重割り込みを許可(IE=1)してください。 図 1-1 INTP4/INTSPM 割り込み判定フローチャート

1.2

INTP5/INTCMP0 判別方法

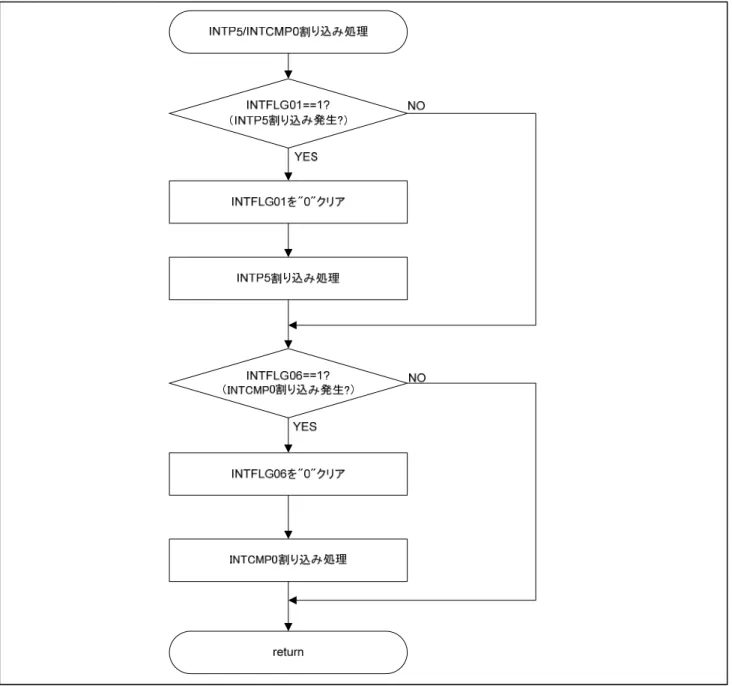

INTP5(端子入力エッジ検出 5)と INTCMP0(コンパレータ検出 0)の 2 つの割り込みを許可した時の割 り込み処理例を図 1-2 に示します。

INTP5 割り込みは INTFLG0(割り込み要因判別フラグ・レジスタ 0)の INTFLG01 ビット、INTCMP0 割 り込みは同レジスタのINTFLG06 ビットで判定することができます。

INTCLM 割り込み発生判定

1.3

INTP13/INTCLM 判別方法

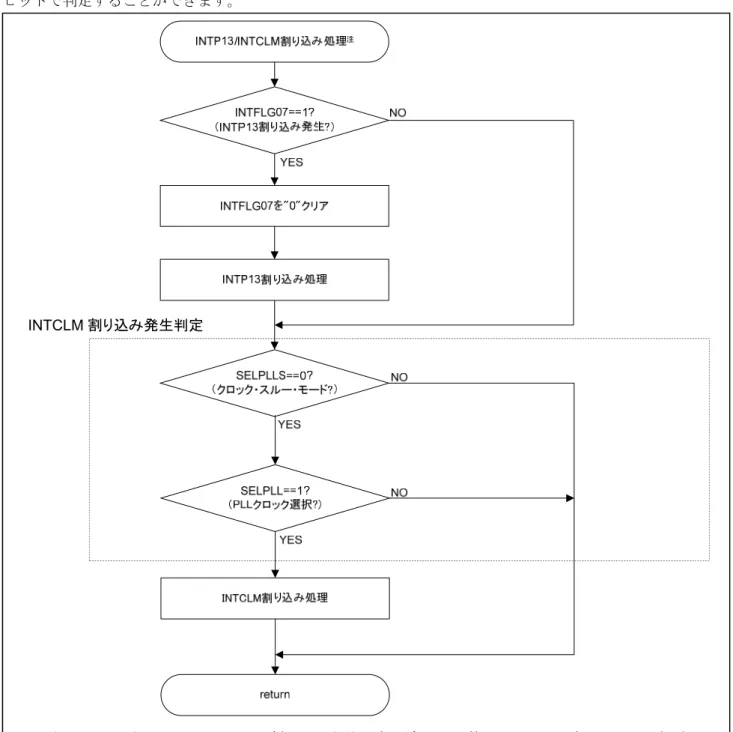

INTP13(端子入力エッジ検出 13)と INTCLM(PLL クロック停止検出)の 2 つの割り込みを許可した時 の割り込み処理例を図 1-3 に示します。

INTP13 割り込みは INTFLG0(割り込み要因判別フラグ・レジスタ 0)の INTFLG07 ビット、INTCLM 割 り込みはPLLSTS(PLL 状態レジスタ)の SELPLLS ビットおよび PLLCTL(PLL 制御レジスタ)の SELPLL ビットで判定することができます。

注:INTP13 と INTCLM の 2 つの割り込みを許可する前に、必ずメイン/PLL 選択クロック(fMP)の

切り替えを実施してください。

INTRTC 割り込み発生判定

INTRTC 割り込み発生判定

1.4

INTP8/INTRTC 判別方法

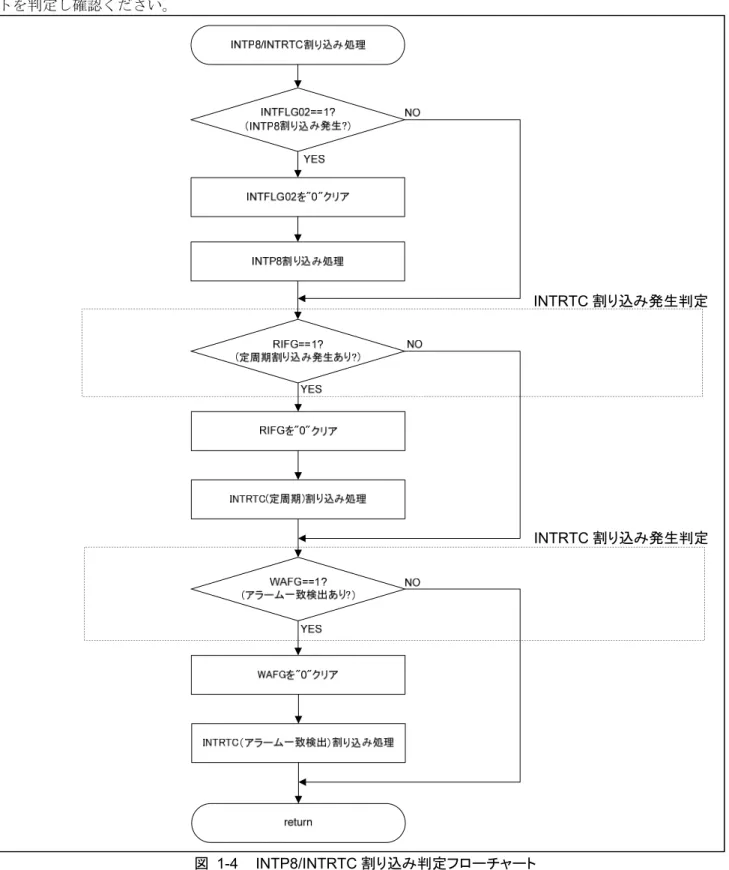

INTP8(端子入力エッジ検出 8)と INTRTC(RTC 定周期信号/アラーム一致検出)の 2 つの割り込みを 許可した時の割り込み処理例を図 1-4 に示します。

INTP8 割り込みは INTFLG0(割り込み要因判別フラグ・レジスタ 0)の INTFLG02 ビット、INTRTC 割り 込みはRTCC1(リアルタイム・クロック・コントロール・レジスタ 1)の WAFG ビットおよび RIFG ビッ トを判定し確認ください。

2. 兼用割り込み使用時の注意点

2.1

INTFLG0 レジスタ ビットクリア時の注意点

割り込み処理中に同一要因の割り込みが新たに発生した場合、INTFLG0(割り込み要因判別フラグ・ レジスタ0)の INTFLG0x ビットをクリアしても割り込み要求(IF ビット)が“1”になることがありま す。その場合、割り込みは発生しますが、割り込み要因(INTFLG0x ビット)は“なし”(割り込み応答で きない)のため、割り込み処理を行わずに終了します。2.2 章に例を示します。INTSPM 割り込み発生判定 新たな INTP4 割り込み発生

2.2

INTFLG00 ビットを使用時の要因判別処理例

INTP4 を割り込み要因として INTP4/INTSPM 割り込みを発生し、図 2-1 の割り込み処理を実施したとしま す。INTFLG00 ビットが“1”であることを判定後、INTFLG00 ビットをクリアする前に、新たな有効エッジ がINTP4 端子に入力されると、割り込み処理中に IF0L(割り込み要求フラグ・レジスタ)の PIF4/SPMIF ビットが再び“1”になります。その後、INTFLG00 ビットを“0”クリアし、INTP4 割り込み処理を終了し ますが、PIF4/SPMIF ビットが“1”のため、再度 INTP4/INTSPM 割り込みが発生し、図 2-1 の割り込み処理 を実行します。この時、INTFLG00 ビットが“0”のため、INTP4 割り込みが検出されず、何も割り込み処 理を行わずに終了します。システム設計にする際に、上記の内容をユーザ側で考慮する必要がありますの で、ご注意ください。 CPU スタック・ポインタ・モニタ機能は SP の異常を検知する安全機能であるため、割り込み優先順位レ ベルを高く設定することをお勧めします。 図 2-2 INTFLG00 ビットを使用時の割り込み判別処理例ホームページとサポート窓口<website and support,ws>

ルネサス エレクトロニクスホームページ http://japan.renesas.com/ お問合せ先 http://japan.renesas.com/contact/ すべての商標および登録商標は,それぞれの所有者に帰属します。改訂記録<revision history,rh>

Rev. 発行日

改訂内容

ページ ポイント

■営業お問合せ窓口

■技術的なお問合せおよび資料のご請求は下記へどうぞ。 総合お問合せ窓口:https://www.renesas.com/contact/

ルネサス エレクトロニクス株式会社 〒135-0061 東京都江東区豊洲3-2-24(豊洲フォレシア)

© 2017 Renesas Electronics Corporation. All rights reserved.

http://www.renesas.com ※営業お問合せ窓口の住所は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。