平成17年度 修士論文

AlGaN/GaN MIS-HFET における

ヒステリシス特性の研究

徳島大学大学院 工学研究科 電気電子工学専攻 物性デバイス講座

平成17年度 修士論文 内容梗概

電気電子工学専攻

研究題目

AlGaN/GaN MIS-HFETにおけるヒステリシス特性の研究

氏 名

松田 潤也

【大野研究室】 はじめに AlGaN/GaN HFET は高電子移動度であるほか、絶縁破壊電界が大きいため高速・高出力デバイスとして 期待されている。しかし実用化にはいくつか課題があり、そのひとつにゲートリークの存在が挙げられる。 ゲートリーク抑制にはMIS 構造が効果的であるとされるが、MIS-HFET にもヒステリシスなどの問題が存 在する。MIS-HFET に関するこれまでの研究で、ワイドバンドギャップ材料では絶縁膜のリークが大きいこ と、AlGaN 層がダイオード的な特性をもつことが判っている。これらをふまえ本研究では I-V 測定とシミュ レーションによりMIS 構造におけるヒステリシスのメカニズムの解析を行った。 I-V特性の周波数依存性 周波数可変カーブトレーサにより ID-VG特性の周波数依存 性の測定を行った(図1-a)。VD=1V とし、ゲートに周波数 0.01Hz~100kHz の正弦波を入力した。低周波では VGの増 加とともにIDも増加し、約2V から一定となった。一方高周 波では IDは VGによらずほぼ一定の値となった。中間周波数 では反時計回りのループを描くヒステリシスがみられた。 SPICEシミュレーション 絶縁膜を R と C との並列接続で、AlGaN 層をダイオード とC の並列接続であらわした等価回路モデルを用いた(図 1-b 内)。低周波では抵抗成分が支配的となり、界面電位がダ イオードのオン電圧を超えると IDが一定となる。高周波では キャパシタ成分が支配的となり、ゲート電圧の変化に対して 界面電位は C の比で決まる変化の小さい直線となる。そのた め IDもほぼ一定の値となる。中間周波数においては、抵抗成 分、キャパシタ成分が混在するために、界面電位とゲート電 位に位相差が生じ、ヒステリシスを引き起こす。この現象は ループ方向も含めシミュレーションで再現できた。 ヒステリシスループの解析 単純化のためダイオードを抵抗に置き換えると、界面の位 相差はそれぞれの抵抗成分とキャパシタ成分の積の関係によ り決まることがわかった。絶縁膜のRC 積が AlGaN 層の RC 積よりも小さいとき、界面電位は遅れの位相となり、ヒステ リシスは測定結果のように反時計回りのループとなる。キャパシタ成分にはそれほど大きな差が無いため、 ヒステリシス特性は絶縁膜とAlGaN 層の抵抗の関係に大きく影響されることになる。 まとめ I-V 特性とシミュレーションから、ヒステリシスはゲート電圧と界面電位の間に存在する位相差が原因で あることがわかった。さらにワイドバンドギャップ材料においては絶縁膜の抵抗値が、そのデバイス特性に 大きく影響しているため、デバイス開発の際にはその点を考慮しなければならないだろう。 0 1 2 3 -4 -2 0 2 4 6 8 VG [V] ID [ m A ] 0.01Hz 10Hz 1kHz 100kHz 1 2 3 I D [ m A ] (a)Experiment 0.01Hz 10Hz 1kHz 0 -4 -2 0 2 4 6 8 VG [V] 100kHz CI CAlGaN Gate 2DEG (b)Simulation RI D AlGaN Insulator 図1. ID-VG特性の周波数依存性目次 第1章 序論 1.1 研究背景・目的 ・・・・・・・・・・・・・・・・・・・・・ 2 1.2 本論文の構成 ・・・・・・・・・・・・・・・・・・・・・ 2 第2章 AlGaN/GaN MIS-HFET について 2.1 HFET について ・・・・・・・・・・・・・・・・・・・・・ 3 2.2 MIS-HFET について ・・・・・・・・・・・・・・・・・ 4 2.3 MIS-HFET の問題点 ・・・・・・・・・・・・・・・・・ 5 2.4 デバイス構造 ・・・・・・・・・・・・・・・・・・・・・ 7 2.5 MIS-HFET の DC 特性 ・・・・・・・・・・・・・・・・・ 8 第3章 周波数可変カーブトレーサ 3.1 周波数可変カーブトレーサについて ・・・・・・・・・・・・・10 3.2 装置構成 ・・・・・・・・・・・・・・・・・・・・・・・・・11 3.3 装置性能 ・・・・・・・・・・・・・・・・・・・・・・・・・12 第4章 測定と結果 4.1 ID-VG特性の周波数依存性 ・・・・・・・・・・・・・・・・・14 4.2 ID-VG特性の掃引中心電圧依存性 ・・・・・・・・・・・・・15 第5章 解析 5.1 AC 特性の等価回路モデル ・・・・・・・・・・・・・・・・・17 5.2 界面電位の周波数依存性 ・・・・・・・・・・・・・・・・・18 5.3 位相差とヒステリシスの関係 ・・・・・・・・・・・・・20 第6章 SPICE シミュレーション 6.1 SPICE シミュレーションについて ・・・・・・・・・・・・・22 6.2 シミュレーション回路 ・・・・・・・・・・・・・・・・・23 6.3 シミュレーション結果 ・・・・・・・・・・・・・・・・・25 6.3.1 ID-VG特性の周波数依存性 ・・・・・・・・・・・・・26 6.3.2 ID-VG特性の掃引中心電圧依存性 ・・・・・・・・・26 第7章 本研究のまとめ ・・・・・・・・・・・・・・・・・・・・・28 謝辞 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・29 参考文献 ・・・・・・・・・・・・・・・・・・・・・・・・・29

第

1章 序論

1.1 研究背景・目的 近年の情報通信技術の発展はめざましく、1837 年のモールス(Morse)の電信通信からは じまり、1876 年には、グラハム・ベル(Graham Bell)が有線電話機を発明し、その後無線通信 が発明された。今日ではラジオ、テレビ(アナログ通信、地上波ディジタル通信)などはもと より、インターネットや携帯電話の普及に伴い、各種無線通信、無線LAN など通信の情報量 は増加の一途をたどっている。そのため、通信技術の更なる高速化と高精度化、高効率化が強 く望まれている。現在、準ミリ波、ミリ波に至る各種の無線システムが開発、計画されている が、これらを実現するためには高周波の無線出力を担う高性能半導体素子が必要である。しか し従来の Si(シリコン)、GaAs(ガリウム砒素)系素子ではスケーリング則に基づき、高周波 動作や出力性能などが限界に達しつつある。更なる高速化、高出力化を実現するためには、こ れらに代わる新しい半導体材料が必要となるが、そのひとつに GaN(窒化ガリウム)が挙げら れる。 3.4eV という大きなバンドギャップを有する GaN は絶縁破壊電界が大きいため、高耐圧、微 細化が可能とされ、また電子飽和速度が高いなどの材料的特長を持つことから、Si、GaAs 素 子を超える次世代の高速、かつ高出力のトランジスタ実現に期待が寄せられている。しかし、GaN 系 FET の開発で大きな問題として大きなゲートリークや電流コラプス、I-V 特性のヒステリシスなどがある。ゲートリークに関しては、ゲート金属と半導体の間に絶縁膜 を挿入したMIS(Metal Insulator Semiconductor)構造を用いることで、低減できることが わかっている。しかし、ゲートに MIS 構造を用いた場合、大きなヒステリシス現象が現れる といった問題点も存在する。また、動作点の違いによっても特性に変化が見られる。そこで本 研究ではAlGaN/GaN MIS-HFET におけるヒステリシス特性のメカニズムを解明するために、 周波数可変カーブトレーサを用いてI-V 特性の測定を行った。またその測定結果を説明するた め等価回路モデルを考案し、SPICE シミュレーションにより考察を行った。 1.2 本論文の構成 第2 章において AlGaN/GaN MIS-HFET についての説明を行い、第 3 章では AC 特性を測 定するための周波数可変カーブトレーサの説明をする。第4 章では前述の装置を用いた測定結 果について述べる。第5 章において、第 4 章で得られた特性について等価回路モデルを用いて 解析を行う。そして第6 章で等価回路モデルを用いた SPICE シミュレーションを行い測定結 果の考察を行い、第7 章では本研究の全体的なまとめを行う。

第

2章 AlGaN/GaN MIS-HFET について

2.1 HFET について

HFET(Heterostructure Field Effect Transistor)は GaAs 系デバイスにおいて衛星放送受 信用パラボラアンテナの低雑音素子として広く使われるようになった。GaAs FET に比べると 同じゲート長を持ったHFET は 12GHz で、約 0.5dB だけ低い雑音指数特性を示す良好なト ランジスタである。現在ではGaAs よりもバンドギャップエネルギーが大きく、電子移動度も 高いGaN に注目が集まっている。

図2.1 に AlGaN/GaN HFET の構造図を示す。HFET の構造的特長は、2DEG(二次元電子 ガス:2 dimension electron gas)と呼ばれる AlGaN-GaN のヘテロ接合界面近傍に形成される チャネル層である。2DEG の形成により電子と不純物イオンとはヘテロ接合界面を境として空 間的に分離される。つまり電子が走行する 2DEG 内には、走行するのに邪魔になる不純物イ オンが存在しないため高電子移動度をもつことができる。これにより同じ半導体材料でも HFET 構造を形成することにより高移動度の高速デバイスを作製することができる。 AlGaN GaN サファイア基板 S G 2DEG D 図2.1 AlGaN/GaN HFET 構造図

AlGaN/GaN HFET は現在、GaN のさまざまな材料的長所から次世代無線通用高周波高出 力デバイスとして期待されているが、その実用化に関してはいくつか問題点もある。まず、プ ロセス技術に関していうと、GaN は Si 系デバイスのような良好な加工性を持っていないこと が挙げられる。またRIE(反応性イオンエッチング:Reactive Ion Etching)などのドライエッチ ングや王水などのウェットエッチングでは高精度な技術が確立していないという問題もある。 そして現在の HFET の電気特性に関しては、ゲートリーク電流が大きいことが最も大きな問 題である。ゲートリーク電流の大きさはGaN 基板の構造にもよるが、通常約 10-6~10-5A、大 きい場合では10-3A 程もある。このように大きいゲートリーク電流を持つ HFET では高いド ープのウェハで作製した場合カットオフできない等の問題が生じてしまう。

2.2 MIS-HFET について

2.1 で述べたように AlGaN/GaN HFET には、大きなゲートリークを有するという問題点が ある。このゲートリークの低減に有効とされるのが、ゲート金属と半導体との間に絶縁膜を挿 入したMIS(Metal Insulator Semiconductor)構造である。図 2.2 に AlGaN/GaN MIS-HFET の構造図を示す。 Insulator AlGaN GaN S G D 図2.2 AlGaN/GaN MIS-HFET 構造図 ゲート直下に挿入する絶縁膜の材料にはSiO2やSiN などが用いられ、いずれもゲートリー クの大幅な減少が実現されている。図2.3 に Standard HFET と MIS-HFET の IG-VG特性を 示す。Standard HFET のゲートリーク電流 IGが1×10-3 A 程度であるのに対し、SiO2では1 ×10-9 A、SiN では 1×10-11 A 程度まで低減されており、MIS 構造のゲートリーク低減に対す る有効性は明らかである。

1.E-13

1.E-11

1.E-09

1.E-07

1.E-05

1.E-03

1.E-01

-10

-8

-6

-4

-2

0

2

V

G[V]

I

G[

A]

HFET SiO2 SiN 図2.3 IG-VG特性比較2.3 MIS-HFET の問題点 ゲートリーク低減に有効な MIS-HFET ではあるが、いくつかの問題も抱えている。まず、 AC 動作時において、周波数によっては大きなヒステリシス現象が発生するという問題がある。 図2.4 に ID-VD特性、図2.5 に ID-VG特性の周波数特性を示す。Standard HFET では動作周 波数による特性の大きな変化は見られないため、このヒステリシス現象はゲート金属直下に挿 入した絶縁膜の影響で引き起こされていることは間違いない。また、AC 動作時の動作点の違 いによっても特性に変化がみられる。 0 1 2 3 4 5 6 7 8 0 2 4 6 8 VD [V] I D [ m A ] 10 1000Hz 100Hz 10Hz 1Hz 0.1Hz 0.01Hz

(a) Standard HFET

0 1 2 3 4 5 6 7 8 0 2 4 6 8 VD [V] ID [ m A] 10 1000Hz 100Hz 10Hz 1Hz 0.1Hz 0.01Hz (b) MIS-HFET 図2.4 ID-VD特性の比較

(a) Standard HFET (b) MIS-HFET 0 2 4 6 8 10 -10 -8 -6 -4 -2 0 2 4 VG [V] ID [ m A ] 1000Hz 100Hz 10Hz 1Hz 0.1Hz 0.01Hz 0 2 4 6 8 10 -10 -8 -6 -4 -2 0 2 4 VG [V] I D [ m A ] 1000Hz 100Hz 10Hz 1Hz 0.1Hz 0.01Hz 図2.5 ID-VG特性の比較 また、絶縁膜材料の種類、絶縁膜の膜厚の違いによっても特性に変化が現れるという問題も ある。このことからも MIS 構造における絶縁膜が、デバイス特性に与える影響は大きいこと がわかる。ゲートリークを大幅に減少させることが可能なMIS-HFET ではあるが、これらの 諸問題の発生メカニズムははっきりしないため、その解明が急がれている。

2.4 デバイス構造

図2.5 に今回測定に使用した AlGaN/GaN 基板の結晶構造図を示す。サファイア基板上に MOCVD 法(Metal Organic Chemical Vapor Deposition)で GaN 層を 2μm、Al0.281GaN28nm を堆積した構造である。AlGaN 層は三層構造であり、中間の 20nm には Si ドープがなされて いる。この基板上に図2.6 に示すプロセスフローに従い、ウェハカットの後、オーミック電極 としてTi/Al/Ni/Au をそれぞれ 50/200/40/30nm を電子線蒸着(EB)によって蒸着した。窒素 雰囲気中で850℃、3分間のアニールの後、RIE により素子間分離を行った。そして、MIS-HFET とするためゲート絶縁膜を堆積後、ゲート電極としてNi/Au を EB によりそれぞれ 80/30nm 蒸着した。測定に使用したトランジスタのゲート長LGは4μm、ゲート幅 WGは50μm、ゲー ト-ドレイン間とゲート-ソース間距離は 5μm である。また、ゲート絶縁膜は EB により SiO2 を90nm 堆積させた。 ウェハカット オーミック電極形成 (EB:Ti/Al/Ni/Au 50/200/40/30nm) ゲート絶縁膜堆積 アニール (N2 中,850℃,3min) 素子間分離(RIE) (エッチング深さ:60nm) ゲート電極形成 (EB:Ni/Au 80/30nm)

t = 20nm, Si 2×10

18AlGaN

t = 2

μ

m

GaN

サファイア基板

t = 5nm

t = 3nm

図2.6 結晶構造 図2.7 プロセスフロー2.5 MIS-HFET の DC 特性 これまでのMIS-HFET に関する研究では絶縁膜の抵抗は無限大であり、ゲートへの逆バイ アス時のゲート電流、すなわちゲートリークはこの絶縁膜の抵抗により制限され、大幅な低減 がなされていると考えられてきた。しかし、我々の研究室における近年の研究で、MIS-HFET におけるゲートリークの低減は絶縁膜ではなく高抵抗化したAlGaN 層に起因していることが わかった。GaN のようなワイドバンドギャップ材料においては、SiO2のような絶縁物の抵抗 も無限大ではなく、ある有限な抵抗として振舞うため、その値がデバイス特性に影響を与える ことになる。更に図2.8 に示すように AlGaN 層のリーク特性の解析により、負バイアスでは 低リークであるが、正バイアス時にある電圧から急激に電流が流れ始める、ダイオード的な特 性を有することが判明した[1]。

-6 -5 -4 -3 -2 -1

0

1

2

3

10

-1510

-1210

-910

-610

-310

0GA

TE

CURRENT [A]

VOLTAGE ACROSS AlGaN LAYER [V]

V

S= 0V, V

D= 1V

HFET

EB SiO

XMISFET

CVD SiO

2MISFET

図2.8 AlGaN 層におけるリーク特性 絶縁膜が有限な抵抗として振舞うことと、AlGaN 層のダイオード的な特性を考慮して、図 2.9 に示すように、絶縁膜を抵抗で、AlGaN 層をダイオードで表現した等価回路を用いること で、MIS-HFET の DC 動作に関しては再現することができた[2]。図 2.10 に ID-VD特性の実測 とシミュレーションの比較を示す。 本研究ではMIS-HFET における AC 動作の解析が目的であるため、この DC 解析の結果を 下に各特性の解析を行うこととする。Gate

Insulator

Diode

R

InsulatorAlGaN

2DEG

図2.9 ゲート構造の等価回路0

5

10

15

0

5

10

15

20

25

Simulated ExperimentDRAIN CURRENT

[mA]

DRAIN VOLTAGE [V]

VG : -4 to +6V, +1V step LG=100μm, WG=200μm 図2.10 MIS-HFET の ID-VD特性第

3章 周波数可変カーブトレーサ

3.1 カーブトレーサについて カーブトレーサとは、測定対象にある周波数の周期バイアスを印加したとき、そこに流れる 電流値を測定することでI-V 特性を得る装置である。電子デバイスの評価は I-V 特性によって なされることが多いが、I-V 特性の測定は電圧や電流などの設定する項目が多く、かつそれら を連続的に変化させたグラフの作成など煩雑な作業を伴う。これらの設定からグラフの作成ま でを自動的に処理する装置がカーブトレーサである。 (a) 抵抗 (b) ダイオー ド (c) 電界効果トランジスタ 図3.1 カーブトレーサの測定例 I V I 0 V V I I 0 V VG VD ID ID VD 0本研究ではMIS-HFET のヒステリシス特性と周波数との関係を観測するために、印加周期 バイアスの周波数が設定可能な周波数可変カーブトレーサを作製し、各種測定を行う。 3.2 装置構成 図3.2 に周波数可変カーブトレーサの構成図を示す。本装置は、信号発生源としてファンク ションジェネレータ(NF, WF1946)、高周波測定を実現するための高速バイポーラ電源(NF, HSA4011)、入出力測定のためのデジタルオシロスコープ(Tektronix, TPS2024)で構成され ている。オシロスコープにより得られた測定データは付属のソフトウェアによりPC に保存さ High Speed Bipolar Amplifier S G D Ri Function Generator Ch1 Ch2 Digital Oscilloscope Ch2 Ch1 PC れる。 図3.2 周波数可変カーブトレーサの構成(ID-VG測定) のトランジスタはプローバに、電流検出用抵抗Ri はブレッドボード上に接 ID-VG測定時はファンクションジェネレータの Ch1 からドレイン電圧として定電圧を出力 するが、ファンクションジェネレータの出力インピーダンスの影響を除去し、かつ高周波測定 を実現するために、高速バイポーラ電源をファンクションジェネレータの Ch1 に接続し、こ れを通してドレインに信号を印加する。また Ch2 からゲート電圧として正弦波を出力する。 オシロスコープは Ch1 を入力、つまりゲート電圧 VGを、Ch2 を出力、つまりドレイン電流 IDを測定する。オシロスコープでは直接電流を測定できないため、電流検出用の抵抗 Ri(= 10Ω)を介し、その両端の電圧 V(=RiID)を測定することで、間接的にドレイン電流IDを得 る。なお測定対象

12-40 -30 -20 -10 0 10 20 30 40 50 -5 -4 -3 -2 -1 0 1 2 3 4 5 V (V) I (mA) 実測 理論 -40 -30 -20 -10 0 10 20 30 40 50 -5 -4 -3 -2 -1 0 1 4 5 V (V) I (mA) 2 3 実測 理論 3. られている。しかし500kHz あた りからヒステリシスが現れはじめ、線形性が崩れている。 (b) f= 00kHz 3 装置性能 今回作製した周波数可変カーブトレーサの性能の評価として、図3.2 のトランジスタの代わ りに抵抗RLを用いてI-V 特性の周波数特性を測定した。RL=100Ωのときの実測値と理論値の 比較を図3.3 に示す。先に述べたとおり測定対象である抵抗 RLのほかに電流検出用の抵抗Ri (=10Ω)も接続されているため、電流の理論値としては V=5V のときに I≒45.5mA となる。 周波数f が 100kHz 以下であるときはほぼ理論通りの値が得 (a) f=1kHz 1

-50 -40 -30 -20 -10 0 10 20 30 40 50 -5 -4 -3 -2 -1 0 1 2 3 4 5 V (V) I (mA) 実測 理論 -50 -40 -30 -20 -10 0 10 20 30 40 50 -5 -4 -3 -2 -1 0 1 2 3 4 I (mA) 5 V (V) 実測 理論 (c) f= 00kHz 図3.3 負荷試験結果(RL=100Ω) 果とファンクションジェネレータの性能から、この周波数可変カーブトレーサ ・掃引周波数範囲:DC ~ 100kHz とする。 5 (d) f=1MHz 負荷試験の結 の測定条件を ・測定範囲 :-10V ~ +10V

第

4章 測定と結果

4.1 ID-VG特性の周波数依存性 周波数可変カーブトレーサを用いてID-VG特性の周波数依存性の測定を行った。測定条件と しては、ドレイン電圧は1V で固定し、ゲートには振幅 VGpp=10V、振幅中心電圧 VGoffset=2V の正弦波信号を印加した。そしてその正弦波信号の周波数を0.01Hz から 100kHz まで変化さ せたときの特性の変化を測定した。 図4.1 に ID-VG特性の周波数依存性の測定結果を示す。周波数が0.01Hz と低周波の時には 大きなヒステリシスは現れず、VGの増加に伴いIDも増加するが、VGが約2V 以上になると ID は一定となった。一方1kHz や 100kHz といった高周波を印加したときにも大きなヒステリシ スは観測されないが、IDはVGの値によらずほぼ一定の値となった。そして、低周波でも高周 波でもない中程度の周波数である10Hz の信号を印加したときには、大きなヒステリシスが観 測された。そして、その際のヒステリシスは反時計回りのループであった。 0 0.5 1 1.5 2 2.5 -4 -2 0 2 4 6 8 VG [V] ID [ m A ] 0.01Hz 10Hz 1kHz 100kHz 図4.1 ID-VG特性の周波数依存性4.2 ID-VG特性の掃引中心電圧依存性 周波数可変カーブトレーサを用いてID-VG特性の掃引中心電圧ス依存性の測定を行った。測 定条件としては、ドレイン電圧は1V で固定し、ゲートには振幅 VGpp=10V の正弦波信号を印 加した。その際の中心電圧VGoffsetを-5V から 5V まで変化させてその特性の変化を測定した。 また正弦波信号の周波数は低周波0.01Hz と高周波 100kHz とした。 図4.2 に ID-VG特性の掃引中心電圧依存性の測定結果を示す。周波数が0.01Hz と低周波の 時にはVGoffsetに関係なく同様の特性が得られた。しかし100kHz の高周波の場合は、VGの変 化に関係なくほぼ一定の値となるのは、4.1 の実験と同様であるが、VGoffsetが-5V の時には ID はほぼ零であったのに対し、VGoffsetが5V では IDは2.3mA 付近で一定となり、VGoffsetの値に よって IDも変化するという結果が得られた。また、VG=VGoffsetにおける電流値は 0.01Hz と 100kHz で等しくなり、100kHz ではその電流値を中心に小さな変化をするという特性となっ た。

0

0.5

1

1.5

2

2.5

-10

-8

-6

-4

-2

0

V

G[V]

I

D[

mA

]

0.01Hz

100kHz

(a) VGoffset=-5V0

0.5

1

1.5

2

2.5

-5

-3

-1

1

3

5

V

G[V]

I

D[

mA

]

0.01Hz

100kHz

(b) VGoffset=0V0

0.5

1

1.5

2

2.5

0

2

4

6

8

1

V

G[V]

I

D[

m

A

]

0

0.01Hz

100kHz

(c) VGoffset=5V 図4.2 ID-VG特性の掃引中心電圧依存性第

5章 解析

5.1 AC 特性の等価回路モデル 第4 章で得られた結果を解析するためには、2.5 で述べた DC 解析モデルを AC 動作に適応 させる必要がある。DC においては抵抗成分のみであるが、AC の場合は周波数成分を含むた め、図5.1 に示すように、キャパシタンスを絶縁膜と AlGaN 層それぞれに並列に接続した等 価回路モデルを用いることにする。Gate

Insulator

Diode

R

InsulatorAlGaN

2DEG

C

InsulatorC

AlGaNV

Interface 図5.1 ゲート構造の AC 解析モデル 絶縁膜/AlGaN 層界面には無数の界面準位が存在していることがわかっている。そのため、 この等価回路において、2DEG の電子を制御する実質的なゲートは絶縁膜/AlGaN 層界面と いうことになる。絶縁膜/AlGaN 層界面の電位を便宜上 VInterfaceとし、この等価回路を用い て第4 章で得られた特性の解析を行う。5.2 界面電位の周波数依存性 図5.1 の回路において、ゲート-2DEG 間に 0.01Hz のような低周波のバイアスを印加した場 合は抵抗成分が支配的となり、キャパシタンス成分は無視することができる。このためVGと VInterfaceとの間に位相差はないことからヒステリシスは現れず、VGがダイオードの ON 電圧 よりも低い場合は図5.2 に示すように VG=VInterfaceとなる。しかし、VGがダイオードのON 電圧を超えるとVInterfaceはダイオードのON 電圧で固定されるため、VGによらず一定となる。 ID-VG特性の周波数依存性の測定において、0.01Hz で VG=2V 以上で IDが一定となったのは、 AlGaN 層のダイオードが ON となったためであると考えられる。

-3

-2

-1

0

1

2

3

-3 -2 -1

0

1

2

3

4

5

6

7

V

G[V]

V

In te rf a ce[

V

]

0.01Hz

10Hz

1kHz

100kHz

図5.2 界面電位の周波数依存性 一方100kHz のような高周波のバイアスを印加した場合、キャパシタンス成分が支配的とな り、抵抗成分は見えなくなる。そのため、この場合もVGとVInterfaceとの間に位相差はなくヒ ステリシスは現れない。そして、このとき等価回路はキャパシタンスの直列接続となり、 VInterfaceは式5.1 の通り、キャパシタンスの比で決まる直線となる。 G AlGaN Insulator Insulator G AlGaN Insulator AlGaN InterfaceV

C

C

C

V

C

j

C

j

C

j

V

+

=

+

=

ω

ω

ω

1

1

1

(5.1)CAlGaNに比べ、膜厚の厚いCInsulatorはキャパシタンスが小さいため、VInterfaceは VGに比べ変 化の小さな直線となる。このため図5.2 に示すように、VInterfaceは傾きの小さな直線となる。 ID-VG特性のゲートバイアス依存性において100kHz の電流値が VGoffsetの上昇とともに増加し た特性は、VInterfaceの値の変動が小さく、かつ高速で変化するため、常にVGoffsetの値に固定さ れているように振舞うため、0.01Hz の VG=VGoffsetでの電流値を付近に固定されることが原因 であると考えられる。 10Hz のような中程度の周波数においては抵抗成分とキャパシタンス成分のどちらも無視で きないため、両成分が混在し、VGと VInterfaceの間に位相差が生じることとなる。この位相差 によりID-VG特性にヒステリシスが現れるものと考えられる。

5.3 位相差とヒステリシスの関係 前節においてVGとVInterfaceの間の位相差がヒステリシスの原因であることを述べた。ヒス テリシスと位相差の間にどのような関係が成り立つか調べるため、図5.3 に示すような回路を 用いて解析を行う。ダイオードのような非線形素子を含む場合、計算が非常に複雑になるため、 単純化のためにAlGaN 層のダイオードを抵抗 RAlGaNに置き換えて計算を行った。

R

AlGaNC

AlGaNR

InsulatorC

Insulator 図5.3 ゲート構造の簡易等価回路モデル 絶縁膜とAlGaN 層のインピーダンスはそれぞれ、 Insulator Insulator Insulator InsulatorC

R

j

R

Z

ω

+

=

1

(5.2) AlGaN AlGaN AlGaN AlGaNC

R

j

R

Z

ω

+

=

1

(5.3) と定義される。この二つのインピーダンスの直列接続として VInterfaceとその位相差∠VInterface を計算する。 (5.4) G Insulator AlGaN Insulator AlGaNj

+

=

AlGaN Insulator AlGaN Insulator AlGaN Insulator G AlGaN Insulator AlGaN InterfaceV

C

C

R

R

j

R

R

C

R

R

R

V

Z

Z

Z

V

)

(

+

+

+

+

=

ω

ω

AlGaN Insulator AlGaN Insulator AlGaN Insulator Insulator Insulator InterfaceR

R

C

C

R

R

C

R

V

+

+

−

=

∠

− −(

)

tan

tan

1ω

1ω

(5.5) 式 5.5 において∠VInterfaceが正であれば VGに対して進み位相、負であれば遅れ位相となる。 進みと遅れの境界条件を算出すると、(5.6) となり、RInsulatorCInsulatorが RAlGaNCAlGaNよりも大きいときに∠VInterfaceは正となり VInterface は VGに対して進み位相となる。逆にRInsulatorCInsulatorが RAlGaNCAlGaNよりも小さいときに∠ VInterfaceは負となりVInterfaceはVGに対して遅れ位相となる。VGを正弦波とすると、図5.4 に 示すように進み位相で時計回り、遅れ位相で反時計回りのヒステリシスループが現れる。 図5.4 位相とヒステリシスループの関係 4.1 で得られた ID-VG特性の周波数依存性において、10Hz で現れた大きなヒステリシスは 反時計回りのループであった。このことから (5.7) AlGaN AlGaN Insulator Insulator

C

R

C

R

<

という関係が成り立つ。このときキャパシタンスの値は誘電率や膜厚の関係から決まるが、抵 抗の値に比べ、大きな差が無いと考えられることから、ヒステリシスの遅れ位相を決定付けて いるのは、抵抗の関係、すなわちRInsulatorがRAlGaNより小さい、という関係であるといえる。-3

-2

-1

0

1

2

3

-5

-2.5

0

2.5

5

V

G[V]

V

Interface[V]

遅れ位相

進み位相

AlGaN r AlGaN Insulato Insulator AlGaN AlGaN Insulator AlGaN Insulator AlGaN Insulator Insulator AlGaN Insulator AlGaN Insulator AlGaN Insulator Insulator Insulator AlGaN Insulator AlGaN Insulator AlGaN Insulator Insulator InsulatorC

R

C

R

C

R

C

R

C

C

R

R

R

R

C

R

R

R

C

C

R

R

C

R

+

+

=

+

+

=

+

+

=

)

(

)

(

)

(

R

C

=

R

C

第

6章 SPICE シミュレーション

6.1 SPICE シミュレーションについて

今回、第5 章で示した等価回路モデルの動作解析に SPICE(Simulation Program with Integrated Circuit Emphasis)を用いた。SPICE とは、1970年代にアメリカ合衆国のカ リフォルニア大学バークレー校で開発された電子回路シミュレーションプログラムである。基 板上に実際に回路を作らなくても回路図をパソコンに入力することで、その回路動作をパソコ ン内で計算し、特性の解析を行うことができる。また、SPICE には各種電子部品のモデルが 搭載されており、これらのモデルのパラメータを変更することによって自分で部品を作成する ことも可能である。SPICE ソフトは多数存在するが、今回は、Spectrum Software の Micro-Cap8 Evaluation を使用した。

Micro-Cap8 Evaluation に限らず、一般的に SPICEには未だ窒化ガリウム系デバイスのモ デルは搭載されていない。そのため、AlGaN/GaN MIS-HFET の特性を解析するためには既 存のデバイスのパラメータを変更し、新たなモデルを作る必要がある。今回はn 型 MOS-FET のモデルの各種パラメータを変更することでAlGaN/GaN HFET として用いた。

6.2 シミュレーション回路 第5 章での解析を実証するために、今回、ゲート構造を図 6.1 に示すような回路で表した。 ゲート絶縁膜を抵抗とキャパシタンスの並列接続で表現し、AlGaN 層をダイオードと MOSFET で表現した。第 5 章では AlGaN 層はダイオードとキャパシタンスで表して解析を 行ったが、今回はID-VG特性の解析を行うために、HFET として動作する素子が必要となるた めMOSFET とした。

Gate

Insulator

AlGaN

2DEG

C

InsulatorR

Insulator 図6.1 ゲート構造の等価回路 シミュレーションでは図6.1 の回路を並列に 8 個接続し、分布定数回路としてより正確なシ ミュレーションを目指した。図6.2 にシミュレーション回路を示す。 測定と同じくドレイン-ソース間に DC 電源により VD=1V を印加している。ゲート-ソース 間には AC 電源を接続し、印加電圧周波数、振幅(Vpp)、振幅中心電圧(Voffset)を設定し、 各測定のシミュレーションを行う。また回路には図に示すように、電流検出用の抵抗(R=1mΩ) と寄生抵抗(R=50Ω)を挿入している。また、MOSFET と Diode のパラメータは表 6.1 に示 すような値を用い、絶縁膜の抵抗RInsulatorとキャパシタンスCInsulatorの値は、RInsulator=4E10、 CInsulator=1E-14 とした。電流検出用抵抗

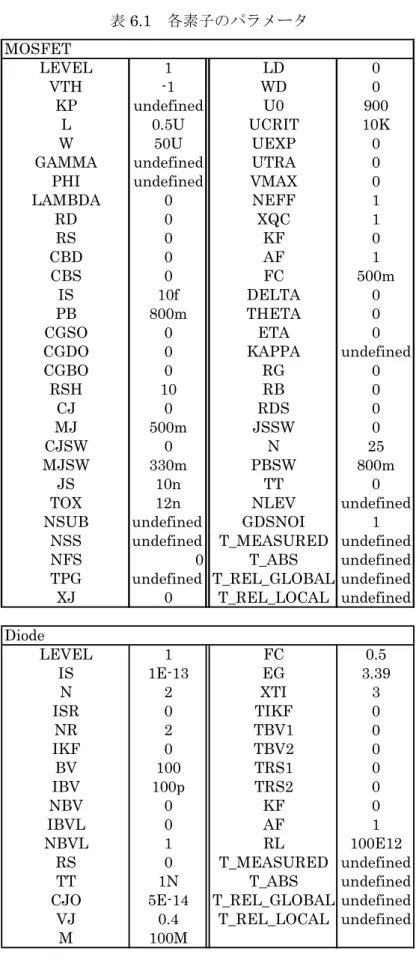

表6.1 各素子のパラメータ LEVEL 1 LD 0 VTH -1 WD 0 KP undefined U0 900 L 0.5U UCRIT 10K W 50U UEXP 0

GAMMA undefined UTRA 0 PHI undefined VMAX 0

LAMBDA 0 NEFF 1 RD 0 XQC 1 RS 0 KF 0 CBD 0 AF 1 CBS 0 FC 500m IS 10f DELTA 0 PB 800m THETA 0 CGSO 0 ETA 0

CGDO 0 KAPPA undefined

CGBO 0 RG 0 RSH 10 RB 0 CJ 0 RDS 0 MJ 500m JSSW 0 CJSW 0 N 25 MJSW 330m PBSW 800m JS 10n TT 0

TOX 12n NLEV undefined NSUB undefined GDSNOI 1

NSS undefined T_MEASURED undefined NFS 0 T_ABS undefined TPG undefined T_REL_GLOBAL undefined XJ 0 T_REL_LOCAL undefined LEVEL 1 FC 0.5 IS 1E-13 EG 3.39 N 2 XTI ISR 0 TIKF 0 NR 2 TBV1 0 IKF 0 TBV2 0 B 3 V 100 TRS1 0 IBV 100p TRS2 0 NBV 0 KF 0 IBVL 0 AF 1 NBVL 1 RL 100E12 RS 0 T_MEASURED undefined TT 1N T_ABS undefined CJO 5E-14 T_REL_GLOBAL undefined VJ 0.4 T_REL_LOCAL undefined

M 100M MOSFET

6.3 シミュレーション結果 図6.2 に示した回路において ID-VG特性の周波数依存性、ID-VG特性のゲートバイアス依存 性のシミュレーションを行った。それぞれのシミュレーション結果を以下に示す 6.3.1 ID-VG特性の周波数依存性 ゲート電圧を振幅VGpp=10V、振幅中心電圧 VGoffset=2V の正弦波信号とし、その周波数 を0.01Hz から 100kHz まで変化させて、ID-VG特性の周波数依存性のシミュレーションを 行った。その結果を図6.3 に示す。4.1 の実験で得られた結果と同様、低周波では VGが約 2V 以上で IDが一定となり、高周波ではVGの値に関わらず、IDはほぼ一定の値となった。 また、中間の周波数では反時計回りの大きなヒステリシスループが得られるなど、ヒステリ シスのループの方向も含め、測定結果を非常によく再現している。

0

0.5

1

1.5

2

2.5

-4

-2

0

2

4

6

8

V

G[V]

I

D[

mA

]

0.01Hz

10Hz

1kHz

100kHz

図6.3 ID-VG特性の周波数依存性のシミュレーション結果6.3.2 ID-VG特性の掃引中心電圧依存性 ゲート電圧を振幅VGpp=10V の正弦波とし、中心電圧 VGoffsetを-5V から 5V まで変化さ せて ID-VG 特性のシミュレーションを行った。正弦波の周波数は測定と同様、0.01Hz と 100kHz である。そのシミュレーション結果を図 6.4 に示す。 測定結果と同様に、低周波特性には変化がなく、高周波においては VGoffsetが-5V の時に はIDは流れないが、VGoffsetを上げていくとそれに伴いIDも増加した。VG=VGoffsetの電圧で は低周波と高周波に IDの差はなく、高周波ではその電流値を中心に変動していることがわ かる。そのためVGoffsetがダイオードのON 電圧以上になったときには VGoffsetに関わらずID は一定となった。掃引中心電圧依存性に関しても、ダイオードを用いた等価回路で、非常よ く再現することができた。

0

0.5

1

1.5

2

2.5

-10

-8

-6

-4

-2

0

V

G[V]

I

D[

mA]

0.01Hz

100kHz

(a) VGoffset=-5V0

0.5

1

1.5

2

2.5

-5

-3

-1

1

3

5

V

G[V]

I

D[

mA

]

0.01Hz

100kHz

(b) VGoffset=0V0

0.5

1

1.5

2

2.5

0

2

4

6

8

1

V

G[V]

I

D[

mA

]

0

0.01Hz

100kHz

(c) VGoffset=5V 図6.4 ID-VG特性の掃引中心電圧依存性のシミュレーション結果第

7章 本研究のまとめ

今回、MIS-HFET における交流動作時のヒステリシス特性を解析するため、周波数可変カー ブトレーサを用いてID-VG特性の測定を行った。ID-VG特性において VGの掃引周波数を変化さ せると、低周波においては、VGの増加とともにIDは増加するが、VGが2V を超えると IDが一 定となるという結果が得られ、かつヒステリシスは小さいという結果が得られた。また、高周波 においては、ヒステリシスは無いもののIDはVGによらずほぼ一定の値となった。そして中間の 周波数において反時計回りのループを描く大きなヒステリシスが観測された。 またVG掃引の中心電圧を変化させると、周波数によって特性に変化がみられた。低周波では 中心電圧を変化させても特性に変化はみられないが、高周波では、中心電圧が増加すると IDも 増加するという結果が得られた。 これらの特性に対してダイオードを用いた等価回路による解析を行った結果、ヒステリシスは ゲート電圧と絶縁膜/AlGaN 層界面の電位との間の位相差により引き起こされており、今回の 測定からは、ヒステリシスループを決定付けているのは絶縁膜の抵抗値であることがわかった。 また高周波での中心電圧の変化による特性変化も同等価回路を用いて説明することができた。 これらの結果から、ワイドバンドギャップ材料においては絶縁膜の特性がデバイス特性に影響 を与えかねないことがわかった。そのため、ワイドバンドギャップ材料を用いてデバイスを作製 する際には、絶縁膜の特性に注意を払う必要があるだろう。謝辞

本研究の遂行にあたって、終始懇切な御指導と御鞭撻を頂きました徳島大学工学部電気電子工 学科 大野泰夫 教授に心より感謝の意を表します。 本研究を進めるにあたり、多大なる御指導と丁寧なご教示を頂きました徳島大学工学部電気電 子工学科 助手 敖金平 先生に深く感謝します。 適切な御指導とご教示を賜りました酒井士郎 教授、富永喜久雄 助教授、直井美貴 助教授、西 野克志 助教授に深く感謝します。 本研究を進めるにあたり、実験装置等についてご尽力を賜りました技術職員 稲岡武氏、桑原 明神氏、山中卓也氏に深く感謝いたします。 有益な助言、的確な御指導と御助言を頂きました博士研究員 Xin Wei 氏、D3 菊田大悟氏、 D1 岡田政也氏、M2 高木亮平氏ならびに大野研究室、酒井研究室、サテライトベンチャービジ ネスラボラトリー、ナイトライドセミコンダクター株式会社の皆様に心より感謝いたします。参考文献

[1] Daigo Kikuta, Ryohei Takaki, Junya Matsuda, Masaya Okada, Xin Wei, Jin-Ping Ao and Yasuo Ohno, “ Gate Leakage Reduction Mechanism of AlGaN/GaN MIS-HFETs ” Extended Abstracts of the International Conference on Solid State Device and Materials, Tokyo, pp. 266-267, September 2005

[2] Daigo Kikuta, Jin-Ping Ao, Junya Matsuda and Yasuo Ohno, “ A Mechanism of Enhancement-mode Operation of AlGaN/GaN MIS-HFET” Abstract of 6th Topical Workshop on Heterostructure Microelectronics, Hyogo, pp. 72-73,August 2005