7

シ リ ーズ

FPGA

メ モ リ

リ ソ ース

ユーザー

ガ イ ド

UG473 (v1.11) 2014 年 11 月 12 日本資料は表記のバージョンの英語版を翻訳したもので、内容に相違が生じる場合には原文を優先しま

す。資料によっては英語版の更新に対応していないものがあります。日本語版は参考用としてご使用の

上、最新情報につきましては、必ず最新英語版をご参照ください。

DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx’s limited warranty, please refer to Xilinx’s Terms of Sale which can be viewed at

http://www.xilinx.com/legal.htm#tos; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx’s Terms of Sale which can be viewed at http://www.xilinx.com/legal.htm#tos.

AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

© Copyright 2011–2014 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries.

本資料は英語版 (v1.11) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。 日本語版は参考用 と し て ご使用の上、 最新情報につ き ま し ては、 必ず最新英語版を ご参照 く だ さ い。 こ の資料に関す る フ ィ ー ド バ ッ ク お よ び リ ン ク な ど の問題につ き ま し ては、jpn_trans_feedback@xilinx.comま でお知 ら せ く だ さ い。 いただ き ま し た ご意見を参考に早急に対応 さ せていただ き ます。 なお、 こ の メ ールア ド レ スへのお問い合わせは受け 付けてお り ません。 あ ら か じ めご了承 く だ さ い。

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。

日付 バージ ョ ン 内容

2011 年 3 月 1 日 1.0 初版

2011 年 3 月 28 日 1.1 2ページの免責条項 と 著作権表示を更新。

表2-1の値、表2-3の記述、表2-4の値を更新。「ALMOST EMPTY フ ラ グ」、「FULL

フ ラ グ」、「ALMOST FULL フ ラ グ」の説明を変更。表2-7と表2-8の値を更新。図2-6

を変更。59ページの ク ロ ッ ク イ ベン ト 2 と ク ロ ッ ク イ ベン ト 4 の説明を変更。「ケー ス 3 : フルの FIFO か ら の読み出 し 」 を図2-8を含め更新。

2011 年 4 月 14 日 1.2 「7シ リ ーズ FPGA と 前世代の FPGA のブ ロ ッ ク RAM お よ び FIFO の相違点」 を追

加。表1-2 : 「7 シ リ ーズデバ イ ス のブ ロ ッ ク RAM リ ソ ース」 を追加。「読み出 し 幅

- READ_WIDTH_[A|B]」 お よ び 「書 き 込み幅 - WRITE_WIDTH_[A|B]」 の有効な 値を明記。「ブ ロ ッ ク RAM の ロ ケーシ ョ ン制約」 の例を 更新。表1-18のパ ラ メ ー タ ー名を更新。

「同期 FIFO」の概要で フ ラ グの動作を明記。「FIFO ALMOST FULL/EMPTY フ ラ グ

のオ フ セ ッ ト 範囲」 の変更、表2-8の注記1の追加、 式 2-1 の削除、 式 2-2 を変更 し て新たに式2-1と し て更新。 「WEBWE[7:0]」 のポー ト 接続の指示を更新。 2011 年 10 月 18 日 1.3 「ス タ ッ ク ド シ リ コ ン イ ン タ ー コ ネ ク ト (SSI)」 を追加。表1-2に Artix-7 お よ び Virtex-7 フ ァ ミ リ を追加 し 、 注記を更新。 2011 年 11 月 18 日 1.4 「Virtex-6 FPGA か ら の変更点」 の 2 番目の箇条書 き を更新。

2012 年 1 月 30 日 1.5 表1-2で、XC7A8、XC7A15、XC7A30T、 お よ び XC7A50T を削除、XC7K420T お よ び XC7VX550T のデバ イ ス あ た り の 36Kb ブ ロ ッ ク RAM の数を更新、 注記 1 で 「GTP/GTX ク ワ ッ ド 」 に変更。

「Simple Dual-Port (SDP) ブ ロ ッ ク RAM」 を更新。

2012 年 7 月 4 日 1.6 「Virtex-6 FPGA か ら の変更点」 の 5 番目 と 6 番目箇条書 き を更新。

表1-2に Virtex-7デバ イ ス を追加。表1-6の RAMB36E1、RAMB18E1、 お よ び FIFO18E1 の説明を更新。 表2-3の WREN の説明を更新。表2-9の TRCCK_RST/TRCKC_RSTを TRREC_RST/ TRREM_RSTに置 き 換え。 2012 年 10 月 2 日 1.7 表1-2か ら XC7A350T、XC7V1500T、 お よ び XC7VH290T を削除。 2013 年 8 月 7 日 1.8 表1-2に 3 つのデバ イ ス を追加。 2013 年 10 月 2 日 1.9 2ページの免責条項 と 著作権表示を更新。「バ イ ト ラ イ ト イ ネーブル」 を更新。 2014 年 1 月 30 日 1.10 「概要」 の最後の箇条書 き を更新。図1-6お よ び図3-2を更新。 2014 年 5 月 9 日 1.10.1 表1-7お よ び表1-8の誤植を訂正。 2014 年 11 月 12 日 1.11 表1-2に XC7A15T デバ イ ス を追加。

改訂履歴. . . 3

このユーザー

ガ イ ド について

内容 . . . 97シ リ ーズ FPGA と 前世代の FPGA のブ ロ ッ ク RAM お よ び FIFO の相違点. . . 9

Virtex-6 FPGA か ら の変更点 . . . .9 Spartan-6 FPGA か ら の変更点 . . . .10 その他の リ ソ ース . . . 10

第

1

章

:

ブ ロ ッ ク

RAM

リ ソ ース

概要 . . . 11 ブ ロ ッ ク RAM の説明. . . 13 同期デ ュ アルポー ト お よ びシ ン グルポー ト RAM . . . 15 デー タ フ ロ ー. . . .15 読み出 し. . . .16 書 き 込み. . . .16 書 き 込みモー ド . . . .16 WRITE_FIRST ま たは透過モー ド (デフ ォ ル ト) . . . .17 READ_FIRST ま たは書 き 込み前読み出 し モー ド . . . .17 NO_CHANGE モー ド. . . .17 競合の回避 . . . .18 非同期 ク ロ ッ ク . . . .18 同期 ク ロ ッ ク . . . .18 7シ リ ーズデバ イ ス のブ ロ ッ ク RAM のその他の機能. . . 19 出力レ ジ ス タ (オプシ ョ ン) . . . .19 個別に選択可能な読み出 し ポー ト と 書 き 込みポー ト の幅. . . .19Simple Dual-Port (SDP) ブ ロ ッ ク RAM . . . .19

カ ス ケー ド 接続が可能なブ ロ ッ ク RAM . . . .21 バ イ ト ラ イ ト イ ネーブル . . . .21 ブ ロ ッ ク RAM の ECC (誤 り 訂正符号) . . . .22 未使用ブ ロ ッ ク RAM のパ ワ ーゲーテ ィ ン グ . . . .22 ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ. . . 23 ブ ロ ッ ク RAM のポー ト 信号 . . . 26 ク ロ ッ ク - CLKARDCLK、CLKBWRCLK . . . .26 イ ネーブル - ENARDEN、ENBWREN . . . .27 バ イ ト ラ イ ト イ ネーブル - WEA、WEBWE . . . .27

レ ジ ス タ イ ネーブル - REGCEA、REGCE、REGCEB . . . .27

セ ッ ト/リ セ ッ ト . . . .27

RSTREGARSTREG、RSTREGB、RSTRAMARSTRAM、RSTRAMB . . . .27

ア ド レ スバ ス - ADDRARDADDR、ADDRBWRADDR . . . .27

デー タ 入力バス - DIADI、DIPADIP、DIBDI、DIPBDIP . . . .29

デー タ 出力バス - DOADO、DOPADOP、DOBDO、DOPBDOP . . . .29

カ ス ケー ド 入力 . . . .30

CASCADEINA、CASCADEINB、CASCADEOUTA、CASCADEOUTB . . . .30

制御ピ ンの反転 . . . .30 GSR . . . .30 未使用の入力 . . . .30 ブ ロ ッ ク RAM のア ド レ スマ ッ プ. . . 31 ブ ロ ッ ク RAM の属性. . . 31 メ モ リ 内容の初期化 - INIT_xx . . . .31

目次

リ セ ッ ト ま たは CE の優先度 - RSTREG_PRIORITY_[A|B] . . . .33 オプシ ョ ンの出力レ ジ ス タ 切 り 替え - DO[A|B]_REG . . . .33 拡張モー ド ア ド レ ス - RAM_EXTENSION_[A|B] . . . .34 読み出 し 幅 - READ_WIDTH_[A|B] . . . .34 書 き 込み幅 - WRITE_WIDTH_[A|B] . . . .34 モー ド 選択 - RAM_MODE . . . .34 書 き 込みモー ド - WRITE_MODE_[A|B] . . . .34 RDADDR_COLLISION_HWCONFIG . . . .34 SIM_COLLISION_CHECK . . . .34 INIT_FILE . . . .35 SIM_DEVICE . . . .35 ブ ロ ッ ク RAM の ロ ケーシ ョ ン制約. . . 35 VHDL ま たは Verilog コ ー ド でのブ ロ ッ ク RAM の初期化. . . 35 RAMB18E1 お よ び RAMB36E1 プ リ ミ テ ィ ブの設計上のその他の注意事項 . . . 35 出力レ ジ ス タ (オプシ ョ ン) . . . .35 独立 し た読み出 し ポー ト と 書 き 込みポー ト の幅を選択. . . .36 RAMB18E1 お よ び RAMB36E1 のポー ト マ ッ ピ ン グ設計規則. . . .36 カ ス ケー ド 接続可能なブ ロ ッ ク RAM . . . .36 バ イ ト ラ イ ト イ ネーブル . . . .37 ブ ロ ッ ク RAM のアプ リ ケーシ ョ ン. . . 38 大規模な RAM 構造の作成 . . . .38 レ ジ ス タ モー ド でのブ ロ ッ ク RAM の RSTREG . . . .38 ブ ロ ッ ク RAM の タ イ ミ ン グモデル . . . 40 ブ ロ ッ ク RAM の タ イ ミ ン グパ ラ メ ー タ ー . . . .40 ブ ロ ッ ク RAM の タ イ ミ ン グ特性. . . .41 ク ロ ッ ク イ ベン ト 1 . . . .41 ク ロ ッ ク イ ベン ト 2 . . . .42 ク ロ ッ ク イ ベン ト 4 . . . .42 ク ロ ッ ク イ ベン ト 5 . . . .42 ブ ロ ッ ク RAM の タ イ ミ ン グモデル. . . .42 ス タ ッ ク ド シ リ コ ン イ ン タ ー コ ネ ク ト (SSI) . . . 43

第

2

章

:

ビル ト イ ン

FIFO

のサポー ト

概要 . . . 45 デ ュ アルク ロ ッ ク FIFO . . . 45 同期 FIFO . . . 46 同期 FIFO イ ンプ リ メ ン テーシ ョ ン . . . .47 FIFO アーキ テ ク チ ャ の概略図. . . 48 FIFO プ リ ミ テ ィ ブ . . . 48 FIFO ポー ト の説明 . . . 49 FIFO の動作. . . 51 リ セ ッ ト . . . .51 動作モー ド . . . .51 標準モー ド. . . .51FWFT (First Word Fall Through) モー ド . . . .51

ス テー タ ス フ ラ グ . . . .51 EMPTY フ ラ グ . . . .52 ALMOST EMPTY フ ラ グ . . . .52 READ ERROR フ ラ グ . . . .52 FULL フ ラ グ. . . .53 WRITE ERROR フ ラ グ . . . .53 ALMOST FULL フ ラ グ . . . .53 FIFO の属性. . . 53

VHDL お よ び Verilog の FIFO テ ンプ レー ト . . . 56 FIFO の タ イ ミ ン グモデル と パ ラ メ ー タ ー . . . 56 FIFO の タ イ ミ ン グ特性. . . .58 ケース 1 : 空の FIFO への書 き 込み. . . .58 ケース 2 : フルま たはほぼフルの FIFO への書 き 込み. . . .60 ケース 3 : フルの FIFO か ら の読み出 し. . . .61 ケース 4 : 空ま たはほぼ空の FIFO か ら の読み出 し. . . .62 ケース 5 : すべての フ ラ グ を リ セ ッ ト. . . .64 ケース 6 : デ ュ アル ク ロ ッ ク FIFO に対す る 読み出 し と 書 き 込みの同時実行 . . . .64 FIFO のアプ リ ケーシ ョ ン. . . 65 FIFO のカ ス ケー ド 接続に よ る ワー ド 数の拡張. . . .65 FIFO の並列接続に よ る ビ ッ ト 数の拡張 . . . .66 ブ ロ ッ ク RAM と FIFO の有効な組み合わせ . . . 67

第

3

章

:

ビル ト イ ン誤 り 訂正

概要 . . . 69 ECC の動作モー ド. . . 70 ブ ロ ッ ク RAM ECC アーキ テ ク チ ャ の概略図. . . 71ブ ロ ッ ク RAM お よ び FIFO ECC プ リ ミ テ ィ ブ . . . .72

ブ ロ ッ ク RAM お よ び FIFO ECC のポー ト. . . 73

ブ ロ ッ ク RAM お よ び FIFO ECC の属性 . . . 76

ECC モー ド の動作. . . 77 標準モー ド の ECC . . . .80 属性での設定 . . . .80 標準 ECC 書 き 込み . . . .80 標準 ECC 読み出 し . . . .80 エン コ ー ド 専用 ECC . . . .81 属性での設定 . . . .81 エン コ ー ド 専用 ECC での書 き 込み . . . .81 エン コ ー ド 専用 ECC での読み出 し . . . .81 デ コ ー ド 専用 ECC . . . .82 属性での設定 . . . .82 デ コ ー ド 専用 ECC でのシ ン グルビ ッ ト エ ラ ーの挿入. . . .82 デ コ ー ド 専用 ECC でのダブルビ ッ ト エ ラ ーの挿入. . . .82 ECC タ イ ミ ン グ特性. . . 83 標準 ECC の書 き 込み タ イ ミ ン グ . . . .83 標準 ECC の読み出 し タ イ ミ ン グ . . . .83 DO_REG = 0 の場合. . . .83 DO_REG = 1 の場合. . . .84 エン コ ー ド 専用 ECC の書 き 込み タ イ ミ ン グ . . . .84 エン コ ー ド 専用 ECC の読み出 し タ イ ミ ン グ . . . .84 デ コ ー ド 専用 ECC の書 き 込み タ イ ミ ン グ . . . .84 デ コ ー ド 専用 ECC の読み出 し タ イ ミ ン グ . . . .84 ブ ロ ッ ク RAM ECC モー ド の タ イ ミ ン グパ ラ メ ー タ ー. . . 85 64 ビ ッ ト ワー ド 用 8 ビ ッ ト パ リ テ ィ の作成 . . . 86

こ のユーザー

ガ イ ド について

ザ イ リ ン ク ス 7 シ リ ーズ FPGA には、3 つの FPGA フ ァ ミ リ があ り ます。 こ れ ら はすべて最 も 低 い消費電力を達成す る よ う 設計 さ れてお り 、 最適な電力、 性能、 コ ス ト の実現に向けて、 標準デザ イ ン を フ ァ ミ リ 間で拡張 さ せ る こ と が可能です。Artix®-7 フ ァ ミ リ は、 量産アプ リ ケーシ ョ ン向け に開発 さ れ、 最 も 低い コ ス ト と 消費電力を実現す る よ う 最適化 さ れてい ま す。Virtex®-7 フ ァ ミ リ は、 最高のシ ス テ ム性能 と 容量を提供す る よ う に最適化 さ れてい ます。Kintex®-7 フ ァ ミ リ は、 対 コ ス ト 性能に最 も 優れた新 し い ク ラ ス の FPGA です。 こ のユーザーガ イ ド は、7 シ リ ーズ FPGA のブ ロ ッ ク RAM について説明 し た技術的な リ フ ァ レ ン ス です。 ブ ロ ッ ク RAM は、 効率的なデー タ の格納やバ ッ フ ァ ーに活用 し 、 高性能な ス テー ト マシ ン ま たは FIFO バ ッ フ ァ ー、 大規模シ フ ト レ ジ ス タ 、 大規模なル ッ ク ア ッ プテーブル、ROM な ど に使用 さ れます。 こ の 『7 シ リ ーズ FPGA メ モ リ リ ソ ースユーザーガ イ ド 』 を含む、7 シ リ ーズ FPGA に関す る す べての資料は、 ザ イ リ ン ク ス の ウ ェ ブサ イ ト (japan.xilinx.com/support/documentation/7_series) か ら 入手で き ます。内容

こ のユーザーガ イ ド は、 次の各章で構成 さ れてい ます。 • 第 1 章 「ブ ロ ッ ク RAM リ ソ ース」 • 第 2 章 「ビル ト イ ン FIFO のサポー ト 」 • 第 3 章 「ビル ト イ ン誤 り 訂正」7

シ リ ーズ

FPGA

と 前世代の

FPGA

のブ ロ ッ ク

RAM

および

FIFO

の

相違点

Virtex-6 FPGA

か らの変更点

• 競合の回避 と ア ド レ ス の衝突の規則が緩和 さ れま し た。 • SDP モー ド の WRITE_FIRST モー ド は、消費電力を抑え る ために自動的に NO_CHANGE モー ド にマ ッ ピ ン グ さ れます。 • ブ ロ ッ ク RAM の内容の初期化お よ び リ ー ド バ ッ ク 動作が、新 し いパ ワーゲーテ ィ ン グ機能の イ ンプ リ メ ン テーシ ョ ンに伴い変更 さ れてい ます。 • 新 し い外部電源 VCCBRAMか ら ブ ロ ッ ク RAM メ モ リ セルに電力が供給 さ れます。• 7シ リ ーズ FPGA では、FIFO リ セ ッ ト の要件が簡略化 さ れてい ます。FIFO リ セ ッ ト のアサー ト が、書 き 込み ク ロ ッ ク お よ び読み出 し ク ロ ッ ク と 同期す る よ う にな り ま し た。ただ し 、 リ セ ッ ト のデ ィ アサー ト は非同期の ま ま です。

• FIFO フ ラ グのレ イ テンシは全体的に Virtex-6 FPGA でのレ イ テンシ と 異な り ます (表2-4参照)。 • RDCLK と WRCLK が異な る場合に、7シ リ ーズ FPGA の ALMOST_FULL_OFFSET の式が変 更 さ れま し た。こ の場合、すべてのケースで表2-8の値に従 う ため、ALMOST_EMPTY_OFFSET の式は削除 さ れます。

Spartan-6 FPGA

から の変更点

• Virtex-6 フ ァ ミ リ と 同様に、7シ リ ーズ FPGA は 36Kb お よ び 18Kb の両ブ ロ ッ ク RAM コ ン フ ィ ギ ュ レーシ ョ ン をサポー ト し ます (Spartan®-6 FPGA の 18Kb/9Kb に対 し て、 ネ イ テ ィ ブ で 36Kb/18Kb)。 • Virtex-6 フ ァ ミ リ には含まれず、Virtex-6 フ ァ ミ リ で利用可能 と な っ てい る 次の主な機能が、 7シ リ ーズ FPGA の イ ンプ リ メ ン テーシ ョ ンに含まれてい ます。 • 専用の内蔵 FIFO • 誤 り 訂正機能 (ECC) • ブ ロ ッ ク RAM の直接カ ス ケー ド 接続 • 出力 ラ ッ チお よ びレ ジ ス タ の個別 リ セ ッ ト 制御 • デー タ 出力の非同期セ ッ ト/リ セ ッ ト

その他の リ ソ ース

その他の資料は、 ザ イ リ ン ク ス の ウ ェ ブサ イ ト か ら 入手で き ます。 japan.xilinx.com/support/documentation/index シ リ コ ンや ソ フ ト ウ ェ ア、IP に関す る ア ンサーデー タ ベース を検索 し た り 、 テ ク ニ カルサポー ト の ウ ェ ブケース を開 く 場合は、 次の ウ ェ ブサ イ ト にア ク セ ス し て く だ さ い。 japan.xilinx.com/support第

1

章

ブ ロ ッ ク

RAM

リ ソ ース

概要

7シ リ ーズ FPGA のブ ロ ッ ク RAM は 2 つの独立 し た 18Kb RAM ま たは 1 つの 36Kb RAM と し て構成可能で、 いずれ も 最大 36Kb のデー タ を格納で き ます。36Kb の各ブ ロ ッ ク RAM は、SDP (Simple Dual-Port) モー ド では 64Kx1 (隣接す る 36Kb ブ ロ ッ ク RAM と カ ス ケー ド 接続)、32Kx1、 16Kx2、8Kx4、4Kx9、2Kx18、1Kx36、512x72 と し て構成で き ます。18Kb の各ブ ロ ッ ク RAM は、SDP モー ド では 16Kx1、8Kx2、4Kx4、2Kx9、1Kx18、512x36 と し て構成で き ます。 Virtex®-6 FPGA のブ ロ ッ ク RAM と 同様に、 書 き 込み と 読み出 し は ク ロ ッ ク に同期 し て行われま

す。 ま た、2 つのポー ト は対称でそれぞれ完全に独立 し てお り 、 保存 し たデー タ のみを共有 し ます。 各ポー ト は、 設定可能な幅のいずれかに指定で き 、 も う 一方のポー ト か ら は独立 し てい ます。 さ ら に、1 つのポー ト の読み出 し ポー ト と 書 き 込みポー ト には別々の幅を設定可能です。 メ モ リ 内容は、 コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ームで初期化ま たは ク リ アで き ます。書 き 込み実行中のデー タ 出力は、 以前の出力を その ま ま維持す る か、 書 き 込まれてい る デー タ を出力す る か、 上書 き さ れ る 以前のデー タ を出力す る か を設定で き ます。 7シ リ ーズ FPGA のブ ロ ッ ク RAM には次の特長があ り ます。 • ブ ロ ッ ク ご と の メ モ リ 格納機能に よ り 、 各ブ ロ ッ ク RAM に最大で 36Kb のデー タ を格納で き ます。 • 2 つの独立 し た 18Kb ブ ロ ッ ク ま たは 1 つの 36Kb ブ ロ ッ ク RAM をサポー ト し ます。 • 各 36Kb ブ ロ ッ ク RAM は SDP モー ド に設定で き 、 デー タ 幅を 2 倍の 72 ビ ッ ト にで き ます。 18Kb ブ ロ ッ ク RAM も こ のモー ド に設定で き 、 デー タ 幅を 2 倍の 36 ビ ッ ト にで き ます。 こ こ で、SDP モー ド と は、 読み出 し 専用ポー ト と 書 き 込み専用ポー ト が 1 つずつあ り 、 それぞれ が独立 し た ク ロ ッ ク で動作 し てい る も の と 定義 し ます。 • SDP モー ド のブ ロ ッ ク RAM では、 一方のデー タポー ト を固定幅 と し 、 も う 一方を可変幅に で き ます。 • 2 つの隣接し たブ ロ ッ ク RAM を組み合わせる こ と で、 外部ロ ジ ッ ク を使用せずに 1 つの 64Kx1 メ モ リ を作成で き ます。

• 36Kb ブ ロ ッ ク RAM ま たは 36Kb FIFO は 64 ビ ッ ト の ECC (誤 り 訂正符号) ブ ロ ッ ク を備え てい ます。 エン コ ー ド/デ コ ー ド 機能が別々に使用可能です。ECC モー ド でエ ラ ー挿入機能が 使用で き ます。 • 初期値に対す る 、 出力の同期セ ッ ト/リ セ ッ ト は、 ブ ロ ッ ク RAM 出力の ラ ッ チお よ びレ ジ ス タ モー ド の両方で使用で き ます。 • 同期セ ッ ト ピ ン と 同期 リ セ ッ ト ピ ン を分離す る こ と に よ り 、オプシ ョ ンの出力レ ジ ス タ のセ ッ ト/リ セ ッ ト と ブ ロ ッ ク RAM の出力 ラ ッ チ段階を個別に制御で き ます。 • ブ ロ ッ ク RAM を同期 FIFO と し て構成す る と 、 フ ラ グの レ イ テ ン シは安定 し ます。

• 18、36、72 ビ ッ ト 幅のブ ロ ッ ク RAM ポー ト には、 バ イ ト ご と に個別の書 き 込み イ ネーブル を含め る こ と がで き ます。 こ れは、 マ イ ク ロ プ ロ セ ッ サ と イ ン タ ーフ ェ イ スす る 際に頻繁に使 用 さ れ る 機能です • 各ブ ロ ッ ク RAM には、 ビル ト イ ンデュ アル ク ロ ッ ク FIFO メ モ リ と し て動作する ためのア ド レ ス シーケ ン ス 処理お よ び制御回路がオプシ ョ ン で含 ま れてい ま す。7シ リ ーズ アーキ テ ク チ ャ では、FIFO は 18Kb ま たは 36Kb メ モ リ と し て構成で き ます。 • すべての入力はポー ト ク ロ ッ ク に同期 し て取 り 込ま れ、Setup-to-Clock タ イ ミ ン グ仕様に従い ます。 • すべての出力は、 書 き 込み イ ネーブル (WE) ピ ンの状態に よ っ て、 読み出 し ま たは書 き 込み中 に読み出 し にな り ます。 こ れ ら の出力は、Clock-to-Out 時間に有効にな り ます。 書 き 込み中の 読み出 し の出力には、3 つの動作モー ド 、WRITE_FIRST、READ_FIRST、NO_CHANGE が あ り ます。 • 書 き 込みには、 ク ロ ッ ク エ ッ ジが 1 つ必要です。 • 読み出 し には、 ク ロ ッ ク エ ッ ジが 1 つ必要です。 • すべての出力ポー ト は、 オプシ ョ ン で ラ ッ チ ま たはレ ジ ス タ 付 き です。 別の読み出 し/書 き 込み を実行す る ま では、 出力ポー ト の値は一定です。 デフ ォ ル ト では、 ブ ロ ッ ク RAM 出力は ラ ッ チモー ド です。 • 出力デー タ パス にはオプシ ョ ンの内部パ イ プ ラ イ ン レ ジ ス タ があ り ます。 レ ジ ス タ モー ド の 使用を強 く 推奨 し ま す。 こ れに よ り 、 高 ク ロ ッ ク レ ー ト での動作が可能にな り ま すが、1 ク ロ ッ ク サ イ ク ルの レ イ テ ン シが追加 さ れます。 7シ リ ーズのブ ロ ッ ク RAM には次の よ う な使用規則があ り ます。

• ECC デ コ ーダーの有効時 (EN_ECC_READ = TRUE)、同期セ ッ ト/リ セ ッ ト (RSTRAM) ポー ト は使用で き ません。

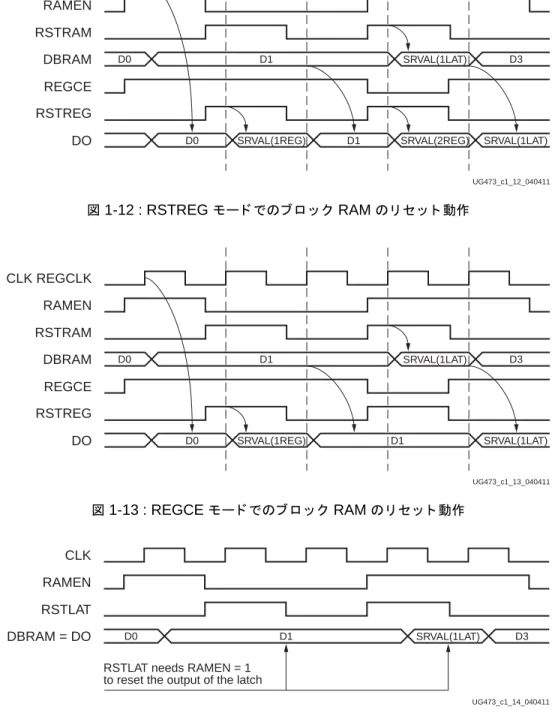

• ブ ロ ッ ク RAM の同期出力レ ジ ス タ (オプシ ョ ン) は、DO_REG = 1 の と き に RSTREG を使用 し てセ ッ ト ま たは リ セ ッ ト (SRVAL) さ れます。RSTREG と REGCE の ど ち ら が優先 さ れ る か は、RSTREG_PRIORITY 属性で指定 し ます。 同期出力 ラ ッ チは DO_REG = 0 ま たは 1 の と き に RSTRAM を使用 し てセ ッ ト ま たは リ セ ッ ト (SRVAL) さ れます。

• ブ ロ ッ ク RAM のア ド レ ス ピ ンお よ び書 き 込み イ ネーブル ピ ンのセ ッ ト ア ッ プタ イ ムは違反 し ない よ う に し ます。ア ド レ スセ ッ ト ア ッ プタ イ ムに違反す る と 、書 き 込み イ ネーブルが Low であ っ て も 、 ブ ロ ッ ク RAM のデー タ 内容が破損 し ます。

• ブ ロ ッ ク RAM の レ ジ ス タモー ド が RSTREG で、RSTREG_PRIORITY = REGCE の場合、 出力 DO レ ジ ス タ 値を リ セ ッ ト す る には、REGCE = 1 と す る 必要があ り ます。 こ のモー ド で は、 ブ ロ ッ ク RAM ア レ イ デー タ 出力 ラ ッ チは リ セ ッ ト さ れません。 ブ ロ ッ ク RAM の ラ ッ チ モー ド SRTRAM の場合、 出力 DO ラ ッ チ値を リ セ ッ ト す る にはブ ロ ッ ク RAM は イ ネーブル (EN = 1) にな っ てい る 必要があ り ます。

• ブ ロ ッ ク RAM プ リ ミ テ ィ ブには RAMB36E1 と RAMB18E1 の 2 つがあ り ます。 ブ ロ ッ ク RAM のモー ド は、RAM_MODE 属性で SDP モー ド ま たは TDP (True Dual-Port) モー ド のい ずれかに設定 し ます。 • 特定のブ ロ ッ ク RAM プ リ ミ テ ィ ブ を使用す る と 、 読み出 し お よ び書 き 込みポー ト に異な る 幅 が選択可能です。 パ リ テ ィ ビ ッ ト はポー ト 幅が x9、x18、x36 の場合のみ利用で き ます。 読み 出 し 幅が x1、x2、x4 の と き は使用 し ないで く だ さ い。 読み出 し 幅が x1、x2、 ま たは x4 の場 合、 有効な書 き 込み幅は x1、x2、x4、x8、x16、x32 です。 同様に、 書 き 込み幅が x1、x2、 ま たは x4 の場合、 プ リ ミ テ ィ ブの属性は 1、2、4、9、18、 あ る いは 36 に設定 さ れますが、 実 際に使用可能な読み出 し 幅はそれぞれ x1、x2、x4、x8、x16、 ま たは x32 と な り ます。表1-1 に、 ポー ト 幅の組み合わせを示 し ます。

ブ ロ ッ ク RAM の説明

• RAMB36E1 の A15 ピ ンは、 カ ス ケー ド 接続にのみ使用 し て く だ さ い。 それ以外では、A15 ピ ンは接続 し ないか、High に固定 し て く だ さ い。 • 非同期 リ セ ッ ト に よ っ て EN 信号が非同期にアサー ト ま たはデ ィ アサー ト さ れ る と 、EN 信号 のセ ッ ト ア ッ プ/ホール ド タ イ ム違反 と な る こ と があ り ます。 その場合、 最初の読み出 し ま た は書 き 込み動作の結果が想定 し た値にな り ません。EN の非同期のアサー ト ま たはデ ィ アサー ト が回避で き ない場合、 非同期の RESET の ア サー ト お よ びデ ィ ア サー ト 中は EN のデ ィ ア サー ト を維持す る か、EN がアサー ト さ れてか ら 有効なデー タサ イ ク ルが発生す る ま で読み出 し サ イ ク ルま たは書 き 込みサ イ ク ルを挿入 し ます。PLL 信号ま たは MMCM LOCKED 信号が 失われ る か、 フ リ ー ラ ン ニ ン グ ク ロ ッ ク が停止 し た場合、 直ちに EN をデ ィ アサー ト し ます。

ブ ロ ッ ク

RAM

の説明

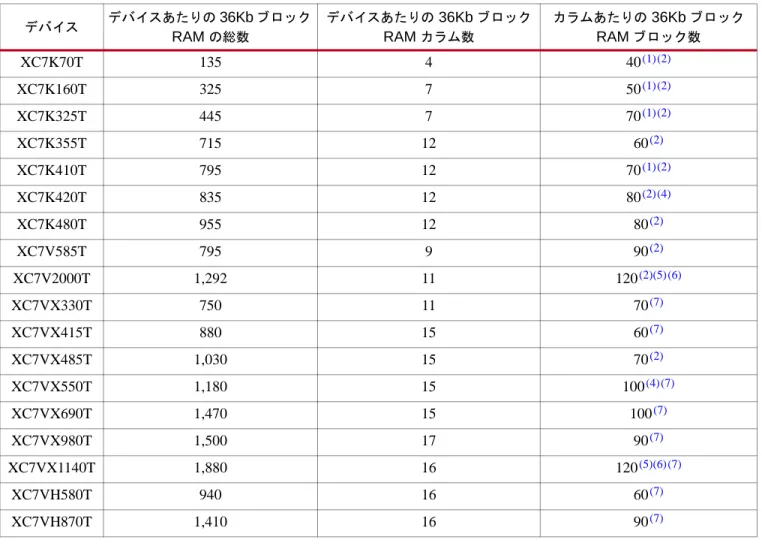

7シ リ ーズデバ イ ス には、 分散 RAM メ モ リ お よ び高速 SelectIO™ メ モ リ イ ン タ ーフ ェ イ ス だけ でな く 、 多数の 36Kb ブ ロ ッ ク RAM が備わっ てい ます。 各 36Kb ブ ロ ッ ク RAM には、 独立 し て 制御 さ れ る 2 つの 18Kb RAM があ り ます。 ブ ロ ッ ク RAM はカ ラ ムに配置 さ れ、 ブ ロ ッ ク RAM リ ソ ース の総数は 7シ リ ーズデバ イ ス に よ っ て異な り ます (表1-2参照)。6Kb ブ ロ ッ ク を カ ス ケー ド 接続す る と 、 タ イ ミ ン グ遅延を最小限に抑えて、 ビ ッ ト 数 と ワー ド 数の多い メ モ リ を イ ンプ リ メ ン ト で き ます。 表 1-1 : パ リ テ ィ ビ ッ ト の使用法 プ リ ミ テ ィ ブ 設定 有効な読み出 し 幅 有効な書き込み幅 読み出 し 幅 書き込み幅 RAMB18E1 1、2、4 9、18 設定幅 と 同一 8、16 RAMB18E1 9、18 1、2、4 8、16 設定幅 と 同一 RAMB18E1 1、2、4 1、2、4 設定幅 と 同一 設定幅 と 同一 RAMB18E1 9、18 9、18 設定幅 と 同一 設定幅 と 同一 RAMB36E1 1、2、4 9、18、36 設定幅 と 同一 8、16、32 RAMB36E1 9、18、36 1、2、4 8、16、32 設定幅 と 同一 RAMB36E1 1、2、4 1、2、4 設定幅 と 同一 設定幅 と 同一 RAMB36E1 9、18、36 9、18、36 設定幅 と 同一 設定幅 と 同一 注記 : 1. 一方のポー ト 幅が 9 よ り 小 さ く 、 も う 一方が 9 以上の場合、 パ リ テ ィ ビ ッ ト DIP/DOP は使用 し ないで く だ さ い。 表 1-2 : 7 シ リ ーズデバイ スのブ ロ ッ ク RAM リ ソ ース デバイ ス デバイ スあた り の 36Kb ブ ロ ッ ク RAM の総数 デバイ スあた り の 36Kb ブ ロ ッ ク RAM カ ラ ム数 カ ラ ムあた り の 36Kb ブ ロ ッ ク RAM ブ ロ ッ ク 数 XC7A15T 25 3 30(1)(2)(4) XC7A35T 50 3 30(1)(2)(4) XC7A50T 75 3 30(1)(2) XC7A75T 105 4 40(1)(2)(4) XC7A100T 135 4 40(1)(2)デ ュ アルポー ト ま たはシ ン グルポー ト のエンベデ ッ ド RAM モジ ュ ール、ROM モジ ュ ール、 同期 FIFO、 デー タ 幅 コ ンバー タ ーは、CORE Generator™ のブ ロ ッ ク メ モ リ モジ ュ ールを使用 し て イ ンプ リ メ ン ト で き ます。デ ュ アルク ロ ッ ク FIFO は、CORE Generator の FIFO Generator モジ ュ ー ルを使用 し て作成で き ます。 同期ま たは非同期 (デ ュ アル ク ロ ッ ク) FIFO の イ ン プ リ メ ン ト には、 専用のハー ド ウ ェ ア リ ソ ー ス が使用 さ れ る ため、FIFO 制御 ロ ジ ッ ク に追加の CLB リ ソ ース を使 用す る 必要はあ り ません。 XC7K70T 135 4 40(1)(2) XC7K160T 325 7 50(1)(2) XC7K325T 445 7 70(1)(2) XC7K355T 715 12 60(2) XC7K410T 795 12 70(1)(2) XC7K420T 835 12 80(2)(4) XC7K480T 955 12 80(2) XC7V585T 795 9 90(2) XC7V2000T 1,292 11 120(2)(5)(6) XC7VX330T 750 11 70(7) XC7VX415T 880 15 60(7) XC7VX485T 1,030 15 70(2) XC7VX550T 1,180 15 100(4)(7) XC7VX690T 1,470 15 100(7) XC7VX980T 1,500 17 90(7) XC7VX1140T 1,880 16 120(5)(6)(7) XC7VH580T 940 16 60(7) XC7VH870T 1,410 16 90(7) 注記 : 1. (デバ イ ス の) 右側のカ ラ ムには複数の GTP/GTX ク ワ ッ ド があ り 、 こ のカ ラ ムの各 GTP/GTX は 10 のブ ロ ッ ク RAM ブ ロ ッ ク を占有 し ます。

2. カ ラ ムには PCI Express®用 Gen1/Gen2 イ ン タ ーフ ェ イ スブ ロ ッ ク が複数あ り 、 各 イ ン タ ーフ ェ イ スブ ロ ッ ク は 5 つのブ ロ ッ ク RAM

ブ ロ ッ ク を占有 し ます。 ブ ロ ッ ク RAM ブ ロ ッ ク は、 複数の PCI Express 用 イ ン タ ーフ ェ イ スブ ロ ッ ク に ま たがっ て カ ス ケー ド 接続で き ません。

3. 中央に位置す る 4 つのブ ロ ッ ク RAM カ ラ ムには複数の GTP ク ワ ッ ド があ り 、 こ れ ら のカ ラ ムの各 GTP ク ワ ッ ド は 10 のブ ロ ッ ク

RAM ブ ロ ッ ク を占有 し ます。

4. ブ ロ ッ ク RAM ブ ロ ッ ク の総数はツールで制限 さ れます。

5. デバ イ ス の左側にあ る ブ ロ ッ ク RAM カ ラ ムでは、SLR (Super Logic Region) あ た り のブ ロ ッ ク RAM ブ ロ ッ ク の数が 2 つ少な く な っ て い ます。

6. 各 SLR にはカ ラ ム あ た り 30 の 36Kb ブ ロ ッ ク RAM ブ ロ ッ ク があ り ます。

7. カ ラ ムには PCI Express 用 Gen3 イ ン タ ーフ ェ イ スブ ロ ッ ク が複数あ り 、各 イ ン ターフ ェ イ スブ ロ ッ ク は 10 個のブ ロ ッ ク RAM ブ ロ ッ ク を占有 し ます。 ブ ロ ッ ク RAM ブ ロ ッ ク は、 複数の PCI Express 用 イ ン ターフ ェ イ スブ ロ ッ ク に ま たがっ て カ ス ケー ド 接続で き ません。

表 1-2 : 7 シ リ ーズデバイ スのブ ロ ッ ク RAM リ ソ ース (続き) デバイ ス デバイ スあた り の 36Kb ブ ロ ッ ク RAM の総数 デバイ スあた り の 36Kb ブ ロ ッ ク RAM カ ラ ム数 カ ラ ムあた り の 36Kb ブ ロ ッ ク RAM ブ ロ ッ ク 数

同期デ ュ アルポー ト お よびシ ングルポー ト RAM

同期デ ュ アル

ポー ト およびシ ン グル

ポー ト

RAM

デー タ

フ ロー

36Kb の TDP ブ ロ ッ ク RAM は、36Kb の記憶領域 と 完全に独立 し た 2 つのア ク セ スポー ト (A お よ び B) で構成 さ れてい ます。 同様に、 各 18Kb ブ ロ ッ ク RAM のデ ュ アルポー ト メ モ リ は、18Kb の記憶領域 と 完全に独立 し た 2 つのア ク セ ス ポー ト (A お よ び B) で構成 さ れてい ます。 構造は完 全に対称で、 両ポー ト は交換可能です。図1-1に RAMB36 の TDP のデー タ フ ロ ーを示 し ま す。 表1-3にポー ト の機能 と その説明を示 し ます。 デー タ の書 き 込み/読み出 し は、 ど ち ら か一方のポー ト ま たは両方のポー ト で実行で き ます。 書 き 込 みは、 それぞれ ク ロ ッ ク に同期 し て行われ、 各ポー ト には、 ア ド レ ス、 デー タ 入力、 デー タ 出力、 ク ロ ッ ク 、 ク ロ ッ ク イ ネーブル、 書 き 込み イ ネーブルが含まれます。 読み出 し お よ び書 き 込みは同 期で実行 さ れます。 そのため、1 つの ク ロ ッ ク エ ッ ジが必要です。 両方のポー ト で同 じ ア ド レ ス にア ク セ ス し た際に、 その調整を行 う 専用モニ タ ーはあ り ません。 2 つの ク ロ ッ ク の タ イ ミ ン グは、 ユーザーの責任で調整 し て く だ さ い。 同 じ ア ド レ ス に同時に書 き 込みを実行 し た場合、 物理的な破損はあ り ませんが、 書 き 込まれたデー タ は不確定にな り ます。 X-Ref Target - Figure 1-1図 1-1 : RAMB36 の TDP デー タ フ ロー DOPA DIPA ADDRA WEA ENA CASCADEOUTB RSTRAMA CLKA RSTREGA REGCEA REGCEB DIPB ADDRB WEB ENB RSTRAMB RSTREGB CLKB

36-Kbit Block RAM

UG473_c1_01_052610 DOPB DOB DOA DIA DIB 36 Kb Memory Array Port A 32 4 32 4 16 4 32 4 16 4 32 4 Port B CASCADEOUTA CASCADEINB CASCADEINA

読み出 し

ラ ッ チモー ド の読み出 し は、 ク ロ ッ ク エ ッ ジに同期 し て行われ ます。 読み出 し ア ド レ ス が読み出 し ポー ト に取 り 込まれてか ら 、RAM ア ク セ ス時間の後に、 格納 さ れたデー タ が出力 ラ ッ チに読み 込まれます。 出力レ ジ ス タ を使用 し た場合は、 読み出 し の レ イ テ ン シが 1 ク ロ ッ クサ イ ク ル増加 し ます。書き込み

書 き 込みは、 ク ロ ッ ク エ ッ ジに同期 し て行われます。 書 き 込みア ド レ スは書 き 込みポー ト に取 り 込 まれ、 入力デー タ が メ モ リ に格納 さ れます。書き込みモー ド

書き込み ク ロ ッ ク エ ッ ジ後の出力 ラ ッ チのデータ は、WRITE_FIRST、READ_FIRST、NO_CHANGE の 3 つの書 き 込みモー ド のいずれ を設定す る かで決定 し ま す。 こ のモー ド は、 コ ン フ ィ ギ ュ レ ー シ ョ ンで設定 し ます。 各ポー ト に対 し て別々の書 き 込みモー ド を設定で き 、 デフ ォ ル ト のモー ド は WRITE_FIRST です。WRITE_FIRST では新た なデー タ が書 き 込 ま れ る と 同時に、 その新規デー タ が出力バス に送信 さ れ、READ_FIRST ではあ ら か じ め保存 さ れてい る デー タ が出力 さ れます。 NO_CHANGE では、 前回の読み出 し 処理の出力がその ま ま送信 さ れます。 表 1-3 : TDP モー ド でのポー ト の機能および説明 ポー ト 名 説明 DI[A|B] デー タ 入力バス DIP[A|B](1) デー タ 入力パ リ テ ィ バ ス で、 追加デー タ 入力に使用で き ます。 ADDR[A|B] ア ド レ スバ ス WE[A|B] バ イ ト ラ イ ト イ ネーブル EN[A|B] 非ア ク テ ィ ブの場合、 ブ ロ ッ ク RAM にデー タ は書 き 込まれず、 出 力バス が以前の状態に保持 さ れます。

RSTREG[A|B] 出力レ ジ ス タ の同期セ ッ ト/リ セ ッ ト (DO_REG = 1)。REGCE よ り も 優先す る か ど う かは、RSTREG_PRIORITY 属性で設定 し ます。 RSTRAM[A|B] 出力デー タ ラ ッ チの同期セ ッ ト/リ セ ッ ト CLK[A|B] ク ロ ッ ク 入力 DO[A|B] デー タ 出力バス DOP[A|B](1) デー タ 出力パ リ テ ィ バ ス で、 追加デー タ 出力に使用で き ます。 REGCE[A|B] 出力レ ジ ス タ ク ロ ッ ク イ ネーブル CASCADEIN[A|B] 64Kx1 モー ド のカ ス ケー ド 入力 CASCADEOUT[A|B] 64Kx1 モー ド のカ ス ケー ド 出力 注記 :

1. デー タパ リ テ ィ ピ ンの詳細は、「デー タ 入力バ ス - DIADI、DIPADIP、DIBDI、DIPBDIP」 を参照 し て く だ さ い。

同期デ ュ アルポー ト お よびシ ングルポー ト RAM

WRITE_FIRST

または透過モー ド

(

デ フ ォル ト

)

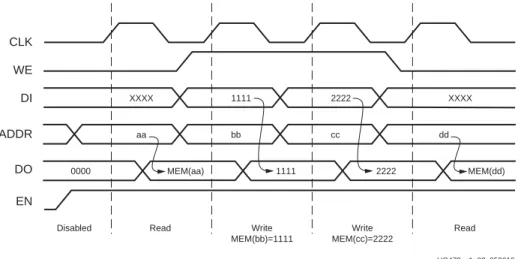

図1-2に示す よ う に、WRITE_FIRST モー ド では入力デー タ を メ モ リ に書 き 込む と 同時にデー タ 出 力に も 格納 さ れます (透過書 き 込み)。 こ こ に示す波形は、 オプシ ョ ンの出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ない ラ ッ チモー ド の場合です。READ_FIRST

または書き込み前読み出 し モー ド

READ_FIRST モー ド では、書 き 込み先ア ド レ ス に格納 さ れていたデー タ が出力 ラ ッ チに送信 さ れ、 それ と 同時に入力デー タ が メ モ リ に格納 さ れます (書 き 込み前に読み込み)。図1-3の波形は、 オプ シ ョ ンの出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ない ラ ッ チモー ド の場合を示 し てい ます。NO_CHANGE

モー ド

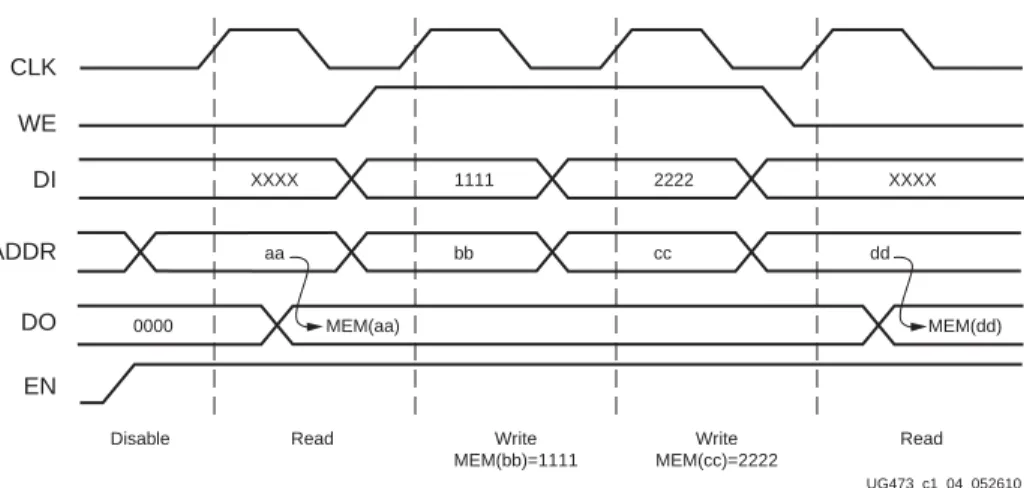

NO_CHANGE モー ド では、 書 き 込み中、 出力 ラ ッ チは変化 し ません。図1-4に示す よ う に、 デー タ 出力には最後に読み込まれたデー タ がその ま ま維持 さ れ、 同 じ ポー ト での書 き 込みに影響 さ れま せん。 こ こ に示す波形は、 オプシ ョ ン の出力パ イ プ ラ イ ン レ ジ ス タ を使用 し ない ラ ッ チモー ド の 場合です。 こ のモー ド が最 も 消費電力を削減で き ま す。 ま た、SDP モー ド のブ ロ ッ ク RAM では WRITE_FIRST モー ド の動作 と 同 じ にな る ため使用で き ません。X-Ref Target - Figure 1-2

図 1-2 : WRITE_FIRST モー ド での波形 CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 XXXX aa bb cc dd 0000 MEM(aa) 1111 2222 MEM(dd) Read Write MEM(bb)=1111 Write MEM(cc)=2222 UG473_c1_02_052610

X-Ref Target - Figure 1-3

図 1-3 : READ_FIRST モー ド での波形 CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 XXXX aa bb cc dd

0000 MEM(aa) old MEM(bb) old MEM(cc) MEM(dd)

Read Write MEM(bb)=1111 Write MEM(cc)=2222 UG473_c1_03_052610

競合の回避

7シ リ ーズ FPGA のブ ロ ッ ク RAM メ モ リ は、 両方のポー ト が任意の メ モ リ 位置に随時ア ク セ ス で き る TDP RAM です。 ただ し 、2 つのポー ト か ら 同 じ メ モ リ 位置へア ク セ スす る 際には制限があ り ます。 こ の よ う な ア ク セ ス には基本的に、 両ポー ト で共通の ク ロ ッ ク を使用 し てい る 場合 (同期 ク ロ ッ ク) と 、 両ポー ト の ク ロ ッ ク 周波数ま たは位相が異な る 場合 (非同期 ク ロ ッ ク) と い う 2 つの場 合が考え ら れます。非同期ク ロ ッ ク

一般的には、 ク ロ ッ ク は非同期であ る こ と が多 く 、 両 ク ロ ッ ク のア ク テ ィ ブエ ッ ジが同時に発生す る こ と はあ り ません。 • 両ポー ト で読み出 し を実行す る 場合、 タ イ ミ ン グに制約はあ り ません。 • 1 つのポー ト で書 き 込みを実行中に、 も う 1 つのポー ト で同 じ メ モ リ 位置に対 し て読み出 し ま たは書 き 込みは実行で き ません。 し たがっ て、READ_FIRST モー ド では、格納 さ れていたデー タ が読み出 さ れ る かが不確定であ る ため、 完全な非同期アプ リ ケーシ ョ ン では TDP、SDP ど ち ら のモー ド で も 使用で き ません。非同期 ク ロ ッ ク に よ っ て 1 つのポー ト ア ド レ ス に対 し て同 時に読み出 し/書 き 込み動作が発生す る 可能性があ る 場合は、WRITE_FIRST モー ド を推奨 し ます。 こ れに違反す る と 、 シ ミ ュ レーシ ョ ン モデルでエ ラ ーが発生 し ます。 こ の制限を無視す る と 、 読み出 し ま たは書 き 込み動作の結果が予測で き な く な り ます。 ただ し 、 デバ イ ス が物理 的に破損す る こ と はあ り ません。読み出 し と 書 き 込みを実行す る と 、書 き 込み位置に有効なデー タ が格納 さ れます。同期ク ロ ッ ク

同期 ク ロ ッ ク は、 両ポー ト の ク ロ ッ ク のエ ッ ジが同時にア ク テ ィ ブにな る と い う 特殊な状況です。 • 同期 ク ロ ッ ク と は、 両方の ク ロ ッ ク 入力ピ ンが同 じ ク ロ ッ ク で駆動 さ れ る も の と 定義 し ます。 • 両ポー ト で読み出 し を実行す る 場合、 タ イ ミ ン グに制約はあ り ません。 • 1 つのポー ト で書 き 込みを実行中に、 も う 1 つのポー ト を使用 し て同 じ メ モ リ 位置に書 き 込み はで き ません。 ただ し 、 両ポー ト で書 き 込むデー タ が同一の場合は例外です。 • 1 つのポー ト で書き込みを実行中、書き込みポー ト が READ_FIRST モー ド であれば、 も う 1 つ のポー ト で同 じ メ モ リ 位置か ら デー タ を正 し く 読み出す こ と がで き ます。 その場合、 両ポー ト の DATA_OUT は書き込み前に格納 さ れていたデータ にな り ます。X-Ref Target - Figure 1-4

図 1-4 : NO_CHANGE モー ド での波形 CLK WE DI ADDR DO EN Disable Read XXXX 1111 2222 XXXX aa bb cc dd 0000 MEM(aa) MEM(dd) Read Write MEM(bb)=1111 Write MEM(cc)=2222 UG473_c1_04_052610

7シ リ ーズデバイ スのブ ロ ッ ク RAM のその他の機能 書 き 込みポー ト が WRITE_FIRST ま たは NO_CHANGE モー ド の場合は、 読み出 し ポー ト の DATA_OUT が無効 (不確定) にな り ます。 読み出 し ポー ト のモー ド 設定は、 こ の動作には影響 を与え ません。

7

シ リ ーズ

デバイ スのブ ロ ッ ク

RAM

のその他の機能

出力レ ジ ス タ

(

オプ シ ョ ン

)

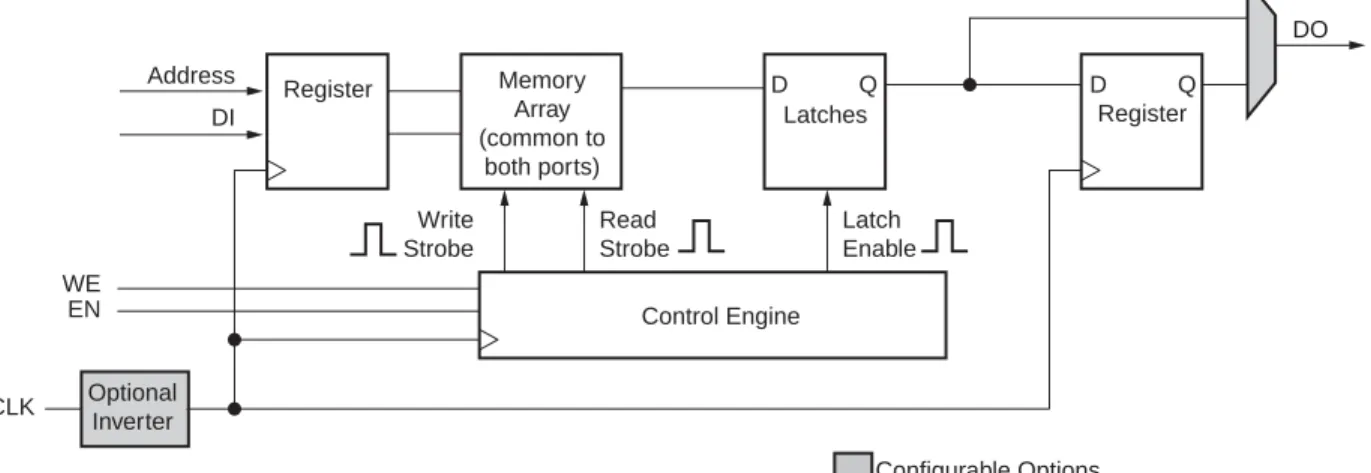

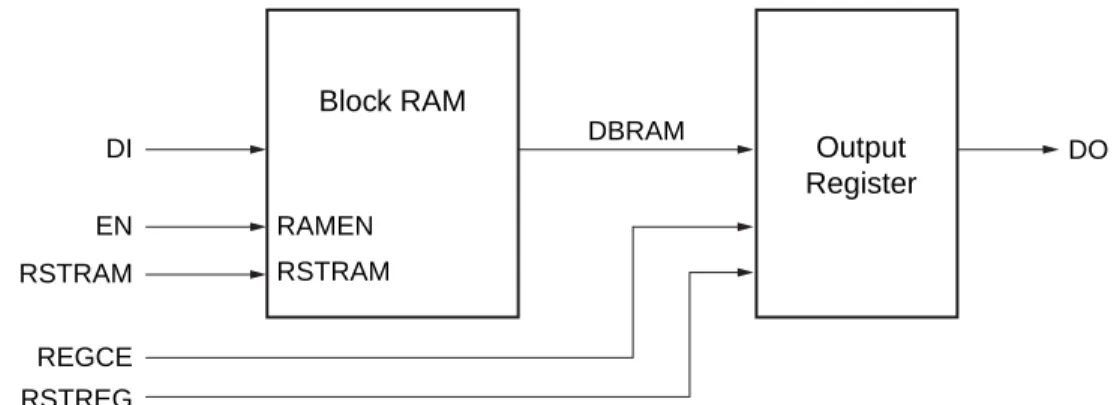

オプシ ョ ン の出力レ ジ ス タ を使用す る と 、 パ イ プ ラ イ ン処理におけ る CLB フ リ ッ プ フ ロ ッ プへの 配線遅延が削減 さ れ、 デザ イ ンのパフ ォーマ ン ス が向上 し ます。 こ れ ら の出力レ ジ ス タ には、 独立 し た ク ロ ッ ク お よ び ク ロ ッ ク イ ネーブルの入力が供給 さ れ る ため、入力レ ジ ス タ の動作か ら 独立 し た値が保持で き ます。図1-5にオプシ ョ ンの出力レ ジ ス タ を示 し ます。個別に選択可能な読み出 し ポー ト と 書き込みポー ト の幅

各ブ ロ ッ ク RAM ポー ト では、 デー タ 幅 と ア ド レ ス幅 (ア スペ ク ト 比) を制御で き ます。7シ リ ーズ FPGA の TDP モー ド のブ ロ ッ ク RAM では こ の機能が拡張 さ れ、 各ポー ト での読み出 し お よ び書 き 込みに異な る デー タ 幅を設定で き る よ う にな っ てい ます。 た と えば、 ポー ト A が 36 ビ ッ ト の読 み出 し 幅 と 9 ビ ッ ト の書 き 込み幅を持ち、 ポー ト B が 18 ビ ッ ト の読み出 し 幅 と 36 ビ ッ ト の書 き 込み幅を持つ よ う 設定可能です。詳細は、31ページの「ブ ロ ッ ク RAM の属性」を参照 し て く だ さ い。 読み出 し ポー ト と 書 き 込みポー ト の幅が異な っ ていて、WRITE_FIRST モー ド が設定 さ れてい る 場 合、 有効なすべての書き込みバ イ ト に対 し て、DO には有効な新規デー タ が現れます。 有効 と な っ て いないすべてのバ イ ト に対 し ては、 メ モ リ に保存 さ れた以前のデー タ が DO ポー ト に出力 さ れます。 読み出 し ポー ト と 書 き 込みポー ト の幅 を 個別に設定で き る こ と に よ り 、 ブ ロ ッ ク RAM に CAM (Content Addressable Memory) を効率的に イ ンプ リ メ ン ト で き ます。 こ のオプシ ョ ンは、7シ リ ーズ FPGA のブ ロ ッ ク RAM を TDP モー ド と し た場合、すべてのポー ト サ イ ズ と モー ド で使用可能です。Simple Dual-Port (SDP)

ブ ロ ッ ク

RAM

18Kb ブ ロ ッ ク お よ び 36Kb ブ ロ ッ ク はそれぞれ、SDP RAM モー ド と し て も 構成で き ます。 こ の モー ド では、ブ ロ ッ ク RAM のポー ト 幅が 2 倍にな り 、18Kb ブ ロ ッ ク RAM では 36 ビ ッ ト 、36Kb X-Ref Target - Figure 1-5

図 1-5 : ブ ロ ッ ク RAM の論理図 (1 ポー ト のみ表示) Register Optional Inverter Latches Register Address DI WE EN CLK Write Strobe Read Strobe Q D D Q DO Control Engine Configurable Options UG473_c1_05_052610 Memory Array (common to both ports) Latch Enable

ポー ト 、 ポー ト B を書 き 込みポー ト と し 、 読み出 し と 書 き 込みを同時に独立 し て実行で き ます。 読 み出 し ポー ト と 書 き 込みポー ト が同 じ デー タ 位置に同時にア ク セ スす る と 、TDP モー ド のポー ト 競 合 と 同様に競合が発生 し ます。SDP モー ド のブ ロ ッ ク RAM では、 コ ン フ ィ ギ ュ レーシ ョ ンポー

ト か ら の リ ー ド バ ッ ク がサポー ト さ れてい ます。7シ リ ーズ FPGA は こ れ ら のモー ド を SDP (READ_FIRST、WRITE_FIRST) でサポー ト し ま す。図1-6に、SDP モー ド におけ る RAMB36 の SDP デー タ フ ロ ーを示 し ます。

X-Ref Target - Figure 1-6

図 1-6 : RAMB36 の SDP デー タ フ ロー 表 1-4 : SDP モー ド でのポー ト の機能および説明 ポー ト 名 説明 DO デー タ 出力バ ス DOP デー タ 出力パ リ テ ィ バ ス DI デー タ 入力バ ス DIP デー タ 入力パ リ テ ィ バ ス RDADDR 読み出 し デー タ ア ド レ スバス RDCLK 読み出 し デー タ ク ロ ッ ク RDEN 読み出 し ポー ト イ ネーブル REGCE 出力レ ジ ス タ ク ロ ッ ク イ ネーブル SBITERR シ ン グルビ ッ ト エ ラ ース テー タ ス DBITERR ダブルビ ッ ト エ ラ ース テー タ ス ECCPARITY ECC エン コ ーダー出力バ ス SSR 出力レ ジ ス タ ま たは ラ ッ チの同期セ ッ ト/リ セ ッ ト WE バ イ ト ラ イ ト イ ネーブル WRADDR 書 き 込みデー タ ア ド レ スバス WRCLK 書 き 込みデー タ ク ロ ッ ク WREN 書 き 込みポー ト イ ネーブル 注記 : 1. ブ ロ ッ ク RAM プ リ ミ テ ィ ブのポー ト 名 と ポー ト 機能名は異な る こ と があ り ます。

36 Kb Memory Array

DO RDEN RDADDR RDCLK REGCE DIP WRADDR WE WRCLK WREN DI UG473_c1_06_011414 64 8 8 15 15 64 DOP 8 SSR7シ リ ーズデバイ スのブ ロ ッ ク RAM のその他の機能

カ スケー ド 接続が可能な ブ ロ ッ ク

RAM

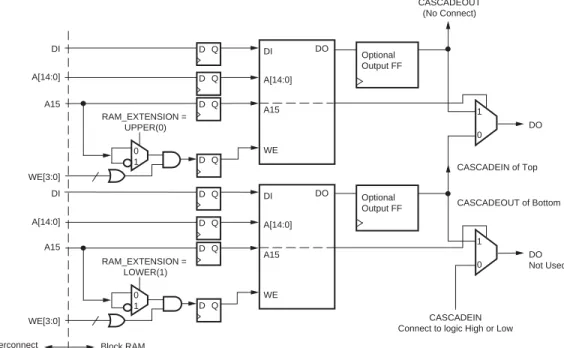

7シ リ ー ズ の ブ ロ ッ ク RAM ア ー キ テ ク チ ャ で は、2 つの 32Kx1 RAM を 組み合わせ て 1 つの 64Kx1 RAM を作成で き ます。 こ の際に、 ロ ーカルイ ン タ ー コ ネ ク ト や追加の CLB ロ ジ ッ ク の使 用は不要です。 隣接す る 2 つのブ ロ ッ ク RAM を カ ス ケー ド 接続す る と 、64Kx1 ブ ロ ッ ク RAM を 作成で き ます。 ただ し 、 ブ ロ ッ ク RAM を 2 つカ ス ケー ド 接続 し て、 ブ ロ ッ ク RAM の ワー ド 数を 増やす こ と がで き る のは、64Kx1 モー ド のみです。 カ ス ケー ド 接続可能なブ ロ ッ ク RAM について は、「RAMB18E1 お よ び RAMB36E1 プ リ ミ テ ィ ブの設計上のその他の注意事項」で詳 し く 説明 し てい ます。 こ れ以外の方法に よ る ビ ッ ト 数 と ワ ー ド 数の拡張については、「大規模な RAM 構造の 作成」 を参照 し て く だ さ い。図1-7に、 カ ス ケー ドモー ド でポー ト を接続 し たブ ロ ッ ク RAM を示 し ます。バイ ト

ラ イ ト

イ ネーブル

ブ ロ ッ ク RAM にはバ イ ト ラ イ ト イ ネーブル機能があ り 、8 ビ ッ ト (1 バ イ ト) 単位で入力デー タ を書 き 込む こ と がで き ます。TDP モー ド の RAMB36E1 には、4 つの独立 し たバ イ ト ラ イ ト イ ネー ブル入力があ り ます。 ま た、SDP モー ド のブ ロ ッ ク RAM (RAMB36E1) には、8 つの独立 し たバ イ ト ラ イ ト イ ネーブル入力があ り ます。表1-5に、36Kb お よ び 18Kb ブ ロ ッ ク RAM で利用で き る バ イ ト ラ イ ト イ ネーブルの数を示 し ます。 各バ イ ト ラ イ ト イ ネーブルは、1 バ イ ト の入力デー タ と 1 パ リ テ ィ ビ ッ ト に対応 し てい ます。 デー タ 幅の コ ン フ ィ ギ ュ レーシ ョ ンにかかわ ら ず、 すべ てのバ イ ト ラ イ ト イ ネーブル入力を駆動す る 必要があ り ます。 こ の機能は、 ブ ロ ッ ク RAM を使 用 し てマ イ ク ロ プ ロ セ ッ サ と 通信す る 場合に有用です。 バ イ ト ラ イ ト イ ネーブル機能は、 デ ュ ア ル ク ロ ッ ク FIFO や ECC モ ー ド で は 使用 で き ま せ ん。 バ イ ト ラ イ ト イ ネ ー ブ ル の 詳細 は、 「RAMB18E1 お よ び RAMB36E1 プ リ ミ テ ィ ブの設計上のその他の注意事項」 を参照 し て く だ さ い。図1-8に、RAMB36E1 のバ イ ト ラ イ ト イ ネーブルの タ イ ミ ン グ図を示 し ます。X-Ref Target - Figure 1-7

図 1-7 : カ スケー ド 接続可能な ブ ロ ッ ク RAM

DO Not Used

DI DI

CASCADEIN Connect to logic High or Low

CASCADEOUT (No Connect) A[14:0] WE DO A15 A15 A[14:0] DO DI DI A[14:0] WE DO D Q D Q D Q D Q D Q D Q D Q D Q A15 A15 A[14:0] WE[3:0] WE[3:0]

Interconnect Block RAM RAM_EXTENSION = UPPER(0) RAM_EXTENSION = LOWER(1) 0 1 0 1 0 1 0 1 UG473_c1_07_040411 CASCADEIN of Top CASCADEOUT of Bottom Optional Output FF Optional Output FF

RAMB36E1 で 36 ビ ッ ト 幅ま たは 18 ビ ッ ト 幅のデー タパ ス を設定す る と 、 デー タ ワ ー ド 内で指 定 し たバ イ ト 位置への書 き 込みを任意のポー ト で制御で き ます。READ_FIRST モー ド の場合、DO バ ス にはア ド レ ス指定 し た ワ ー ド 全体が書 き 込み前の内容で現れ ます。WRITE_FIRST の場合は、 DO には新たに書 き 込まれた有効なバ イ ト と 未書 き 込みバ イ ト の メ モ リ の初期内容の組み合わせが 出力 さ れます。

ブ ロ ッ ク

RAM

の

ECC (

誤 り 訂正符号

)

36Kb ブ ロ ッ ク RAM でのブ ロ ッ ク RAM お よ び FIFO イ ンプ リ メ ン テーシ ョ ンでは、64 ビ ッ ト の ECC (誤 り 訂正符号) を備え る こ と がで き ます。 こ の機能を使用す る と 、 ブ ロ ッ ク RAM の読み出 し デー タ のシ ン グルビ ッ ト お よ びダブルビ ッ ト エ ラ ーが検出で き ます。シ ン グルビ ッ ト エ ラ ーは出 力デー タ で修正 さ れます。

未使用ブ ロ ッ ク

RAM

のパワー

ゲーテ ィ ング

7シ リ ーズデバ イ ス は、 未使用 ま たは イ ン ス タ ン シエー ト さ れていないブ ロ ッ ク RAM の電源を 18Kb 単位で細か く 切断 し ま す。 デザ イ ン内で イ ン ス タ ン シエー ト さ れていないすべての 18K ブ ロ ッ ク に対 し てパ ワ ーゲーデ ィ ン グ を有効にす る こ と で、 消費電力を削減で き ま す。 パ ワ ーゲー テ ィ ン グ を用いた 18K ブ ロ ッ ク は、 コ ン フ ィ ギ ュ レーシ ョ ン中に初期化 さ れず、 コ ン フ ィ ギ ュ レー シ ョ ン イ ン タ ーフ ェ イ ス か ら リ ー ド バ ッ ク で き ません。 従来の FPGA フ ァ ミ リ と は異な り 、 コ ン フ ィ ギ ュ レーシ ョ ンお よ び リ ー ド バ ッ ク には有効な ビ ッ ト ス ト リ ームが必要です。 空白のビ ッ ト ス ト リ ームは使用で き ません。 イ ン ス タ ン シエー ト さ れていないブ ロ ッ ク RAM へのア ク セ スは、 内 部動作を無効にす る こ と に よ っ て避け る こ と がで き ます。 表 1-5 : 使用可能なバイ ト ラ イ ト イ ネーブル プ リ ミ テ ィ ブ 最大ビ ッ ト 幅 バイ ト ラ イ ト イ ネーブル数 RAMB36E1 TDP モー ド 36 4 RAMB36E1 SDP モー ド 72 8 RAMB18E1 TDP モー ド 18 2 RAMB18E1 SDP モー ド 36 4X-Ref Target - Figure 1-8

図 1-8 : バイ ト ラ イ ト 動作の波形 (x36 WRITE_FIRST) CLK WE DI ADDR DO EN Disabled Read XXXX 1111 2222 1111 0011 XXXX aa bb bb cc 0000 MEM(aa) 1111 1122 MEM(cc) Read Write MEM(bb)=1111 Byte Write MEM(bb)=1122 UG473_c1_08_052610

ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ

ブ ロ ッ ク

RAM

のラ イ ブ ラ リ

プ リ ミ テ ィ ブ

7シ リ ーズ FPGA のブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ、RAMB18E1 お よ び RAMB36E1 はすべて のブ ロ ッ ク RAM コ ン フ ィ ギ ュ レ ーシ ョ ン の基本構築ブ ロ ッ ク です。 その他のブ ロ ッ ク RAM のプ リ ミ テ ィ ブおよ びマ ク ロ は、 こ のプ リ ミ テ ィ ブを基に し てい ます。 ブ ロ ッ ク RAM の属性 に よ っ ては、1 つのプ リ ミ テ ィ ブでのみ設定で き ます (パ イ プ ラ イ ン レ ジ ス タ 、 カ ス ケー ド な ど)。 詳 細は、「ブ ロ ッ ク RAM の属性」 を参照 し て く だ さ い。 9 ビ ッ ト 幅 (8+1)、18 ビ ッ ト 幅 (16+2)、36 ビ ッ ト 幅 (32+4) の コ ン フ ィ ギ ュ レーシ ョ ン では、 入力 お よ び出力デー タバ ス は 2 つのバ ス で表 さ れます。各バ イ ト に関連付け ら れてい る 9 番目のビ ッ ト にはパ リ テ ィ ビ ッ ト (誤 り 訂正ビ ッ ト) を保存す る か、 追加のデー タ ビ ッ ト と し て使用で き ま す。 こ の 9 番目のビ ッ ト には、 特定の機能はあ り ません。 パ リ テ ィ ビ ッ ト 用に別のバ ス を使用 し た方が 良いデザ イ ン も あ り ますが、 たいていの場合は、 通常のデー タバス と パ リ テ ィ バ ス を一緒に し て、 9 ビ ッ ト 、18 ビ ッ ト 、 ま たは 36 ビ ッ ト バ ス を使用 し て も 問題あ り ません。 読み出 し/書 き 込み、 お よ び保存はパ リ テ ィ ビ ッ ト を含めてすべてのビ ッ ト で同様に行われます。

図1-9に、36Kb の TDP のブ ロ ッ ク RAM プ リ ミ テ ィ ブ (RAMB36) の I/O ポー ト を示 し ます。

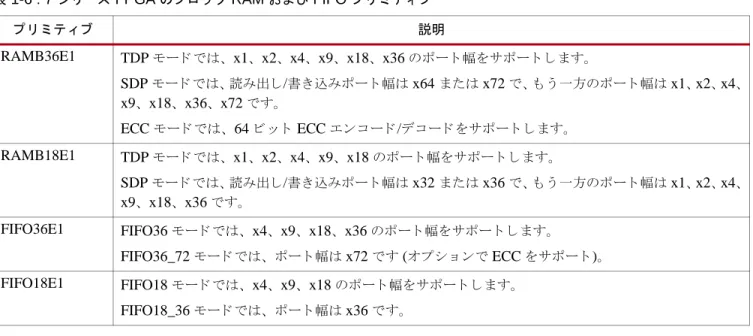

表1-6にプ リ ミ テ ィ ブの一覧を示 し ます。

X-Ref Target - Figure 1-9

図 1-9 : ブ ロ ッ ク RAM ポー ト 信号 (RAMB36E1) DOPADOP DOPBDOP DIADI DIPADIP ADDRARDADDR WEA ENARDEN RSTREGARSTREG CLKARDCLK DOADO DOBDO RSTRAMARSTRAM REGCEAREGCE DIBDI DIPBDIP ADDRBWRADDR WEBWE ENBWREN RSTREGB RSTRAMB REGCEB CLKBWRCLK UG473_c1_09_052610 32 4 16 4 32 4 32 4 32 4 16 8 CASCADEOUTA CASCADEOUTB CASCADEINA CASCADEINB

表1-7と表1-8に、表1-6で示 し たプ リ ミ テ ィ ブの各ポー ト 名 と 説明を示 し ます。ECC ポー ト につ

いては、第 3 章 「ビル ト イ ン誤 り 訂正」 で説明 し ます。

表 1-6 : 7シ リ ーズ FPGA のブ ロ ッ ク RAM および FIFO プ リ ミ テ ィ ブ

プ リ ミ テ ィ ブ 説明 RAMB36E1 TDP モー ド では、x1、x2、x4、x9、x18、x36 のポー ト 幅をサポー ト し ます。 SDP モー ド では、読み出 し/書 き 込みポー ト 幅は x64 ま たは x72 で、 も う 一方のポー ト 幅は x1、x2、x4、 x9、x18、x36、x72 です。 ECC モー ド では、64 ビ ッ ト ECC エン コ ー ド/デコ ー ド をサポー ト し ます。 RAMB18E1 TDP モー ド では、x1、x2、x4、x9、x18 のポー ト 幅をサポー ト し ます。 SDP モー ド では、読み出 し/書 き 込みポー ト 幅は x32 ま たは x36 で、 も う 一方のポー ト 幅は x1、x2、x4、 x9、x18、x36 です。 FIFO36E1 FIFO36 モー ド では、x4、x9、x18、x36 のポー ト 幅をサポー ト し ます。 FIFO36_72 モー ド では、 ポー ト 幅は x72 です (オプシ ョ ンで ECC をサポー ト)。 FIFO18E1 FIFO18 モー ド では、x4、x9、x18 のポー ト 幅をサポー ト し ます。 FIFO18_36 モー ド では、 ポー ト 幅は x36 です。 表 1-7 : RAMB36E1 のポー ト 名 と 説明 ポー ト 名 説明 DIADI[31:0] ポー ト A デー タ 入力。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名 マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DIPADIP[3:0] ポー ト A デー タ パ リ テ ィ 入力。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド での ポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DIBDI[31:0] ポー ト B デー タ 入力。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名 マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DIPBDIP[3:0] ポー ト B デー タパ リ テ ィ 入力。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド での ポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。

ADDRARDADDR[15:0] ポー ト A ア ド レ ス入力バス。RAM_MODE = SDP の場合、RDADDR バ ス と な り ます。 ADDRBWRADDR[15:0] ポー ト B ア ド レ ス入力バス。RAM_MODE = SDP の場合、WRADDR バ ス と な り ます。 WEA[3:0] ポー ト A バ イ ト ラ イ ト イ ネーブル。RAM_MODE = SDP の場合は使用 し ません。

WEBWE[7:0] ポー ト B バ イ ト ラ イ ト イ ネーブル。RAM_MODE = SDP の場合、 バ イ ト ラ イ ト イ ネーブル と な り ます。

ENARDEN ポー ト A イ ネーブル。RAM_MODE = SDP の場合、RDEN と な り ます。 ENBWREN ポー ト B イ ネーブル。RAM_MODE = SDP の場合、WREN と な り ます。

RSTREGARSTREG 同期出力レ ジ ス タ のセ ッ ト/リ セ ッ ト 。SRVAL_A (DOA_REG = 1) で初期化 し ます。REGCE よ り も 優先す る か ど う かは RSTREG_PRIORITY_A で設定 し ます。RAM_MODE = SDP の場合、 RSTREG と な り ます。

RSTREGB 同期出力レ ジ ス タ のセ ッ ト/リ セ ッ ト 。SRVAL_B (DOB_REG = 1) で初期化 し ます。REGCE よ り も 優先す る か ど う かは、RSTREG_PRIORITY_B で設定 し ます。

ブ ロ ッ ク RAM の ラ イ ブ ラ リ プ リ ミ テ ィ ブ

RSTRAMARSTRAM 同期出力 ラ ッ チのセ ッ ト/リ セ ッ ト 。SRVAL_A (DOA_REG = 0) で初期化 し ます。RAM_MODE = SDP の場合、RSTRAM と な り ます。

RSTRAMB 同期出力 ラ ッ チのセ ッ ト/リ セ ッ ト 。SRVAL_B (DOB_REG = 0) で初期化 し ます。 CLKARDCLK ポー ト A ク ロ ッ ク 入力。RAM_MODE = SDP の場合、RDCLK と な り ます。 CLKBWRCLK ポー ト B ク ロ ッ ク 入力。RAM_MODE = SDP の場合、WRCLK と な り ます。

REGCEAREGCE ポー ト A 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOA_REG = 1)。RAM_MODE = SDP の場合、 REGCE と な り ます。 REGCEB ポー ト B 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOB_REG = 1)。 CASCADEINA ポー ト A カ ス ケー ド 入力。RAM_MODE = TDP の場合のみ使用 し ます。 CASCADEINB ポー ト B カ ス ケー ド 入力。RAM_MODE = TDP の場合のみ使用 し ます。 CASCADEOUTA ポー ト A カ ス ケー ド 出力。RAM_MODE = TDP の場合のみ使用 し ます。 CASCADEOUTB ポー ト B カ ス ケー ド 出力。RAM_MODE = TDP の場合のみ使用 し ます。 DOADO[31:0] ポー ト A デー タ 出力バス。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DOPADOP[3:0] ポー ト A パ リ テ ィ 出力バス。ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DOBDO[31:0] ポー ト B デー タ 出力バス。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DOPBDOP[3:0] ポー ト B パ リ テ ィ 出力バス。ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 表 1-8 : RAMB18E1 のポー ト 名 と 説明 ポー ト 名 説明 DIADI[15:0] ポー ト A デー タ 入力。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名 マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DIPADIP[1:0] ポー ト A デー タパ リ テ ィ 入力。 ア ド レ スは ADDRARDADDR で指定 し ます。SDP モー ド での ポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DIBDI[15:0] ポー ト B デー タ 入力。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名 マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DIPBDIP[1:0] ポー ト B デー タパ リ テ ィ 入力。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド での ポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。

ADDRARDADDR[13:0] ポー ト A ア ド レ ス入力バ ス。RAM_MODE = SDP の場合、RDADDR バ ス と な り ます。 ADDRBWRADDR[13:0] ポー ト B ア ド レ ス入力バ ス。RAM_MODE = SDP の場合、WRADDR バス と な り ます。 WEA[1:0] ポー ト A バ イ ト ラ イ ト イ ネーブル。RAM_MODE = SDP の場合は使用 し ません。

WEBWE[3:0] ポー ト B バ イ ト ラ イ ト イ ネーブル (WEBWE [1:0])。RAM_MODE = SDP の場合、 バ イ ト ラ イ ト イ ネーブル と な り ます。

ENARDEN ポー ト A イ ネーブル。RAM_MODE = SDP の場合、RDEN と な り ます。 表 1-7 : RAMB36E1 のポー ト 名 と 説明 (続き)

ブ ロ ッ ク

RAM

のポー ト 信号

ブ ロ ッ ク RAM の各ポー ト は、 同 じ 36Kb メ モ リ セルのセ ッ ト にア ク セ ス し ますが、 動作はそれぞ れ独立 し てい ます。ク ロ ッ ク

- CLKARDCLK

、

CLKBWRCLK

各ポー ト は、 それぞれの ク ロ ッ ク ピ ンに完全に同期 し ます。 すべてのポー ト の入力ピ ンにはセ ッ ト ア ッ プ タ イ ムがあ り 、CLK ピ ン を基準 と し ます。 ま た、 出力デー タ バ ス の Clock-to-Out も CLK ピ ン を基準 と し ます。 ク ロ ッ ク の極性は設定変更可能で、 デフ ォ ル ト では立ち上が り エ ッ ジ と な っ てい ます。SDP モー ド では、CLKA ポー ト が RDCLK と な り 、CLKB ポー ト が WRCLK と な り ます。ENBWREN ポー ト B イ ネーブル。RAM_MODE = SDP の場合、WREN と な り ます。

RSTREGARSTREG 同期出力レ ジ ス タ のセ ッ ト/リ セ ッ ト 。SRVAL_A (DOA_REG = 1) で初期化 し ます。REGCE よ り も 優先す る か ど う かは RSTREG_PRIORITY_A で設定 し ます。RAM_MODE = SDP の場合、 RSTREG と な り ます。

RSTREGB 同期出力レ ジ ス タ のセ ッ ト/リ セ ッ ト 。SRVAL_B (DOB_REG = 1) で初期化 し ます。REGCE よ り も 優先す る か ど う かは、RSTREG_PRIORITY_B で設定 し ます。

RSTRAMARSTRAM 同期出力 ラ ッ チのセ ッ ト/リ セ ッ ト 。SRVAL_A (DOA_REG = 0) で初期化 し ます。RAM_MODE = SDP の場合、RSTRAM と な り ます。

RSTRAMB 同期出力 ラ ッ チのセ ッ ト/リ セ ッ ト 。SRVAL_B (DOB_REG = 0) で初期化 し ます。 CLKARDCLK ポー ト A ク ロ ッ ク 入力。RAM_MODE = SDP の場合、RDCLK と な り ます。 CLKBWRCLK ポー ト B ク ロ ッ ク 入力。RAM_MODE = SDP の場合、WRCLK と な り ます。

REGCEAREGCE ポー ト A 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOA_REG = 1)。RAM_MODE = SDP の場合、 REGCE と な り ます。 REGCEB ポー ト B 出力レ ジ ス タ ク ロ ッ ク イ ネーブル (DOB_REG = 1)。 DOADO[15:0] ポー ト A デー タ 出力バ ス。 ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DOPADOP[1:0] ポー ト A パ リ テ ィ 出力バ ス。ア ド レ ス は ADDRARDADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DOBDO[15:0] ポー ト B デー タ 出力バ ス。 ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 DOPBDOP[1:0] ポー ト B パ リ テ ィ 出力バス。ア ド レ ス は ADDRBWRADDR で指定 し ます。SDP モー ド でのポー ト 名マ ッ ピ ン グは、表1-13を参照 し て く だ さ い。 表 1-8 : RAMB18E1 のポー ト 名 と 説明 (続き) ポー ト 名 説明

ブ ロ ッ ク RAM のポー ト 信号

イ ネーブル

- ENARDEN

、

ENBWREN

イ ネーブルピ ンは、 ポー ト の読み出 し 、 書 き 込み、 お よ びセ ッ ト/リ セ ッ ト 機能を制御 し ます。 ポー ト の イ ネーブル ピ ン が非ア ク テ ィ ブの と き 、 出力ピ ンは前の状態を維持 し 、 デー タ は メ モ リ セル に書 き 込まれません。イ ネーブルの極性は設定変更可能で、デフ ォ ル ト ではア ク テ ィ ブ High と な っ てい ます。SDP モー ド では、ENA ポー ト が RDEN と な り 、ENB ポー ト が WREN と な り ます。

バイ ト

ラ イ ト

イ ネーブル

- WEA

、

WEBWE

デー タ 入力バ ス の内容を指定 し た メ モ リ 位置に書 き 込むには、 ク ロ ッ ク の立ち上が り エ ッ ジ前の セ ッ ト ア ッ プ タ イ ム中に EN と WE の両方がア ク テ ィ ブにな る 必要があ り ます。デー タ が出力 ラ ッ チに読み込まれ る か ど う かは、 書 き 込みモー ド (WRITE_FIRST、READ_FIRST、NO_CHANGE) の設定に よ っ て決ま り ます。WE が非ア ク テ ィ ブで、EN がア ク テ ィ ブの場合は読み出 し 処理が行 われ、 書 き 込みモー ド の設定にかかわ ら ず、 ア ド レ ス バ ス で指定 さ れた メ モ リ セルの内容がデー タ 出力バ ス に送信 さ れます。 書 き 込み イ ネーブル ピ ンの極性は変更で き ず、 常にア ク テ ィ ブ High です。SDP モー ド では、WEBWE[7:0] ポー ト がバ イ ト ラ イ ト イ ネーブル と な り ます。TDP モー ド では、WEA[3:0] と WEB[3:0] がそれぞれポー ト A と ポー ト B のバ イ ト ラ イ ト イ ネーブル と な り ます。

レ ジ ス タ

イ ネーブル

- REGCEA

、

REGCE

、

REGCEB

レ ジ ス タ イ ネーブルピ ン (REGCE) は、 オプシ ョ ンの出力レ ジ ス タ を制御 し ます。RAM が レ ジ ス タ モー ド の場合、REGCE = 1 と 指定す る と 、 ク ロ ッ ク エ ッ ジで出力が レ ジ ス タ に取 り 込まれます。 REGCE の極性は変更で き ず、 常にア ク テ ィ ブ High です。SDP モー ド では、REGCEA ポー ト が REGCE と な り ます。

セ ッ ト

/

リ セ ッ ト

RSTREGARSTREG

、

RSTREGB

、

RSTRAMARSTRAM

、

RSTRAMB

ラ ッ チモー ド では、RSTRAM ピ ンに よ っ てデー タ 出力 ラ ッ チに SRVAL の値が同期で格納 さ れま す。 詳細は、31ページの 「ブ ロ ッ ク RAM の属性」 を参照 し て く だ さ い。 オプシ ョ ンの出力レ ジ ス タ が有効の場合 (DO_REG = 1)、RSTREG 信号に よ っ てデー タ 出力レ ジ ス タ に SRVAL の値が同期 的に格納 さ れ ます。RSTREG と REGCE の ど ち ら を優先す る かは、RSTREG_PRIORITY 属性で 指定 し ます。 デー タ 出力 ラ ッ チ ま たは出力レ ジ ス タ は、 パ リ テ ィ ビ ッ ト を含め同期で 0 ま たは 1 に アサー ト さ れます。 各ポー ト には、 それぞれ 36 ビ ッ ト の SRVAL[A|B] 属性が指定 さ れます。 こ の 初期化に よ っ て RAM メ モ リ セルが変化す る こ と はな く 、も う 1 つのポー ト での書 き 込みに も 影響 を与え ません。 ど ち ら の信号 も 極性は設定変更可能で、 デフ ォ ル ト ではア ク テ ィ ブ High と な っ て い ます。SDP モー ド では、RSTREGA ポー ト が RSTREG と な り 、RSTRAMA ポー ト が RSTRAM

と な り ます。

ア ド レ ス

バス

- ADDRARDADDR

、

ADDRBWRADDR

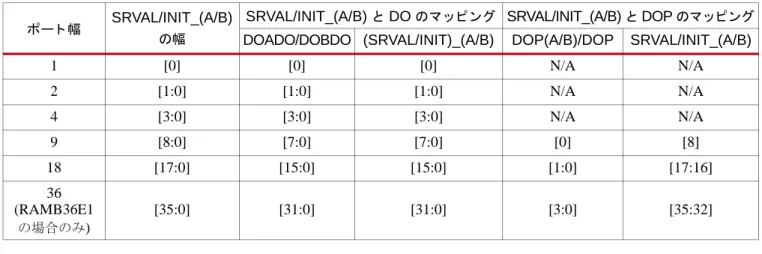

ア ド レ スバ ス は、 読み出 し ま たは書 き 込みを実行す る メ モ リ セルを選択 し ます。SDP モー ド では、 ADDRA ポー ト が RDADDR と な り 、ADDRB ポー ト が WRADDR と な り ます。表1-9、表1-10、

表1-11、表1-12に示す よ う に、RAMB18E1 ま たは RAMB36E1 のア ド レ スバ ス幅は、 ポー ト の デー タ ビ ッ ト 幅に よ っ て決ま り ます。