© 2005–2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

いかな る

FPGA

設計において も 、最高のパフ ォーマ ン ス を得

る ために欠かせない要因の

1

つが、 デザ イ ンの適切な

RTL

記述です。

RTL

レベルの設計中に、ち ょ っ と し た工夫をす る

こ と が、

100MHz

未満で動作す る デザ イ ン か

400MHz

以上

で動作す る デザ イ ンかの明暗を分け る こ と につなが り ます。

安定 し たデザ イ ン

パ フ ォ ーマ ン ス と は、 デザ イ ン

プ ロ セ ス

におけ る 様々な要因を熟慮 し た結果にほかな り ません。

まず

は、デザ イ ンに最 も 適 し たハー ド ウ ェ ア

プ ラ ッ ト フ ォーム を

選択 し な く てはな り ません。

そ し て、 選んだデバ イ ス

アーキ

テ ク チ ャ と 、 イ ンプ リ メ ン テーシ ョ ン

ツールの設定や機能を

検討す る 必要があ り ます。

さ ら に、 こ れは本稿の目的で も あ

り ま す が、 タ ー ゲ ッ ト

デバ イ ス 上 に 効果的 に 配置 で き る

HDL

コ ー ド を記述 し な く てはな り ま せん。

こ れ ら の各項目

の詳細を記載 し た リ ソ ース は、 ウ ェ ブ

サ イ ト に多数掲載 さ れ

てい ます。

本稿では、 デザ イ ン のパフ ォ ーマ ン ス を向上 さ せ

る コ ー ド の記述方法 と そ の ヒ ン ト に焦点 を 当て て紹介 し ま

す。

適切な

FPGA

コ ーデ ィ ン グ方法を繰 り 返 し 述べつつ、 あ

ま り 知 ら れ て い な い な が ら も 、 最新のザ イ リ ン ク ス

FPGA

アーキ テ ク チ ャ にその ま ま応用可能な技術を紹介 し ます。

WP231 (1.1) 2006 年 1 月 6 日デザイ ン

パフ ォ ーマ ン ス向上の

ための

HDL

コ ーデ ィ ング法

リ セ ッ ト の使用 と

パ フ ォ ーマ ン ス

シ ス テ ム規模のオプシ ョ ンの う ち、 パフ ォーマ ン スやエ リ ア、 消費電力に大 き な影 響をお よ ぼすオプシ ョ ンが リ セ ッ ト です。シ ス テ ム設計者の中には、 グ ロ ーバル非 同期 リ セ ッ ト の使用を電源投入時の回路の初期化に限定す る 設計者 も い ますが、 こ れはFPGA

設計に と っ ては不要な こ と です。ザ イ リ ン ク ス のFPGA

アーキ テ ク チ ャ では、 リ セ ッ ト の使用 と その タ イ プがデザ イ ンのパフ ォーマ ン ス と 密接に関係 し て い る ため、 次の よ う な リ セ ッ ト ス ト ラ テジがあ り ます。•

シ フ ト レ ジ ス タ ル ッ ク ア ッ プ テーブル(SRL)

の よ う な、デバ イ ス の ラ イ ブ ラ リ コ ン ポーネ ン ト の使用を抑制す る 。•

専用のハー ド ウ ェ ア ブ ロ ッ ク の同期エ レ メ ン ト の使用を控え る 。•

フ ァ ブ リ ッ ク 内の ロ ジ ッ ク を最適化 し ない。•

リ セ ッ ト 信号の フ ァ ン ア ウ ト は大 き く な る 場合があ る ため、 配置配線を厳 し く 制 約す る 。SRL

すべての最新ザ イ リ ン ク スFPGA

アーキ テ ク チ ャ では、 ル ッ ク ア ッ プテーブル(LUT)

エ レ メ ン ト を ロ ジ ッ ク 、ROM/RAM

あ る いはSRL

と し て コ ン フ ィ ギ ュ レー シ ョ ンで き ます。合成ツールでは、RTL

コ ー ド か ら ど の構造が使用 さ れてい る かが 推論で き ます。 ただ し 、SRL

の ラ イ ブ ラ リ コ ン ポーネ ン ト が リ セ ッ ト 機能を持たな いため、 パフ ォーマ ン ス を最適化 し たシ フ ト レ ジ ス タ(SRL)

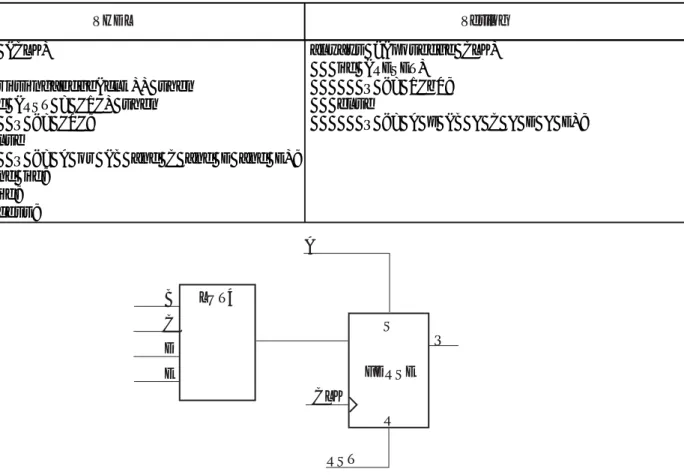

を使用す る 場合に リ セ ッ ト が コ ーデ ィ ン グで き ません。リ セ ッ ト を コ ーデ ィ ン グ し て シ フ ト レ ジ ス タ を 推論す る 場合には、数個の フ リ ッ プ フ ロ ッ プ、 あ る いは ロ ジ ッ ク を周辺に追加 し て リ セ ッ ト を機能 さ せ る 必要があ り ます。図1

に示す よ う に、 シ フ ト レ ジ ス タ で リ セ ッ ト を使用 し ない コ ーデ ィ ン グでは、 通常、 出力で形成 さ れ る レ ジ ス タ は1

つな ので、 エ リ アお よ びパフ ォーマ ン ス は最適 と な り ます。 リ セ ッ ト を使用 し ない場合に比べ、 使用 し た場合にエ リ ア と 消費電力に及ぼす効果 は明 ら かですが、 パフ ォーマ ン ス に与え る 影響はそれほ ど明確ではあ り ません。通 常、 レ ジ ス タ 間の タ イ ミ ン グ パ ス(

フ リ ッ プ フ ロ ッ プのClock-to-Out

、 配線遅延、 次の フ リ ッ プ フ ロ ッ プのセ ッ ト ア ッ プ タ イ ム)

はデザ イ ン内の最長パス にな ら ない ため、 フ リ ッ プ フ ロ ッ プで構築 し たシ フ ト レ ジ ス タ のパフ ォーマ ン ス が ク リ テ ィ カ ルにな る こ と はあ り ません。ただ し 、 リ ソ ース の追加使用(

フ リ ッ プ フ ロ ッ プお よ び 配線)

がデザ イ ンの他の部分の配置配線にマ イ ナ ス の影響を与え、 配線遅延が長 く な る 場合があ り ます。SRL

に さ ら に ロ ジ ッ ク を追加 し て リ セ ッ ト 機能を持たせ る と 、 追加 し た ロ ジ ッ ク 部分がSRL

のClock-to-Out

に影響を与え、 デー タ が目的の ロ ジ ッ ク に到達す る ま で時間がかか り 、 パフ ォーマ ン ス が低下 し ます。 ヒ ン ト 図 1 : パ フ ォ ーマ ン ス を最適化 し たシ フ ト レ ジ ス タ D Q Q15 Address CE (Write Enable) CLK SRLC16E D Q Synchronous Output WP231_01_110905 FF乗算器 と

RAM

最新のザ イ リ ン ク ス

FPGA

アーキ テ ク チ ャ では、 すべてに専用の演算 リ ソ ース があ り ます。こ の リ ソ ース は、 多数のDSP

アルゴ リ ズ ム な ど で乗算に使用で き ますが、 バレル シ フ タ な ど のアプ リ ケーシ ョ ン で も 使用で き ます。同様に、 さ ま ざ ま なサ イ ズの

RAM

が、 ほぼすべてのFPGA

で、 アプ リ ケーシ ョ ン を問わず使用 さ れてい ます。すべてのザ イ リ ン ク スFPGA

には、RAM

、ROM

、 大 規模LUT

、 さ ら には汎用 ロ ジ ッ ク と し て使用で き る ブ ロ ッ クRAM

エ レ メ ン ト があ り ます。乗算器 とRAM

リ ソ ース の両方を利用す る こ と で、 よ り コ ンパ ク ト で高性 能なデザ イ ンが実現で き ます。 パフ ォーマン ス においては、 選択す る リ セ ッ ト の タ イ プに よ っ てデザ イ ンに与え る 影響が違い ます。乗算器ブ ロ ッ ク お よ びRAM

レ ジ ス タ は、 共に同期 リ セ ッ ト だけ を有 し ますので、 こ れ ら の機能に対 し て非同期 リ セ ッ ト を コ ーデ ィ ン グす る と 、 ブ ロ ッ ク 内の レ ジ ス タ が使用で き な く な り ます。こ れに よ っ て、 パフ ォーマ ン ス に多 大な影響を及ぼ し ます。た と えば、 最高速のVirtex

TM-4

を タ ーゲ ッ ト デバ イ ス と し て、 完全にパ イ プ ラ イ ン化 さ れた乗算器で非同期 リ セ ッ ト を使用す る と 、 パフ ォー マ ン ス は、 約200MHz

に下が り ます。同期 リ セ ッ ト を使 う よ う 再 コ ーデ ィ ン グす る と 、 パフ ォーマ ン ス は2

倍以上の500MHz

に向上 し ます。Virtex-4

のブ ロ ッ クRAM

は、 乗算器 と 同様にオプシ ョ ンの レ ジ ス タ を備え てい ま す。こ れ ら の出力レ ジ ス タ を使用す る と 、RAM

の ク ロ ッ ク か ら 出力ま での時間が短 縮 し 、 デザ イ ン全体の処理速度が向上 し ます。オプシ ョ ンの レ ジ ス タ には リ セ ッ ト ポー ト がないため、 リ セ ッ ト の ビヘ イ ビ ア を コ ーデ ィ ン グ し て も 、 結果的に出力レ ジ ス タ は イ ネーブル さ れません。 ま た、RAM

をLUT

あ る いは汎用 ロ ジ ッ ク と し て使用す る 際に派生す る 問題があ り ます。時には、 エ リ ア と パフ ォーマ ン ス の理由か ら 、ROM

や汎用 ロ ジ ッ ク と し て コ ン フ ィ ギ ュ レーシ ョ ン し た複数のLUT

を1

個のブ ロ ッ クRAM

に圧縮す る こ と が有 効な場合があ り ます。方法 と し ては、 こ れ ら の構造を マニ ュ アルで指定す る か、 も し く は、 合成ツールに制約を加え、 自動的に ロ ジ ッ ク デザ イ ンのその部分を未使用 のブ ロ ッ ク

RAM

リ ソ ース にマ ッ プす る かのいずれかです。ブ ロ ッ クRAM

の リ セ ッ ト コ ン フ ィ ギ ュ レーシ ョ ンに よ り 、 同期 リ セ ッ ト を使用す る 場合や、 リ セ ッ ト を全 く 使用 し ない場合には、 デザ イ ン機能を変更せずに、 汎用 ロ ジ ッ ク が配置で き ます。 ヒ ン ト•

レ ジ ス タ を専用 リ ソ ース にパ ッ ク で き な く な り 、 パフ ォーマ ン ス、 使用率、 ツー ルの最適化に影響を与え る ため、 非同期 リ セ ッ ト の使用は避け る 。汎用ロ ジ ッ ク

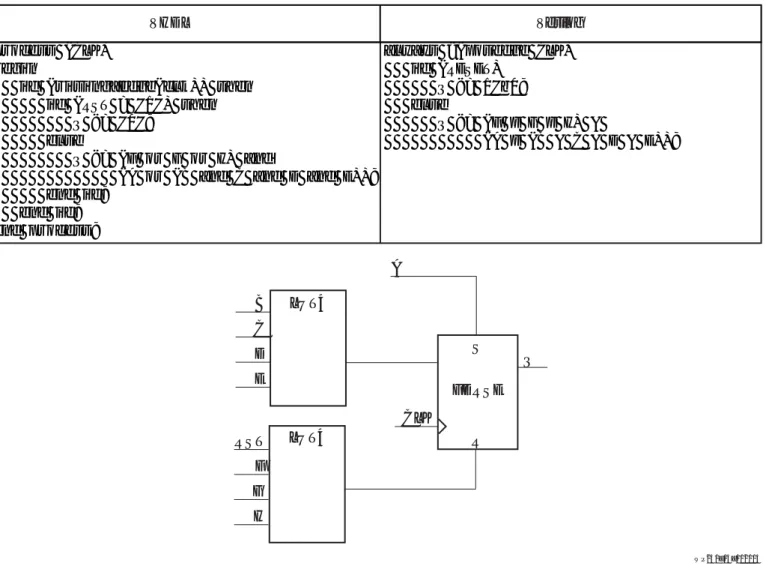

非同期 リ セ ッ ト の影響は、 汎用 ロ ジ ッ ク 構造のパフ ォーマ ン ス に も 現れます。FPGA

のすべての汎用レ ジ ス タ がセ ッ ト お よ び リ セ ッ ト を同期ま たは非同期のいずれにで も プ ロ グ ラ ムで き る ため、 非同期 リ セ ッ ト を使用 し て も 問題がない よ う に思え ます が、 それは得て し て誤 り です。非同期 リ セ ッ ト が ど の よ う に最適化を妨げ る か、図2

に コ ー ド 例を示 し ます。非同期 リ セ ッ ト を使用 し ない場合、 信号が必要 と す る リ ソ ース が利用で き る ため、 レ ジ ス タ を駆動 し てい る 他の同期パ ス が最適化で き ます(

図3

のFDRSE

を参照)

。 例1 :

非同期 リ セ ッ ト コ ー ド を イ ンプ リ メ ン ト す る 場合には、 ロ ジ ッ ク 生成に5

つの信号 が使用 さ れ る ため、 合成ツールでデー タ パ ス に対す る2

つのLUT

の推論が必要に な り ます。こ の コ ー ド は、 図2

の よ う に イ ンプ リ メ ン ト で き ます。例

2 :

同期 リ セ ッ ト を使用 し て こ の コ ー ド を書 き 換え る と 、 合成ツールでは、 機能の イ ン プ リ メ ン ト に よ り 柔軟に対応で き ます。こ の コ ー ド は、図3

の よ う に イ ンプ リ メ ン ト で き ます。 図 2 : 非同期 リ セ ッ ト のイ ン プ リ メ ン ト A B C D E LUT4 LUT4 CLK RST CLR FDCE WP231_02_112105 process (CLK, RST) begin if (RST = '1') then Q <= '0';elsif (rising_edge(clk)) then

Q <= A or (B and C and D and E); end if;

end process;

always @(posedge CLK, posedge RST) if (RESET)

Q <= 1'b0; else

Q <= A | (B & C & D & E);

VHDL Verilog

図

3

で示 し た イ ンプ リ メ ン ト では、 合成ツールはA

がア ク テ ィ ブHigh

の と き 、Q

が常に ロ ジ ッ ク1

であ る と 認識 し ます(OR

フ ァ ン ク シ ョ ン)

。FDRSE

レ ジ ス タ は同 期セ ッ ト あ る いは リ セ ッ ト と し て コ ン フ ィ ギ ュ レーシ ョ ン さ れてい る ため、 セ ッ ト は同期デー タ パ ス の一部 と し て自由に使用で き ます。 例3 :

非同期セ ッ ト あ る いは リ セ ッ ト がパフ ォーマ ン ス に深 く 関わ り があ る こ と を示す、8

つの信号を使用 し た さ ら に複雑な機能を見てみます。こ の機能の イ ンプ リ メ ン ト に は、 最低で も3

つのLUT

が必要です。こ の コ ー ド は、図4

の よ う に イ ンプ リ メ ン ト で き ます。 図 3 : 同期 リ セ ッ ト のイ ン プ リ メ ン ト でパ フ ォ ーマ ン スが改善 C B E D LUT4 CLK RST Q R S FDRSE WP231_03_112105 A VHDL Verilog process (CLK) begin if (rising_edge(clk)) then if (RST = '1') then Q <= '0'; elseQ <= A or (B and C and D and E); end if; end if; end process; always @(posedge CLK) if (RESET) Q <= 1'b0; else

例

4

こ の コ ー ド は、 同期 リ セ ッ ト を使用 し て 図5

の よ う に書 き 換え、 イ ンプ リ メ ン ト で き ます。 図 4 : 8 つの入力機能を使用 し た非同期 リ セ ッ ト のイ ン プ リ メ ン ト B A C D E LUT4 F G H LUT4 LUT4 CLK RST Q CLR FDCE WP231_04_112105 VHDL Verilog process (CLK, RST) begin if (RST = '1') then Q <= '0';elsif (rising_edge(clk)) then Q <= (F or G or H) and

(A or (B and C and D and E)); end if;

end process;

always @(posedge CLK, posedge RST) if (RESET)

Q <= 1'b0; else

Q <= (F | G | H) &

図

5

の イ ンプ リ メ ン ト 結果が示す よ う に、 同 じ ロ ジ ッ ク フ ァ ン ク シ ョ ンの イ ンプ リ メ ン ト に使用す るLUT

が少な く て済む う え、 こ の フ ァ ン ク シ ョ ン を生成す る 各信号 で ロ ジ ッ ク レベルが減少す る ため、 デザ イ ンが よ り 高速化 さ れます。デザ イ ン内の ロ ジ ッ ク の多 く は同期なので、 同期を使用す る 場合、 あ る いは リ セ ッ ト を ま っ た く 使用 し ない場合には、 デザ イ ン を さ ら に最適化 し 、 エ リ ア を縮小 さ せ、 パフ ォーマ ン ス が向上で き ます。 ヒ ン ト•

グ ロ ーバル リ セ ッ ト が必要か ど う か を確認す る 。•

非同期制御信号の使用を控え る 。加算器ツ リ ーではな く 加算器チ ェ ーン を使用する

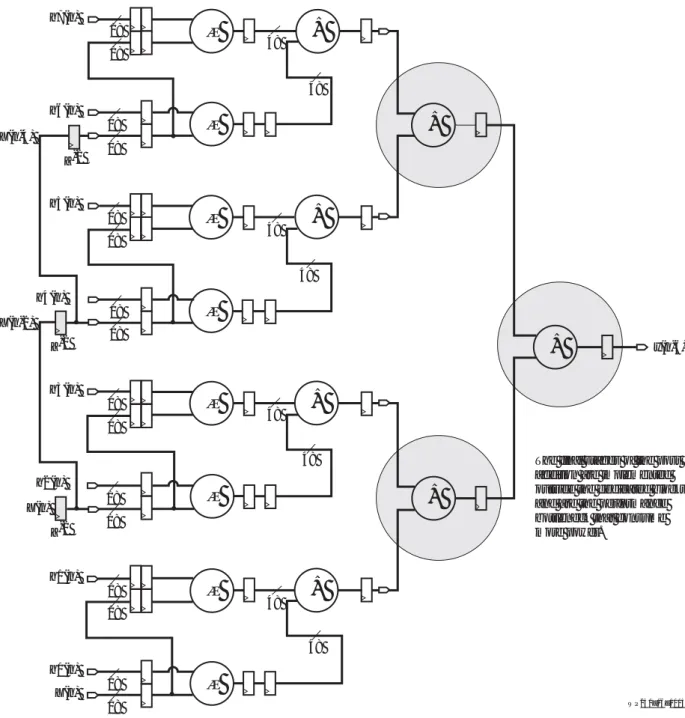

多 く の信号処理アルゴ リ ズ ムでは、 サンプルの入力ス ト リ ームに四則演算を実行後、 こ の四則演算のすべての出力の和を求め ます。FPGA

の よ う なパ ラ レル アーキ テ ク チ ャ では、 和を イ ンプ リ メ ン ト す る ため、 加算器には一般的に ツ リ ー構造が使われ ます。加算器ツ リ ーの使用で懸念 さ れ る のは、 サ イ ズが変化す る 点です。加算器の数 は、 加算器ツ リ ーの入力数で決ま り ます。加算器ツ リ ーの入力数が多いほ ど、 必要 な加算器の数 も 増え、 ロ ジ ッ ク リ ソ ースや消費電力 も 増加 し ます。ま た、 大 き な ツ リ ーほ ど ツ リ ーの末端に進むに し たがい、 加算器の規模が大型化 し 、 ロ ジ ッ ク レベ 図 5 : 同期制御信号で ロ ジ ッ ク レ ベル数が削減で き る LUT4 CLK A B C D E RST F G H Q S R LUT4 FDRSE WP231_05_112105 VHDL Verilog process (CLK) begin if (rising_edge(clk)) then if (RST = '1') then Q <= '0'; else Q <= (F or G or H) and(A or (B and C and D and E)); end if; end if; end process; always @(posedge CLK) if (RESET) Q <= 1'b0; else Q <= (F | G | H) &

ル数が増え、 シ ス テ ム パフ ォーマ ン ス の悪化を招 き ます。デバ イ ス の使用率 と 消費 電力を で き る だけ抑え、 加算器ツ リ ーのパフ ォーマ ン ス を維持す る には、 加算器ツ リ ーを専用のシ リ コ ン リ ソ ース と し て イ ンプ リ メ ン ト し ます

(

図6

参照)

。し か し 、 シ リ コ ン エ リ ア を縮小 し 、 かつ加算器ツ リ ーの大半を専用 リ ソ ース内に イ ンプ リ メ ン ト す る のは、FPGA

の製造 メ ーカには不可能です。Virtex-4

デバ イ ス フ ァ ミ リ は、DSP48

専用シ リ コ ンの列を使用す る と い う 別の手段 で和を イ ンプ リ メ ン ト し ます。図

7

に示す よ う に、 加算器ツ リ ーではな く 、 チ ェ ー ン型の加算器を使用 し て和を イ ン ク リ メ ン ト さ せ、 算出 し ます。こ の方法は、 従来 の

FPGA

と は一線を画 し 、ロ ジ ッ ク と イ ン タ ー コ ネ ク ト の両者全体が専用シ リ コ ン 内に存在す る こ と か ら 、DSP

アルゴ リ ズ ムのパフ ォーマ ン ス の最大化お よ び消費電 力の低減につなが り ます。 ま た、パ イ プ ラ イ ン化す る と 、DSP48

ブ ロ ッ ク のパ フ ォーマ ン ス は、 加算器の数にかかわ ら ず、 最速の ス ピー ド グ レー ド で500MHz

と な り ます。48

ビ ッ ト の加算器あ る いはア キ ュ ム レー タ を組み合わせたポー ト を カ ス ケー ド 接続す る と 、 現在のサンプルの算出に加え、 それま でに算出 し たすべてのサ ンプルの和 も 計算で き ます。図 6 : 加算器のツ リ ー構造がパ フ ォ ーマ ン ス を低下 さ せ、 消費電力を増加 さ せる 48 48 y(n-6) 18 18 48 48

×

+

+

18 18 18 18 18 18 h0(n) X(n) h1(n) 48 48 18 18 48 48×

+

×

18 18×

18 18 18 18 h2(n) X(n) h3(n) h4(n) X(n-2) X(n-4) h5(n) h6(n) h7(n)+

+

Z-2 Z-2 Z-2×

×

×

×

+

The final stages of the post addition are implemented outside the dedicated blocks and are the performance bottleneck that consume more power.

WP231_06_111505

+

Virtex-4

の加算器のチ ェーン構造を利用す る には、 加算器ツ リ ーの記述を加算器 チ ェ ーンの記述に置 き 換え ます。ダ イ レ ク ト フ ォーム フ ィ ル タ か ら 転置フ ィ ル タ へ の変換、 あ る いはシ ス ト リ ッ ク フ ォーム フ ィ ル タ への変換方法は、UG073:

『FPGA

のXtremeDSP

ユーザーガ イ ド 』 を参照 し て く だ さ い。 通常、 こ の変換に よ っ て、 デザ イ ンに レ イ テ ン シが追加 さ れます。変換終了後、 アルゴ リ ズ ムはアプ リ ケーシ ョ ンの要求す る 以上に高速で動作 し ます。その場合、 マルチチ ャ ネ リ ン グ やフ ォールデ ィ ン グ な ど のいずれかの手法を使用 し て、 デバ イ ス の使用率や消費電 力を さ ら に向上で き ます。いずれの手法 も 、 小型デバ イ スへのデザ イ ンの イ ンプ リ 図 7 : チ ェ ーン型の加算器でパフ ォ ーマ ン スが予測で き る Slice 7 Slice 8 Slice 6 Slice 5 48 48 48 18 18 48 48 48 48×

×

+

×

18 18 18 18×

18 18 48 Y(n–10) h0(n) X(n) h1(n-1) Slice 3 Slice 4 Slice 2 Slice 1 Zero 48 48 48 18 18 48 48 48 48×

×

×

18 18 18 18×

18 18 h2(n-2) h3(n-3) h4(n-4) h5(n-5) h6(n-6) h7(n-7) 48The post adders are contained wholly in dedicated silicon for highest performance and lowest power.

+

+

+

+

+

+

+

有効です。

•

マルチチ ャ ネ リ ン グ と は、 非常に高速な演算エ レ メ ン ト を利用 し て、 は る かに低 いサンプル率で複数入力ス ト リ ーム(

チ ャ ネル)

を処理す る こ と です。こ の手法 は、 シ リ コ ン効率をチ ャ ネル数 と ほぼ等倍に高め ます。マルチチ ャ ネル フ ィ ル タ リ ン グは、 時分割多重化単一チ ャ ネル フ ィ ル タ と し て見 る こ と がで き ます。た と えば、 一般的なマルチチ ャ ネル フ ィ ル タ リ ン グでは、 各チ ャ ネルに個別のデジ タ ル フ ィ ル タ を使用 し て、 複数入力チ ャ ネルが フ ィ ル タ リ ン グ さ れます。Virtex-4

のDSP48

ス ラ イ ス を利用す る と 、8

倍 ク ロ ッ ク の単一フ ィ ル タ で ク ロ ッ キ ン グで き る ため、 単一デジ タ ル フ ィ ル タ で8

つすべての入力チ ャ ネルが フ ィ ル タ リ ン グで き ます。 し たが っ て、FPGA

に必要な リ ソ ース数が約1/8

に削 減で き ます。•

フ ォールデ ィ ン グは同様の概念で動作 し ます。時分割多重化複数入力ス ト リ ーム を使用せずに、 個別フ ィ ル タ の タ ッ プ を時分割多重化す る と 、 フ ィ ル タ が使用す る リ ソ ース が少な く な り ます。空いた リ ソ ース は別の用途に使用で き ます。 ヒ ン ト•

Virtex-4

の加算器を ツ リ ー構造にせず、 カ ス ケー ド 接続 し た記述を使用す る。ブ ロ ッ ク

RAM

のパ フ ォ ーマ ン ス を最大化

メ モ リ エ レ メ ン ト を効率的に推論す る 場合、 パフ ォーマ ン ス に影響を与え る 次の要 因を考慮す る 必要があ り ます。•

専用ブ ロ ッ クRAM

と 分散RAM

の ど ち ら を使用す る か。•

出力パ イ プ ラ イ ン レ ジ ス タ を使用す る 。•

非同期 リ セ ッ ト の使用を控え る 。 他の要因 と し ては、HDL

の コ ーデ ィ ン グ ス タ イ ル と 合成ツールの設定が メ モ リ の パフ ォーマ ン ス に大 き く 影響 し ます。HDL

コ ーデ ィ ン グ ス タ イル デ ュ アルポー ト ブ ロ ッ ク メ モ リ を推論す る 場合、2

つのポー ト が同 じ メ モ リ セル に同時にア ク セ スす る こ と が考え ら れます。た と えば、 両ポー ト が、 異な る 値を同 時に同 じ メ モ リ セルに書 き 込みす る と 、 競合が発生 し 、 メ モ リ セルの内容が不安定 にな り ます。 ま た、 メ モ リ の コ ン フ ィ ギ ュ レーシ ョ ン で懸念 さ れ る 例には、 タ ーゲ ッ ト デバ イ ス に よ っ て メ モ リ の出力値が異な る 点があ り ます。最新のVirtex

お よ びSpartan

TM フ ァ ミ リ は、 プ ロ グ ラ マブルな3

種の動作モー ド に よ っ て、 書 き 込み中の メ モ リ 出力が 管理で き ます。デバ イ ス のユーザーガ イ ド に、 こ れ ら の動作モー ド の詳細が記載 さ れてい ます。 例5 :

合成ツールは、 表1

に示 し た よ う に、 コ ーデ ィ ン グ ス タ イ ルに よ っ て こ れ ら のモー ド のいずれかを推論で き ます。ヒ ン ト

•

「書 き 込み前に読み出 し 」 モー ド を使用せず、 ブ ロ ッ クRAM

のパフ ォーマ ン ス の最大化を実現す る 。 合成ツールの設定 ブ ロ ッ ク メ モ リ のパフ ォーマ ン ス に大 き な影響を与え る 要因で、 次に重要なのは合 成ツールの設定です。合成ツール(Synplicity

社のSynplify

な ど)

に よ っ ては、RAM

の周囲にバ イ パ ス ロ ジ ッ ク を挿入 し 、RTL

と ハー ド ウ ェ ア間で発生す る おそ れのあ る ミ ス マ ッ チを回避 し ます。こ の余剰 ロ ジ ッ ク には、 読み出 し お よ び書 き 込 みが同 じ メ モ リ セルで実行 さ れ る 場合の既知の値へのRAM

出力を強化す る 目的が あ り ます。同 じ メ モ リ セルで絶対に読み出 し と 書 き 込みが同時に実行 さ れない設計 であれば、 合成ツールでアプ リ ケーシ ョ ンにバ イ パス ロ ジ ッ ク が追加 さ れない よ う 設定で き ます(

表2

を参照)

。余剰 ロ ジ ッ ク には、 メ モ リ のすべての出力パス上に オーバーヘ ッ ド ロ ジ ッ ク を追加す る ため、 メ モ リ パフ ォーマ ン スへのマ イ ナ ス の影 響 も あ り ます。追加 ロ ジ ッ ク を回避、 あ る いは使用 し ない こ と が、 メ モ リ パフ ォー マ ン ス の維持につなが り ます。 表 1 : ブ ロ ッ ク RAM オペ レ ーテ ィ ン グ モー ド イ ン タ ー フ ェ イ スの用例 VHDL Verilog-- 'write first' or transparent mode process (clk) begin if (rising_edge(clk)) then if (we = '1') then mem(conv_integer(addr)) <= di ; do <= di; else do <= mem(conv_integer(addr)); end if; end if; end process;

-- 'read first' or read before write(slower) process (clk) begin if (rising_edge(clk)) then if (we = '1') then mem(conv_integer(addr)) <= di; end if; do <= mem(conv_integer(addr)); end if; end process;

-- 'no change' mode process (clk) begin if (rising_edge(clk)) then if (we = '1') then mem(conv_integer(addr)) <= di ; else do <= mem(conv_integer(addr)); end if; end if; end process;

// 'write first' or transparent mode always @(posedge clk) begin

if(we) begin do <= data; mem[address] <= data; end else do <= mem[address]; end

// 'read first' or read before write mode(slower) always @(posedge clk) begin

if (we)

mem[address] <= data; do <= mem[address]; end

// 'no change' mode always @(posedge clk) if (we) mem[address] <= data; else do <= mem[address]; end

ヒ ン ト

•

合成ツールの設定、 テ ンプ レー ト の推論、 メ モ リ ブ ロ ッ ク のパフ ォーマ ン ス を 最大化す る ための制限事項を確認す る 。レ ジ ス タ の一般的な使用方法

FPGA

アーキ テ ク チ ャ では、 各LUT

に1

つの レ ジ ス タ があ り 、I/O

には、 メ モ リ エレ メ ン ト や

DSP

エ レ メ ン ト の よ う な専用ブ ロ ッ ク や追加レ ジ ス タ があ り ます。こ の よ う な リ ソ ース を使用す る こ と が、 パフ ォーマ ン ス の最大化の実現に不可欠 と な り ます。レ ジ ス タ には、 デザ イ ン パフ ォーマ ン ス を向上 さ せ る 複数の目的があ り ます。 こ れ ら の レ ジ ス タ は、 ク リ テ ィ カルパ ス、 ク リ テ ィ カル ネ ッ ト の フ ァ ン ア ウ ト 、 セ ッ ト ア ッ プ、I/O

あ る いは専用ブ ロ ッ ク か ら のClock-to-Out

で、 ロ ジ ッ ク レベル 数の削減に使用 さ れます。使用可能な レ ジ ス タ を最適化す る ためのガ イ ド ラ イ ンは 後述 し ます。 専用ブ ロ ッ ク レ ジ ス タ の使用FPGA

には、 メ モ リ やDSP

と い っ た、 ほぼすべてのデザ イ ンで使用す る 機能の専用 回路があ り ます。こ れ ら のブ ロ ッ ク にはオプシ ョ ンの レ ジ ス タ があ り ます。こ れ ら の レ ジ ス タ を イ ネーブルにす る と 、 セ ッ ト ア ッ プ、Clock-to-Out

と ブ ロ ッ ク ク ロ ッ ク 速度のいずれかあ る いは両方のブ ロ ッ ク パフ ォーマ ン ス が向上で き ます。合成ツー ルは、 エ リ ア を最小限に抑え、 消費電力を削減 し 、 パフ ォーマ ン ス を最大に引 き 上 げ る ため、 こ れ ら のブ ロ ッ ク に レ ジ ス タ を自動的にパ ッ ク し よ う と し ます。設計者 は、 合成ツールで制約を与え て、 推論 し た コ ン ポーネ ン ト のマ ッ ピ ン グ を制御で き ます。こ れ ら のブ ロ ッ ク を イ ン ス タ ン シエー ト す る 際、 アプ リ ケーシ ョ ンのパ フ ォーマ ン ス を最大化す る レ ジ ス タ を イ ネーブルにす る 必要があ り ますが、 合成 ツールのデフ ォ ル ト 設定では、 ユーザーが イ ン ス タ ン シエー ト し た ア キ テ ク チ ャ の コ ン ポーネ ン ト が最適化 さ れません。最高のパフ ォーマ ン ス を導 く ためにすべての レ ジ ス タ を イ ネーブルにす る こ と が理想的ですが、 レ イ テ ン シの要件を常に満たす と は限 り ません。その場合は、 設計者の責任において適切な レ ジ ス タ の集合を イ ネーブルにす る 必要があ り ます。た と えば、 乗算器

(MREG)

と 入力レ ジ ス タ(AREG

お よ びBREG)

だけが使用 さ れ る 場合、Virtex-4 DSP48

のセル(

高速の スピー ド グ レー ド

)

は1.8ns

、Clock-to-Output

が2.3ns

と な り ます。同 じ 機能 と レ イ テ ン シ を維持 し なが ら 、MREG

ではな く ア キ ュ ム レー タ の出力レ ジ ス タ(PREG)

を イ ネーブルにす る と 、 セ ッ ト ア ッ プ タ イ ムが3ns

に延び、Clock-to-Out

は0.6ns

に短 縮 し ます。詳細は、 図

8

を参照 し て く だ さ い。 表 2 : 競合を避け る グルー ロ ジ ッ ク の挿入をデ ィ ス エーブルにする VHDL Verilogtype mem_type is array (127 downto 0) of

std_logic_vector (7 downto 0); signal mem : mem_type;

-- disable conflict avoidance logic attribute syn_ramstyle of mem : signal is

"no_rw_check";

// disable conflict avoidance logic reg [7:0] mem [127:0] /* synthesis

次の項目を考慮す る こ と が重要です。

•

駆動す る ロ ジ ッ ク の タ イ ミ ン グ、 あ る いは専用ブ ロ ッ ク で駆動 さ れ る ロ ジ ッ ク の タ イ ミ ン グ•

HDL

コ ー ド 内の レ ジ ス タ の位置 ヒ ン ト•

専用ブ ロ ッ ク を推論す る 場合、 合成ツールが、 パフ ォーマ ン ス を最良にす る レ ジ ス タ のセ ッ ト を イ ネーブルに し ない場合に合成制約を使用す る(

イ ン ス タ ン シ エーシ ョ ンについて考慮が必要)

。•

イ ン ス タ ン シエー ト し た コ ン ポーネ ン ト に ど の レ ジ ス タ を イ ネーブルにす る か選 択す る 場合、 レ ジ ス タ の最大数が使用 さ れ る こ と を確認 し 、 ブ ロ ッ ク 内の レ ジ ス タ か ら レ ジ ス タ への遅延、 お よ びレ ジ ス タ 間の遅延を考慮す る 。I/O

レ ジ ス タ を使用する ザ イ リ ン ク ス のすべてのFPGA

は、FPGA

の入力パ ス と 出力パ ス に専用の レ ジ ス タ を備え てい ます。こ の レ ジ ス タ を利用 し て、 入力パ ス のセ ッ ト ア ッ プ タ イ ムお よ び 出力パス のClock-to-Out

を短縮 し 、 外部デバ イ スへのデー タ 供給の タ イ ミ ン グ要件 を容易に満たす こ と がで き ます。ただ し 、 場合に よ っ ては専用のI/O

レ ジ ス タ を使用 す る こ と で、FPGA

内の タ イ ミ ン グにマ イ ナ ス の影響が出 る 場合があ り ます。 内部 ロ ジ ッ ク への配線遅延を促すケース です。 こ れ ら の レ ジ ス タ は、I/O

の タ イ ミ ン グ を満たす こ と が不可欠な場合にはI/O

内に配置 し 、 そ う でない場合はFPGA

フ ァ ブ リ ッ ク 内に配置すべ き です。Synplify

の よ う な合成ツールでは、 タ イ ミ ン グ仕様に し たが っ て、 フ ァ ブ リ ッ ク 内あ る いはI/O

内に自動的に レ ジ ス タ が配置 さ れます。合 成ツールが自動配置を サポー ト し ていない場合、 あ る いは レ ジ ス タ を手動で制御 し なが ら 配置 し たい場合は、 次の手順を実行 し て く だ さ い。1.

合成ツール(

合成ツール資料を参照)

のグ ロ ーバルI/O

レ ジ ス タ 配置オプシ ョ ン をデ ィ ス エーブルにす る 。2. IOB=TRUE

をUCF

フ ァ イ ルあ る いは ソ ースHDL

コ ー ド に追加 し て、 レ ジ ス タ をI/O

に配置指定す る(

制約ガ イ ド のIOB

制約を参照)

。3. ISE Project Navigator

でMap

オプシ ョ ン[Pack I/O Registers/Latches into IOBs]

をデ ィ ス エーブルにす る

(

あ る いは、 コ マ ン ド ラ イ ンか ら-pr

ス イ ッ チを使用 し ない)

。こ の設定に よ っ て、 レ ジ ス タ はI/O

に自動的に配置 さ れません。図9

を 参照 し て く だ さ い。 図 8 : DSP48 内部レ ジ ス タ AREG BREG WP231_08_111405×

+

MREG PREG 48I/O

レ ジ ス タ の使用を制御す る こ と で、FPGA

内部の タ イ ミ ン グ仕様を満たす必要 のあ るFPGA

への入出力のデー タ パス の タ イ ミ ン グのバ ラ ン ス を取 り ます。ま た、 画期的な方法 と し て、FPGA

へのすべての入出力ポー ト 上の レ ジ ス タ が最上位のHDL

コ ー ド で記述で き ます。コ ー ド の最上位階層で レ ジ ス タ を指定す る と 、FPGA

の イ ンプ リ メ ン ト に階層デザ イ ン手法を使用 し た場合の配置の競合が回避で き ます。 ま た、 ボー ド 基板のキ ャ プチ ャ ツールで使用で き ない場合があ る ポー ト の記述用の 階層名を作成す る 必要 も あ り ません。 ヒ ン ト•

I/O

セルへの レ ジ ス タ のグ ロ ーバルパ ッ ク をデ ィ ス エーブルにす る 。その代わ り 、 回路基板上で タ イ ミ ン グが ク リ テ ィ カルな レ ジ ス タ だけは、FPGA

のI/O

セルにパ ッ ク さ れ る よ う 制約 し ます。 フ ァ ン アウ ト の大き いレ ジ ス タ を複製する レ ジ ス タ の複製手法を使用す る と 、 複製 さ れた レ ジ ス タ が信号の フ ァ ン ア ウ ト を小 さ く し 、 ク リ テ ィ カルパ ス の動作速度を向上で き ます。こ の方法に よ っ て、 イ ンプ リ メ ン テーシ ョ ン ツールで異な る ロ ー ド 信号や関連 ロ ジ ッ ク の配置配線にゆ と り が で き ます。合成ツールでは、 こ の手法が頻繁に用い ら れます。タ イ ミ ン グ レ ポー ト で、 配線遅延の長い、 フ ァ ン ア ウ ト の小 さ いネ ッ ト が ク リ テ ィ カルパス と さ れた場 合には、 合成ツールでの複製制約あ る いは手動複製レ ジ ス タ を考慮す る 必要があ り ます。表3

に、64

ロ ー ド 信号を手動で一度に複製す る 方法をHDL

コ ー ド で示 し ま す。 図 9 : レ ジ ス タ が I/O セルに無差別にパ ッ ク さ れないよ う にする WP231_09_110905例

6 :

通常、 手動で複製 し た レ ジ ス タ が合成ツールで自動的に最適化 さ れない よ う 、 合成 制約を さ ら に追加す る 必要があ り ます。上記の例では、XST

構文(EQUIVALENT_REGISTER_REMOVAL)

が使用 さ れてい ます。 合成ツールの多 く は、 フ ァ ン ア ウ ト の し き い値を利用 し て、 レ ジ ス タ を複製す る か ど う かを自動的に判別 し ます。し き い値を グ ロ ーバルに調整す る こ と で、 フ ァ ン ア ウ ト の大 き いネ ッ ト を自動的に複製す る こ と がで き ますが、 ど の レ ジ ス タ を複製す べ き かを設計者が制御で き る ほ ど高機能ではあ り ません。さ ら な る 措置 と し て、 特 定の レ ジ ス タ か階層レベルに属性を与え る か、 ど の レ ジ ス タ を複製 し 、 ど の レ ジ ス タ を複製すべ き でないか を指定 し て く だ さ い。 ヒ ン ト•

配置配線ツールの レ ポー ト で、 フ ァ ン ア ウ ト の大 き い信号がデザ イ ンのパフ ォー マ ン ス に影響を与え てい る 場合、 複製を考慮す る 。 パイ プ ラ イ ンのレ ベルを追加する パフ ォーマ ン ス を向上 さ せ る 他の手段 と し ては、 複数レベルの ロ ジ ッ ク を持つ長い デー タ パ ス を再構築 し 、 複数 ク ロ ッ ク サ イ ク ルに再分配す る 方法があ り ます。こ の 手法では、 レ イ テ ン シお よ びパ イ プ ラ イ ン化 さ れたオーバーヘ ッ ド ロ ジ ッ ク が増加 し ますが、 デー タ の スループ ッ ト が向上 し 、 ク ロ ッ ク サ イ ク ルが高速化 し ます。FPGA

には優れた レ ジ ス タ が豊富にあ る ので、 追加レ ジ ス タ やオーバーヘ ッ ド ロ 表 3 : レ ジ ス タ の複製例 VHDL Verilogattribute EQUIVALENT_REGISTER_REMOVAL : string; attribute EQUIVALENT_REGISTER_REMOVAL of

ce1 : signal is "NO"; attribute EQUIVALENT_REGISTER_REMOVAL of

ce2 : signal is "NO"; begin

-- Clock enable register with 64 fanout -- replicated once process (clk) begin if (rising_edge(clk)) then ce1 <= ce; ce2 <= ce; end if; end process; process (clk) begin if (rising_edge(clk)) then if (ce1='1') then

res(31 downto 0) <= a_data(31 downto 0); end if;

if (ce2='1') then

res(63 downto 32) <= a_data(63 downto 32); end if;

end if; end process;

(*EQUIVALENT_REGISTER_REMOVAL="NO"*) reg ce1, ce2; // Clock enable register with 64 fanout

// replicated once always @(posedge clk) begin ce1 = ce; ce2 = ce; end always @(posedge clk) begin if (ce1) res[31:0] <= a_data[31:0]; if (ce2) res[63:32] <= a_data[63:32]; end

ロ ッ ク に分散 さ れ る ため、 他のデザ イ ン部分においては、 追加 し たパ ス の レ イ テ ン シ を反映 さ せたデザ イ ン を特に考慮す る 必要があ り ます。表

4

に、6

レベルの レ ジ ス タ を32 X 32

乗算器に加え た場合の コ ーデ ィ ン グ方法を示 し ます。合成ツールでは、 最適化 さ れたVirtex-4 DSP48

の レ ジ ス タ と こ れ ら の レ ジ ス タ をパ イ プ ラ イ ン化 し 、 デー タ の ス ループ ッ ト を最大に し ます。 可能であれば、 デザ イ ンの検証方法お よ びツールセ ッ ト で リ タ イ ミ ン グ と パ イ プ ラ イ ン を ま と めて、 デザ イ ン パフ ォーマ ン ス を向上 さ せ る よ う 考慮すべ き です。リ タ イ ミ ン グ と は、 組み合わせ ロ ジ ッ ク の レ ジ ス タ を調整 し て自動的に移動す る 合成や 配置配線のアルゴ リ ズ ムで、 デザ イ ンの主要な入出力において同等の ビヘ イ ビ ア を 維持 し なが ら 、 タ イ ミ ン グ を向上 さ せます。 リ タ イ ミ ン グに よ っ て、 コ ー ド 変更をせずにパフ ォーマ ン ス を向上 さ せ、RTL

デザ イ ン を簡略化で き ます。ただ し 、 リ タ イ ミ ン グに よ っ てデザ イ ン検証を よ り 複雑化 さ せて し ま う 場合があ り ます。 レ ジ ス タ 名、 その位置、 機能がRTL

と の記述に合致 し な く な る こ と が理由です。そのため、 リ タ イ ミ ン グ を使用 し ない設計者 も い ます。 リ タ イ ミ ン グ を使用 し ない場合には、 デバ イ ス に関す る 設計者の知識を活か し てRTL

で レ ジ ス タ を記述 し 、 使用可能なデバ イ ス リ ソ ース の レ ジ ス タ を効率的に配置 で き ます。パフ ォーマ ン ス において、 内在す る アーキ テ ク チ ャ の ロ ジ ッ ク の イ ンプ リ メ ン テーシ ョ ンは常に考慮すべ き です。ま た、 ロ ジ ッ ク の レベル数 と 信号の見込 まれ る フ ァ ン ア ウ ト 数に該当す る 各 コ ー ド も 考慮すべ き で し ょ う 。RTL

コ ー ド では、 ロ ジ ッ ク の レベルやフ ァ ン ア ウ ト に偏 り が出ない よ う 、 レ ジ ス タ の均等配置を選択 す る 必要があ り ます。こ のガ イ ド ラ イ ンにそ っ て ロ ジ ッ ク を配置すれば、 可能な限 り デザ イ ン パフ ォーマ ン ス を向上 さ せ る こ と がで き ます。 ヒ ン ト•

レ ジ ス タ 間の ロ ジ ッ ク レベルを調整す る と 、 デザ イ ンのパフ ォーマ ン ス が向上 し ます。RTL

コ ー ド でパ イ プ ラ イ ンの レベルを追加す る か、 合成ツールに リ タ イ ミ ン グのオプシ ョ ン を適切に適用す る か、 あ る いはその両方を実行 し て く だ さ い。 表 4 : パイ プ ラ イ ンのレ ベルを追加する VHDL Verilogtype regbank6x64 is array(PIPE-1 downto 0) of std_logic_vector(63 downto 0); signal prod: regbank6x64;

-- 32x32 multiplier with 4 DSP48 (PIPE=6) prod(0) <= a * b;

regbank: for i in 1 to PIPE generate begin process (clk) begin if (rising_edge(clk)) then prod(i) <= prod(i-1); end if; end process; end generate; mult_out <= prod(PIPE); parameter PIPE = 6;

reg signed [63:0] prod [PIPE-1:0];

// 32x32 multiplier with 4 DSP48 (PIPE=6) always @(posedge clk) begin

prod[0] <= a * b;

for (i=1; i<=PIPE-1; i=i+1) prod[i] <= prod[i-1]; end

推論かイ ン ス タ ン シ エー ト かの選択

通常、 ビヘ イ ビ アか ら デザ イ ン を記述 し 、FPGA

で使用可能なゲー ト に、 合成ツー ルで コ ー ド を マ ッ ピ ン グす る こ と が望ま し い と さ れてい ます。コ ー ド を移植 し やす く す る には、 推論 し た ロ ジ ッ ク すべて を合成ツールで可視 し 、 機能同士の最適化が 実行で き る よ う に し ます。こ の最適化に含まれ る のは、ロ ジ ッ ク の複製、 結合 と 再構 築、 レ ジ ス タ 間の ロ ジ ッ ク 遅延を調整す る ための リ タ イ ミ ン グです。デバ イ ス の ラ イ ブ ラ リ セルを イ ン ス タ ン シエー ト し て も 、 合成ツールではデフ ォ ル ト で最適化 さ れません。 し たが っ て、デバ イ ス の ラ イ ブ ラ リ セルの最適化を命令 し て も 、 合成 ツールではRTL

を使用 し た同レベルでの最適化は通常実行で き ません。そのため、 合成ツールではセルを介 し た最適化ではな く 、 パ スへ、 も し く はパ ス か ら のセルの 最適化を実行 し ます。た と えば、SRL

を イ ン ス タ ン シエー ト し た結果、 こ のSRL

が 駆動す る ロ ジ ッ ク の コ ーンが長い場合には、 こ のパス がボ ト ルネ ッ ク と な る 可能性 があ り ます(

前述のSRL

を参照 し て く だ さ い)

。SRL

のClock-to-Out

は、 一般的な レ ジ ス タ よ り も 遅延が長 く な り ます。Clock-to-Out

遅延を改善 さ せつつSRL

が使用 す る エ リ アの縮小を妨げない よ う にす る と 、 一般的な フ リ ッ プ フ ロ ッ プで最終的に イ ンプ リ メ ン ト さ れ るSRL

の遅延が、 実際の遅延 よ り 短 く 生成 さ れ る こ と にな り ま す。と はいえ、 イ ン ス タ ン シエーシ ョ ンに都合のいい場合 も あ り ます。合成ツールで マ ッ ピ ン グす る と 、 タ イ ミ ン グ、 消費電力、 エ リ ア制約が満た さ れない場合や、

FPGA

内のあ る 特別な機能が推論で き な く な る 場合です。イ ン ス タ ン シエーシ ョ ン においては、 設計者が合成ツール全体を管理 し ます。た と えば、 設計者はパフ ォー マ ン ス を向上 さ せ る ために、 合成ツールが通常実行す るLUT

と キ ャ リ ーチ ェーン のエ レ メ ン ト 結合を選択せずに、LUT

だけ を使用 し た コ ンパ レー タ を イ ンプ リ メ ン ト で き ます。その他の場合、 イ ン ス タ ン シエーシ ョ ンだけがデバ イ ス の複雑な リ ソ ース を使用可能にす る 手段 と な り ます。理由は次の通 り です。•

HDL

言語に限界があ り ます。具体例では、 ダブルデー タ レー ト(DDR)

出力信 号を駆動す る のに2

つの異な る プ ロ セ ス が必要 と な る ため、VHDL

で記述で き ません。•

ハー ド ウ ェ アが複雑化 し ます。Virtex-4

のI/O

のSerDes

エ レ メ ン ト を イ ン ス タ ン シエー ト す る 方が、 ビヘ イ ビ ア を記述す る よ り 容易です。•

合成ツールでの推論には限度があ り ます。た と えば、 現状の合成ツールでは、Virtex-4

のFIFO

あ る いはDSP48

対称型丸め込みやサチ ュ レー ト の ビヘ イ ビ ア の記述か ら の推論がで き ません。つま り 、 設計者が イ ン ス タ ン シエー ト し ない限 り 、 それ ら の回路の使用はで き ない と い う こ と です。 ヒ ン ト•

デザ イ ンの ビヘ イ ビ ア を最大限に記述す る 。•

ビヘ イ ビ アの コ ー ド を合成 し て も タ イ ミ ン グが満た さ れない場合には、 合成ツー ルの タ イ ミ ン グ制約や設定を確認 し てか ら 、 デバ イ ス の ラ イ ブ ラ リ コ ン ポーネ ン ト を イ ン ス タ ン シエーシ ョ ンす る コ ー ド と 交換す る 。•

一般的なVerilog

やVHDL

の ビヘ イ ビ ア構築では、 言語テ ンプ レー ト を考慮 し て記述す る 。•

COREGenerator

TM、Architecture Wizard

、ISE

の言語テ ンプ レー ト を考慮 し て、デバ イ ス の ラ イ ブ ラ リ コ ン ポーネ ン ト を イ ン ス タ ン シエー ト す る 。

ク ロ ッ ク

イ ネーブル と ゲー ト 付き ク ロ ッ クの違い

ザ イ リ ン ク ス では、

CLB

レ ジ ス タ には通常、 ク ロ ッ ク ポー ト を ゲー ト す る のではな く 、 専用の ク ロ ッ ク イ ネーブル ポー ト の使用を推奨 し てい ます。ゲー ト 付 き ク ロ ッタ イ ミ ン グ特性、 デザ イ ン解析への効果が高ま り ます。デバ イ ス で使用で き る ク ロ ッ ク イ ネーブル リ ソ ース の使用には、 い く つかの方法があ り ます。消費電力の削 減 と し て ク ロ ッ ク ド メ イ ン全体のゲー ト に望ま し いのは、

BUFGCE

と い う ク ロ ッ ク イ ネーブルのグ ロ ーバルバ ッ フ ァ リ ソ ース を使用す る 方法です(

図10

を参照 し て く だ さ い)

。 デザ イ ンの特定の狭いエ リ アで、 ク ロ ッ ク を数サ イ ク ル間停止 さ せ る こ と のみを目 的 と し たアプ リ ケーシ ョ ンに適 し てい る のは、FPGA

レ ジ ス タ の ク ロ ッ ク イ ネーブ ルピ ン を使用す る 方法です。まず、図11

に示 し て あ る のが、 ク ロ ッ ク 信号の不適切 なゲー ト 方法の例です。 次に、図

12

に示すのが、 コ ー ド を書 き 直 し て、 ク ロ ッ ク イ ネーブルピ ン を効果的にマ ッ プ し た も のです。 図 10 : BUFGCE BUFGCE WP231_10_110905 O I CE 図 11 : ゲー ト 付き ク ロ ッ ク - ザイ リ ン ク ス で推奨 し ない コ ーデ ィ ン グ方法 D DATA LOAD IN1 IN2 CLK AND3 GATECLK OUT1 DFF CE C Q WP231_11_112105 VHDL VerilogGATECLK <= (IN1 and IN2 and CLK); process (GATECLK) begin if (rising_edge(GATECLK)) then if (LOAD = '1') then OUT1 <= DATA; end if; end if; end process;

assign GATECLK = (IN1 & IN2 & CLK); always @(posedge GATECLK)

begin if (LOAD)

OUT1 <= DATA; end

ヒ ン ト

•

ゲー ト 付 き ク ロ ッ ク を使用 し ない。•

グ ロ ーバル ク ロ ッ ク バ ッ フ ァ の ク ロ ッ ク イ ネーブル ポー ト を使用 し て、 ク ロ ッ ク ド メ イ ン全体の ク ロ ッ ク を停止す る 。•

ロ ーカルに ク ロ ッ ク をデ ィ ス エーブルにす る 場合は、 レ ジ ス タ の ク ロ ッ ク イ ネーブルポー ト を使用す る 。•

ク ロ ッ ク イ ネーブル信号の複製は、 パ ス の一部が タ イ ミ ン グ要件を満た さ ない 場合に考慮す る 。ネス ト し た

If-Then-Else

、

Case

構文および組み合わせ

For

ループ

if

構文お よ びcase

構文のネ ス ト や他の構文中に構文 と し て含め る こ と は避け、 コ ー ド 中に含むネ ッ ト 数を最小限に抑え て く だ さ い。if

構文中にif

構文を入れすぎ る と 、 行が長 く な り 、 構文の最適化に支障を き た し ます。構文のネ ス ト を最小限にす る こ と で、 一般的には コ ー ド が読みやす く 、 移植 し やす く な り 、 プ リ ン ト す る 場合に も フ ォーマ ッ ト が容易にな り ます。HDL

でfor

ループ を記述す る 場合、 特に演算 ロ ジ ッ ク 、 特定のオペレーシ ョ ンの ロ ジ ッ ク に対 し て望ま し いのは、 デー タ パ ス に最低1

つの レ ジ ス タ を配置す る こ と で す。す る と 、 コ ンパ イ ル中に、 合成ツールではループが展開 さ れません。こ れ ら の同 期エ レ メ ン ト がない と 、 合成ツールは各ループの反復で生成 さ れた ロ ジ ッ ク を連結 す る ので、 組み合わせパ ス が非常に長 く な り 、 結果 と し てデザ イ ン パフ ォーマ ン ス に影響を き た し ます。 ヒ ン ト•

シーケ ン シ ャ ルな構文のネ ス ト 数を最小限にす る 。•

長い組み合わせパ ス を作成す る 場合には、for

ループに レ ジ ス タ を追加す る 。 図 12 : ク ロ ッ ク イ ネーブル - ク ロ ッ ク 信号のゲー ト に効果的な手法 D DATA IN1 IN2 LOAD CLOCK ENABLE AND3 OUT1 DFF CE C Q WP231_12_112105ENABLE <= IN1 and IN2 and LOAD; process begin if (rising_edge(CLOCK)) then if (ENABLE = '1') then DOUT <= DATA; end if; end if; end process;

assign ENABLE = (IN1 & IN2 & LOAD); always @(posedge CLOCK)

begin

if (ENABLE) DOUT <= DATA; end

デザ イ ンの階層分離の選択では、

HDL

コ ー ド 記述の容易性に左右 さ れ る ケース がた びたび発生 し ます。ただ し 、 デザ イ ン過程に費やす時間を短縮 し つつ、 パフ ォーマ ン ス の観点か ら デザ イ ン階層全体を最高の状態にす る には、 デザ イ ンの最適化、 イ ンプ リ メ ン ト 方法、 検証を熟考す る こ と が、 よ り 重要 と な る 場合 も あ り ます。最適 化 と い う 点か ら 見 る と 、 合成ツールの多 く は論理的なデザ イ ン階層を 「 ソ フ ト 」 と し て扱い、 それは、 階層を で き る だけ維持す る こ と 、 最適化に影響が出ない範囲で の階層を分離す る こ と 、 ま たは階層下の フ ッ ト プ リ ン ト お よ び ロ ジ ッ ク 内容を変更 す る こ と を意味 し ます。イ ン ク リ メ ン タ ルデザ イ ンや階層維持を検証対象 と す る よ う な階層的デザ イ ン手法を用い る と 、 論理的境界に跨 る 最適化は実行で き ません。 ガ イ ド ラ イ ンに適切に従わない場合には、 ロ ジ ッ ク レベルあ る いは配置制約が多 く な り 、 デザ イ ンの最適化に影響を与え ます。非階層デザ イ ンの イ ンプ リ メ ン テー シ ョ ン フ ロ ーを使用 し た と し て も 、 ガ イ ド ラ イ ンに従 う こ と で、 よ り 容易に実行が で き 、 配置配線ツールで も 、 ロ ジ ッ ク の最適化、 お よ び配置に と っ て最良の選択が な さ れます。次にガ イ ド ラ イ ン を説明 し ます。1.

階層内のすべての入出力に レ ジ ス タ を付けて く だ さ い。それが難 し い場合には、 出力だけで も 必ずレ ジ ス タ を付けて く だ さ い。一般的な ロ ジ ッ ク の最適化におい て、 階層の影響を受けな く な り ます。2.

イ ン ス タ ン シエー ト し たI/O

バ ッ フ ァ 、 レ ジ ス タ 、DDR

回路、SerDes

、 遅延エ レ メ ン ト を含むすべてのI/O

コ ン ポーネ ン ト をデザ イ ンの最上位に配置 し て く だ さ い。最上位にすべて を配置で き ない場合には、1

階層にすべて を収め る よ う に し て く だ さ い。3. FPGA

の共有機能や リ ソ ース に配置す る 必要のあ る レ ジ ス タ ま たは ロ ジ ッ ク の セ ッ ト は、 同位層に収めて く だ さ い。た と えば、Virtex-4

のDSP48

に乗算器、 ア キ ュ ム レー タ 、 関連レ ジ ス タ を配置す る 必要のあ る デザ イ ンでは、 こ れ ら すべ てのエ レ メ ン ト を同層のモジ ュ ールに収めなければな り ません。4.

リ ソ ース を共有 し てい る 合成ツールの ロ ジ ッ ク は、 同位に配置 し て く だ さ い。5.

階層境界で フ ァ ン ア ウ ト の大 き い レ ジ ス タ は、 手動で複製 し て く だ さ い。 以上の簡単なガ イ ド ラ イ ン を遵守す る な ら ば、 選択 し た階層がデザ イ ンの最適化や、 デザ イ ンのパフ ォーマ ン ス に影響を及ぼす こ と はあ り ません。こ の規定に従え ない 場合には、 イ ンプ リ メ ン ト し たデザ イ ンの ク リ テ ィ カルパ ス を確認 し て、 階層に変 更を加え る こ と が最終的なデザ イ ンのパフ ォーマ ン ス に影響があ る か を判断す る よ う お勧め し ます。ま と め

合成お よ び配置配線アルゴ リ ズ ムにおけ る 昨今の進歩が も た ら し た影響で、 特定の デバ イ ス か ら 最大のパフ ォーマ ン ス を引 き 出す こ と が、 よ り 容易にな り ま し た。合 成ツールでは、 複雑な演算や メ モ リ 記述を推論 し 、 専用のハー ド ウ ェ ア ブ ロ ッ ク に マ ッ ピ ン グで き ます し 、 リ タ イ ミ ン グの よ う な最適化や、 ロ ジ ッ ク やレ ジ ス タ の複 製 も で き ます。ま た、 配置配線の輻輳を緩和す る ため、 タ イ ミ ン グ制約に基づいて、 配置配線ツールでネ ッ ト リ ス ト を再構築 し 、 タ イ ミ ン グ ド リ ブン パ ッ ク や配置がで き る よ う にな り ま し た。と はいえ、 特定の

RTL

の記述では、 ツールが最大化で き る パフ ォーマ ン ス は限 ら れてい ます。デザ イ ンのパフ ォーマ ン ス を さ ら に改善す る 必 要のあ る 場合には、 タ ーゲ ッ ト デバ イ ス、 ツールの制約やオプシ ョ ンに よ り 一層精 通 し 、 本稿で説明 し た コ ーデ ィ ン グのガ イ ド ラ イ ンに従 う のが非常に効率的な方法 と いえ ます。その他の

リ ソ ース

デザ イ ン パフ ォーマ ン ス を最大化 さ せ る ための、 さ ら な る ヒ ン ト が記載 さ れた リ ソ ース を紹介 し ます。『合成シ ミ ュ レーシ ョ ン デザ イ ン ガ イ ド 』