TB3195

Cortex-M7 ベースの MCUにおける

キャッシュ

コヒーレンシの管理

はじめに

本書では各種シナリオでのキャッシュ コヒーレンシ問題の概要を説明します。また、キャッシュ コヒー レンシ問題を管理または回避する方法も提案します。TB3195

目次

はじめに ...1 1. キャッシュ ポリシーの概要...3 2. サポートされている設定 ...4 3. キャッシュ コヒーレンシ問題 ...5 4. キャッシュ メンテナンス API を使ったキャッシュ コヒーレンシの処理 ...7 5. DMA と CPU が共有するメモリ領域でのキャッシュの無効化 ...12 6. 関連リソース ...15 Microchip 社のウェブサイト ...16 お客様向け変更通知サービス ...16 カスタマサポート ...16 Microchip 社のデバイスコード保護機能...16 法律上の注意点 ...17 商標 ...17 DNV による品質管理システム認証 ...18 各国の営業所とサービス ...19TB3195

キ ャッシュ

ポリシーの概要

1.

キャッシュ

ポリシーの概要

表1-1. キャッシュ ポリシー 読み出しポリシー (キャッシュミスの場合): リードアロケート Cortex-M7 ベースの MCUにおいて全てのキャッシュ可 能ロケーションはリードアロケートです。これは、 キャッシュミス発生時にデータキャッシュ ラインを アロケートし、32 バイト(Note 参照)のデータをメイン メモリからキャッシュメモリにフェッチする事を意味 します。その結果、これらのメモリ位置への以降のアク セスはキャッシュヒット条件となり、データを直接 キャッシュメモリから読み出します。 書き込みポリシー (キャッシュヒットの場合): ライトバック キャッシュヒット時、データキャッシュのみ更新して メインメモリは更新しません。キャッシュラインを dirty としてマークし、キャッシュラインをパージする か明示的にクリーンするまで、メインメモリへの書き 込みを延期します。 ライトスルー キャッシュヒット時、データキャッシュとメインメモ リの両方を更新します。 書き込みポリシー (キャッシュミスの場合): ライトアロケート キャッシュミス時、キャッシュラインをアロケートして メインメモリからのデータをロードします。これは、 プロセッサでストア命令を実行すると、バースト読み 出しが発生してデータをメインメモリからキャッシュに フェッチする可能性がある事を意味します。 ライトアロケートなし キャッシュミス時、キャッシュラインをアロケートせず にデータをメインメモリに直接書き込みます。この場 合、読み出しでのキャッシュミスが発生するまでラ インをキャッシュせず、その後リードアロケート ポリ シーを使ってキャッシュをロードします。TB3195

サ ポートされている設定

2.

サポートされている設定

リードおよびライトアロケート付きライトバック: WB-RWA • 最高の性能を提供します。キャッシュヒットはキャッシュメモリのみ更新します。書き込みでキャッ シュミスの場合、データをメインメモリからキャッシュにコピーします。その結果、以降のアクセス はキャッシュヒットとなります。 リードアロケート付きライトバック (ライトアロケートなし): WB-NWA • キャッシュヒットはキャッシュメモリのみ更新します。書き込みでキャッシュミスの場合、データを キャッシュにフェッチしません。これは、データを書き込むがすぐにはリードバックしない時にのみ 有利です。 リードアロケート付きライトスルー (ライトアロケートなし): WT-NWA • 各書き込み(キャッシュヒットとキャッシュミスのどちらか)をメインメモリ上で実行します。これは キャッシュの利点を無効にします。 • キャッシュ コヒーレンシ問題を部分的に解決します。 キャッシュ不可 • 各読みと書きをメインメモリ上で実行します。 • キャッシュ コヒーレンシに関する問題は発生しません。TB3195

キ ャッシュ

コヒーレンシ問題

3.

キャッシュ

コヒーレンシ問題

複数のバスマスタ(例えば、CPU と DMA)が共有しているメモリが同じイメージを持つ時、メモリ領域は コヒーレントであると表現します。 DMA が SRAM に書き込むアプリケーションを考えてみましょう。 条件: SRAM 上でキャッシュが有効になっており、キャッシュ適用性属性はリードおよびライトアロケー ト付きライトバック(WB-RWA)に設定されています。CPUは前に DMA バッファを読み出していて、この ためリードアロケート ポリシーによって同じものがキャッシュメモリでも利用可能です。 図3-1. キャッシュ コヒーレンシ問題 - DMA が SRAM に書き込む 説明 1. DMA は周辺モジュールからデータを読み出して、SRAM 内の受信バッファを更新します。 2. CPU が受信バッファを読み出す際、CPUはキャッシュに存在するデータを読み出し、SRAM 内で 利用可能な新規データは読み出しません。 DMA が SRAM から読み出す別の例について考えます。 条件: SRAM上でキャッシュが有効になっており、キャッシュ適用性属性はWB-RWAに設定されています。 SRAM --- --- --- --- --- --- --- --- D-Cache --- --- --- --- --- --- --- ---DMA

1. DMA Writes @MemX @MemX+8 W7 W6 W5 W4 W3 new W1 W0 W2 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- W7 W6 W5 W4 W3 W2 W1 W0 2. CPU Reads (Cache Hit)Peripheral

CPU

TB3195

キ ャッシュ

コヒーレンシ問題

図3-2. キャッシュ コヒーレンシ問題 - DMA が SRAM から読み出す 説明 1. キャッシュ ポリシーが WB-RWA に設定されているため、CPUは送信バッファに送信されるデー タを更新し、キャッシュだけが更新されてメインメモリは更新されません。2. DMA が送信バッファを読み出す時、DMA はメインメモリにある古いデータを読み出し、CPUに よって更新されてキャッシュに書き込まれている最新の値は読み出しません。 SRAM --- --- --- --- --- --- --- --- D-Cache --- --- --- --- --- --- --- --- @MemX+8 W7 W6 W5 W4 W3 W2 W1 W0 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- W7 W6 W5 W4 W3 New W1 W0 W2 1. CPU Writes (Cache Hit)

DMA

Peripheral

CPU

2. DMA Reads @MemXTB3195

キ ャッシュ

メンテナンス API を使ったキャッシュ コヒーレンシの処理

4.

キャッシュ

メンテナンス API を使ったキャッシュ コヒーレンシの処理

このソリューションでは、アプリケーションはCortex-M7 キャッシュ メンテナンス動作を使って、実行時 にキャッシュを管理する必要があります。キャッシュ メンテナンス API によって、ユーザは以下のアク ションを実行できます。 1. キャッシュを有効または無効にする – キャッシュの ON/OFF 2. キャッシュを無効化する – キャッシュラインを無効としてマークします。リードアロケート ポリ シーとライトアロケート ポリシーによって、以降のアクセスではデータをメインメモリからキャッ シュに強制的にコピーします。 3. キャッシュをクリーンする – dirty とマークされたキャッシュラインをメインメモリに書き戻します。 Cortex Microcontroller Software Interface Standard (CMSIS)には以下の D-キャッシュ メンテナンス APIを 提供しています。 表4-1. CMSIS データキャッシュ メンテナンス API キャッシュ メンテナンス API 説明 SCB_EnableDCache (void) データキャッシュを有効にします。データキャッシュ 全体を有効にする前に無効にします。 SCB_DisableDCache (void) データキャッシュを無効にします。キャッシュを無効に する前に、データキャッシュをクリーンしてdirty なデー タをメインメモリにフラッシュします。 SCB_InvalidateDCache(void) データキャッシュ全体を無効にします。 SCB_InvalidateDCache_by_Addr(uint32_t * addr, int32_t dsize ) データ キャッシュ ラインをアドレスで無効にします。

SCB_CleanDCache(void) データキャッシュをクリーンします。

SCB_CleanDCache_by_Addr

(uint32_t *addr, int32_t dsize) データ キャッシュ ラインをアドレスでクリーンします。

SCB_CleanInvalidateDCache(void) データキャッシュ全体をクリーンして無効にします。

SCB_CleanInvalidateDCache_by_Addr

(uint32_t *addr, int32_t dsize) データにします。 キャッシュ ラインをアドレスでクリーンして無効

アドレスAPI によってキャッシュ クリーンとキャッシュ無効化を行う時は以下の点に注意します。

addr – キャッシュラインのサイズ境界に合わせる必要があります。つまり DMA バッファアドレスを 32 バ イト境界に合わせる事が必要です。

dsize – キャッシュ ライン サイズの倍数にする必要があります。つまり DMA バッファサイズは 32 バイト の倍数である事が必要です。

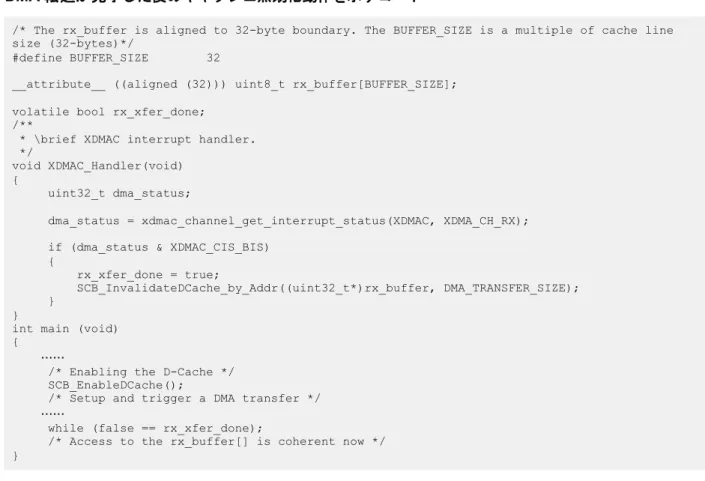

DMA が SRAM に書き込む時にキャッシュ メンテナンス API を使用

条件: キャッシュ ポリシーは WB-RWA です。CPU は最初に受信バッファ(rx_buffer[])にアクセスし、そ

れをD-キャッシュにキャッシュします。

TB3195

キ ャッシュ

メンテナンス API を使ったキャッシュ コヒーレンシの処理

2. キャッシュ無効化動作を実行して、キャッシュ済みの rx_buffer[]を無効化します。 3. CPU は rx_buffer[]の読み出しを試みますが、rx_buffer[]はステップ 2 で無効化したので結果として キャッシュミスになります。 図4-1. DMAが SRAM に書き込んだ後のキャッシュ無効化動作 4. リードアロケート ポリシーにより、キャッシュラインをアロケートして、このアロケート済みの キャッシュラインにデータをSRAM 内の rx_buffer[]からコピーします。 5. これにより、キャッシュからの CPU 読み出しはコヒーレントになります。 図4-2. キャッシュ無効化動作の後、CPUによる D-キャッシュからの読み出しはコヒーレントになる 以下のサンプルコードに、(GCCコンパイラを使って)キャッシュラインのサイズ境界に合わせたDMAバッ ファを定義する方法を示します。BUFFER_SIZE はキャッシュ ライン サイズ(32 バイト)の倍数にする必要があります。DMA_TRANSFER_SIZE は DMA が転送したバイト数です。DMA 読み出し動作が完了した

ら、キャッシュ無効化API を使ってキャッシュ内の受信バッファを無効化します。メイン関数はキャッ

シュ メンテナンス API を使ってデータキャッシュを有効にします。

Note: この技術概要で提供する全てのサンプルコードは Microchip社の Atmel Software Framework (ASF3)

で利用できるAPI 関数を参照しています。 SRAM --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- D-Cache DMA 1. DMA Writes @MemX @MemX+8 W7 W6 W5 W4 W3 new W1 W0 W2 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- Peripheral CPU SRAM --- --- --- --- --- --- --- --- @MemX+8 D-Cache --- --- --- --- --- --- --- --- W7 W6 W5 W4 W3 new W1 W0 W2 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- W7 W6 W5 W4 W3 new W1 W0 W2 5.

Reads out of cache are now coherent

3. A CPU read results in

a cache miss

TB3195

キ ャッシュ

メンテナンス API を使ったキャッシュ コヒーレンシの処理

DMA 転送が完了した後のキャッシュ無効化動作を示すコード

DMA が SRAM から読み出す時にキャッシュ メンテナンス API を使用

条件: キャッシュ ポリシーは WB-RWA に設定されています。CPUは最初に送信バッファ(tx_buffer[])にア

クセスし、それをD-キャッシュにキャッシュします。

1. CPU は DMA によって送信される tx_buffer[]にデータを書き込みます。

2. DMA 転送を有効にする前に、キャッシュ クリーン動作を実行してキャッシュ済みの tx_buffer[]を SRAM にフラッシュします。

3. SRAM からの DMA 読み出しがコヒーレントになります。

図4-3. CPUが D-キャッシュに書き込んだ後のキャッシュ クリーン動作

/* The rx_buffer is aligned to 32-byte boundary. The BUFFER_SIZE is a multiple of cache line size (32-bytes)*/

#define BUFFER_SIZE 32

__attribute__ ((aligned (32))) uint8_t rx_buffer[BUFFER_SIZE]; volatile bool rx_xfer_done;

/**

* \brief XDMAC interrupt handler. */

void XDMAC_Handler(void) {

uint32_t dma_status;

dma_status = xdmac_channel_get_interrupt_status(XDMAC, XDMA_CH_RX); if (dma_status & XDMAC_CIS_BIS)

{

rx_xfer_done = true;

SCB_InvalidateDCache_by_Addr((uint32_t*)rx_buffer, DMA_TRANSFER_SIZE); }

}

int main (void) {

……

/* Enabling the D-Cache */ SCB_EnableDCache();

/* Setup and trigger a DMA transfer */ ……

while (false == rx_xfer_done);

/* Access to the rx_buffer[] is coherent now */ } SRAM --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- D-Cache DMA 3. DMA Reads @MemX @MemX+8 W7 W6 W5 W4 W3 new W1 W0 W2 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- W7 W6 W5 W4 W3 new W1 W0 W2 1. CPU Writes (Cache Hit) Peripheral CPU

TB3195

キ ャッシュ

メンテナンス API を使ったキャッシュ コヒーレンシの処理

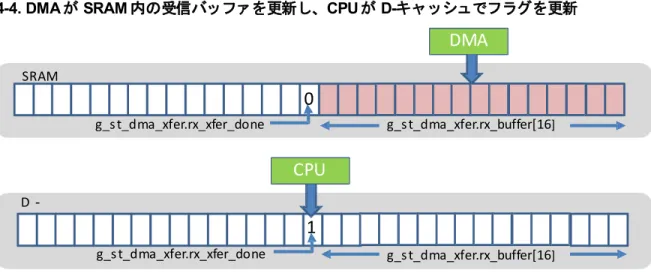

CPU が D-キャッシュに書き込んだ後のキャッシュ クリーン動作を示すコード 前のサンプルコードでは DMA 転送を有効にする前に、CPU によるキャッシュ クリーン動作が送信バッ ファ内の更新済みデータをSRAM に書き込みます。 Note: DMA リンク記述子を使っている場合、記述子が更新されるたびに、アプリケーションはリンク記述 子アドレスに対応するキャッシュをクリーンしてDMA と CPU との間のコヒーレンシを維持する必要が あります。 Important: 全てのキャッシュ動作は 32 バイトのキャッシュラインで実行されます。その結果、 前述したサンプルの受信バッファと送信バッファのサイズが 32 バイトの倍数でない場合、 キャッシュ無効化またはキャッシュ クリーン動作によって、以下のサンプルコードに示すよう な予期せぬ動作が発生する可能性があります。 32 バイトの倍数でない DMAバッファによる影響を示すコード 前のサンプルコードでは受信バッファは16 バイトです。DMA は周辺モジュールから 16 バイトを SRAM内のg_st_dma_xfer.rx_buffer[]に読み出し、DMA 割り込みを生成します。DMA ISRでは CPUは D-キャッ

int main (void) {

……

strcpy(tx_buffer, "DMA Transmit String");

SCB_CleanDCache_by_Addr((uint32_t*)tx_buffer, DMA_TRANSFER_SIZE); xdmac_channel_enable(XDMAC, XDMA_CH_TX);

}

#define BUFFER SIZE 16 typedef struct

{

/* The rx_buffer is aligned to 32-byte boundary.

The BUFFER_SIZE is 16-bytes which is not a multiple of the cache line size. */

__attribute__ ((aligned (32))) uint8_t rx_buffer[BUFFER_SIZE]; bool rx_xfer_done;

}st_dma_xfer;

static st_dma_xfer g_st_dma_xfer; /**

*\brief XDMAC interrupt handler. */

void XDMAC Handler(void) {

uint32 t dma status;

dma_status = xdmac_channel_get_interrupt_status(XDMAC, XDMA_CH_RX); if (dma_status & XDMAC_CIS_BIS)

{ g_st_dma_xfer.rx_xfer_done = true; SCB_InvalidateDCache_by_Addr((uint32_t*)g_st_dma_xfer.rx_buffer, DMA_TRANSFER_SIZE); } }

TB3195

キ ャッシュ

メンテナンス API を使ったキャッシュ コヒーレンシの処理

したので、D-キャッシュに格納されています。その後キャッシュ無効化動作を実行し、これによってキャッ

シュ済みラインを無効にします。

図4-4. DMAが SRAM 内の受信バッファを更新し、CPUが D-キャッシュでフラグを更新

キャッシュ ラインは無効にされているので、CPUがメイン関数で g_st_dma_xfer.rx_xfer_done フラグに アクセスすると、結果として32 バイトのキャッシュライン全体が SRAM から D-キャッシュにコピーされ ます(リードアロケート ポリシーにより)。これが g_st_dma_xfer.rx_xfer_done フラグを上書きして 0 に戻 します。 その結果、CPUは 1 にセットされた g_st_dma_xfer.rx_xfer_done フラグを見る事はありません。 図4-5. データキャッシュに存在するデータをキャッシュ無効化動作が誤って破損 この問題の原因はDMA バッファが 32 バイトの倍数でない事です。DMA が 32 バイトの非整数倍のデー タを周辺モジュールとの間で転送するよう設定されている場合でも、同じキャッシュラインで定義した変 数が破損されるのを避けるために、DMA バッファは 32 バイトの整数倍にする必要があります。例えば、 DMA が周辺モジュールとの間で 50 バイトの読み出し/書き込みを行うよう設定されていても、DMA バッ ファのサイズは64 にする必要があります。 SRAM

0

g_st_dma_xfer.rx_xfer_done g_st_dma_xfer.rx_buffer[16]DMA

D‐1

g_st_dma_xfer.rx_xfer_done g_st_dma_xfer.rx_buffer[16]CPU

SRAM g_st_dma_xfer.rx_xfer_done0

g_st_dma_xfer.rx_buffer[16] Cache Invalidate D‐ g_st_dma_xfer.rx_xfer_done0

g_st_dma_xfer.rx_buffer[16]CPU never sees the rx_xfer_done bit set to 1 as it is overwritten with the SRAM contents by the cache invalidate operation.

TB3195

DMA と CPU が共有するメモリ領域でのキャッシュの無効化

5.

DMA と CPU が共有するメモリ領域でのキャッシュの無効化

このアプローチでは、CPU だけがアクセスするメモリ領域をキャッシュ可能として残しておきながら、

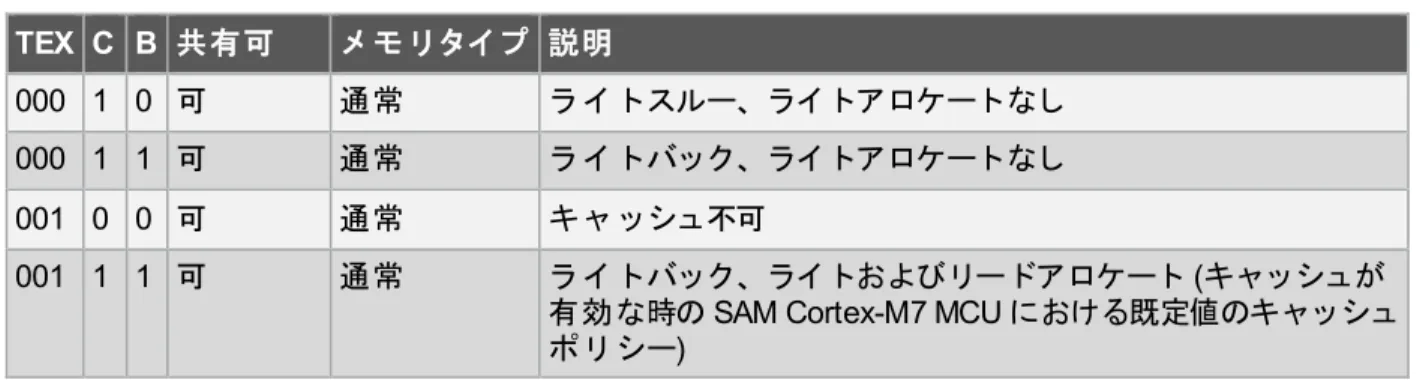

CPU と DMA が共有するメモリ領域をメモリ保護ユニット(MPU)を使ってキャッシュ不可として定義します。 応用例: CPU と DMA が共有メモリを同時に更新できます。例えば CPU と DMA は GMAC受信バッファ 記述子エントリの所有権ビットを同時に更新できます。 長所: アプリケーションに対し透過的です。キャッシュ メンテナンスが不要です。キャッシュのない MCU からキャッシュのあるMCUへのドライバの移植が容易になります。 短所: MPUを使って、キャッシュ不可の専用メモリ領域を作成する必要があります。これには複雑なリン カスクリプト ファイルが必要です。 キャッシュ不可のメモリ領域を作成するMPUの設定:

ユーザはSAM Cortex-M7 MCUを使って最大 16 の MPU領域を作成できます。下表に、メモリ領域を設定

して有効にするために使うMPUレジスタを示します。

詳細は http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0646b/BIHJJABA.html を参照して

ください。

表5-1. MPUレジスタ

MPUレジスタ 説明

MPU_RNR MPU_RBAR レジスタと MPU_RASR レジスタが参照するメモリ領域を選択します。

有効な値は16 の MPU領域に対応する 0~15 です。 MPU_RBAR MPU 領域のベースアドレスを定義します。領域の開始アドレスは領域のサイズに合わ せる必要があります(つまり 64 KB の領域は 0x00010000 または 0x00020000 において 64 KB の倍数に合わせる必要があります)。 MPU_RASR MPU 領域の領域サイズとメモリ属性を定義した上で、その領域を有効にする必要があ ります。領域サイズの最小値は32 バイトで、2 のべき乗で定義します。 MPU_CTRL MPU を有効/無効にします。 MPU_RASRレジスタの TEX、C、B の各ビットはメモリ領域のキャッシュ適用性を定義します。下表に通 常のメモリタイプのエンコードを示します。 表5-2. MPUアクセス パーミッション属性 TEX C B 共有可 メモリタイプ 説明 000 1 0 可 通常 ライトスルー、ライトアロケートなし 000 1 1 可 通常 ライトバック、ライトアロケートなし 001 0 0 可 通常 キャッシュ不可 001 1 1 可 通常 ライトバック、ライトおよびリードアロケート (キャッシュが

有効な時のSAM Cortex-M7 MCU における既定値のキャッシュ

ポリシー)

TB3195

DMA と CPU が共有するメモリ領域でのキャッシュの無効化

以下のサンプルコードではMPU を無効にしてから SRAM メモリ領域の 1 セクション(0x2045F0000 から 始まり、サイズは4096 バイト)をキャッシュ不可として設定し、有効にします。残りの SRAM メモリ領域 は既定値のキャッシュ ポリシー(WB-RWA)を維持してキャッシュ可能のままにしておきます。アクセス パーミッション(AP)を特権/非特権ソフトウェアの両方が RW アクセス権を持てるようフルアクセスに設 定し、その後MPUを有効にします。 キャッシュ不可のメモリ領域を作成するMPU設定を示すコード GNUリンカスクリプト用の以下のサンプルコードに示すように、リンカ スクリプト ファイルを変更して キャッシュ不可のメモリスペースを定義し、キャッシュ不可のメモリ領域にリンクする DMA バッファを 配置できます。 キャッシュ不可データ用のメモリセクションを作成するためのリンカスクリプトの変更/* Memory Spaces Definitions */ MEMORY {

rom (rx) : ORIGIN = 0x00400000, LENGTH = 0x00200000 ram (rwx) : ORIGIN = 0x20400000, LENGTH = 0x0005F000

ram_nocache (rwx) : ORIGIN = 0x2045F000, LENGTH = 0x00001000 } /* Section Definitions */ SECTIONS { ……. .ram_nocache (NOLOAD): { . = ALIGN(4); _s_ram_nocache = .; *(.ram_nocache) . = ALIGN(4); _e_ram_nocache = .; } > ram_nocache

.ram_nocache_data : AT (_etext + SIZEOF(.relocate)) {

. = ALIGN(4);

_s_ram_nocache_vma = .;

_s_ram_nocache_lma = LOADADDR(.ram_nocache_data); *(.ram_nocache_data)

#define SRAM_NOCACHE_START_ADDRESS (0x2045F000UL) #define NOCACHE_SRAM_REGION_SIZE 0x1000

#define MPU_NOCACHE_SRAM_REGION (11)

#define INNER_OUTER_NORMAL_NOCACHE_TYPE(x) ((0x01 << MPU_RASR_TEX_Pos ) | ( DISABLE << MPU_RASR_C_Pos ) | ( DISABLE << MPU_RASR_B_Pos ) | ( x << MPU_RASR_S_Pos))

/* Disable the MPU region */ MPU->CTRL = MPU_DISABLE; dw_region_base_addr = SRAM_NOCACHE_START_ADDRESS | MPU_REGION_VALID | MPU_NOCACHE_SRAM_REGION; dw_region_attr = MPU_AP_FULL_ACCESS | INNER_OUTER_NORMAL_NOCACHE_TYPE( SHAREABLE ) | mpu_cal_mpu_region_size(NOCACHE_SRAM_REGION_SIZE) | MPU_REGION_ENABLE; MPU->RBAR = dw_region_base_addr; MPU->RASR = dw_region_attr; /* Enable the MPU region */

MPU->CTRL = (MPU_ENABLE | MPU_PRIVDEFENA); __DSB();

TB3195

DMA と CPU が共有するメモリ領域でのキャッシュの無効化

. = ALIGN(4); _e_ram_nocache_vma = .; } > ram_nocache ………. } 前 述のリンカ スクリプト サンプルでは.ram_nocache_data セクションのロード メモリ アドレス が.text セクションと.relocate セクションの末尾となるように指定します。 リセットハンドラで以下のコードを使って、.ram_nocache セクション内の初期化されていない変数に ゼロをセットし、.ram_nocache_data 内の初期化された変数の初期値を(フラッシュから SRAM に)コ ピーします。 キャッシュ不可データ用のメモリセクションを初期化するCスタートアップ コードの変更extern uint32_t _s_ram_nocache; extern uint32_t _e_ram_nocache; extern uint32_t _s_ram_nocache_vma; extern uint32_t _e_ram_nocache_vma; extern uint32_t _s_ram_nocache_lma; void Reset_Handler(void)

{

uint32_t *pSrc, *pDest; ………

/* Initialize the no cache data segment */ pSrc = &_s_ram_nocache_lma;

pDest = &_s_ram_nocache_vma; if (pSrc != pDest) {

for (; pDest < &_e_ram_nocache_vma;) { *pDest++ = *pSrc++;

} }

/* Clear the no cache zero segment */

for (pDest = &_s_ram_nocache; pDest < &_e_ram_nocache;) { *pDest++ = 0; } ……… } アプリケーションでは以下のサンプルコードに示すように、DMA バッファを.ram_nocache メモリ領域 に配置できます。アプリケーションがキャッシュ不可メモリ領域の変数を初期化した場合、これらの変数 が.ram_nocache_data セクションに含まれるように定義する必要があります。 キャッシュ不可のメモリセクションにバッファを定義するアプリケーション コード キャッシュ コヒーレンシを回避する別の方法として、密結合メモリ(TCM)を使う方法があります。TCM の 内容はキャッシュされず、CPUと DMA の両方からアクセスできるからです。TCM にはキャッシュへのア クセスと同様のスピードでアクセスできます。キャッシュミスおよびキャッシュ コヒーレンシ問題による 遅延は発生しません。 応用例: キャッシュサイズ(16 KB)よりも大きいサイズのバッファ 長所: 性能に影響しません。アプリケーションに対して透過的です(キャッシュ メンテナンスが不要)。 短所: リンカスクリプトの変更が必要です。

__attribute__ ((section (".ram_nocache"), aligned (32))) uint8_t rx_buf[BUFFER_SIZE]; __attribute__ ((section (".ram_nocache"), aligned (32))) uint8_t tx_buf[BUFFER_SIZE];

TB3195

関 連リソース

6.

関連リソース

詳細は以下の文書を参照してください。それぞれリンク先からダウンロードできます。

1. ARM Cortex-M7 Processor Technical Reference Manual – L1 caches

2. ARM Cortex-M7 Processor Technical Reference Manual – Memory Protection Unit

3.

http://ww1.microchip.com/downloads/en/AppNotes/Atmel-44047-Cortex-M7-Microcontroller-Optimize-Usage-SAM-V71-V70-E70-S70-Architecture_Application-note.pdf

4. メモリ保護ユニット(MPU)の設定方法

5. Atmel SMART SAM V7x TCM Memory

TB3195

Microchip 社のウェブサイト

Microchip 社は自社が運営するウェブサイト(www.microchip.com)を通してオンライン サポートを提供し ています。当ウェブサイトでは、お客様に役立つ情報やファイルを簡単に見つけ出せます。一般的なインター ネット ブラウザから以下の内容がご覧になれます。 • 製品サポート - データシートとエラッタ、アプリケーション ノートとサンプル プログラム、設計リ ソース、ユーザガイドとハードウェア サポート文書、最新のソフトウェアと過去のソフトウェア • 一般的技術サポート - よく寄せられる質問(FAQ)、技術サポートのご依頼、オンライン ディスカッ ション グループ、Microchip 社のコンサルタント プログラムおよびメンバーリスト • ご注文とお問い合わせ - 製品セレクタと注文ガイド、最新プレスリリース、セミナー/イベントの一覧、 お問い合わせ先(営業所/販売代理店)の一覧お客様向け変更通知サービス

Microchip 社のお客様向け変更通知サービスは、お客様に Microchip 社製品の最新情報をお届けするサービ スです。ご興味のある製品ファミリまたは開発ツールに関する変更、更新、リビジョン、エラッタ情報を いち早くメールにてお知らせします。Microchip 社ウェブサイト(http://www.microchip.com/)にアクセスし、[DESIGN SUPPORT]メニューの下の

[Product Change Notification]からご登録ください。

カスタマサポート

Microchip 社製品をお使いのお客様は、以下のチャンネルからサポートをご利用頂けます。 • 販売代理店または販売担当者 • 各地の営業所 • 技術サポート サポートは販売代理店までお問い合わせください。もしくは弊社までご連絡ください。本書の最後のペー ジに各国の営業所の一覧を記載しています。 技術サポートは以下のウェブページからもご利用になれます。http://www.microchip.com/supportMicrochip 社のデバイスコード保護機能

Microchip 社製デバイスのコード保護機能について以下の点にご注意ください。 • Microchip 社製品は、該当する Microchip 社データシートに記載の仕様を満たしています。 • Microchip 社では、通常の条件ならびに仕様に従って使用した場合、Microchip 社製品のセキュリティ レベルは、現在市場に流通している同種製品の中でも最も高度であると考えています。 • しかし、コード保護機能を解除するための不正かつ違法な方法が存在する事もまた事実です。弊社の 理解では、こうした手法は全て、Microchip 社データシートにある動作仕様書以外の方法で Microchip 社製品を使用する事になります。このような行為は知的所有権の侵害に該当する可能性が 非常に高いと言えます。 • Microchip 社は、コードの保全性に懸念を抱いているお客様と連携し、対応策に取り組んでいきます。TB3195

• Microchip 社を含む全ての半導体メーカーで、自社のコードのセキュリティを完全に保証できる企業 はありません。コード保護機能とは、Microchip 社が製品を「解読不能」として保証するものではあ りません。 コード保護機能は常に進歩しています。Microchip 社では、常に製品のコード保護機能の改善に取り組んで います。Microchip 社のコード保護機能の侵害は、デジタル ミレニアム著作権法に違反します。そのよう な行為によってソフトウェアまたはその他の著作物に不正なアクセスを受けた場合、デジタル ミレニアム 著作権法の定める所により損害賠償訴訟を起こす権利があります。法律上の注意点

本書に記載されているデバイス アプリケーション等の情報は、ユーザの便宜のためにのみ提供されるもの であり、更新によって無効とされる事があります。お客様のアプリケーションが仕様を満たす事を保証す る責任は、お客様にあります。Microchip 社は、明示的、暗黙的、書面、口頭、法定のいずれであるかを問 わず、本書に記載されている情報に関して、状態、品質、性能、商品性、特定目的への適合性をはじめと する、いかなる類の表明も保証も行いません。 Microchip 社は、本書の情報およびその使用に起因する一切の責任を否認します。Microchip 社の明示的な 書面による承認なしに、生命維持装置あるいは生命安全用途にMicrochip 社の製品を使用する事は全て購 入者のリスクとし、また購入者はこれによって発生したあらゆる損害、クレーム、訴訟、費用に関して、 Microchip 社は擁護され、免責され、損害をうけない事に同意するものとします。暗黙的あるいは明示的を 問わず、Microchip 社が知的財産権を保有しているライセンスは一切譲渡されません。商標

Microchip 社の名称とロゴ、Microchip ロゴ、AnyRate、AVR、AVRロゴ、AVR Freaks、BeaconThings、 BitCloud、CryptoMemory、CryptoRF、dsPIC、FlashFlex、flexPWR、Heldo、JukeBlox、KeeLoq、KeeLoq

ロゴ、Kleer、LANCheck、LINK MD、maXStylus、maXTouch、MediaLB、megaAVR、MOST、MOSTロ

ゴ、MPLAB、OptoLyzer、PIC、picoPower、PICSTART、PIC32 ロゴ、Prochip Designer、QTouch、RightTouch、 SAM-BA、SpyNIC、SST、SST ロゴ、SuperFlash、tinyAVR、UNI/O、XMEGA は米国およびその他の国に

おけるMicrochip Technology Incorporated の登録商標です。

ClockWorks、The Embedded Control Solutions Company、EtherSynch、Hyper Speed Control、HyperLight Load、IntelliMOS、mTouch、Precision Edge、Quiet-Wire は米国における Microchip Technology Incorporated 社の登録商標です。

Adjacent Key Suppression、AKS、Analog-for-the-Digital Age、Any Capacitor、AnyIn、AnyOut、BodyCom、 chipKIT、chipKIT ロゴ、CodeGuard、CryptoAuthentication、CryptoCompanion、CryptoController、dsPICDEM、 dsPICDEM.net、Dynamic Average Matching、DAM、ECAN、EtherGREEN、In-Circuit Serial Programming、 ICSP、Inter-Chip Connectivity、JitterBlocker、KleerNet、KleerNet ロゴ、Mindi、MiWi、motorBench、MPASM、 MPF、MPLAB Certified ロゴ、MPLIB、MPLINK、MultiTRAK、NetDetach、Omniscient Code Generation、 PICDEM、PICDEM.net、PICkit、PICtail、PureSilicon、QMatrix、RightTouch ロゴ、REAL ICE、Ripple Blocker、 SAM-ICE、Serial Quad I/O、SMART-I.S.、SQI、SuperSwitcher、SuperSwitcher II、Total Endurance、TSHARC、 USBCheck、VariSense、ViewSpan、WiperLock、Wireless DNA、ZENA は、米国およびその他の国におけ るMicrochip Technology Incorporated の商標です。

SQTP は、米国における Microchip Technology Incorporated のサービスマークです。

Silicon Storage Technology は、米国以外の国における Microchip Technology Inc.の登録商標です。 GestIC は 、米国以外の国における Microchip Technology Inc.の 子会社である Microchip Technology Germany II GmbH & Co. KG の登録商標です。

TB3195

その他の商標は各社に帰属します。© 2018, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved. ISBN: 978-1-5224-3039-1

DNV による品質管理システム認証

ISO/TS 16949

Microchip 社では、Chandlerおよび Tempe(アリゾナ州)、Gresham(オレゴン州)の本部、設計部およびウェ

ハー製造工場そしてカリフォルニア州とインドのデザイン センターが ISO/TS-16949:2009 認証を取得し

ています。Microchip 社の品質システムプロセスおよび手順は、PIC® MCUおよび dsPIC® DSC、KEELOQ®

コード ホッピング デバイス、シリアル EEPROM、マイクロペリフェラル、不揮発性メモリ、アナログ製

品に採用されています。さらに、開発システムの設計と製造に関するMicrochip 社の品質システムは ISO

各国の営業所とサービス

北 米 ア ジア/太平洋 ア ジア/太平洋 ヨ ーロッパ

本 社 ア ジア太平洋支社 中 国 - 厦門 オ ーストリア - ヴェルス

2355 West Chandler Blvd. Suites 3707-14, 37th Floor Tel: 86-592-2388138 Tel: 43-7242-2244-39 Chandler, AZ 85224-6199 Tower 6, The Gateway Fax: 86-592-2388130 Fax: 43-7242-2244-393 Tel: 480-792-7200 Harbour City, Kowloon 中 国 - 珠海 デ ンマーク - コペンハーゲン Fax: 480-792-7277 香 港 Tel: 86-756-3210040 Tel: 45-4450-2828

技 術 サポート: Tel: 852-2943-5100 Fax: 86-756-3210049 Fax: 45-4485-2829 http://www.microchip.com/ Fax: 852-2401-3431 イ ンド - バンガロール フ ィンランド - エスポー サ ポ ート オ ーストラリア - シドニー Tel: 91-80-3090-4444 Tel: 358-9-4520-820 URL: Tel: 61-2-9868-6733 Fax: 91-80-3090-4123 フ ランス - パリ www.microchip.com Fax: 61-2-9868-6755 イ ンド - ニューデリー Tel: 33-1-69-53-63-20 ア トランタ 中 国 - 北京 Tel: 91-11-4160-8631 Fax: 33-1-69-30-90-79 Duluth, GA Tel: 86-10-8569-7000 Fax: 91-11-4160-8632 フ ランス - サンクルー Tel: 678-957-9614 Fax: 86-10-8528-2104 イ ンド - プネ Tel: 33-1-30-60-70-00 Fax: 678-957-1455 中 国 - 成都 Tel: 91-20-3019-1500 ド イツ - ガーヒング オ ースティン、TX Tel: 86-28-8665-5511 日 本 - 大阪 Tel: 49-8931-9700 Tel: 512-257-3370 Fax: 86-28-8665-7889 Tel: 81-6-6152-7160 ド イツ - ハーン

ボ ストン 中 国 - 重慶 Fax: 81-6-6152-9310 Tel: 49-2129-3766400

Westborough, MA Tel: 86-23-8980-9588 日 本 - 東京 ド イツ - ハイルブロン Tel: 774-760-0087 Fax: 86-23-8980-9500 Tel: 81-3-6880-3770 Tel: 49-7131-67-3636 Fax: 774-760-0088 中 国 - 東莞 Fax: 81-3-6880-3771 ド イツ - カールスルーエ シ カゴ Tel: 86-769-8702-9880 韓 国 - 大邱 Tel: 49-721-625370

Itasca, IL 中 国 - 広州 Tel: 82-53-744-4301 ド イツ - ミュンヘン

Tel: 630-285-0071 Tel: 86-20-8755-8029 Fax: 82-53-744-4302 Tel: 49-89-627-144-0 Fax: 630-285-0075 中 国 - 杭州 韓 国 - ソウル Fax: 49-89-627-144-44 ダ ラス Tel: 86-571-8792-8115 Tel: 82-2-554-7200 ド イツ - ローゼンハイム Addison, TX Fax: 86-571-8792-8116 Fax: 82-2-558-5932 または Tel: 49-8031-354-560 Tel: 972-818-7423 中 国 - 香港 SAR 82-2-558-5934 イ スラエル - ラーナナ Fax: 972-818-2924 Tel: 852-2943-5100 マ レーシア - クアラルンプール Tel: 972-9-744-7705 デ トロイト Fax: 852-2401-3431 Tel: 60-3-6201-9857 イ タリア - ミラノ Nov i, MI 中 国 - 南京 Fax: 60-3-6201-9859 Tel: 39-0331-742611 Tel: 248-848-4000 Tel: 86-25-8473-2460 マ レーシア - ペナン Fax: 39-0331-466781 ヒ ューストン、TX Fax: 86-25-8473-2470 Tel: 60-4-227-8870 イ タリア - パドヴァ Tel: 281-894-5983 中 国 - 青島 Fax: 60-4-227-4068 Tel: 39-049-7625286 イ ンディアナポリス Tel: 86-532-8502-7355 フ ィリピン - マニラ オ ランダ - ドリューネン Noblesv ille, IN Fax: 86-532-8502-7205 Tel: 63-2-634-9065 Tel: 31-416-690399 Tel: 317-773-8323 中 国 - 上海 Fax: 63-2-634-9069 Fax: 31-416-690340 Fax: 317-773-5453 Tel: 86-21-3326-8000 シ ンガポール ノ ルウェー - トロンハイム Tel: 319536-2380 Fax: 86-21-3326-8021 Tel: 65-6334-8870 Tel: 47-7289-7561

ロ サンゼルス 中 国 - 瀋陽 Fax: 65-6334-8850 ポ ーランド - ワルシャワ

Mission Viejo, CA Tel: 86-24-2334-2829 台 湾 - 新竹 Tel: 48-22-3325737 Tel: 949-462-9523 Fax: 86-24-2334-2393 Tel: 886-3-5778-366 ル ーマニア - ブカレスト Fax: 949-462-9608 中 国 - 深圳 Fax: 886-3-5770-955 Tel: 40-21-407-87-50 Tel: 951-273-7800 Tel: 86-755-8864-2200 台 湾 - 高雄 ス ペイン - マドリッド ロ ーリー、NC Fax: 86-755-82031950 Tel: 886-7-213-7830 Tel: 34-91-708-08-90 Tel: 919-844-7510 中 国 - 武漢 台 湾 – 台北 Fax: 34-91-708-08-91 ニ ューヨーク、NY Tel: 86-27-5980-5300 Tel: 886-2-2508-8600 ス ウェーデン - ヨーテボリ Tel: 631-435-6000 Fax: 86-27-5980-5118 Fax: 886-2-2508-0102 Tel: 46-31-704-60-40

サ ンノゼ、CA 中 国 - 西安 タ イ - バンコク ス ウェーデン - ストックホルム

Tel: 408-735-9110 Tel: 86-29-8833-7252 Tel: 66-2-694-1351 Tel: 46-8-5090-4654 Tel: 408-436-4270 Fax: 86-29-8833-7256 Fax: 66-2-694-1350 イ ギリス - ウォーキンガム

カ ナダ - トロント Tel: 44-118-921-5800

Tel: 905-695-1980 Fax: 44-118-921-5820