Arria 10

デバイスの可変精度 DSP ブロッ

ク

3

2014.08.18 A10-DSP 署名 フィードバック この章では、高性能デジタル信号処理(DSP)アプリケーションでより高いビット精度をサポー トするにあたって、Arria® 10 デバイスの可変精度 DSP ブロックがどのように最適化されるかに ついて説明します。Arria 10

デバイスでサポートされる動作モード

表 3-1: Arria 10 デバイスにおける可変精度 DSP ブロックの動作モード 可変精度 DSPブロッ クのリソー ス 動作モード サポートさ れるインス タンス数 プリアダー のサポート 係数のサポート 入力カスケードのサポ ート チェインアウトの サポート 1 つの可 変精度 DSP ブ ロック 固定小数点独立 18 x 19 乗算 2 あり あり あり (2) (3) なし 固定小数点独立 27 x 27 乗算 1 あり あり あり (4) あり 固定小数点の 2 つ の 18 x 19 乗算加 算器モード 1 あり あり あり あり 36 ビット入力に 加算する固定小数 点 18 x 18 乗算加 算器 1 なし なし なし あり 固定小数点 18 x 19 シストリック・ モード 1 あり あり あり あり 浮動小数点乗算モ ード 1 なし なし なし なし 浮動小数点加算器 または減算モー ド 1 なし なし なし なし 1 つの可 変精度 DSP ブ ロック 浮動小数点乗算加 算器または減算モ ード 1 なし なし なし あり 浮動小数点乗算器 累積モード 1 なし なし なし なし 浮動小数点ベクタ 1 モード 1 なし なし なし あり 浮動小数点ベクタ 2 モード 1 なし なし なし あり (2) 下部の乗算器の遅延レジスタのみ使用可能です。 (3) プリアダーへの 2 つの入力それぞれが 18 ビットの最大幅を有します。入力カスケードがプリアダ ー入力の 1 つを供給するために使用される場合、入力カスケードの最大幅は 18 ビットです。 3-2 Arria 10デバイスでサポートされる動作モード 2014.08.18A10-DSP可変精度 DSPブロッ クのリソー ス 動作モード サポートさ れるインス タンス数 プリアダー のサポート 係数のサポート 入力カスケードのサポ ート チェインアウトの サポート 2 つの可 変精度 DSP ブ ロック 複素数 18x19 乗算 1 なし なし あり なし 表 3-2: Arria 10 デバイスにおける可変精度 DSP ブロックの動作モード 可変精度 DSP ブロックのリ ソース 動作モード ダイナミック

ACCUMULATE ダイナミックLOADCONST ダイナミックSUB ダイナミック NEGATE

1 つの可変 精度 DSP ブロック 固定小数点独立 18 x 19 乗算 なし なし なし なし 固定小数点独立 27 x 27 乗算 あり あり なし あり 固定小数点の 2 つの 18 x 19 乗算 加算器モード あり あり あり あり 36 ビット入力に 加算する固定小 数点 18 x 18 乗算 加算器 あり あり あり あり 固定小数点 18 x 19 シストリッ ク・モード あり あり なし なし 浮動小数点乗算 モード なし なし なし なし 浮動小数点加算 器または減算モ ード なし なし なし なし 浮動小数点乗算 加算器または減 算モード なし なし なし なし 浮動小数点乗算 器累積モード あり なし なし なし 浮動小数点ベク タ 1 モード なし なし なし なし 浮動小数点ベク タ 2 モード なし なし なし なし 2 つの可変 精度 DSP 複素数 18 x 19 乗算 なし なし なし なし A10-DSP 2014.08.18 Arria 10デバイスでサポートされる動作モード 3-3

機能

Arria 10 の可変精度 DSP ブロックは、固定小数点演算と浮動小数点演算をサポートしていま す。 固定小数点演算のための機能: • 高性能、消費電力の最適化、および完全にレジスタされた乗算演算 • 18 ビットおよび 27 ビットのワード長 • DSP ブロックにつき 2 つの 18 x 19 乗算器または 1 つの 27 x 27 乗算器 • 乗算結果を組み合わせるビルトイン加算、減算、および 64 ビットのダブル累算レジスタ • プリアダーがディセーブルされる際の 19 ビットまたは 27 ビットのカスケード接続とプリア ダーがフィルタリング・アプリケーションのタップ・ディレイ・ラインを形成するために使 用される際の 18 ビットのカスケード接続 • 外部ロジックのサポートなしで、あるブロックから次のブロックへ出力結果を伝えるための 64 ビット出力バスのカスケード接続 • 対称フィルタの 19 ビット・モードと 27 ビット・モードでサポートされるハード・プリアダ ー • フィルタ実装の 18 ビットおよび 27 ビットの両モードにおける内部係数レジスタ・バンク • 分散された出力加算器を有する 18 ビットおよび 27 ビットのシストリック有限インパルス応 答(FIR)フィルタ • バイアスされた丸め処理のサポート 浮動小数点演算ための機能: • 乗算、加算、減算、積和、および積差 • 累算機能とダイナミック・アキュムレータのリセット・コントロールを有する乗算 • カスケード加算機能を有する乗算 • カスケード減算機能を有する乗算 • 複素数乗算 • ダイレクト・ベクタ・ドット積 • シストリック FIR フィルタ 関連情報• Arria 10 Device Handbook: Known Issues

Arria 10 Device Handbook の章にて予定される更新をリストします。 • Arria 10 デバイスの概要

各デバイスにおける乗算器の数に関する詳細を提供します。

リソース

表 3-3: Arria 10 デバイスの乗算器数 次の表は、各 Arria 10 デバイスの可変精度 DSP リソースをビット単位によりリストしています。 バリアント 製品ライン 可変精度 DSPブロ ック 独立した入力および 出力 乗算演算子 ピーク ギガ単位で の秒あたり の浮動小数 点動作 (GFLOP) 単精度浮 動小数点 加算器 18 x 19 乗算加算 器モード 18 x 18 36ビット入力 に加算する乗 算加算器 18 x 19 乗算器 27 x 27 乗算器 Arria 10 GX GX 160 156 312 156 140 156 156 156 GX 220 191 382 191 173 192 191 191 GX 270 830 1,660 830 720 800 830 830 GX 320 985 1,970 985 887 985 985 985 GX 480 1,368 2,736 1,368 1,231 1,368 1,368 1,368 GX 570 1,523 3,046 1,523 1,371 1,523 1,523 1,523 GX 660 1,688 3,376 1,688 1,510 1,678 1,688 1,688 GX 900 1,518 3,036 1,518 1,366 1,518 1,518 1,518 GX 1150 1,518 3,036 1,518 1,366 1,518 1,518 1,518 Arria 10 GT GT 1150GT 900 1,5181,518 3,0363,036 1,5181,518 1,3661,366 1,5181,518 1,5181,518 1,5181,518 Arria 10 SX SX 160 156 312 156 140 156 156 156 SX 220 191 382 191 173 192 191 191 SX 270 830 1,660 830 720 800 830 830 SX 320 985 1,970 985 887 985 985 985 SX 480 1,368 2,736 1,368 1,231 1,368 1,368 1,368 SX 570 1,523 3,046 1,523 1,371 1,523 1,523 1,523 SX 660 1,688 3,376 1,688 1,510 1,678 1,688 1,688デザインの検討事項

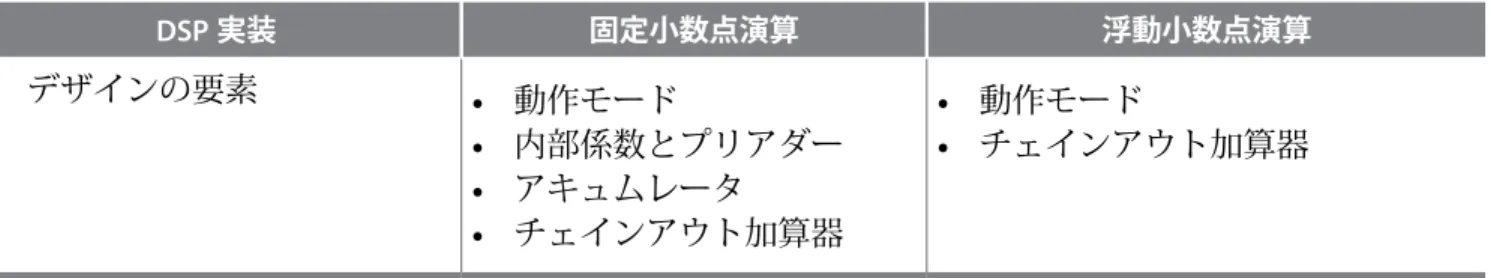

デザインにあたって以下の要素を考慮する必要があります。 A10-DSP 2014.08.18 リソース 3-5表 3-4: デザインの検討事項 DSP実装 固定小数点演算 浮動小数点演算 デザインの要素 • 動作モード • 内部係数とプリアダー • アキュムレータ • チェインアウト加算器 • 動作モード • チェインアウト加算器

動作モード

Quartus II ソフトウェアには、乗算器の動作モードを制御するために使用できる IP コアが含まれ ます。IP カタログでパラメータ設定を入力すると、Quartus II ソフトウェアは自動的に可変精度 DSP ブロックをコンフィギュレーションします。また、可変精度 DSP ブロックは DSP Builder Advanced Blockset と OpenCL を使用して実装するこ ともできます。 表 3-5: 動作モード 固定小数点演算 浮動小数点演算 アルテラは、Arria 10 の可変精度 DSP ブロック の各種モードをデザインに実装するにあたっ て 2 つの方法(Quartus II の DSP IP コアを使用 する方法と HDL 推測を使用する方法)を提供 します。 固定小数点演算実装の Arria 10 の可変精度 DSP ブロックでは、次の Quartus II の IP コアがサポ ートされます。 • LPM_MULT • ALTERA_MULT_ADD • ALTMULT_COMPLEX アルテラは、Arria 10 の可変精度 DSP ブロック の各種モードをデザインに実装するにあたっ て 1 つの方法(Quartus II の DSP IP コアを使用 する方法)を提供します。 関連情報

• Introduction to Megafunction User Guide

• Integer Arithmetic Megafunctions User Guide

• Floating-Point Megafunctions User Guide

• Quartus II Software Help

固定小数点演算向けの内部係数とプリアダー

プリアダー機能を使用するにあたって、プリアダーへの入力は同じクロック設定である必要があ ります。

また、プリアダー機能をイネーブルする場合、入力カスケード・サポートは 18 ビット・モード でのみ使用可能です。 18 ビットおよび 27 ビットの両モードでは、係数機能とプリアダー機能を個別に使用することが できます。

固定小数点演算向けのアキュムレータ

Arria 10 デバイスのアキュムレータは、出力レジスタ・バンクとアキュムレータの間に位置する 64 ビットのダブル累算レジスタをイネーブルすることによってダブル累算をサポートします。 ダブル累算レジスタは、プログラミング・ファイルでスタティックに設定されています。チェインアウト加算器

表 3-6: チェインアウト加算器 固定小数点演算 浮動小数点演算 出力チェイン・パスを使用して、他の DSP ブロ ックからの結果を加算することができます。 出力チェイン・パスを使用して、他の DSP ブロックからの結果を加算することができます。 特定の動作モードへのサポート: • 積和モードまたは積差モード • ベクタ 1 モード • ベクタ 2 モードブロック・アーキテクチャ

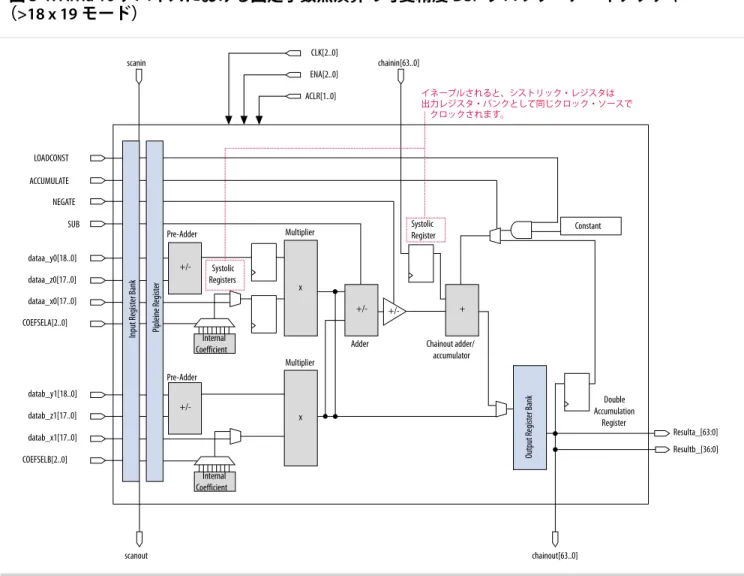

Arria 10 の可変精度 DSP ブロックは以下の要素で構成されています。 表 3-7: ブロック・アーキテクチャ DSP実装 固定小数点演算 浮動小数点演算 ブロック・アーキ テクチャ •• 入力レジスタ・バンクパイプライン・レジスタ • プリアダー • 内部係数 • 乗算器 • 加算器 • アキュムレータとチェイン アウト加算器 • シストリック・レジスタ • ダブル累算レジスタ • 出力レジスタ・バンク • 入力レジスタ・バンク • パイプライン・レジスタ • 乗算器 • 加算器 • アキュムレータとチェインアウト加算器 • 出力レジスタ・バンク A10-DSP 2014.08.18 固定小数点演算向けのアキュムレータ 3-7可変精度 DSP ブロックが固定小数点演算シストリック FIR モードでコンフィギュレーションさ れない場合、両方のシストリック・レジスタがバイパスされます。 図 3-1: Arria 10 デバイスにおける固定小数点演算の可変精度 DSP ブロック・アーキテクチャ (>18 x 19 モード) Input Regist er B ank scanin scanout LOADCONST ACCUMULATE NEGATE dataa_y0[18..0] dataa_z0[17..0] dataa_x0[17..0] COEFSELA[2..0] datab_y1[18..0] datab_z1[17..0] datab_x1[17..0] COEFSELB[2..0] SUB +/-Pre-Adder +/-Pre-Adder +/-Internal Coefficient Internal Coefficient Multiplier Adder +/- +/-Systolic Registers Systolic Register Chainout adder/ accumulator + Output Regist er B ank Constant Double Accumulation Register chainin[63..0] chainout[63..0] Resulta_[63:0] Multiplier x x CLK[2..0] ENA[2..0] ACLR[1..0] イネーブルされると、シストリック・レジスタは 出力レジスタ・バンクとして同じクロック・ソースで クロックされます。 Pipleine Regist er Resultb_[36:0] 3-8 ブロック・アーキテクチャ 2014.08.18A10-DSP

図 3-2: Arria 10 デバイスにおける固定小数点演算の可変精度 DSP ブロック・アーキテクチャ (>27 x 27 モード) + Constant 64 Double Accumulation Register Result[63..0] chainout[63..0] Internal Coefficients +/-LOADCONST ACCUMULATE NEG dataa_y0[26..0] dataa_z0[25..0] dataa_x0[26..0] COEFSELA[2..0] Multiplier x chainin[63..0] Output Register Bank Chainout Adder/ Accumulator Input Register Bank Pre-Adder +/-Pipeline Register 図 3-3: Arria 10 デバイスにおける浮動小数点演算の可変精度 DSP ブロック・アーキテクチャ chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] dataa_y0[31:0] dataa_z0[31:0] Output Register Bank result[31:0] Input Register Bank Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank

A10-DSP

入力レジスタ・バンク

表 3-8: 入力レジスタ・バンク 固定小数点演算 浮動小数点演算 • データ • ダイナミック・コントロール信号 • 遅延レジスタの 2 セット • データ • ダイナミック・コントロール信号 DSP ブロック内のすべてのレジスタはポジティブ・エッジでトリガされ、パワー・アップ時にク リアされます。各乗算器オペランドは、入力レジスタをバイパスして直接入力レジスタまたは乗 算器を供給することができます。 次の可変精度 DSP ブロック信号は、可変精度 DSP ブロック内の入力レジスタを制御します。 • CLK[2..0] • ENA[2..0] • ACLR[0] 固定小数点演算の 18 x 19 モードでは、入力カスケードおよびチェインアウト機能の両方を使用 する場合、遅延レジスタを使用してレイテンシ要件のバランスを取ることができます。 タップ遅延ライン機能を使用すると、一般配線またはカスケード・チェインから乗算器入力の上 位レグ、固定小数点演算 18 x 19 モードの dataa_y0 と datab_y1、および固定小数点演算 27 x 27 モ ードのみの dataa_y0 を駆動することができます。固定小数点演算の遅延レジスタの 2 セット

固定小数点演算の 18 x 19 シストリック・モードで使用可能な、入力カスケード・チェインに沿 った 2 つの遅延レジスタは、上位遅延レジスタと下位遅延レジスタになります。その他のすべて の固定小数点演算モードでは、下位遅延レジスタのみ使用できます。 3-10 入力レジスタ・バンク 2014.08.18A10-DSP図 3-4: Arria 10 デバイスにおける固定小数点演算 18 x 19 モードの可変精度 DSP ブロックの入力レ ジスタ 次の図は、データ・レジスタのみを表しています。コントロール信号のレジスタは図示されてい ません。 dataa_y0[18..0] dataa_z0[17..0] dataa_x0[17..0] datab_y1[18..0]

Top delay registers

datab_z1[17..0]

datab_x1[17..0]

Bottom delay registers scanin[18..0] scanout[18..0] CLK[2..0] ENA[2..0] ACLR[0] A10-DSP 2014.08.18 固定小数点演算の遅延レジスタの 2 セット 3-11

図 3-5: Arria 10 デバイスにおける固定小数点演算 27 x 27 モードの可変精度 DSP ブロックの入力レ ジスタ 次の図は、データ・レジスタのみを表しています。コントロール信号のレジスタは図示されてい ません。 dataa_y0[26..0] dataa_z0[25..0] dataa_x0[26..0] scanin[26..0] CLK[2..0] ENA[2..0] ACLR[0] scanout[26..0]

パイプライン・レジスタ

パイプライン・レジスタは最大 Fmax 性能を得るために使用されます。なお、高い Fmax が不要 の場合、パイプライン・レジスタはバイパスすることができます。 次の可変精度 DSP ブロック信号が可変精度 DSP ブロック内のパイプライン・レジスタを制御し ます。 • CLK[2..0] • ENA[2..0] • ACLR[1] 浮動小数点演算は、以下のいずれかを実行することができるパイプライン・レジスタの 2 つのレ イテンシ・レイヤを有します。 • パイプライン・レジスタのすべてのレイテンシ・レイヤをバイパスする • パイプライン・レジスタのレイテンシ・レイヤのいずれか 1 つを使用する • パイプライン・レジスタの両方のレイテンシ・レイヤを使用する 3-12 パイプライン・レジスタ 2014.08.18A10-DSP固定小数点演算向けのプリアダー

各可変精度 DSP ブロックはそれぞれ、2 つの 19 ビット・プリアダーを有します。これらのプリ アダーは以下の構成でコンフィギュレーションすることができます。 • 2 つの独立した 19 ビット・プリアダー • 1 つの 27 ビット・プリアダー プリアダーは、次の入力コンフィギュレーションで加算と減算の両方をサポートします。 • 18 x 19 モードにおける 18 ビット(符号ありまたは符号なし)の加算あるいは減算 • 27 x 27 モードにおける 26 ビットの加算あるいは減算 同じ DSP ブロック内のプリアダーの両方が使用される場合、プリアダーは同じ動作タイプ(加 算または減算のいずれか)を共有する必要があります。固定小数点演算向けの内部係数

Arria 10 の可変精度 DSP ブロックでは、ダイナミック入力または内部係数のいずれかから被乗数 を柔軟に選択することができます。 内部係数は、18 ビット・モードと 27 ビット・モードで被乗数の定数係数を最大 8 つサポートす ることができます。内部係数機能をイネーブルすると、係数マルチプレクサの選択を制御するに あたってCOEFSELA/COEFSELBが使用されます。乗算器

1 つの可変精度 DSP ブロックは、乗算器のデータ幅と実装に応じて多数の乗算を並行して実行す ることができます。 各可変精度 DSP ブロックはそれぞれ、2 つの乗算器を有します。これら 2 つの乗算器は、いくつ かの動作モードでコンフィギュレーションすることができます。 表 3-9: 動作モード 固定小数点演算 浮動小数点演算 • 1 つの 27 x 27 乗算器 • 2 つの 18(符号ありまたは符号な し)x 19(符号あり)乗算器 1 つの浮動小数点演算単精度乗算器 関連情報 3-15 ページの 動作モードの説明 乗算器の動作モードについての詳細を提供します。加算器

動作モードに応じて、以下のように加算器を使用することができます。 • 1 つの 55 ビット加算器または 38 ビット加算器 • 2 つの 18 x 19 モード(加算器がバイパスされる) • 1 つの浮動小数点演算単精度加算器 A10-DSP 2014.08.18 固定小数点演算向けのプリアダー 3-13DSP実装 ダイナミック SUB ポートを使用 した加算 ダイナミック SUB ポートを使用した減算 固定小数点演算 あり あり 浮動小数点演算 なし なし

固定小数点演算のアキュムレータとチェインアウト加算器

Arria 10 の可変精度 DSP ブロックでは、固定小数点演算向けの 64 ビットのアキュムレータと 64 ビットの加算器をサポートしています。 次の信号は、アキュムレータの機能をダイナミックに制御することができます。 • NEGATE • LOADCONST • ACCUMULATE アキュムレータは、出力レジスタ・バンクとアキュムレータの間に位置する 64 ビットのダブル 累算レジスタをイネーブルすることによってダブル累算をサポートします。 ダブル累算レジスタは、プログラミング・ファイルでスタティックに設定されています。 アキュムレータおよびチェインアウト加算器機能は、2 つの固定小数点演算の独立した 18 x 19 モードではサポートされません。 表 3-10: アキュムレータ機能とダイナミック・コントロール信号 次の表では、各機能のダイナミック信号の設定と説明をリストしています。なお、この表中の X は"don't care"の値を示します。機能 説明 NEGATE LOADCONST ACCUMULATE

Zeroing アキュムレータをディセーブルします。 0 0 0 Preload 結果は常にプリロー ド値に加算されます。 64 ビットのプリロー ド値の 1 ビットのみ が“1”になります。こ れは、64 ビット結果 の任意の位置への、 DSP 結果の丸めとし て使用することがで きます。 0 1 0 Accumulation 前の累算結果に現在の結果を加算します。 0 X 1 Decimation + Accumulate この機能は現在の結 果を 2 の補数に変換 し、以前の結果に加算 します。 1 X 1 3-14 固定小数点演算のアキュムレータとチェインアウト加算器 2014.08.18A10-DSP

機能 説明 NEGATE LOADCONST ACCUMULATE Decimation + Chainout Adder この機能は現在の結 果を 2 の補数に変換 し、以前の DSP ブロ ックの出力に加算し ます。 1 0 0

固定小数点演算のシストリック・レジスタ

各可変精度 DSP ブロックはそれぞれ、2 つのシストリック・レジスタを有します。可変精度 DSP ブロックが固定小数点演算シストリック FIR モードでコンフィギュレーションされない場合、両 方のシストリック・レジスタがバイパスされます。 シストリック・レジスタの最初のセットは、上位乗算器の 18 ビット入力と 19 ビット入力をそれ ぞれ登録するために使用される 18 ビットおよび 19 ビットのレジスタで構成されています。 シストリック・レジスタの 2 番目のセットは、以前の可変精度 DSP ブロックからのチェインイ ン入力を遅延させるために使用されます。 また、出力レジスタとして、同じクロック・ソースのすべてのシストリック・レジスタをクロッ クする必要があります。なお、出力レジスタはオンにしておく必要があります。固定小数点演算のダブル累算レジスタ

ダブル累算レジスタは、アキュムレータのフィードバック・パスにおける追加のレジスタです。 ダブル累算レジスタをイネーブルすると、アキュムレータのフィードバック・パスにて追加のク ロック・サイクル遅延が生じます。 このレジスタは、出力レジスタ・バンクと同じCLK、ENA、およびACLR 設定を有します。 このレジスタをイネーブルすることによって、同じ数の可変精度 DSP ブロックを使用する 2 つ のアキュムレータ・チャネルを有することができます。これはインタリーブした複雑なデータ (I、Q)を処理する際に役立ちます。出力レジスタ・バンク

クロック信号のポジティブ・エッジは 74 ビットのバイパス可能な出力レジスタ・バンクをトリ ガし、パワー・アップ後にクリアされます。 次の可変精度 DSP ブロック信号は、各可変精度 DSP ブロックの出力レジスタを制御します。 • CLK[2..0] • ENA[2..0] • ACLR[1]動作モードの説明

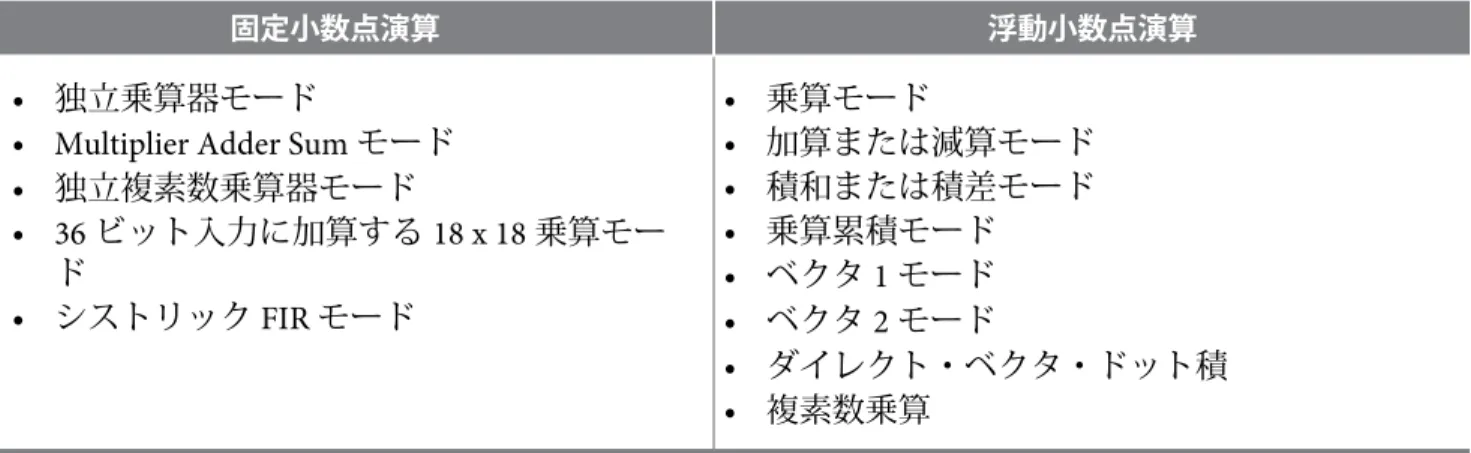

この項では、固定小数点演算および浮動小数点演算の動作モードを効果的にサポートするため に、Arria 10 の可変精度 DSP ブロックをコンフィギュレーションする方法を説明します。 A10-DSP 2014.08.18 固定小数点演算のシストリック・レジスタ 3-15表 3-11: 動作モード

固定小数点演算 浮動小数点演算

• 独立乗算器モード

• Multiplier Adder Sum モード

• 独立複素数乗算器モード • 36 ビット入力に加算する 18 x 18 乗算モー ド • シストリック FIR モード • 乗算モード • 加算または減算モード • 積和または積差モード • 乗算累積モード • ベクタ 1 モード • ベクタ 2 モード • ダイレクト・ベクタ・ドット積 • 複素数乗算

固定小数点演算の動作モード

独立乗算器モード

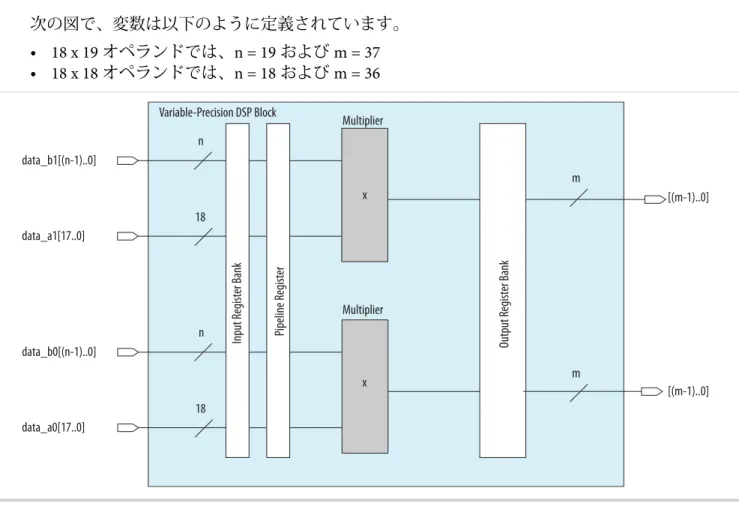

独立した入力および出力乗算器モードでは、可変精度 DSP ブロックは汎用乗算器の個別の乗算 演算を実行します。 コンフィギュレーション ブロックごとの乗算器数 18(符号ありまたは符号なし)x 18(符号ありまたは符 号なし) 2 18(符号ありまたは符号なし)x 19(符号あり) 2 27(符号ありまたは符号なし)x 27(符号ありまたは符 号なし) 1 3-16 固定小数点演算の動作モード 2014.08.18A10-DSP18 x 18または 18 x 19 独立乗算器 図 3-6: Arria 10 デバイスの各可変精度 DSP ブロックにおける 2 つの 18 x 18 または 18 x 19 独立乗算 器 次の図で、変数は以下のように定義されています。 • 18 x 19 オペランドでは、n = 19 および m = 37 • 18 x 18 オペランドでは、n = 18 および m = 36 [(m-1)..0] Multiplier x Multiplier x Input Regist er B ank data_b1[(n-1)..0] data_a1[17..0] n 18 Variable-Precision DSP Block data_b0[(n-1)..0] data_a0[17..0] n 18 m [(m-1)..0] m Output Regist er B ank Pipeline Regist er 27 x 27独立乗算器 図 3-7: Arria 10 デバイスの各可変精度 DSP ブロックにおける 1 つの 27 x 27 独立乗算器モード このモードでは、チェインアウト加算器またはアキュムレータと組み合わせた場合、resultは 最大 64 ビットになり得ます。 Input Regist er B ank Multiplier x Result[53..0] dataa_b0[26..0] dataa_a0[26..0] 27 27 54 Variable-Precision DSP Block Output Regist er B ank Pipeline Regist er A10-DSP 2014.08.18 18 x 18または 18 x 19 独立乗算器 3-17

独立複素数乗算器

Arria 10 デバイスは、2 つの固定小数点演算 Multiplier Adder Sum モードを使用して 18 x 19 複素 数乗算器モードをサポートします。

図 3-8: 複素数乗算式のサンプル

虚数部の[(a × d) + (b × c)]は 1 番目の可変精度 DSP ブロックに実装され、実数部の[(a × c) - (b × d)]は 2 番目の可変精度 DSP ブロックに実装されます。

18 x 19複素数乗算器 図 3-9: Arria 10 デバイスの 2 つの可変精度 DSP ブロックと 1 つの 18 x 19 複素数乗算器 Variable-Precision DSP Block 1 Variable-Precision DSP Block 2 Input Regist er B ank Imaginary Part (ad+bc) Multiplier c[18..0] b[17..0] 19 18 Multiplier d[18..0] a[17..0] 19 18 38 Adder + x x Output Regist er B ank Input Regist er B ank Real Part (ac-bd) d[18..0] b[17..0] 19 18 c[18..0] a[17..0] 19 18 38 Output Regist er B ank Multiplier Multiplier Adder -x x Pipeline Regist er Pipeline Regist er A10-DSP 2014.08.18 18 x 19複素数乗算器 3-19

Multiplier Adder Sum

モード

図 3-10: Arria 10 デバイスの 1 つの可変精度 DSP ブロックの 2 つの 18 x 19 乗算器の和 Input Regist er B ank Result[37..0] dataa_y0[18..0] dataa_x0[17..0] 19 18 Variable-Precision DSP Block datab_y1[18..0] datab_x1[17..0] 19 18 38 Multiplier Multiplier Adder +/-SUB_COMPLEX Output Regist er B ank x x Pipeline Regist er36

ビット入力に加算する 18 x 19 乗算モード

Arria 10 の可変精度 DSP ブロックは、1 つの 18 x 19 乗算を 36 ビット入力に加算することができ ます。 下部の乗算器がバイパスされている間は、上位の乗算器を使用して 18 x 19 乗算への入力を提供 します。 datab_y1[17..0]信号とdatab_y1[35..18]信号は、36 ビット入力を生成するために連結 されます。 図 3-11: Arria 10 デバイスの 36 ビット入力に加算する 18 x 19 乗算モード Input Regist er B ank Result[37..0] dataa_y0[17..0] dataa_x0[17..0] 19 18 Variable-Precision DSP Block datab_y1[35..18] datab_y1[17..0] 18 18 37 Multiplier Adder SUB_COMPLEX Output Regist er B ank x +/-Pipeline Regist erシストリック FIR モード

図 3-12: 基本的な FIR フィルタの式 タップの数や入力容量によって、多数の加算器のチェインを介する遅延は非常に大きくなること があります。遅延性能の問題を解決するには、タップごとに配置される追加の遅延要素でシスト リック形式を使用して、レイテンシの増加を代償に性能を向上させます。 図 3-13: シストリック FIR フィルタの等価回路 1 − k c ] [ n x ] [ n y 1 c c2 ck ] [ 1 n w w2 n[ ] w k−1 n[ ] w k[ n] Arria 10 の可変精度 DSP ブロックは、次のシストリック FIR 構造をサポートします。 • 18 ビット • 27 ビット シストリック FIR モードでは、乗算器の入力はソースの 4 つの異なるセットから供給できま す。 • 2 つのダイナミック入力 • 1 つのダイナミック入力と 1 つの係数入力 • 1 つの係数入力と 1 つのプリアダー出力 • 1 つのダイナミック入力と 1 つのプリアダー出力 可変精度ブロック・アーキテクチャ・ビューへのシストリック・モード・ユーザー・ビューのマッ ピング 次の図は、レジスタをリタイミングし、加算器を再構築することにより、Arria 10 の可変精度 DSP ブロック(d)を使用してシストリック FIR フィルタ(a)のユーザー・ビューを実装できる A10-DSP 2014.08.18 可変精度ブロック・アーキテクチャ・ビューへのシストリック・モード・ユーザ ー・ビューのマッピング 3-21

よび dataa_x0 入力パスでシストリック・レジスタにリタイミングすることができます。レジス タのリタイミングの最終結果は(c)に示されています。加算器の入力と位置の再構築による 2 つの乗算器の加算結果は、(d)に示されているようにチェインアウト加算器によってチェインイ ン入力に加算されます。 図 3-14: 可変精度ブロック・アーキテクチャ・ビューへのシストリック・モード・ユーザー・ビュー のマッピング x[n] c1

(a) Systolic FIR Filter

User View Architecture View (Before Retiming)(b) Variable Precision Block

Second DSP Block dataa_y0 x[n] dataa_x0 c1 datab_y1 x[n-2] datab_x1 c2 w1[n] w2[n] dataa_y0 x[n-4] dataa_x0 c3 w3[n] Register B datab_y1 x[n-6] datab_x1 c4 w4[n] Register C y[n] Register A Multiplier Multiplier Adder Output Register Bank Result First DSP Block Result Output Register Bank Retiming Chainout Adder Chainin from Previous DSP Block

(c) Variable Precision Block Architecture View (After Retiming)

Second DSP Block dataa_y0 x[n] dataa_x0 c1 datab_y1 x[n-2] datab_x1 c2 w1[n] w2[n] dataa_y0 x[n-4] dataa_x0 c3 w3[n] Register B datab_y1 x[n-6] datab_x1 c4 w4[n] Register C y[n] Register A Multiplier Multiplier Adder Output Register Bank Result First DSP Block Result Output Register Bank Chainout Adder Chainin from Previous DSP Block Systolic Register Systolic Registers

(d) Variable Precision Block Architecture View (Adder Restructured)

Second DSP Block dataa_y0 x[n] dataa_x0 c1 datab_y1 x[n-2] datab_x1 c2 w1[n] w2[n] dataa_y0 x[n-4] dataa_x0 c3 w3[n] Register B datab_y1 x[n-6] datab_x1 c4 w4[n] Register C y[n] Register A Multiplier Multiplier Adder Output Register Bank Result First DSP Block Result Output Register Bank Chainout Adder Chainin from Previous DSP Block Systolic Register Systolic Registers Adder x[n-2] c2 w1[n] w2[n] x[n-4] c3 w3[n] x[n-6] c4 w4[n] y[n] Register B Register A Register A 18ビットのシストリック FIR モード 18 ビットのシストリック FIR モードでは、加算器はデュアル 44 ビット加算器としてコンフィギ ュレーションされます。そのため、18 ビット動作(36 ビット積)を使用する際、オーバーヘッ ドの 8 ビットを提供します。これにより、合計で 256 の乗算器の積が可能になります。 3-22 18ビットのシストリック FIR モード 2014.08.18A10-DSP

図 3-15: Arria 10 デバイスの 18 ビット・シストリック FIR モード Input Regist er B ank dataa_y0[17..0] dataa_z0[17..0] dataa_x0[17..0] COEFSELA[2..0] datab_y1[17..0] datab_z1[17..0] datab_x1[17..0] COEFSELB[2..0] +/-Pre-Adder +/-Pre-Adder +/-Internal Coefficient Internal Coefficient Multiplier Multiplier Adder +/-Systolic Registers Systolic Register Chainout adder or accumulator + Output Regist er B ank chainin[43..0] chainout[43..0] Result[43..0]

18-bit Systolic FIR x x 18 18 18 18 18 18 3 3 44 44 44 Pipeline Regist er イネーブルされると、シストリック・レジスタは 出力レジスタ・バンクとして同じクロック・ソースで クロックされます。 27ビットのシストリック FIR モード 27 ビットのシストリック FIR モードでは、チェインアウト加算器またはアキュムレータは 64 ビット動作にコンフィギュレーションされます。また、27 ビットのデータ( 54 ビット積)を 使用する際、オーバヘッドの 10 ビットを提供します。これにより、合計で 1,024 の乗算器の積 が可能になります。 27 ビット・シストリック FIR モードでは、DSP ブロックごとに 1 ステージのシストリック・フ ィルタを実装することができます。なお、このモードではシストリック・レジスタは不要です。 A10-DSP 2014.08.18 27ビットのシストリック FIR モード 3-23

図 3-16: Arria 10 デバイスの 27 ビット・シストリック FIR モード Input Regist er B ank dataa_y0[25..0] dataa_z0[25..0] dataa_x0[26..0] COEFSELA[2..0] Pre-Adder +/-Internal Coefficient Multiplier Adder +/-Chainout adder or accumulator + chainin[63..0] chainout[63..0] 27-bit Systolic FIR

27 x Output Regist er B ank 26 3 27 26 64 64 Pipeline Regist er

浮動小数点演算の動作モード

単一の浮動小数点演算機能

1 つの浮動小数点演算 DSP は、次の機能を実行することができます。 • 乗算モード • 加算または減算モード • 乗算累積モード 乗算モード このモードでは、基本的な浮動小数点乗算(y*z)を適用することができます。 3-24 浮動小数点演算の動作モード 2014.08.18A10-DSP図 3-17: Arria 10 デバイスの乗算モード chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] dataa_y0[31:0] dataa_z0[31:0] Output Register Bank result[31:0] Input Register Bank Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank 加算または減算モード このモードでは、基本的な浮動小数点加算(x+y)または基本的な浮動小数点減算(x-y)を適用 することができます。 図 3-18: Arria 10 デバイスの加算または減算モード chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] dataa_y0[31:0] dataa_z0[31:0] Output Register Bank Input Register Bank result[31:0] Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank

乗算累積モード

このモードでは、以前の乗算結果との浮動小数点加算に続いて浮動小数点乗算を実行します

A10-DSP

図 3-19: Arria 10 デバイスの乗算累積モード chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] dataa_y0[31:0] dataa_z0[31:0] Output Register Bank Input Register Bank result[31:0] Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank

複数の浮動小数点演算機能

複数の浮動小数点演算 DSP は、以下の機能を実行することができます。 • チェインイン・パラメータがオフの場合、単一の浮動小数点演算 DSP を使用する積和または 積差モード • ベクタ 1 モード • ベクタ 2 モード • ダイレクト・ベクタ・ドット積 • 複素数乗算 積和または積差モード このモードでは、浮動小数点加算または浮動小数点減算に続いて浮動小数点乗算を実行します { ((y*z) + x)または((y*z) - x) }。なお、チェインイン・パラメータを使用することにより、マルチ プル・チェイン・モードをイネーブルすることができます。 3-26 複数の浮動小数点演算機能 2014.08.18A10-DSP図 3-20: Arria 10 デバイスの積和または積差モード chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] dataa_y0[31:0] dataa_z0[31:0] Output Register Bank Input Register Bank result[31:0] Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank ベクタ 1 モード このモードでは、以前の可変 DSP ブロックからのチェインイン入力との浮動小数点加算に続い て浮動小数点乗算を実行します。入力 x は直接チェインアウトに供給されます。 (チェインアウト= x で、結果= y*z +チェインイン) 図 3-21: Arria 10 デバイスのベクタ 1 モード chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] dataa_y0[31:0] dataa_z0[31:0] Output Register Bank Input Register Bank result[31:0] Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank

A10-DSP

ベクタ 2 モード このモードでは、乗算結果が直接チェインアウトに供給される浮動小数点乗算を実行します。以 前の可変 DSP ブロックからのチェインイン入力は出力結果として入力 x に加算されます。 (チェインアウト= y*z で、結果= x +チェインイン) 図 3-22: Arria 10 デバイスのベクタ 2 モード chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] dataa_y0[31:0] dataa_z0[31:0] Output Register Bank result[31:0] Input Register Bank Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank ダイレクト・ベクタ・ドット積 次の図では、ダイレクト・ベクタ・ドット積は、以下の DSP モードを設定することによって複 数の DSP ブロックで実装されています。 • チェインイン・パラメータがオンの積和および減算モード • ベクタ 1 • ベクタ 2 3-28 ベクタ 2 モード 2014.08.18A10-DSP

図 3-23: ダイレクト・ベクタ・ドット積 chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] B dataa_y0[31:0] A dataa_z0[31:0] Output Register Bank Input Register Bank result[31:0] AB + CD Multiplier Adder Pipeline Register Bank Pipeline Register Bank Pipeline Register Bank chainout[31:0] chainin[31:0] accumulate AB + CD dataa_x0[31:0] D dataa_y0[31:0] C dataa_z0[31:0] Output Register Bank result[31:0] AB + CD + EF + GH Input Register Bank Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank chainout[31:0] chainin[31:0] accumulate EF + GH dataa_x0[31:0] F dataa_y0[31:0] E dataa_z0[31:0] Output Register Bank Input Register Bank result[31:0] EF + GH Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank chainout[31:0] chainin[31:0] accumulate AB + CD + EF + GH dataa_x0[31:0] H dataa_y0[31:0] G dataa_z0[31:0] Output Register Bank result[31:0] Input Register Bank Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank chainout[31:0] chainin[31:0] accumulate dataa_x0[31:0] J dataa_y0[31:0] I dataa_z0[31:0] Output Register Bank Input Register Bank result[31:0] IJ +KL Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank Vector One Vector Two Vector One Multi-Chain Vector Two 複素数乗算 Arria 10 デバイスは、4 つの Arria 10 可変精度 DSP ブロックを使用して浮動小数点演算の単精度 複素数乗算器をサポートします。 図 3-24: 複素数乗算式のサンプル A10-DSP 2014.08.18 複素数乗算 3-29

虚数部の[(a × d) + (b × c)]は最初の 2 つの可変精度 DSP ブロックに実装され、実数部の[(a × c) - (b × d)]は 2 番目の可変精度 DSP ブロックに実装されます。 図 3-25: 実数結果の複素数乗算 chainin[31:0] accumulate dataa_x0[31:0] a dataa_y0[31:0] c dataa_z0[31:0] Output Register Bank result[31:0] Input Register Bank Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank chainout[31:0] accumulate dataa_x0[31:0] b dataa_y0[31:0] d dataa_z0[31:0] Output Register Bank Input Register

Bank result[31:0] Result Real

Multiplier Subtract Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank chainout[31:0] chainin[31:0]

Multiplication Mode

Multiply-Add or Multiply-Subtract Mode

図 3-26: 虚数結果の複素数乗算 chainin[31:0] accumulate dataa_x0[31:0] a dataa_y0[31:0] d dataa_z0[31:0] Output Register Bank result[31:0] Input Register Bank Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank chainout[31:0] accumulate dataa_x0[31:0] b dataa_y0[31:0] c dataa_z0[31:0] Output Register Bank Input Register

Bank result[31:0] Result Imaginary

Multiplier Adder Pipeline Register Bank Pipeline Register

Bank PipelineRegister Bank chainout[31:0] chainin[31:0]

Multiplication Mode

Multiply-Add or Multiply-Subtract Mode

改訂履歴

A10-DSP

日付 バージョン 変更内容 2014 年 8 月 2014.08.18 • 浮動小数点演算を追加。 • 可変精度 DSP ブロックの動作モードにダイナミック ACCUMULATE、ダイナミック LOADCONST、ダイナミック SUB、ダイナミック NEGATE を追加。 • 入力カスケード・チェインに沿って上位遅延レジスタと下位遅 延レジスタを追加。 • 可変精度 DSP ブロック内のパイプライン・レジスタを制御する 可変精度 DSP ブロック信号を追加。 • 同じ DSP ブロック内の両方のプリアダーが使用されている場 合、プリアダーは同じ動作タイプ(加算または減算のいずれか) を共有しなければならない、という条件を追加。 • 55 ビット加算器を更新。 • 38 ビット加算器を追加。 • 2 つの 18 x 19 モード(加算器がバイパスされる)を更新。 • Decimation を Decimation + Accumulate に更新。

• アキュムレータ機能とダイナミック・コントロール信号に

Decimation + Chainout Adder を追加。

• ブロックごとの 1 つの乗算器に 27(符号ありまたは符号なし) x 27(符号ありまたは符号なし)コンフィギュレーションを追 加。 • 1 つの可変精度 DSP ブロックの 2 つの 18 x 19 乗算の和のブロ ック図と、36 ビット入力に加算する 1 つの 18 x 18 乗算モードの ブロック図からチェインアウト加算器またはアキュムレータを 削除。 • 基本的な FIR フィルタの式を更新。 • 可変精度ブロック・アーキテクチャ・ビューへのシストリック・ モード・ユーザー・ビューのマッピングを追加。 • 27 ビットのシストリック FIR モードではシストリック・レジス タは不要である旨を追加。 2013 年 12 月 2013.12.02 初版 3-32 改訂履歴 2014.08.18A10-DSP

![図 3-2: Arria 10 デバイスにおける固定小数点演算の可変精度 DSP ブロック・アーキテクチャ (>27 x 27 モード) + Constant 64 Double AccumulationRegister Result[63..0] chainout[63..0]InternalCoefficients+/-LOADCONSTACCUMULATENEGdataa_y0[26..0]dataa_z0[25..0]dataa_x0[26..0]COEFSELA[2..0]Multiplie](https://thumb-ap.123doks.com/thumbv2/123deta/7027943.785549/9.918.99.845.94.933/デバイスおける可変精度ブロックアーキテクチャモードConstantDoubleInternalCoefficientsCOEFSELAMultiplie.webp)

![図 3-4: Arria 10 デバイスにおける固定小数点演算 18 x 19 モードの可変精度 DSP ブロックの入力レ ジスタ 次の図は、データ・レジスタのみを表しています。コントロール信号のレジスタは図示されてい ません。 dataa_y0[18..0] dataa_z0[17..0] dataa_x0[17..0] datab_y1[18..0]](https://thumb-ap.123doks.com/thumbv2/123deta/7027943.785549/11.918.88.869.182.904/デバイスブロックジスタデータレジスタコントロールレジスタ.webp)

![図 3-5: Arria 10 デバイスにおける固定小数点演算 27 x 27 モードの可変精度 DSP ブロックの入力レ ジスタ 次の図は、データ・レジスタのみを表しています。コントロール信号のレジスタは図示されてい ません。 dataa_y0[26..0] dataa_z0[25..0] dataa_x0[26..0] scanin[26..0] CLK[2..0]ENA[2..0]ACLR[0] scanout[26..0] パイプライン・レジスタ パイプライン・レジスタは最大 Fmax 性能を得るた](https://thumb-ap.123doks.com/thumbv2/123deta/7027943.785549/12.918.210.834.186.656/データレジスタパイプラインレジスタパイプラインレジスタ.webp)

![図 3-12: 基本的な FIR フィルタの式 タップの数や入力容量によって、多数の加算器のチェインを介する遅延は非常に大きくなること があります。遅延性能の問題を解決するには、タップごとに配置される追加の遅延要素でシスト リック形式を使用して、レイテンシの増加を代償に性能を向上させます。 図 3-13: シストリック FIR フィルタの等価回路 1−ck ][ nx ][ nyc1c2ck]1 n[ww2 n[]w k−1 n[]w k[ n] Arria 10 の可変精度 DSP ブロックは、次](https://thumb-ap.123doks.com/thumbv2/123deta/7027943.785549/21.918.126.842.506.667/フィルタチェインシストレイテンシシストリックフィルタブロック.webp)