Vivado Design Suite

ユーザー

ガ イ ド :

プ ログ ラ ムおよびデバ ッ グ

Notice of Disclaimer

The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products.To the maximum extent permitted by applicable law:(1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY,

NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications.You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent.Certain products are subject to the terms and conditions of the

Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms

contained in a license issued to you by Xilinx.Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical

Applications:http://www.xilinx.com/warranty.htm#critapps.

© Copyright 2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries.All other trademarks are the property of their respective owners.

本資料は英語版 (v2012.2) を翻訳し た も ので、 内容に相違が生じ る 場合には原文を優先し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。 日本語版は参考用 と し て ご使用の上、 最新情報につ き ま し ては、 必ず最新英語版を ご参照 く だ さ い。 こ の資料に関す る フ ィ ー ド バ ッ ク お よ び リ ン ク な ど の問題につ き ま し ては、jpn_trans_feedback@xilinx.com までお知 ら せ く だ さ い。 いただ き ま し た ご意見を参考に早急に対応 さ せていただ き ます。 なお、 こ の メ ール ア ド レ スへのお問い合わせは受け付け てお り ません。 あ ら か じ めご了承 く だ さ い。

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。 日付 バージ ョ ン 改訂内容 2012 年 7 月 25 日 1.0 初版改訂履歴 . . . 2

第 1 章 : 概要

は じ めに . . . 5第 2 章 : デバイ スのプ ログ ラ ム

概要 . . . 6 ビ ッ ト ス ト リ ームの生成 . . . 6 ビ ッ ト ス ト リ ーム フ ァ イ ルのフ ォーマ ッ ト 設定の変更 . . . 7 デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ーム設定の変更 . . . 8 FPGA デバ イ ス のプ ロ グ ラ ム . . . 8 iMPACT の起動. . . 8 Vivado ハー ド ウ ェ ア セ ッ シ ョ ン を使用し た FPGA デバ イ ス のプ ロ グ ラ ム . . . 9第 3 章 : デザイ ンのデバ ッ グ

概要 . . . 14 RTL レベル デザ イ ン シ ミ ュ レーシ ョ ン . . . 14 イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン シ ミ ュ レーシ ョ ン . . . 15 イ ン シ ス テ ム デバ ッ グ . . . 15第 4 章 : イ ン シス テム デバ ッ グ フ ロー

概要 . . . 16 イ ン シ ス テ ム デバ ッ グ用のデザ イ ンのプ ローブ . . . 16 ネ ッ ト リ ス ト 挿入デバ ッ グ プ ローブ フ ロー . . . 17 HDL イ ン ス タ ンシエーシ ョ ン プ ローブ フ ローの概要 . . . 25 HDL イ ン ス タ ンシエーシ ョ ン デバ ッ グ プ ローブ フ ロー . . . 26 デバ ッ グ コ ア を含むデザ イ ンの イ ンプ リ メ ンテーシ ョ ン . . . 30第 5 章 : ハー ド ウ ェ アでのデザイ ンのデバ ッ グ

概要 . . . 31ChipScope Pro Analyzer を使用 し たデザ イ ンのデバ ッ グ . . . 31

Vivado ロ ジ ッ ク 解析を使用し たデザ イ ンのデバ ッ グ . . . 32 ハー ド ウ ェ ア ターゲ ッ ト に接続し て FPGA デバ イ ス をプ ロ グ ラ ム . . . 32 計測のための ILA コ アの設定 . . . 33 ILA コ アの ト リ ガー条件の設定. . . 33 ILA コ アの ト リ ガー位置の設定. . . 33 ILA プ ローブ情報の記述. . . 34 ILA プ ローブ情報の読み出 し . . . 34 ILA プ ローブの表示. . . 35 ILA プ ローブの ト リ ガー比較値の設定. . . 35

ILA コ アの ト リ ガーの供給. . . 37 ILA コ アの ト リ ガーの停止. . . 37 ILA コ アの ス テー ト の表示. . . 38 ILA コ アか ら のデータ を波形ビ ューアーで表示. . . 38 ILA コ アでキ ャ プチ ャ さ れたデータ の保存および復元. . . 38 ラ ボ環境での Vivado ロ ジ ッ ク 解析の使用. . . 39

Vivado ロ ジ ッ ク 解析機能 と ChipScope Pro Analyzer の同時使用 . . . 40

ハー ド ウ ェ ア セ ッ シ ョ ンの Tcl オブジ ェ ク ト およびコ マン ド . . . 42 ハー ド ウ ェ ア セ ッ シ ョ ンの Tcl コ マン ド の使用 . . . 45

第 6 章 : 波形ウ ィ ン ド ウを使用 し た ILA プ ローブ デー タ の表示

概要 . . . 46 波形ウ ィ ン ド ウ の機能お よ び制限事項 . . . 46 波形 コ ン フ ィ ギ ュ レーシ ョ ンの信号お よ びバ ス . . . 47 波形 コ ン フ ィ ギ ュ レーシ ョ ンの ILA プ ローブ . . . 48 波形 コ ン フ ィ ギ ュ レーシ ョ ンのカ ス タ マ イ ズ . . . 49 オブジ ェ ク ト 名の変更 . . . 52 基数お よ びアナ ロ グ波形 . . . 54 ズーム機能 . . . 57付録 A : デバイ ス コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ーム設定

デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン設定の説明 . . . 58付録 B : その他の リ ソ ース

ザ イ リ ン ク ス リ ソ ース . . . 64 ソ リ ュ ーシ ョ ン セン ター . . . 64 参考資料 . . . 64概要

は じ めに

デザ イ ン を イ ン プ リ メ ン ト し た ら 、FPGA デバ イ ス を プ ロ グ ラ ム し 、 デザ イ ン を イ ン シ ス テ ムでデバ ッ グ し なが ら

ハー ド ウ ェ アでデザ イ ン を実行 し ます。FPGA デバ イ ス のプ ロ グ ラ ムおよび イ ン シ ス テ ム デバ ッ グの実行に必要な コ

マ ン ド はすべて、Vivado™統合設計環境 (IDE) の Flow Navigator の [Program and Debug] にあ り ます (図1-1 参照)。

X-Ref Target - Figure 1-1

第 2 章

デバイ スのプ ログ ラ ム

概要

ハー ド ウ ェ アのプ ロ グ ラ ムは、 次の 2 つの段階に分け る こ と がで き ます。 1. イ ンプ リ メ ン ト 済みデザ イ ンか ら ビ ッ ト ス ト リ ーム データ プ ロ グ ラ ム フ ァ イ ルを生成 2. ハー ド ウ ェ アに接続 し 、 プ ロ グ ラ ム フ ァ イ ルを ターゲ ッ ト FPGA デバ イ ス にダ ウ ン ロー ドビ ッ ト ス ト リ ームの生成

ビ ッ ト ス ト リ ーム デー タ フ ァ イ ルを生成する 前に、 ビ ッ ト ス ト リ ーム設定が正 し いか ど う かを確認する こ と が重要 です。 Vivado™ IDE では、 次の 2 つのビ ッ ト ス ト リ ーム設定があ り ます。 1. ビ ッ ト ス ト リ ーム フ ァ イ ルのフ ォーマ ッ ト 設定 2. デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン設定Flow Navigator の [Bitstream Settings] を ク リ ッ ク す る か、 [Flow] → [Bitstream Settings] を ク リ ッ ク す る と 、 [Project Settings] ダ イ ア ロ グ ボ ッ ク ス の [Bitstream] ページが開き ます (図2-1)。 ビ ッ ト ス ト リ ーム設定が正し い こ と を確認し た ら 、write_bistream Tcl コ マ ン ド ま たは Flow Navigator の [Generate Bitstream] を使用 し て ビ ッ ト ス ト リ ーム デー タ フ ァ イ ルを生成で き ます。

ビ ッ ト ス ト リ ーム フ ァ イルのフ ォ ーマ ッ ト 設定の

変更

デフ ォル ト では、write_bistream Tcl コ マン ド でバ イ ナ リ ビ ッ ト ス ト リ ーム フ ァ イ ル (.bit) が生成 さ れます。 生成 さ れ る フ ァ イ ルの フ ォーマ ッ ト を変更する には、 次のオプシ ョ ン を使用 し ます。 • -raw_bitfile : ロー ビ ッ ト フ ァ イ ル (.rbt) を生成し ます。 ロー ビ ッ ト フ ァ イ ルには、 バ イ ナ リ ビ ッ ト ス ト リ ー ム フ ァ イ ル と 同 じ情報が ASCII 形式で含まれます。 出力フ ァ イ ル名は filename.rbt と な り ます。 • -mask_file : マ ス ク フ ァ イ ル (.msk) を生成し ます。マ ス ク フ ァ イ ルには、 ビ ッ ト ス ト リ ーム フ ァ イ ルの コ ン フ ィ ギ ュ レーシ ョ ン デー タ が含まれる 場所を示すマ ス ク デー タ が含まれます。 こ のフ ァ イ ルは、 検証時にビ ッ ト ス ト リ ームの ど の ビ ッ ト を リ ー ド バ ッ ク データ と 比較するべ き かを判断する ために使用 し ます。 マ ス ク ビ ッ ト が 0 の場合はそのビ ッ ト はビ ッ ト ス ト リ ーム デー タ に対 し て検証 さ れ、マ ス ク ビ ッ ト が 1 の場合はそのビ ッ ト は検 証 さ れません。 出力フ ァ イ ル名は file.msk と な り ます。 • -no_binary_bitfile : バ イ ナ リ ビ ッ ト ス ト リ ーム フ ァ イ ル (.bit) を生成し ません。 こ のオプシ ョ ンは、 バ イ ナ リ ビ ッ ト ス ト リ ーム フ ァ イ ルを生成せずに、 ASCII 形式のビ ッ ト ス ト リ ーム フ ァ イ ルま たはマ ス ク フ ァ イ ルを生 成 し た り 、 ビ ッ ト ス ト リ ーム レ ポー ト を生成 し た り する場合に使用 し ます。X-Ref Target - Figure 2-1

デバイ ス コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ーム設定の変更

デバイ ス コ ン フ ィ ギュ レーシ ョ ン ビ ッ ト ス ト リ ーム

設定の変更

コ ン フ ィ ギ ュ レーシ ョ ン設定で最 も 頻繁に変更 さ れ る のは、デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン設定です。 こ れ ら の設 定はデバ イ ス モデルのプ ロ パテ ィ であ り 、 XDC フ ァ イ ルで set_property コ マン ド を使用 し て変更 し ます。 次の 例では、 ス タ ー ト ア ッ プ DONE サ イ ク ル プ ロ パテ ィ を変更し ています。set_property BITSTREAM.STARTUP.DONE_CYCLE 4 [current_design]

その他の例は、Vivado テンプレー ト に含まれてい ます。付録A 「デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト ス ト リ ー

ム設定」 に、 すべてのデバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン設定が説明 さ れてい ます。

FPGA デバイ スのプ ロ グ ラ ム

ビ ッ ト ス ト リ ーム データ プ ロ グ ラ ム フ ァ イ ルを生成し た ら 、 ターゲ ッ ト FPGA デバ イ ス にダ ウ ン ロー ド し ます。 こ

れには、2 つの方法があ り ます。

• Flow Navigator で [Launch iMPACT] を ク リ ッ ク する か、 [Flow] → [Launch iMPACT] を ク リ ッ ク し て、 iMPACT デ

バ イ ス プ ロ グ ラ ム ツールを起動し ます。 • ハー ド ウ ェ ア セ ッ シ ョ ン を開き、Vivado IDE に含まれてい る ネ イ テ ィ ブ イ ンシ ス テ ム デバ イ ス プ ロ グ ラ ミ ン グ 機能を使用 し ます。

iMPACT の起動

iMPACT ツールでは、 デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ン と フ ァ イ ルの生成を実行で き ます。 • デバ イ ス コ ン フ ィ ギ ュ レーシ ョ ンでは、 JTAG ダ ウ ン ロー ド ケーブル (ザ イ リ ン ク ス パ ラ レル ケーブル IV、 ザ イ リ ン ク ス プ ラ ッ ト フ ォーム ケーブル USB、 ザ イ リ ン ク ス プ ラ ッ ト フ ォーム ケーブル USB II、 ま たは Digilent JTAG ケーブル) を使用し て、 ザ イ リ ン ク ス FPGA および PROM を直接コ ン フ ィ ギ ュ レーシ ョ ンで き ます。 • バ ウ ン ダ リ ス キ ャ ン モー ド で実行する と 、 ザ イ リ ン ク ス FPGA、 CPLD、 PROM を コ ン フ ィ ギ ュ レーシ ョ ン ま たはプ ロ グ ラ ムで き ます。

• フ ァ イ ル生成では、System ACE™ CF、 PROM、 SVF、 STAPL、 および XSVF な どのプ ロ グ ラ ム フ ァ イ ルを作成

で き ます。

iMPACT では、 次 も 実行で き ます。

• デザ イ ンの コ ン フ ィ ギ ュ レーシ ョ ン データ の リ ー ド バ ッ ク および検証 • コ ン フ ィ ギ ュ レーシ ョ ン エ ラ ーのデバ ッ グ

• SVF および XSVF フ ァ イ ルの実行

iMPACT は、 [Generate Bitstream] コ マン ド が実行 さ れてい る ど の イ ンプ リ メ ン ト 済みデザ イ ンで も 、 Vivado IDE か ら 直接起動で き ます。iMPACT を起動する には、 Flow Navigator で [Launch iMPACT] を ク リ ッ ク し ます。

Vivado ツールか ら iMPACT を起動し た場合、 BIT ビ ッ ト ス ト リ ーム フ ァ イ ルが自動的に iMPACT に読み込まれます。 iMPACT の詳細は、 iMPACT ヘルプを参照し て く だ さ い。

Vivado ハー ド ウ ェ ア セ ッ シ ョ ン を使用 し た FPGA デ

バイ スのプ ロ グ ラ ム

Vivado IDE ツールには、 1 つ以上の FPGA デバ イ ス を含むハー ド ウ ェ アに接続 し、 それ ら の FPGA デバ イ ス をプ ロ グ ラ ム し 、 それ ら の FPGA デバ イ ス にア ク セ スする機能が含まれてい ます。 ハー ド ウ ェ アへの接続は、 Vivado IDE GUI ま たは Tcl コ マン ド で実行で き ます。 ど ち ら の場合 も 、 ハー ド ウ ェ アに接続し 、 ターゲ ッ ト FPGA デバ イ ス をプ ロ グ ラ ムする 手順は同 じ です。 1. ハー ド ウ ェ ア セ ッ シ ョ ン を開き ます。 2. ホ ス ト コ ン ピ ュ ー タ ー上で稼働中のハー ド ウ ェ ア サーバーで制御 さ れてい る ハー ド ウ ェ ア タ ーゲ ッ ト を開 き ます。 3. ビ ッ ト ス ト リ ーム データ プ ロ グ ラ ム フ ァ イ ルを適切な FPGA デバ イ ス に関連付け ます。 4. プ ロ グ ラ ム フ ァ イ ルをハー ド ウ ェ ア デバ イ ス にプ ロ グ ラ ム (ダ ウ ン ロー ド ) し ます。

ハー ド ウ ェ ア セ ッ シ ョ ン を開 く

デザ イ ン をハー ド ウ ェ アにプ ロ グ ラ ム し た り デバ ッ グす る には、 ま ずハー ド ウ ェ ア セ ッ シ ョ ン を開き ます。 ハー ド ウ ェ ア セ ッ シ ョ ン を開 く には、 次のいずれかを実行 し ます。• Flow Navigator で [Program and Debug] → [Open Hardware Session] を ク リ ッ ク し ます。 • [Flow] → [Open Hardware Session] を ク リ ッ ク し ます。

ハー ド ウ ェ ア タ ーゲ ッ ト 接続を開 く

次に、 ハー ド ウ ェ ア ターゲ ッ ト (1 つ以上の FPGA デバ イ ス で構成 さ れる JTAG チ ェーン を含むハー ド ウ ェ ア ボー ド

な ど) を開き、 ハー ド ウ ェ ア タ ーゲ ッ ト への接続を制御する ハー ド ウ ェ ア サーバー (CSE サーバー と も 呼ばれる ) に

接続 し ます。 こ れには、 次のいずれか を実行 し ます。

• [Hardware] ビ ューの [Open New Hardware Target] リ ン ク を ク リ ッ ク し、 ウ ィ ザー ド を使用 し てハー ド ウ ェ ア ター ゲ ッ ト への新 し い接続を開き ます。

• [Hardware] ビ ューの [Open Recent Hardware Target] リ ン ク を ク リ ッ ク し、 最近接続 し たハー ド ウ ェ ア ターゲ ッ ト への接続を開き ます。

Vivado ハー ド ウ ェ ア セ ッ シ ョ ン を使用 し た FPGA デバイ スのプ ログ ラ ム

新 し いハー ド ウ ェ ア タ ーゲ ッ ト を開 く

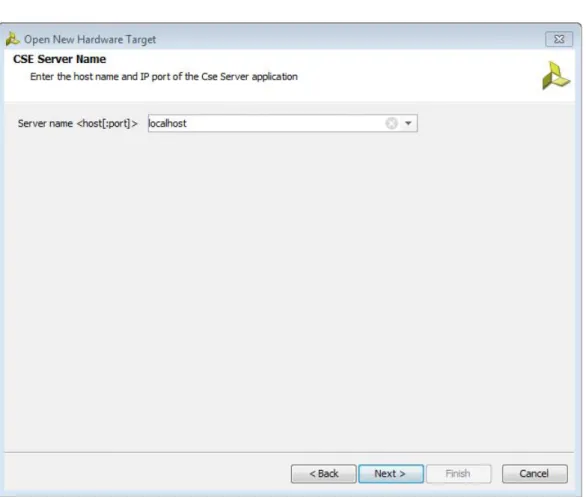

Open New Hardware Target ウ ィ ザー ド では、 ウ ィ ザー ド の指示に従いなが ら 、 ハー ド ウ ェ ア サーバー と ターゲ ッ ト を 接続で き ます。 次の手順に従い ます。

1. タ ーゲ ッ ト ボー ド が接続 さ れてい る マシ ン上のハー ド ウ ェ ア ターゲ ッ ト を制御する、 ホ ス ト 名 と CSE サーバー

(ハー ド ウ ェ ア サーバーま たは cse_server と も 呼ばれ る) のポー ト を指定 し ます (図2-2)。

注記 : ホ ス ト 名を [localhost] にする と 、 Vivado ツールを実行 し てい る マシ ンで cse_server プ ロ セ ス が自動的に開 始 し 、 ウ ィ ザー ド の こ の後のページで使用 さ れます。

X-Ref Target - Figure 2-2

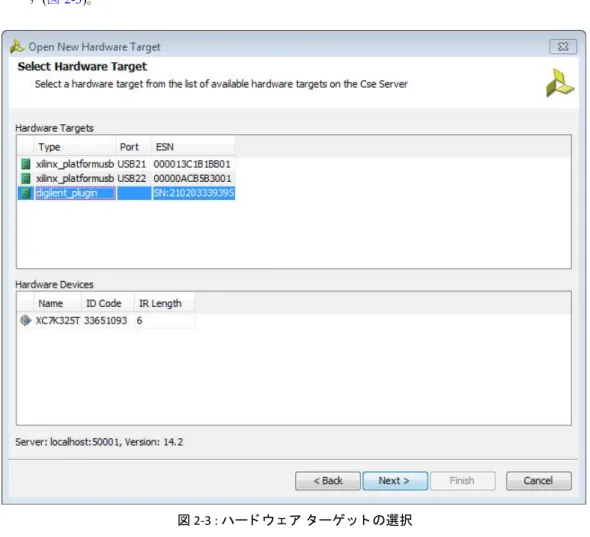

2. ハー ド ウ ェ ア サーバーで制御 さ れてい る ターゲ ッ ト の リ ス ト か ら 、 適切なハー ド ウ ェ ア ターゲ ッ ト を選択し ま す。 タ ーゲ ッ ト を選択す る と 、 そのハー ド ウ ェ ア タ ーゲ ッ ト で使用可能なハー ド ウ ェ ア デバ イ ス が表示 さ れま す (図2-3)。 3. TCK ク ロ ッ ク ピ ンの周波数な ど、 ハー ド ウ ェ ア ターゲ ッ ト のプ ロ パテ ィ を設定 し ます。 ハー ド ウ ェ ア ターゲ ッ ト に よ っ て、 設定可能なプ ロ パテ ィ は異な り ます。 プ ロ パテ ィ の詳細は、 各ハー ド ウ ェ ア ターゲ ッ ト の資料を参 照 し て く だ さ い。

最近開いたハー ド ウ ェ ア タ ーゲ ッ ト を開 く

Open New Hardware Target ウ ィ ザー ド は、 [Open Recent Hardware Target] リ ン ク を ク リ ッ ク し た場合に使用 さ れ る最近 接続 し たハー ド ウ ェ ア ターゲ ッ ト の リ ス ト も ア ッ プデー ト し ます。[Hardware] ビ ューの [Open Recent Hardware Target] リ ン ク を ク リ ッ ク する と 、 ウ ィ ザー ド を使用 し てハー ド ウ ェ ア ターゲ ッ ト に接続する 代わ り に、最近接続し たハー ド

ウ ェ ア ターゲ ッ ト への接続を再開で き ます。

X-Ref Target - Figure 2-3

Vivado ハー ド ウ ェ ア セ ッ シ ョ ン を使用 し た FPGA デバイ スのプ ログ ラ ム

Tcl コ マ ン ド を使用 し てハー ド ウ ェ ア タ ーゲ ッ ト を開 く

Tcl コ マン ド を使用し て、 ハー ド ウ ェ ア サーバー /ターゲ ッ ト に接続する こ と も 可能です。 た と えば、 localhost:50001 上の cse_server で制御 さ れる digilent_plugin ターゲ ッ ト (シ リ アル番号 210203339395) に接続する には、 次の Tcl コ マ ン ド を使用 し ます。

connect_hw_server -host localhost -port 50001

current_hw_target [get_hw_targets */digilent_plugin/SN:210203339395] open_hw_target ハー ド ウ ェ ア ターゲ ッ ト への接続を開 く と 、 [Hardware] ビ ューにハー ド ウ ェ ア サーバー、 ハー ド ウ ェ ア ターゲ ッ ト 、 お よ び タ ーゲ ッ ト のハー ド ウ ェ ア デバ イ ス が表示 さ れます (図2-4)。

プ ログ ラ ム フ ァ イルをハー ド ウ ェ ア デバイ スに関連付け

ハー ド ウ ェ ア タ ーゲ ッ ト に接続 し た ら 、 FPGA デバ イ ス をプ ロ グ ラ ムする前に、 ビ ッ ト ス ト リ ーム デー タ プ ロ グ ラ ム フ ァ イ ル を デ バ イ ス に 関連付 け る 必要 が あ り ま す。 [Hardware] ビ ュ ー で ハー ド ウ ェ ア デバ イ ス を 選択 し、 [Properties] ビ ューで [Programming File] プ ロ パテ ィ が適切な ビ ッ ト ス ト リ ーム デー タ フ ァ イ ル (.bit) に設定 さ れて い る こ と を確認 し ます。注記 : Vivado IDE では、 開いてい る ハー ド ウ ェ ア タ ーゲ ッ ト の最初のデバ イ ス の [Programming File] プ ロ パテ ィ 値 と

し て、 現在の イ ンプ リ メ ン ト 済みデザ イ ンの .bit フ ァ イ ルが自動的に使用 さ れます。

ま た、set_property Tcl コ マン ド を使用し て、 ハー ド ウ ェ ア デバ イ ス の PROGRAM.FILE プ ロパテ ィ を設定で き ます。 set_property PROGRAM.FILE {C:/design.bit} [lindex [get_hw_devices] 0]

X-Ref Target - Figure 2-4

ハー ド ウ ェ ア デバイ スのプ ログ ラム

プ ロ グ ラ ム フ ァ イ ル を ハー ド ウ ェ ア デバ イ ス に関連付け た ら 、 [Hardware] ビ ュ ーでデバ イ ス を 右 ク リ ッ ク し、 [Program Device] を ク リ ッ ク し て、 ハー ド ウ ェ ア デバ イ ス をプ ロ グ ラ ム し ます。 program_hw_device Tcl コ マン ド で も

同 じ 操作を実行で き ます。 た と えば、JTAG チ ェーンの最初のデバ イ ス を プ ロ グ ラ ムする には、 次の Tcl コ マン ド を

使用 し ます。

program_hw_devices [lindex [get_hw_devices] 0]

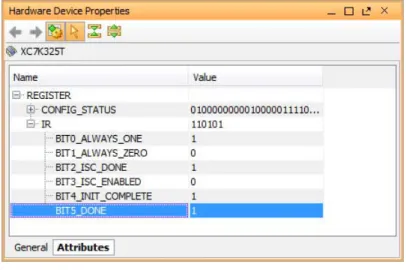

進捗状況 イ ン ジ ケ ー タ ーで プ ロ グ ラ ム が 100% 完了 し た こ と が示 さ れ た ら 、 プ ロ グ ラ ム が正常に完了 し た か を [Hardware Device Properties] ビ ュ ーの DONE の ス テータ ス で確認で き ます (図2-5)。

DONE の ス テータ ス は、 get_property Tcl コ マン ド で も 確認で き ます。 た と えば、 JTAG チ ェーンの最初のデバ イ ス で あ る Kintex™-7 デバ イ ス の DONE ス テータ ス を確認する には、 次の Tcl コ マン ド を使用 し ます。

get_property REGISTER.IR.BIT5_DONE [lindex [get_hw_devices] 0]

フ ラ ッ シ ュ デバ イ ス を使用 し た り 、 iMPACT ツールな どの外部デバ イ ス プ ロ グ ラ ム ツールを使用する な ど、 別の方

法でハー ド ウ ェ ア デバ イ ス をプ ロ グ ラ ム し た場合は、 ハー ド ウ ェ ア デバ イ ス を右 ク リ ッ ク し て [Refresh Device] を ク リ ッ ク す る か、refresh_hw_device Tcl コ マ ン ド を実行す る と 、 ハー ド ウ ェ ア デバ イ ス の ス テー タ ス を更新で き ます。 こ れに よ り 、DONE ス テータ ス だけでな く 、 デバ イ ス の さ ま ざ ま なプ ロ パテ ィ が更新 さ れます。

ハー ド ウ ェ ア タ ーゲ ッ ト を閉 じ る

ハー ド ウ ェ ア ターゲ ッ ト を閉じ るには、 [Hardware] ビ ューでハー ド ウ ェ ア ターゲ ッ ト を右ク リ ッ ク し、 [Close Target] を ク リ ッ ク し ます。Tcl コ マン ド で も同じ操作を実行で き ます。 た と えば、 localhost サーバー上の xilinx_platformusb/USB21 ターゲ ッ ト を閉じ る には、 次の Tcl コ マン ド を使用し ます。 close_hw_target {localhost/xilinx_platformusb/USB21}

ハー ド ウ ェ ア サーバーへの接続を閉 じ る

ハー ド ウ ェ ア サーバーへの接続を閉 じ る には、 [Hardware] ビ ュ ーでハー ド ウ ェ ア サーバーを右 ク リ ッ ク し、 [Close Server] を ク リ ッ ク し ます。 Tcl コ マン ド で も 同 じ 操作を実行で き ます。 た と えば、 localhost サーバーへの接続を閉じ る には、 次の Tcl コ マン ド を使用し ます。 disconnect_hw_server localhostX-Ref Target - Figure 2-5

第 3 章

デザイ ンのデバ ッ グ

概要

FPGA デザ イ ンのデバ ッ グは複数の段階を含む反復作業です。 複雑な問題を処理する 場合 と 同様に、 FPGA デザ イ ン のデバ ッ グ プ ロ セ ス も 、一度にデザ イ ン全体を処理する のではな く 、細分化し てセ ク シ ョ ン ご と に集中し て作業する のがベス ト です。1 回に 1 モジ ュールを追加 し なが ら デザ イ ン フ ローを反復 し、 デザ イ ン全体の中でそれを正し く 機 能 さ せる よ う にする のが、 実績のあ る デザ イ ンお よ びデバ ッ グ手法の 1 つです。 こ の手法は、 デザ イ ン フ ローの次の 段階で使用で き ます。 • RTL レベル デザ イ ン シ ミ ュ レーシ ョ ン • イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン シ ミ ュ レーシ ョ ン • イ ン シ ス テ ム デバ ッ グRTL レ ベル デザイ ン シ ミ ュ レ ーシ ョ ン

シ ミ ュ レ ーシ ョ ン検証プ ロ セ ス中にデザ イ ン の機能をデバ ッ グで き ま す。 ザ イ リ ン ク ス の Vivado™ IDE では、 フル デザ イ ン シ ミ ュ レーシ ョ ン機能が提供 さ れてい ます。 デザ イ ンの RTL シ ミ ュ レーシ ョ ン を実行する には、 Vivado デ ザ イ ン シ ミ ュ レータ を使用で き ます。 RTL レベル シ ミ ュ レーシ ョ ン環境でデザ イ ン デバ ッ グ を実行する と 、 デザ イ ン全体を完全に表示で き 、 デザ イ ン/デバ ッ グ サ イ ク ルをすばや く 反復実行で き る な どの利点があ り ますが、 大型デ ザ イ ン を妥当な時間内にシ ミ ュ レーシ ョ ン し た り 、 実際のシ ス テ ム環境を正確にシ ミ ュ レーシ ョ ンす る のが困難であ る な ど の制限があ り ます。Vivado シ ミ ュ レー タ の使用については、 『Vivado Design Suite ユーザー ガ イ ド : ロ ジ ッ ク シ ミ ュ レーシ ョ ン』 (UG937) [参照 1] を参照し て く だ さ い。イ ン プ リ メ ン テーシ ョ ン後のデザイ ン シ ミ ュ レー

シ ョ ン

Vivado シ ミ ュ レータ は、 イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン シ ミ ュ レーシ ョ ンに も 使用で き ます。 Vivado シ ミ ュ レー タ を使用 し て イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン をデバ ッ グする と 、 デザ イ ンの タ イ ミ ン グ精度の高いモデル を使用で き る な ど の利点があ り ますが、 前のセ ク シ ョ ンで述べた よ う に、 ラ ン タ イ ムが長い こ と や、 シ ス テ ム モデル での正確 さ な ど の制限があ り ます。イ ン シ ス テム デバ ッ グ

Vivado IDE には、 イ ンプ リ メ ン テーシ ョ ン後の FPGA デザ イ ン を イ ン シ ス テ ムでデバ ッ グで き る ロ ジ ッ ク 解析機能 も あ り ます。 イ ン シ ス テ ムでのデザ イ ンのデバ ッ グには、 イ ンプ リ メ ン テーシ ョ ン後のデザ イ ン を、 実際のシ ス テ ム環 境で、 シ ス テ ム ス ピー ド で、 タ イ ミ ン グ精度の高いデバ ッ グ を実行で き る と い う 利点があ り ますが、 シ ミ ュ レーシ ョ ン モデルを使用 し た場合に比べてデバ ッ グ信号を確認 し づ ら い、 デザ イ ンのサ イ ズや複雑 さ に よ っ てはデザ イ ン/イ ンプ リ メ ン テーシ ョ ン/デバ ッ グの反復実行の ラ ン タ イ ムが長 く な る可能性があ る な どの制限があ り ます。 Vivado ツールでは複数のデバ ッ グ方法が提供 さ れてい る ので、 ニーズに応じ た方法でデザ イ ン をデバ ッ グで き ます。 Vivado IDE の イ ンシ ス テ ム ロ ジ ッ ク デバ ッ グ機能については、第4 章「イ ン シ ス テ ム デバ ッ グ フ ロー」で説明 し ます。

第 4 章

イ ン シ ス テム デバ ッ グ フ ロー

概要

Vivado ツールには、 実際のハー ド エア デバ イ ス上でデザ イ ンの イ ン シ ス テ ム デバ ッ グ を実行する機能が多数含まれ てい ます。 イ ン シ ス テ ム デバ ッ グ フ ローには、 次の 3 つの段階があ り ます。 1. プ ロ ーブ : デザ イ ンでプ ローブする信号を特定し 、 プ ローブ方法を指定し ます。 2. イ ンプ リ メ ンテーシ ョ ン : プローブする ネ ッ ト に追加さ れたデバ ッ グ IP を含むデザイ ンを イ ンプ リ メ ン ト し ます。 3. 解析 : デザ イ ンに含まれ るデバ ッ グ IP にア ク セ ス し 、 機能的な問題をデバ ッ グおよび検証し ます。 こ の イ ン シ ス テ ム デバ ッ グ フ ローは、前のセ ク シ ョ ンで説明 し た反復デザ イ ン/デバ ッ グ フ ローを使用する こ と を意 図 し てい ます。 イ ン シ ス テ ム デバ ッ グ フ ローを使用する場合は、 デザ イ ン サ イ ク ルので き る だけ早い段階で、 デザ イ ンの一部がハー ド ウ ェ アで機能す る よ う にす る こ と をお勧め し ます。 こ の章では、 イ ン シ ス テ ム デバ ッ グ フ ロー の 3 つの段階を説明 し、 Vivado™ ロ ジ ッ ク デバ ッ グ機能を使用 し てデザ イ ンがハー ド ウ ェ ア上で機能す る よ う にす る 方法を示 し ます。イ ン シ ス テム デバ ッ グ用のデザイ ンのプ ローブ

イ ン シ ス テ ム デバ ッ グ フ ローのプ ローブ段階には、 次の 2 つの段階があ り ます。 1. プ ロ ーブする 信号ま たはネ ッ ト を特定 し ます。 2. デザ イ ンにデバ ッ グ コ ア を追加する方法を決め ます。 多 く の場合、 プ ロ ーブす る 信号お よ びそのプ ロ ーブ方法は、 ほかの信号のプ ロ ーブに影響 し ます。 ま ず、 デザ イ ン ソ ース コ ー ド にデバ ッ グ IP コ ンポーネ ン ト イ ン ス タ ン ス を手動で追加する か (HDL イ ン ス タ ン シエーシ ョ ン プ ロー ブ フ ロー )、 合成済みネ ッ ト リ ス ト に Vivado ツールで自動的にデバ ッ グ コ アが追加 さ れる よ う にする か (ネ ッ ト リ ス ト 挿入プ ロ ーブ フ ロー ) を決定する と 有益です。表4-1 に、 異な るデバ ッ グ方法の利点 と 欠点を示 し ます。 表 4-1 : デバ ッ グ ス ト ラ テ ジ デバ ッ グ目標 推奨デバ ッ グ プ ログ ラ ム フ ロー HDL ソ ー ス コ ー ド でデバ ッ グ信号を 特定 し 、 フ ロ ーの後の方でデバ ッ グ を イ ネーブル/デ ィ ス エーブルにで き る よ う にす る • mark_debug プ ロ パテ ィ を使用し て、 HDL でデバ ッ グ用の信号に タ グ を 付け る • Set up Debug ウ ィ ザー ド を使用し て、ネ ッ ト リ ス ト 挿入プ ローブ フ ロー を実行する HDL ソ ース コ ー ド を変更せずに、 合 成 済み デ ザ イ ン ネ ッ ト リ ス ト で デ バ ッ グ ネ ッ ト を特定する • 合成済みデザイ ン ネ ッ ト リ ス ト でネ ッ ト を右ク リ ッ ク し て [Mark Debug] を ク リ ッ ク し 、 デバ ッ グする ネ ッ ト を選択する • Set up Debug ウ ィ ザー ド を使用し て、ネ ッ ト リ ス ト 挿入プ ローブ フ ロー を実行するネ ッ ト リ ス ト 挿入デバ ッ グ プ ローブ フ ロー

Vivado ツールでデバ ッ グ コ ア を挿入する方法は、 さ ま ざ ま なニーズに対応で き る よ う 複数あ り ます。

• シ ンプルな ウ ィ ザー ド を使用 し 、 デバ ッ グする ネ ッ ト に基づいて、ILA (Integrated Logic Analyzer) v2.0 コ ア を自 動的に生成お よ び設定 し ます。 こ れが一番簡単な方法です。

• [Debug] ビ ューを使用 し て、 個々の コ ア、 ポー ト 、 およびパ ラ メ ーターを設定 し ます。 [Debug] ビ ューを開 く に

は、 レ イ ア ウ ト セ レ ク ターで [Debug] を選択、 [Layers] → [Debug] を ク リ ッ ク 、 ま たは [Windows] → [Debug] を ク リ ッ ク し ます。

• Tcl デバ ッ グ コ マン ド を手動で入力する か、 ス ク リ プ ト を作成し ます。

こ れ ら の方法を組み合わせて利用 し 、 デバ ッ グ コ ア を挿入およびカ ス タ マ イ ズする こ と も で き ます。

デバ ッ グする HDL 信号のマー ク

合成の前に HDL ソ ース レベルでデバ ッ グする 信号を特定す る には、 mark_debug 制約を使用 し ます。 HDL でデバ ッ

グ用にマー ク さ れた信号に対応する ネ ッ ト が、[Debug] ビ ューの [Unassigned Debug Nets] の下に表示 さ れます。

デバ ッ グ用にネ ッ ト を マー ク する 方法は、 プ ロ ジ ェ ク ト が RTL ソ ース ベース であ る か合成済みネ ッ ト リ ス ト ベース

であ る かに よ っ て異な り ます。RTL ネ ッ ト リ ス ト ベース のプ ロ ジ ェ ク ト の場合は、 次の方法を使用し ます。

• Vivado 合成を使用する場合、 VHDL および Verilog ソ ース フ ァ イ ルで mark_debug 制約を使用し てデバ ッ グ用の

ネ ッ ト を マー ク で き ます。mark_debug 制約に有効な値は、 TRUE ま たは FALSE です。 Vivado 合成では、 こ の制

約の値を SOFT に設定する こ と はで き ません。

• XST (Xilinx Synthesis Technology) を使用する場合、 VHDL および Verilog ソ ース フ ァ イ ルで mark_debug 制約を使

用 し てデバ ッ グ用のネ ッ ト を マー ク で き ます。有効な値は TRUE ま たは FALSE だけでな く 、SOFT に設定し て指

定ネ ッ ト を最適化で き ます。

合成済みネ ッ ト リ ス ト ベース のプ ロ ジ ェ ク ト の場合は、 次の方法を使用 し ます。

• Synopsis® 社の Synplify® 合成ツールを使用する 場合、 VHDL ま たは Verilog で mark_debug および syn_keep 制約 を使用す る か、SDC (Synopsys Design Constraints) フ ァ イ ルで mark_debug 制約を使用 し て、 デバ ッ グ用にネ ッ ト

を マー ク で き ます。Synplify では SOFT 値はサポー ト さ れません。 こ れは、 こ の動作が syn_keep 制約で制御 さ れ

る ためです。

• Mentor Graphics® 社の Precision® 合成ツールを使用する場合、 VHDL ま たは Verilog で mark_debug 制約を使用し てデバ ッ グ用にネ ッ ト を マー ク で き ます。

次のセ ク シ ョ ンに、Vivado 合成、 XST、 Synplify、 および Precision ソ ース フ ァ イ ルの構文例を示し ます。 Tcl コ マ ン ド を 使用 し て デバ ッ グ プ ロ ーブ フ ローを自動化する • set_property Tcl コ マン ド を使用し 、デバ ッ グする ネ ッ ト に mark_debug プ ロ パテ ィ を設定する • ネ ッ ト リ ス ト 挿入プ ローブ フ ロー用の Tcl コ マン ド を使用 し、デバ ッ グ コ ア を作成 し てデバ ッ グ ネ ッ ト に接続する HDL ソ ース で ILA デバ ッ グ コ ア イ ン ス タ ン ス に信号を接続す る • デバ ッ グする HDL 信号を特定する • HDL イ ン ス タ ン シエーシ ョ ン プ ローブ フ ローを使用し 、ILA (Integrated Logic Analyzer) コ ア を生成 し て イ ン ス タ ン シ エー ト し 、 デザ イ ン のデ バ ッ グ信号に接続する 表 4-1 : デバ ッ グ ス ト ラ テ ジ (続き) デバ ッ グ目標 推奨デバ ッ グ プ ログ ラ ム フ ロー

ネ ッ ト リ ス ト 挿入デバ ッ グ プ ローブ フ ロー

Vivado 合成での mark_debug の構文例

次に、Vivado 合成を使用する場合の VHDL および Verilog の構文例を示し ます。

• VHDL の構文例

attribute mark_debug : string;

attribute mark_debug of char_fifo_dout: signal is "true";

• Verilog の構文例

(* mark_debug = "true" *) wire [7:0] char_fifo_dout;

XST での mark_debug の構文例

次に、XST を使用する 場合の VHDL および Verilog の構文例を示 し ます。

• VHDL の構文例

attribute mark_debug : string;

attribute mark_debug of char_fifo_dout: signal is "true";

• Verilog の構文例

(* mark_debug = "true" *) wire [7:0] char_fifo_dout;

Synplify での mark_debug の構文例

次に、Synplify を使用する場合の VHDL、 Verilog、 SDC の構文例を示し ます。

• VHDL の構文例

attribute syn_keep : boolean; attribute mark_debug : string;

attribute syn_keep of char_fifo_dout: signal is true; attribute mark_debug of char_fifo_dout: signal is "true";

• Verilog の構文例

(* syn_keep = "true", mark_debug = "true" *) wire [7:0] char_fifo_dout;

• SDC の構文例

define_attribute {n:char_fifo_din[*]} {mark_debug} {"true"}

重要: SDC ソースのネ ッ ト 名には、 接頭辞 と し て n: を付け る必要があ り ます。

注記 : SDC (Synopsys Design Constraints) は、 特に タ イ ミ ン グ解析において設計の要件を ツールに渡すための業界標準

です。SDC 仕様の リ フ ァ レ ン ス コ ピーは、 次の Synopsys 社のサ イ ト か ら 登録をする と 入手で き ます。

Precision での mark_debug の構文例

次に、Precision を使用する場合の VHDL、 Verilog、 XCF の構文例を示し ます。

• VHDL の構文例

attribute mark_debug : string;

attribute mark_debug of char_fifo_dout: signal is "true";

• Verilog の構文例

(* mark_debug = "true" *) wire [7:0] char_fifo_dout;

デザイ ンの合成

次に、Vivado IDE で [Run Synthesis] を ク リ ッ ク する か、 次の Tcl コ マン ド を使用し て、 デバ ッ グ コ ア を含むデザ イ ン を合成 し ます。

launch_runs synth_1 wait_on_run synth_1

synth_design Tcl コ マン ド を使用し てデザ イ ン を合成する こ と も で き ます。デザ イ ンの さ ま ざ ま な合成方法は、『Vivado Design Suite ユーザー ガ イ ド : 合成』 (UG901) [参照 2] を参照 し て く だ さ い。

合成済みデザイ ン でデバ ッ グ用のネ ッ ト を マー ク

Flow Navigator で [Open Synthesized Design] を ク リ ッ ク し て合成済みデザ イ ン を開き、 [Debug] レ イ ア ウ ト を選択し て [Debug] ビ ューを表示し ます。 デバ ッ グ用にマー ク し た HDL 信号に対応する ネ ッ ト が、 [Debug] ビ ューの [Unassigned Debug Nets] フ ォ ルダーの下に表示 さ れます (図4-1)。

合成済みデザ イ ン ネ ッ ト リ ス ト でデバ ッ グする ネ ッ ト を追加でマー ク する には、 次のいずれかの方法を使用 し ます。

• [Netlist]、 [Schematic] な どの任意のビ ューでネ ッ ト を右 ク リ ッ ク し 、 [Mark Debug] を ク リ ッ ク し ます。

• 任意の ビ ュ ーでネ ッ ト を選択 し 、[Debug] ビ ューの [Unassigned Debug Nets] フ ォルダーに ド ラ ッ グ ア ン ド ド ロ ッ プ し ます。

• Set up Debug ウ ィ ザー ド でネ ッ ト を選択し ます。 詳細は、「Set Up Debug ウ ィ ザー ド を使用し たデバ ッ グ コ アの

挿入」 を参照 し て く だ さ い。

X-Ref Target - Figure 4-1

ネ ッ ト リ ス ト 挿入デバ ッ グ プ ローブ フ ロー

Set Up Debug ウ ィ ザー ド を使用 し たデバ ッ グ コ アの挿入

デバ ッ グ用にネ ッ ト を マー ク し た ら 、 それ ら のネ ッ ト をデバ ッ グ コ アに割 り 当て ます。 Vivado IDE の Set up Debug

ウ ィ ザー ド を使用する と 、 デバ ッ グ コ ア を自動作成し 、 デバ ッ グ ネ ッ ト を コ アの入力に割 り 当て る こ と がで き ます。

Set Up Debug ウ ィ ザー ド を使用し てデバ ッ グ コ ア を挿入する には、 次の手順に従い ます。

1. [Debug] ビ ュ ーの [Unassigned Debug Nets] フ ォ ルダーを使用する か、 ネ ッ ト を直接 ク リ ッ ク し て、 デバ ッ グする ネ ッ ト を選択 し ます (オプシ ョ ン)。

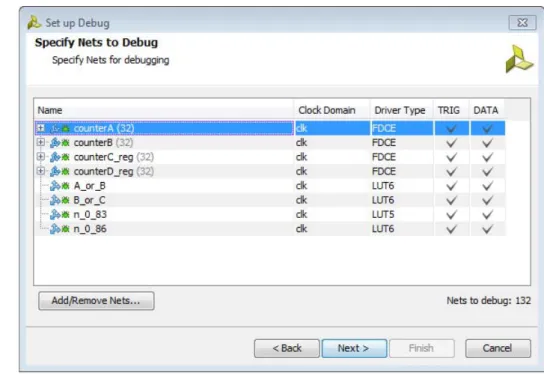

2. Vivado IDE メ イ ン メ ニ ューか ら [Tools] → [Set up Debug] を ク リ ッ ク し ます。 3. [Next] を ク リ ッ ク し ます。 [Specify Nets to Debug] ページが開き ます (図4-2)。

4. [Add/Remove Nets] を ク リ ッ ク し 、 ネ ッ ト を追加する か、 既存のネ ッ ト を削除し ます。

5. デバ ッ グ ネ ッ ト を右 ク リ ッ ク し て [Select Clock Domain] を ク リ ッ ク し、 ネ ッ ト の値をサンプ リ ン グする ク ロ ッ ク ド メ イ ン を変更 し ます。

注記 : Set up Debug ウ ィ ザー ド では、 同期エ レ メ ン ト のパス を検索する こ と に よ り 、 デバ ッ グ ネ ッ ト に適切な ク ロ ッ

ク ド メ イ ンが自動的に選択 さ れます。 自動的に選択 さ れた ク ロ ッ ク ド メ イ ン を変更する 必要があ る 場合に、 [Select

Clock Domain] ダ イ ア ロ グ ボ ッ ク ス を使用 し ます。 ただ し、 表に示 さ れ る 各 ク ロ ッ ク ド メ イ ンに対 し て個別の ILA v2.0 コ ア イ ン ス タ ン ス が作成 さ れる ので、 注意が必要です。

6. デバ ッ グ ネ ッ ト の選択が完了 し た ら 、 [Next] を ク リ ッ ク し ます。

注記 : Set up Debug ウ ィ ザー ド は、 ク ロ ッ ク ド メ イ ンにつき 1 つの ILA コ ア を挿入 し ます。 デバ ッ グ用に選択 さ れた ネ ッ ト は、 挿入 さ れた ILA v2.0 コ アのプ ローブ ポー ト に自動的に割 り 当て ら れます。 ウ ィ ザー ド の最終ページは コ

ア生成のサマ リ ページで、 検出 さ れた ク ロ ッ ク 数、 生成および削除 さ れる ILA コ アの数が示 さ れます。

7. 内容を確認 し た ら [Finish] を ク リ ッ ク し 、 合成済みデザ イ ン ネ ッ ト リ ス ト に ILA v2.0 コ ア を挿入お よ び接続 し ます。

X-Ref Target - Figure 4-2

[Debug] ビ ュ ーを使用 し たデバ ッ グ コ アの追加 と カ ス タ マ イ ズ

[Debug] ビ ュ ーでは、 Set up Debug ウ ィ ザー ド にない ILA v2.0 コ ア挿入に関する 詳細な設定を実行で き ます。 コ アの

生成お よ び削除、 デバ ッ グ ネ ッ ト の接続、 コ ア パ ラ メ ーターの設定な ど を実行で き ます。 [Debug] ビ ューには、 次の も のが表示 さ れます。 • debug_core_hub コ アに接続 さ れてい るデバ ッ グ コ アの リ ス ト • 割 り 当て ら れていないネ ッ ト の リ ス ト デバ ッ グ コ アおよびポー ト は、 ポ ッ プア ッ プ メ ニ ューま たはビ ューの上部にあ る ツールバーか ら 制御で き ます。

デバ ッ グ コ アの生成および削除

[Debug] ビ ューでデバ ッ グ コ ア を生成する には、 ツールバーの [Create Debug Core] を ク リ ッ ク し ます。 [Create Debug Core] ダ イ ア ロ グ ボ ッ ク ス (図4-3) を使用する と 、 親イ ン ス タ ン スおよびデバ ッ グ コ ア名を変更し た り 、 コ アのパ ラ メ ー タ ーを設定で き ます。 既存のデバ ッ グ コ ア を削除す る には、 [Debug] ビ ューで コ ア を右 ク リ ッ ク し、 [Delete] を ク リ ッ ク し ます。

X-Ref Target - Figure 4-3

ネ ッ ト リ ス ト 挿入デバ ッ グ プ ローブ フ ロー

デバ ッ グ コ ア ポー ト の追加、 削除、 および カ ス タ マ イズ

デバ ッ グ コ アの追加および削除だけでな く 、 各デバ ッ グ コ アのポー ト を追加、 削除、 お よびカ ス タ マ イ ズで き ます。

デバ ッ グ ポー ト を追加する には、 次の手順に従い ます。

1. [Debug] ビ ューでデバ ッ グ コ ア を選択し ます。

2. ツールバーの [Create Debug Port] を ク リ ッ ク し ます。 [Create Debug Port] ダ イ ア ロ グ ボ ッ ク ス が表示 さ れます (図4-4)。 3. ポー ト 幅を指定 し ます。 4. [OK] を ク リ ッ ク し ます。 5. デバ ッ グ ポー ト を削除する には、 [Debug] ビ ュ ーでポー ト を右 ク リ ッ ク し 、 [Delete] を ク リ ッ ク し ます。

デバ ッ グ コ アへのネ ッ ト の接続および接続解除

ネ ッ ト お よ びバ ス (バ ス ネ ッ ト ) を [Schematic] ま たは [Netlist] ビ ュ ーか ら デバ ッ グ コ アのポー ト に ド ラ ッ グ ア ン ド ド ロ ッ プで き ます。 ネ ッ ト 選択内容に応 じ てポー ト が自動的に拡張 さ れます。 ま た、 ネ ッ ト ま たはバ ス を右 ク リ ッ ク し 、[Assign to Debug Port] を ク リ ッ ク し て も 、 ネ ッ ト ま たはバス をデバ ッ グ ポー ト に割 り 当て る こ と がで き ます。 重要: 複数のネ ッ ト ま たはバス を、 ILA v2.0 コ アの同じ プ ローブ ポー ト に割 り 当てないで く だ さ い。 Vivado ロ ジ ッ ク解析機能では、 こ の よ う なプ ロ ーブ ポー ト の処理に制限があ り ます。 各ネ ッ ト ま たはバス を 1 つのプ ローブ ポー ト

に割 り 当てて く だ さ い。

デバ ッ グ コ ア の ポ ー ト か ら ネ ッ ト の 接続 を 解除す る に は、 ポ ー ト に 接続 さ れ て い る ネ ッ ト を 右 ク リ ッ ク し 、 [Disconnect Net] を ク リ ッ ク し ます。

X-Ref Target - Figure 4-4

デバ ッ グ コ アのプ ロパテ ィ の変更

各デバ ッ グ コ アには、 コ アの動作を カ ス タ マ イ ズする パ ラ メ ーターがあ り ます。 debug_core_hub デバ ッ グ コ アの プ ロ パテ ィ の変更については、29 ページの 「デバ ッ グ コ ア ハブの BSCAN ユーザー ス キ ャ ン チ ェーンの変更」 を参 照 し て く だ さ い。 ILA v2.0 デバ ッ グ コ アのプ ロ パテ ィ も 変更で き ます。 た と えば、 ILA v2.0 デバ ッ グ コ アでキ ャ プチ ャ さ れ る サンプ ルの数を変更する には、 次の手順に従い ます (図4-5)。1. [Debug ] ビ ュ ーで ILA コ ア (u_ila_0 な ど) を選択し ます。

2. [Instance Properties] ビ ューで [Debug Core Options] タ ブを ク リ ッ ク し ます。

3. [C_DATA_DEPTH] の ド ロ ッ プダ ウ ン リ ス ト か ら 、 キ ャ プチ ャする サンプル数を選択し ます。

X-Ref Target - Figure 4-5

ネ ッ ト リ ス ト 挿入デバ ッ グ プ ローブ フ ロー

Tcl コ マ ン ド を使用 し たデバ ッ グ コ ア挿入

Set up Debug ウ ィ ザー ド の使用に加え、 Tcl コ マン ド を使用 し てデバ ッ グ コ ア を作成、 接続、 お よび合成済みデザ イ ン ネ ッ ト リ ス ト に挿入で き ます。

1. ILA v2.0 コ アのブ ラ ッ ク ボ ッ ク ス を作成し ます。

create_debug_core u_ila_0 labtools_ilalib_v2

2. ILA v2.0 コ アのデータ深 さ プ ロ パテ ィ を設定し ます。

set_property C_DATA_DEPTH 1024 [get_debug_cores u_ila_0]

3. ILA v2.0 コ アの CLK ポー ト の幅を 1 に設定し 、 適切な ク ロ ッ ク ネ ッ ト に接続し ます。 set_property port_width 1 [get_debug_ports u_ila_0/CLK]

connect_debug_port u_ila_0/CLK [get_nets [list clk ]]

注記 : ILA v2.0 コ アの CLK ポー ト は、 create_debug_core コ マン ド で自動的に作成 さ れる ので、 改めて作成 する 必要はあ り ません。

4. PROBE0 ポー ト の幅を、 そのポー ト に接続する ネ ッ ト の数に設定 し ます。

set_property port_width 1 [get_debug_ports u_ila_0/PROBE0]

注記 : ILA v2.0 コ アの最初のプ ローブ ポー ト (PROBE0) は、 create_debug_core コ マン ド で自動的に作成 さ れる の で、 改めて作成する 必要はあ り ません。

5. PROBE0 ポー ト を、 そのポー ト に接続する ネ ッ ト に接続し ます。

connect_debug_port u_ila_0/PROBE0 [get_nets [list A_or_B]]

6. (オプシ ョ ン) 必要なだけプ ローブ ポー ト を作成し 、 幅を設定し て、 デバ ッ グする ネ ッ ト に接続し ます。

create_debug_port u_ila_0 PROBE

set_property port_width 2 [get_debug_ports u_ila_0/PROBE1]

connect_debug_port u_ila_0/PROBE1 [get_nets [list {A[0]} {A[1]}]]to debug

7. (オプシ ョ ン) デバ ッ グ コ ア を合成し 、 合成済みデザ イ ンのほかの部分 と 共にフ ロ アプ ラ ンで き る よ う に し ます。

implement_debug_cores [get_debug_cores]

こ れ ら の コ マ ン ド お よ びその他の関連コ マ ン ド の詳細は、Tcl コ ン ソ ールで 「help -category ChipScope」 と 入 力 し て く だ さ い。

デザイ ンのイ ン プ リ メ ン テーシ ョ ン

デバ ッ グ コ ア を挿入、 接続、 カ ス タ マ イ ズ し た ら 、 デザ イ ン を イ ンプ リ メ ン ト し ます。 詳細は、「デバ ッ グ コ ア を含 むデザ イ ンの イ ンプ リ メ ン テーシ ョ ン」 を参照 し て く だ さ い。

HDL イ ン ス タ ン シ エーシ ョ ン プ ローブ フ ローの概要

HDL イ ン ス タ ン シエーシ ョ ン プ ローブ フ ローでは、 HDL デザ イ ン ソ ース で直接デバ ッ グ コ ア コ ンポーネン ト を カ ス タ マ イ ズ、 イ ン ス タ ン シエー ト 、 お よ び接続 し ます。表4-2 に、 こ のフ ローでサポー ト さ れるデバ ッ グ コ ア を示し ます。

ICON、VIO、および ILA v1.x コ アは、 こ れ ら の コ ア を含むレ ガシ デザ イ ン と の互換性のため、Vivado ツールでサポー ト さ れてい ます。ILA v2.0 コ アには、 ILA v1.x コ ア と 比較 し て次の よ う な利点があ り ます。 • Vivado ロ ジ ッ ク 解析で機能 し ます。 詳細は、31 ページの 「ハー ド ウ ェ アでのデザ イ ンのデバ ッ グ」 を参照 し て く だ さ い。 • ICON コ アの挿入および接続は必要あ り ません。 重要: ILA v2.0 の HDL イ ン ス タ ンシエーシ ョ ン フ ローでは、合成済みデザ イ ン ネ ッ ト リ ス ト にブ ラ ッ ク ボ ッ ク ス イ ン ス タ ン ス が作成 さ れ ます。 こ のブ ラ ッ ク ボ ッ ク スは、 デザ イ ン イ ンプ リ メ ン テーシ ョ ン プ ロ セ ス の opt_design ま たは place_design の段階で実際の ILA v2.0 コ アに置き換え ら れます。 表 4-2 : HDL イ ン ス タ ン シエーシ ョ ン プ ローブ フ ローで使用可能なデバ ッ グ コ ア デバ ッ グ コ ア バージ ョ ン 説明 解析ツール

ICON (Integrated Controller) v1.06a ILA 1.05a お よ び VIO 1.05a コ ア を JTAG チ ェ ー ン に 接続す る た め の デ バ ッ グ コ ア ハブ

ChipScope Pro Analyzer

VIO (Virtual Input/Output) v1.05a デザ イ ン の信号 を JTAG チ ェ ー ン ス

キ ャ ン レ ー ト で監視 ま たは制御す る

た め に使用す る デバ ッ グ コ ア (ICON

コ アへの接続が必要)

ChipScope Pro Analyzer

ILA (Integrated Logic Analyzer) v1.05a ハー ド ウ ェ ア イ ベン ト を ト リ ガー し、 デー タ を シ ス テ ム速度でキ ャ プチ ャ す

る ために使用す る デバ ッ グ コ ア (ICON コ アへの接続が必要)

ChipScope Pro Analyzer

ILA (Integrated Logic Analyzer) v2.0 ハー ド ウ ェ ア イ ベン ト を ト リ ガー し、 デー タ を シ ス テ ム速度でキ ャ プチ ャ す

る ために使用す る デバ ッ グ コ ア

HDL イ ン ス タ ン シ エーシ ョ ン デバ ッ グ プ ローブ フ ロー

HDL イ ン ス タ ン シ エーシ ョ ン デバ ッ グ プ ローブ

フ ロー

HDL イ ン ス タ ン シエーシ ョ ン フ ローの手順は、 次の と お り です。 1. プ ローブする信号用に、 適切な数のプ ローブ ポー ト を含む ILA v2.0 デバ ッ グ コ アを カ ス タ マ イ ズ し て生成し ます。 2. デバ ッ グ コ ア を含むデザ イ ン を合成 し ます。 3. (オプシ ョ ン) デバ ッ グ コ アのプ ロ パテ ィ を変更し ます。 4. デバ ッ グ コ ア を含むデザ イ ン を イ ンプ リ メ ン ト し ます。デバ ッ グ コ アのカ ス タ マ イズおよび生成

Flow Navigator で [Project Manager] → [IP Catalog] を ク リ ッ ク し 、必要なデバ ッ グ コ ア を選択 し て カ ス タ マ イ ズ し ます。 デバ ッ グ コ アは、 IP カ タ ロ グの [Debug & Verification] → [Debug] カ テ ゴ リ にあ り ます (図4-6)。 デバ ッ グ コ ア を カ ス

タ マ イ ズする には、IP コ ア を ダブル ク リ ッ ク する か、 右 ク リ ッ ク し て [Customize IP] を ク リ ッ ク し ます。 ILA v2.0 コ アの カ ス タ マ イ ズの詳細は、 『Integrated Logic Analyzer (ILA) v2.0 データ シー ト 』 (DS875) を参照 し て く だ さ い。 コ ア を カ ス タ マ イ ズ し た ら 、[Generate] ボ タ ン を ク リ ッ ク し ます。 カ ス タ マ イ ズ さ れたデバ ッ グ コ アが生成 さ れ、[Sources] ビ ュ ーに追加 さ れます。

X-Ref Target - Figure 4-6

デバ ッ グ コ アのイ ン ス タ ン シエーシ ョ ン

デバ ッ グ コ ア を生成 し た ら 、 HDL ソ ース に イ ン ス タ ン シエー ト し、 デバ ッ グ用にプ ロ ーブす る 信号に接続 し ます。 次に、Verilog HDL ソ ース フ ァ イ ルの ILA v2.0 イ ン ス タ ン ス の例を示 し ます。 ila_v2_0_0 i_ila ( .CLK(clk), .PROBE0(counterA), .PROBE1(counterB), .PROBE2(counterC), .PROBE3(counterD), .PROBE4(A_or_B), .PROBE5(B_or_C), .PROBE6(C_or_D), .PROBE7(D_or_A) );注記 : レ ガシ VIO および ILA v1.x コ アでは、 ICON v1.x コ アへの接続が必要です。 ILA v2.0 コ アでは、 ICON コ ア イ ン ス タ ン スへの接続は必要あ り ません。 その代わ り に debug_core_hub デバ ッ グ コ アが合成済みデザ イ ン ネ ッ ト リ ス

ト に自動的に挿入 さ れ、ILA v2.0 コ ア と JTAG ス キ ャ ン チ ェーンの間が接続 さ れます。

デバ ッ グ コ ア を含むデザイ ンの合成

次に、Vivado IDE で [Run Synthesis] を ク リ ッ ク する か、 次の Tcl コ マン ド を使用し て、 デバ ッ グ コ ア を含むデザ イ ン を合成 し ます。

launch_runs synth_1 wait_on_run synth_1

synth_design Tcl コ マン ド を使用し てデザ イ ン を合成する こ と も で き ます。デザ イ ンの さ ま ざ ま な合成方法は、『Vivado Design Suite ユーザー ガ イ ド : 合成』 (UG901) [参照 2] を参照 し て く だ さ い。

重要: デザイ ンに追加し た ILA v2.0 コ アはブ ラ ッ ク ボ ッ ク ス イ ン ス タ ン スであ り 、 デザ イ ン イ ンプ リ メ ンテーシ ョ ン プ ロ セ ス の opt_design ま たは place_design の段階で実際の ILA v2.0 コ アに置き換え ら れます。合成中に表示 さ れる 次の ク リ テ ィ カル警告は無視 し て も 問題あ り ません。

CRITICAL WARNING:[Designutils 20-1022] Could not resolve non-primitive black box cell 'ila' instantiated in module 'inst'.

HDL イ ン ス タ ン シ エーシ ョ ン デバ ッ グ プ ローブ フ ロー

合成済みデザイ ン でのデバ ッ グ コ アの表示

デザ イ ン を 合成 し た ら 、 合成済みデザ イ ン を 開い て デバ ッ グ コ ア を 表示 し 、 プ ロ パ テ ィ を 変更で き ま す。 Flow Navigator で [Open Synthesized Design] を ク リ ッ ク し て 合成済みデザ イ ン を 開 き 、 [Debug] レ イ ア ウ ト を 選択 し て [Debug] ビ ューを表示し ます。 debug_core_hub に接続 さ れてい る ILA v2.0 コ アが表示 さ れます (図4-7)。

X-Ref Target - Figure 4-7

デバ ッ グ コ ア ハブの BSCAN ユーザー スキ ャ ン チ ェ ーンの変更

debug_core_hub の BSCAN ユーザー ス キ ャ ン チ ェーン イ ンデ ッ ク ス を表示お よび変更する には、 [Debug] ビ ュ ー で debug_core_hub を選択 し、[Instance Properties] ビ ューで [Debug Core Options] を ク リ ッ ク し て、[C_USER_SCAN_CHAIN] の値を変更 し ます (図4-8)。

重要: レ ガ シ ICON、 ILA、 ま た は VIO v1.x コ ア と ILA v2.0 コ ア を 両方使用す る 場合は、 debug_core_hub の C_USER_SCAN_CHAIN プ ロ パテ ィ を ICON v1.x コ アのバ ウ ン ダ リ ス キ ャ ン チ ェ ーン設定 と 競合 し ない値に設定す

る 必要があ り ます。 その よ う に し ない と 、 イ ンプ リ メ ン テーシ ョ ン フ ローの後の方でエ ラ ーが発生 し ます。

X-Ref Target - Figure 4-8

デバ ッ グ コ ア を含むデザイ ンのイ ン プ リ メ ン テーシ ョ ン

デバ ッ グ コ ア を含むデザイ ンのイ ン プ リ メ ン テー

シ ョ ン

Vivado ツールでは、 debug_core_hub デバ ッ グ コ アは、 最初ブ ラ ッ ク ボ ッ ク ス と し て作成 さ れます。 こ れ ら の コ アは、 配置配線を実行する 前に イ ンプ リ メ ン ト し てお く 必要があ り ます。デバ ッ グ コ アのイ ン プ リ メ ン テーシ ョ ン

デバ ッ グ コ アの イ ンプ リ メ ン テーシ ョ ンは、デザ イ ン を イ ンプ リ メ ン ト する と 自動的に実行 さ れますが、 フ ロ アプ ラ ン ま たは タ イ ミ ン グ解析用に手動で イ ンプ リ メ ン ト する こ と も で き ます。 コ ア を手動で イ ンプ リ メ ン ト す る には、 次 のいずれかを実行 し ます。• [Debug] ビ ューのツールバーの [Implement Debug Cores] を ク リ ッ ク し ます。

• [Debug] ビ ューでデバ ッ グ コ ア を右 ク リ ッ ク し 、 [Implement Debug Cores] を ク リ ッ ク し ます。

各ブ ラ ッ ク ボ ッ ク ス デバ ッ グ コ アが生成 さ れ、 合成 さ れます。 こ の処理には、 多少時間がかか る 場合があ り ます。

こ の間、 進捗状況を示すダ イ ア ロ グ ボ ッ ク ス が表示 さ れます。 デバ ッ グ コ アの イ ンプ リ メ ン テーシ ョ ンが完了する

と 、 デバ ッ グ コ アのブ ラ ッ ク ボ ッ ク ス が処理 さ れ、 生成 さ れた イ ン ス タ ン ス にア ク セ ス で き ます。

デザイ ンのイ ン プ リ メ ン テーシ ョ ン

デバ ッ グ コ ア を含むデザ イ ン を イ ンプ リ メ ン ト する には、 Vivado IDE で [Run Implementation] を ク リ ッ ク する か、 次 の Tcl コ マン ド を使用し ます。

launch_runs impl_1 wait_on_run impl_1

イ ンプ リ メ ン テーシ ョ ン コ マン ド opt_design、 place_design、 および route_design を使用し て、 デザ イ ン を イ ンプ リ メ ン ト する こ と も 可能です。デザ イ ンの さ ま ざ ま な イ ンプ リ メ ン テーシ ョ ン方法は、『Vivado Design Suite ユーザー ガ イ ド : イ ンプ リ メ ンテーシ ョ ン』 (UG904) [参照 3] を参照し て く だ さ い。

ハー ド ウ ェ ア でのデザイ ンのデバ ッ グ

概要

デザ イ ンにデバ ッ グ コ ア を追加 し た ら 、 ラ ン タ イ ム ロ ジ ッ ク 解析機能を使用 し て、 ハー ド ウ ェ ア上でデザ イ ン をデ

バ ッ グで き ます。 デザ イ ンに含まれ る デバ ッ グ コ アに よ っ て、 次の 2 つのツールを使用で き ます。

• ChipScope™ Pro Analyzer : ICON v1.x、 ILA v1.x、 VIO v1.x、 およびすべての IBERT デバ ッ グ コ アで使用 • Vivado™ ロ ジ ッ ク 解析機能 : ILA v2.0 デバ ッ グ コ アで使用

デザ イ ンに ICON/ILA/VIO v1.x と ILA v2.0 デバ ッ グ コ アの両方が含まれてい る場合は、 ChipScope Pro Analyzer ツー

ル と Vivado ロ ジ ッ ク 解析機能を同時に使用し て、 同 じ ハー ド ウ ェ ア ターゲ ッ ト ボー ド 上で動作し てい る同じ デザ イ

ン をデバ ッ グで き ます。 詳細は、32 ページの 「Vivado ロ ジ ッ ク 解析を使用 し たデザ イ ンのデバ ッ グ」 を参照 し て く

だ さ い。

ChipScope Pro Analyzer を使用 し たデザイ ンのデバ ッ グ

ChipScope Pro Analyzer ツールは、 デザ イ ンに含まれる ICON v1.x、 ILA v1.x、 VIO v1.x デバ ッ グ コ アにア ク セ スする ために使用 し ます。ChipScope Pro Analyzer ツールが イ ン ス ト ール さ れてい る場合は、 [Generate Bitstream] が実行 さ れ てい る イ ンプ リ メ ン ト 済みデザ イ ンに対 し て、Vivado IDE か ら 直接起動で き ます。

ChipScope Pro Analyzer を起動する には、 次のいずれかの操作を実行し ます。 • メ イ ン メ ニ ューか ら [Flow ] → [Launch ChipScope Analyzer] を ク リ ッ ク し ます。 • Tcl コ ン ソ ールか ら launch_chipscope_analyzer Tcl コ マン ド を実行 し ます。

ビ ッ ト ス ト リ ーム フ ァ イ ル (BIT) と CDC ネ ッ ト 接続名フ ァ イ ルが、自動的に ChipScope Pro Analyzer で読み込まれま す。ChipScope Pro Analyzer の詳細は、http://japan.xilinx.com/support/documentation/dt_chipscopepro.htm を参照し て く だ

Vivado ロ ジ ッ ク 解析を使用 し たデザイ ンのデバ ッ グ

Vivado ロ ジ ッ ク解析を使用 し たデザイ ンのデバ ッ グ

Vivado ロ ジ ッ ク 解析機能は、 ChipScope Pro Analyzer ツールは、 デザ イ ンに含まれる ILA v2.0 デバ ッ グ コ アにア ク セ スする ために使用 し ます。Vivado ロ ジ ッ ク 解析機能を使用する には、 Flow Navigator で [Program and Debug] → [Open Hardware Session] を ク リ ッ ク し ます。 デザ イ ンのデバ ッ グ手順は、 次の と お り です。 1. ハー ド ウ ェ ア ターゲ ッ ト に接続 し、 FPGA デバ イ ス を .bit フ ァ イ ルでプ ロ グ ラ ム し ます。 2. ILA デバ ッ グ コ アの ト リ ガー条件 と プ ローブ比較条件を設定し ます。 3. ILA デバ ッ グ コ ア を ト リ ガー待機状態に し ます。 4. 波形ビ ュ ーアーで ILA デバ ッ グ コ アか ら のデータ を表示し ます。

ハー ド ウ ェ ア タ ーゲ ッ ト に接続 し て FPGA デバイ ス

を プ ロ グ ラ ム

デバ ッ グ の前に FPGA デバ イ ス を プ ロ グ ラ ムす る 手順は、第2 章の 「Vivado ハー ド ウ ェ ア セ ッ シ ョ ン を使用 し た FPGA デバ イ ス のプ ロ グ ラ ム」 で説明 さ れてい る 手順 と 同 じ です。ILA v2.0 コ ア を含む .bit フ ァ イ ルでデバ イ ス をプロ グ ラ ムする と 、[Hardware] ビ ューにデバ イ ス の ス キ ャ ンで検出 さ れた ILA コ アが表示 さ れます (図5-1)。

X-Ref Target - Figure 5-1

計測のための ILA コ アの設定

デザ イ ンに追加 し た ILA コ アは、 [Hardware] ビ ュ ーの ターゲ ッ ト デバ イ ス の下に表示 さ れます。 ILA コ アが表示 さ れ ない場合は、 デバ イ ス を右 ク リ ッ ク し て [Refresh Hardware] を ク リ ッ ク し ます。 FPGA デバ イ ス が再度ス キ ャ ン さ れ、 [Hardware] ビ ューの表示が更新 さ れます。

注記 : FPGA デバ イ ス をプ ロ グ ラ ム ま たは更新し て も ILA コ アが表示 さ れない場合は、デバイ スが正し い .bit フ ァ イ ルでプ ロ グ ラ ム さ れてい る か、 イ ンプ リ メ ン ト 済みデザ イ ンに ILA v2.0 コ アが含まれてい る かを確認し て く だ さ い。 ILA コ ア (図5-1 では hw_ila_1) を選択する と 、 [ILA Core Properties] ビ ューにプ ロ パテ ィ が表示 さ れます。 [Hardware]

ビ ュ ーで も 、ILA コ アのい く つかの設定を変更で き ます。

• ト リ ガー条件

• ト リ ガー位置

• デー タ の深 さ

ILA コ アの ト リ ガー条件の設定

[Hardware] ビ ューの [Trigger Cond] ま たは [ILA Core Properties] ビ ュ ーの [Trigger Condition] プ ロ パテ ィ を使用 し て、 ト リ ガー条件を [AND] ま たは [OR] に設定 し ます。 [AND] に設定する と 、 すべての ILA プ ローブ比較が一致し た場合に

ト リ ガー イベン ト が発生 し ます。 [OR] に設定する と 、 ILA プ ローブ比較のいずれかが一致し た場合に ト リ ガー イ ベ

ン ト が発生 し ます。set_property Tcl コ マン ド を使用し て も ILA コ アの ト リ ガー条件を変更で き ます。 set_property CONTROL.TRIGGER_CONDITION AND [get_hw_ilas hw_ila_1]

ILA コ アの ト リ ガー位置の設定

[Hardware] ビ ューの [Trigger Pos] ま たは [ILA Core Properties] ビ ューの [Trigger Position] プ ロ パテ ィ を使用し て、 キ ャ

プチ ャ データ バ ッ フ ァ ーの ト リ ガー マー ク の位置を設定し ます。 ト リ ガー位置は、 キ ャ プチ ャ データ バ ッ フ ァ ーの 任意のサ ンプル番号に設定で き ます。 た と えば、 サンプル数が 1024 のキ ャ プチ ャ データ バ ッ フ ァ ーの場合は次の よ う にな り ます。 • サンプル番号 0 は、 キ ャ プチ ャ データ バ ッ フ ァ ーの最初 (一番左) のサンプルに対応 し ます。 • サンプル番号 1023 は、 キ ャ プチ ャ データ バ ッ フ ァ ーの最後 (一番右) のサンプルに対応し ます。 • サンプル番号 511 および 512 は、 キ ャ プチ ャ データ バ ッ フ ァ ーの中央のサンプルに対応し ます。 set_property Tcl コ マン ド を使用し て も ILA コ アの ト リ ガー位置を変更で き ます。

ILA プ ローブ情報の記述

ILA コ アのデー タ 深 さ の設定

[Hardware] ビ ューの [Data Depth] ま たは [ILA Core Properties] ビ ュ ーの [Capture data depth] プ ロ パテ ィ を使用し て、ILA

コ アのキ ャ プチ ャ データ バ ッ フ ァ ーのデータ深 さ を設定し ます。デー タ深 さ は、1 か ら 最大データ深 さ の間の 2 のべ

き 乗に設定で き ます。

注記 : ネ ッ ト リ ス ト 挿入プ ローブ フ ローでデザ イ ンに追加 し た ILA コ アのキ ャ プチ ャ バ ッ フ ァ ーの最大データ 深 さ

を設定する 方法は、23 ページの 「デバ ッ グ コ アのプ ロ パテ ィ の変更」 を参照 し て く だ さ い。

set_property Tcl コ マン ド を使用し て も ILA コ アのデータ深 さ を変更で き ます。 set_property CONTROL.DATA_DEPTH 512 [get_hw_ilas hw_ila_1]

ILA プ ローブ情報の記述

[ILA Probes] ビ ューには、ILA v2.0 コ ア を使用 し てプ ローブ さ れるデザ イ ンのネ ッ ト に関する情報が表示 さ れます。 こ の情報はデザ イ ンか ら 抽出 さ れ、 通常は .ltx と い う 拡張子のデータ フ ァ イ ルに保存 さ れます。 ILA プ ローブ フ ァ イ ルは、 イ ンプ リ メ ン テーシ ョ ン プ ロ セ ス中に自動的に作成 さ れますが、write_debug_probes Tcl コ マ ン ド を使用 し てデバ ッ グ プ ローブ情報を フ ァ イ ルに書き出す こ と も で き ます。 1. 合成済みデザ イ ン ま たはネ ッ ト リ ス ト デザ イ ン を開き ます。 2. Tcl コ マン ド write_debug_probes filename.ltx を実行 し ます。

ILA プ ローブ情報の読み出 し

ILA プ ロ ーブ フ ァ イ ルの名前が debug_nets.ltx で、 デバ イ ス に関連付け ら れてい る ビ ッ ト ス ト リ ーム プ ロ グ ラ ム フ ァ イ ル (.bit) と 同 じデ ィ レ ク ト リ にあ る場合、 自動的に FPGA ハー ド ウ ェ ア デバ イ ス に関連付け ら れます。 プ ロ ーブ フ ァ イ ルの場所を指定する には、 次の手順に従い ます。 1. [Hardware] ビ ューで FPGA デバ イ ス を選択 し ます。2. [Hardware Device Properties] ビ ュ ーの [Probes file] でフ ァ イ ルの場所を設定 し ます。 3. [Apply] を ク リ ッ ク し て変更を適用 し ます。

プ ローブ フ ァ イ ルの場所は、 次の set_property Tcl コ マン ド を使用 し て も 設定で き ます。

ILA プ ローブの表示

[ILA Probes] ビ ューには、 各 ILA コ アに関連付け ら れてい る プ ローブが表示 さ れます。 FPGA ハー ド ウ ェ ア デバ イ ス にプ ロ ーブ フ ァ イ ルを関連付けた ら 、ハー ド ウ ェ ア デバ イ ス を右 ク リ ッ ク し 、[Refresh Device] を ク リ ッ ク し て、[ILA Probes] ビ ューを更新し ます (図5-2)。

ILA プ ローブの ト リ ガー比較値の設定

ILA v2.0 コ アのプ ロ ーブ入力におけ る等価条件ま たは不等価条件の検出には、 ILA プ ロ ーブ ト リ ガー コ ンパレー タ が使用 さ れます。 ト リ ガー条件は、 各 ILA プ ローブ ト リ ガー コ ンパレータ の結果を AND ま たは OR で統合し た結果

です。 詳細は、33 ページの 「ILA コ アの ト リ ガー条件の設定」 を参照 し て く だ さ い。ILA プ ローブの比較値を指定す

る には、[ILA Probes] ビ ュ ーで [Compare Value] セルを選択し 、 [Compare Value] ダ イ ア ロ グ ボ ッ ク ス を開き ます (図5-3)。

X-Ref Target - Figure 5-2

図 5-2 : [ILA Probes] ビ ュ ー

X-Ref Target - Figure 5-3

![図 1-1 : Flow Navigator の [Program and Debug]](https://thumb-ap.123doks.com/thumbv2/123deta/5820591.540566/5.892.343.508.437.961/図-flow-navigator-の-program-debug.webp)

![図 2-1 : [Project Settings] ダ イ ア ログ ボ ッ ク スの [Bitstream] ページ](https://thumb-ap.123doks.com/thumbv2/123deta/5820591.540566/7.892.126.718.110.630/図21ProjectSettingsダイアログボックスのBitstreamページ.webp)

![図 2-4 : ハー ド ウ ェ ア タ ーゲ ッ ト への接続を開いた後の [Hardware] ビ ュ ー](https://thumb-ap.123doks.com/thumbv2/123deta/5820591.540566/12.892.221.629.330.649/ハードウェアターゲット接続開い後ビュー.webp)

![図 4-1 : [Debug] ビ ュ ーの [Unassigned Debug Nets] フ ォルダー](https://thumb-ap.123doks.com/thumbv2/123deta/5820591.540566/19.892.316.631.612.852/図41DebugビューのUnassignedDebugNetsフォルダー.webp)

![図 4-3 : [Create Debug Core] ダ イ ア ログ ボ ッ ク ス](https://thumb-ap.123doks.com/thumbv2/123deta/5820591.540566/21.892.261.686.454.806/図43CreateDebugCoreダイアログボックス.webp)

![図 4-4 : [Create Debug Port] ダ イ ア ログ ボ ッ ク ス](https://thumb-ap.123doks.com/thumbv2/123deta/5820591.540566/22.892.260.685.344.696/図44CreateDebugPortダイアログボックス.webp)