1. 概 要 AK4432はディジタルオーディオ機器に対応した32ビットDACです。内部回路は新開発の32bit Digital Filter を採用し、低群遅延、高音質を実現しています。内蔵のポストフィルタには新規スイッチトキャ パシタフィルタ(SCF)を採用し、クロックジッタによる精度の劣化を改善します。サンプリングレートは 192kHzまで対応しており、DVD-Audio,カーオーディオサラウンドシステム等のシステムに最適です。AK4432 は超小型16pin TSSOPパッケージに実装され、基板スペースを削減します。 2. 特 長 1. 2ch 32bit DAC - 128倍オーバサンプリング - 32ビット高音質低群遅延ディジタルフィルタ - シングルエンド出力、スムージングフィルタ内蔵 - THD+N: 91dB - DR, S/N: 108dB - チャネル独立ディジタルボリューム内蔵 (12dB~-115dB, 0.5dB Step, Mute) - ソフトミュート - ディエンファシス内蔵 (32kHz, 44.1kHz, 48kHz対応) - I/Fフォーマット: 前詰め, 後詰め, I2S, TDM - ゼロ検出機能 2. サンプリング周波数

- Normal Speed Mode: 8kHz to 48kHz - Double Speed Mode: 64kHz to 96kHz - Quad Speed Mode: 128kHz to 192kHz 3. マスタクロック

256fs, 384fs, 512fs or 768fs (Normal Speed Mode: fs=8kHz 48kHz) 256fs or 384fs (Double Speed Mode: fs=48kHz 96kHz) 128fs or 192fs (Quad Speed Mode: fs=96kHz 192kHz)

4. Pインタフェース: 3線シリアル(7MHz max)/ I2Cバス (400kHzモード, 1MHz モード) 5. 電源電圧 - アナログ電源: AVDD = 3.0 3.6V - 入出力バッファ電源: LVDD = 3.0 3.6V - ディジタル電源用LDO内蔵 6. 消費電流: 7.8mA (fs=48kHz) 7. Ta = - 40 105℃

8. パッケージ: 16-pin TSSOP (0.65mm pitch)

108dB 192kHz 32bit 2-Channel Audio DAC

3. 目次 1. 概 要 ... 1 2. 特 長 ... 1 3. 目次 ... 2 4. ブロック図と機能説明 ... 3 ■ ブロック図 ... 3 ■ AK4436/38、AK4452/54/56/58との相違点 ... 4 5. ピン配置と機能説明 ... 5 ■ オーダリングガイド ... 5 ■ ピン配置 ... 5 ■ ピン機能 ... 6 ■ 使用しないピンの処理について ... 6 6. 絶対最大定格 ... 7 7. 推奨動作条件 ... 7 8. アナログ特性 ... 8 9. フィルタ特性(fs=48kHz) ... 9

■ Sharp Roll-Off Filter (DASD bit = “0”, DASL bit = “0”) ... 9

■ Slow Roll-Off Filter (DASD bit = “0”, DASL bit = “1”) ... 10

■ Short Delay Sharp Roll-Off Filter (DASD bit = “1”, DASL bit = “0”) ... 11

■ Short Delay Slow Roll-Off Filter (DASD bit = “1”, DASL bit = “1”) ... 12

10. DC特性 ... 13 11. スイッチング特性 ... 14 ■ タイミング波形 ... 17 12. 動作説明 ... 21 ■ システムクロック ... 21 ■ オーディオインタフェースフォーマット ... 23 ■ ディジタルボリューム機能 ... 30 ■ ソフトミュート機能 ... 31 ■ エラー検出 ... 32 ■ システムリセット ... 32 ■ パワーダウン機能 ... 33 ■ パワーオフ、リセット機能 ... 34 ■ クロック同期化機能 ... 35 ■ パラレルモード ... 36 (1) オーディオインターフェース ... 36 (2)ソフトミュート ... 36 (3) システムクロック ... 36 ■ シリアルコントロールインタフェース... 37 ■ レジスタマップ ... 43 ■ 詳細説明 ... 44 13. 外部接続回路例 ... 46

4. ブロック図と機能説明

■

ブロック図 Audio I/F LRCK BICK SDTI MCLK LRCK BICK SDIN MCLK PDN DAC DAC uP I/F (I2C/SPI) ACKS/CCLK/SCL DIF/CDTI/SDA LVDD SCF AOUTL SCF AOUTR SMF SMF LDOO LDO AVDD VSS P/S VCOM SMUTE/CSN/I2CFIL Figure 1. ブロック図■

AK4436/38、AK4452/54/56/58との相違点AK4432 AK4436 / 38 AK4452 / 54 / 56 / 58 Channel 2ch 6ch / 8ch 2ch / 4ch / 6ch / 8ch fs 8k to 192kHz 8k to 768kHz 8k to 768kHz

S/(N+D) 91dB 91dB 107dB

DR 108dB 108dB 115dB

AVDD (Analog Supply) 3.0 to 3.6V 3.0 to 3.6V 3.0 to 5.5V TVDD or LVDD (I/O Buffer) 3.0 to 3.6V 1.7 to 3.6V 1.7 to 3.6V Digital Filter SA(Sharp) 69.9dB 80dB 80dB GD(Sharp) 26.4/fs 26.8/fs 26.8/fs GD (SD Slow) 5.2/fs 4.8/fs 4.8/fs

Super Slow Roll-off No Yes Yes

OSR Doubler (Over Sampling) No (128x) Yes (256x) Yes (256x)

Zero Detection No Yes Yes

Digital Volume +12 to -115.0dB +0 to -127.0dB +0 to -127.0dB ATT Speed (*Default) 1020/fs (*)

4080

4080/fs (*) 2040、510、255

4080/fs (*) 2040、510、255

LR Ch Output Select No Yes Yes

Reset Function

(MCLK detect) No Yes Yes

Clock Synchronization Yes (Note) Yes Yes

Package 16-pin TSSOP 32-pin QFN AK4452/54: 32-pin QFN AK4456/58: 48-pin QFN

Note. オーディオインタフェースフォーマットは前詰め、32-bit I2S 互換に制限されます。後詰めフォー マットは使用できません。

5. ピン配置と機能説明

■

オーダリングガイドAK4432VT -40 +105C 16-pin TSSOP (0.65mm pitch) AKD4432 評価ボード

■

ピン配置 1 MCLK LRCK BICK SMUTE/CSN/I2CFIL ACKS/CCLK/SCL DIF/CDTI/SDA AK4432 Top View 2 3 4 5 6 7 8 LDOO LVDD VSS AVDD VCOM AOUTL AOUTR P/S 16 15 14 13 12 11 10 9 PDN SDTI Figure 2. ピン配置■

ピン機能No. Pin Name I/O PD状態 Function

1 MCLK I - Master Clock Input Pin 2 BICK I - Audio Serial Data Clock Pin 3 SDTI I - Audio Serial Data Input 4 LRCK I - Input Channel Clock Pin

5 PDN I -

Power-Down & Reset Pin

When “L”, the AK4432 is powered-down and the control registers are reset to default state.

6

SMUTE I

-

Soft Mute Pin in Parallel control mode.

When this pin is changed to “H”, soft mute cycle is initiated. When returning “L”, the output mute releases.

CSN I Chip Select Pin in 3-wire serial control mode I2CFIL I

I2C Interface Mode Select Pin

“L”: Fast Mode (400kHz), “H”: Fast Mode Plus (1MHz). Do not change this pin during PDN pin = “H”.

7

ACKS I

-

Auto Setting Mode in Parallel control mode

“L”: Manual Setting Mode, “H”: Auto Setting Mode CCLK I Control Data Clock Pin in 3-wire serial control mode SCL I Control Data Clock Pin in I2C Bus serial control mode

8

DIF I

-

Audio Data Format Select in Parallel control mode. “L”:32bit MSB, “H”:32bit I2S

CDTI I Control Data Input Pin in 3-wire serial control mode SDA

I/O Control Data Input Pin in I

2

C Bus serial control mode P

9 P/S I -

Parallel/Serial Mode Select Pin “L”: Serial Mode, “H”: Parallel Mode Do not change this pin during PDN pin = “H”. 10 AOUTR O Hi-z Rch Analog Output Pin

11 AOUTL O Hi-z Lch Analog Output Pin 12 VCOM O 500ohm

Pull-down

Common Voltage Output Pin, AVDDx1/2

Large external capacitor around 2.2µF is used to reduce power-supply noise.

13 VSS - - Ground Pin

14 AVDD - - Analog Power Supply Pin, 3.0V3.6V

15 LVDD - - LDO Power Supply / Digital I/F Power Supply Pin, 3.0V3.6V 16 LDOO O 580ohm

Pull-down

LDO Output Pin

This pin should be connected to ground with 1.0µF. Note 1. 全てのディジタル入力ピンはフローティングにしないで下さい。

■

使用しないピンの処理について6. 絶対最大定格 (VSS =0V; Note 2)

Parameter Symbol Min. Max. Unit

Power Supply AVDD -0.3 4.3 V

Power Supply LVDD -0.3 4.3 V

Input Current (any pins except for supplies) IIN - 10 mA Input Voltage (Note 3) VIN -0.3 (LVDD+0.3) or 4.3 V Ambient Temperature (power applied) Ta -40 105 C

Storage Temperature Tstg -65 150 C Note 2. 電圧はグランドに対する値です。VSSはアナロググラウンドに接続して下さい。 Note 3. ディジタル入力電圧のmax値は、(LVDD+0.3)Vまたは4.3Vのどちらか低い方です 注意: この値を超えた条件で使用した場合、デバイスを破壊することがあります。 また通常の動作は保証されません。 7. 推奨動作条件 (VSS=0V; Note 2)

Parameter Symbol Min. Typ. Max. Unit

Power

Supplies Analog AVDD 3.0 3.3 3.6 V

LDO, Digital (I/F) LVDD 3.0 3.3 3.6 V Note 4. 周辺デバイスが電源ONの状態でAK4432の電源をOFFにしないで下さい。また、I2Cインタフェ

ースを使用する場合、SDA, SCL pinのプルアップ抵抗の接続先はLVDD以下にして下さい。 注意: 本データシートに記載されている条件以外のご使用に関しては、当社では責任負いかねますので

8. アナログ特性

(特記なき場合は、Ta=25C; AVDD = LVDD=3.3V; VSS =0V; fs=48kHz, 96kHz, 192kHz; BICK=64fs; Signal Frequency=1kHz; 32bit Data; Measurement Frequency=20Hz20kHz at fs=48kHz, 20Hz~40kHz at fs=96kHz, 20Hz~40kHz at fs=192kHz)

Parameter Min. Typ. Max. Unit

DAC Analog Output Characteristics

Resolution - - 32 bit

Output Voltage (Note 5) 2.55 2.83 3.11 Vpp S/(N+D) (0dBFS) fs=48kHz 80 91 - dB fs=96kHz - 89 - dB fs=192kHz - 89 - dB Dynamic Range (-60dBFS) fs=48kHz (A-weighted) - 108 - dB fs=96kHz - 101 - dB fs=192kHz - 101 - dB S/N fs=48kHz (A-weighted) - 108 - dB fs=96kHz - 101 - dB fs=192kHz - 101 - dB Interchannel Isolation 90 110 - dB

Interchannel Gain Mismatch - 0 0.7 dB

Load Resistance (Note 6) 10 - - k

Load Capacitance - - 30 pF

Note 5. フルスケール出力電圧です。出力電圧はAVDDに比例 (AVDD x 0.86)します。 Note 6. AC負荷。

Parameter Min. Typ. Max. Unit

Power Supplies

Power Supply Current

Normal Operation (PDN pin = “H”)

AVDD fs=48kHz, 96kHz, 192kHz LVDD fs=48kHz

fs=96kHz fs=192kHz Power-down mode (PDN pin = “L”) (Note 7)

- - - - - 6.5 1.3 1.6 2.1 10 9.0 2 2.5 3.0 200 mA mA mA mA µA Note 7. 静止時。クロックを含む全てのディジタル入力ピンをVSSに固定した場合の値です。

9. フィルタ特性(fs=48kHz) (Ta= -40 +105C; AVDD =3.0 3.6V, LVDD=3.0 3.6V; DEM=OFF)

■

Sharp Roll-Off Filter (DASD bit = “0”, DASL bit = “0”) fs=48kHzParameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.08dB~+0.08dB PB 0 - 22.2 kHz -6.0dB PB - 23.99 - kHz Passband Ripple PR -0.08 +0.08 dB Stopband (Note 8) SB 26.2 kHz Stopband Attenuation SA 69.9 dB

Group Delay (Note 9) GD - 26.4 - 1/fs Digital Filter + SCF + SMF

Frequency Response : 0Hz 20kHz FR -0.20 -0.10 dB fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.08dB~+0.08dB PB 0 - 44.4 kHz -6.0dB PB - 48.00 - kHz Passband Ripple PR -0.08 +0.08 dB Stopband (Note 8) SB 52.5 kHz Stopband Attenuation SA 69.8 dB

Group Delay (Note 9) GD - 26.4 - 1/fs Digital Filter + SCF + SMF

Frequency Response : 0Hz 40kHz FR -0.50 -0.10 dB fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.08dB~+0.08dB PB 0 - 88.8 kHz -6.0dB PB - 96.00 - kHz Passband Ripple PR -0.08 +0.08 dB Stopband (Note 8) SB 104.9 kHz Stopband Attenuation SA 69.8 dB

Group Delay (Note 9) GD - 26.4 - 1/fs Digital Filter + SCF + SMF

■

Slow Roll-Off Filter (DASD bit = “0”, DASL bit = “1”) fs=48kHzParameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.07dB~+0.021dB PB 0 - 9.0 kHz -3.0dB PB - 19.75 - kHz Passband Ripple PR -0.07 +0.021 dB Stopband (Note 8) SB 42.6 kHz Stopband Attenuation SA 72.6 dB

Group Delay (Note 9) GD - 26.4 - 1/fs Digital Filter + SCF + SMF

Frequency Response: 0Hz 20kHz FR -3.75 -2.75 dB fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.07dB~+0.023dB PB 0 - 18.1 kHz -3.0dB PB - 39.6 - kHz Passband Ripple PR -0.07 +0.023 dB Stopband (Note 8) SB 85.1 kHz Stopband Attenuation SA 72.6 dB

Group Delay (Note 9) GD - 26.4 - 1/fs Digital Filter + SCF + SMF

Frequency Response: 0Hz 40kHz FR -4.25 -2.75 dB fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.07dB~+0.023dB PB 0 - 36.1 kHz -3.0dB PB - 79.3 - kHz Passband Ripple PR -0.07 +0.023 dB Stopband (Note 8) SB 170.3 kHz Stopband Attenuation SA 72.6 dB

Group Delay (Note 9) GD - 26.4 - 1/fs Digital Filter + SCF + SMF

■

Short Delay Sharp Roll-Off Filter (DASD bit = “1”, DASL bit = “0”) fs=48kHzParameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.07dB~+0.07dB PB 0 - 22.0 kHz -6.0dB PB - 24.11 - kHz Passband Ripple PR -0.07 +0.07 dB Stopband (Note 8) SB 26.2 kHz Stopband Attenuation SA 56.6 dB

Group Delay (Note 9) GD - 5.9 - 1/fs Digital Filter + SCF + SMF

Frequency Response : 0Hz 20kHz FR -0.20 -0.10 dB fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.08dB~+0.08dB PB 0 - 44.3 kHz -6.0dB PB - 48.25 - kHz Passband Ripple PR -0.08 +0.08 dB Stopband (Note 8) SB 52.5 kHz Stopband Attenuation SA 56.4 dB

Group Delay (Note 9) GD - 5.9 - 1/fs Digital Filter + SCF + SMF

Frequency Response : 0Hz 40kHz FR -0.50 -0.10 dB fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.08dB~+0.08dB PB 0 - 88.6 kHz -6.0dB PB - 96.50 - kHz Passband Ripple PR -0.08 +0.08 dB Stopband (Note 8) SB 104.9 kHz Stopband Attenuation SA 56.4 dB

Group Delay (Note 9) GD - 5.9 - 1/fs Digital Filter + SCF + SMF

■

Short Delay Slow Roll-Off Filter (DASD bit = “1”, DASL bit = “1”) fs=48kHzParameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.07dB~+0.05dB PB 0 - 10.1 kHz -3.0dB PB - 20.24 - kHz Passband Ripple PR -0.07 +0.05 dB Stopband (Note 8) SB 43.0 kHz Stopband Attenuation SA 74.9 dB

Group Delay (Note 9) GD - 5.2 - 1/fs Digital Filter + SCF + SMF

Frequency Response : 0Hz 20kHz FR -3.50 -2.50 dB fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.07dB~+0.05dB PB 0 - 20.3 kHz -3.0dB PB - 40.50 - kHz Passband Ripple PR -0.07 +0.05 dB Stopband (Note 8) SB 86.0 kHz Stopband Attenuation SA 74.9 dB

Group Delay (Note 9) GD - 5.2 - 1/fs Digital Filter + SCF + SMF

Frequency Response : 0Hz 40kHz FR -4.00 -2.50 dB fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

Passband (Note 8) -0.07dB~+0.05dB PB 0 - 40.6 kHz -3.0dB PB - 81.00 - kHz Passband Ripple PR -0.07 +0.05 dB Stopband (Note 8) SB 172.0 kHz Stopband Attenuation SA 74.9 dB

Group Delay (Note 9) GD - 5.2 - 1/fs Digital Filter + SCF + SMF Frequency Response : 0Hz 80kHz FR -4.75 -2.75 dB Note 8. 各振幅特性の周波数はfs(サンプリングレート)に比例します。各応答は1kHzを基準としたも のです。 Note 9. ディジタルフィルタによる演算遅延で、16/24/32bitのインパルスデータが入力レジスタにセッ トされてからアナログ信号のピークが出力されるまでの時間です。

10. DC特性

(Ta= -40 +105C; AVDD =3.0 3.6V, LVDD =3.0 3.6V, VSS=0V)

Parameter Symbol Min. Typ. Max. Unit

SCL,SDAを除くディジタル入力ピン High-Level Input Voltage

Low-Level Input Voltage

VIH1 VIL1 80%LVDD - - - - 20%LVDD V V SCL, SDA Pin

High-Level Input Voltage Low-Level Input Voltage

VIH2 VIL2 70%LVDD - - - - 30%LVDD V V SDA Pin

Low-Level Output Voltage

Fast Mode (Iout= 3mA) Fast Mode Plus (Iout= 20mA)

VOL1 VOL2 - - 0.4 0.4 V V

11. スイッチング特性

(特記なき場合は、 Ta=-40 105C; AVDD=LVDD=3.0 3.6V; CL=20pF)

Parameter Symbol Min. Typ. Max. Unit

Master Clock Timing External Clock

256fsn:

Pulse Width Low Pulse Width High 384fsn:

Pulse Width Low Pulse Width High 512fsn, 256fsd, 128fsq:

Pulse Width Low Pulse Width High 768fsn, 384fsd, 192fsq:

Pulse Width Low Pulse Width High

fCLK tCLKL tCLKH fCLK tCLKL tCLKH fCLK tCLKL tCLKH fCLK tCLKL tCLKH 2.048 32 32 3.072 22 22 4.096 16 16 16.384 11 11 12.288 18.432 24.576 36.864 MHz ns ns MHz ns ns MHz ns ns MHz ns ns

LRCK Timing (Slave Mode) Stereo mode

(TDM1-0 bits = “00”)

Normal Speed Mode Double Speed Mode Quad Speed Mode Duty Cycle fsn fsd fsq Duty 8 48 96 - 50 48 96 192 - kHz kHz kHz % TDM128 mode (TDM1-0 bits = “01”) LRCK frequency

I2S compatible: Pulse Width Low MSB or LSB justified: Pulse Width High

fsn fsd fsq tLRL tLRH 8 48 96 1/(128fsq) 1/(128fsq) 48 96 192 127/(128fsq) 127/(128fsq) kHz kHz kHz s s TDM256 mode (TDM1-0 bits = “10”) LRCK frequency

I2S compatible: Pulse Width Low MSB or LSB justified: Pulse Width High

fsn fsd tLRL tLRH 8 48 1/(256fsd) 1/(256fsd) 48 96 255/(256fsd) 255/(256fsd) kHz kHz s s

Parameter Symbol Min. Typ. Max. Unit Audio Interface Timing

Normal Mode (TDM1-0 bits = “00”)

BICK Period

Normal Speed Mode Double Speed Mode Quad Speed Mode BICK Pulse Width Low BICK Pulse Width High

BICK “” to LRCK Edge (Note 10) LRCK Edge to BICK “” (Note 10) SDTI Hold Time

SDTI Setup Time

tBCK tBCK tBCK tBCKL tBCKH tBLR tLRB tSDH tSDS 1/256fsn 1/256fsd 1/128fsq 18 18 5 5 5 5 ns ns ns ns ns ns ns ns ns TDM128 mode (TDM1-0 bits = “01”) BICK Period

Normal Speed Mode Double Speed Mode Quad Speed Mode BICK Pulse Width Low BICK Pulse Width High

BICK “” to LRCK Edge (Note 10) LRCK Edge to BICK “” (Note 10) SDTI Hold Time

SDTI Setup Time

tBCK tBCK tBCK tBCKL tBCKH tBLR tLRB tSDH tSDS 1/128fsn 1/128fsd 1/128fsq 18 18 5 5 5 5 ns ns ns ns ns ns ns ns ns TDM256 mode (TDM1-0 bits = “10”) BICK Period

Normal Speed Mode Double Speed Mode BICK Pulse Width Low BICK Pulse Width High

BICK “” to LRCK Edge (Note 10) LRCK Edge to BICK “” (Note 10) SDTI Hold Time

SDTI Setup Time

tBCK tBCK tBCKL tBCKH tBLR tLRB tSDH tSDS 1/256fsn 1/256fsd 18 18 5 5 5 5 ns ns ns ns ns ns ns ns Note 10. この規格値はLRCKのエッジとBICKの立ち上がりエッジが重ならないように規定しています。

Parameter Symbol Min. Typ. Max. Unit Control Interface Timing (3-wire Serial mode):

CCLK frequency CCLK Pulse Width Low

Pulse Width High CDTI Setup Time CDTI Hold Time CSN “H” Time CSN “” to CCLK “” CCLK “” to CSN “” fCCK tCCKL tCCKH tCDS tCDH tCSW tCSS tCSH 60 60 60 60 150 150 240 7 MHz ns ns ns ns ns ns ns

Control Interface Timing (I2C Fast mode):

SCL Clock Frequency

Bus Free Time Between Transmissions

Start Condition Hold Time (prior to first clock pulse) Clock Low Time

Clock High Time

Setup Time for Repeated Start Condition

SDA Hold Time from SCL Falling (Note 11) SDA Setup Time from SCL Rising

Rise Time of Both SDA and SCL Lines Fall Time of Both SDA and SCL Lines Setup Time for Stop Condition

Pulse Width of Spike Noise Suppressed by Input Filter Capacitive load on bus

fSCL tBUF tHD:STA tLOW tHIGH tSU:STA tHD:DAT tSU:DAT tR tF tSU:STO tSP Cb - 1.3 0.6 1.3 0.6 0.6 0 0.1 - - 0.6 0 - 400 - - - - - - - 1.0 0.3 - 50 400 kHz s s s s s s s s s s ns pF

Control Interface Timing (I2C Fast mode Plus):

SCL Clock Frequency

Bus Free Time Between Transmissions

Start Condition Hold Time (prior to first clock pulse) Clock Low Time

Clock High Time

Setup Time for Repeated Start Condition

SDA Hold Time from SCL Falling (Note 12) SDA Setup Time from SCL Rising

Rise Time of Both SDA and SCL Lines Fall Time of Both SDA and SCL Lines Setup Time for Stop Condition

Pulse Width of Spike Noise Suppressed by Input Filter Capacitive load on bus

fSCL tBUF tHD:STA tLOW tHIGH tSU:STA tHD:DAT tSU:DAT tR tF tSU:STO tSP Cb - 0.5 0.26 0.5 0.26 0.26 0 0.05 - - 0.26 0 - 1 - - - - - - - 0.12 0.12 - 50 550 MHz s s s s s s s s s s ns pF

Power-down & Reset Timing

PDN Pulse Width (Note 13) tPD 800 ns Note 11. データは最低300ns(SCLの立ち下がり時間)の間保持されなければなりません。

Note 12. データは最低120ns(SCLの立ち下がり時間)の間保持されなければなりません。

Note 13. 電源投入時はPDN pin を“L” にすることでリセットがかかります。PDN pinは800ns以上の “L” を入力してください。50ns以下の “L”ではリセットされません。

■

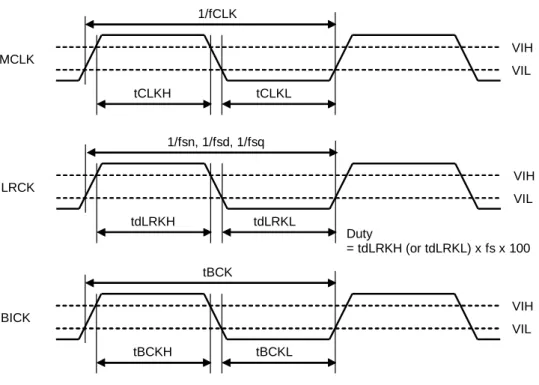

タイミング波形 1/fCLK tCLKL VIH tCLKH MCLK VIL 1/fsn, 1/fsd, 1/fsq LRCK VIH VIL tBCK tBCKL VIH tBCKH BICK VIL tdLRKL tdLRKH Duty = tdLRKH (or tdLRKL) x fs x 100Figure 3. Clock Timing (TDM1-0 bits = “00”)

1/fCLK tCLKL VIH tCLKH MCLK VIL 1/fs LRCK VIH VIL tLRL tLRH tBCK tBCKL VIH tBCKH BICK VIL

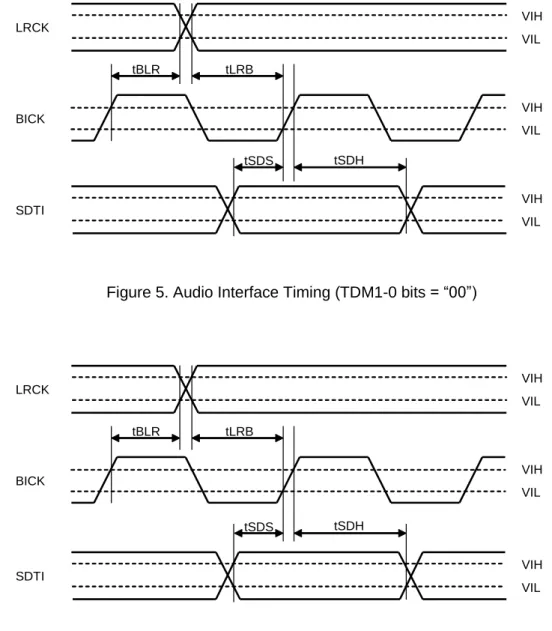

tLRB LRCK VIH BICK VIL VIH VIL tBLR tSDS SDTI VIH VIL tSDH

Figure 5. Audio Interface Timing (TDM1-0 bits = “00”)

tLRB LRCK VIH BICK VIL VIH VIL tBLR tSDS SDTI VIH VIL tSDH

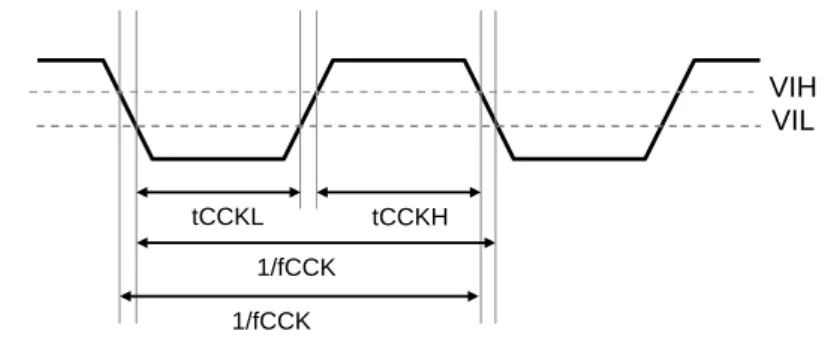

tCCKH tCCKL 1/fCCK 1/fCCK CCLK VIH VIL

Figure 7. 3-wire Serial mode Interface timing

tCSW tCDS tCDH tCSH tCSH tCSS CSN CDTI VIH VIL VIH tCSS CCLK VIL VIH VIL

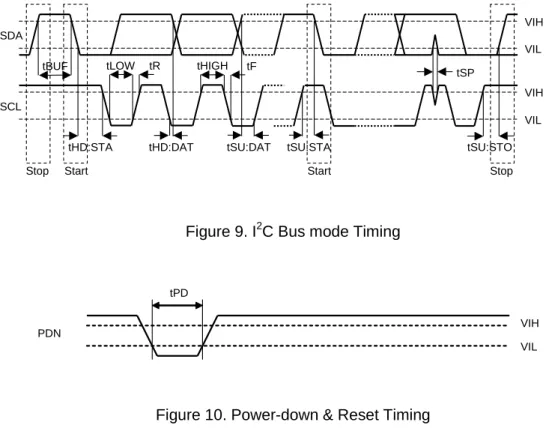

tHIGH SCL SDA VIH tLOW tBUF tHD:STA tR tF

tHD:DAT tSU:DAT tSU:STA

Stop Start Start Stop

tSU:STO VIL

VIH

VIL tSP

Figure 9. I2C Bus mode Timing

tPD

VIL

PDN VIH

12. 動作説明

■

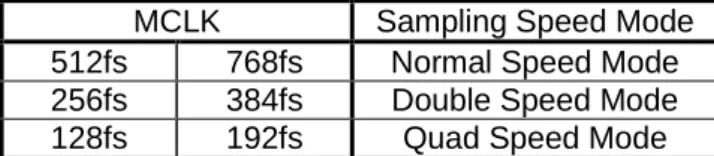

システムクロックAK4432に必要なクロックは、MCLK, LRCK, BICK です。MCLKとBICKおよびLRCKは同期する必要は ありますが位相を合わせる必要はありません。MCLK周波数を設定する方法は、DFS1-0 bitで設定する 方法 (Manual Setting Mode) とデバイス内部で自動設定する方法 (Auto Setting Mode) の2つがあります。 Manual Setting Mode (ACKS bit = “0”: Default)では、DFS1-0 bitでサンプリングスピードが設定され (Table 1)、各スピードでのMCLK周波数は自動検出され、内部クロックは適切な周波数に自動設定され ます(Table 2, Table 3, Table 4)。Auto Setting Mode (ACKS bit = “1”) では、MCLK周波数は自動検出さ れ(Table 5)、内部クロックは適切な周波数に自動設定される(Table 6)ため、DFS1-0 bitの設定は不要で す。

PDN pinを“H”にした後、MCLK、LRCKを入力することでリセット解除されます。

通常動作時にクロックの供給が停止して再度クロックが供給された場合、出力に異音が発生する可能性 がありますので、異音が問題になる場合は外部でミュートしてください。

DFS1 DFS0 Sampling Speed Mode (fs)

0 0 Normal Speed Mode 8kHz~48kHz (default) 0 1 Double Speed Mode 48kHz~96kHz

1 0 Quad Speed Mode 96kHz~192kHz

1 1 N/A -

(N/A: Not available) Table 1.サンプリングスピード (Manual Setting Mode)

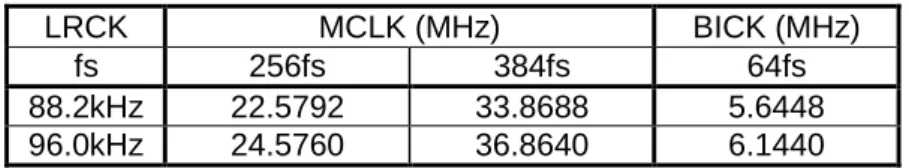

LRCK MCLK (MHz) BICK (MHz)

fs 256fs 384fs 512fs 768fs 64fs 8.0kHz 2.0480 3.0720 4.0960 6.1440 0.512 44.1kHz 11.2896 16.9344 22.5792 33.8688 2.8224 48.0kHz 12.2880 18.4320 24.5760 36.8640 3.0720

Table 2. システムクロック例 (Normal Speed Mode @Manual Setting Mode)

LRCK MCLK (MHz) BICK (MHz)

fs 256fs 384fs 64fs

88.2kHz 22.5792 33.8688 5.6448 96.0kHz 24.5760 36.8640 6.1440

Table 3. システムクロック例 (Double Speed Mode @Manual Setting Mode)

LRCK MCLK (MHz) BICK (MHz)

MCLK Sampling Speed Mode 512fs 768fs Normal Speed Mode 256fs 384fs Double Speed Mode 128fs 192fs Quad Speed Mode Table 5. サンプリングスピード (Auto Setting Mode)

LRCK MCLK (MHz) Sampling

Speed Mode fs 128fs 192fs 256fs 384fs 512fs 768fs

8.0kHz - - - - 4.0960 6.1440

Normal Speed Mode 44.1kHz - - - - 22.5792 33.8688

48.0kHz - - - - 24.5760 36.8640 88.2kHz - - 22.5792 33.8688 - -

Double Speed Mode 96.0kHz - - 24.5760 36.8640 - -

176.4kHz 22.5792 33.8688 - - - -

Quad Speed Mode 192.0kHz 24.5760 36.8640 - - - -

■

オーディオインタフェースフォーマットTDM1-0 bits, DIF2-0 bits, SDS2-0 bits, DIF pinは動作中に切り替えないでください。

SYNCE bit = “1” (default)では、前詰め/ I2Sフォーマットは使用できますが、後詰めフォーマットは使用

できません。

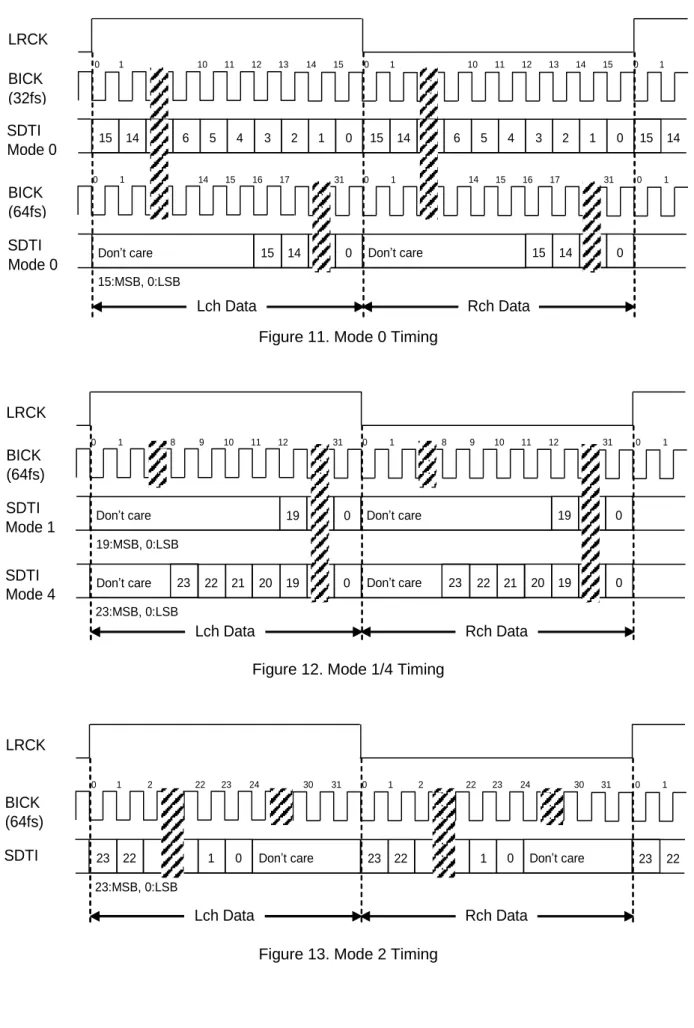

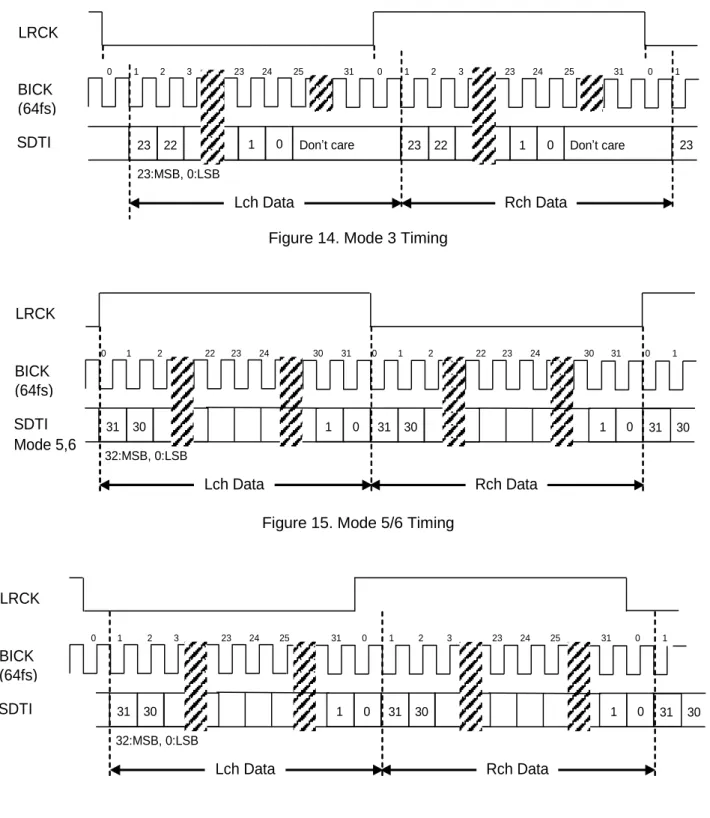

Normal Mode (TDM1-0 bit=“00”)

オーディオデータはBICKとLRCKを使ってSDTIから2ch分のデータが入力されます。8種類のデータフ ォーマット(Table 7)がDIF2-0 bitで選択できます。全モードともMSBファースト、2’sコンプリメントの

データフォーマットでBICKの立ち上がりでラッチされます。前詰め及びI2 Sファーマット設定時、デー タの最大ビットで使用しない場合には、データのないビットには“0”を入力して下さい。(例:Mode 2を 16ビットで使用する場合、後ろの8ビットには “0”を入力して下さい。) TDM128 Mode (TDM1-0 bit=“01”) オーディオデータはBICKとLRCKを使ってSDTIから4ch分のデータが入力でき、SDS1-0 bitsで選択され るデータを出力します。BICKは128fs固定です。6種類のデータフォーマット(Table 7)がDIF2-0 bitで選 択できます。全モードともMSBファースト、2’sコンプリメントのデータフォーマットでBICKの立ち上 がりでラッチされます。

TDM256 Mode (TDM1-0 bit=“1X”)

オーディオデータはBICKとLRCKを使ってSDTIから8ch分のデータが入力でき、SDS1-0 bitsで選択され るデータを出力します。BICKは256fs固定です。6種類のデータフォーマット(Table 7)がDIF2-0 bitで選 択できます。全モードともMSBファースト、2’sコンプリメントのデータフォーマットでBICKの立ち上 がりでラッチされます。

Mode TDM1 TDM0 DIF2 DIF1 DIF0 SDTI Format LRCK BICK Normal (Note 15) 0 0 0 0 0 0 16-bit 後詰め H/L 32fs 1 0 0 1 20-bit 後詰め H/L 40fs 2 0 1 0 24-bit 前詰め H/L 48fs 3 0 1 1 16-bit I 2 S 互換 L/H 32fs 24-bit I2S 互換 L/H 48fs 4 1 0 0 24-bit 後詰め H/L 48fs 5 1 0 1 32-bit 後詰め H/L 64fs 6 1 1 0 32-bit 前詰め H/L 64fs 7 1 1 1 32-bit I2S 互換 L/H 64fs TDM128 - 0 1 0 0 0 N/A 128fs - 0 0 1 N/A 128fs 8 0 1 0 24-bit 前詰め 128fs 9 0 1 1 24-bit I2S 互換 128fs 10 1 0 0 24-bit 後詰め 128fs 11 1 0 1 32-bit 後詰め 128fs 12 1 1 0 32-bit 前詰め 128fs 13 1 1 1 32-bit I2S 互換 128fs TDM256 - 1 0 0 0 0 N/A 256fs - 0 0 1 N/A 256fs 14 0 1 0 24-bit 前詰め 256fs 15 0 1 1 24-bit I2S 互換 256fs 16 1 0 0 24-bit 後詰め 256fs 17 1 0 1 32-bit 後詰め 256fs 18 1 1 0 32-bit 前詰め 256fs 19 1 1 1 32-bit I2S 互換 256fs Note 15. 各chに対して、設定したビット以上のBICKを入力してください。 Table 7. オーディオデータフォーマット(N/A: Not available)

SDTI BICK LRCK SDTI 15 14 6 5 4 BICK 0 1 10 11 12 13 14 15 0 1 10 11 12 13 14 15 0 1 3 2 1 0 15 14 (32fs) (64fs) 0 1 14 15 16 17 31 0 1 14 15 16 17 31 0 1 15 14 0 15 14 0

Mode 0 Don’t care Don’t care

15:MSB, 0:LSB

Mode 0 15 14 6 5 4 3 2 1 0

Lch Data Rch Data

Figure 11. Mode 0 Timing

SDTI LRCK BICK (64fs) 0 1 9 10 11 12 31 0 1 9 10 11 12 31 0 1 19 0 19 0

Mode 1 Don’t care Don’t care

19:MSB, 0:LSB SDTI

Mode 4

23:MSB, 0:LSB

20 19 0 20 19 0

Don’t care 22 21 Don’t care 22 21

Lch Data Rch Data

8

23 23

8

Figure 12. Mode 1/4 Timing

LRCK BICK (64fs) SDTI 0 1 2 22 24 31 0 1 31 0 1 23:MSB, 0:LSB 22 1 0 Don’t care 23 Lch Data Rch Data 23 30 2 22 23 24 30 22 1 0 Don’t care 23 23 22

LRCK BICK (64fs) SDTI 0 1 2 3 24 31 0 1 31 0 1 23:MSB, 0:LSB 22 1 0 Don’t care 23 Lch Data Rch Data 23 25 2 3 23 24 25 22 1 0 Don’t care 23 23

Figure 14. Mode 3 Timing

LRCK BICK (64fs) SDTI 0 1 2 22 24 31 0 1 31 0 1 32:MSB, 0:LSB 30 1 0 31 Lch Data Rch Data 23 30 2 22 23 24 30 30 1 0 31 31 30 Mode 5,6

Figure 15. Mode 5/6 Timing

LRCK BICK (64fs) SDTI 0 1 2 3 24 31 0 1 31 0 1 32:MSB, 0:LSB 30 1 0 31 Lch Data Rch Data 23 25 2 3 23 24 25 30 1 0 31 31 30

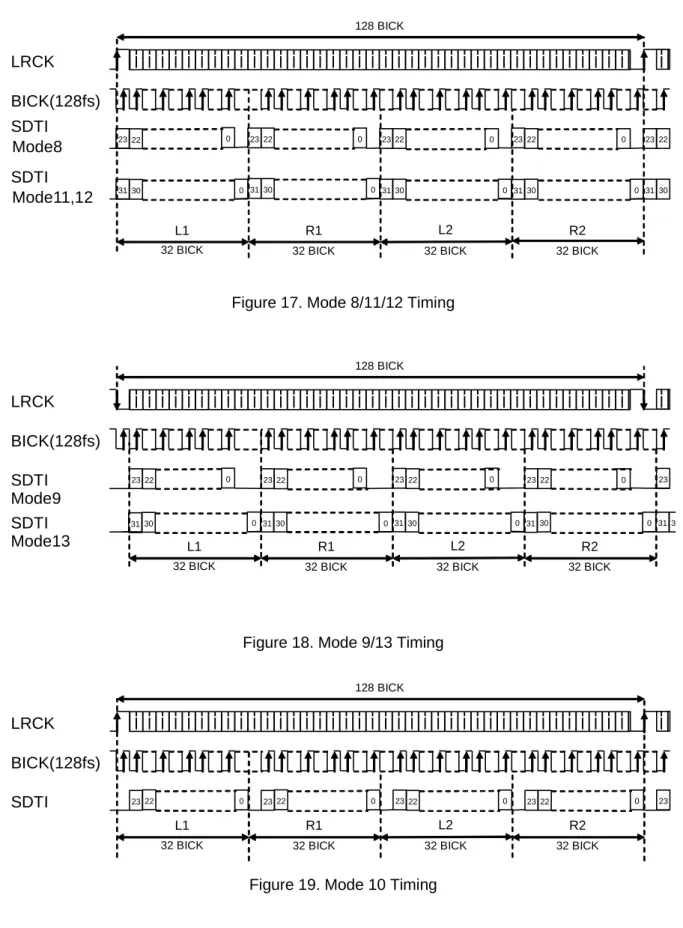

LRCK BICK(128fs) 128 BICK L1 32 BICK R1 32 BICK L2 32 BICK R2 32 BICK SDTI 22 0 22 0 22 0 22 0 23 23 23 23 23 22 Mode8 SDTI 30 0 30 0 30 2 0 30 0 31 31 31 31 31 30 Mode11,12

Figure 17. Mode 8/11/12 Timing

LRCK BICK(128fs) 128 BICK L1 32 BICK R1 32 BICK L2 32 BICK R2 32 BICK SDTI 23 22 0 23 22 0 23 22 0 23 22 0 23 SDTI Mode9 Mode13 30 0 30 0 30 2 0 30 0 31 31 31 31 31 30

Figure 18. Mode 9/13 Timing

LRCK BICK(128fs) 128 BICK L1 32 BICK R1 32 BICK L2 32 BICK R2 32 BICK SDTI 23 22 0 23 22 0 23 22 0 23 22 0 23

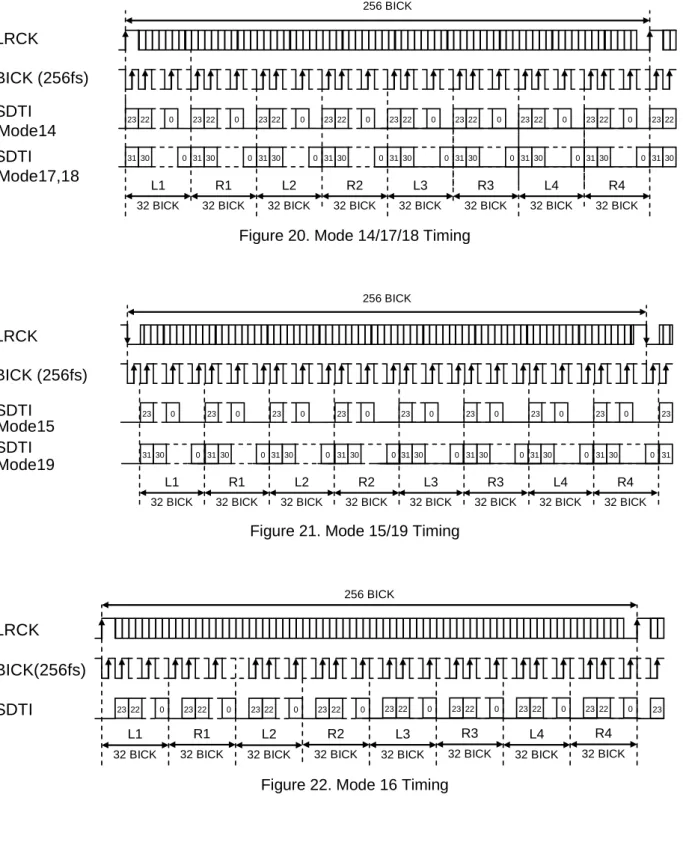

23 LRCK BICK (256fs) 22 0 L1 32 BICK 256 BICK 22 0 R1 32 BICK 22 23 22 0 23 L2 32 BICK 22 0 R2 32 BICK 23 23 SDTI 31 30 0 31 30 0 31 30 0 31 30 0 31 30 SDTI Mode14 Mode17,18 23 22 0 L3 32 BICK 22 0 R3 32 BICK 23 22 0 L4 32 BICK 22 0 R4 32 BICK 23 23 31 30 0 31 30 0 31 30 0 31 30 0

Figure 20. Mode 14/17/18 Timing

LRCK BICK (256fs) 23 0 L1 32 BICK 256 BICK 23 0 R1 32 BICK 23 23 0 L2 32 BICK 23 0 R2 32 BICK SDTI Mode15 31 30 0 31 30 0 31 30 0 31 30 0 31 SDTI Mode19 23 0 L3 32 BICK 23 0 R3 32 BICK 23 0 L4 32 BICK 23 0 R4 32 BICK 31 30 0 31 30 0 31 30 0 31 30 0

Figure 21. Mode 15/19 Timing

LRCK BICK(256fs) SDTI 256 BICK 22 0 L1 32 BICK 22 0 R1 32 BICK 22 0 L2 32 BICK 22 0 R2 32 BICK 23 23 23 23 22 0 23 L3 32 BICK 22 0 R3 32 BICK 22 0 L4 32 BICK 22 0 R4 32 BICK 23 23 23 23

データセレクト

AK4432はSDS1-0 bitで各DACの再生するデータを選択できます。

LRCK

SDTI L1 R1

Figure 23. Data Slot in Normal Mode

SDTI L1 R1

LRCK

128 BICK

R2 L2

Figure 24. Data Slot in TDM128 Mode

SDTI L1 R1 LRCK

256 BICK

R2

L2 L3 R3 L4 R4

Figure 25. Data Slot in TDM256 Mode

SDS1 SDS0 DAC1 Lch Rch Normal x x L1 R1 TDM128 x 0 L1 R1 x 1 L2 R2 TDM256 0 0 L1 R1 0 1 L2 R2 1 0 L3 R3 1 1 L4 R4 (x: don’t care) Table 8. Data Select

■

ディジタルボリューム機能AK4432はチャネル独立ディジタルボリューム(256レベル, 0.5dBステップ)を内蔵しています。入力デー タを設定されたアッテネーションレベル分だけ、設定された遷移時間で増幅、減衰します。

アッテネーションレベルはチャンネル毎にレジスタのATTL/R7-0 bitsでそれぞれ設定します(Table 9)。 DAC Lch

ATTL7-0bits

DAC Rch

ATTR7-0bits Attenuation Level

00h 00h +12.0dB 01h 01h +11.5dB 02h 02h +11.0dB : : : 17h 17h +0.5dB 18h 18h 0.0dB (default) 19h 19h -0.5dB : : : FDh FDh -114.5dB FEh FEh -115.0dB FFh FFh MUTE (-∞) Table 9. ディジタルボリュームの減衰量

ディジタルボリューム設定値間の遷移時間はATS bitで設定します(Table 10)。設定値間の遷移はソフト 遷移で、ATT Speedの1/4毎に0.125dB遷移します(Table 10)。したがって、遷移中にスイッチングノイ ズは発生しません。

Mode ATS ATT speed(遷移時間)

1 step(0.5dB) ソフト遷移(0.125dB) 0 0 4/fs 1/fs (default) 1 1 16/fs 4/fs Table 10. ディジタルボリュームの1ステップの遷移時間 00H(+12dB)からFFH(MUTE)の遷移時間は、Mode0の場合255step*4/fs+1/fs(mute分 )=1021/fs (21.3ms@fs=48kHz)かかり、Mode1の場合255step*16/fs+4/fs(mute分)=4084/fs (85.1ms@fs=48kHz)か かります。 Mode ATS 00h ⇔ FFhの遷移時間 fs表記 fs=48kHz fs=44.1kHz fs=8kHz 0 0 1021/fs 21.3ms 23.2ms 127.6ms (default) 1 1 4084/fs 85.1ms 92.6ms 510.5ms

■

ソフトミュート機能ソフトミュートはディジタル的に実行されます。SMUTE pinを“H”またはSMUTE bitを“1”にするとその 時点のATT設定値からATT設定値 ATT遷移時間で入力データが (“0”)までアテネーションされます。 SMUTE pinを“L”またはSMUTE bitを“0”にすると状態が解除され、からATT設定値 ATT遷移時間 でATT設定値まで復帰します。ATT遷移時間はATS bitで設定します。ソフトミュート開始後、までア テネーションされる前に解除されるとアテネーションが中断され、同じサイクルでATT設定値まで復帰 します。ソフトミュート機能は信号を止めずに信号源を切り替える場合などに有効です。 SMUTE pin or SMUTE bit Attenuation ATT_Level - AOUT GD GD (1) (2) (3) (1) (2) 注: (1) ATT設定値 ATT遷移時間。例えば、ATT設定値が“255”の場合は1020LRCKサイクルです。 (2) ディジタル入力に対するアナログ出力は群遅延(GD)をもちます。 (3) ソフトミュート開始後、までアテネーションされる前に解除されるとアテネーションが中断さ れ、同じサイクルでATT設定値まで復帰します。 Figure 26. ソフトミュート機能とゼロ検出機能

■

エラー検出 AK4432はエラー発生時に自動で動作を停止する機能を有しています。(Table 12)に示す3項目のエラー が検出されるとLDOがパワーダウンし、レジスタへのアクセスができなくなり、ディジタル回路の動作 が停止します。エラーの原因が解決されても自動復帰はしないため、PDN pin = “L”で一旦リセットして から、再立ち上げを行ってください。 I2C使用時は、エラーが発生するとACKが返らなくなります。 No エラー項目 エラー判定条件 1 内部リファレンス電圧エラー 内部リファレンス電圧が立ち上がらない2 LDO過電圧検出 LDO電圧 > 1.6V (Typ) 3 LDO過電流検出 LDO電流< 100mA (Typ)

Table 12. エラー検出

■

システムリセット電源 ON 時には、PDN pinに一度 “L” を入力してリセットして下さい。LDO, VCOMなど基準電圧のパワ ーダウンはPDN pin = “H”で解除され、その後1ms以降にレジスタの書き込みが可能になります。DACは MCLKおよびLRCKが入力された後、パワーアップします。MCLKおよびLRCK が入力されるまではパワ ーダウン状態です。

■

パワーダウン機能 PDN pinを“L”にするとパワーダウン状態になり、アナログ出力はフローティング状態(Hi-Z)になります。 Figure 27にパワーダウン及びパワーアップ時のシステムタイミング例を示します。 PDN pin Power Reset Normal Operation(レジスタお書き込み、DAC入力可能)Clock In MCLK,LRCK,BICK DAC In (Digital) DAC Out (Analog) External Mute (7) Mute ON Don’t care “0”data GD (3) (5) (6) GD (5) Mute ON “0”data Don’t care Internal State (4) (4) (1) Internal PDN (2) LDOO pin 注: (1) AVDD, LVDD立ち上げと、PDNピンを800ns間 “L” にしてください。 (2) パワーアップ後、REF発生回路(アナログ基準電圧源)、LDO(内部ディジタル駆動用電源) が立ち上がります。また、コントロールレジスタが初期化されます。コントロールレジスタへ の設定はPDN pin=“H”から1ms以上後に行ってください。 (3) ディジタル入力に対してアナログ出力は群遅延(GD)を持ちます。 (4) パワーダウン時、アナログ出力はHi-Zです。 (5) PDN信号のエッジ(“”)でクリックノイズが出力されます。このノイズはデータが“0”の場合で も出力されます。 (6) パワーダウン状態(PDN pin = “L”)では各クロック入力(MCLK, BICK, LRCK)を止めることができ ます。 (7) クリックノイズ(5)が問題になる場合はアナログ出力を外部でミュートして下さい。タイミング

■

パワーオフ、リセット機能PMDA DAC レジスタ アナログ出力

0 OFF 保持 Hi-Z

1 ON 保持 Normal (default)

Table 13. Power OFF and Reset Function パワーオフ機能 (PMDA bit) PMDA bitを“0”に設定するとDACが瞬時にパワーオフ状態になります。このとき、レジスタ以外の全て の回路がパワーダウン状態となり、アナログ出力はフローティング状態(Hi-Z)になります。Figure 28に パワーオフ及びパワーオン時のシステムタイミング例を示します。 Normal Operation Internal State PMDA bit

Power-off Normal Operation

GD GD “0” data D/A Out (Analog) D/A In (Digital) Clock In MCLK, BICK, LRCK (1) (3) External MUTE (5) (3) (1) Mute ON (2) (4) Don’t care 注: (1) ディジタル入力に対するアナログ出力は群遅延(GD)を持ちます。 (2) パワーオフ時、アナログ出力はHi-Zです。 (3) 内部PMDA信号のエッジ(“”)でクリックノイズが出力されます。このノイズはデータが“0”の 場合でも出力されます。

(4) パワーオフ状態(PMDA bit= “0”)では各クロック入力(MCLK, BICK, LRCK)を止めることができま す。

(5) クリックノイズ(3)が問題になる場合はアナログ出力を外部でミュートして下さい。タイミング 例を示します。

■

クロック同期化機能AK4432はAK7738のDAC出力との位相差を13/256fsの範囲内になるよう、内部カウンタをリセットする 機能を備えています。同期化機能はSYNCE-bitを “1”に設定することで動作します(default= “1”)。SYNCE bitの切替えは、データがALL “0”(無入力)のときに行ってください。

SYNCE bit = “1”に設定すると、オーディオインタフェースフォーマットは前詰め、32-bit I2S 互換に 制限されます。後詰めフォーマットは使用できません。 (1) AK7738との同期化 クロック同期化機能により、以下のユースケース(Figure 29)にて、AK7738のDAC出力とAK4432の DAC出力の位相を13/256fs以内に合わせることができます。 ケース1 ケース2 Figure 29. AK7738との同期化可能な接続方法

注:AK7738と同期させる場合は、AK7738, AK4432共に、BICK=64fs, 32bit前詰め(DIF2-0= “110”) に設 定してください。

LRCK[kHz] BICK[fs] MCLK[fs] MCLK[MHz] 位相差[1/MCLK] 位相差[µs] 位相差[deg] 標準速 48 64 256 12.288 7 ~ 13 0.57 ~ 1.06 4.1 ~ 7.6

■

パラレルモード AK4432はPS pin= “H”の時、ピン設定で制御可能なパラレルモードになります。パラレルモードではレ ジスタ設定が必要な機能は使用できませんが、以下の3つの機能はピン設定により、使用することが可 能です。 ピンで設定できない機能は、レジスタのdefault設定で動作します。 (1) オーディオインターフェースDIF pinにより、オーディオインタフェースモードを設定できます(Table 15)。使用できるモードは32-bit 前詰め (DIF pin = “L”) と32-bit I2S 互換 (DIF pin = “H”) の2モードになります。

DIF pin Mode

L Mode6(Table 7) H Mode7(Table 7) Table 15. オーディオデータフォーマット

(2)ソフトミュート

SMUTE pin によりSMUTE信号を制御することにより、ソフトミュート機能を使用できます(Figure 26)。

(3) システムクロック

ACKS pin を “H”とすることで、Auto Setting Modeに設定することができます。ACKS pin が “L”のとき は、Manual Setting Modeに設定されます。但し、Normal Speed Mode固定です(Table 16)。Table 15の MCKI周波数を入力してください。

ACKS pin MCKI Sampling Speed Mode

L 768fs, 512fs, 384fs, 256fs Normal Speed Mode H 512fs, 768fs Normal Speed Mode H 256fs, 384fs Double Speed Mode

H 128fs, 192fs Quad Speed Mode

■

シリアルコントロールインタフェースAK4432は3線シリアルとI2Cの両方のインタフェースに対応しています。パワーダウン解除後はI2Cイン タフェースとして動作します。3線シリアルコントロールモードで使用したい場合は、CSN pinが“H”の 状態で、パワーダウンを解除し、下記のダミーコマンドを4回連続で発行することで使用可能になりま す。(Figure 30)

ダミーコマンドは、CSN pin = “L”期間中に、CDTI pinから“0xDE → 0xADDA → 0x7A”を入力します。 データはMSBファーストです。(Figure 30)

CSN

CCLK

CDTI don’tcare (L/H) 0xDE (8bit) 0xADDA (16bit) 0x7A(8bit)

don’tcare (L/H) CSN CCLK CDTI ダミーコマンド ダミーコマンド ダミーコマンド ダミーコマンド Figure 30. ダミーコマンドフォーマット

(1) 3線シリアルコントロールモード

このモードでは3線式シリアルI/F pin: CSN, CCLK, CDTIで書き込みを行います。I/F上のデータは Command Code (8bit, 最上位bitはR/Wフラグで“1”固定(Write only), 残りの7bitは“1000000”固定), Register Address (MSB first, 16bit)とControl Data (MSB first, 8bit)で構成されます(Figure 31)。データ送 信側はCCLKの“”で各ビットを出力し、受信側は“”で取り込みます。データの書き込みはControl Data 8bit目のCCLKの“”で有効になります。CCLKのクロックスピードは7MHz (max)です。

AK4432はControl Dataを連続で書き込むことができます(Figure 35)。データを1バイト送った後、停止 条件を送らず更にデータを送ると、Register Addressが自動的にインクリメントされ、次のデータは次 のサブアドレスに格納されます。アドレス “05H”にデータを書き込んだ後、さらに次のアドレスに書き 込んだ場合にはアドレス“00H”にデータが書き込まれます。 PDN pinを“L”にすると内部レジスタ値が初期化されます。 CSN CCLK

CDTI don’tcare (L/H) Command Code (8bit) Register Address (16bit) Control Data (8bit)

don’tcare (L/H)

Figure 31. Control I/F Timing

R/W 1 0 0 0 0 0 0

R/W: READ/WRITE (Fixed to “1”, Write only) Figure 32. Command Code の構成

0 0 0 0 0 0 0 0 0 0 0 0 0 A2 A1 A0 Figure 33. Register Address の構成

D7 D6 D5 D4 D3 D2 D1 D0

Figure 34. Control Data の構成 * 3線シリアルモードはデータ読み出しをサポートしません。

* PDN pin = “L”時は、コントロールレジスタへの書き込みはできません。

(2) I2Cバスコントロールモード

AK4432のI2Cバスモードのフォーマットは、高速モード(max: 400kHz)と高速モードプラス(max: 1MHz) に対応しています(Table 17)。使用中、I2Cバスモードのフォーマットは高速モードか高速モードプラス のどちらか固定としてください。高速モードと高速モードプラスの切替は、PDN =“L”の時に行ってくだ さい。 SMUTE/CSN/I2CFIL pin バスモード L 高速モード H 高速モードプラス Table 17. I2Cバスモード設定 (1) WRITE命令 I2Cバスモードにおけるデータ書き込みシーケンスはFigure 36に示されます。バス上のICへのアクセス には、最初に開始条件 (Start Condition) を入力します。SCLラインが “H”の時にSDAラインを “H”から “L” にすると、開始条件が作られます(Figure 44)。開始条件の後、スレーブアドレスが送信されます。この アドレスは上位7ビットで構成され、“0011001”になります。8ビット目にはデータ方向ビット(R/W) が 続きます (Figure 37)。アドレスが一致した場合、AK4432は確認応答 (Acknowledge) を生成し、命令が 実行されます。マスタは確認応答用のクロックパルスを生成し、SDAラインを解放しなければなりませ ん(Figure 45)。R/W bitが “0”の場合はデータ書き込み、R/W bitが “1”の場合はデータ読み出しを行いま す。 第2バイトはコマンドコードです。コマンドコードは8ビット、MSB firstで構成され、“11000000”固定で す。 第3, 4バイトはサブアドレス(レジスタアドレス)です。サブアドレスは16bit (第3, 4バイトでそれぞれ8 ビットずつ) 、MSB firstで構成され、第3バイトは全ビット”0”固定、第4バイトの上位5ビットは “0”固定 です(Figure 38)。第5バイト以降はコントロールデータです。コントロールデータは8ビット、MSB first で構成されます(Figure 41)。AK4432は、各バイトの受信を完了するたびに確認応答を生成します。デ ータ転送は、必ずマスタが生成する停止条件 (Stop Condition) によって終了します。SCLラインが “H” の時にSDAラインを “L”から “H”にすると、停止条件が作られます(Figure 44)。 AK4432は複数のバイトのデータを一度に書き込むことができます。データを1バイト送った後、停止条 件を送らず更にデータを送ると、サブアドレスが自動的にインクリメントされ、次のデータは次のサブ アドレスに格納されます。アドレス “05H”にデータを書き込んだ後、さらに次のアドレスに書き込んだ 場合にはアドレス“00H”にデータが書き込まれます。 クロックが “H”の間は、SDAラインの状態は一定でなければなりません。データラインが “H”と “L”の間 で状態を変更できるのは、SCLラインのクロック信号が “L”の時に限られます(Figure 46)。SCLラインが “H”の時にSDAラインを変更するのは、開始条件、停止条件を入力するときのみです。

SDA Slave Command

R/W=”0” T R S A T S T O P

0 0 1 1 0 0 1 R/W R/W: READ/WRITE (“0”: Write, “1”: Read)

Figure 37. 第1バイトの構成 1 1 0 0 0 0 0 0 Figure 38. 第2バイトの構成 0 0 0 0 0 0 0 0 Figure 39. 第3バイト以降の構成 0 0 0 0 0 A2 A1 A0 Figure 40. 第4バイト以降の構成 D7 D6 D5 D4 D3 D2 D1 D0 Figure 41. 第5バイト以降の構成

(2) READ命令 第一バイト目に書き込みスレーブアドレス(R/W bit = “0”) 指定を受信すると(Figure 37)、第二バイト目 にコマンドコード“01000000”(Figure 43)、第三、第四バイト目にアドレスを受信します(Figure 39, Figure 40)。第四バイトを受信し、アクノリッジを送信したらリスタートコンディションを受信します。 その後第一バイト目に読み出しスレーブアドレス(R/W bit = “1”) 指定を受信すると、第二バイト目以降 に、データの送信を行います。データが出力された後、マスタが確認応答を生成せず停止条件を送ると、 READ動作は終了します。

SDA Command Code Address(0) Address(1) P

R/W=”0” T R S A T A C K A C K A C K A C K S T O P S AddressSlave R/W=”1” E A S T R T R Data(0) Data(1) A C K A C K

S AddressSlave Data(n)

A C K A C K M T A S E R M T A S E R M T A S E R M T A S E R N A C K Figure 42. ランダムアドレスリード 0 1 0 0 0 0 0 0 Figure 43. 第2バイトの構成(READ時)

SCL SDA stop condition start condition S P Figure 44. 開始条件と停止条件 SCL FROM MASTER acknowledge DATA OUTPUT BY TRANSMITTER DATA OUTPUT BY RECEIVER 1 8 9 START CONDITION not acknowledge

clock pulse for acknowledgement S 2 Figure 45. I2Cバスでの確認応答 SCL SDA data line stable; data valid change of data allowed

■

レジスタマップAddr Register Name D7 D6 D5 D4 D3 D2 D1 D0

00H Power Management 0 0 0 0 0 0 PMDA 0

01H Control 1 0 0 0 0 0 DFS1 DFS0 ACKS

02H Data interface 0 SDS1 SDS0 TDM1 TDM0 DIF2 DIF1 DIF0

03H Control 2 0 0 0 DASL DASD ATS SMUTE SYNCE

04H AOUTL Volume Control ATTL7 ATTL6 ATTL5 ATTL4 ATTL3 ATTL2 ATTL1 ATTL0 05H AOUTR Volume Control ATTR7 ATTR6 ATTR5 ATTR4 ATTR3 ATTR2 ATTR1 ATTR0 Note 17. アドレス06HFFHは書き込み不可です。

Note 18. “0”で指定されたビットへの “1”の書き込みは禁止です。 Note 19. PDN pin を “L” にすると、レジスタ値は初期化されます。

■

詳細説明Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 00H Power Management 0 0 0 0 0 0 PMDA 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 0 0 1 0

PMDA: DACのパワーマネジメント 0: パワーダウン。

1: 通常動作。

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0

01H Control 1 0 0 0 0 0 DFS1 DFS0 ACKS

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 0 0 0 0

ACKS: クロック自動認識モード有効 0: 無効, Manual Setting Mode 1: 有効, Auto Setting Mode

ACKS= “1”のとき、MCLK周波数は自動検出されます。この場合DFSの設定は無視されま す。ACKS= “0”のとき、サンプリングスピードモードはDFS0, 1で設定し、各モードでの MCLK周波数は自動検出されます。

DFS1-0: サンプリングスピードコントロール(Table 1) ACKS bit= “1”のとき、DFSの設定は無視されます。

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 02H Data interface 0 SDS1 SDS0 TDM1 TDM0 DIF2 DIF1 DIF0

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 0 1 1 0

DIF2-0: オーディオインターフェースフォーマットモード選択(Table 7) Default: “110” (32bit 前詰め)

TDM1-0: TDMフォーマット選択 Default: “00” (Stereo Mode)

Mode TDM1 TDM0 Sampling Speed Mode

0 0 0 Stereo mode (Normal, Double, Quad Speed Mode) 1 0 1 TDM128 mode (Normal, Double, Quad Speed Mode) 2 1 0 TDM256 mode (Double, Quad Speed Mode)

Addr Register Name

D7 D6 D5 D4 D3 D2 D1 D0

03H Control 2 0 0 0 DASL DASD ATS SMUTE SYNCE

R/W R/W R/W R/W R/W R/W R/W R/W R/W Default 0 0 0 0 0 0 0 1 SYNCE: 同期機能有効 0: OFF 1: ON (default) SMUTE: ソフトミュート機能有効 0: 通常動作(default) 1: DAC出力がソフトミュートされます。 ATS: ディジタルアテネータ遷移時間設定 (Table 10) Default: “0”

DASD: Digital filter setting for DAC

0: Sharp roll off filter or Slow roll off filter (default)

1: Short Delay sharp roll off filter or Short Delay slow roll off filter DASL: SLow Roll-off filter enable for DAC

0: Sharp roll-off filter (default) 1: SLow roll-off filter

DASD bit DASL bit Mode

0 0 Sharp roll-off filter (default) 0 1 SLow roll-off filter

1 0 Short Delay sharp roll-off filter 1 1 Short Delay SLow roll-off filter

Table 18 Digital Filter setting for DAC

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 04H AOUTL Volume Control ATTL7 ATTL6 ATTL5 ATTL4 ATTL3 ATTL2 ATTL1 ATTL0 05H AOUTR Volume Control ATTR7 ATTR6 ATTR5 ATTR4 ATTR3 ATTR2 ATTR1 ATTR0

R/W R/W R/W R/W R/W R/W R/W R/W R/W Default 0 0 0 1 1 0 0 0 ATTL7-0: DAC Lch アテネーションレベル Default:18(0dB) ATTR7-0: DAC Rch アテネーションレベル Default:18(0dB)

13. 外部接続回路例 MCLK 1 BICK 2 SDTI 3 LRCK 4 PDN 5 SMUTE/CSN/I2CFIL 6 ACKS/CCLK/SCL 7 DIF/CDTI/SDA 8 LDOO 16 LVDD 15 AVDD 14 VSS 13 VCOM 12 AOUTL 11 AOUTR 10 PS 9 μP AK4432 2.2u 0.1u + Rch Out Lch Out MUTE Analog Ground Digital Ground Analog Supply 3.0 to 3.6V 10u Audio Controller LDO Supply 3.0 to 3.6V 0.1u + 10u 1.0u 1.0u 1.0u AVDD or VSS に接続 Figure 47. システム接続例 (P/S pin = “H”) MCLK 1 BICK 2 SDTI 3 LRCK 4 PDN 5 SMUTE/CSN/I2CFIL 6 ACKS/CCLK/SCL 7 DIF/CDTI/SDA 8 LDOO 16 LVDD 15 AVDD 14 VSS 13 VCOM 12 AOUTL 11 AOUTR 10 PS 9 μP AK4432 2.2u 0.1u + Rch Out Lch Out MUTE Analog Ground Digital Ground Analog Supply 3.0 to 3.6V 10u Audio Controller LDO Supply 3.0 to 3.6V 0.1u + 10u 1.0u 1.0u 1.0u Figure 48. システム接続例 (P/S pin = “L”)

1. グランドと電源のデカップリング 電源とグランドの取り方には十分注意して下さい。VSSはアナロググランドに接続して下さい。小容量 のデカップリングコンデンサはなるべく電源ピンの近くに接続して下さい。 2. 基準電圧入力 VCOMはAVDDx1/2電圧を出力しており、アナログ信号のコモン電圧として使われます。このピンには 高周波ノイズを除去するために2.2F ±50% (温度特性を含む) のセラミックコンデンサをVSSとの間に 接続して下さい。セラミックコンデンサはピンに出来るだけ近づけて接続して下さい。VCOM pinから 電流を取ってはいけません。また、ディジタル信号、特にクロック信号は変調器へのカップリングを避 けるためVCOMからできるだけ離して下さい。 LDOOは1.2Vの電圧を出力しており、内部ディジタル回路を駆動するための電源として使われます。こ のピンには、LDOを安定化させるために1F ±50% (温度特性を含む) のセラミックコンデンサをVSSと の間に接続してください。セラミックコンデンサはピンに出来るだけ近づけて接続して下さい。LDOO pinから電流を取ってはいけません。 3.アナログ出力 DAC出力の出力レンジはVCOM電圧を中心に0.86xAVDD Vpp(typ)です。入力コードのフォーマットは 2’sコンプリメント(2の補数)で、7FFFFFFFH(@32bit)に対しては正のフルスケール、 80000000H(@32bit)に対しては負のフルスケール、00000000H(@32bit)での理想値はVCOM電圧が出力 されます。ΔΣ変調器が発生する帯域外ノイズ(シェーピングノイズ)はシングルエンド出力時には内蔵 のスイッチトキャパシタフィルタ(SCF)と連続フィルタ(CTF)で除去されます。 本LSIのアナログ出力はVCOM電圧に対して数mV程度のオフセットを持つため通常の使用ではコンデ ンサでDC成分をカットします。

14. パッケージ

■

外形寸法図16-pin TSSOP (Unit: mm)

■

材質・メッキ仕様■

マーキングAKM

4432

XXYYY

1) Pin #1 indication

2) Date Code: XXXX (4 digits) 3) Marking Code: 4432

15. 改訂履歴 Date (Y/M/D) Revision Reason Page Contents

重要な注意事項 0. 本書に記載された弊社製品(以下、「本製品」といいます。)、および、本製品の仕様につ きましては、本製品改善のために予告なく変更することがあります。従いまして、ご使用を 検討の際には、本書に掲載した情報が最新のものであることを弊社営業担当、あるいは弊社 特約店営業担当にご確認ください。 1. 本書に記載された情報は、本製品の動作例、応用例を説明するものであり、その使用に際し て弊社および第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うもの ではありません。お客様の機器設計において当該情報を使用される場合は、お客様の責任にお いて行って頂くとともに、当該情報の使用に起因してお客様または第三者に生じた損害に対 し、弊社はその責任を負うものではありません。 2. 本製品は、医療機器、航空宇宙用機器、輸送機器、交通信号機器、燃焼機器、原子力制御用 機器、各種安全装置など、その装置・機器の故障や動作不良が、直接または間接を問わず、 生命、身体、財産等へ重大な損害を及ぼすことが通常予想されるような極めて高い信頼性を 要求される用途に使用されることを意図しておらず、保証もされていません。そのため、別 途弊社より書面で許諾された場合を除き、これらの用途に本製品を使用しないでください。 万が一、これらの用途に本製品を使用された場合、弊社は、当該使用から生ずる損害等の責 任を一切負うものではありません。 3. 弊社は品質、信頼性の向上に努めておりますが、電子製品は一般に誤作動または故障する場 合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により、生命、身体、財産 等が侵害されることのないよう、お客様の責任において、本製品を搭載されるお客様の製品に 必要な安全設計を行うことをお願いします。 4. 本製品および本書記載の技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、ある いはその他軍事用途の目的で使用しないでください。本製品および本書記載の技術情報を輸出ま たは非居住者に提供する場合は、「外国為替及び外国貿易法」その他の適用ある輸出関連法 令を遵守し、必要な手続を行ってください。本製品および本書記載の技術情報を国内外の法 令および規則により製造、使用、販売を禁止されている機器・システムに使用しないでくだ さい。 5. 本製品の環境適合性等の詳細につきましては、製品個別に必ず弊社営業担当までお問合せく ださい。本製品のご使用に際しては、特定の物質の含有・使用を規制するRoHS指令等、適用 される環境関連法令を十分調査のうえ、かかる法令に適合するようにご使用ください。お客