概要

こ のア プ リ ケーシ ョ ン ノ ー ト では、 ザ イ リ ン ク ス 7 シ リ ーズ FPGA が備え る 専用の SelectIO™ イ ン タ ーフ ェ イ ス シ リ ア ラ イ ザー (OSERDESE2) コ ン ポーネ ン ト を使用 し 、シ リ アル LVDS (低電圧差動信 号) 入力を用いてデジ タ ルアナ ロ グコ ンバー タ ー (DAC) と 接続す る 方法を説明 し ます。 リ フ ァ レ ン ス デザ イ ンは、 高速パ ラ レル LVDS 入力を備え た DAC へ Kintex-7 FPGA を接続す る 基本の LVDS イ ン タ ーフ ェ イ ス と な っ てい ます。は じ めに

一般的な DAC は、12、14、 ま たは 16 ビ ッ ト の分解能を提供 し 、 シ ン グルパ ッ ケージ内に複数の コ ン バー タ ーが含まれてい ます。 パ ッ ケージ内の各 コ ンバー タ ーは個別の入力を使用 し ます。 各入力セ ッ ト は、 イ ン タ ー リ ーブデー タ サプ ラ イ と 呼ばれ る 1 つま たは複数のデー タチ ャ ネルを備え てい ます。 こ こ では、OSERDESE2 の高い汎用性 と 柔軟性について説明 し ます。 大半の コ ンバー タ ーは、SPI (シ リ アルペ リ フ ェ ラ ルイ ン タ ーフ ェ イ ス) を使用 し て動作モー ド を設定 し ます。FPGA の SelectIO イ ン タ ー フ ェ イ ス は、OSERDESE2 と し て構成 さ れ ま す。 各 OSERDESE2 には、

FPGA ロ ジ ッ ク か ら 最大 8 ビ ッ ト が与え ら れます。 ま た各 OSERDESE2 は、 接続 さ れ る DAC にシ ン

グルデー タ レー ト (SDR) ま たはダブルデー タ レー ト (DDR) モー ド でパ ラ レルデー タ のシ リ アル ス

ト リ ーム を供給 し ます。

FPGA

の リ ソ ース

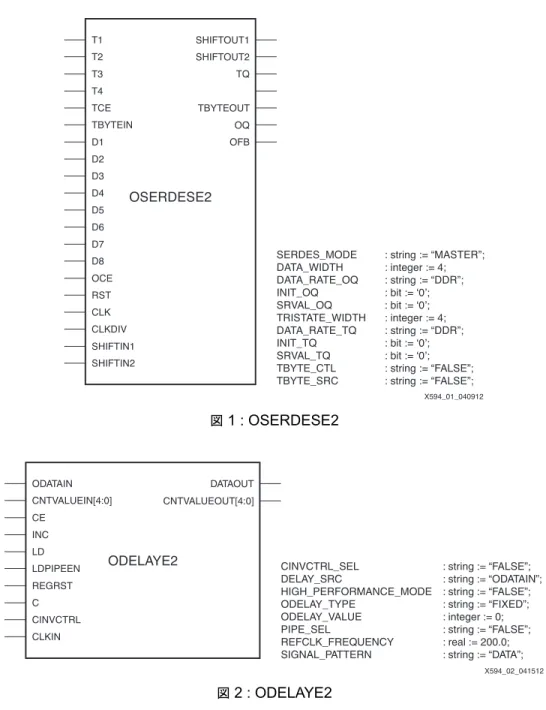

7 シ リ ーズFPGA には、HR (High Range) I/O バン ク と HP (High Performance) I/O バン ク があ り ます。 こ れ ら のバン ク の詳細は、『7 シ リ ーズ FPGA SelectIO リ ソ ースユーザーガ イ ド 』[参照1]を参照 し て く だ さ い。DAC イ ン タ ーフ ェ イ ス で重要な点は、OSERDESE2 と ODELAYE2 コ ン ポーネ ン ト は HP I/O バン ク 内でのみ使用で き る と い う こ と です。ODELAYE2 コ ン ポーネ ン ト がない OSERDESE2 コ ン ポーネ ン ト は、HR I/O バン ク 内で使用で き ます。 こ のアプ リ ケーシ ョ ン ノ ー ト では、OSERDESE2 (図1) と ODELAYE2 (図2) の両方の属性を持つシ ン ボルを記載 し てい ます。 こ れ ら の コ ン ポーネ ン ト に関す る 詳細は、 『 7 シ リ ーズ FPGA SelectIO リ ソ ー ス ユーザーガ イ ド 』 (UG471) [参照1]を参照 し て く だ さ い。 ア プ リ ケーシ ョ ン ノ ー ト : 7 シ リ ーズ FPGA XAPP594 (v1.0) 2012 年 8 月 22 日パラ レル

LVDS

高速

DAC

イ ン タ ー フ ェ イ ス

著者 : Marc DefossezDAC LVDS

イ ン

タ ー フ ェ イ ス

一般的に、 高速 DAC は、 イ ン タ ーフ ェ イ ス コ ン ポーネ ン ト で使用 さ れ る ク ロ ッ ク を出力 し ます。 イ ン タ ーフ ェ イ ス コ ン ポーネ ン ト (すなわち、FPGA) は、 受信 し た ク ロ ッ ク の レー ト でデー タ と ク ロ ッ ク を 供給す る こ と が要求 さ れます。FPGA か ら DAC に送 ら れ る デー タ と ク ロ ッ ク は、 位相が揃え ら れた信 号 と し て現れ る か、 デー タ に対 し て 90° 位相シ フ ト さ れた信号 と し て現れます。 大半の高速 DAC には、 イ ン タ ー リ ーブ形式のデー タ が必要です。 し たが っ て、 少な く と も 2 つの I/Oバン ク が必要です。DAC か ら 出力 さ れ る ク ロ ッ ク は、CC (ク ロ ッ ク 兼用) I/O (_CC_IO) を介 し て FPGA

内の MMCM (ミ ッ ク ス ド モー ド ク ロ ッ クマネージ ャ ー) に供給 さ れます。 こ の方式には次の よ う な利点があ り ます。 • 入力 さ れ る DAC の ク ロ ッ ク にジ ッ タ ーがあ る 場合、MMCM はジ ッ タ ーを低減す る 。 • MMCM は DAC イ ン タ ーフ ェ イ ス に必要なすべての ク ロ ッ ク を供給で き る 。 • MMCM は必要に応 じ て、外部フ ィ ー ド バ ッ クループ を介 し て PCB 上の DAC の入力ピ ン で DAC に供給 さ れ る デー タ の位相を揃え る か、 ま たはシ フ ト (90° な ど) で き る 。

X-Ref Target - Figure 1

図 1 : OSERDESE2

X-Ref Target - Figure 2

図 2 : ODELAYE2 X594_01_040912 T1 T2 T3 T4 TCE TBYTEIN

SERDES_MODE : string := “MASTER”; DATA_WIDTH : integer := 4; DATA_RATE_OQ : string := “DDR”; INIT_OQ : bit := ‘0’; SRVAL_OQ : bit := ‘0’; TRISTATE_WIDTH : integer := 4; DATA_RATE_TQ : string := “DDR”; INIT_TQ : bit := ‘0’; SRVAL_TQ : bit := ‘0’; TBYTE_CTL : string := “FALSE”; TBYTE_SRC : string := “FALSE”;

D1 D2 D3 D4 D5 D6 D7 D8 OCE RST CLK CLKDIV SHIFTIN1 SHIFTIN2 SHIFTOUT1 SHIFTOUT2 OSERDESE2 TQ TBYTEOUT OQ OFB X594_02_041512 ODATAIN CNTVALUEIN[4:0] CE INC LD

LDPIPEEN CINVCTRL_SEL : string := “FALSE”;

DELAY_SRC : string := “ODATAIN”; HIGH_PERFORMANCE_MODE : string := “FALSE”; ODELAY_TYPE : string := “FIXED”; ODELAY_VALUE : integer := 0; PIPE_SEL : string := “FALSE”; REFCLK_FREQUENCY : real := 200.0; SIGNAL_PATTERN : string := “DATA”;

REGRST C CINVCTRL CLKIN DATAOUT ODELAYE2 CNTVALUEOUT[4:0]

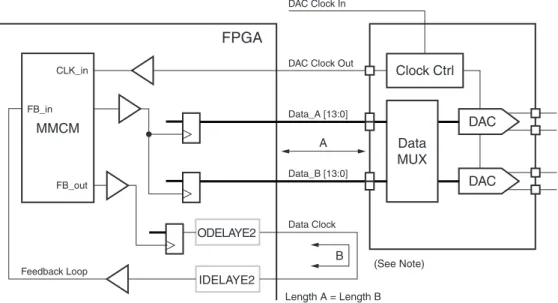

DAC LVDS イ ン タ ー フ ェ イ ス 図3に、 基本的な DAC イ ン タ ーフ ェ イ ス のセ ッ ト ア ッ プ を示 し ます。DAC の分解能が 10 ビ ッ ト よ り 大 き い場合、 こ の イ ン タ ーフ ェ イ ス は 2 つの I/O バン ク を必要 と し ます。1 つの I/O バン ク は最大 24 の 差動 I/O を持つ こ と がで き ます。分解能 14 ビ ッ ト の DAC が イ ン タ ー リ ーブデー タ を必要 と す る 場合、 2 つの I/O バン ク が必要です。 MMCM は I/O バ ン ク の後の FPGA ロ ジ ッ ク の近 く に配置 さ れ、 必要 な ク ロ ッ ク 領域に対応 し ま す (RLOC ま たは LOC 属性が必要な場合があ る)。 大半の DAC イ ン タ ーフ ェ イ ス には、 外部フ ィ ー ド バ ッ ク ループは不要です。DAC は、 位相が揃え ら れた、 ま たは 90° シ フ ト さ れた ビ ッ ト ク ロ ッ ク を持つデー タ を FPGA か ら 取得 し ます。 こ の フ ィ ー ド バ ッ ク ループは、OSERDESE2 コ ン ポーネ ン ト を使用 し て設計で き ます (7ページの 「DAC への ビ ッ ト ク ロ ッ ク 」 を参照)。 一部の DAC はデー タ のみを取得 し ます。 こ のデー タ は、DAC の ピ ン ま で イ ン タ ーフ ェ イ スデザ イ ン でモニ タ リ ン グす る 必要があ り ます。 こ の場合は、PCB 上の MMCM フ ィ ー ド バ ッ クループが必要で す (図4)。 こ れは、LVDS 用に構成 さ れた I/O を最善の位置 と な る 両方の I/O バン ク の中間 (上のバン ク の一番下の I/O ま たは下のバン ク の一番上の I/O) に配置す る こ と で実現で き ます。PCB 上の フ ィ ー ド バ ッ ク パ ス は、 使用す る DAC に応 じ て、FPGA 出力ピ ンか ら DAC 入力ピ ン ま でのデー タ 接続 と 同 じ 長 さ ま たは 2 倍の長 さ にす る 必要があ り ます。 フ ィ ー ド バ ッ ク 信号は、LVDS 用に構成 さ れた ク ロ ッ

ク 兼用 I/O を介 し て FPGA に戻 さ れます。

X-Ref Target - Figure 3

図 3 : 基本的な DAC イ ン タ ー フ ェ イ スのセ ッ ト ア ッ プ X594_03_060612 MMCM Data MUX Clock Ctrl DAC DAC

FPGA

CLK_in FB_in FB_out Feedback Loop Data Clock Data_B [13:0] Data_A [13:0] DAC Clock Out DAC Clock In注記 : 一部の DAC デバ イ ス には、DAC 入力ピ ン上の ク ロ ッ ク に基づいてデー タ の到達を調整す る ク ロ ッ ク 調整機能が さ ら に追加 さ れてい ます。 ク ロ ッ ク 入力お よ び出力を持つ DAC 内の遅延バ ッ フ ァ ー は、SPI ポー ト を 介 し て 調整可能です。 こ のバ ッ フ ァ ーは、 ク ロ ッ ク フ ィ ー ド バ ッ ク ループ内で、 ODELAYE2 ま たは IDELAYE2 コ ン ポーネ ン ト 、 あ る いはその両方の代わ り に使用で き ます。 動的遅延調整な ど の機能 も FPGA に追加で き ます。図5に、 ク ロ ッ ク フ ィ ー ド バ ッ ク の出力パ ス内の ODELAYE2 と 入力パ ス内の IDELAYE2 を示 し ます。 両方の コ ン ポーネ ン ト 、 ま たはいずれか一方の コ ン ポーネ ン ト を使用で き ま す。 いずれの遅延 ラ イ ン も 、PicoBlaze™ プ ロ セ ッ サ (ま たはほかのプ ロ セ ッ サ) あ る いは ス テー ト マシ ンで制御で き ます。MMCM フ ィ ー ド バ ッ クループのキ ャ リ ブ レーシ ョ ンが必要な場合は、FPGA と DAC 間の接続の初期化段階で行 う 必要があ り ます。

X-Ref Target - Figure 4

図 4 : 外部フ ィ ー ド バ ッ クループ を使用する MMCM を備えた基本的な DAC イ ン タ ー フ ェ イ ス

X-Ref Target - Figure 5

図 5 : 外部フ ィ ー ド バ ッ ク 遅延の制御 X594_04_072612 MMCM Data MUX Clock Ctrl ODELAYE2 B IDELAYE2 DAC DAC

FPGA

CLK_in FB_in FB_out Feedback Loop Data Clock Data_B [13:0] Data_A [13:0] DAC Clock Out DAC Clock In A (See Note) Length A = Length B X594_05_062012 MMCM CLKIN1 CLKFBIN CLKFBOUT ODELAYE2_varload ODATAIN DATAOUT CNTVALUEIN[4:0] CNTVALUEOUT[4:0] C CE INC RST BUFG OBUFDS + IBUFDS IDELAYE2_varload DATAOUT IDATAIN CNTVALUEOUT[4:0] CNTVALUEIN[4:0] C CE INC RST IBUFDS 2*Picoblaze_DataIn 2*Picoblaze_DataOut RefClk SIGNAL_PATTERN=CLOCK SIGNAL_PATTERN=CLOCKDAC LVDS イ ン タ ー フ ェ イ ス 注記 : • MMCM の外部フ ィ ー ド バ ッ ク ループには、3ns ま たは 1 CLKIN の要件があ り ます (MMCM_TFBDELAY)。 • ODELAYE2 は HR I/O バン ク でのみ使用可能です。 • IDELAYE2 と ODELAYE2 の タ ッ プ値は、 適用 さ れ る 基準周波数、 環境条件 (電圧 と 温度)、 遅延 チ ェーン内の位置に よ っ て決ま り ます。

DAC

か ら のビ ッ ト

ク ロ ッ ク

DAC は高速ビ ッ ト レー ト のデジ タ ルク ロ ッ ク を FPGA に供給 し ます。 こ の ク ロ ッ ク は OSERDESE2

のシ リ アル出力の基準 と な る ため、 ビ ッ ト レー ト ク ロ ッ ク と 呼ばれます。 多 く の DAC デバ イ スは、 接 続 さ れ る イ ン タ ーフ ェ イ ス FPGA か ら の イ ン タ ー リ ーブデー タ を要求 し ます。 こ れには、FPGA イ ン タ ー フ ェ イ ス が DAC の分解能 と 同 じ 幅の 2 つのバ ス を備え て い る 必要が あ り ま す。 イ ン タ ー リ ーブ デー タ を必要 と す る分解能 16 ビ ッ ト の DAC は、FPGA の 2 つの 16 ビ ッ ト 差動バス を必要 と する ため、 2 つの I/O バン ク が使用 さ れます。1 つのバン ク には DAC と 16 ビ ッ ト デー タバス か ら の ク ロ ッ ク 入力 が含まれ、 も う 1 つのバン ク には DAC と 2 つ目の 16 ビ ッ ト デー タバス の ク ロ ッ ク が含まれます。 ビ ッ ト ク ロ ッ ク は DAC がアナ ロ グ出力の生成に使用す る ク ロ ッ ク のデジ タ ルバージ ョ ン です。 し た がっ て、 ビ ッ ト ク ロ ッ ク は非常に低ジ ッ タ ーの特性を持ち ます。 PCB デザ イ ンの最 も 簡単な方法は、FPGA の ク ロ ッ ク 兼用 I/O にビ ッ ト ク ロ ッ ク を供給す る こ と です。 こ の方法では、DAC と FPGA 間のすべての接続はほぼ直線の接続にな り 、 すべての ト レース長の調整 が簡単に行え ます。 ビ ッ ト ク ロ ッ ク は、FPGA 内で次の異な る 方法で使用で き ます。

• ク ロ ッ ク 管理を使用 し ない場合、BUFMR、BUFIO、 お よ び BUFR ク ロ ッ クバ ッ フ ァ ーを介 し て

• 受信 し た DAC ク ロ ッ ク を MMCM への入力 と し て使用 し 、OSERDESE2 コ ン ポーネ ン ト ま たは

FPGA 内のアプ リ ケーシ ョ ン、 あ る いはその両方に必要な ク ロ ッ ク を生成す る

ク ロ ッ ク管理を使用 し ない場合

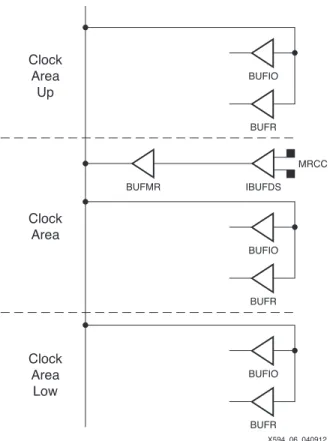

こ の場合、DAC か ら 入力 さ れ る ク ロ ッ ク は、 ク ロ ッ ク 兼用 I/O 入力か ら BUFMR ク ロ ッ クバ ッ フ ァ ー に配線 さ れます。 こ こ か ら 、 使用 さ れ る 各 I/O バン ク 内の BUFIO と BUFR が制御 さ れます。

シ ン グル リ ージ ョ ナル ク ロ ッ ク 入力の ク ロ ッ ク 兼用 I/O か ら 複数の I/O バン ク を制御す る 必要があ る

場合は、BUFMR (マルチ領域 ク ロ ッ ク バ ッ フ ァ ー) が必要です。BUFMR の出力は、BUFMR が配置

さ れ る I/O バン ク 内の BUFIO お よ び BUFR バ ッ フ ァ ー と 、 隣接 I/O バン ク の一方ま たは両方 (上ま た

リ フ ァ レ ン スデザ イ ンフ ァ イ ルには、3 つの I/O バン ク 内の OSERDESE2 と ISERDESE2 を供給先 と

す る BUFMR の使用例が含まれます (図6を参照)。

注記 :

• BUFMR、BUFR、 お よ び BUFIO のセ ッ ト を使用す る 場合は、 必ず FPGA 内のすべての コ ン ポー

ネ ン ト に LOC 制約を適用 し ます。

• FPGA と DAC 間のすべての出力 (ク ロ ッ ク お よ びデー タ) に ロ ッ ク (LOC) 制約を適切に使用 し ま

す。

• OSERDESE2 の使用に関す る すべてのガ イ ド ラ イ ン (11ページの 「OSERDESE2」 を参照) を適用

し ます。

• BUFMR、BUFR、 ま たは BUFIO か ら ク ロ ッ ク を供給 さ れ る OSERDESE2 と アプ リ ケーシ ョ ンの

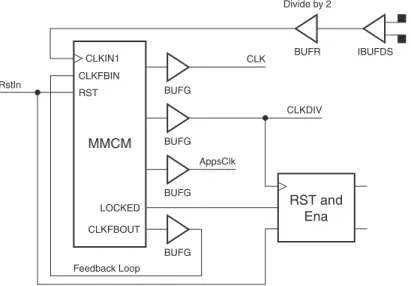

間に、 小型のエ ラ ス テ ィ ッ クバ ッ フ ァ ー、FIFO、 ま たはデー タバ ッ フ ァ ーを配置 し ます。 こ のデー タバ ッ フ ァ ーに よ り 、アプ リ ケーシ ョ ン ク ロ ッ ク と OSERDESE2 の ク ロ ッ ク 間の ク ロ ッ ク ド メ イ ン を簡単に切 り 替えで き ます。OSERDESE2.CLKDIV と アプ リ ケーシ ョ ン ク ロ ッ ク が同 じ 周波数 を持つ場合で も 、位相の違いのためにデー タバ ッ フ ァ ーがなければ簡単には処理で き ない こ と があ り ます (図6を参照)。 MMCM を使用する場合のク ロ ッ ク の使用 DAC か ら の ク ロ ッ ク が ク ロ ッ ク 兼用 I/O に接続 さ れ、MMCM が使用 さ れ る 場合 (図7)、 ク ロ ッ ク は

BUFR を介 し て MMCM に到達す る 必要があ り ます。 こ の場合、DAC か ら の ク ロ ッ ク は通常、BUFR

よ り 後の ク ロ ッ ク ネ ッ ト ワー ク には高速すぎ ます (デー タ シー ト DS181 『Artix-7 FPGA デー タ シー ト

: DC 特性お よ びス イ ッ チ特性』[参照2]、 デー タ シー ト DS182 『Kintex-7 FPGA デー タ シー ト : DC お

よ び AC ス イ ッ チ特性』 [参照3]、 ま たはデー タ シー ト DS183 『Virtex-7 T XT FPGA デー タ シー ト : DC 特性お よ びス イ ッ チ特性』 [参照4]を参照)。

X-Ref Target - Figure 6

図 6 : BUFMR ク ロ ッ キングの使用 X594_06_040912 BUFIO BUFR IBUFDS BUFMR Clock Area Up Clock Area Clock Area Low MRCC BUFIO BUFR BUFIO BUFR

DAC LVDS イ ン タ ー フ ェ イ ス こ のため、BUFR は入力 さ れ る 高速 ク ロ ッ ク を 2 つに分周 し ます。 こ れで、MMCM は こ の ク ロ ッ ク を 必須ビ ッ ト OSERDESE2.CLK と ワ ー ド ク ロ ッ ク OSERDESE2.CLKDIV に供給で き ます。 注記 : • MMCM の 2 つの出力を、OSERDESE2 の専用ビ ッ ト ク ロ ッ ク お よ び ワー ド ク ロ ッ ク (CLK お よ び CLKDIV) と し て使用 し ます。

• MMCM か ら 出力 さ れ る CLKDIV ワー ド ク ロ ッ ク は、OSERDESE2 ま たは OSERDESE2 を出力先

と するデー タバ ッ フ ァ ーの読み出 し 側の前にあ る レ ジ ス タ に ク ロ ッ ク を供給する必要があ り ます。

• DAC イ ン タ ーフ ェ イ スは通常は複数の I/O バン ク に渡 る ため、BUFG ク ロ ッ クバ ッ フ ァ ーを介 し

て OSERDESE2 への ク ロ ッ ク を配線 し ます。

• I/O バン ク 内で MMCM を使用 し 、 ク ロ ッ ク 兼用 I/O を介 し て DAC か ら の ク ロ ッ ク を キ ャ プチ ャ し ます。 こ れには LOC 制約が必要 と な る 可能性があ り ます。

DAC

へのビ ッ ト

ク ロ ッ ク

DAC は、OSERDESE2 が DAC 用のデー タ を生成す る レー ト と 同 じ ビ ッ ト レー ト で動作す る ク ロ ッ ク

を 接 続 イ ン タ ー フ ェ イ ス に 要 求 し ま す。DAC 用 の ク ロ ッ ク を 生 成 す る 最 も 効 率 的 な 方 法 は、

OSERDESE2 を ク ロ ッ ク ジ ェ ネ レー タ ー と し て使用す る こ と です。 こ の方法に よ り 、FPGA で生成 さ

れ る ク ロ ッ ク と デー タ の同期が保証 さ れます。

各 OSERDESE2 は、 ま っ た く 同 じ 方法、 同 じ タ イ ミ ン グで FPGA 出力パ ッ ド に接続 し ます。FPGA 内

の複数の I/O バン ク は、 それぞれ同 じ OSERDESE2 お よ び I/O コ ン ポーネ ン ト で構成 さ れてい る ため、

同 じ 方 法 と タ イ ミ ン グ で 接 続 し ま す。1 つ の フ ァ ミ リ の 異 な る FPGA コ ン ポ ー ネ ン ト 内 に あ る OSERDESE2 は、 同 じ ス ピー ド グ レー ド パ ラ メ ー タ ー と 動作パ ラ メ ー タ ーを使用 し てい る 限 り 、 同 じ (タ イ ミ ン グ) 特性を持ち ます。 OSERDESE2 は、CLKDIV ク ロ ッ ク の立ち上が り エ ッ ジで動作す る 入力レ ジ ス タ と 、CLK ク ロ ッ ク の 立ち上が り エ ッ ジで動作す る ロ ー ド 可能なパ ラ レ ル/シ リ アルレ ジ ス タ を備え たデバ イ ス です。 セ ッ ト ポ イ ン ト と し て DATA_WIDTH パ ラ メ ー タ ーを持つ内部ス テー ト マシ ンは、 パ ラ レル入力レ ジ ス タ か ら のデー タ が適切な タ イ ミ ン グでパ ラ レル/シ リ アル レ ジ ス タ に確実に転送 さ れ る よ う に し ます。 し たがっ て、OSERDESE2 に常に同 じ デー タ が ロ ー ド さ れ る 場合、 シ リ アル出力は ク ロ ッ ク と 全 く 同 じ よ う な繰 り 返 し デー タ ス ト リ ームにな り ます。

X-Ref Target - Figure 7

図 7 : 有効な MMCM のセ ッ ト ア ッ プ X594_07_041512 MMCM RST and Ena CLKIN1 CLKFBIN RST CLKFBOUT BUFG IBUFDS BUFR Divide by 2 RstIn AppsClk Feedback Loop LOCKED BUFG CLKDIV BUFG CLK BUFG

入力デー タ の形式に よ っ て、 シ リ アル出力の形式が決ま り ます。8 ビ ッ ト 入力の OSERDESE2 へのパ ラ レ ル入力が01010101[7:0] であ る 場合、 シ リ アル出力 (DDR モー ド) は50/50 の ク ロ ッ ク 信号にな り ます。 こ の ク ロ ッ ク 信号の レー ト は、OSERDESE2 に供給す る CLK の レー ト に直接関連付け ら れます。 た と えば、CLK が 625MHz であ り 、OSERDESE2 が DDR モー ド で動作す る 場合、 出力は 625MHz の ク ロ ッ ク にな り ます。 図8に、 固定 レ ー ト の OSERDESE2 ク ロ ッ ク ジ ェ ネ レ ー タ ーを示 し ま す。図9に、 プ ロ グ ラ マブル レー ト の OSERDESE2 ク ロ ッ クジ ェ ネ レー タ ーを示 し ます。 リ フ ァ レ ン ス デザ イ ン フ ァ イ ルには、OSERDESE2 を ク ロ ッ ク ジ ェ ネ レ ー タ ー と し て使用す る プ ロ ジ ェ ク ト が含まれてい ます。 DAC が、 供給 さ れ る デー タ に対 し て位相シ フ ト さ れた ク ロ ッ ク を必要 と す る 場合、 こ の位相シ フ ト は、 固定モー ド ま たは可変モー ド の ODELAYE2 を使用 し て実現で き ます。図8 と図9に、 こ のセ ッ ト ア ッ プ を グ レー表示 し ます。 注記 : • OSERDESE2 の使用に関す る すべてのガ イ ド ラ イ ン (11ページの 「OSERDESE2」 を参照) を適用 し ます。

X-Ref Target - Figure 8

図 8 : 固定レー ト のク ロ ッ ク ジ ェ ネ レー タ ー

X-Ref Target - Figure 9

図 9 : プ ログ ラ マ ブル ク ロ ッ ク ジ ェ ネ レー タ ー X594_08_040912 REGISTER ODELAYE2 OSERDESE2 OSERDESE2 in: Master, DDR Configuration Data Clock CLOCK [PATTERN] CLK CLKDIV SyncRst OCE RST SyncEna X594_09_041512 ODELAYE2 OSERDESE2 Address Count, Enable

and Load State Machine

OSERDESE2 in: Master, DDR Configuration Data Clock CLK CLKDIV SyncRst OCE Din WrAddr Wrt LUT FF Wen Wclk Dout RdAddr Rst Ren Rclk RST SyncEna

デー タ • OSERDESE2 は HP I/O バン ク でのみ使用可能です。

デー タ

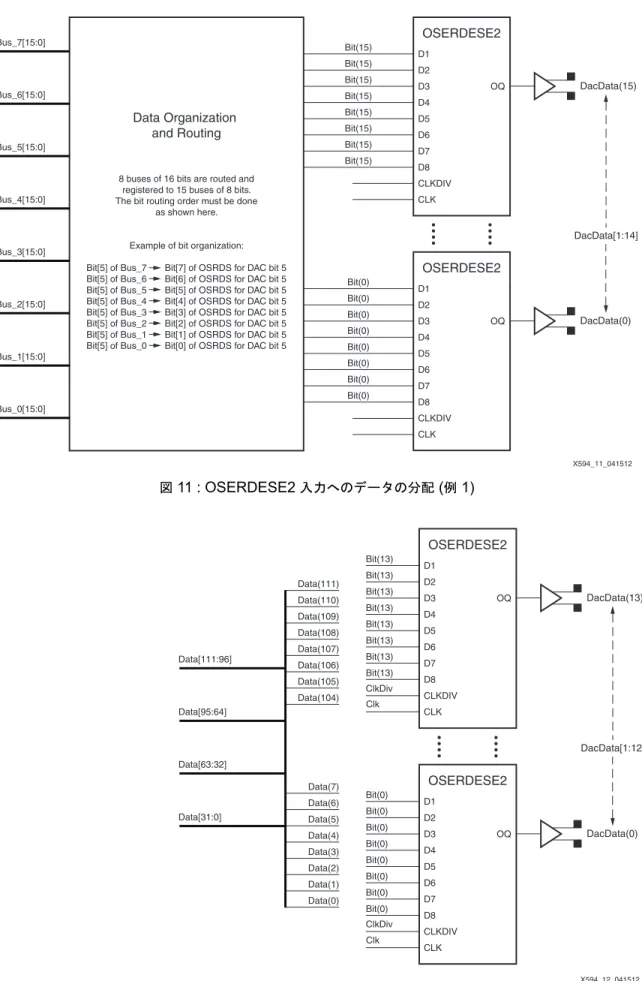

DAC はパ ラ レルデー タ を要求 し ます。 し たがっ て、 少な く と も 1 つのデー タバス を DAC の分解能 と 同 じ 幅で構成す る 必要があ り ます。 バ ス の各ビ ッ ト は、1 つの OSERDESE2 コ ン ポーネ ン ト で表 さ れま す。 各 OSERDESE2 の入力は、1 ニブル (4 ビ ッ ト) ま たは 1 バ イ ト (8 ビ ッ ト) です。 し たがっ て、 各 OSERDESE2 は、DAC に接続す る パ ラ レルバ ス内のい く つかの ビ ッ ト を表す 1 ニブルま たは 1 バ イ ト を ロ ー ド す る 必要があ り ます。 こ のため、図10に示す よ う に、OSERDESE2 に ロ ー ド さ れ る ニブルま たはバ イ ト は、DAC に接続す る バ ス の 1 ビ ッ ト に対応す る 一連のビ ッ ト を表 し ます。1.2GSPS (gigasample per second) の 14 ビ ッ ト DAC が 600MHz ク ロ ッ ク を FPGA に供給す る 場合、次

の こ と を前提にで き ます。 • OSERDESE2 は必ず DDR モー ド で使用 し ます。 • OSERDESE2 が 8 ビ ッ ト DDR モー ド で使用 さ れ る 場合、MMCM を用いて 600MHz の CLK と 150MHz の CLKDIV を生成で き ます。 • FPGA 内のアプ リ ケーシ ョ ンは、150MHz の レー ト で 14 × 8 ビ ッ ト = 112 ビ ッ ト を供給す る 必要 があ り ます。 • 一時的な ス ト レージ と し て分散型 メ モ リ 内で ク ロ ッ ク ド メ イ ン切 り 替えデー タ バ ッ フ ァ ーを使用 す る 場合、 こ の要件を満たす こ と は難 し く あ り ません。 • 図11 と図12に示す よ う に、 メ モ リ か ら の出力ビ ッ ト は FPGA の配線ネ ッ ト ワー ク で OSERDESE2 の入力に分配 さ れます。図11に、 アプ リ ケーシ ョ ンが 16 ビ ッ ト バ ス形式でデー タ を 供給す る 16 ビ ッ ト 分解能 の DAC の例 を 示 し ま す。図12に示す例 で は、DAC の分解能は

X-Ref Target - Figure 10

図 10 : DAC 入力バス用の OSERDESE2 のビ ッ ト 配列 X594_10_041512 OSERDESE2 Eight N-bits flowing out serially to make DacData(N) DacData(N) D1 Bit(N) D2 Bit(N) D3 OQ Bit(N) D4 Bit(N) D5 Bit(N) D6 Bit(N) D7 Bit(N) D8 Bit(N) CLKDIV ClkDiv CLK Clk OSERDESE2 DacData(0) DacData[1:N–1] D1 Bit(0) D2 Bit(0) D3 OQ Bit(0) D4 Bit(0) D5 Bit(0) D6 Bit(0) D7 Bit(0) D8 Bit(0) CLKDIV ClkDiv CLK Clk

X-Ref Target - Figure 11 図 11 : OSERDESE2 入力へのデー タ の分配 (例 1) X594_11_041512 OSERDESE2 DacData(15) D1 Bit(15) D2 Bit(15) D3 OQ Bit(15) D4 Bit(15) D5 Bit(15) D6 Bit(15) D7 Bit(15) D8 Bit(15) CLKDIV CLK OSERDESE2 DacData(0) DacData[1:14] D1 Bit(0) Data Organization and Routing

8 buses of 16 bits are routed and registered to 15 buses of 8 bits. The bit routing order must be done

as shown here.

Example of bit organization:

Bit[5] of Bus_7 Bit[7] of OSRDS for DAC bit 5 Bit[5] of Bus_6 Bit[6] of OSRDS for DAC bit 5 Bit[5] of Bus_5 Bit[5] of OSRDS for DAC bit 5 Bit[5] of Bus_4 Bit[4] of OSRDS for DAC bit 5 Bit[5] of Bus_3 Bit[3] of OSRDS for DAC bit 5 Bit[5] of Bus_2 Bit[2] of OSRDS for DAC bit 5 Bit[5] of Bus_1 Bit[1] of OSRDS for DAC bit 5 Bit[5] of Bus_0 Bit[0] of OSRDS for DAC bit 5

D2 Bit(0) D3 OQ Bit(0) D4 Bit(0) D5 Bit(0) D6 Bit(0) D7 Bit(0) D8 Bit(0) CLKDIV CLK Bus_7[15:0] Bus_6[15:0] Bus_5[15:0] Bus_4[15:0] Bus_3[15:0] Bus_2[15:0] Bus_1[15:0] Bus_0[15:0]

X-Ref Target - Figure 12

図 12 : OSERDESE2 入力へのデー タ の分配 (例 2) X594_12_041512 OSERDESE2 DacData(13) D1 Bit(13) D2 Bit(13) D3 OQ Bit(13) D4 Bit(13) D5 Bit(13) D6 Bit(13) D7 Bit(13) D8 Bit(13) Data(111) Data(110) Data(109) Data(108) Data(107) Data(106) Data(105) Data(104) Data(7) Data(6) Data(5) Data(4) Data(3) Data(2) Data(1) Data(0) ClkDiv Clk ClkDiv Clk CLKDIV CLK OSERDESE2 DacData(0) DacData[1:12] D1 Bit(0) D2 Bit(0) D3 OQ Bit(0) D4 Bit(0) D5 Bit(0) D6 Bit(0) D7 Bit(0) D8 Bit(0) CLKDIV CLK Data[111:96] Data[95:64] Data[63:32] Data[31:0]

OSERDESE2 図11では、8 つの 16 ビ ッ ト デー タ バ ス が配線 さ れ、 最終的に 16 個の 8 ビ ッ ト バ スへ出力 さ れます。 • こ の例では DAC の分解能が 16 ビ ッ ト であ る ため、16 個のバ ス • OSERDESE2 の入力幅が 8 ビ ッ ト であ る ため、8 ビ ッ ト のバ ス こ の例では、 ビ ッ ト の配線順序は次の よ う にな り ます。 • デー タバ ス Y、 こ こ で Y は 16 ビ ッ ト デー タ 入力バ ス の う ち 1 つ • ビ ッ ト n、 こ こ で n は Y バス の う ち 1 つの 1 ビ ッ ト • OSERDESE2 入力バス X、 こ こ で X は OSERDESE2 の 8 ビ ッ ト 入力 • ビ ッ ト m、 こ こ で m は X バ ス の う ち 1 つの 1 ビ ッ ト バ ス Y の ビ ッ ト n は、OSERDESE2 入力 m の ビ ッ ト Y と し て現れ ます。 た と えば、 次の よ う にな り ます。

• Bus_7 の ビ ッ ト (5) DAC ビ ッ ト (5) に対応す る OSERDESE2 入力のビ ッ ト (7)

• Bus_6 の ビ ッ ト (5) DAC ビ ッ ト (5) に対応す る OSERDESE2 入力のビ ッ ト (6)

• Bus_5 の ビ ッ ト (5) DAC ビ ッ ト (5) に対応す る OSERDESE2 入力のビ ッ ト (5)

• Bus_4 の ビ ッ ト (5) DAC ビ ッ ト (5) に対応す る OSERDESE2 入力のビ ッ ト (4)

• Bus_3 の ビ ッ ト (5) DAC ビ ッ ト (5) に対応す る OSERDESE2 入力のビ ッ ト (3)

• Bus_2 の ビ ッ ト (5) DAC ビ ッ ト (5) に対応す る OSERDESE2 入力のビ ッ ト (2)

• Bus_1 の ビ ッ ト (5) DAC ビ ッ ト (5) に対応す る OSERDESE2 入力のビ ッ ト (1)

• Bus_0 の ビ ッ ト (5) DAC ビ ッ ト (5) に対応す る OSERDESE2 入力のビ ッ ト (0)

図12に、DAC 用のデー タ を 32 ビ ッ ト バ ス形式で供給す る 2 番目のアプ リ ケーシ ョ ン例を示 し ます。 使用 さ れてい る DAC の分解能は 14 ビ ッ ト であ る ため、MSB バ ス の下位 16 ビ ッ ト が用い ら れ ま す。 OSERDESE2 の入力に対す る アプ リ ケーシ ョ ンバ ス の接続は、 アプ リ ケーシ ョ ン バ ス の順序で リ ニア に接続す る こ と も (DataBus_13[111:96] = OSERDESE2 の 13 お よ び 12 か ら 、 DataBus_0[31:0] = OSERDESE2 の 3、2、1、 お よ び 0 入力 ま で)、 カ ス タ ム順序で接続す る こ と も で き ます。 すべての場合で ロ ジ ッ ク は不要であ り 、FPGA の配線 リ ソ ース に よ っ て適切な接続の実装が保 証 さ れます。 アプ リ ケーシ ョ ン と OSERDESE2 入力の間のほかの接続方式には、図11 と図12に示 し たの と 同様の 方法ま たは ま っ た く 異な る 方法を使用で き ます。OSERDESE2 を ほかのデー タ 幅で使用す る 場合、 アプ リ ケーシ ョ ンへの接続は、 例 1 (図11) お よ び例 2 (図12) と は ま っ た く 異な る も のにな る 可能性があ り ます。

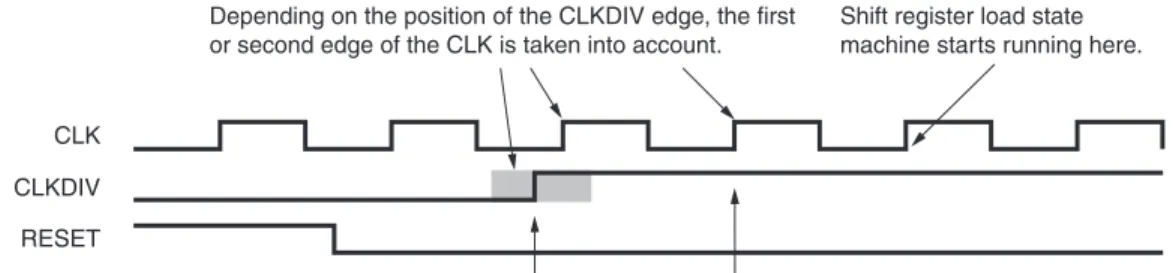

OSERDESE2

OSERDESE2 (図1) はパ ラ レル入力レ ジ ス タ であ り 、 ロ ー ド 可能なパ ラ レル/シ リ アルシ フ ト レ ジ ス タ が後に続 き ます。 デー タ は CLKDIV の立ち上が り エ ッ ジでパ ラ レルレ ジ ス タ に ロ ー ド さ れ、CLK の立 ち上が り エ ッ ジでパ ラ レル/シ リ アルレ ジ ス タ にシ フ ト ア ウ ト さ れます。 2 つの レ ジ ス タ 間の接続は内部ス テー ト マシ ンが制御 し ます。 ス テー ト マシ ンは、CLK、CLKDIV、 お よ び DATA_WITDH 属性を制限 し 、 デー タ が常に正 し い タ イ ミ ン グでパ ラ レ ル入力レ ジ ス タ か ら パ ラ レル/シ リ アルレ ジ ス タ に転送 さ れ る よ う に し ます。 OSERDESE2 は次の よ う にセ ッ ト ア ッ プで き ます。 • マ ス タ ー専用ま たはマ ス タ ー/ス レーブ • DDR モー ド では 2、4、6、8、10、 ま たは 14 ビ ッ ト 入力 (10 ビ ッ ト 入力 と 14 ビ ッ ト 入力は、 マ ス タ ー/ス レーブ構成でのみ使用可能) • SDR モー ド では 2、3、4、5、6、7、8、10、 ま たは 14 ビ ッ ト 入力DAC イ ン タ ーフ ェ イ ス では、OSERDESE2 はマ ス タ ー、4 ビ ッ ト 、 ま たは 8 ビ ッ ト の DDR モー ド で 使用 さ れます。CLKDIV レー ト は、CLK レー ト の 2 分の 1 (4 ビ ッ ト) ま たは 4 分の 1 (8 ビ ッ ト) に設 定す る 必要があ り ます。 OSERDESE2 を使用す る 場合は、 次の点に注意 し て く だ さ い。 • パ ラ レル入力レ ジ ス タ には、 イ ネーブル (OCE) や リ セ ッ ト (RST) はあ り ません。つま り 、CLKDIV の立ち上が り エ ッ ジが印加 さ れ る と 、OSERDESE2 の入力ピ ン上で使用可能なすべてのデー タ はた だちにパ ラ レル入力レ ジ ス タ に ロ ー ド さ れます。 • OCE ピ ンは、 シ フ ト レ ジ ス タ のシ リ アル MSB 出力レ ジ ス タ にのみ接続 さ れます。 • OSERDESE2 が リ セ ッ ト の リ リ ース直後に未知のデー タ の生成を開始 し ない よ う に、LUT をプ ロ グ ラ マブルシ フ ト レ ジ ス タ (SRL32) と し て使用 し 、CLKDIV ク ロ ッ ク の数サ イ ク ル間 イ ネーブル 入力をデ ィ アサー ト し て く だ さ い。 リ セ ッ ト の リ リ ース後に イ ネーブル入力をデ ィ アサー ト し てお く ク ロ ッ ク サ イ ク ル数は、 現在 SRL32 のア ド レ ス入力でプ ロ グ ラ ム可能です。 OSERDESE2 の リ セ ッ ト の リ リ ース後、 任意の信号が変化す る 前に CLKDIV の立ち上が り エ ッ ジに続 いて CLK の立ち上が り エ ッ ジが必要です (図13を参照)。

OSERDESE2 の リ セ ッ ト の リ リ ース を CLKDIV に同期 さ せて、 リ セ ッ ト の リ リ ース か ら CLKDIV の

数サ イ ク ル後に イ ネーブルを設定す る こ と を推奨 し ます。 タ イ ミ ン グ制約を使用 し て リ セ ッ ト と イ ネー ブルを制御す る こ と で、 イ ン タ ーフ ェ イ ス のすべての OSERDESE2 が同時に有効にな り 、 同 じ タ イ ミ ン グでデー タ の生成を開始す る こ と が保証 さ れます。 デー タ は ISERDESE2 に ロ ー ド さ れた後、 ただちにそ こ か ら 出力 さ れ る こ と はあ り ません。 リ セ ッ ト の リ リ ース後、CLKDIV の立ち上が り エ ッ ジでパ ラ レル入力レ ジ ス タ にデー タ が ロ ー ド さ れ、 同時に内部 ス テー ト マシ ンが リ セ ッ ト か ら 解放 さ れ ます。 前回の CLKDIV の立ち上が り エ ッ ジに続 く CLK の立 ち上が り エ ッ ジで、 内部ス テー ト マシ ンが ス タ ー ト し ます。 パ ラ レ ル入力 レ ジ ス タ か ら パ ラ レ ル/シ リ ア ル レ ジ ス タ にデー タ を 転送す る 内部 ス テー ト マ シ ン は、 DATA_WIDTH 属性に よ っ て決ま り ます。CLKDIV の立ち上が り エ ッ ジに続 く CLK の立ち上が り エ ッ ジの後、OSERDESE2 の内部ス テー ト マシ ンはパ ラ レル/シ リ アルレ ジ ス タ を フ ラ ッ シ ュ し ます。 ビ ッ

ト 数は、OSERDESE2 の DATA_WIDTH お よ び DATA_RATE 属性に よ っ て決ま り ま す。 こ の処理は リ セ ッ ト の リ リ ース直後に行われ る ため、OSERDESE2 は ロ ー ド パル ス が発生す る ま ですべて 0 を送 信 し ます。 内部ス テー ト マシ ンはパルス を生成 し 、 パ ラ レル入力レ ジ ス タ の内容をパ ラ レル/シ リ アルシ フ ト レ ジ ス タ に ロ ー ド し ま す。 パ ラ レ ル 入 力 レ ジ ス タ に 最 初 に ロ ー ド さ れ た 内 容 を 処 理 し な い 場 合、 OSERDESE2 か ら 出力 さ れ る 最初のシ リ アルデー タ は不要なデー タ と 考え ら れます。 OSERDES2 が未知のデー タ を出力 し ない よ う に、OSERDES2 入力の前に レ ジ ス タ を配置 し (図14を 参照)、 次の対策を講 じ る こ と を推奨 し ます。 • CLKDIV で レ ジ ス タ に ク ロ ッ ク 供給す る

X-Ref Target - Figure 13

図 13 : OSERDESE2 の リ セ ッ ト か らの解放

X594_13_060612

CLK CLKDIV RESET

Depending on the position of the CLKDIV edge, the first or second edge of the CLK is taken into account.

The edges are needed to take the OSERDESE2 out of reset. At this CLKDIV edge, data is or can be loaded into the input parallel register of the OSERDESE2.

Shift register load state machine starts running here.

OSERDESE2 • レ ジ ス タ の リ セ ッ ト と イ ネーブルを OSERDES2 の リ セ ッ ト と イ ネーブルに接続す る • 同期フ リ ッ プ フ ロ ッ プか ら レ ジ ス タ お よ び OSERDES2 ま での リ セ ッ ト お よ び イ ネーブル ネ ッ ト 上に タ イ ミ ン グ制御制約を イ ンプ リ メ ン ト す る こ れで、OSERDESE2 の入力の前に置かれた レ ジ ス タ は次の よ う に動作 し ます。 • リ セ ッ ト がア ク テ ィ ブの間は、CLKDIV のエ ッ ジで OSERDESE2 入力レ ジ ス タ に 0 が ロ ー ド さ れ る • リ セ ッ ト の リ リ ース後の最初の CLKDIV の立ち上が り エ ッ ジで も 、OSERDESE2 に 0 が ロー ド さ れる • こ の立ち上が り エ ッ ジで、OSERDESE2 の前に置かれた レ ジ ス タ に有効なデー タ が ロ ー ド さ れ る • 次の CLKDIV の立ち上が り エ ッ ジで OSERDESE2 に意味のあ るデータ が ロー ド さ れ、 OSERDESE2 はシ リ アル形式でデータ の生成を開始する。OSERDESE2 はシ リ アル出力上に未 知のデータ を生成する こ と はない。 複数の OSERDESE2 は出力ピ ン上に同期データ を供給する リ セ ッ ト に続 く 最初の ロ ー ド の後、 デー タ が ロ ー ド さ れ、 規則的なパ タ ーン でシ フ ト さ れます。 図15に、8 ビ ッ ト DDR モー ド の OSERDESE2 を示 し ます。 リ セ ッ ト が リ リ ース さ れ、CLKDIV の立 ち上が り エ ッ ジでデータ が OSERDESE2 に ロー ド さ れた後、4 CLK サ イ ク ルでそのデー タ は出力に現れ ます。4 CLK サ イ ク ルかか る のは、8 ビ ッ ト が ロー ド さ れ、 コ ン ト ロ ー ラ ーが まず以前の 8 ビ ッ ト (すべ て 0) を DDR CLK レー ト でシ フ ト ア ウ ト する ためです。

X-Ref Target - Figure 14

図 14 : ア ク テ ィ ベーシ ョ ン制御レ ジ ス タ と 組み合わせた OSERDESE2 X594_14_040912 REGISTER OSERDESE2 OSERDESE2 in: Master, DDR Configuration Data Clock DataIn CLK CLKDIV SyncRst OCE RST SyncEna

OSERDESE2 にはいつで も 新 し いデー タ を ロ ー ド で き ます。 ただ し 、 ロ ー ド さ れたすべてのデー タ が常 に出力に現れ る わけではあ り ません。 ス テー ト マシ ンは、 実行中のシ フ ト 操作の完了後にのみ入力パ ラ レルレ ジ ス タ か ら 出力シ フ ト レ ジ ス タ にデー タ を転送 し ます (図16を参照)。 ス テー ト マシ ンは、DATA_WIDTH お よ び DATA_RATE 属性に基づ く CLK レー ト でシ フ ト レ ジ ス タ ロ ー ド パル ス を生成 し ます。 デー タ は、 パ ラ レ ル/シ リ アル出力レ ジ ス タ に ロ ー ド さ れた後 も 、 入力パ ラ レルレ ジ ス タ か ら 消去 さ れません。 し たが っ て、 それ以降の ロ ー ド パルス でパ ラ レルレ ジ ス タ に新 し いデー タ が ロ ー ド さ れない場合、パ ラ レル/シ リ アルレ ジ ス タ には同 じ デー タ が ロ ー ド さ れます (図16 を参照)。

X-Ref Target - Figure 15

図 15 : リ セ ッ ト の リ リ ース後の最初のデー タ 出力 X594_15_072012 1 0 0 0 10110111 1 1 1 0 1 1 0 1 1 1 Data is loaded in

the parallel register.

Reset internally released after rising CLKDIV and CLK edge.

New data loaded in parallel-to-serial register and output. OSERDESE2

state machine starts here.

Data loaded in parallel-to-serial register. First bit appears at the output.

Because no new data is loaded in the parallel input register, the old data is transmitted again.

00000000 10110111 oce_dly rst_dly clk_dly clkdiv_dly DataIn load_int oq_zd OSERDESE2 Mstr/Slv OSERDESE2 flushed

X-Ref Target - Figure 16

図 16 : 継続的な操作でのデー タ の流れ X594_16_072012 1 0 0 0 01010101 0 1

This value is loaded in the parallel register and in the serial register for transmission from the OSERDESE2. This value is loaded in the

parallel register but is never loaded in the serial register.

00000000 10110111 11000110 01010101 oce_dly rst_dly clk_dly clkdiv_dly DataIn load_int oq_zd

State machine started and OSERDESE2 flushed. Data loaded

in input parallel register.

First loaded pattern transmitted from the OSERDESE2.

リ フ ァ レ ン スデザイ ン

リ フ ァ レ ン ス

デザ

イ ン

こ のアプ リ ケーシ ョ ン ノ ー ト の リ フ ァ レ ン ス デザ イ ン フ ァ イ ルは次のサ イ ト か ら ダ ウ ン ロ ー ド で き る ため、 デバ イ ス の リ ソ ース使用率の表は掲載 し てい ません。 https://secure.xilinx.com/webreg/clickthrough.do?cid=192049 表1に、 リ フ ァ レ ン スデザ イ ンの詳細を示 し ます。 リ フ ァ レ ン スデザ イ ンは 4 つの小 さ なデザ イ ン で構成 さ れてい ます。こ れ ら のデザ イ ンの一部ま たはす べて を使用 し て、DAC イ ン タ ーフ ェ イ ス を作成で き ます。 し たが っ て、FPGA リ ソ ー ス の使用は、 使 用す る DAC のブ ラ ン ド と タ イ プで決ま り ます。 イ ン タ ー リ ーブデー タ を必要 と す る DAC を 選択 し た場合は、2 倍の数の OSERDESE2 デー タ コ ン ポーネ ン ト が必要です。DAC の分解能に よ っ ては、2 つの I/O バン ク が必要にな る 可能性があ り ます。 ユーザーが面積の推定値を希望す る 場合は、 選択 し た I/O バン ク 内のすべての OSERDESE2 が使用 さ れ る と す る と 、 面積は 8 × 50 ス ラ イ ス に相当 し ます。 こ れは ISERDESE2/OSERDESE2 コ ン ポーネ ン ト と 最初のブ ロ ッ ク RAM コ ン ポーネ ン ト セ ッ ト の間の面積です (図17を参照)。 表 1 : リ フ ァ レ ン スデザイ ンの詳細 パラ メ ー タ ー 説明 全般 開発者 Marc Defossez タ ーゲ ッ ト デバ イ ス XC7K325T-2FFG900 ソ ース コ ー ド の提供 あ り ソ ース コ ー ド の形式 VHDL 使用 し た IP な し シ ミ ュ レーシ ョ ン 機能シ ミ ュ レーシ ョ ンの実施 あ り タ イ ミ ン グシ ミ ュ レーシ ョ ンの実施 な し テ ス ト ベンチの形式 VHDLシ ミ ュ レー タ の ツール と バージ ョ ン ISE® Design Suite 13.4

SPICE/IBIS シ ミ ュ レーシ ョ ンの実施 な し

イ ン プ リ メ ン テーシ ョ ン

合成ツール/バージ ョ ン ISE Design Suite 13.4、XST 13.4

イ ンプ リ メ ン テーシ ョ ンツール/バージ ョ ン ISE Design Suite 13.4 ス タ テ ィ ッ ク タ イ ミ ン グ解析の実施 あ り

ハー ド ウ ェ ア検証

ハー ド ウ ェ ア検証の実施 あ り

X-Ref Target - Figure 17

図 17 : 有効なデバイ スの リ ソ ース使用エ リ ア

Upper Half I/O Bank

Lower Half I/O Bank

4 BUFIO 4 BUFR 2 BUFMR INFIFO INFIFO PLL INFIFO INFIFO MMCM 8 by 25 Slices 8 by 25 Slices Slices Slices IDELAYCTRL OUTFIFO OUTFIFO OUTFIFO OUTFIFO 25 Single-Ended I/O or 24 Differential I/O + 1 Single-Ended I/O ISERDESE2 IDELAYE2 ODELAYE2 OSERDESE2 Block RAM RAMB36E1 Block RAM RAMB36E1 X594_17_080812

参考資料

リ フ ァ レ ン ス

デザイ ンのデ ィ レ ク ト リ

セ ッ ト ア ッ プ

図18に、 リ フ ァ レ ン スデザ イ ンのデ ィ レ ク ト リ 構造を示 し ます。

参考資料

こ の文書では、 次の参考資料を使用 し てい ます。1. UG471 : 『 7 シ リ ーズ FPGA SelectIO リ ソ ースユーザーガ イ ド 』

2. DS181 : 『Artix-7 FPGA デー タ シー ト : DC 特性お よ びス イ ッ チ特性』

3. DS182 : 『Kintex-7 FPGA デー タ シー ト : DC お よ び AC ス イ ッ チ特性』

4. DS183 : 『Virtex-7 T XT FPGA デー タ シー ト : DC 特性お よ びス イ ッ チ特性』

ま と め

7 シ リ ーズFPGA イ ン タ ーフ ェ イ ス は、OSERDESE2 の機能を使用 し て、 市販のあ ら ゆ る 最新 DAC デバ イ ス に対応す る 高速 LVDS イ ン タ ーフ ェ イ ス 開発用の柔軟性の高い汎用プ ラ ッ ト フ ォ ーム を提供 し ます。

X-Ref Target - Figure 18

図 18 : リ フ ァ レ ン スデザイ ンのデ ィ レ ク ト リ 構造

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。Notice of

Disclaimer

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited

Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to

warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:

http://www.xilinx.com/warranty.htm#critapps. 本資料は英語版 (v1.0) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。 日本語版は参考用 と し て ご使用の上、 最新情報につ き ま し ては、 必ず最新英語版を ご参照 く だ さ い。 こ の資料に関す る フ ィ ー ド バ ッ ク お よ び リ ン ク な ど の問題につ き ま し ては、 jpn_trans_feedback@xilinx.comま でお知 ら せ く だ さ い。 いただ き ま し た ご意見を参考に早急に対応 さ せていただ き ます。 なお、 こ の メ ールア ド レ スへのお問い合わせは受け付けてお り ません。 あ ら か じ め ご了承 く だ さ い。 日付 バージ ョ ン 内容 2012 年 8 月 22 日 1.0 初版 リ リ ース

![図 3 : 基本的な DAC イ ン タ ー フ ェ イ スのセ ッ ト ア ッ プ X594_03_060612MMCMDataMUXClock CtrlDACDACFPGACLK_inFB_inFB_outFeedback LoopData ClockData_B [13:0]Data_A [13:0]DAC Clock OutDAC Clock In](https://thumb-ap.123doks.com/thumbv2/123deta/5952149.571078/3.918.312.803.236.470/基本DACンターフェイスットアップMMCMDataMUXClockDataADAC.webp)

![図 10 : DAC 入力バス用の OSERDESE2 のビ ッ ト 配列X594_10_041512OSERDESE2Eight N-bitsflowing outserially to makeDacData(N)DacData(N)D1Bit(N)D2Bit(N)D3OQBit(N)D4Bit(N)D5Bit(N)D6Bit(N)D7Bit(N)D8Bit(N)CLKDIVClkDivCLKClkOSERDESE2DacData(0)DacData[1:N–1]D1Bit(0)D2Bit(0)](https://thumb-ap.123doks.com/thumbv2/123deta/5952149.571078/9.918.399.709.277.743/図DAC入力バスOSERDESEット配列XOSERDESEto1BitND2BitND3OQBitND4BitND5BitND6BitND7BitND8BitNCLKDIVClkDivCLKClkOSERDESE2DacData0DacData1N1D1Bit0D.webp)