Virtex-6 FPGA

ク ロ ッ ク

リ ソ ース

ユーザー

ガ イ ド

display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2009–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. 本資料は英語版 (v1.4) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。 日本語版は参考用 と し て ご使用の上、 最新情報につ き ま し ては、 必ず最新英語版を ご参照 く だ さ い。

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。 日付 バージ ョ ン 改訂内容 2009 年 6 月 24 日 1.0 初版 リ リ ース 2009 年 9 月 16 日 1.1 ま えが き の 「 こ のユーザーガ イ ド について」 を更新。第 2 章で 「CLKOUT4_CASCADE」 の説明を更新 し 、 い く つかの説明を明確化。25 ページの表 1-5に Virtex-6 HXT デバ イ ス を追加。45 ページの表 2-3に メ モ 1 を追加。 「COMPENSATION」属性の説明を修正 し 、表 2-4に メ モ 1 を追加。2010 年 1 月 19 日 1.2 「I/O ク ロ ッ クバ ッ フ ァ - BUFIO」を更新。「 リ ージ ョ ナルク ロ ッ クバ ッ フ ァ - BUFR」 を変更。「水平 ク ロ ッ ク バ ッ フ ァ - BUFH」を明確化。

第 2 章の 「MMCM (Mixed-Mode Clock Manager)」か ら CLKFBOUT の分数分周 (分 数 M カ ウ ン タ) 機能の説明を削除。 具体的には、図 2-2を更新、表 2-2で

CLKFBOUT_MULT_F の可能な値を訂正、CLKFBOUT_USE_FINE_PS の説明を訂 正。式2-6と 式2-7を明確化。「CLKINSEL – ク ロ ッ ク 入力切 り 替え」を更新。57

ト ア ッ プ/ホール ド タ イ ムの条件を更新。 第 2 章の「は じ めに」で 3 つ目の段落 (キ ャ リ ブ レーシ ョ ン回路に関す る 記述) を追加。 「 ク ロ ッ ク ネ ッ ト ワー ク の ス キ ュ ー調整」 を更新。「固定ま たはダ イ ナ ミ ッ クモー ド の 補間型フ ァ イ ン位相シ フ ト 」で VCO の例を変更。表 2-4で、CLKFBOUT_MULT_F の可能な値を更新す る と 共に、 ソ フ ト ウ ェ アモデルに合わせて文字列型の表記を ブー ル型に変更。「ダ イ ナ ミ ッ ク リ コ ン フ ィ ギ ュ レーシ ョ ン ポー ト 」 を更新。 2010 年 4 月 7 日 1.4 ページ35と表 2-4で STARTUP_WAIT 属性に設定可能な値を更新。

改訂履歴. . . 2

このユーザー

ガ イ ド について

ユーザーガ イ ド の内容 . . . 7 その他の資料. . . 7 その他の リ ソ ース . . . 8第

1

章

:

ク ロ ッ ク

リ ソ ース

グ ロ ーバルク ロ ッ ク 、 リ ージ ョ ナルク ロ ッ ク 、I/O ク ロ ッ ク . . . 9 グ ロ ーバルク ロ ッ ク . . . .9 リ ージ ョ ナルク ロ ッ ク と I/O ク ロ ッ ク. . . .9 ク ロ ッ キ ン グアーキ テ ク チ ャ . . . .10 グ ロ ーバルク ロ ッ ク リ ソ ース . . . 11 グ ロ ーバルク ロ ッ ク 入力. . . .12 グ ロ ーバルク ロ ッ ク 入力バ ッ フ ァ のプ リ ミ テ ィ ブ . . . .12 ク ロ ッ クゲーテ ィ ン グに よ る 消費電力削減 . . . .12 グ ロ ーバルク ロ ッ クバ ッ フ ァ. . . .12 グ ロ ーバルク ロ ッ クバ ッ フ ァ のプ リ ミ テ ィ ブ. . . .13 その他の使用モデル. . . .21 ク ロ ッ ク ツ リ ー と ネ ッ ト - GCLK . . . .24 ク ロ ッ ク 領域 . . . .24 リ ージ ョ ナルク ロ ッ ク リ ソ ース . . . 25 CC (Clock-Capable、 ク ロ ッ ク 兼用) I/O . . . .26 I/O ク ロ ッ クバ ッ フ ァ - BUFIO . . . .26 BUFIO プ リ ミ テ ィ ブ. . . .26 BUFIO の使用モデル. . . .27 リ ージ ョ ナルク ロ ッ ク バ ッ フ ァ - BUFR . . . .28 BUFR プ リ ミ テ ィ ブ . . . .28 BUFR の属性 と モー ド . . . .29 BUFR の使用モデル . . . .30 リ ージ ョ ナルク ロ ッ ク ネ ッ ト. . . .31 水平 ク ロ ッ ク バ ッ フ ァ - BUFH. . . .32 高性能 ク ロ ッ ク . . . .33 VHDL お よ び Verilog テ ンプ レー ト . . . 34第

2

章

: MMCM (Mixed-Mode Clock Manager)

は じ めに. . . 35 MMCM . . . .36 一般的な使用法について. . . 38 MMCM プ リ ミ テ ィ ブ . . . .38 MMCM_BASE プ リ ミ テ ィ ブ. . . .38 MMCM_ADV プ リ ミ テ ィ ブ. . . .39 ク ロ ッ クネ ッ ト ワー ク の ス キ ュ ー調整. . . .39 整数分周のみを使用 し た周波数合成 . . . .40 分数分周を使用 し た周波数合成. . . .40 ジ ッ タ フ ィ ル タ . . . .40 制限. . . .41 VCO 動作範囲. . . .41 最小お よ び最大入力周波数 . . . .41 デ ュ ーテ ィ サ イ ク ルのプ ロ グ ラ ム . . . .41 位相シ フ ト. . . .41MMCM のプ ロ グ ラ ミ ン グ . . . .43 入力周波数の決定 . . . .43 M お よ び D 値の指定 . . . .44 MMCM のポー ト . . . .45 MMCM の各ポー ト の説明 . . . .46 MMCM の属性. . . .50 MMCM の ク ロ ッ ク 入力信号. . . .52 カ ウ ン タ 制御 . . . .53 VCO と 出力カ ウ ン タ の波形についての詳細 . . . 54 リ フ ァ レ ン ス ク ロ ッ ク の切 り 替え . . . 55 入力 ク ロ ッ ク ま たはフ ィ ー ド バ ッ ク ク ロ ッ ク の欠如. . . .55 MMCM の使用モデル. . . 55 ク ロ ッ クネ ッ ト ワー ク の ス キ ュ ー調整. . . .55 内部フ ィ ー ド バ ッ ク を使用 し た MMCM . . . .56 ゼ ロ 遅延バ ッ フ ァ. . . .57 MMCM 同士の接続. . . .58 MMCM のアプ リ ケーシ ョ ン例. . . .60 ダ イ ナ ミ ッ ク リ コ ン フ ィ ギ ュ レーシ ョ ンポー ト . . . .60

こ のユーザーガ イ ド は、Virtex®-6 FPGA ク ロ ッ ク リ ソ ース について説明 し た テ ク ニ カル リ フ ァ レ ン ス です。

ユーザー

ガ イ ド の内容

こ のユーザーガ イ ド は、 次の各章か ら 構成 さ れてい ます。 • 第 1 章 「 ク ロ ッ ク リ ソ ース」

• 第 2 章 「MMCM (Mixed-Mode Clock Manager)」

その他の資料

次の資料 も 、http://japan.xilinx.com/support/documentation/virtex-6.htmか ら ダ ウ ン ロー ド で き ます。 • 『Virtex-6 フ ァ ミ リ 概要』 Virtex-6 フ ァ ミ リ の特徴 と 製品群の概要を説明 し てい ます。 • 『Virtex-6 FPGA デー タ シー ト: DC 特性お よ びス イ ッ チ特性』 Virtex-6 フ ァ ミ リ の DC 特性お よ びス イ ッ チ特性の仕様が記載 さ れてい ます。 • 『Virtex-6 FPGA パ ッ ケージお よ びピ ン配置仕様』 デバ イ ス/パ ッ ケージの組み合わせお よ び最大 I/O 数の表、 ピ ン定義、 ピ ン配置表、 ピ ン配置図、 機械的図面、 温度仕様が記載 さ れてい ます。 • 『Virtex-6 FPGA コ ン フ ィ ギ ュ レーシ ョ ンガ イ ド 』 こ の包括的な コ ン フ ィ ギ ュ レーシ ョ ンガ イ ド は、 コ ン フ ィ ギ ュ レーシ ョ ンイ ン タ ーフ ェ イ ス (シ リ アル と SelectMAP)、 ビ ッ ト ス ト リ ームの暗号化、 バ ウ ン ダ リ ス キ ャ ンお よ び JTAG コ ン フ ィ ギ ュ レーシ ョ ン、 リ コ ン フ ィ ギ ュ レーシ ョ ンテ ク ニ ッ ク 、SelectMAP イ ン タ ーフ ェ イ スお よ び JTAG イ ン タ ーフ ェ イ ス での リ ー ド バ ッ ク の各章で構成 さ れてい ます。• 『Virtex-6 FPGA SelectIO リ ソ ースユーザーガ イ ド 』

Virtex-6 の各デバ イ ス で使用可能な SelectIO™ リ ソ ース について説明 し てい ます。 • 『Virtex-6 FPGA コ ン フ ィ ギ ャ ブル ロ ジ ッ クブ ロ ッ ク ユーザーガ イ ド 』 すべての Virtex-6 デバ イ ス で使用可能な コ ン フ ィ ギ ャ ブルロ ジ ッ クブ ロ ッ ク (CLB) の機能に ついて説明 し てい ます。 • 『Virtex-6 FPGA メ モ リ リ ソ ース ユーザーガ イ ド 』 ブ ロ ッ ク RAM と FIFO の機能について説明 し てい ます。

• 『Virtex-6 FPGA GTH ト ラ ン シーバユーザーガ イ ド 』 FF1154 パ ッ ケージの XC6VHX250T お よ び XC6VHX380T を除 く すべての Virtex-6 HXT FPGA で使用可能な GTH ト ラ ン シーバについて説明 し てい ます。 • 『Virtex-6 FPGA GTX ト ラ ン シーバユーザーガ イ ド 』 XC6VLX760 を除 く すべての Virtex-6 FPGA で使用可能な GTX ト ラ ン シーバについて説明 し てい ます。

• 『Virtex-6 FPGA エンベデ ッ ド ト ラ イ モー ド イ ーサネ ッ ト MAC ユーザーガ イ ド 』

XC6VLX760 を除 く すべての Virtex-6 FPGA で使用可能な専用 ト ラ イ モー ド イ ーサネ ッ ト MAC (メ デ ィ アア ク セ ス コ ン ト ロ ー ラ) について説明 し てい ます。

• 『Virtex-6 FPGA DSP48E1 ス ラ イ スユーザーガ イ ド 』

Virtex-6 FPGA の DSP48E1 ス ラ イ ス のアーキテ ク チ ャ について説明 し 、 コ ン フ ィ ギ ュ レー シ ョ ン例 も 記載 し てい ます。

• 『Virtex-6 FPGA シ ス テ ム モニ タユーザーガ イ ド 』

すべての Virtex-6 デバ イ ス で使用可能な System Monitor 機能の概要について説明 し てい ます。 • 『Virtex-6 FPGA PCB デザ イ ンガ イ ド 』 PCB お よ び イ ン タ ーフ ェ イ ス レベルのデザ イ ン を決定す る 方法に焦点を当てた Virtex-6 デバ イ ス の PCB デザ イ ン情報を提供 し ます。

その他の リ ソ ース

シ リ コ ンや ソ フ ト ウ ェ ア、IP に関する ア ンサーデー タ ベース を検索 し た り 、テ ク ニ カルサポー ト の ウ ェ ブケース を開 く 場合は、 次の Web サ イ ト にア ク セ ス し て く だ さ い。 http://japan.xilinx.com/supportク ロ ッ ク

リ ソ ース

グローバル

ク ロ ッ ク、 リ ージ ョ ナル

ク ロ ッ ク、

I/O

ク ロ ッ ク

Virtex®-6 デバ イ ス は、 ク ロ ッ ク の使用を目的 と し て複数の領域に分割 さ れてい ます。 ク ロ ッ ク 領域 数はデバ イ ス のサ イ ズに よ っ て異な り 、最小デバ イ ス で 6 領域、最大デバ イ ス では 18 領域 と な っ て い ます。領域の高 さ は CLB 40 個分で、中央に HROW (Horizontal Clock Row) があ り ます。グ ロ ー バル I/O お よ び リ ージ ョ ナルク ロ ッ ク リ ソ ース は、複雑な も のか ら シ ンプルな も の ま で さ ま ざ ま な 要件を管理 し ます。 ロ ーカル配線な ど の ク ロ ッ ク 以外の リ ソ ース は、 ク ロ ッ ク 機能の実行には推奨 さ れてい ません。

グ ローバル

ク ロ ッ ク

Virtex-6 デバ イ ス には 32 本のグ ロ ーバル ク ロ ッ ク ラ イ ンがあ り 、 こ れ ら を使用 し てデバ イ ス全体 のすべてのシーケ ン シ ャ ル リ ソ ース (CLB、 ブ ロ ッ ク RAM、DSP、I/O) に ク ロ ッ ク を供給で き ま す。 こ れ ら 32 本のグ ロ ーバル ク ロ ッ ク ラ イ ンの う ち 12 本が任意の ク ロ ッ ク 領域で使用可能です。 グ ロ ーバル ク ロ ッ ク を駆動で き る のは、 グ ロ ーバル ク ロ ッ ク バ ッ フ ァ のみです。グ ロ ーバル ク ロ ッ ク は、 ク ロ ッ ク イ ネーブル回路ま たはグ リ ッ チのないマルチプ レ ク サ と し て も 使用で き ます。 ま た、 グ ロ ーバル ク ロ ッ ク を使用す る こ と で、2 つの ク ロ ッ ク リ ソ ース間の選択がで き る だけでな く 、 問題のあ っ た ク ロ ッ ク ソ ース か ら の切 り 替え も 可能です。 通常、 グ ロ ーバル ク ロ ッ クバ ッ フ ァ は、 ク ロ ッ ク 分配遅延を な く すため、 あ る いは別の ク ロ ッ ク に 対す る 遅延を調整す る ために CMT (ク ロ ッ クマネージ メ ン ト タ イ ル) で駆動 さ れます。グ ロ ーバル ク ロ ッ ク 数は CMT よ り 多 く な っ てい ますが、多 く の場合、1 つの CMT で複数のグ ロ ーバルク ロ ッ ク を駆動 し ます。リ ージ ョ ナル

ク ロ ッ ク と

I/O

ク ロ ッ ク

各領域には最大 8 つの差動 リ ージ ョ ナルク ロ ッ クバ ッ フ ァ と 6 つの リ ージ ョ ナルク ロ ッ ク ツ リ ー があ り ます。Virtex-6 FPGA の I/O バン ク は、 正確に 1 ク ロ ッ ク 領域に広がっ てい ます。 それぞれ のバン ク には 4 つの CC (Clock Capable) ク ロ ッ ク 入力があ り ます。各入力は、同 じ バン ク ま たは領 域内にあ る 4 つの I/O ク ロ ッ ク 、4 つの リ ージ ョ ナル ク ロ ッ ク 、1 つの CMT を差動方式ま たはシ ン グルエン ド 方式で駆動で き ます。4 つの I/O ク ロ ッ ク の う ち 2 つは上下に隣接す る バン ク を駆動 で き 、 残 り の 2 つは ロ ーカルバン ク のみを駆動で き ます。 ま た、 リ ージ ョ ナルク ロ ッ ク は、 隣接領 域の リ ージ ョ ナル ク ロ ッ ク ツ リ ーを駆動可能です。CC (Clock Capable) I/O がシ ン グルエン ド ク ロ ッ ク で駆動 さ れてい る 場合、 その ク ロ ッ ク は、 差動 ク ロ ッ ク ピ ンペアの正 (P) 側に接続す る 必要 があ り ます。 負 (N) 側は、 汎用 I/O と し て使用す る か未接続にで き ます。リ ージ ョ ナルク ロ ッ ク バ ッ フ ァ は、 入力 ク ロ ッ ク レー ト を 1 ~ 8 の任意の整数値で分周す る よ う にプ ロ グ ラ ムで き ます。 こ の機能 と IOB のプ ロ グ ラ マブルな SerDes (『Virtex-6 FPGA SelectIO リ ソ ースユーザーガ イ ド 』 の第 3 章を参照) を組み合わせ る と 、 ロ ジ ッ ク リ ソ ース を追加せずに ソ ー ス同期シ ス テ ムにおけ る ク ロ ッ ク ド メ イ ンの切 り 替えがで き ます。

ク ロ ッ キン グ

アーキテ ク チ ャ

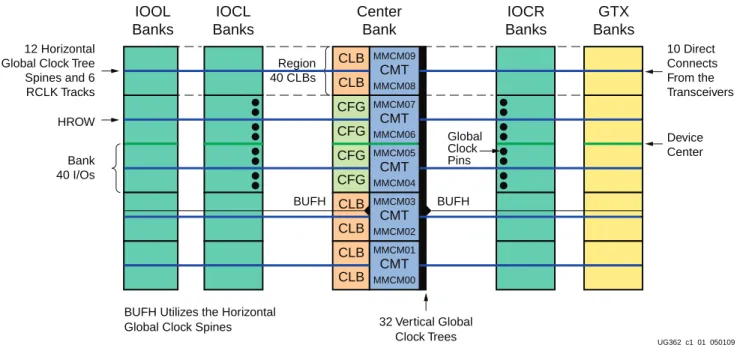

Virtex-6 デバ イ ス には、 専用の コ ン フ ィ ギ ュ レーシ ョ ン ピ ン を含む中央カ ラ ムがあ り ます。 その上 下の領域は CLB と な っ てい ます (ロ ジ ッ ク のみ)。 中央カ ラ ムの右隣には CMT カ ラ ムがあ り 、1 領 域につ き 1 つの CMT があ り ます。 各 CMT には 2 つの MMCM (Mixed-Mode Clock Manager) が 含まれます。 詳細は、第 2 章 「MMCM (Mixed-Mode Clock Manager)」を参照 し て く だ さ い。ま た、 CMT カ ラ ムにはグ ロ ーバル ク ロ ッ ク ツ リ ーの垂直ス パ イ ンが 32 本含まれます。 垂直方向で見 る

と 、Virtex-6 FPGA は領域単位で構成 さ れてい ます (1 領域の高 さ は CLB 40 個分/1 バン ク 分)。 各 領域の中心には HROW (Horizontal Clock Row) があ り 、 こ の中には 12 本の水平 ク ロ ッ ク スパ イ ン、6 つの リ ージ ョ ナル ク ロ ッ ク (BUFR)、 お よ び水平 ク ロ ッ ク (最大 12 BUFH) が含まれます。 BUFH は水平 ク ロ ッ ク ス パ イ ン と 同 じ リ ソ ース を使用 し ます。 こ のアーキ テ ク チ ャ には、新 し い タ

イ プの水平 ク ロ ッ ク ツ リ ー と し て高性能 ク ロ ッ ク が導入 さ れてお り 、MMCM か ら I/O への ク ロ ッ クパ ス におけ る ジ ッ タ の低減を実現 し てい ます。 詳細は、 『Virtex-6 FPGA SelectIO ユーザーガ イ ド 』 を参照 し て く だ さ い。

すべての Virtex-6 FPGA には、中央カ ラ ムの左右に 2 つの I/O カ ラ ム (左側が IOCL、右側が IOCR) があ り 、 こ れ ら の間に CLB が配置 さ れてい ます。LX、LXT、SXT デバ イ スは左端に IOOL (I/O Outer Column) と 呼ばれ る カ ラ ムがあ り 、 デバ イ ス に よ っ ては右端に も I/O カ ラ ム を持つ も のがあ り ます。 右端に I/O カ ラ ム を持たないデバ イ ス では、 代わ り にギガ ビ ッ ト ト ラ ン シーバ (GT) カ ラ ムがあ り ます。 各領域/バン ク の中央には、HROW があ り ます。HROW には、 グ ロ ーバル ク ロ ッ ク バ ッ フ ァ (BUFG) お よ び BUFH の垂直グ ロ ーバルク ロ ッ ク スパ イ ンが含まれます (BUFG が使用 さ れ る と き は BUFH も 使用 さ れます)。 内側の I/O カ ラ ムには 8 つのグ ロ ーバルク ロ ッ ク ピ ンペ ア (GC) が 4 つのバン ク に ま たがっ て配置 さ れてお り 、 各種 I/O 規格に柔軟に対応で き る よ う に な っ てい ます。 ど の I/O カ ラ ムに も 4 つの CC (Clock-Capable) ピ ンペアがあ り 、 こ れ ら は BUFIO お よ び BUFR に接続可能です。各バン ク では、4 つの CC ピ ンの う ち 2 つが隣接す る 領域の BUFIO に接続で き ます。 さ ら に、中央カ ラ ムの BUFR と CC ピ ンは同 じ 領域内の MMCM を直接駆動で き る ほか、BUFG を駆動す る 垂直グ ロ ーバル ク ロ ッ ク ス パ イ ン を経由 し て間接的に BUFG を駆動す る こ と も で き ます。図 1-1に、バン キ ン グお よ びグ ロ ーバル ク ロ ッ キ ン グアーキ テ ク チ ャ の例を概 略図で示 し ます。図 1-2は、 内側に 2 つの I/O カ ラ ム を持つ 1 つの領域での ク ロ ッ キ ン グ を詳細に 示 し た も のです。

X-Ref Target - Figure 1-1

図 1-1 : ブ ロ ッ ク レ ベルのバンキングおよびグローバルク ロ ッ キングアーキテ ク チ ャ の例

IOOL

Banks

IOCL

Banks

Center

Bank

IOCR

Banks

GTX

Banks

HROW BUFH Region 40 CLBs BUFH 12 HorizontalGlobal Clock Tree Spines and 6 RCLK Tracks 10 Direct Connects From the Transceivers Device Center Global Clock Pins Bank 40 I/Os CLB CLB CFG CFG CFG CFG CLB CLB CLB CLB MMCM09 CMT MMCM08 MMCM07 CMT MMCM06 MMCM05 CMT MMCM04 MMCM03 CMT MMCM02 MMCM01 CMT MMCM00

BUFH Utilizes the Horizontal

Global Clock Spines 32 Vertical Global

グローバル

ク ロ ッ ク

リ ソ ース

グ ロ ーバルク ロ ッ ク は、すべての ク ロ ッ ク 入力 と FPGA の さ ま ざ ま な リ ソ ース を接続す る ための専 用ネ ッ ト ワー ク です。 こ れ ら のネ ッ ト ワ ー ク は、 ス キ ュ ー、 デ ュ ーテ ィ サ イ ク ルの歪み、 消費電力 を抑え、 ジ ッ タ 耐性が向上す る よ う に設計 さ れてい ます。 ま た、 非常に高い周波数の信号をサポー ト する よ う に も 設計 さ れてい ます。 グ ロ ーバル ク ロ ッ ク の信号パ ス を理解す る と 、 さ ま ざ ま な グ ロ ーバル ク ロ ッ ク リ ソ ース について も 理解で き る よ う にな り ます。 グ ロ ーバルク ロ ッ ク リ ソ ース と ネ ッ ト ワー ク には、次のパ スお よ び コ ン ポーネ ン ト が含まれます。 • 「グ ロ ーバル ク ロ ッ ク 入力」 • 「グ ロ ーバル ク ロ ッ クバ ッ フ ァ 」 • 「 ク ロ ッ ク ツ リ ー と ネ ッ ト - GCLK」 • 「 ク ロ ッ ク 領域」 X-Ref Target - Figure 1-2図 1-2 : 内側に 2 つの I/O カ ラ ムを持つ領域の ク ロ ッ キン グ構造

CMT

IOCL

Bank

40 I/OsIOCR

Bank

40 I/Os MMCM X0Yn In Same Region MMCM X0Yn In Same Region To Bank Above SRCC Pin Pair MRCC Pin Pair MRCC Pin Pair SRCC Pin Pair SRCC Pin Pair Two Single Region BUFIOs Two Multi-Region BUFIOsTwo BUFRs Two BUFRs

MRCC Pin Pair HROW HROW To Outer Columns Clocking Region 40 CLBs High To Outer Columns MRCC Pin Pair SRCC Pin Pair To Bank Above To Bank Below SRCC = Single Region Clock Capable I/O MRCC = Multi Region Clock Capable I/O

Single ended clocks must be connected to the P-side of the differential pair.

To Bank Below

4 4

4 4

グ ローバル

ク ロ ッ ク入力

Virtex-6 FPGA には、 ク ロ ッ ク 入力 と し て使用 し ない場合は通常のユーザー I/O と し て使用で き る 特別な グ ロ ーバルク ロ ッ ク 入力があ り ます。各デバ イ ス には 8 つのグ ロ ーバルク ロ ッ ク 入力があ り ます。 ク ロ ッ ク 入力は、 差動 I/O 規格 も 含め、 任意の I/O 規格に コ ン フ ィ ギ ュ レーシ ョ ン可能です。 各 ク ロ ッ ク 入力は、 シ ン グルエン ド 方式ま たは差動方式のいずれかにで き 、 必要であれば 8 つの ク ロ ッ ク 入力すべて を差動方式 と す る こ と も で き ます。 出力 と し て使用す る 場合、 グ ロ ーバル ク ロ ッ ク 入力ピ ンは、 任意の出力規格に コ ン フ ィ ギ ュ レーシ ョ ン可能です。各グ ロ ーバルク ロ ッ ク 入力ピ ンは、 シ ン グルエン ド 出力規格ま たはすべての差動出力規格をサポー ト し ます。 グ ロ ーバルク ロ ッ ク 入力は内側の I/O カ ラ ムにあ る 4 つのバン ク に分散 さ れてお り 、I/O 規格を柔軟に選択で き る よ う にな っ てい ます。

グ ローバル

ク ロ ッ ク 入力バ ッ フ ァ のプ リ ミ テ ィ ブ

表 1-1に、 入力 ク ロ ッ ク I/O の入力バ ッ フ ァ のプ リ ミ テ ィ ブ を示 し ます。IOSTANDARD 属性を適切な規格に設定す る と 、 こ れ ら 2 つのプ リ ミ テ ィ ブを Virtex-6 FPGA の SelectIO™ リ ソ ース と 組み合わせて使用で き る よ う にな り ます。 使用可能な I/O 規格の詳細は、 『Virtex-6 FPGA SelectIO リ ソ ースユーザーガ イ ド 』 の第 1 章を参照 し て く だ さ い。

ク ロ ッ ク

ゲーテ ィ ン グに よ る消費電力削減

Virtex-6 FPGA の ク ロ ッ ク アーキ テ ク チ ャ では、デザ イ ンへの電力供給を部分的に停止す る ク ロ ッ ク ゲーテ ィ ン グ を簡単な方法で実装で き ます。 ほ と ん ど の場合、 デザ イ ンには未使用の BUFGCE リ ソ ース がい く つか含まれます。BUFGCE は、 入力を 1 つの ク ロ ッ ク で駆動可能で、 出力は複数の 異な る ロ ジ ッ ク 領域を駆動で き ます。 た と えば、 常時動作 さ せ る 必要のあ る ロ ジ ッ ク をすべて少数 の ク ロ ッ ク 領域に制約 し ておけば、BUFGCE 出力に よ っ て こ れ ら の領域を駆動で き ます。BUFGCE の イ ネーブル信号を ト グルす る こ と で、 ロ ジ ッ ク 領域のダ イ ナ ミ ッ ク 消費電力を完全に停止で き る ため、 消費電力を簡単に削減で き ます。消費電力の削減量は、XPE (Xilinx Power Estimator) や XPower (Xilinx Power Analyzer) を使用 し て概算で き ます。電力の差分は対応す る ク ロ ッ ク ネ ッ ト の周波数を 0MHzに設定す る か、 ツールに 適切な ス テ ィ ミ ュ ラ ス を入力 し て算出 し ます。

グ ローバル

ク ロ ッ ク

バ ッ フ ァ

各 Virtex-6 デバ イ ス には 32 個のグ ロ ーバル ク ロ ッ クバ ッ フ ァ があ り ます。グ ロ ーバルク ロ ッ ク 入 力は、 差動入力ピ ンペアの P 側か ら グ ロ ーバルク ロ ッ クバ ッ フ ァ 入力のいずれかに直接接続で き ます。グ ロ ーバルク ロ ッ ク ピ ン入力は 8 つあ り ます。従来の Virtex アーキ テ ク チ ャ と は異な り 、上 下半分の同 じ 側 と い う 制約はあ り ません。差動グ ロ ーバルク ロ ッ ク ピ ンのペアは、それぞれ PCB 上 の差動ま たはシ ン グルエン ド ク ロ ッ ク のいずれかに接続で き ます。シ ン グルエン ド ク ロ ッ ク を使用 す る 場合、 ピ ンペアの P 側を使用す る 必要があ り ます。 こ れは、 直接接続 さ れてい る のが こ の ピ ン だけであ る ためです。 ピ ンの命名規則については、Virtex-6 パ ッ ケージ仕様を参照 し て く だ さ い。シ ン グルエン ド ク ロ ッ ク を差動ピ ンペアの P 側に接続 し た場合、N 側を別のシ ン グルエン ド ク ロ ッ ク ピ ン と し て使用す る こ と はで き ませんが、 ユーザー I/O と し ては使用可能です。 表 1-1 : ク ロ ッ ク バ ッ フ ァ のプ リ ミ テ ィ ブ プ リ ミ テ ィ ブ 入力 出力 説明 IBUFG I O シ ン グルエン ド I/O の入力 ク ロ ッ ク バ ッ フ ァ IBUFGDS I、IB O 差動 I/O の入力 ク ロ ッ ク バ ッ フ ァデバ イ ス の上半分にあ る MMCM はデバ イ ス の上半分にあ る BUFG し か駆動で き ず、 下半分の MMCM は下半分の BUFG し か駆動で き ません。 同様に、MMCM への フ ィ ー ド バ ッ ク と し て使用 で き る のは、MMCM と デバ イ ス の同 じ 側 (上半分ま たは下半分) にあ る BUFG に限 ら れます。 グ ロ ーバル ク ロ ッ ク バ ッ フ ァ を使用す る と 、 ク ロ ッ ク や信号な ど の ソ ース か ら グ ロ ーバル ク ロ ッ ク ツ リ ーお よ びネ ッ ト へのア ク セ ス が可能にな り ます。 グ ロ ーバル ク ロ ッ ク バ ッ フ ァ への入力に 使用で き る ソ ース は、 次の と お り です。 • グ ロ ーバルク ロ ッ ク 入力 • 内側の I/O カ ラ ム と 同 じ 領域にあ る CC 入力 • ク ロ ッ クマネージ メ ン ト タ イ ル (CMT) : 1 つの CMT に含ま れ る 2 つの MMCM がデバ イ ス の同 じ 側にあ る BUFG を駆動 • ほかのグ ロ ーバルク ロ ッ ク バ ッ フ ァ 出力 (BUFG) • 汎用 イ ン タ ー コ ネ ク ト • リ ージ ョ ナルク ロ ッ ク バ ッ フ ァ (BUFR) • ギガ ビ ッ ト ト ラ ン シーバ Virtex-6 FPGA の ク ロ ッ ク 兼用 (CC) 入力は、MMCM カ ラ ムにあ る 垂直 ク ロ ッ ク ネ ッ ト ワー ク を 経由 し て間接的にグ ロ ーバル ク ロ ッ クバ ッ フ ァ を駆動で き ます。32 個の BUFG はデバ イ ス のそれ ぞれ 16 個ずつ 2 つのグループに分かれてい ます。BUFG に直接接続す る リ ソ ース (GTX ト ラ ン シーバな ど) にはすべて こ の上半分/下半分の制限があ り ます。 た と えば、 上半分にあ る MMCM は 同 じ デバ イ ス の上半分にあ る 16 個の BUFG し か駆動で き ません。 同様に、 下半分の MMCM で駆 動で き る のは下半分の 16 個の BUFG のみに限 ら れます。 すべてのグ ロ ーバル ク ロ ッ クバ ッ フ ァ は、Virtex-6 デバ イ ス の全 ク ロ ッ ク 領域を駆動可能です。 た だ し 、1 つの ク ロ ッ ク 領域で駆動で き る ク ロ ッ ク は 12 ま でです。ク ロ ッ ク 領域は ク ロ ッ ク ツ リ ーの ブ ラ ンチであ り 、 上下 20 個ずつの CLB 行で構成 さ れてい ます (高 さ は CLB 40 個分)。 その幅はデ バ イ ス の半分です。 ク ロ ッ クバ ッ フ ァ は、2 つの ク ロ ッ ク 入力を備えた同期ま たは非同期のグ リ ッ チのない 2:1 マルチ プ レ ク サ と し て使用で き る よ う に設計 さ れてい ます。Virtex-6 デバ イ ス の制御ピ ンには幅広い機能 があ り 、効率的な入力切 り 替えが可能です。次のセ ク シ ョ ン以降は、Virtex-6 FPGA の ク ロ ッ ク バ ッ フ ァ の各種構成、 プ リ ミ テ ィ ブ、 使用モデルについて説明 し てい ます。

グ ローバル

ク ロ ッ ク

バ ッ フ ァ のプ リ ミ テ ィ ブ

表 1-2に、 グ ロ ーバル ク ロ ッ クバ ッ フ ァ のプ リ ミ テ ィ ブを示 し ます。 表 1-2 : グローバルク ロ ッ ク バ ッ フ ァ のプ リ ミ テ ィ ブ プ リ ミ テ ィ ブ 入力 出力 制御BUFGCTRL I0、I1 O CE0、CE1、IGNORE0、IGNORE1、S0、S1

BUFG I O – BUFGCE I O CE BUFGCE_1 I O CE BUFGMUX I0、I1 O S BUFGMUX_1 I0、I1 O S BUFGMUX_CTRL I0、I1 O S メ モ : 1. すべてのプ リ ミ テ ィ ブは、BUFGCTRL の ソ フ ト ウ ェ アプ リ セ ッ ト か ら 派生 し た も のです。

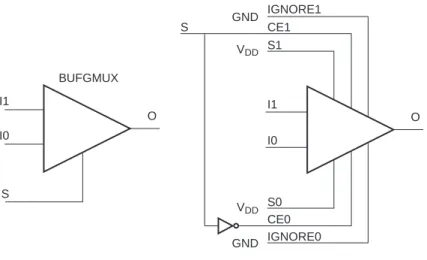

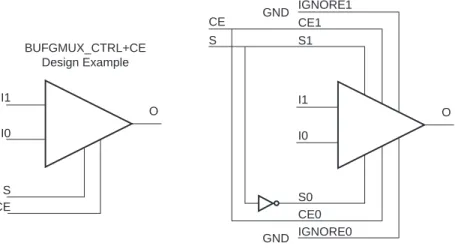

BUFGCTRL

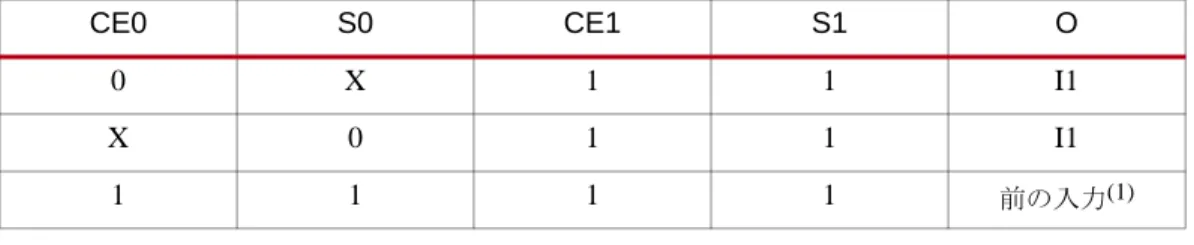

BUFGCTRL プ リ ミ テ ィ ブ (図 1-3を参照) では、2 つの非同期 ク ロ ッ ク の切 り 替えが可能です。 そ の他のグ ロ ーバルク ロ ッ クバ ッ フ ァ プ リ ミ テ ィ ブはすべて BUFGCTRL の コ ン フ ィ ギ ュ レーシ ョ ンか ら 派生 し た も のです。こ れ ら のプ リ ミ テ ィ ブの コ ン フ ィ ギ ュ レーシ ョ ンは、ISE

®

ソ フ ト ウ ェ アツールに よ り 管理 さ れます。BUFGCTRL には、S0、S1、CE0、CE1 の 4 つのセ レ ク ト ラ イ ン と IGNORE0 お よ び IGNORE1 の 2 つの制御 ラ イ ンがあ り ます。こ れ ら の 6 つの制御 ラ イ ン を使用 し て入力 I0 と I1 を制御 し ます。

BUFGCTRL は、2 つの ク ロ ッ ク 入力を グ リ ッ チな し で切 り 替え る よ う 設計 さ れてい ます。S0 と S1 の変化後に選択 さ れてい る ク ロ ッ ク が High か ら Low に切 り 替わ る と 、 出力は も う1 つの ク ロ ッ ク が High か ら Low に遷移す る ま で Low を維持 し ます。 その後、 新 し い ク ロ ッ ク が出力を駆動 し 始 め ます。 デフ ォ ル ト の コ ン フ ィ ギ ュ レーシ ョ ンでは BUFGCTRL は立ち下が り エ ッ ジ を認識、 入力 が切 り 替わ る 前は Low に保持 さ れ る よ う にな っ てい ますが、立ち上が り エ ッ ジ を使用 し て High を 保持す る よ う に も 設定で き ます。 アプ リ ケーシ ョ ンに よ っ ては、上記の よ う な切 り 替え条件が適 さ ない場合 も あ り ます。 その場合は、 IGNORE ピ ン を アサー ト す る と BUFGCTRL は 2 つの ク ロ ッ ク 入力の切 り 替え条件を検出 し な く な り ます。つま り 、IGNORE を アサー ト する と セ レ ク ト ピ ンの変化 と 同時にマルチプ レ ク サの入力 が切 り 替わ り ます。IGNORE0 を アサー ト す る と I0 入力か ら 切 り 替わ り 、IGNORE1 を アサー ト す る と I1 入力か ら 切 り 替わ り ます。

入力 ク ロ ッ ク は、S0 と CE0 か S1 と CE1 のペアの ど ち ら かが High にアサー ト さ れなければ選択 で き ません。S か CE の ど ち ら かが High にアサー ト さ れていない と き は、必要な入力が選択 さ れま せん。 通常は、 両方のペア (4 つのすべてのセ レ ク ト ラ イ ン) が同時に High にアサー ト さ れ る こ と はあ り ません。セ レ ク ト ラ イ ン と し て使用す る のはセ レ ク ト ペアの一方の ピ ンのみで、 も う 一方は High に固定 さ れます。表 1-3はその真理値表です。

X-Ref Target - Figure 1-3

図 1-3 : BUFGCTRL プ リ ミ テ ィ ブ 表 1-3 : ク ロ ッ ク リ ソ ースの真理値表 CE0 S0 CE1 S1 O 1 1 0 X I0 1 1 X 0 I0 IGNORE1 IGNORE0 CE1 CE0 S1 S0 I1 I0 O BUFGCTRL UG362_c1_03_040209

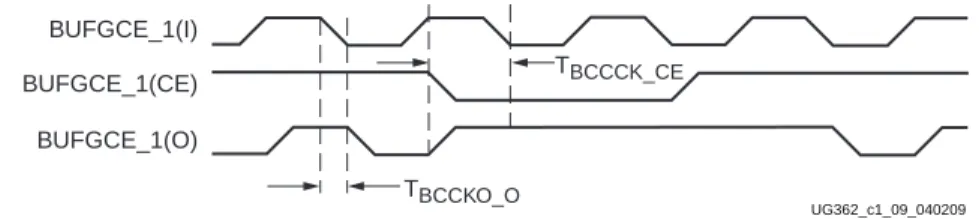

S と CE はど ち ら も 目的の出力を選択す る ために使用 し ますが、 ピ ンの動作はやや異な り ます。CE を使用す る と 、S を使用す る よ り も 高速に ク ロ ッ ク を切 り 替え る こ と がで き ます。CE ピ ン でセ ッ ト ア ッ プ/ホール ド タ イ ム違反があ る と 、 ク ロ ッ ク 出力でグ リ ッ チが発生 し ます。 一方、S ピ ン を使用 す る と 、 セ ッ ト ア ッ プ/ホール ド タ イ ム と 無関係に、2 つの ク ロ ッ ク 入力を切 り 替え る こ と がで き ま す。 こ の際、 グ リ ッ チは発生 し ません。 詳細は、「BUFGMUX_CTRL」を参照 し て く だ さ い。 CE ピ ンは従来の Virtex アーキ テ ク チ ャ と の互換性があ り ます。 図 1-4の タ イ ミ ン グ図は、BUFGCTRL プ リ ミ テ ィ ブ を使用 し た場合の ク ロ ッ ク の切 り 替わ り を示 し てい ます。 正確な タ イ ミ ン グ値は、 ス ピー ド フ ァ イ ルか ら 求め る こ と がで き ます。 • タ イ ム イ ベン ト 1 の前は、 出力 O に入力 I0 が選択 さ れてい ます。

• タ イ ム イ ベン ト 1 の立ち上が り エ ッ ジ よ り TBCCCK_CE前に、CE0 と S0 が Low にデ ィ アサー ト さ れます。 こ れ と ほぼ同時に、CE1 と S1 が High にアサー ト さ れます。

• タ イ ム イ ベン ト 3 よ り TBCCKO_O後に、 出力 O が入力 I1 に切 り 替わ り ます。 こ れは、I0 が High か ら Low にな り (イ ベン ト 2)、I1 が High か ら Low にな る と 発生 し ます。

0 X 1 1 I1 X 0 1 1 I1 1 1 1 1 前の入力(1) メ モ : 1. 前の入力 と は、 こ の ス テー ト に移行す る 前の有効な入力 ク ロ ッ ク の こ と です。 2. こ れ以外の ス テー ト ではすべて、 出力が INIT_OUT 値にな り 、 ト グル し ません。 表 1-3 : ク ロ ッ ク リ ソ ースの真理値表 (続き) CE0 S0 CE1 S1 O

X-Ref Target - Figure 1-4

図 1-4 : BUFGCTRL の タ イ ミ ング図

I0

I1

S0

S1

IGNORE0

IGNORE1

O

CE0

CE1

1 2 3 4 5 6 TBCCCK_CE UG362_c1_04_040209TBCCKO_O TBCCKO_O TBCCKO_O

• タ イ ム イ ベン ト 4 で IGNORE1 がアサー ト さ れます。

• タ イ ム イ ベン ト 5 で CE0 と S0 が High にアサー ト さ れ、CE1 と S1 が Low にデ ィ アサー ト さ れます。 タ イ ム イ ベン ト 6 よ り TBCCKO_O後に、 出力 O の入力が I1 か ら I0 に切 り 替わ り ます。 こ の際、I1 が High か ら Low に切 り 替わ る 必要はあ り ません。 BUFGCTRL には、 ほかに次の よ う な機能があ り ます。 • I0 と I1 入力は、 コ ン フ ィ ギ ュ レーシ ョ ン後、デバ イ ス が動作を開始す る 前にあ ら か じ め選択 さ れます。 • コ ン フ ィ ギ ュ レーシ ョ ン後の最初の出力には、High ま たは Low の ど ち ら で も 選択で き ます。 • CE0 と CE1 のみを使用 し て ク ロ ッ ク を選択 (S0 と S1 を High に固定) し た場合、 前に選択 さ

れた ク ロ ッ ク の High か ら Low への遷移を待つ こ と な く 別の ク ロ ッ ク を選択で き ます。 表 1-4に、BUFGCTRL プ リ ミ テ ィ ブの属性を示 し ます。

BUFG

BUFG は、 ク ロ ッ ク 入力 と ク ロ ッ ク 出力を各 1 つ持つ入力 ク ロ ッ クバ ッ フ ァ です。 こ のプ リ ミ テ ィ ブは BUFGCTRL に対 し て、 一部の ピ ン を ロ ジ ッ ク High ま たは Low に固定 し た も のです。図 1-5

に、BUFG と BUFGCTRL の関係を示 し ます。BUFG には LOC 制約を使用で き ます。 表 1-4 : BUFGCTRL 属性 属性名 説明 設定可能な値 INIT_OUT コ ン フ ィ ギ ュ レーシ ョ ン後に BUFGCTRL 出力を特 定の値に初期化 し ます。 立ち上が り エ ッ ジ と 立ち下 が り エ ッ ジのいずれを使用す る か を設定 し ます。 ま た、 ク ロ ッ ク の選択を切 り 替えた と き の出力レベル を設定 し ます。 0 (デフ ォ ル ト)、1 PRESELECT_I0 TRUE の場合、 コ ン フ ィ ギ ュ レーシ ョ ン後の BUFGCTRL の出力に I0 入力が選択 さ れます。(1) FALSE (デフ ォ ル ト)、 TRUE PRESELECT_I1 TRUE の場合、 コ ン フ ィ ギ ュ レーシ ョ ン後の BUFGCTRL の出力に I1 入力が選択 さ れます。(1) FALSE (デフ ォ ル ト)、 TRUE メ モ : 1. 2 つの PRESELECT 属性を同時に TRUE にはで き ません。 2. LOC 制約を使用で き ます。

図 1-6の タ イ ミ ン グ図に示す よ う に、 出力には入力 と 同 じ 波形が現れます。

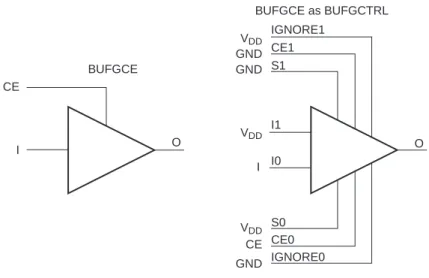

BUFGCE および BUFGCE_1

BUFG と は異な り 、BUFGCE は ク ロ ッ ク 入力、 ク ロ ッ ク 出力、 ク ロ ッ ク イ ネーブルラ イ ン を 1 つ ずつ持つ ク ロ ッ ク バ ッ フ ァ です。 こ のプ リ ミ テ ィ ブは BUFGCTRL に対 し て、一部の ピ ン を ロ ジ ッ ク High ま たは Low に固定 し た も のです。図 1-7に、BUFGCE と BUFGCTRL の関係を示 し ます。 BUFGCE と BUFGCE_1 には LOC 制約を使用で き ます。

X-Ref Target - Figure 1-5

図 1-5 : BUFG と BUFGCTRL の関係

X-Ref Target - Figure 1-6

図 1-6 : BUFG の タ イ ミ ング図

X-Ref Target - Figure 1-7

図 1-7 : BUFGCE と BUFGCTRL の関係 IGNORE1 IGNORE0 CE1 CE0 S1 S0 I1 I0 O BUFG UG362_c1_05_040209 VDD GND VDD VDD VDD I O I GND GND BUFG(I) BUFG(O) TBCCKO_O UG362_c1_06_040209 IGNORE1 IGNORE0 CE1 CE0 S1 S0 I1 I0 O BUFGCE BUFGCE as BUFGCTRL UG362_c1_07_040209 VDD GND VDD CE VDD O I I CE GND GND

BUFGCE の切 り 替え条件は BUFGCTRL と 同様です。入力 ク ロ ッ ク の立ち上が り エ ッ ジ前に CE 入 力が Low にな る場合は、 その後の入力 ク ロ ッ クパルスは出力に送信 さ れず、 出力は Low に保たれ ます。入力 ク ロ ッ ク が High の間に CE が変化 し て も 、ク ロ ッ ク が Low にな る ま で出力に影響はあ り ません。ク ロ ッ ク がデ ィ ス エーブルにな る と 出力は Low の ま ま と な り ます。ただ し 、ク ロ ッ ク がデ ィ ス エーブルにな る時点での ク ロ ッ ク High パルスは出力 さ れます。 ク ロ ッ ク イ ネーブルラ イ ンに BUFGCTRL の CE ピ ン を使用す る ため、セ レ ク ト 信号はセ ッ ト ア ッ プ タ イ ム要件を満たす必要があ り ます。 こ の条件に違反す る と グ リ ッ チが発生 し ます。図 1-8に、 BUFGCE の タ イ ミ ン グ図を示 し ます。 BUFGCE_1 は BUFGCE と 類似 し てい ますが、 入力の切 り 替え条件のみ異な り ます。 入力 ク ロ ッ ク の立ち下が り エ ッ ジ前に CE 入力が Low の場合は、その後の入力 ク ロ ッ クパルスは出力に送信 さ れ ず、 出力は High の ま ま です。 入力 ク ロ ッ ク が Low の間に CE が変化 し て も 、 ク ロ ッ ク が High にな る ま で出力に影響はあ り ません。 ク ロ ッ ク がデ ィ ス エーブルにな る と 出力は High のま ま と な り ま す。 ただ し、 ク ロ ッ ク がデ ィ ス エーブルにな る時点での ク ロ ッ ク Low パルス は出力 さ れます。 図 1-9に、BUFGCE_1 の タ イ ミ ン グ図を示 し ます。 BUFGMUX および BUFGMUX_1 BUFGMUX は ク ロ ッ ク 入力 2 つ と 、 ク ロ ッ ク 出力、 ク ロ ッ ク イ ネーブル ラ イ ン を 1 つずつ持つ ク ロ ッ ク バ ッ フ ァ です。 こ のプ リ ミ テ ィ ブは BUFGCTRL に対 し て、 一部の ピ ン を ロ ジ ッ ク High ま たは Low に固定 し た も のです。図 1-10 に、BUFGMUX と BUFGCTRL の関係を示 し ます。 BUFGMUX と BUFGCTRL の ど ち ら に も LOC 制約を使用で き ます。

X-Ref Target - Figure 1-8

図 1-8 : BUFGCE の タ イ ミ ン グ図

X-Ref Target - Figure 1-9

図 1-9 : BUFGCE_1 の タ イ ミ ング図 BUFGCE(I) BUFGCE(CE) BUFGCE(O) UG362_c1_08_040209 TBCCKO_O TBCCCK_CE BUFGCE_1(I) BUFGCE_1(CE) BUFGCE_1(O) UG362_c1_09_040209 TBCCKO_O TBCCCK_CE

BUFGMUX は CE ピ ン を セ レ ク ト ピ ン と し て使用す る ため、 セ レ ク ト を使用す る 場合は、 セ ッ ト ア ッ プ タ イ ム要件を満た し てい る 必要があ り ます。セ ッ ト ア ッ プ タ イ ム違反があ る と 、 グ リ ッ チが 発生す る 可能性があ り ます。

BUFGMUX の入力切 り 替え条件は BUFGCTRL の CE ピ ン と 同様です。図 1-11に、BUFGMUX の タ イ ミ ン グ図を示 し ます。

図 1-11の説明

• 現在の ク ロ ッ ク は I0 です。 • S が High に変化 し ます。

• マルチプ レ ク サは I0 が Low か ら High にアサー ト さ れ る のを待ち ます。

• I0 が High にな る と 、I1 が High にな る ま でマルチプ レ ク サの出力は High に保たれます。 • I1 が Low か ら High に切 り 替わ る と 、 出力は I1 に切 り 替わ り ます。

• セ ッ ト ア ッ プ/ホール ド タ イ ム要件が満た さ れてい る 場合、 出力にグ リ ッ チやシ ョ ー ト パルス は発生 し ません。

X-Ref Target - Figure 1-10

図 1-10 : BUFGMUX と BUFGCTRL の関係

X-Ref Target - Figure 1-11

図 1-11 : BUFGMUX の タ イ ミ ング図 IGNORE1 IGNORE0 CE1 S CE0 S1 S0 I1 I0 O BUFGMUX UG362_c1_10_040209 VDD VDD O I1 I0 S GND GND S I 0 I1 O TBCCKO_O ug362_c1_11_040209 TBCCKO_O TBCCCK_CE begin switching using I1

BUFGMUX_1 は立ち上が り エ ッ ジ を認識 し 、入力が切 り 替わ る ま で High に保持 さ れます。図 1-12

に、BUFGMUX_1 の タ イ ミ ン グ図を示 し ます。BUFGMUX お よ び BUFGMUX_1 には LOC 制約 を使用で き ます。

図 1-12の説明

• 現在の ク ロ ッ ク は I0 です。 • S が High に変化 し ます。

• マルチプ レ ク サは I0 が High か ら Low にデ ィ アサー ト さ れ る のを待ち ます。

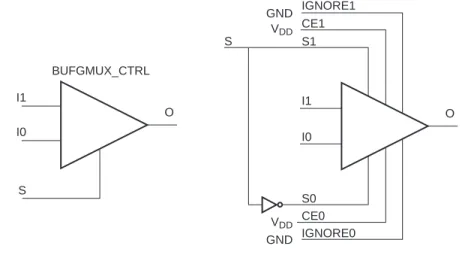

• I0 が Low にな る と 、I1 が Low にな る ま でマルチプ レ ク サの出力は Low に保たれます。 • I1 が High か ら Low に切 り 替わ る と 、 出力が I1 に切 り 替わ り ます。 • セ ッ ト ア ッ プ/ホール ド タ イ ム要件が満た さ れてい る 場合、 出力にグ リ ッ チやシ ョ ー ト パルス は発生 し ません。 BUFGMUX_CTRL BUFGMUX_CTRL は、 従来の BUFGMUX_VIRTEX4 プ リ ミ テ ィ ブに代わ る も のです。 BUFGMUX_CTRL は 2 つの ク ロ ッ ク 入力 と 1 つの ク ロ ッ ク 出力、そ し て 1 つのセ レ ク ト ラ イ ン を 持つ ク ロ ッ ク バ ッ フ ァ です。 こ のプ リ ミ テ ィ ブは BUFGCTRL に対 し て、 一部の ピ ン を ロ ジ ッ ク High ま たは Low に固定 し た も のです。図 1-13に、BUFGMUX_CTRL と BUFGCTRL の関係を 示 し ます。

X-Ref Target - Figure 1-12

図 1-12 : BUFGMUX_1 の タ イ ミ ン グ図

X-Ref Target - Figure 1-13

図 1-13 : BUFGMUX_CTRL と BUFGCTRL の関係 S I0 I1 O ug362_c1_12_040209 TBCCCK_CE TBCCKO_O IGNORE1 IGNORE0 CE1 S CE0 S1 S0 I1 I0 O BUFGMUX_CTRL ug362_c1_13_051809 VDD VDD O I1 I0 S GND GND

BUFGMUX_CTRL では、S ピ ンがセ レ ク ト ピ ン と し て使用 さ れます。S はグ リ ッ チを発生 さ せず にいつで も 切 り 替え可能です。S のセ ッ ト ア ッ プ/ホール ド タ イ ムに よ っ て、 新 し い ク ロ ッ ク への切 り 替え前に、その前の ク ロ ッ ク の余分なパルス が出力 さ れ る かが決ま り ます。図 1-14の よ う に、セ ッ ト ア ッ プタ イ ム TBCCCK_Sよ り 前、I0 が High か ら Low にな る 前に S が変化 し た場合、I0 の余分 なパルス は出力 さ れません。S がホール ド タ イ ムの後に変化 し た場合は、 余分なパルス が出力 さ れ ます。S がセ ッ ト ア ッ プ/ホール ド タ イ ムに違反す る と 、 余分なパルス が出力 さ れ る こ と も あ り ます が、 グ リ ッ チは発生 し ません。 いずれの場合で も 、 出力は遅い方の ク ロ ッ ク の 3 ク ロ ッ ク サ イ ク ル 分以内に新 し い ク ロ ッ ク に変わ り ます。 S0 と S1 のセ ッ ト ア ッ プ/ホール ド タ イ ムの要件は、CE0 と CE1 の よ う な立ち上が り エ ッ ジではな く 、 立ち下が り エ ッ ジが基準 と な っ てい ます。 BUFGMUX_CTRL の入力切 り 替え条件は BUFGCTRL の S ピ ン と 同様です。図 1-14に、 BUFGMUX_CTRL の タ イ ミ ン グ図を示 し ます。 BUFGMUX_CTRL には、 その他次の よ う な機能があ り ます。 • コ ン フ ィ ギ ュ レーシ ョ ン後の I0 お よ び I1 入力を あ ら か じ め選択で き ます。 • コ ン フ ィ ギ ュ レーシ ョ ン後の最初の出力は、High ま たは Low の ど ち ら にで も 設定で き ます。

その他の使用モデル

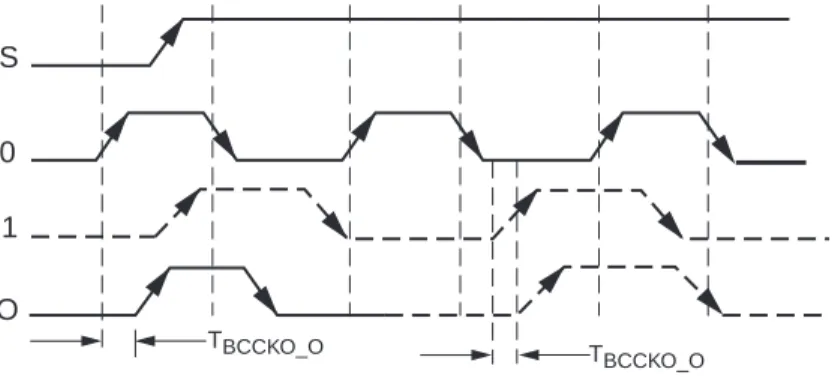

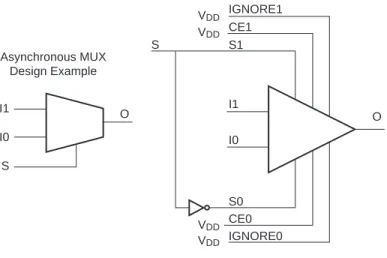

BUFGCTRL を使用 し た非同期 MUX アプ リ ケーシ ョ ンに よ っ ては、 ク ロ ッ ク 入力の即座の切 り 替えや BUFGCTRL のエ ッ ジ認識の無視 が必要 と な り ます。た と えば、ク ロ ッ ク 入力の 1 つが ト グルを停止 し てい る よ う な場合、BUFGCTRL では ク ロ ッ ク エ ッ ジが認識 さ れないため、ク ロ ッ ク 出力の切 り 替え条件は成立 し ません。こ の よ う な 場合には非同期 MUX (マルチプ レ ク サ) を使用 し ます。図 1-15に、BUFGCTRL を使用し た非同期 MUX のデザ イ ン例を示し ます。図 1-16は、 非同期 MUX の タ イ ミ ン グ図です。X-Ref Target - Figure 1-14

図 1-14 : BUFGMUX_CTRL の タ イ ミ ング図

S

I 0

I1

O

ug362_c1_14_040209 TBCCKO_O TBCCKO_O図 1-16の説明 • 現在の ク ロ ッ ク は I0 です。 • S が High に変化 し ます。 • 直後に ク ロ ッ ク 出力が I1 に切 り 替わ り ます。 • IGNORE 信号が High にアサー ト さ れ る と 、 グ リ ッ チを発生 さ せない よ う にす る 機能はデ ィ ス エーブルにな り ます。

X-Ref Target - Figure 1-15

図 1-15 : BUFGCTRL を使用 し た非同期マルチ プ レ ク サのデザイ ン例 X-Ref Target - Figure 1-16

図 1-16 : 非同期マルチ プ レ ク サの タ イ ミ ング図 IGNORE1 IGNORE0 CE1 S CE0 S1 S0 I1 I0 S I1 I0 O Asynchronous MUX Design Example ug362_c1_15_040209 VDD VDD VDD VDD O UG362_c1_16_040209 TBCCKO_O TBCCKO_O

I0

I1

S

O

at I0 Begin I1ク ロ ッ ク イ ネーブル付き BUFGMUX_CTRL ク ロ ッ ク イ ネーブル付 き の BUFGMUX_CTRL を使用す る と 、 入力 ク ロ ッ ク を選択で き ます。 ク ロ ッ ク イ ネーブルを使用 し 、 出力をデ ィ ス エーブルにす る こ と も 可能です。図 1-17に、 BUFGCTRL を使用 し たデザ イ ン例を示 し ます。図 1-18は、 その タ イ ミ ン グ図です。 図 1-18の説明 • タ イ ム イ ベン ト 1 で出力 O に入力 I0 が選択 さ れます。 • タ イ ム イ ベン ト 2 の前に S が High にアサー ト さ れます。 • タ イ ム イベン ト 2 よ り TBCCKO_O後に、 出力 O が入力 I1 に切 り 替わ り ます。こ れは、I0 が High か ら Low にな り 、I1 が High か ら Low にな る と 発生 し ます。

• タ イ ム イ ベン ト 3 よ り TBCCCK_CE前に、CE が Low にアサー ト さ れます。 ク ロ ッ ク 出力は Low に切 り 替わ り 、I1 が High か ら Low に切 り 替わっ た後 も Low に保持 さ れます。

X-Ref Target - Figure 1-17

図 1-17 : CE 付き BUFGMUX_CTRL と BUFGCTRL IGNORE1 IGNORE0 CE1 S CE CE CE0 S1 S0 I1 I0 O BUFGMUX_CTRL+CE Design Example ug362_c1_17_051509 O I1 I0 S GND GND

X-Ref Target - Figure 1-18

図 1-18 : CE 付き BUFGMUX_CTRL の タ イ ミ ング図 ug362_c1_18_040209 TBCCKO_O TBCCCK_CE TBCCKO_O at I0 Clock Off

I0

I1

S

CE

O

Begin I11

2

3

ク ロ ッ ク

ツ リ ー と ネ ッ ト

- GCLK

Virtex-6 ク ロ ッ ク ツ リ ーは、 ス キ ュ ーお よ び消費電力が少な く な る よ う 設計 さ れてい ます。未使用 ブ ラ ンチの接続は切断 さ れます。ま た、 ク ロ ッ ク ツ リ ーは、 ロ ジ ッ ク リ ソ ースすべてが使用 さ れ る 場合に ロ ー ド お よ びフ ァ ン ア ウ ト を制御す る よ う に も 設計 さ れてい ます。 グ ロ ーバル ク ロ ッ ク ラ イ ン と バ ッ フ ァ はすべて、 差動方式で イ ンプ リ メ ン ト さ れます。 こ れに よ り 、 デ ュ ーテ ィ サ イ ク ルお よ び同相 ノ イ ズ除去が改善 し ます。 Virtex-6 アーキ テ ク チ ャ では、 グ ロ ーバル ク ロ ッ ク ラ イ ンのピ ンは ロ ジ ッ ク リ ソ ース の ク ロ ッ ク ピ ンだけでな く 、CLB のほかの ピ ン (SR や CE な ど の制御ピ ン) も 駆動で き ます。 こ のアーキ テ ク チ ャ は、 高速信号接続や大容量の ロ ー ド お よ び大 き い フ ァ ン ア ウ ト が必要なアプ リ ケーシ ョ ンに適 し てい ます。ク ロ ッ ク 領域

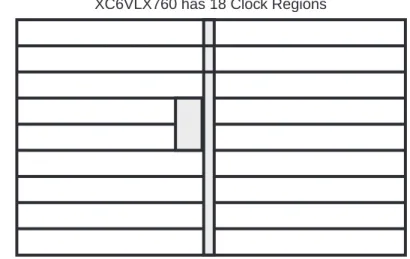

Virtex-6 デバ イ ス では、 ク ロ ッ ク 領域の使用に よ っ て ク ロ ッ ク 分配が改善 さ れてい ます。 各 ク ロ ッ ク 領域には最大 12 のグ ローバルク ロ ッ ク ド メ イ ン を含め る こ と がで き ます。 こ れ ら 12 のグ ロ ーバル ク ロ ッ ク は、32 個のグ ローバルク ロ ッ ク バ ッ フ ァ を自由に組み合わせて駆動で き ます。 ク ロ ッ ク 領 域の寸法は CLB 20 個分 (IOB 40 個) の高 さ 、 チ ッ プの 1/2 の幅に固定 さ れてい ます (図 1-19)。 こ の よ う に ク ロ ッ ク 領域の寸法を固定する こ と で、 大規模な Virtex-6 デバ イ ス に さ ら に多 く の ク ロ ッ ク 領域が含まれ る よ う にな り ま し た。こ のため、Virtex-6 デバ イ ス では従来の FPGA アーキテ ク チ ャ よ り も 多 く の ク ロ ッ ク ド メ イ ン をサポー ト で き る よ う にな っ てい ます。表 1-5に、 各 Virtex-6 デバ イ ス の ク ロ ッ ク 領域数を示 し ます。CMT と グ ロ ーバルク ロ ッ ク リ ソ ースは、コ ン フ ィ ギ ュ レーシ ョ ン ピ ン を含む中央カ ラ ムの右側に配置 さ れてい ます。X-Ref Target - Figure 1-19

図 1-19 : ク ロ ッ ク 領域

ug362_c1_19_040209

All clock regions are 40 CLBs tall (20 CLBs above and 20 CLBs below a horizontal row)

XC6VLX75T has 6 Clock Regions

XC6VLX760 has 18 Clock Regions

CMT Column Resources Center Column Configuration Resources 20 CLBs 20 CLBs

All clock regions span half the die All clock regions

リ ージ ョ ナル

ク ロ ッ ク

リ ソ ース

リ ージ ョ ナルク ロ ッ ク ネ ッ ト ワー ク は、 グ ロ ーバルク ロ ッ ク ネ ッ ト ワー ク か ら 独立 し た ク ロ ッ ク ネ ッ ト ワー ク です。グ ロ ーバルク ロ ッ ク と は異な り 、 リ ージ ョ ナルク ロ ッ ク 信号 (BUFR) は 3 つの ク ロ ッ ク 領域ま で し か到達 し ません。2 つの I/O ク ロ ッ ク 信号で 1 つの領域を駆動 し 、 ほかの 2 つ の I/O ク ロ ッ ク でその上下の領域/バン ク を駆動で き ます。 こ れ ら ネ ッ ト ワー ク は、 特に ソ ース同期 イ ン タ ーフ ェ イ ス のデザ イ ンで有用です。Virtex-6 デバ イ ス の I/O バン ク のサ イ ズは、 ク ロ ッ ク 領 域のサ イ ズ と 同一です。 リ ージ ョ ナルク ロ ッ ク の理解には、 リ ージ ョ ナル ク ロ ッ ク 信号のパ ス についての理解が必要です。 Virtex-6 デバ イ ス の リ ージ ョ ナル ク ロ ッ ク リ ソ ースお よ びネ ッ ト ワー ク は、次のパ ス と コ ン ポーネ ン ト で構成 さ れてい ます。 • 「CC (Clock-Capable、 ク ロ ッ ク 兼用) I/O」 • 「I/O ク ロ ッ クバ ッ フ ァ - BUFIO」 • 「 リ ージ ョ ナルク ロ ッ クバ ッ フ ァ - BUFR」 • 「 リ ージ ョ ナルク ロ ッ ク ネ ッ ト 」 • 「水平 ク ロ ッ ク バ ッ フ ァ - BUFH」 • 「高性能 ク ロ ッ ク 」 表 1-5 : Virtex-6 FPGA のク ロ ッ ク 領域数 デバイ ス ク ロ ッ ク領域数 XC6VLX75T 6 XC6VLX130T 10 XC6VLX195T 10 XC6VLX240T 12 XC6VLX365T 12 XC6VLX550T 18 XC6VLX760 18 XC6VSX315T 12 XC6VSX475T 18 XC6VHX250T 12 XC6VHX255T 12 XC6VHX380T 18 XC6VHX565T 18CC (Clock-Capable

、 ク ロ ッ ク兼用

) I/O

いずれの ク ロ ッ ク 領域に も 、各 I/O カ ラ ムの I/O バン ク ご と に 4 つの CC I/O ピ ンペアがあ り ます。 こ れ ら の I/O ペアは通常の I/O ペア と 同 じ ですが、 限定 さ れた場所にあ り 、 近 く の リ ージ ョ ナル ク ロ ッ ク リ ソ ースやその他の ク ロ ッ ク リ ソ ース に特別にハー ド ウ ェ ア接続可能です。 各バン ク には、 CC I/O 専用のサ イ ト が 4 つあ り ます。CC ピ ン を ク ロ ッ ク 入力 と し て使用す る 場合、BUFIO お よ び BUFR を駆動で き ます。各 I/O カ ラ ムは リ ージ ョ ナルク ロ ッ クバ ッ フ ァ (BUFR) をサポー ト し 、 各デバ イ ス には最大 4 つの I/O カ ラ ムがあ り ます。 内側の 2 つの I/O カ ラ ムはすべてのデバ イ ス に 用意 さ れてお り 、1 領域で 4 つの BUFR をサポー ト し ます。 デバ イ ス に よ っ ては、 外側に最大 2 つ の I/O カ ラ ム を備えてい ます。 シ ン グルエン ド ク ロ ッ ク ピ ン と し て使用す る 場合は、「グ ロ ーバル ク ロ ッ クバ ッ フ ァ 」で説明 し て い る よ う に、 ピ ンペアの P 側を使用す る 必要があ り ます。 こ れは、P 側の ピ ン し か直接接続 さ れて いないためです。

Virtex-6 デバ イ ス では、内側の I/O カ ラ ムの CC ピ ンで MMCM お よ び BUFG の ク ロ ッ ク 入力を駆 動す る こ と がで き ます。こ の方法で MMCM 入力 ク ロ ッ ク を駆動す る と 、グ ロ ーバルク ロ ッ ク ピ ン を使用 し て ク ロ ッ ク を MMCM に接続 し た場合 よ り も パ ス の性能が向上 し ます。CC ピ ンは、 MMCM と 同 じ 領域/バン ク で MMCM の左右いずれかの側になければな り ません。

I/O

ク ロ ッ ク

バ ッ フ ァ

- BUFIO

I/O ク ロ ッ クバ ッ フ ァ (BUFIO) は、Virtex-6 デバ イ ス で使用可能な ク ロ ッ ク バ ッ フ ァ です。BUFIO は I/O カ ラ ム内の専用 ク ロ ッ ク ネ ッ ト を駆動 し 、 グ ロ ーバル ク ロ ッ ク リ ソ ース か ら は独立 し てい ます。 こ のため、BUFIO は ソ ース同期デー タキ ャ プチ ャ (ク ロ ッ ク を転送/受信 し て分配す る) に最 適です。BUFIO を駆動で き る のは、同 じ バン ク 内の CC I/O のみです。1 つの ク ロ ッ ク 領域には、各 バン ク に 4 つの BUFIO があ り ます。デバ イ ス に よ っ ては、1 つの領域に 2 つのバン ク (内側 と 外側 のカ ラ ム) を持つ も の も あ り ます。 各 BUFIO は同 じ 領域/バン ク にあ る 1 つの I/O ク ロ ッ クネ ッ ト ワー ク を駆動で き 、4 つの BUFIO の う ち 2 つがその上下の領域を駆動で き ます。I/O ク ロ ッ ク ネ ッ ト ワー ク の範囲は同 じ バン ク/ク ロ ッ ク 領域ま たはその上下のバン ク/ク ロ ッ ク 領域の I/O カ ラ ム ま でなので、BUFIO で ロ ジ ッ ク リ ソ ース (CLB、 ブ ロ ッ ク RAM、DSP な ど) は駆動で き ません。

BUFIO

プ リ ミ テ ィ ブ

BUFIO は ク ロ ッ ク 信号を入力 し て出力す る シ ンプルなバ ッ フ ァ です。 入力 と 出力間には位相遅延 があ り ます。図 1-20に BUFIO を示 し ます。ポー ト については、表 1-6を参照 し て く だ さ い。BUFIO には配置制約を使用で き ます。X-Ref Target - Figure 1-20

図 1-20 : BUFIO プ リ ミ テ ィ ブ 表 1-6 : BUFIO のポー ト と 定義 ポー ト 名 タ イ プ 幅 定義 O 出力 1 ク ロ ッ ク 出力ポー ト I 入力 1 ク ロ ッ ク 入力ポー ト BUFIO ug362_c1_20_040209 O I

BUFIO

の使用モデル

図 1-21では、BUFIO が CC I/O を使用 し て I/O ロ ジ ッ ク を駆動 し てい ます。こ の イ ンプ リ メ ン テー シ ョ ンは、 転送 ク ロ ッ ク を使用 し て入力デー タ を キ ャ プチ ャ す る ソ ース同期アプ リ ケーシ ョ ンに最 適です。

X-Ref Target - Figure 1-21

図 1-21 : BUFIO によ る I/O ロ ジ ッ クの駆動 I/O I/O I/O I/O I/O I/O I/O BUFIO BUFIO BUFR BUFR ug362_c1_21_061009

To Fabric

To Adjacent

Region

To Adjacent

Bank

To Adjacent

Region

To Adjacent

Bank

I/O I/O I/OClock Capable I/O Multiple Regions I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O P N P N P N P N

Not all available BUFIOs are shown. Clock Capable I/O

Multiple Regions Clock Capable I/O Single Region

Clock Capable I/O Single Region

リ ージ ョ ナル

ク ロ ッ ク

バ ッ フ ァ

- BUFR

リ ージ ョ ナル ク ロ ッ クバ ッ フ ァ (BUFR) も 、Virtex-6 デバ イ ス で使用可能な ク ロ ッ ク バ ッ フ ァ で す。BUFR は、 ク ロ ッ ク 領域内の専用 ク ロ ッ クネ ッ ト に ク ロ ッ ク 信号を送信 し 、 グ ロ ーバル ク ロ ッ ク ツ リ ーか ら は独立 し てい ます。 各 BUFR は、 その領域内の 6 つの リ ージ ョ ナル ク ロ ッ クネ ッ ト と 、隣接す る ク ロ ッ ク 領域 (すなわち最大で 3 つの ク ロ ッ ク 領域) の 6 つの ク ロ ッ ク ネ ッ ト を駆動で き ます。BUFIO と 異な り 、BUFR は I/O ロ ジ ッ ク だけでな く 、同 じ ク ロ ッ ク 領域お よ び隣接す る ク ロ ッ ク 領域の ロ ジ ッ ク リ ソ ース (CLB、 ブ ロ ッ ク RAM な ど) も 駆動で き ます。BUFR は CC ピ ン、 ロ ーカル イ ン タ ー コ ネ ク ト 、GT、MMCM 高性能 ク ロ ッ ク で駆動可能です。 ま た、 ク ロ ッ ク 入力信 号を分周 し た ク ロ ッ ク も 出力で き ます。分周値は 1 ~ 8 の整数です。BUFR は ク ロ ッ ク ド メ イ ンの 切 り 替えやシ リ アルか ら パ ラ レルへの変換が必要な ソ ース同期アプ リ ケーシ ョ ンに適 し てい ます。 各 I/O カ ラ ムは リ ージ ョ ナルク ロ ッ クバ ッ フ ァ をサポー ト し てい ます。各デバ イ ス には最大 4 つの I/O カ ラ ムがあ り ます (中央左右に内側の 2 つのカ ラ ム、 その左右外側に最大 2 つのカ ラ ム)。 内側 のカ ラ ムはすべてのデバ イ ス にあ り ますが、外側のカ ラ ムの有無はデバ イ ス に よ っ て異な り ます。し たがっ て、Virtex-6 アーキ テ ク チ ャ では 1 つの領域に最大 4 つの BUFR があ り 、その う ちの 2 つは 内側のカ ラ ムか ら 外に駆動 し (すべてのデバ イ ス に存在)、 残 り の 2 つは外側の I/O カ ラ ムか ら 内に 駆動 し ます (該当デバ イ ス のみ)。Virtex-6 デバ イ ス では、BUFR で MMCM ク ロ ッ ク 入力 と BUFG を直接駆動す る こ と も で き ます。

BUFR

プ リ ミ テ ィ ブ

BUFR (図 1-22、表 1-7) は ク ロ ッ ク 入力 と ク ロ ッ ク 出力があ る バ ッ フ ァ で、 入力 ク ロ ッ ク 周波数を 分周で き ます。 ま た、Virtex-6 FPGA の BUFR は、MMCM ク ロ ッ ク 入力 と BUFG を直接駆動す る こ と も で き ます。

X-Ref Target - Figure 1-22

図 1-22 : BUFR プ リ ミ テ ィ ブ 表 1-7 : BUFR のポー ト と 定義 ポー ト 名 タ イ プ 幅 定義 O 出力 1 ク ロ ッ ク 出力ポー ト CE 入力 1 ク ロ ッ ク イ ネーブルポー ト 。 バ イ パ スモー ド では使用不可 CLR 入力 1 分周用の非同期 ク リ アで、出力を Low にす る 。バ イ パ スモー ド では使用不可 I 入力 1 ク ロ ッ ク 入力ポー ト CLR CE I O ug362_c1_22_040209

CE ピ ンに関する追加記述

CE がアサー ト/デ ィ アサー ト さ れ る と 、出力 ク ロ ッ ク 信号はオン/オ フ にな り ます。 グ ロ ーバルセ ッ ト/ リ セ ッ ト (GSR) 信号が High の場合、BUFR は CE が High に保持 さ れていて も ト グル し ませ ん。 ク ロ ッ ク が BUFR 入力ポー ト につながっ てい る 場合、BUFR 出力は GSR 信号のデ ィ アサー ト 後に ト グル し ます。

BUFR

の属性 と モー ド

BUFR での ク ロ ッ ク 分周は、ソ フ ト ウ ェ アで BUFR_DIVIDE 属性を設定す る こ と で指定で き ます。 表 1-8に、BUFR_DIVIDE 属性で設定可能な値を示 し ます。

BUFR の伝搬遅延は、BUFR_DIVIDE = 1 と BUFR_DIVIDE = BYPASS で異な り ます。 1 に設定 し た場合の遅延は BYPASS よ り も わずかに多 く な り ます。 その他の分周値を設定 し た場合 も 、 BUFR_DIVIDE = 1 の と き と 同 じ 伝搬遅延 と な り ます。 入力 ク ロ ッ ク と 出力 ク ロ ッ ク の位相関係 も 、BYPASS 以外のすべての分周値で同 じ です。 BUFR_DIVIDE 属性を使用 し た場合の BUFR の入力 と 出力の タ イ ミ ン グ関係は、図 1-23を参照 し て く だ さ い。 こ の例では、BUFR_DIVIDE = 3 に設定 し てい ます。 こ の図の前の時点で、CLR がア サー ト さ れてい ます。 図 1-23の説明 • ク ロ ッ ク イ ベン ト 1 の前に CE が High にアサー ト さ れます。 • CE がアサー ト さ れ、TBRCKO_O後に出力 O が入力 I を 3 分周 し た周波数で ト グルを開始 し ま す。TBRCKO_Oお よ びその他の タ イ ミ ン グ値は、ス ピー ド フ ァ イ ルに正確に記載 さ れてい ます。 メ モ : 奇数で分周 し た場合のデ ュ ーテ ィ サ イ ク ルは 50/50 にな り ません。Low パルス の方が I の 1 サ イ ク ル分だけ長 く な り ます。 表 1-8 : BUFR_DIVIDE 属性 属性名 説明 設定可能な値 BUFR_DIVIDE 入力 ク ロ ッ ク を分周す る 値を指定 1, 2, 3, 4, 5, 6, 7, 8 BYPASS (デフ ォ ル ト) メ モ : 1. BUFR には配置制約を使用で き ます。

X-Ref Target - Figure 1-23

図 1-23 : BUFR_DIVIDE の属性値を使用 し た BUFR の タ イ ミ ング図

ug362_c1_23_040209

TBRCKO_O TBRDO_CLRO TBRCKO_O I

CE CLR O

• タ イ ム イ ベン ト 2 で CLR がアサー ト さ れます。 タ イ ム イ ベン ト 2 の TBRDO_CLRO時間後、O の ト グルが停止 し ます。 • タ イ ム イ ベン ト 3 で CLR がデ ィ アサー ト さ れます。 • タ イ ム イ ベン ト 4 の TBRCKO_O後に、I を 3 で割っ た周波数で O が再び ト グルを開始 し ます。

BUFR

の使用モデル

BUFRは ク ロ ッ ク ド メ イ ン の切 り 替えやシ リ アルか ら パ ラ レ ルへの変換が必要な ソ ー ス 同期アプ リ ケーシ ョ ンに適 し てい ます。BUFIO と は異な り 、BUFR は IOB 以外の FPGA の ロ ジ ッ ク リ ソ ー ス に ク ロ ッ ク を供給で き ます。図 1-24に、BUFR のデザ イ ン例を示 し ます。X-Ref Target - Figure 1-24

図 1-24 : BUFR によ る各種ロ ジ ッ ク リ ソ ースの駆動 ug362_c1_24_040209 CLBs CLBs CLBs CLBs CLBs CLBs CLBs CLBs Block RAM Block RAM DSP Tile DSP Tile BUFR

To Region

Above

To more

FPGA logic

resources

To Region

Below

I/O Tile I/O Tile I/O Tile I/O Tile I/O Tile I/O Tile I/O Tile I/O Tile BUFIO Clock Capable I/Oリ ージ ョ ナル

ク ロ ッ ク

ネ ッ ト

Virtex-6 デバ イ ス には、グ ロ ーバルク ロ ッ ク ツ リ ーお よ びネ ッ ト だけでな く 、 リ ージ ョ ナル ク ロ ッ ク ネ ッ ト も 含まれます。 ク ロ ッ ク ツ リ ーは、 ス キ ュ ーお よ び消費電力が少な く な る よ う 設計 さ れて い ます。 未使用ブ ラ ンチの接続は切断 さ れます。 ま た、 ク ロ ッ ク ツ リ ーは、 ロ ジ ッ ク リ ソ ースすべ てが使用 さ れ る 場合に ロ ー ド お よ びフ ァ ン ア ウ ト を制御す る よ う に も 設計 さ れてい ます。 リ ージ ョ ナルク ロ ッ ク ネ ッ ト は Virtex-6 デバ イ ス全体ではな く 、1 つの ク ロ ッ ク 領域内でのみ伝搬 で き ます。1 つの ク ロ ッ ク 領域には 6 つの独立 し た リ ージ ョ ナルク ロ ッ クネ ッ ト があ り ます。 リ ージ ョ ナルク ロ ッ クネ ッ ト にア ク セ スする には、BUFR を イ ン ス タ ン シエー ト する必要があ り ま す。BUFR は最高で 2 つの隣接する ク ロ ッ ク 領域の リ ージ ョ ナルク ロ ッ ク を駆動で き ます (図 1-25)。 上辺ま たは下辺の領域にあ る BUFR は、 隣接する 1 つの領域にのみア ク セ ス で き ます。 ま た、 左側 の BUFR は中央にあ る I/O カ ラ ムに入力可能です。X-Ref Target - Figure 1-25

図 1-25 : BUFR によ る複数領域の駆動

ug362_c1_25_011609

水平ク ロ ッ ク

バ ッ フ ァ

- BUFH

水平 ク ロ ッ ク バ ッ フ ァ (BUFH) は、1 つの領域内で水平グ ロ ーバル ク ロ ッ ク ツ リ ースパ イ ン を駆 動 し ます (図 1-26)。1 つの領域には 12 の BUFH があ り ます。 ど の BUFH に も ク ロ ッ ク イ ネーブ ル (CE) ピ ンがあ り 、ク ロ ッ ク を動作中ににオ フ にで き ます。BUFH は次の方法で中央か ら 駆動で き ます。 • 同 じ 領域内の MMCM 出力 • BUFG 出力 • ロ ーカル イ ン タ ー コ ネ ク ト • 水平 ク ロ ッ ク 領域に隣接す る 左ま たは右にあ る 内側カ ラ ムのバン ク か ら のCC I/O BUFH を使用す る には、図 1-27に示す よ う に互いに隣接す る 左右 2 つの領域に ロ ジ ッ ク が収ま っ ていなければな り ません。 ク ロ ッ ク イ ネーブルピ ンは電力の供給を完全に遮断で き る ため、消費電 力の削減に役立ち ます。こ のため、BUFG を使用す る よ り も BUFH を使用 し て 2 つの隣接す る 領域 を駆動 し た方が、 ジ ッ タ が少な く 高性能な上、 消費電力 も 抑え る こ と がで き ます。X-Ref Target - Figure 1-26

図 1-26 : BUFH および BUFHCE プ リ ミ テ ィ ブ 表 1-9 : UFH および BUFHCE のポー ト と 定義 ポー ト 名 タ イ プ 幅 定義 O 出力 1 ク ロ ッ ク 出力ポー ト CE 入力 1 ク ロ ッ ク イ ネーブルポー ト I 入力 1 ク ロ ッ ク 入力ポー ト I O ug362_c1_26_040209 CE I O

BUFH

BUFHCE

高性能 ク ロ ッ ク

Virtex-6 デバ イ ス には、各 I/O カ ラ ムに 4 つの高性能 ク ロ ッ ク (HPC) があ り ます。こ れは、MMCM か ら 各領域へ供給 さ れ、その領域の内側お よ び外側の I/O カ ラ ム (GTX ト ラ ン シーバカ ラ ム を含む ) へ接続 さ れます。こ れ ら の ク ロ ッ ク (図 1-28) は MMCM に よ っ て安定化 さ れた電源で直接駆動 さ

れ、VCCINT電源 ド メ イ ンに入 る こ と はあ り ません。し たがっ て、非常にジ ッ タ が少な く 、デ ュ ーテ ィ

サ イ ク ルの歪み も 最小限に抑え ら れてい ます。HPC は I/O カ ラ ム で BUFIO に接続 し 、I/O ロ ジ ッ ク を駆動 し ます。4 つの HPC の う ち 2 つは、複数領域の BUFIO を使用せずに上下のI/Oバン ク を 直接駆動で き ます。 ま た、HPCは別の ク ロ ッ ク バ ッ フ ァ を経由 し な く て も OSERDES に直接接続 で き ます。こ のため、低ジ ッ タ でデュ ーテ ィ サ イ ク ルの歪み も 小 さ い ク ロ ッ ク 転送が可能です。HPC に、 関連付け ら れたバ ッ フ ァ はあ り ません。ISE ソ フ ト ウ ェ アは、 デザ イ ンにおけ る IOLOGIC (OLOGIC) への接続をチ ェ ッ ク し 、こ の リ ソ ース をいつ使用す る かを自動的に判断 し ます。HPC は、 同 じ 領域内の BUFR を駆動 し て ソ ース同期 イ ン タ ーフ ェ イ ス デザ イ ン をサポー ト す る こ と も で き ます。CMT 内のいずれの MMCM (CLKOUT0 ~ CLKOUT3) も 右側ま たは左側の領域にあ る HPC を駆動可能です。

X-Ref Target - Figure 1-27

図 1-27 : 水平ク ロ ッ クバ ッ フ ァ ug362_c1_27_040209

CMT and Cloc

king Column

BUFH BUFH Clocking Region 12 12VHDL

および

Verilog

テ ン プ レー ト

すべての ク ロ ッ キ ン グ リ ソ ース用の VHDL と Verilog コ ー ド お よ び ISE 言語テ ンプ レー ト が 『 ラ イ ブ ラ リ ガ イ ド 』 か ら 利用可能です。

X-Ref Target - Figure 1-28

図 1-28 : 高性能ク ロ ッ ク (HPC) OSERDES OSERDES BUFIOs BUFR BUFR BUFIOs OSERDES OSERDES OSERDES OSERDES BUFIOs BUFR BUFR BUFIOs OSERDES OSERDES

To Bank Above From Bank Above From Bank Above To Bank Above

To Bank Below From Bank Below From Bank Below To Bank Below

IOCL Bank 40 1/Os IOCR Bank 40 1/Os HPC To Outer Column HPC To Outer Column or GTX HPC[3:0] HPC[3:0] MMCM X0Yn In The Same Region

MMCM X0Yn In The Same Region

CLKOUT[3:0] CLKOUT[3:0] CMT 2 2 2 2 2 2 2 4 4 4 4 4 4 4 2 4 4 4 2 2 2 2 UG362_c1_28_011609 Notes:

1) Any of the MMCM CLKOUT[3:0] outputs can drive any of the HPC[3:0] to the inner or outer columns or GTX column (outer I/O and GTX column not shown).

2) HPCs can drive OSERDES directly. The same two HPCs can drive directly OSERDES in the adjacent Banks. 3) Any MMCM CLKOUT[3:0] can drive any BUFIO and any BUFR.