http://onsemi.jp

LV4904V

概要 LV4904Vは、ディジタル入力対応の高性能・高効率の音響用2チャンネルDクラスアンプである。1チ ップでしかも少ない外付け部品でDクラスアンプが実現可能となっている。ポップレスのソフトミ ュート・ゲインコントローラを内蔵しており、セットのマスターボリュームとしても利用できる。 I2Cバスインターフェースを介して各種機能設定を行えるが、I2Cを使用せずに端子設定のみで機能 設定を行うことも可能となっている。LV4904Vはミニコンポ、薄型テレビ、アミューズメント機器、 電子楽器等のパワーアンプに適している。 特長 ・I2S入力、2チャンネルD級パワーアンプ ・可変倍オーバーサンプラ内蔵 ・ゲインコントローラ(+12dB∼-81dB、1.5dBステップ) ・ソフトミュート ・I2Cバス、もしくは端子設定により制御 ・電源電圧低下保護回路、過電流保護回路、熱保護回路を搭載 仕様 ・入力PCM(Fs) :32kHz/44.1kHz/48kHz/88.1kHz/96kHz/176.2kHz/192kHz ・マスタクロック入力 :256fs/384fs/512fs/768fs(Fs=32/44.1/48kHzの時) ・入力フォーマット :I2S/24bit前詰MSB-First/24bit後詰LSB-First/16/18/20/24bit後詰 MSB-First ・出力 :10W×2ch(PVD=15V,RL=8Ω),15W×2ch(PVD=18V,RL=8Ω) ・効率 :85%(PVD=15V,RL=8Ω,fin=1kHz,PO=10W) ・THD+N :0.1%(PVD=15V,RL=8Ω,fin=1kHz,PO=1W,フィルタ:AES17) ・電源電圧 :PVD=8∼20V、VDD=3.3V ・パッケージ :SSOP44J(275mil) モノリシック集積回路ディジタル入力D級

パワーアンプ

絶対最大定格/Ta=25℃ 項目 記号 条件 定格値 unit パワーセル電源 PVD 外部印加電圧 -0.3∼24 V ロジック電源 VDD 外部印加電圧 -0.3∼4.0 V 最大接合部温度 Tj max 125 ℃ 動作周囲温度 Topr −30∼+70 ℃ 保存周囲温度 Tstg −50∼+150 ℃ 推奨動作条件/Ta=25℃

項目 記号 条件 min typ max unit

パワーセル電源 PVD 外部印加電圧 8 13 20 V

ロジック電源 VDD 外部印加電圧 3.0 3.3 3.6 V

負荷 RL スピーカ負荷 8 - - Ω

電気的特性

項目 記号 条件 min typ max unit

ディジタル/Ta=25℃,VDD=3.3V,PVD=13V スタンバイ電流 IPD - 1 10 μA 動作時電流 IOP - 12 30 mA H入力電圧 VIHHIS 0.8VDD - 5.5 V L入力電圧 VILHIS -0.3 - 0.2VDD V H入力電流 IH VIN=VDD - - 10 μA L入力電流 IL VIN=GND -10 - - μA IOH VOUT=VDD-0.4V -0.8 - - mA 出力端子電流 IOL VOUT=0.4V 1 - - mA パワー/Ta=25℃,VDD=3.3V,PVD=13V,RL=8Ω,L=22μH(TOKO:A7040HN-220M),C=33μF,Fin=1KHz

スタンバイ電流 IST PVD,RSTB=Low - 1 10 μA ミュート時電流 IMUTE PVD,ENABLE=Low - 1 10 mA 無信号時電流 ICCO PVD,50% duty - 16 60 mA Power Tr ON抵抗※1 RDSON ID=1A - 300 - mΩ 出力電力1 POUT1 8Ω,15V,THD+N=10%,変調度87.5% 9 10 - W 出力電力2 POUT2 8Ω,18V,THD+N=10%,変調度87.5% 12 14 - W 出力ノイズ VN IHF-A - 4 10 mV THD+N THD PO=1W,1kHz,8Ω - 0.1 0.3 % チャンネルセパレー ション CHSEP PO=1W,1kHz,8Ω 40 60 - dB ※1:Power Tr ON抵抗(RDSON)については、設計保証値で最大360mΩである。

注:各特性は、弊社測定環境による値であり、パターンレイアウト、使用部品等により特性が変わる可能性があ る。

最大定格を超えるストレスは、デバイスにダメージを与える危険性があります。最大定格は、ストレス印加に対してのみであり、推奨動作条件を超えての機能 的動作に関して意図するものではありません。推奨動作条件を超えてのストレス印加は、デバイスの信頼性に影響を与える危険性があります。

外形図 unit:mm (typ) 3285 ピン配置図 SANYO : SSOP44J(275mil) 7. 6 15.0 0.65 5. 6 (0.68) (1. 5) 44 23 1 22 0.22 0. 5 0.2 1. 7max SIDE VIEW BOTTOM VIEW TOP VIEW Exposed Die-Pad 23 22 24 21 25 20 26 19 27 18 28 17 29 16 30 15 31 14 32 13 33 12 34 11 35 10 36 9 37 8 38 7 39 6 40 5 41 4 42 3 43 2 44 1

LV4904V

VDD VSS OUT_CH1_P BOOT_CH1_P VDD PGND1 PGND1 A1 OUT_CH1_N BOOT_CH1_N PT AB1 PVD1 TEST MODE MUTEB GAIN5 GAIN4 GAIN3 GAIN2 GAIN1 GAIN0 SDA SCL Pd max -- Ta 0 3.0 1.0 --30 0 30 90 120 2.0 60 1.02 1.32 2.40 1.85アプリケーション回路例 + VD RL 23 22 24 21 25 20 26 19 27 18 28 17 29 16 30 15 31 14 32 13 33 12 34 11 35 10 36 9 37 8 38 7 39 6 40 5 41 4 42 3 43 2 44 1

L

V4904V

VDD RSTB VDD VSS VSS ENABLE MCK BCK LRCK SDIN DFORM0 DFORM1 DFORM2 MCKFS PVD2 OUT_CH2_P BOOT_CH2_P VDD A2 OUT_CH2_N BOOT_CH2_N PGND2 PGND2 PGND1 PGND1 OUT_CH1_P BOOT_CH1_P VDDA1 OUT_CH1_N BOOT_CH1_N PTAB1 PVD1 TEST MODE MUTEB GAIN5 GAIN4 GAIN3 GAIN2 GAIN1 GAIN0 SDA SCL -DC 8-20V + VDD -DC 3.3V RL PTAB2 SRATE I2C Bus Control Signal Mute Signal Reset Signal Enable Signal I2S Inputs Control Signalブロック図 29 28 26 25 30 16 1 12 13 33 32 4 6 3 2 7 8 9 10 11 42 41 40 39 20 19 17 38 37 36 35 RSTB VDD VSS VDD VSS SERIAL/P ARALLEL CONVER TER OVER_SAMPLER VOLUME_CONTROLLER NOISE_SHAPING 5 BCK LRCK SDIN MCK 34 CONTROLLER I2C I/F 43 44 ENABLE DFORM0 DFORM1 DFORM2 MCKFS SRATE GAIN0 GAIN1 GAIN2 GAIN3 GAIN4 GAIN5 MUTEB MODE TEST SDA SCL PWM_CONVER TER PWM RECEIVER PWM RECEIVER CONTROL DELAY OUTPUT STAGE CH1+ OUTPUT STAGE CH1-PWM RECEIVER PWM RECEIVER CONTROL DELAY OUTPUT STAGE CH2-OUTPUT STAGE CH2+ THERMAL OVER CURRENT SEQUENCE PVD1 OUT_CH1_P BOOT_CH1_P OUT_CH1_N BOOT_CH1_N OUT_CH2_P BOOT_CH2_P OUT_CH2_N BOOT_CH2_N 24 PGND1 23 22 21 PGND1 PGND2 PGND2 15 PVD2 REGULATOR (5V) 27 18 VDDA2 VDDA1 31 PTAB1 14 PTAB2 VSS PGND1 PGND2

端子説明 端子 番号 端子記号 I/O 端子機能 等価回路図 1 RSTB DI リセット設定入力(Lowアクティブ) 2 ENABLE DI システムイネーブル設定入力 3 MCK DI マスタクロック入力 4 BCK DI 3線シリアルのビットクロック入力 5 LRCK DI 3線シリアルのLRクロック入力 6 SDIN DI 3線シリアルのシリアルデータ入力 7 DFORM0 DI 入力フォーマット設定入力0 8 DFORM1 DI 入力フォーマット設定入力1 9 DFORM2 DI 入力フォーマット設定入力2 10 MCKFS DI マスタクロック(MCK)レート設定端子 11 SRATE DI 入力データサンプリングレート設定端子 12 VDD - ディジタル系電源(3.3V) 13 VSS - 小信号系グランド(GND) 14 PTAB2 - サブストレートGND 15 PVD2 - パワーセル電源端子 16 OUT_CH2_P O 出力端子、CH2(Rch)+ 16 GND PVD 17 BOOT_CH2_P I/O ブートストラップ入出力端子、CH2(Rch)+ 18 VDDA2 O 内部電源用デカップリングコンデンサ接続 端子 19 BOOT_CH2_N I/O ブートストラップ入出力端子、CH2(Rch)- 20 OUT_CH2_N O 出力端子、CH2(Rch)- 20 GND PVD 21 PGND2 CH2パワーGND 22 PGND2 CH2パワーGND 23 PGND1 CH1パワーGND 24 PGND1 CH1パワーGND 次ページへ続く。

前ページより続く。 端子 番号 端子記号 I/O 端子機能 等価回路図 25 OUT_CH1_N O 出力端子、CH1(Lch)- 25 GND PVD 26 BOOT_CH1_N I/O ブートストラップ入出力端子、CH1(Lch)- 27 VDDA1 O 内部電源用デカップリングコンデンサ接続 端子 28 BOOT_CH1_P O ブートストラップ入出力端子、CH1(Lch)+ 29 OUT_CH1_P O 出力端子、CH1(Lch)+ 29 GND PVD 30 PVD1 - パワーセル電源端子 31 PTAB1 - サブストレートGND 32 VSS - 小信号系GND 33 VDD - ディジタルIO電源(3.3V) 34 TEST DI テストモード設定端子(Low固定) 35 MODE DI 出力モード設定端子 36 MUTEB DI ミュート設定入力(Lowアクティブ) 37 GAIN5 DI ゲイン設定入力5 38 GAIN4 DI ゲイン設定入力4 39 GAIN3 DI ゲイン設定入力3 40 GAIN2 DI ゲイン設定入力2 41 GAIN1 DI ゲイン設定入力1 42 GAIN0 DI ゲイン設定入力0 43 SDA DIO [I2C I/F]データ

44 SCL DI [I2C I/F]ビットクロック

44

1.モード切り替え(I2C/端子併用モード⇔端子制御モード) 1-1.モードの説明 I2Cバス/端子併用モード I2Cバスと端子の両方で機能設定が可能となるモードである。ある端子設定においてはI2Cバスレ ジスタによる設定が有効になり、その他の端子設定時には端子による設定が有効となる。 端子制御モード LV4904Vを端子設定のみで制御するモードである。制御にI2Cバスを必要としない利点があるが、 設定可能なパラメータは制限される。以下の表にI2Cバス経由での設定可能項目と端子のみでの 設定可能項目との相違点を示す。 I2Cバス/端子併用モードと端子制御モードの機能の違い 記号 説明 I2Cバスによる設定 端子による設定 DFORM 入力データフォーマット 7通り 2通り MCKFS マスタクロックMCKレート 4通り(256fs/384fs/512fs/768fs) 2通り(256fs/512fs) SRATE 入力データサンプルレート 32kHz∼192kHz 44.1kHz∼96kHz GAIN ゲインコントローラ設定 2チャンネル独立制御可能 2チャンネル共通制御 MUTE ミュート 2チャンネル独立制御可能 2チャンネル共通制御 PSTP PWM出力停止設定 2チャンネル独立制御可能 2チャンネル共通制御 IDPEN ミュート時50%パルス設定 ON/OFF可能 ON固定

MDIDX 変調度設定 87.5% ⇔ 100%切り替え可能 87.5%固定 NSORD ノイズシェイピング次数 5次 ⇔ 7次切り替え可能 7次固定 1-2.モードの設定方法 I2Cバス/端子併用モード SCL=SDA=Low以外の状態でRSTBをLow → Highにすると、I2Cバス/端子併用モードになる。ただし、 その際にはMCK端子から所定のクロックが入力されている必要がある。 図 I2Cバス/端子併用モードの設定方法 端子制御モード SCL=SDA=Lowの状態でRSTBをLow → Highとすると、端子設定モードになる。ただし、その際には MCK端子から所定のクロックが入力されている必要がある。 図 端子制御モードの設定方法 SCL SDA RSTB SCL SDA RSTB

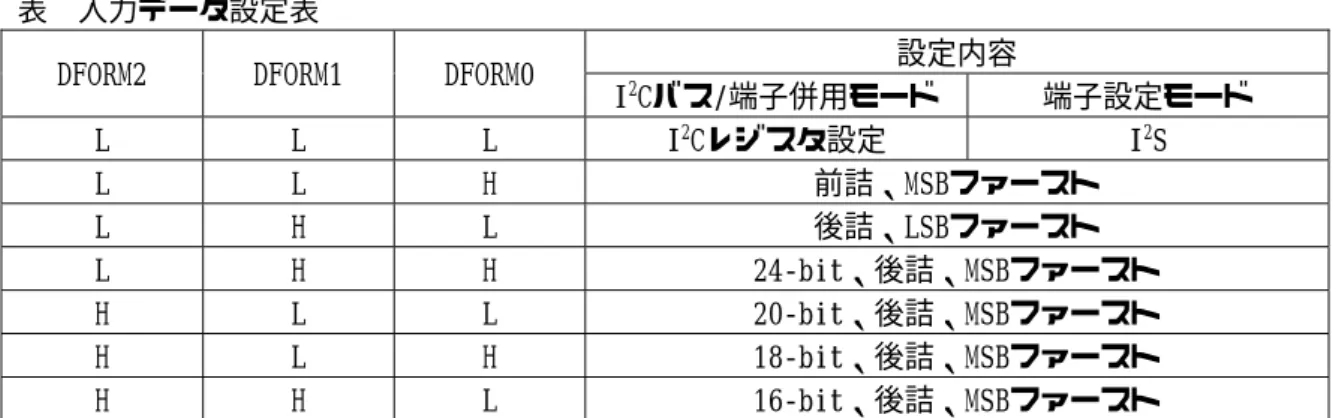

2.端子機能説明 2-1.ハードリセット端子(RSTB) RSTBはLow activeのハードリセット端子である。 RSTB=Lowにする事によりLV4904Vが初期化される。RSTB=Lowとなると内部レジスタがクリアされ、 I2Cバスレジスタも初期値に戻る。 表 RSTBの機能 RSTB 設定内容 L ハードリセット(レジスタクリア) H 通常動作時 2-2.システムイネーブル端子(ENABLE) ENABLEはLV4904Vのシステムイネーブル端子である。 ENABLE=Lowにすると、他のあらゆる設定(ミュート、ゲイン)にかかわらず出力がミュートされ、 PWM出力が停止する(ハイ・インピーダンスにする)。LV4904Vを動作させるには、ENABLE=Highにす る。 ENABLEの機能をON/OFFさせる必要がなければ、ENABLE端子をHighに固定して使用する事も可能であ る。以下の表にENABLEの機能設定を示す。 表 ENABLEの機能設定 ENABLE 設定内容 L システムディセーブル H システムイネーブル 2-3.マスタクロック入力端子 MCKからマスタクロックを入力する。 MCKの詳細は「8-1.入力データ設定」を参照すること。 2-4.3線シリアル入力端子(BCK,LRCK,SDIN) BCK,LRCK,SDINは3線シリアルデータ入力に使用される端子である。 BCK,LRCK,SDINの詳細は「8-1.入力データ設定」を参照すること。 2-5.I2Cバス端子(SCL,SDA) SCL,SDAはI2Cバス通信に使用される端子である。 LV4904VのI2Cバスインターフェースにはマスタとしての機能は無く、スレーブとしてのみ動作する。 I2Cバスクロック端子はSCLであり、入力としてのみ動作する。したがって、LV4904VがSCLラインを Lowにしてwaitを要求する事は無い。I2Cバスデータ端子はSDAで、Nchオープンドレインとなってい るため、データラインはプルアップする必要がある。 I2Cバスインターフェースに関する詳細な内容は、「5.I2Cバス仕様」を参照すること。 2-6.入力データフォーマット設定端子(DFORM0,DFORM1,DFORM2) 入力されるデータフォーマットに合わせるように、DFORM0,DFORM1,DFORM2端子のHigh/Lowを設定す る。I2Cバス/端子併用モードではDFORM0=DFORM1=DFORM2=Lowの時、I2Cレジスタによるデータフォー マット設定(8-1の表)が有効となる。I2Cレジスタの初期設定はI2Sとなっているため、リセット解除 後の初期状態におけるDFORM0=DFORM1=DFORM2=Lowによる設定はI2Sとなる。 DFORM0,DFORM1,DFORM2によるフォーマット設定表を以下に示す。

表 入力データ設定表

設定内容

DFORM2 DFORM1 DFORM0

I2Cバス/端子併用モード 端子設定モード L L L I2Cレジスタ設定 I2S L L H 前詰、MSBファースト L H L 後詰、LSBファースト L H H 24-bit、後詰、MSBファースト H L L 20-bit、後詰、MSBファースト H L H 18-bit、後詰、MSBファースト H H L 16-bit、後詰、MSBファースト 2-7.マスタクロック設定端子(MCKFS) MCK端子から入力されるマスタクロックのレートに合うようにMCKFS端子のHigh/Lowを設定する。 I2Cバス/端子併用モードではMCKFS=Lowの時、I2Cレジスタによるマスタクロック設定(8-2.マスタク ロック設定)が有効となる。I2Cレジスタの初期設定は256fsとなっているため、リセット解除後の 初期状態におけるMCKFS=Lowによる設定は256fsとなる。 MCK端子から入力されるクロックのレートがMCKFS端子やI2Cレジスタによる設定と一致しない場合、 異音が発生したり出力がOFFされたりする。 MCKFSの機能設定を以下に示す。 MCKFSの機能設定 設定内容 MCKFS I2Cバス・端子併用モード 端子設定モード L I2Cレジスタ設定 256fs H 512fs 2-8.サンプルレート設定端子(SRATE) 入力データのサンプルレートに合うようにSRATE端子のHigh/Lowを設定する。 I2Cバス/端子併用モードではSRATE=Lowの時、I2Cレジスタによるサンプルレート設定(8-2.マスタク ロック設定)が有効となる。I2Cレジスタの初期設定は44.1kHz/48kHzとなっているため、リセット 解除後の初期状態におけるSRATE=Lowによる設定は44.1kHz/48kHzとなる。 以下にSRATEの機能設定を示す。 SRATEの機能設定 設定内容 SRATE I2Cバス・端子併用モード 端子設定モード L I2Cレジスタ設定 44.1kHz/48kHz H 88.2kHz/96kHz 2-9.ゲイン設定端子(GAIN0,GAIN1,GAIN2,GAIN3,GAIN4,GAIN5) GAIN0∼GAIN5端子をHigh/Low設定する事によりゲインを設定することが出来る。 I2Cバス/端子併用モードではGAIN0∼GAIN5全てがLowの時、I2Cレジスタによるゲイン設定(8-2.表ゲ イン設定)が有効となる。I2Cレジスタ設定の初期値はミュート状態となっているため、リセット解 除後の初期状態におけるGAIN0∼GAIN5=Lowによる設定はミュートである。 GAIN0∼GAIN5によるゲイン設定表を以下に示す。また、端子6ビットによるゲイン設定はレジスタ6 ビットによるゲイン設定と同じであるので、詳細な設定値については8-2.の表を参照する事。

ゲイン設定表

設定内容

GAIN5 GAIN4 GAIN3 GAIN2 GAIN1 GAIN0

I2Cバス/端子併用モード 端子設定モード H H H H H H +12.0dB H H H H H L +10.5dB H H H H L H +9.0dB … … … (この間1.5dB刻み) H H H L L L +1.5dB H H L H H H 0dB H H L H H L -1.5dB … … … (この間1.5dB刻み) L L L L H L -79.5dB L L L L L H -81.0dB L L L L L L I2Cレジスタ設定 ミュート 2-10.ミュート端子(MUTEB) MUTEBはLch/Rchを共通で制御するLowアクティブのソフトミュート端子である。 I2Cバス/端子併用モードではMUTEB=Lowの時、I2Cレジスタによるミュート設定(8-2.表ミュート設 定)が有効となる。I2Cレジスタ設定の初期値はミュート状態となっているため、リセット解除後の 初期状態におけるMUTEB=Lowによる設定はミュートである。 以下の表にMUTEBの機能設定を示す。 MUTEBの機能設定 設定内容 MUTEB I2Cバス/端子併用モード 端子設定モード L I2Cレジスタ設定 ミュートON H ミュートOFF 2-11.テストモード設定端子(TEST,MODE) TESTとMODEはテスト用端子である。使用時にはTEST=MODE=Lowにすること。以下の表にTEST,MODEの 機能設定を示す。 TEST,MODEの機能設定 TEST,MODE 設定内容 L LV4904V使用時の設定 H 設定禁止

3.起動・終了シーケンス 起動、終了時のポップノイズを低減するために、以下の起動・終了シーケンスを推奨する。 3-1.起動シーケンス 起動シーケンス 3-2.終了シーケンス 終了シーケンス PVD VDD ENABLE RSTB MCK MUTEB MUTEBL_Reg MUTEBR_Reg >8.0V >3.0V >2ms >50ms PVD VDD ENABLE RSTB MUTEB MUTEBL_Reg MUTEBR_Reg OUT_1P/1N OUT2P/2N >1ms >200ms Hi-Z

4.保護回路 LV4904Vは電源電圧低下保護回路、過電流保護回路、熱保護回路を持っている。 4-1.電源電圧低下保護回路 電源電圧保護回路は低電圧での不安定動作を回避するため、PVD端子電圧をモニタし、アタック電 圧(VD=7V typ.)を超えた後、アンプをONにする。また、動作中に何らかの原因でPVD端子電圧が低 下した際の不安定動作も回避できるようにリカバリ電圧(6V typ.)を設定している。アタック電圧 とリカバリ電圧との間には約1Vのヒステリシスを持たせているため、閾値付近での電源電圧低下保 護回路の連続ON/OFFといった不安定動作が防止される。以下に電源電圧低下保護回路の動作模式図 を示す。 電源電圧保護回路動作 また、PDV用一次電源が抜かれた場合のポップ音対策としても使用できるように、MUTE ON時と同様 のシーケンスにてAMPをONするように設計してある。 弊社デモボードでは、一次電源ラインに追加している電源コンデンサ(470μF)に蓄積されている電 荷によって上記処理が行えるように設計してある。 実際のセットでは一次電源が他のブロックにも繋がっているため、立ち下がりの時定数が異なって いる可能性があるので注意すること。

4-2.過電流保護回路 過電流保護回路は出力トランジスタを過電流から守るための回路で、天絡、地絡、負荷ショートに よる過電流を検出し検出電流値が約6Aに達した場合、約20μsec.間出力トランジスタをOFFさせる。 出力トランジスタがOFFして約20μsec.経過後、通常動作に自動復帰し、引き続き過電流が検出さ れれば再度保護動作に入る。この保護動作は過電流の異常状態を一時的に回避する機能であって、 ICが破壊しないことを保証するものではない。下記に過電流保護回路の動作模式図を示す。 過電流保護回路動作イメージ図 過電流保護回路動作イメージ図 IDETECT HOLD TIME

4-3.熱保護回路 熱保護回路はICが異常発熱した場合に、ICの破壊、劣化を防止するための保護回路である。放熱不 足や、誤結線等によりICのジャンクション温度(Tj)が定格以上に上昇した場合、熱保護回路により 出力トタンジスタのハイサイド、ローサイドともにOFFにし、出力をハイ・インピーダンス状態に する。シャットダウン後、ジャンクション温度が低下すると自動復帰する。熱保護回路のアタッ ク・リカバリ温度にはヒステリシスを持たせているため、閾値温度付近での熱回路の連続ON/OFFと いった不安定動作が防止される。 但し、熱保護回路は異常発熱状態を一時的に回避する機能であり、ICが破壊しない事を保証するも のではない。また、熱保護回路の動作温度は保証値ではない。下記に熱保護回路の動作イメージを 示す。 熱保護回路動作

5.I2Cバス仕様 5-1.I2Cバスインターフェース概要 LV4904Vは標準モード(MAX100kHz)に対応している。LV4904VのデバイスIDは11011000(read) / 11011001(write)となっている。LV4904VのI2Cバスインターフェースにはマスタとしての機能は無 く、スレーブとしてのみ動作する。 5-2.I2Cバス転送ルール I2C送受信が行われていないバスフリー状態においては、SCL,SDAともHighである必要がある。SCL, SDAともHighの状態から、SCLをHighにしたままSDAをLowにすることにより通信が開始される。これ をスタートコンディションと呼ぶ。 I2C送受信を終了するにはSCLがHighの状態で、SDAをLowからHighに変化させる。これをストップコ ンディションと呼ぶ。 スタートコンディション送信完了後、続いてデータの転送を開始する。データはマスタ側からスレ ーブ側のLV4904Vへ向かって8ビット単位で送られ、LV4904Vは8ビット受信する毎にSDA端子をLowに して応答する。これをアクノリッジ(ACK)と呼ぶ。送信側はバスをフリーにしてACKに備える。 SCL SDA H H SCL SDA H H SCL

5-3.データライト LV4904Vにデータをライトする場合には、スタートコンディションを送信後、デバイスID、ライト するアドレス、データの順に送信し、最後にストップコンディションを送信する。7ビットのデバ イスIDにリード/ライトフラグビットがつくが、このビットをLowにしてライトモードにする。 5-4.データリード データリードコマンドを送信する事により、LV4904Vのレジスタに保持されているデータをリード する事が出来る。データをリードするには最初にダミーライトサイクルにてアドレスを送信した後 にリスタートする。引き続きリードサイクルにおいてデバイスIDとリードフラグを送信すると、 LV4904Vはダミーライトサイクルで送信されたアドレスのデータをSDAラインに出力する。送信側は、 I2Cバスをフリー状態にしてデータ受信に備える。データ受信後はACKをかえさずストップコンディ ションを送信し通信を終了する。 5-5.内部レジスタの初期化 I2CバスによりアドレスFFhでアクセスされる内部レジスタは、書き込み専用となっている。このレ ジスタに対し、FFhという値を書き込むことにより、内部レジスタは初期値に戻る。 6.I2Cレジスタマップ レジスタ アドレス D7 D6 D5 D4 D3 D2 D1 D0 START 00h 最後にアクセスされたアドレス(リード専用)

DATA 10h 0 MCKFS_I2C[1:0] SRATE_I2C[1:0] DFORM[2:0]

GAINL 20h PSTPL MUTEBL GAINL[5:0] GAINR 21h PSTPR MUTEBR GAINR[5:0]

start 1 1 0 1 1 0 0 R/W ACK ACK ACK stop

LV4904V LV4904V LV4904V

start R/W ACK ACK ACK stop

LV4904V LV4904V LV4904V

start R/W

LV4904V

start 1 1 0 1 1 0 0 R/W ACK ACK ACK stop

LV4904V LV4904V LV4904V

7.I2Cコマンドリスト レジスタ アドレス ビット 信号名 端子説明 初期値 [2:0] DFORM 3線シリアルPCM入力、フォーマット設定 000 [4:3] SRATE_I2C 3線シリアルPCM入力、サンプルレート設定 01 [6:5] MCKFS_I2C マスタクロックレート 00 DATA 10h [7] 0固定 0 [5:0] GAINL チャンネル1(Lチャンネル)、ゲイン設定 00000 [6] MUTEBL チャンネル1(Lチャンネル)、ミュート設定 0 GAINL 20h [7] PSTPL チャンネル1(Lチャンネル)、出力停止設定 0 [5:0] GAINR チャンネル2(Rチャンネル)、ゲイン設定 00000 [6] MUTEBR チャンネル2(Rチャンネル)、ミュート設定 0 GAINR 21h [7] PSTPR チャンネル2(Rチャンネル)、出力停止設定 0 [0] 1固定 1 [1] IDPEN ミュート時パルス動作制御 1 [2] MDIDX PWM変調度設定 0 MISC 30h [3] NSORD ノイズシェーパ次数設定 0 8.I2Cバスレジスタ説明 8-1.入力データ設定 レジスタ アドレス D7 D6 D5 D4 D3 D2 D1 D0 DATA 10h 0 MCKFS_I2C[1:0] SRATE_I2C[1:0] DFORM_I2C[2:0]

入力される3線シリアル入力のフォーマットと一致するように、DFORM_I2Cを設定する。

DFORM_I2Cによる設定は、I2Cバス/端子併用モードで端子設定DFORM0=DFORM1=DFORM2=Lowの時のみ有

効になる。上記以外の端子設定や端子設定モードの場合は、2-6.の項で示される端子による設定が 有効になり、DFORM_I2Cによる設定は無効となる。DFORM_I2Cによって設定されるフォーマットを以 下の表及び図に示す。 データフォーマット設定(太字が初期設定) DFORM_I2C 設定データフォーマット 000 I2S 001 左詰、MSBファースト 010 右詰、LSBファースト 011 24ビット、右詰MSBファースト 100 20ビット、右詰MSBファースト 101 18ビット、右詰MSBファースト 110 16ビット、右詰MSBファースト [DFORM_I2C=0000] BCK=64fs, I2S(図は24ビット) [DFORM_I2C =0001] BCK=64fs, 左詰MSBファースト(図は24ビット) 23 22 2120 3 2 1 0 2322 21 20 3 2 1 0 2322 21 32fs Lch 32fs Rch 32fs Lch 32fs Rch

[DFORM_I2C =0010] BCK=64fs, 右詰LSBファースト(図は24ビット)

[DFORM_I2C =011/100/101/110] BCK=64fs, 24/20/18/16ビット, 右詰MSBファースト

マスタクロック、入力サンプルレートに応じて、マスタクロックレートMCKFS_I2Cとサンプルレー

トSRATE_I2Cとを設定する。MCKFS_I2Cによる設定は、I2Cバス/端子併用モードで端子設定MCKFS=Low

の時にのみ有効になる。MCKFS=Highの場合や端子設定モードの場合は、2-7.の項で示される端子に

よる設定が有効になり、MCKFS_I2Cによる設定は無効となる。SRATE_I2Cによる設定は、I2Cバス/端

子併用モードで端子設定SRATE=Lowの時にのみ有効になる。SRATE=Highの場合や端子設定モードの 場合は、2-8.の項で示される端子による設定が有効になり、SRATE_I2Cによる設定は無効となる。。 これらの設定が不正で入力信号と一致しない場合、異音を発生させたり出力がOFFされたりする。 また、設定を切り替える際にはノイズを発生するので、あらかじめ出力をミュートすること。 SRATEとMCKFSにより設定されるマスタクロックの設定を以下の表に示す。 マスタクロック設定(太字が初期設定) SRATE_I2C MCKFS_I2Cの設定とMCKレート [1] [0] サンプルレート [00] [01] [10] [11] 0 0 32kHz 256fs 384fs 512fs 768fs 0 1 44.1/48kHz 256fs 384fs 512fs 768fs 1 0 88.2/96kHz 128fs 192fs 256fs 384fs 1 1 176.4/192kHz 64fs 96fs 128fs 192fs 8-2.ゲイン・ミュート設定 GAINLによりLchのボリュームをGAINRによりRchのボリュームを6bit、64段階で設定する。ボリュー ムの設定範囲は+12dB∼-81dB、1.5dBステップとなっている。 GAINLとGAINRによる設定は、I2Cバス/端子併用モードで端子設定GAIN0∼GAIN5がすべてLowの時に レジスタ アドレス D7 D6 D5 D4 D3 D2 D1 D0 GAINL 20h PSTPL MUTEBL GAINL[5:0]

GAINR 21h PSTPR MUTEBR GAINR[5:0] 23 22 21 0 1 2 3 20 21 22 23 0 1 2 3 21 22 23 32fs Lch 32fs Rch 20 0 1 2 3 2 1 0 2 1 0 32fs Lch 32fs Rch 3 24/20/18/16 bit 24/20/18/16 bit

GAINL、GAINRによるボリュームの設定値を以下の表に示す。 ゲイン設定(太字が初期設定) No. GAINL GAINR ゲイン(dB) No. GAINL GAINR ゲイン(dB) No. GAINL GAINR ゲイン(dB) 63 111111 +12.0 41 101001 -21.0 19 010011 -54.0 62 111110 +10.5 40 101000 -22.5 18 010010 -55.5 61 111101 +9.0 39 100111 -24.0 17 010001 -57.0 60 111100 +7.5 38 100110 -25.5 16 010000 -58.5 59 111011 +6.0 37 100101 -27.0 15 001111 -60.0 58 111010 +4.5 36 100100 -28.5 14 001110 -61.5 57 111001 +3.0 35 100011 -30.0 13 001101 -63.0 56 111000 +1.5 34 100010 -31.5 12 001100 -64.5 55 110111 0.0 33 100001 -33.0 11 001011 -66.0 54 110110 -1.5 32 100000 -34.5 10 001010 -67.5 53 110101 -3.0 31 011111 -36.0 9 001001 -69.0 52 110100 -4.5 30 011110 -37.5 8 001000 -70.5 51 110011 -6.0 29 011101 -39.0 7 000111 -72.0 50 110010 -7.5 28 011100 -40.5 6 000110 -73.5 49 110001 -9.0 27 011011 -42.0 5 000101 -75.0 48 110000 -10.5 26 011010 -43.5 4 000100 -76.5 47 101111 -12.0 25 011001 -45.0 3 000011 -78.0 46 101110 -13.5 24 011000 -46.5 2 000010 -79.5 45 101101 -15.0 23 010111 -48.0 1 000001 -81.0 44 101100 -16.5 22 010110 -49.5 0 000000 MUTE 43 101011 -18.0 21 010101 -51.0 42 101010 -19.5 20 010100 -52.5 MUTEBLによりLchのミュートを、MUTEBRによりRchのミュートを設定する。MUTEBL、MUTEBRはともに Lアクティブである。 MUTEBL、MUTEBRによる設定は、I2Cバス/端子併用モードで端子設定MUTEB=Lowの時のみ有効になる。 上記以外の端子設定や端子設定モードの場合は、2-10.の項で示される端子による設定が有効にな り、MUTEL、MUTERによる設定は無効となる。MUTEBL、MUTEBRによるミュート設定を以下の表に示す。 ミュート設定(太字が初期設定) MUTEBL/MUTEBR 設定内容 0 ミュート 1 音声出力ON PSTPLによりLchのPWM出力を、PSTPRによりRchのPWM出力を停止する事が出来る。 PSTPL、PSTPRによるPWM出力停止設定を以下の表に示す。 PWM出力停止設定(太字が初期設定) PSTPL/PSTPR 設定内容 0 通常出力動作 1 PWM出力停止

8-3.その他の設定

レジスタ アドレス D7 D6 D5 D4 D3 D2 D1 D0 PWM1 41h Reserved NSORD MDIDX IDPEN 1

IDPENを設定する事により、ミュート時や無信号時にPWM出力を50%dutyパルスに固定するか、アイ ドリング動作させておくかを選択する事が出来る。 IDPENの機能設定を以下の表に示す。 IDPENの機能設定(太字が初期設定) IDPEN 設定内容 0 アイドリング動作 1 50% duty パルス MDIDXを設定する事により、PWM変調器の変調度を切り替える事が出来る。 MDIDXの機能設定を以下の表に示す。 MDIDXの機能設定(太字が初期設定) MDIDX 設定内容 0 87.5% 1 100% NSORDを設定する事により、ノイズシェーパの次数を切り替える事が出来る。 NSORDの機能設定を以下の表に示す。 NSORDの機能設定(太字が初期設定) NSORD 設定内容 0 7次 1 5次

特性データ

Ta=27℃,Fs=48kHz, Master Clock=256fs

Ipd -- VDD 0 0.1 0.02 2.6 2.8 3.0 3.2 3.4 3.6 3.8 10 8 6 4 2 12 14 16 10 8 6 4 12 14 16 4.0 Ipd -- Ta 0 0.6 0.1 -40 0 60 100 Ist -- PVD 0 0.3 0.4 0.2 0.1 0.5 0 18 Ist -- Ta 0 Imute -- PVD 0 2 1 10 0 2 1 3 4 5 18 Imute -- Ta ICCO -- PVD 0 20 0 10 20 ICCO -- Ta 0.04 0.06 0.08 RSTB=Low VDD=3.3V RSTB=Low 0.2 0.4 0.8 -20 2020 40 80 RSTB=Low 20 0.3 0.4 0.2 0.1 0.5 PVD=15V RSTB=Low -40 -20 0 2020 40 60 80 100 RL=8Ω RSTB=High ENABLE=Low 20 -40 -20 0 20 40 60 80 100 VD=15V RL=8Ω RSTB=High ENABLE=Low 6 -40 -20 0 20 40 60 80 100 10 8 6 4 12 14 16 18 20 RL=8Ω RSTB=High ENABLE=High MUTEB=Low 30 30 40 50 VD=15V RL=8Ω RSTB=High ENABLE=High MUTEB=Low

Iop -- VDD 0 20 5 2.6 2.8 3.0 3.2 3.4 3.6 3.8 10 9 12 14 16 4.0 ICC -- Ta 0 15 20 -40 0 60 100 VDDA -- PVD VDDA -- Ta VNO -- PVD 0 10 2 0.1 1 18 VNO -- Ta CH sep. -- PVD 0 -20 CH sep. -- Ta 10 15 PVD=15V RSTB=High ENABLE=High MUTE=Low 5 10 -20 2020 40 80 -40 -20 0 2020 40 60 80 100 RL=8 RSTB=High ENABLE=High MUTEB=High VOL=+12dB IHF-A 20 -40 -20 0 20 40 60 80 100 10 VD=15V RL=8 RSTB=High ENABLE=High MUTEB=Low VDD A -V 10 8 6 4 12 14 16 18 20 0 2 1 3 4 5 6 RL=8 RSTB=High ENABLE=High MUTEB=Low VDD A -V 0 2 1 3 4 5 6 VD=15V RL=8 RSTB=High ENABLE=High MUTEB=Low 4 6 8 11 13 15 17 19 VD=15V RL=8 VIN=-138dBFS VOL=+12dB IHF-A RL=8 fIN=1kHz VO=0dBm DIN AUDIO -40 -60 0 -20 -40 -60 VD=15V RL=8 fIN=1kHz VO=0dBm AES17

0 25 5 10 Power -- Ta 0 15 20 -40 0 60 100 THD+N -- PVD THD+N -- Ta THD+N -- Frequency 10 15 5 10 -20 2020 40 80 -40 -20 0 2020 40 60 80 100 100000 PVD=15V RL=8 fIN=1kHz THD+N=10% 2CH-Drive AES17 0.01 0.1 1 10 100 1000 10000 Power -- PVD 10 9 11 12 13 14 15 16 17 18 19 20 RL=8 fIN=1kHz 2CH-Drive PCL=0X00 AES17 20 87.5% modulation 100% modulation 87.5% modulation 100% modulation Power - W Power - W 10 9 11 12 13 14 15 16 17 18 19 20 0.01 0.1 1 10 RL=8 fIN=1kHz PO=1W 2CH-Drive Vol=+12dB AES17 CH1 CH2 CH1 CH2 PVD=15V RL=8 PO=1W 2CH-Drive Vol=+12dB AES17 0.01 0.1 10 1 PVD=15V RL=8 PO=1W 2CH-Drive Vol=+12dB AES17 CH2 CH1 0.001 THD+N -- Power 10 0.01 0.1 1 0.01 0.1 10 1 PVD=15V RL=8 2CH-Drive Vol=+12dB AES17 Power - W 0.0001 100Hz 1kHz 6.67kHz 0.001 THD+N -- Power 10 0.01 0.1 1 0.01 0.1 10 1 PVD=15V RL=8 2CH-Drive Vol=+12dB AES17 Power - W 0.0001 CH1 CH2

0 100 20 10 Power -- VIN 1 10 1 1000 ID -- Power Pd -- Power Response -- Frequency 40 60 0.01 0.1 10 100 100000 0 0.5 1 2 100 1000 10000 Power -- Efficiency 2 0 4 6 8 10 80 Ef ficiency - % Power - W 2 0 4 6 8 10 0 1 2 6 -10 10 0 CH2 CH1 PVD=15V RL=8 fIN=1kHz 2CH-Drive AES17 Power - W 100 0.001 0.0001 VIN - mFFS PVD=15V RL=8 fIN=1kHz 2CH-Drive Vol=+12dB AES17 I D - A Power - W PVD=15V RL=8 fIN=1kHz 2CH-Drive AES17 1.5 Power - W Pd - W 2 0 4 6 8 10 PVD=15V RL=8 fIN=1kHz 2CH-Drive AES17 3 4 5 PVD=15V RL=8 PO=1W 2CH-Drive Vol=+12dB AES17 -8 -6 -4 -2 2 4 6 8 Power -- Ta 0 6 10 -40 0 60 100 2 4 -20 2020 40 80 Upper Power - W RL=8Ω RSTB=High ENABLE=High MUTEB=High 8 Lower

ON Semiconductor及びONのロゴはSemiconductor Components Industries, LLC (SCILLC)の登録商標です。SCILLCは特許、商標、著作権、トレードシークレット(営業秘密)と他の知 的所有権に対する権利を保有します。SCILLCの製品/特許の適用対象リストについては、以下のリンクからご覧いただけます。www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLCは通告なしで、本書記載の製品の変更を行うことがあります。SCILLCは、いかなる特定の目的での製品の適合性について保証しておらず、また、お客様 の製品において回路の応用や使用から生じた責任、特に、直接的、間接的、偶発的な損害に対して、いかなる責任も負うことはできません。SCILLCデータシー トや仕様書に示される可能性のある「標準的」パラメータは、アプリケーションによっては異なることもあり、実際の性能も時間の経過により変化する可能性がありま す。「標準的」パラメータを含むすべての動作パラメータは、ご使用になるアプリケーションに応じて、お客様の専門技術者において十分検証されるようお願い致しま す。SCILLCは、その特許権やその他の権利の下、いかなるライセンスも許諾しません。SCILLC製品は、人体への外科的移植を目的とするシステムへの使用、生命維持を 目的としたアプリケーション、また、SCILLC製品の不具合による死傷等の事故が起こり得るようなアプリケーションなどへの使用を意図した設計はされておらず、また、 これらを使用対象としておりません。お客様が、 このような意図されたものではない、 許可されていないアプリケーション用にSCILLC製品を購入または使用した場合 、 たとえ、SCILLCがその部品の設計または製造に関して過失があったと主張されたとしても、 そのような意図せぬ使用、 また未許可の使用に関連した死傷等から、直接 、 又は間接的に生じるすべてのクレーム、費用、損害、経費、および弁護士料などを、お客様の責任において補償をお願いいたします。また、SCILLCとその役員、従業員、 子会社、関連会社、代理店に対して、いかなる損害も与えないものとします。 SCILLCは雇用機会均等/差別撤廃雇用主です。この資料は適用されるあらゆる著作権法の対象となっており、いかなる方法によっても再販することはできません。 ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner. (参考訳)