MS0250-J-01 2012/11 - 1 -

概 要

AK4101A は 192kHz 対応 4 出力ディジタル・オーディオ・トランスミッタ(DIT)です。AK4101A は AES3, IEC60958, S/PDIF, EIAJ CP1201 の各規格に対応しています。AK4101A は入力されたオーディ オデータと補助情報などをバイフェーズエンコードし、ケーブルへ出力します。オーディオシリアル ポートは 8 種類のフォーマットに対応します。

特 長 192kHzサンプリングレート対応

AES3, IEC60958, S/PDIF, EIAJ CP1201プロフェッショナル & 民生フォーマット準拠 CRCCコード, パリティビット生成 RS422ラインドライバ4系統内蔵 チャネルステータス&ユーザビット用バッファ64バイト内蔵 チャネルステータス&ユーザビットへ非同期/同期アクセス対応 多様なマスタクロックに対応: 128fs, 256fs, 384fs, 512fs オーディオフォーマット: 前詰め/後詰め/I2 S 4線式シリアルホストインタフェース オーディオルーティングモード(トランスペアレントモード) 電源電圧: 4.75 ∼ 5.25V TTLレベルI/F 小型パッケージ: 44ピンLQFP Ta: - 40 ∼ 85 °C

Quad Outputs 192kHz 24-Bit DIT

MS0250-J-01 2012/11 - 2 - ブロック図 Host Serial Interface Audio Serial Interface BICK LRCK SDTI1 TXP1 MU X CRCC Generator Prescaler RS422 Line Dr ive rs Biphase Encoder SDTI2 SDTI3 SDTI4 DI F 2 DI F 1 DI F 0 CK S 1 CK S 0 MCL K BLS TRA N S VS S VD D TXN1 TXP2 TXN2 TXP3 TXN3 TXP4 TXN4 C1 C2 C3 C4 U1 U2 U3 U4 V12 V34 FS0 FS1 FS2 FS3 Regis ter CS N CC L K CDT I CDTO AN S PDN

MS0250-J-01 2012/11 - 3 -

オーダリングガイド

AK4101AVQ -40 ∼ +85°C 44pin LQFP (0.8mm pitch) ピン配置 PDN TR ANS 1 MCLK 2 SDTI1 3 SDTI2 4 SDTI3 5 SDTI4 6 VDD 7 VSS 8 BICK 9 LRCK 10 FS0/CSN 11 V34 V12 U2 U1 DI F 2 DI F1 V DD DI F 0 FS 1 /C D T I F S 2/ CCLK FS3 /CD T O C1 C2 C4 AN S BL S CKS0 VS S 33 32 31 30 29 28 27 26 25 24 23 TXP1 TXN1 TXP2 TXN2 VSS VDD TXP3 TXN3 TXP4 TXN4 CKS1

AK4101AVQ

Top View C3 U4 U3 44 43 42 41 40 39 38 37 36 35 34 12 13 14 15 16 17 18 19 20 21 22 AK4101 との比較Function AK4101 AK4101A

Ambient Temperature -10 ~ 70°C -40 ~ 85°C

CRCC generation by FS3-0 pins. Synchronous mode X O

CRCC generation by FS3-0 bits. Asynchronous mode X O

O: 入力データがCRCCに反映されます。 X: 入力データはCRCCに反映されません。

MS0250-J-01 2012/11 - 4 - ピン/機能 No. ピン名称 I/O 機 能 1 PDN I パワーダウン&リセットピン (プルアップピン) このピンを “L”にするとパワーダウン状態になり、TXP/N pin は “L”、レジスタは初期化されます。 2 MCLK I マスタクロック入力ピン 3 SDTI1 I オーディオシリアルデータ入力 1 ピン 4 SDTI2 I オーディオシリアルデータ入力 2 ピン (プルダウンピン) 5 SDTI3 I オーディオシリアルデータ入力 3 ピン (プルダウンピン) 6 SDTI4 I オーディオシリアルデータ入力 4 ピン (プルダウンピン) 7 VDD - 電源ピン, 4.75V∼5.25V 8 VSS - グランドピン, 0V 9 BICK I/O オーディオシリアルデータクロック入出力ピン

SDTI pin 用のシリアルクロック。DIF2-0 の設定で出力ピンにできま す。 10 LRCK I/O 入出力チャネルクロックピン L/R チャネルを示します。DIF2-0 の設定で出力ピンにできます。 FS0 I サンプリング周波数選択 0 ピン(同期モード時) (プルダウンピン) CSN I ホストインタフェースチップセレクトピン(非同期モード時) (プルダウンピン) 11 AKMODE I AK4112B モードピン(オーディオルーティングモード時) (プルダウンピン) 0: 非 AKM レシーバモード, 1: AK4112B モード FS1 I サンプリング周波数選択 1 ピン(同期モード時) (プルダウンピン) 12 CDTI I ホストインタフェースデータ入力ピン(非同期モード時) (プルダウンピン) FS2 I サンプリング周波数選択 2 ピン(同期モード時) (プルダウンピン) 13 CCLK I ホストインタフェースビットクロック入力ピン(非同期モード時) (プルダウンピン) FS3 I サンプリング周波数選択 3 ピン(同期モード時) (プルダウンピン) 14 CDTO O ホストインタフェースデータ出力ピン(非同期モード時) (プルダウンピン) 15 C1 I チャネル 1 チャネルステータスビット入力ピン 16 C2 I チャネル 2 チャネルステータスビット入力ピン (プルダウンピン) 17 C3 I チャネル 3 チャネルステータスビット入力ピン (プルダウンピン) 18 C4 I チャネル 4 チャネルステータスビット入力ピン (プルダウンピン) 19 ANS I 非同期/同期モード選択ピン (プルアップピン) 0: 非同期(Asynchronous)モード, 1: 同期(Synchronous)モード 20 BLS I/O ブロックスタート入出力ピン (プルダウンピン) ノーマルモード時、最初の 4 バイトで “H”を出力します。オーディ オルーティングモード時は入力ピンになります。ノーマルモードで PDN pin = “L”の時、BLS pin は “H”を出力します。 21 CKS0 I クロックモード選択 0 ピン (プルアップピン) 22 VSS - グランドピン, 0V

MS0250-J-01 2012/11 - 5 - No. ピン名称 I/O 機 能 23 CKS1 I クロックモード選択 1 ピン (プルダウンピン) 24 TXN4 O チャネル 4 差動反転出力ピン 25 TXP4 O チャネル 4 差動非反転出力ピン 26 TXN3 O チャネル 3 差動反転出力ピン 27 TXP3 O チャネル 3 差動非反転出力ピン 28 VDD - 電源ピン, 4.75V∼5.25V 29 VSS - グランドピン, 0V 30 TXN2 O チャネル 2 差動反転出力ピン 31 TXP2 O チャネル 2 差動非反転出力ピン 32 TXN1 O チャネル 1 差動反転出力ピン 33 TXP1 O チャネル 1 差動非反転出力ピン 34 DIF0 I オーディオシリアルインタフェース選択 0 ピン (プルダウンピン) 35 VDD - 電源ピン, 4.75V∼5.25V 36 DIF1 I オーディオシリアルインタフェース選択 1 ピン (プルダウンピン) 37 DIF2 I オーディオシリアルインタフェース選択 2 ピン (プルダウンピン) 38 U1 I チャネル 1 ユーザデータビット入力ピン (プルダウンピン) 39 U2 I チャネル 2 ユーザデータビット入力ピン (プルダウンピン) 40 U3 I チャネル 3 ユーザデータビット入力ピン (プルダウンピン) 41 U4 I チャネル 4 ユーザデータビット入力ピン (プルダウンピン) 42 V12 I チャネル 1&2 バリディティビット入力ピン 43 V34 I チャネル 3&4 バリディティビット入力ピン (プルダウンピン) 44 TRANS I オーディオルーティングモードピン(同期モード時) 0: ノーマルモード 1: オーディオルーティング(トランスペアレント)モード Notes: 1. プルアップ、プルダウン抵抗はデバイス内部に接続されており、抵抗値は 43kΩ (typ)です。 2. プルアップ、プルダウンピンを除くすべての入力ピンはフローティングにしないで下さい。

MS0250-J-01 2012/11 - 6 -

絶対最大定格 (VSS=0V; Note 3)

Parameter Symbol min max Unit

Power Supply VDD -0.3 6.0 V

Input Current (All pins except supply pins) IIN - ±10 mA Input Voltage VIN -0.3 VDD+0.3 V Ambient Operating Temperature Ta -40 85 °C Storage Temperature Tstg -65 150 °C Notes: 3. 電圧はすべてグランドに対する値です。 注意: この値を超えた条件で使用した場合、デバイスを破壊することがあります。 また通常の動作は保証されません。 推奨動作条件 (VSS=0V; Note 1)

Parameter Symbol min typ max Unit

Power Supply VDD 4.75 5.0 5.25 V 注意: 本データシートに記載されている条件以外のご使用に関しては、当社では責任負いかねますので

十分ご注意下さい。

DC特性

(Ta=25°C; VDD=4.75~5.25V)

Parameter Symbol min typ max Unit

Power Supply Current (fs=108kHz, Note 4) IDD 10 20 mA High-Level Input Voltage

Low-Level Input Voltage

VIH VIL 2.4 - - - - 0.8 V V High-Level Output Voltage

(Except TXP/N pins: Iout=-400µA) (TXP/N pins: Iout= -8mA) Low-Level Output Voltage

(Except TXP/N pins: Iout= 400µA) (TXP/N pins: Iout= 8mA)

VOH VOH VOL VOL VDD-1.0 VDD-0.8 - - - - - - - - 0.4 0.6 V V V V Input Leakage Current Iin - - ±10 μA Notes:

4. 4mA(typ)@fs=48kHz, 12mA(typ)@fs=192kHz.

プロ用出力ドライバ1chあたり20mA(typ)増加します。全4chにプロ用出力ドライバを接続した場合、消費 電流は90mA(typ)になります。

PDN pin = “L”, TRANS pin = “H”でプルアップ、プルダウンピン以外のすべての入力ピンをVSSに固定し た場合、消費電流は150μA(typ)です。

MS0250-J-01 2012/11 - 7 -

スイッチング特性 (Ta=25°C; VDD=4.75~5.25V; CL=20pF)

Parameter Symbol min typ max Unit

Master Clock Timing

Frequency Duty Cycle fCLK dCLK 3.584 40 27.648 60 MHz % LRCK Timing Frequency

Duty Cycle at Slave Mode Duty Cycle at Master Mode

fs dLCK 28 45 50 192 55 kHz % %

Audio Interface Timing

Slave Mode

BICK Period

BICK Pulse Width Low Pulse Width High

LRCK Edge to BICK “↑” (Note 5) BICK “↑” to LRCK Edge (Note 5) SDTI Hold Time

SDTI Setup Time

tBCK tBCKL tBCKH tLRB tBLR tSDH tSDS 36 15 15 15 15 8 8 ns ns ns ns ns ns ns Master Mode BICK Frequency BICK Duty BICK “↓” to LRCK SDTI Hold Time SDTI Setup Time

fBCK dBCK tMBLR tSDH tSDS -20 20 20 64fs 50 20 Hz % ns ns ns

Control Interface Timing

CCLK Period

CCLK Pulse Width Low Pulse Width High CDTI Setup Time CDTI Hold Time CSN “H” Time

CSN “↓” to CCLK “↑” CCLK “↑” to CSN “↑” CDTO Delay

CSN “↑” to CDTO Hi-Z (Note 6)

tCCK tCCKL tCCKH tCDS tCDH tCSW tCSS tCSH tDCD tCCZ 200 80 80 50 50 520 50 50 45 70 ns ns ns ns ns ns ns ns ns ns

Power-down & Reset Timing

PDN Pulse Width tPDW 150 ns

Notes:

5. この規格値はLRCKのエッジとBICKの立ち上がりエッジが重ならないように規定しています。 6. CDTO pin は内部でプルダウン抵抗に接続されています。

MS0250-J-01 2012/11 - 8 - タイミング波形 1/fCLK tCLKL VIH tCLKH MCLK VIL dCLK = tCLKH x fCLK x 100 = tCLKL x fCLK x 100 VIH LRCK VIL 1/fs tBCK tBCKL VIH tBCKH BICK VIL クロックタイミング tLRB LRCK VIH BICK VIL tSDS VIH SDTI VIL tSDH VIH VIL tBLR オーディオインタフェースタイミング (スレーブモード) LRCK BICK tMBLR 50%VDD 50%VDD SDTI tSDH tSDS VIH VIL オーディオインタフェースタイミング (マスタモード)

MS0250-J-01 2012/11 - 9 - tCCKL CSN CCLK tCDS CDTI tCDH tCSS C0 * tCCKH

CDTO Hi-Z (with pull-down resistor) * C1 VIH VIL VIH VIL VIH VIL WRITE/READ コマンド入力タイミング tCSW CSN CCLK CDTI D2 D0 tCSH CDTO D1 D3 VIH VIL VIH VIL VIH VIL Hi-Z

(with pull-down resistor)

WRITE データ入力タイミング CSN CCLK tDCD CDTO CDTI A1 A0 Hi-Z (with pull-down resistor) 50%VDD VIH VIL VIH VIL VIH VIL D7 D6 D5 READ データ出力タイミング 1

MS0250-J-01 2012/11 - 10 - CSN CCLK tCCZ CDTO D2 D1 CDTI D0 D3 tCSW tCSH 50%VDD VIH VIL VIH VIL VIH VIL READ データ出力タイミング 2 tPDW PDN VIL パワーダウン&リセットタイミング

MS0250-J-01 2012/11 - 11 -

動作説明 概要

AK4101AはAES3, IEC60958, S/PDIF, EIAJ CP1201の各インタフェースの規格に従ってオーディオデータ及び 補助情報などをバイフェーズエンコードし、伝送するモノリシックCMOS集積回路です。4系統のステレオ チャネルを同時に出力することができます。個別に受け取ったオーディオデータと補助情報などを内部で バイフェーズエンコードし、直接またはトランスを通して伝送ラインへ出力されます。動作モードは非同 期(asynchronous)、同期(synchronous)の2種類あります。詳細については、“非同期モード/同期モード”の項を 参照してください。 初期化 初期化にはPDN pinの立ち上がりから8 BICKサイクルかかります。また正しく同期をとるために、MCLKと LRCKは同期する必要はありますが位相を合わせる必要はありません。 MCLK と LRCK の関係 正しく同期をとるために、MCLK と LRCK は同じクロック信号から直接(分周器を通して)もしくは間接的 に(例えば DSP を通して)生成する必要があります。BICK と LRCK の関係は固定にし、動作中に変更しない で下さい。MCLK と LRCK の位相関係が初期状態から(128fs x 3) サイクルだけシフトすると内部フレームと ビットカウンタのリセットがかかります。この時、コントロールレジスタは初期化されません。なお、 MCLK は次の周波数に対応します。 CKS1 CKS0 MCLK fs 0 0 128fs 28k-192kHz 0 1 256fs 28k-108kHz 1 0 384fs 28k-54kHz 1 1 512fs 28k-54kHz Table 1. MCLK 周波数 非同期(Asynchronous)モード/同期(Synchronous)モード 1. 非同期 (Asynchronous) モード (ソフトウェアコントロール) ANS pinを “L”にすると非同期モードになります。このモードでは16から24ビットのオーディオサンプルは オーディオシリアルポートを通して受け取られ、チャネルステータスおよびユーザデータはシリアルホス トインタフェースを通して受け取られます。シリアルホストインタフェースによりチャネルステータスと ユーザデータ保持用の内部バッファメモリおよびコントロールレジスタにアクセスすることができます。 チャネル当たり4バイトのチャネルステータスとユーザデータが蓄えられます。このデータはオーディオシ リアルポートからのオーディオデータと多重化され、パリティビットが生成されます。ビットストリーム はバイフェーズエンコードされ、RS422ラインドライバを通して出力されます。チャネルステータスの CRCCコードはAES3のプロフェッショナルモードに従って生成されます。またこのモードではシリアルホ ストインタフェースを通したソフトウェアコントロールによりミュート、リセット、オーディオフォーマ ット選択、クロック周波数設定および出力イネーブルを行うこともできます。

MS0250-J-01 2012/11 - 12 - 2. 同期 (Synchronous) モード (ハードウェアコントロール) 同期モードではコントロールデータ用にピンが設けられ、全チャネルステータス、全ユーザデータおよび バリディティビットはピンからシリアルに入力することができます。また16から24ビットのオーディオサ ンプルがオーディオシリアルポートを通して受け取られます。これらのデータは多重化され、パリティビ ットが生成されます。ビットストリームはバイフェーズエンコードされ、RS422ラインドライバを通して出 力されます。4系統のチャネルはそれぞれ個別にチャネルステータスピンとユーザデータピンを持ちます。 2-1. オーディオルーティングモード (トランスペアレントモード)

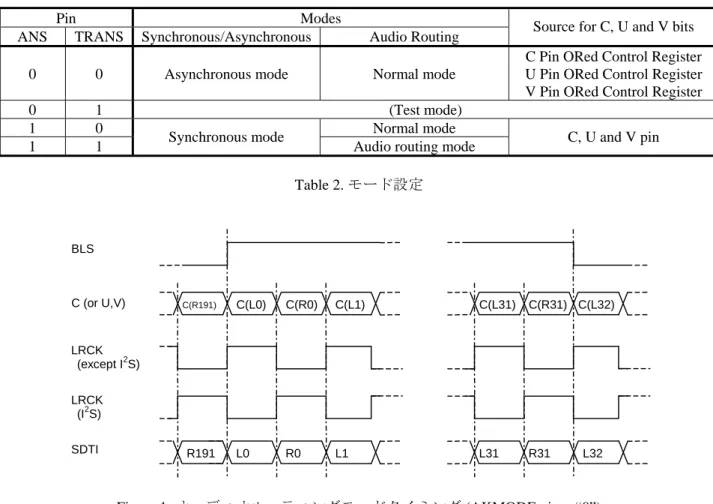

ANS pin =TRANS pin = “1”にするとオーディオルーティングモード(トランスペアレントモード)になります。 このモードでは、チャネルステータス(C)、ユーザデータ(U)、バリディティ(V)の各ビットはそのまま通過 します。ブロックスタート(B)信号は入力になり、伝送するブロック構造をレシーバのブロック構造に合わ せます。C,U,Vはその時のオーディオサンプルと同一サブフレーム内で伝送されます。CRCCバイトは生成 されず、Cビットはそのまま通過します。オーディオルーティングモードではFS0/CSN pin はAKMODE pin になり、 “H”にするとAK4112Bと直接つなぐことができます。 “L”にするとAKM以外のレシーバと合わせ て使用できます。TRANS pin = “1”, ANS pin = “0”の設定はテストモードですので、使用しないで下さい。

Pin Modes

ANS TRANS Synchronous/Asynchronous Audio Routing Source for C, U and V bits 0 0 Asynchronous mode Normal mode

C Pin ORed Control Register U Pin ORed Control Register V Pin ORed Control Register

0 1 (Test mode)

1 0 Normal mode

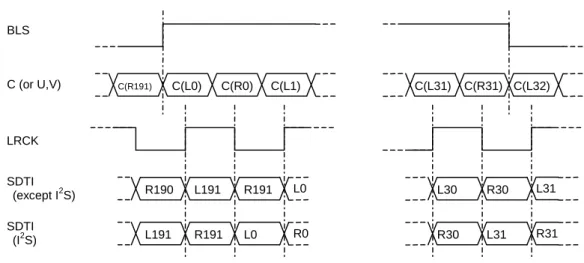

1 1 Synchronous mode Audio routing mode C, U and V pin Table 2. モード設定 BLS C (or U,V) C(R191) C(L0) C(R0) C(L1) C(L31) C(R31) C(L32) SDTI LRCK (I2S) L0 R0 L31 R31 R191 L1 L32 LRCK (except I2S)

MS0250-J-01 2012/11 - 13 - BLS C (or U,V) LRCK C(L0) C(R0) C(L1) C(L31) C(R31) C(L32) C(R191) SDTI (except I2S) L191 R191 L0 R30 L31 R31 SDTI (I2S) L191 R191 L0 L30 R30 L31 R190 R0

Figure 2. オーディオルーティングモードタイミング (AKMODE pin = “1”)

ブロックスタートタイミング ノーマルモード

ノーマルモード(TRANS pin = “0”)ではブロックスタート信号は出力になります。各ブロックのフレーム0の チャネル2の先頭から2BICKサイクル後に “H”になり、最初の32フレームの間 “H”を保持します。

オーディオルーティングモード(トランスペアレントモード)

オーディオルーティングモード(トランスペアレントモード) (ANS pin = TRANS pin = “1”)では、ブロックス タートは入力になります。I2 Sモード以外のとき、ブロックスタート信号はLchの最初のBICK立ち上がりエ ッジから次のLRCK立ち上がりエッジ直前のBICK立ち上がりエッジまでの間に取り込まれ、次のLchがブロ ックの第1サブフレームとなります。下のFigure 3を参照して下さい。 BICK LRCK (except I2S) (n-1)th channel 1 nth channel 1 LRCK (I2S) (n-1)th channel 1 nth channel 1 (1) Figure 3. オーディオルーティングモード時のブロックスタートタイミング “(1)”の範囲内でブロックスタート信号を受け取ると、“nth channel 1”がブロックの第 1 サ ブフレームとなります。

MS0250-J-01 2012/11 - 14 -

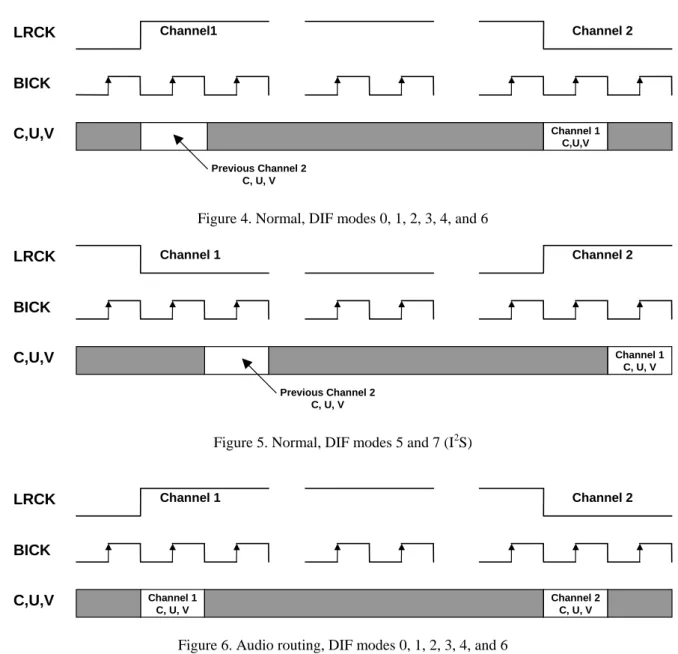

C, U, V シリアルポート ノーマルモード

ノーマルモード(TRANS pin = “0”)のとき、C, U, V bitsはオーディオデータの次のサブフレームで受け取られ ます(同期モードではピンから、非同期モードではコントロールレジスタから)。V bitを “0”にすることでオ ーディオデータが変換に適していることを示します。V12 pinはチャネル 1 と 2、V34 pinはチャネル 3 と 4 のバリディティをそれぞれ示します。Figure 4と Figure 5を参照して下さい。

オーディオルーティングモード(トランスペアレントモード)

オーディオルーティングモード(トランスペアレントモード) (ANS pin = TRANS pin = “1”)のとき、C, U, V bitsはオーディオデータと同じサブフレームで受け取られます。Mode 5と7以外の全DIFモードでC, U, V bits はLRCK立ち上がりエッジ直後のBICK立ち上がりエッジで受け取られます。Mode 5と7(I2

S)のときは、C, U, V bitsはLRCK立ち下がりエッジから2番目のBICK立ち上がりエッジで受け取られます。Figure 6とFigure 7 を参照して下さい。 C,U,V BICK LRCK Channel1 Channel 2 Channel 1 C,U,V Previous Channel 2 C, U, V

Figure 4. Normal, DIF modes 0, 1, 2, 3, 4, and 6

C,U,V BICK LRCK Channel 1 Channel 2 Channel 1 C, U, V Previous Channel 2 C, U, V

Figure 5. Normal, DIF modes 5 and 7 (I2S)

C,U,V BICK LRCK Channel 1 C, U, V Channel 1 Channel 2 Channel 2 C, U, V

MS0250-J-01 2012/11 - 15 - C,U,V BICK LRCK Channel 1 C, U, V Channel 1 Channel 2 Channel 2 C, U, V Figure 7. Audio routing, DIF modes 5 and 7 (I2S)

オーディオシリアルインタフェース オーディオシリアルインタフェースはオーディオデータを入力するために使われ、ビットクロック(BICK)、 ワードクロック(LRCK)および4つのデータピン(SDTI1-4)の合計6ピンで構成されます。LRCKはLおよびRチ ャネルを示します。同期モード時はDIF2-0 pin、非同期モード時はコントロールレジスタによって各入力モ ードを選択します。ただし、非同期モード時はDIF2-0 pinと内部でORが取られます。オーディオデータフ ォーマットは前詰めおよび後詰めモードで16から24ビットに対応します。またI2 Sモードにも対応します。 AK4101Aはマスタモード、スレーブモードのどちらにも設定できます。

Mode DIF2 DIF1 DIF0 SDTI Master / Slave LRCK BICK 0 0 0 0 16bit, Right justified Slave H/L (I) 32fs-128fs (I) 1 0 0 1 18bit, Right justified Slave H/L (I) 36fs-128fs (I) 2 0 1 0 20bit, Right justified Slave H/L (I) 40fs-128fs (I) 3 0 1 1 24bit, Right justified Slave H/L (I) 48fs-128fs (I) 4 1 0 0 24bit, Left justified Slave H/L (I) 48fs-128fs (I) 5 1 0 1 24bit, I2S Slave L/H (I) 50fs-128fs (I) 6 1 1 0 24bit, Left justified Master H/L (O) 64fs (O) 7 1 1 1 24bit, I2S Master L/H (O) 64fs (O)

Table 3. オーディオデータフォーマットモード [NOTE: (I): Input, (O): Output]

LRCK(i) BICK(i) SDTI(i) 0 1 2 31 0 1 15:MSB, 0:LSB Lch Data Rch Data 15 16 17 31 0 1 2 15 16 17 0 1 0 1 30 15 14 14 15 30 Figure 8. Mode 0 タイミング

MS0250-J-01 2012/11 - 16 - LRCK(i) BICK(i) SDTI(i) 0 1 2 31 0 1 17:MSB, 0:LSB Lch Data Rch Data 13 15 14 1331 0 1 2 14 15 0 1 0 1 30 17 16 16 17 30 Figure 9. Mode 1 タイミング LRCK(i) BICK(i) SDTI(i) 0 1 2 31 0 1 19:MSB, 0:LSB Lch Data Rch Data 11 13 12 1131 0 1 2 12 13 0 1 0 1 30 19 18 18 19 30 Figure 10. Mode 2 タイミング LRCK(i) BICK(i) SDTI(i) 0 1 8 31 0 1 23:MSB, 0:LSB Lch Data Rch Data 9 10 11 31 0 1 8 9 10 11 0 1 0 1 30 21 20 20 21 30 22 23 23 22 Figure 11. Mode 3 タイミング

MS0250-J-01 2012/11 - 17 - LRCK BICK SDTI(i) 0 1 2 31 0 1 23:MSB, 0:LSB Lch Data Rch Data 21 22 23 31 0 1 2 21 22 23 23 22 2 30 1 0 0 1 30 21 22 23 21 2 23 22 Figure 12. Mode 4, 6 タイミング

Mode 4: LRCK, BICK: Input Mode 6: LRCK, BICK: Output

LRCK BICK SDTI(i) 0 1 2 31 0 1 23:MSB, 0:LSB Lch Data Rch Data 23 3 31 0 1 2 3 23 23 22 24 1 0 24 3 2 23 22 2 1 0 21 22 23 22 Figure 13. Mode 5, 7 タイミング

Mode 5: LRCK, BICK: Input Mode 7: LRCK, BICK: Output

MS0250-J-01 2012/11 - 18 - サンプリング周波数設定 民生モードにおいて、チャネルステータスのバイト 3 のビット 3-0 は FS3-0 pins で設定できます。また、プ ロフェッショナルモードにおいて、チャネルステータスのバイト 0 の ビット 7-6 およびバイト 4 のビット 6-3 は FS3-0 pins で設定できます。 FS[3:0] Sampling Frequency Byte 3 Bits 3-0 0000 44.1kHz 0000 0001 Not Indicated 0001 0010 48kHz 0010 0011 32kHz 0011 0100 22.05kHz 0100 0101 Reserved 0101 0110 24kHz 0110 0111 Reserved 0111 1000 88.2kHz 1000 1001 Reserved 1001 1010 96kHz 1010 1011 Reserved 1011 1100 176.4kHz 1100 1101 Reserved 1101 1110 192kHz 1110 1111 Reserved 1111 Table 4. サンプリング周波数設定(民生モード) FS[3:0] Sampling Frequency Byte 0 Bits 7-6 Byte 4 Bits 6-3 0000 Not Defined 00 0000 0001 44.1kHz 01 0000 0010 48kHz 10 0000 0011 32kHz 11 0000 0100 Not Defined 00 0000 0101 Not Defined 00 0000 0110 Not Defined 00 0000 0111 Not Defined 00 0000 1000 For vectoring 00 1000 1001 22.05kHz 00 1001 1010 88.2kHz 00 1010 1011 176.4kHz 00 1011 1100 192kHz 00 0011 1101 24kHz 00 0001 1110 96kHz 00 0010 1111 Not Defined 00 1111 Table 5. サンプリング周波数設定(プロフェッショナルモード)

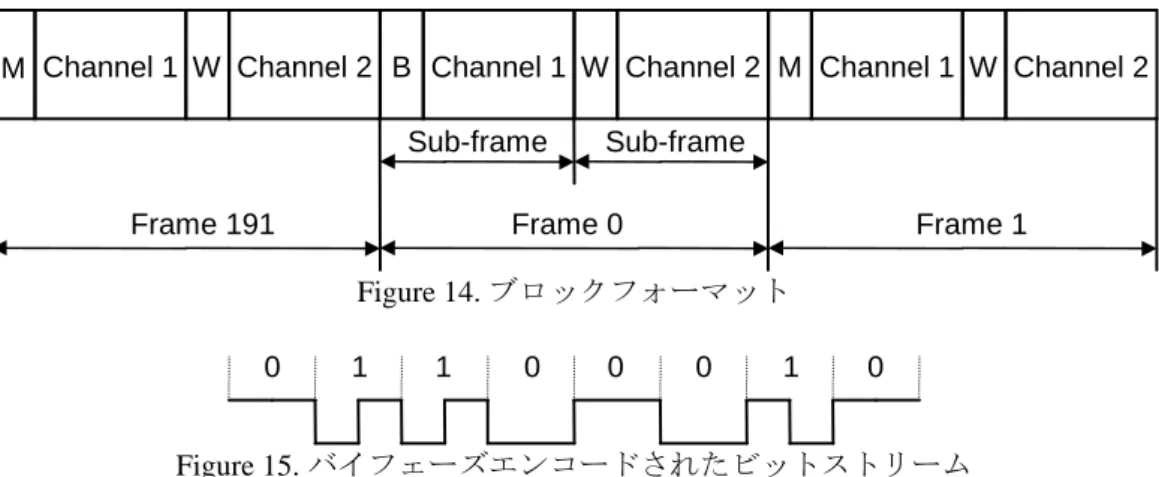

MS0250-J-01 2012/11 - 19 - データ伝送フォーマット TX出力で伝送されるデータのフォーマットは Figure 14に示されます。各ブロックは 192 フレームで構成さ れ、各フレームは 2 つのサブフレームで構成されます。各サブフレームは 32 ビットの情報を持ちます。受 け取った各データビットはバイフェーズマークエンコーディングにより 2 つのバイナリ状態のシンボルに 符号化されます。プリアンブルはデータと区別できるようにバイフェーズエンコーディングになっていま せん。バイフェーズエンコードにおいて、入力シンボルの前半分の状態は常に直前のシンボルの後半分の 状態の反転になっています。シンボルの後半分の状態は、ロジック 0 では前半分と同じ、ロジック 1 では 前半分の反転になります。Figure 15は 16 個のシンボル状態にエンコードされた 8 個のデータビットのサン プルストリームを示します。

Frame 191 Frame 0 Frame 1

Sub-frame Sub-frame

M Channel 1 W Channel 2 B Channel 1 W Channel 2 M Channel 1 W Channel 2

Figure 14. ブロックフォーマット 0 1 1 0 0 0 1 0 Figure 15. バイフェーズエンコードされたビットストリーム サブフレームは下の Figure 16のように定義されます。ビット 0-3 は同期のためのプリアンブルです。プリ アンブルには 3 種類あります。ブロックプリアンブル(B)はフレーム 0 の第 1 サブフレームに含まれます。 チャネル 1 プリアンブル(M)はフレーム 0 以外の全フレームの第 1 サブフレームに含まれます。チャネル 2 プリアンブル(W)は全フレームの第 2 サブフレームに含まれます。 各プリアンブルに対するシンボルのエンコードは下の Table 6のように定義されます。ビット 4-27 は 24 ビ ットのオーディオサンプルが 2 の補数で含まれ、ビット 27 がMSBです。16 ビットモードではビット 4-11 はすべて 0 です。ビット 28 はバリディティフラグです。オーディオサンプルに信頼性がない場合 “1”にな っています。ビット 29 はユーザデータビットです。192 ビットのユーザデータワードの先頭ビットはフレ ーム 0 に、最終ビットはフレーム 191 にそれぞれ含まれます。ビット 30 はチャネルステータスビットです。 チャネルステータスビットも同様に 192 ビットワードの先頭ビットはフレーム 0 に、最終ビットはフレー ム 191 にそれぞれ含まれます。ビット 31 はビット 4-31 に対する偶数パリティビットです。

Sync

V

U

C

P

L M

S Audio sam ple S

B B

0 3 4 27 28 29 30 31

Figure 16. サブフレームのフォーマット データのブロックはサンプリング周波数(fs)の 64 倍の定ビットレートで伝送される連続したフレームから 成り立ちます。ステレオオーディオでは、L または A チャネルのデータはチャネル 1 に、R または B チャ ネルのデータはチャネル 2 に含まれます。モノラルオーディオでは、オーディオデータはチャネル 1 に含 まれます。Preamble Preceding state = 0 Preceding state = 1

B 11101000 00010111 M 11100010 00011101 W 11100100 00011011 Table 6. サブフレームのプリアンブルエンコーディング

MS0250-J-01 2012/11 - 20 - ラインドライバ AK4101Aは4つのRS422ドライバを内蔵します。AES3の規格では、ラインドライバは内部インピーダンス 110Ω ±20%のバランス出力で、110Ωの負荷に対し2∼7Vppのバランス出力をドライブする能力が要求されて います。RS422ドライバの内部インピーダンスはシリーズに56Ωの抵抗を挿入することで規格を満たします。 民生(S/PDIF)では75Ω ±20%の出力インピーダンスと0.5Vpp±20%の出力レベルが要求されています。330Ωと 100Ωの並列接続によってこの要求を満たすことができます。パワーダウンもしくはソフトウェアミュート によって出力をグランドにすることができます。 TXP TXN 56 0.1u XLR Connector Transformer Figure 17. プロフェッショナル用出力ドライバ回路 TXP TXN 330 0.1u RCA Phono Connector Transformer 100 Figure 18. 民生用出力ドライバ回路

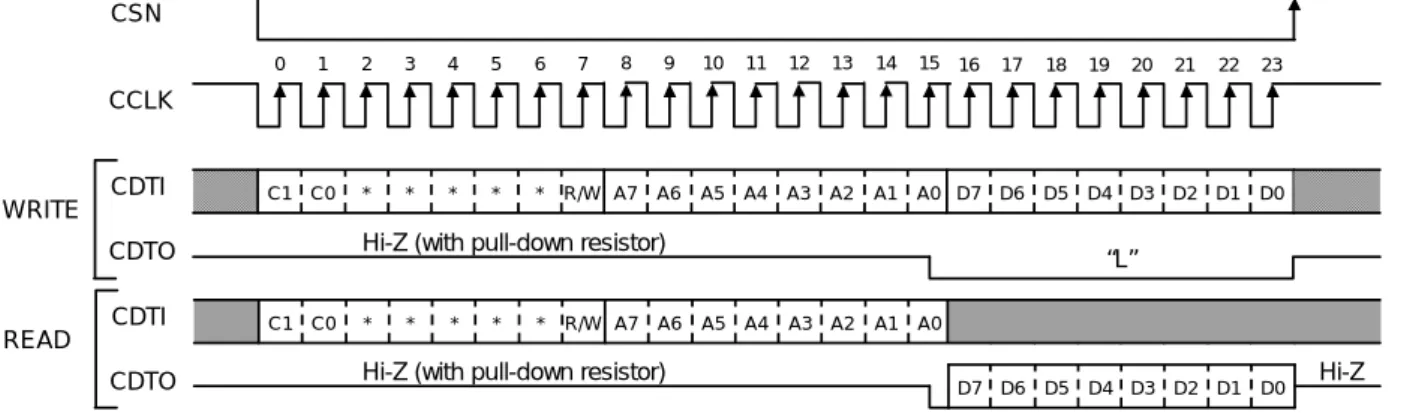

MS0250-J-01 2012/11 - 21 - シリアルコントロールインタフェース 非同期モードでは、4つのデュアル機能ピンが4線式マイコンインタフェース用のCSN, CCLK, CDTI, CDTO pins になります。内部66バイトのコントロールレジスタが読み書き可能です。コントロールレジスタの内 容のうち一部はAK4101Aの動作モードを設定します。Figure 19はシリアルコントロールインタフェースの 読み出しおよび書き込み動作時のシリアルデータのフローを示します。C1-0 bits はチップアドレスです。 AK4101AではC1-0 bits は “11”固定です。R/W bit が “0”の場合は読み出し、 “1”の場合は書き込み動作です。 A7-0 bits で構成されるレジスタアドレスはデコードされ、コントロールレジスタの各バイトを選択するの に使われます。CDTI pin におけるD7-0 bits は書き込み動作時にマイコンから来るコントロールデータです。 CDTO pin におけるD7-0 bits は読み出し動作時に指定されたアドレスにあるコントロールレジスタからのデ ータです。アドレスとデータビットはCSN pin = “L”によってフレームされます。書き込み動作時、各アド レスおよびデータビットはCCLKの立ち上がりエッジで取り込まれます。読み出し動作時、アドレスビット はCCLKの立ち上がりエッジで取り込まれ、CDTOのデータはCCLKの立ち下がりエッジで出力されます。 CCLKの最大周波数は5MHzです。 CDTI CCLK CSN C1 0 1 2 3 4 5 6 7 16 17 18 19 20 21 22 23 D4 D5 D6 D7 * * * * * C0 R/W D3 D2 D1 D0

CDTO Hi-Z (with pull-down resistor) WRITE

CDTI C1 C0 * * * * * R/W D7 D6 D5 D4 D3 D2 D1 D0

CDTO Hi-Z (with pull-down resistor) READ D4 D5 D6 D7 D3 D2 D1 D0 Hi-Z A7 8 9 10 11 12 13 14 15 A1 A2 A3 A4 A5 A6 A0 A7 A6 A5 A4 A3 A2 A1 A0 “L”

C1-C0: Chip Address (Fixed to “11”) R/W: READ/WRITE (0:READ, 1:WRITE) *: Don’t care

A7-A0: Register Address D7-D0: Control Data Figure 19. コントロールインタフェースタイミング CSN AK4101A CCLK CDTI CDTO CSN AK4101A CCLK CDTI CDTO μP CSN1 CCLK CDTI CDTO CSN2

Figure 20. Typical connection with μP

Note: CDTO pin は内部にプルダウン抵抗が接続されているので、 外部でプルアップしないで下さい。

MS0250-J-01 2012/11 - 22 -

レジスタマップ

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 00H Clock/Format Control CRCE DIF2 DIF1 DIF0 CKS1 CKS0 MUTEN RSTN 01H Validity/fs Control V4 V3 V2 V1 FS3 FS2 FS1 FS0 02H Ch 1 A-channel C-bit

buffer for Byte 0 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0 03H Ch 1 A-channel C-bit

buffer for Byte 1 CA15 CA14 CA13 CA12 CA11 CA10 CA9 CA8 04H Ch 1 A-channel C-bit

buffer for Byte 2 CA23 CA22 CA21 CA20 CA19 CA18 CA17 CA16 05H Ch 1 A-channel C-bit

buffer for Byte 3 CA31 CA30 CA29 CA28 CA27 CA26 CA25 CA24

06H-09H

Ch 1 B-channel C-bit buffer for Byte 0-3

CB7 … CB31 … … … … … … … … … … … … CB0 … CB24 0AH-0DH Ch 1 A-channel U-bit buffer for Byte 0-3

UA7 … UA31 … … … … … … … … … … … … UA0 … UA24 0EH-11H Ch 1 B-channel U-bit buffer for Byte 0-3

UB7 … UB31 … … … … … … … … … … … … UB0 … UB24 12H-15H Ch 2 A-channel C-bit

buffer for Byte 0-3 …

16H-19H

Ch 2 B-channel C-bit

buffer for Byte 0-3 …

1AH-1DH

Ch 2 A-channel U-bit

buffer for Byte 0-3 …

1EH-21H

Ch 2 B-channel U-bit

buffer for Byte 0-3 …

22H-25H

Ch 3 A-channel C-bit

buffer for Byte 0-3 …

26H-29H

Ch 3 B-channel C-bit

buffer for Byte 0-3 …

2AH-2DH

Ch 3 A-channel U-bit

buffer for Byte 0-3 …

2EH-31H

Ch 3 B-channel U-bit

buffer for Byte 0-3 …

32H-35H

Ch 4 A-channel C-bit

buffer for Byte 0-3 …

36H-39H

Ch 4 B-channel C-bit

buffer for Byte 0-3 …

3AH-3DH

Ch 4 A-channel U-bit

buffer for Byte 0-3 …

3EH-41H

Ch 4 B-channel U-bit

buffer for Byte 0-3 … Table 7. レジスタマップ Notes: (1) ステレオモードでは A が Lch、B が Rch を示します。 (2) 非同期モード時、DIF2-0, CKS1-0 bits の設定はピン設定と内部で OR が取られます。 (3) アドレス 42H∼FFH にはデータを書き込まないで下さい。 (4) PDN pin = “L”で、レジスタは初期化されます。

MS0250-J-01 2012/11 - 23 -

詳細説明

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 00H Clock/Format Control CRCE DIF2 DIF1 DIF0 CKS1 CKS0 MUTEN RSTN

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 1 0 0 0 0 0 1 1

RSTN: タイミングリセット

0: 内部フレームとビットカウンタのリセット。コントロールレジスタは初期化されません。 TXP pin は “H”、TXN pin は “L”になります。ノーマルモード時、BLS pinは “H”になりま す。 1: 通常動作 (Default) MUTEN: 非同期モードのパワーダウン&ミュート 0: パワーダウン。コントロールレジスタは初期化されません。 TXP, TXN pins は “L”になります。ノーマルモード時、BLS pin は “H”になります。 1: 通常動作 (Default) CKS1-0: マスタクロック周波数選択 (Table 1) Default: “00” (Mode 0: MCLK=128fs) CKS1-0 bitsの設定はピン設定と内部でORが取られます。 DIF2-0: オーディオデータフォーマット (Table 3)

Default: “000” (Mode 0: 16bit後詰め)

DIF2-0 bitsの設定はピン設定と内部でORが取られます。 CRCE: プロフェッショナルモード時の CRCC 有効

0: CRCC は生成されません。

1: プロフェッショナルモード時は CRCC が生成され、民生モード時は生成されません。 (Default)

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 01H Validity/fs Control V4 V3 V2 V1 FS3 FS2 FS1 FS0 R/W R/W R/W R/W R/W R/W R/W R/W R/W Default 0 0 0 0 0 0 0 0 FS3-0: サンプリング周波数選択 (Table 4, Table 5) Default: “0000” (民生モード時は “44.1kHz”、プロフェッショナルモード時は “未規定”) V1-4: バリディティフラグ 0: Valid (Default) 1: Invalid

V12 pin V1 bit V2 bit V bit on TX1 V bit on TX2

0 0 0 0 0 0 0 1 0 1 0 1 0 1 0 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 1 Table 8. 非同期モード時のV bitの設定

MS0250-J-01 2012/11 - 24 -

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 02H Ch 1 A-channel C-bit

buffer for Byte 0 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0 06H Ch 1 B-channel C-bit

buffer for Byte 0 CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0 12H Ch 2 A-channel C-bit

buffer for Byte 0 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0 16H Ch 2 B-channel C-bit

buffer for Byte 0 CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0 22H Ch 3 A-channel C-bit

buffer for Byte 0 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0 26H Ch 3 B-channel C-bit

buffer for Byte 0 CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0 32H Ch 4 A-channel C-bit

buffer for Byte 0 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0 36H Ch 4 B-channel C-bit

buffer for Byte 0 CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 0 1 0 0

C0-7: Channel Status Byte 0 Default: “00100000”

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 03H Ch 1 A-channel C-bit

buffer for Byte 1 CA15 CA14 CA13 CA12 CA11 CA10 CA9 CA8 07H Ch 1 B-channel C-bit

buffer for Byte 1 CB15 CB14 CB13 CB12 CB11 CB10 CB9 CB8 13H Ch 2 A-channel C-bit

buffer for Byte 1 CA15 CA14 CA13 CA12 CA11 CA10 CA9 CA8 17H Ch 2 B-channel C-bit

buffer for Byte 1 CB15 CB14 CB13 CB12 CB11 CB10 CB9 CB8 23H Ch 3 A-channel C-bit

buffer for Byte 1 CA15 CA14 CA13 CA12 CA11 CA10 CA9 CA8 27H Ch 3 B-channel C-bit

buffer for Byte 1 CB15 CB14 CB13 CB12 CB11 CB10 CB9 CB8 33H Ch 4 A-channel C-bit

buffer for Byte 1 CA15 CA14 CA13 CA12 CA11 CA10 CA9 CA8 37H Ch 4 B-channel C-bit

buffer for Byte 1 CB15 CB14 CB13 CB12 CB11 CB10 CB9 CB8

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 0 0 0 0

C8-15: Channel Status Byte 1 Default: “00000000”

MS0250-J-01 2012/11 - 25 -

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 04H Ch 1 A-channel C-bit

buffer for Byte 2 CA23 CA22 CA21 CA20 CA19 CA18 CA17 CA16 14H Ch 2 A-channel C-bit

buffer for Byte 2 CA23 CA22 CA21 CA20 CA19 CA18 CA17 CA16 24H Ch 3 A-channel C-bit

buffer for Byte 2 CA23 CA22 CA21 CA20 CA19 CA18 CA17 CA16 34H Ch 4 A-channel C-bit

buffer for Byte 2 CA23 CA22 CA21 CA20 CA19 CA18 CA17 CA16

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 1 0 0 0 0

CA16-23: Channel Status Byte 2 for A-channel Default: “00001000”

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 08H Ch 1 B-channel C-bit

buffer for Byte 2 CB23 CB22 CB21 CB20 CB19 CB18 CB17 CB16 18H Ch 2 B-channel C-bit

buffer for Byte 2 CB23 CB22 CB21 CB20 CB19 CB18 CB17 CB16 28H Ch 3 B-channel C-bit

buffer for Byte 2 CB23 CB22 CB21 CB20 CB19 CB18 CB17 CB16 38H Ch 4 B-channel C-bit

buffer for Byte 2 CB23 CB22 CB21 CB20 CB19 CB18 CB17 CB16

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 1 0 0 0 0 0

CB16-23: Channel Status Byte 2 for B-channel Default: “00000100”

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0 05H Ch 1 A-channel C-bit

buffer for Byte 3 CA31 CA30 CA29 CA28 CA27 CA26 CA25 CA24 09H Ch 1 B-channel C-bit

buffer for Byte 3 CB31 CB30 CB29 CB28 CB27 CB26 CB25 CB24 15H Ch 2 A-channel C-bit

buffer for Byte 3 CA31 CA30 CA29 CA28 CA27 CA26 CA25 CA24 19H Ch 2 B-channel C-bit

buffer for Byte 3 CB31 CB30 CB29 CB28 CB27 CB26 CB25 CB24 25H Ch 3 A-channel C-bit

buffer for Byte 3 CA31 CA30 CA29 CA28 CA27 CA26 CA25 CA24 29H Ch 3 B-channel C-bit

buffer for Byte 3 CB31 CB30 CB29 CB28 CB27 CB26 CB25 CB24 35H Ch 4 A-channel C-bit

buffer for Byte 3 CA31 CA30 CA29 CA28 CA27 CA26 CA25 CA24 39H Ch 4 B-channel C-bit

buffer for Byte 3 CB31 CB30 CB29 CB28 CB27 CB26 CB25 CB24

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 0 0 1 0

C24-31: Channel Status Byte 3 Default: “01000000”

MS0250-J-01 2012/11 - 26 -

Addr Register Name D7 D6 D5 D4 D3 D2 D1 D0

0AH-0DH

Ch 1 A-channel U-bit buffer for Byte 0-3

UA7 … UA31 … … … … … … … … … … … … UA0 … UA24 0EH-11H Ch 1 B-channel U-bit buffer for Byte 0-3

UB7 … UB31 … … … … … … … … … … … … UB0 … UB24 1AH-1DH Ch 2 A-channel U-bit buffer for Byte 0-3

UA7 … UA31 … … … … … … … … … … … … UA0 … UA24 1EH-21H Ch 2 B-channel U-bit buffer for Byte 0-3

UB7 … UB31 … … … … … … … … … … … … UB0 … UB24 2AH-2DH Ch 3 A-channel U-bit buffer for Byte 0-3

UA7 … UA31 … … … … … … … … … … … … UA0 … UA24 2EH-31H Ch 3 B-channel U-bit buffer for Byte 0-3

UB7 … UB31 … … … … … … … … … … … … UB0 … UB24 3AH-3DH Ch 4 A-channel U-bit buffer for Byte 0-3

UA7 … UA31 … … … … … … … … … … … … UA0 … UA24 3EH-41H Ch 4 B-channel U-bit buffer for Byte 0-3

UB7 … UB31 … … … … … … … … … … … … UB0 … UB24 R/W R/W R/W R/W R/W R/W R/W R/W R/W Default 0 0 0 0 0 0 0 0

U0-31: User Data Default: all “0”

MS0250-J-01 2012/11 - 27 - コントロールレジスタの初期値 ビット 初期値 CRCE 1 CRCC 生成 DIF2-0 000 16bit, 後詰め CKS1-0 00 MCLK=128fs V4-1 0000 Valid データ FS3-0 0000 fs=44.1kHz MUTEN 1 通常動作 RSTN 1 通常動作 Channel Status - Bit0 0 民生モード - Bit1 0 オーディオモード - Bit2 1 著作権保護なし - Bit3-5 000 エンファシスなし Byte0 - Bit6-7 00 Mode 0

Byte1 - Bit0-7 00000000 カテゴリーコード: General - Bit0-3 0000 ソース番号: 指定なし Byte2 - Bit4-7 1000 0100 チャネル: A チャネル: B - Bit0-3 0100 fs=48kHz - Bit4-5 00 クロック精度: 標準 Byte3 - Bit6-7 00 User Data All zeros

MS0250-J-01 2012/11 - 28 - パッケージ 0.15 0.09 ~ 0.20 0.37±0.10 10.0 1.70max 1 11 23 33

44pin LQFP (Unit: mm)

10 .0 12.0 34 44 0. 80 22 12 12. 0 0 ~ 0.2 0°∼10° 0.60±0.20 材質・メッキ仕様 パッケージ材質: エポキシ系樹脂 リードフレーム材質: 銅 リードフレーム処理: 半田(無鉛)メッキMS0250-J-01 2012/11 - 29 - マーキング

AK4101AVQ

XXXXXXX

1

1) Pin #1 indication2) Date Code: XXXXXXX(7 digits) 3) Marking Code: AK4101AVQ 4) Asahi Kasei Logo

改訂履歴 Date (Y/M/D) Revision Reason Page Contents 03/07/28 00 初版

12/11/12 01 仕様変更 28 パッケージ

MS0250-J-01 2012/11 - 30 - 重要な注意事項 z 本書に記載された製品、および、製品の仕様につきましては、製品改善のために予告なく変更することがありま す。従いまして、ご使用を検討の際には、本書に掲載した情報が最新のものであることを弊社営業担当、あるい は弊社特約店営業担当にご確認ください。 z 本書に記載された周辺回路、応用回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応 用例を説明するものです。お客様の機器設計において本書に記載された周辺回路、応用回路、ソフトウェアおよ びこれらに関連する情報を使用される場合は、お客様の責任において行ってください。本書に記載された周辺 回路、応用回路、ソフトウェアおよびこれらに関連する情報の使用に起因してお客様または第三者に生じた損害 に対し、弊社はその責任を負うものではありません。また、当該使用に起因する、工業所有権その他の第三者の 所有する権利に対する侵害につきましても同様です。 z 本書記載製品が、外国為替および、外国貿易管理法に定める戦略物資(役務を含む)に該当する場合、輸出す る際に同法に基づく輸出許可が必要です。 z 医療機器、安全装置、航空宇宙用機器、原子力制御用機器など、その装置・機器の故障や動作不良が、直接ま たは間接を問わず、生命、身体、財産等へ重大な損害を及ぼすことが通常予想されるような極めて高い信頼性 を要求される用途に弊社製品を使用される場合は、必ず事前に弊社代表取締役の書面による同意をお取りくだ さい。 z この同意書を得ずにこうした用途に弊社製品を使用された場合、弊社は、その使用から生ずる損害等の責任を 一切負うものではありませんのでご了承ください。 z お客様の転売等によりこの注意事項の存在を知らずに上記用途に弊社製品が使用され、その使用から損害等 が生じた場合は全てお客様にてご負担または補償して頂きますのでご了承下さい。

![Table 3. オーディオデータフォーマットモード [NOTE: (I): Input, (O): Output]](https://thumb-ap.123doks.com/thumbv2/123deta/5965522.573343/15.892.117.782.124.254/Table3オーディオデータフォーマットモードNOTEIInputOOutput.webp)