概要

信号の多重化は一般的に よ く 用い ら れ る 機能で あ り 、 通常はザ イ リ ン ク ス の イ ン プ リ メ ン テーシ ョ ン ツールやデバ イ ス に よ っ て適切に処理 さ れ ま す。 し か し 、 デザ イ ン に よ っ ては通常の多重化が難 し く 、 異な る 多重化テ ク ニ ッ ク を使用 し て最 も 状況に適 し た処理を選択す る 必要があ り ます。 デバ イ ス の機能 やそれぞれの多重化テ ク ニ ッ ク の適正を十分理解 し てお く こ と が、 優れたデザ イ ン を構築す る 上で重要 です。 こ のアプ リ ケーシ ョ ン ノ ー ト では、 イ ンプ リ メ ン テーシ ョ ン を最大限に制御 し 、 予測可能な結果 を生み出す VHDL や Verilog コ ー ド について も 説明 し ます。概要

FPGA は、 数多 く の同時 ス イ ッ チ ン グ動作を伴 う 演算 と ロ ジ ッ ク の基板です。 た と えば、 有線ネ ッ ト ワー ク のルーテ ィ ン グシ ス テ ムでは、FPGA が M:N を構成す る ロ ジ ッ ク エ レ メ ン ト 間に さ ま ざ ま な配 線パ タ ーン を提供 し ます。 高帯域幅が求め ら れ る のに伴っ て M と N が共に大き く な り 、M が N よ り 大 き い 場 合 は、 効 率 的 な 多 重 化 タ ス ク を イ ン プ リ メ ン ト す る 必 要 が 生 じ て き ま す。 こ の た め、 Spartan®-6 FPGA、Virtex®-6 FPGA、 お よ び 7 シ リ ーズ FPGA におけ る デー タ パ ス の配線は、 シ ス テ ム設計で不可欠です。FPGA の イ ンプ リ メ ン テーシ ョ ンでシ ス テ ムの目標を達成す る には、 合成以外の処理が必要 と な る 場合 があ り ます (例 : PlanAhead® ツールを使用 し て配置を固定)。 こ のアプ リ ケーシ ョ ン ノ ー ト では、 別の 方法 と し て ISE® Design Suite ま たは Vivado™ Design Suite を使用 し て HDL を記述す る だけで、デー タ 配線 ロ ジ ッ ク を効果的に イ ン プ リ メ ン ト す る 新 し い手法を紹介 し ま す。 こ の手法では、 デザ イ ン ク ロ ージ ャ ーを達成す る ために 2 つの こ と を並行 し て行い ます。1 つ目は、 汎用 イ ン タ ー コ ネ ク ト 配線の 使用を可能な限 り 抑えなが ら ス ラ イ ス内に よ り 多 く の ロ ジ ッ ク を含めて、パフ ォーマ ン を向上 さ せます。 2 つ目は、 よ り 多 く の ロ ジ ッ ク を最小限の配線で イ ン プ リ メ ン ト す る こ と で結果の確定性を向上 さ せ、 イ ンプ リ メ ン テーシ ョ ンにおけ る FPGA リ ソ ース使用率の削減や ソ フ ト ウ ェ ア ラ ン タ イ ムの向上な ど、 シ ス テ ム デザ イ ンのほかの部分に利点を も た ら し ます。 よ り 効率的な多重化お よ びデー タ 配線のためには、 まず ロ ジ ッ ク を配線す る ビヘ イ ビ ア合成で通常は推 論 さ れない Spartan-6 FPGA、Virtex-6 FPGA、 お よ び 7 シ リ ーズ FPGA の ス ラ イ ス アーキ テ ク チ ャ の 特徴を理解す る 必要があ り ます。 その知識を持っ た上で比較的単純な実践的な手法を用い、 使用 リ ソ ー ス 数の削減や M:N ロ ジ ッ ク の 1 ビ ッ ト あ た り の配線数削減な ど の大 き な利点を得 る こ と がで き ま す。 デザ イ ンでは、2Nマルチプ レ ク サー、 バ イ ナ リ セ レ ク ト のマルチプ レ ク サー (2N以外のサ イ ズ)、 別手 段 と し てのデー タ セ レ ク タ ー、 お よ び こ れ ら の FPGA イ ン プ リ メ ン テーシ ョ ン を示 し てい ます。 こ れ ら の手法では、FPGA ス ラ イ ス内にあ る 基本エ レ メ ン ト (BEL) を使用 し て再利用可能なセルを構築 し ま す。 こ のセルは、 ユーザー要件に応 じ て簡単に修正可能でユーザー制約を適用 し な く て も FPGA の任意 の位置に配置で き ます。

デー タ 配線ロ ジ ッ クのビヘ イ ビ ア合成における問題

マルチプ レ ク サーお よ びデー タ 配線 ロ ジ ッ ク のビヘ イ ビ ア合成を、FPGA イ ンプ リ メ ン テーシ ョ ン ツー ル と 組み合わせて実行 し た場合、効率の良 く ない結果 と な る 可能性があ り 、特に多入力マルチプ レ ク サー を イ ンプ リ メ ン ト す る 場合は最適な結果が得 ら れません。 通常、 合成ツールではデバ イ ス が持つ最 も 確 実な多重化機能が使用 さ れ る ため、高速な ク ロ ッ ク レー ト で大規模なデー タ パ ス幅を含む必要があ る 場 合には、 効率が低下す る 可能性があ り ます。ア プ リ ケーシ ョ ン ノ ー ト : Spartan-6 フ ァ ミ リ 、Virtex-6 フ ァ ミ リ 、 7 シ リ ーズ FPGA

XAPP522 (v1.1) 2012 年 8 月 30 日

最小限の配線 リ ソ ースでデー タパス性能を

向上 させるマルチプ レ クサー設計手法

概要

大規模マルチプ レ ク サー構造では、 小規模マルチプ レ ク サーの イ ン ス タ ン ス を多数カ ス ケー ド 接続す る 必要があ り ます。 こ の よ う に複製 さ れた カ ス ケー ド 接続では、LUT と 汎用 イ ン タ ー コ ネ ク ト の接続に多 く の配線を必要 と す る 傾向があ り ます。 マルチプ レ ク サーは、 本質的に多対少 (M:N) の配線パ タ ーン で す。 し たがっ て、 大規模マルチプ レ ク サーには配線が多 く 必要 と な り ます。 たいていの場合、 デー タ は FPGA 全体に分散 さ れた ISERDES/OSERDES プ リ ミ テ ィ ブ、 ブ ロ ッ ク RAM メ モ リ 、 お よ び DSP ブ ロ ッ ク な ど の間を行 き 来す る 必要があ る ため、 こ れ ら の配線は FPGA の大部分に広が り ます。 ス ラ イ ス 間の配線 リ ソ ース を多用す る と 、AC パフ ォーマ ン ス を低下 さ せ る 要因 と な る ため、 適切な イ ン プ リ メ ン テーシ ョ ン ス タ イ ルを選択す る こ と が重要です。 ス ラ イ ス外の汎用配線 リ ソ ース を使用す る こ と が求め ら れてい る よ う ですが、有効な FPGA リ ソ ース が 最大限に活用 さ れていない場合が よ く あ り ます。 こ れ ら の リ ソ ース はすべて ス ラ イ ス内にあ り ます。 こ れ ら を活用す る こ と で、 少ない配線で よ り 多 く の ロ ジ ッ ク を イ ンプ リ メ ン ト で き ます。

FPGA

ス ラ イ スの構築ブ ロ ッ ク

:

内部を見る

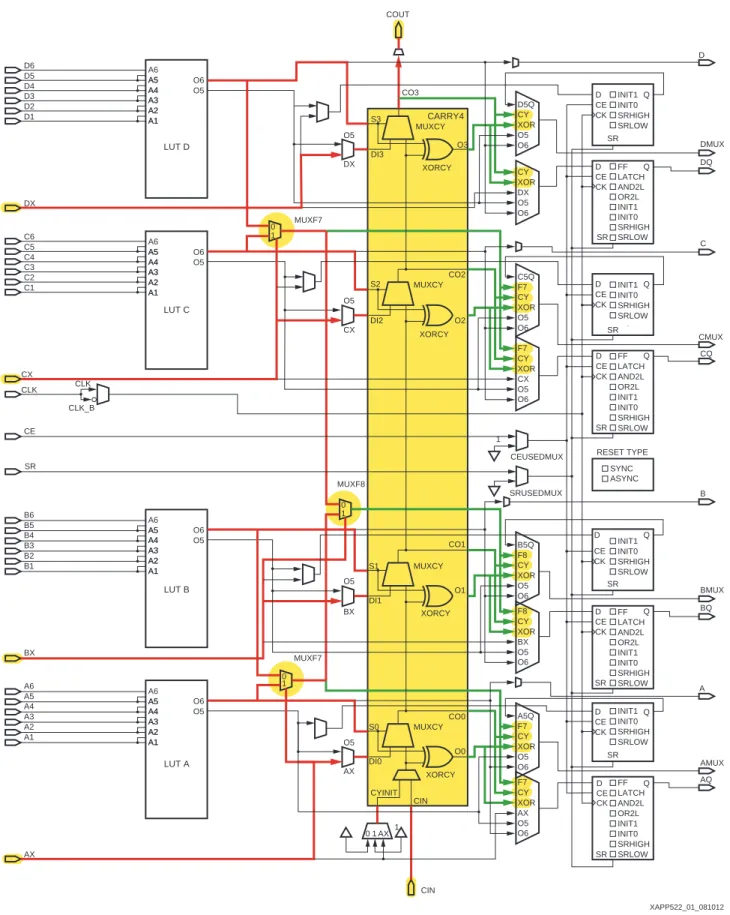

Spartan-6 FPGA、Virtex-6 FPGA、 お よ び 7 シ リ ーズ FPGA はすべて、 非常に多 く の コ ン フ ィ ギ ュ レー シ ョ ン ロ ジ ッ ク ブ ロ ッ ク (CLB) を備え てお り 、 各 CLB には 2 つの ス ラ イ ス が含まれます。 こ のアプ リ ケーシ ョ ン ノ ー ト では、 次に示すス ラ イ ス の特性を利用 し ます。 • SLICEL : ロ ジ ッ ク と 算術機能のみ実行 し ます。 • SLICEM : ロ ジ ッ ク 、 算術、 メ モ リ/シ フ ト レ ジ ス タ 機能を実行 し ます。 SLICEL と SLICEM を組み合わせて使用す る こ と で、 さ ま ざ ま な機能を シ ス テ ム に イ ン プ リ メ ン ト で き ます。 デザ イ ン には SLICEL のみを示 し てい ますが、 こ のアプ リ ケーシ ョ ン ノ ー ト で説明す る 設計 手法は SLICEM ス ラ イ ス に も 同様に適用で き る ため、 一般的な説明 と し て不足す る 内容はあ り ません。 注記 : Virtex-6 FPGA お よ び 7 シ リ ーズ FPGA に含まれ る ス ラ イ ス は SLICEL と SLICEM の 2 種類の みですが、Spartan-6 FPGA には簡略化 さ れた SLICEX も 含まれます。 こ のアプ リ ケーシ ョ ン ノ ー ト で 説明す る 手法は SLICEX に適用で き ませんが、通常はデザ イ ンの要件を満たすのに十分な数の SLICEL と SLICEM が含まれてい ます。 1 つの ス ラ イ ス には 4 つの 6 入力 LUT と 8 つの フ リ ッ プ フ ロ ッ プがあ り ます。図1 に、SLICEL 内の 主な ロ ジ ッ ク を詳細に示 し ます。 図1 では、 付加的な内部 BEL お よ びその他の リ ソ ー ス を黄色でハ イ ラ イ ト し 、 入力経路は赤色で、 出 力経路は緑色でハ イ ラ イ ト し てい ます。 こ こ で説明す る すべてのパ ス は ス ラ イ ス内部にあ り 、 汎用配線 リ ソ ース は使用 し てい ません。BEL お よ びス ラ イ ス内の配線は、 高速演算 ロ ジ ッ ク や多重化用に設計 さ れてい る ため非常に高速です。 こ れ ら 演算以外の構築ブ ロ ッ ク の役割を理解 し てお く こ と で、 拡張性に優れた多重化構造お よ びデー タ 配線構造を実現で き ます。 さ ら に、 こ れ ら の柔軟な構築ブ ロ ッ ク に よ っ て、 豊富なデー タ パス エ レ メ ン ト が も た ら さ れます。

概要

X-Ref Target - Figure 1

図 1 : FPGA の SLICEL 1 0 1 0 CLK CLK_B C2 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 A1 AX BX CE A4 A2 A3 A5 CLK A6 B1 B2 B3 B4 B5 B6 SR CX C1 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 C4 C5 C3 C6 D2 D1 D3 DX D4 D5 D6 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 INIT0 INIT1 CK CE D SR DI0 S0 DI1 S1 DI2 S2 DI3 S3 O0 CO0 O1 CO1 O2 CO2 O3 CO3 CYINIT CIN CARRY4 LUT D LUT C LUT B LUT A INIT0 INIT1 SRHIGH SRLOW SRHIGH SRLOW CK CE D SR LATCH FF OR2L AND2L CK CE D SR SRHIGH SRLOW CK CE D SR LATCH FF OR2L AND2L CK CE D SR SRHIGH SRLOW SYNC ASYNC RESET TYPE SRHIGH SRLOW CK CE D SR XAPP522_01_081012 LATCH FF OR2L AND2L INIT0 INIT1 INIT0 INIT1 INIT0 INIT1 SRHIGH SRLOW INIT0 INIT1 INIT0 INIT1 CK CE D SR LATCH FF OR2L AND2L SRHIGH SRLOW INIT0 INIT1 CK CE D Q Q Q Q Q Q Q Q SR SRHIGH SRLOW O6 O5 XOR CY F7 C5Q CIN AX 1 0 O5 AX 1 1 0 O5 BX O5 CX O6 O5 XOR CY F7 A5Q F7 CY XOR AX O5 O6 F8 CY XOR BX O5 O6 O6 O5 XOR CY F8 B5Q SRUSEDMUX 1 F7 CY XOR CX O5 O6 CEUSEDMUX AMUX BMUX CMUX AQ A B CQ BQ O5 DX CY XOR DX O5 O6 D5Q CY XOR O5 O6 DMUX DQ C D MUXF7 COUT MUXF7 MUXF8 MUXCY XORCY MUXCY XORCY MUXCY XORCY MUXCY XORCY

概要

MUXF7

および

MUXF8 BEL

図1では、2 つの MUXF7 BEL と 1 つの MUXF8 BEL を黄色の丸でハ イ ラ イ ト し てい ます。 こ れ ら の BEL は、 ス ラ イ ス内部にあ る 非常に高速な多重化 ロ ジ ッ ク で構成 さ れてい ます。 説明上、図1 の左下に あ る LUT6 を LUT A と し ます。 ス ラ イ ス内の LUT カ ラ ムでは、下か ら 上に向か っ て LUT B、LUT C、 LUT D と な り 、図1 の左上に LUTD があ り ます。

MUXF7 BEL お よ び MUXF8 BEL のセ レ ク ト ラ イ ンへは、LUT A ~ LUT D の入力 と は関係のない ス ラ イ ス 入力を用いて ア ク セ ス し ます。 つま り 、図1 の左側に赤色でハ イ ラ イ ト し た AX、BX、 お よ び CX ラ イ ン を使用す る ため、 こ れ ら の入力は ス ラ イ ス内の LUT 配線へ影響を及ぼ し ません。AX と CX は、2 つの MUXF7 のセ レ ク ト ラ イ ンへそれぞれ配線 さ れてい ま す。 赤色でハ イ ラ イ ト さ れた AX で 制御 さ れ る 一番下の MUXF7 は、LUT A と LUT B の出力 O6 か ら のデー タ 入力を受け取 り ます。 同様 に、CX で制御 さ れ る 一番上の MUX 7 は、LUT C と LUT D の出力 O6 か ら デー タ 入力を受け取 り ます。 MUXF 7 は、 制御 ラ イ ン に よ っ て ロ ジ ッ ク が判断 さ れ る よ う に あ ら か じ め構成 さ れてい ま す。 た と え ば、 入力 AX お よ び CX が 0 の場合は、LUT B と LUT D のデー タ がマルチプ レ ク サー出力へ配線 さ れ ます。 同様に、 入力 AX お よ び CX が1の場合は、LUT A と LUT C のデー タ がマルチプ レ ク サー 出力へ配線 さ れます。図1 に示 さ れてい る よ う に、 こ れ ら のマルチプ レ ク サー出力は ス ラ イ ス の外にあ る ロ ジ ッ ク へ と 配線で き ます。 こ れ ら の配線は、 プ ロ グ ラ ム可能な コ ン フ ィ ギ ュ レーシ ョ ン マルチプ レ ク サー (F7) へ接続 さ れます。 こ の よ う に、 汎用 イ ン タ ー コ ネ ク ト へア ク セ ス、 あ る いは内部フ リ ッ プ フ ロ ッ プ を介 し てか ら 汎用 イ ン タ ー コ ネ ク ト へア ク セ ス で き る こ と が、 コ ン フ ィ ギ ュ レーシ ョ ン可能な ス ラ イ ス の特徴の 1 つです。

MUXF7 BEL は LUT の近 く に配置 さ れ、 専用配線が短 く 、0 と 1のセ レ ク ト 信号用にデー タ 規則があ

ら か じ め設定 さ れてい る ため非常に高速です。

ス ラ イ ス内部の多重化機能は、 入力 BX か ら セ レ ク ト ラ イ ン を受け取 る MUXF8 を使用す る こ と で さ ら に拡張 さ れます (図1 参照)。MUXF7 BEL の出力のみが MUXF8 BEL の入力 と な り 、 こ の よ う に し て 1 段目の 2 つのマルチプ レ ク サーの後に、 マルチプ レ ク サーを も う 1 つ配置 し ます。MUXF8 は、F8 へ接続す る ラ イ ン を介 し て フ リ ッ プ フ ロ ッ プお よ び汎用 イ ン タ ー コ ネ ク ト へア ク セ スす る よ う に構成で き ます (図1)。

こ れ ら の BEL は、 デー タ 配線用に多様な機能を提供で き る 内部でプ ロ グ ラ ム可能な リ ソ ース です。 た と えば、 最大 6 変数の 2 つの ロ ジ ッ ク フ ァ ン ク シ ョ ン を各 MUX7 で直接 2:1 マルチプ レ ク ス し 、 2 つ の LUT6 出力を結合で き ます。LUT6 で 4:1 マルチプ レ ク サーを イ ンプ リ メ ン ト し て MUXF7 を追加す る と 、1 ス ラ イ ス に 2 つの 8:1 マルチプ レ ク サーを構築で き ます。 同様に MUXF7 を MUXF8 と 結合す る と 、1 ス ラ イ ス に 16:1 のマルチプ レ ク サーを構築可能です。LUT6 で実行す る ロ ジ ッ ク フ ァ ン ク シ ョ ンは、マルチプ レ ク サーの ロ ジ ッ ク フ ァ ン ク シ ョ ン であ る必要はあ り ません。 ど の よ う な ロ ジ ッ ク フ ァ ン ク シ ョ ンで も 可能です。MUXF7 お よ び MUXF8 を使用す る マルチプ レ ク サーの例を 「最初の例」お よ び 「マルチプ レ ク サーの一般的な構築ブ ロ ッ ク 」 に示 し ます。 その他に も 、 非常に高速で効率的な配 線を備えた大規模なマルチプ レ ク サーの例を紹介 し ます。

CARRY4

ブ ロ ッ ク

CARRY4 ブ ロ ッ ク には、2 種類 (MUXCY お よ び XORCY) の BEL が 4 回複製 さ れて配置 さ れてい ま す。図1の中央に、 黄色でハ イ ラ イ ト さ れた大 き な CARRY4 ブ ロ ッ ク が あ り ま す。MUXF7 お よ び MUXF8 BEL と 非常に よ く 似た MUXCY には、 あ ら か じ め設定 さ れた配線があ り 、 制限付 き なが ら コ ン フ ィ ギ ュ レーシ ョ ン可能です。MUXCY の名目上の機能は、 迅速な 2 進数の加算を行 う ための高速 キ ャ リ ー伝搬 ロ ジ ッ ク と し て動作す る こ と です。

し か し 、 こ の MUXCY は実際にはマルチプ レ ク サー と し て機能 し 、 デー タ 配線用の ロ ジ ッ クゲー ト に も な り ます。MUXCY BEL を ゲー ト と し て使用 し て独自のデー タ 配線を行 う 方法は、「別手段 と し ての

最初の例

ラ ム で き ます。 た と えば、 デー タ パ ス ロ ジ ッ ク 内のプ ロ グ ラ マブル ビ ッ ト フ ィ ール ド を マ ス ク す る 際 に、 こ の選択的な反転を適用で き ます。MUXCY と XORCY を組み合わせて使用す る こ と で、 さ ら に 大規模な XOR 機能が実現可能にな り ます。MUXCY を活用 し てデー タ 配線機能を構築す る 方法は、「別

手段 と し てのデー タ セ レ ク タ ー」 で詳 し く 説明 し ます。

図1の緑色でハ イ ラ イ ト さ れてい る 配線は、MUXCY お よ び XORCY BEL には、 ス ラ イ ス内の出力 コ ン フ ィ ギ ュ レーシ ョ ン マルチプ レ ク サーの入力 (CY お よ び XOR) を介 し て、 フ リ ッ プ フ ロ ッ プ ま たは 汎用 イ ン タ ー コ ネ ク ト のいずれかへ接続す る 出力があ る こ と を示 し てい ます。

注記 : 一番下の MUXCY は、 キ ャ リ ー チ ェ ーン入力 と し て CYINIT ま たは CIN のいずれか を選択す る よ う に設計 さ れてい る マルチプ レ ク サー と 関連 し てい る 点がほか と 異な り ます。 ス ラ イ ス を カ ス ケー ド 接続 し て さ ら に大規模な フ ァ ン ク シ ョ ン を構築す る 場合は CIN が選択 さ れます。キ ャ リ ーチ ェーンの 開始を初期化す る 場合は CYINIT が選択 さ れます。

キ ャ リ ー イ ン

(CIN)

リ ソ ース

CIN リ ソ ース は、図1 の大 き な黄色いボ ッ ク ス の一番下にあ る CARRY4 ブ ロ ッ ク の一部です。 下か ら 上へ伝搬 さ れ る キ ャ リ ーチ ェーンの一番下には複数の入力があ り 得ます。 デー タ 配線アプ リ ケーシ ョ ン で重要なのは CIN 入力です。 こ の入力は、CYINIT 入力で選択 さ れた固定ビ ッ ト 0 お よ び 1 へア ク セ スす る ために、 コ ン フ ィ ギ ュ レーシ ョ ンマルチプ レ ク サーを共有 し ます。 通常、 こ の固定 さ れた ビ ッ ト 設定は、カ ウ ン タ ーの強制 イ ン ク リ メ ン ト や加算器のキ ャ リ ー イ ン入力な ど、特定の算術機能のキ ャ リ ー チ ェーン を開始す る ために使用 さ れます。 ただ し 、 デー タ 配線用に文字通 り の 0 お よ び 1 ビ ッ ト を送信可能で、 実際のデー タ ビ ッ ト も キ ャ リ ー チ ェーンに入力で き ます。 デー タ は、CYINIT パ ス を使用す る AX か ら 入力 さ れます。LUT

のみを使用する場合よ り も 多入力

図1 に示す と お り 、 黄色でハ イ ラ イ ト さ れた入力のほかに AX、BX、CX、DX、CYINIT、 お よ び ロ ー カル生成 さ れた 0/1 ビ ッ ト な ど が利用可能です。 こ れ ら の入力は、 ス ラ イ ス LUT 用の配線 と 併用 さ れま す。 ま た、 こ れ ら の入力を CARRY4 BEL と 共に使用す る と 、LUT のみを使用す る 場合 よ り も 多 く の配線能力を実現で き ます。

CARRY4/CIN

と

MUXF7/MUXF8

間における名目上の相互排他

一 般 に、 ス ラ イ ス 内 部 の BEL を 活 用 す る ア プ リ ケ ー シ ョ ン で は、CARRY4/CIN ま た は MUXF7/MUXF8 のいずれか一方を使用 し ます。 物理的には、 ス ラ イ ス を半分に分け る な ど し て 1 つの ス ラ イ ス で こ れ ら 2 つを共に使用 し て も 問題はあ り ません。 一例 と し て、図1 の下部に配置 さ れてい る LUTA と LUTB と 共に CARRY4 ブ ロ ッ ク を組み合わせて使用 し なが ら 、上部に配置 さ れてい る LUTC と LUTD と 共に MUXF7 を組み合わせて使用 し ます。 こ の よ う な場合は、 ほぼ確実に 1 つの ス ラ イ ス にパ ッ ク さ れた 2 つの異な る アプ リ ケーシ ョ ンにな り ます。

一般的なデー タ 多重化アプ リ ケーシ ョ ン では、MUXF7/MUXF8 BEL ま たは CARRY4/CIN BEL のい ずれか を使用す る と 最 も 効果的です。MUXF7/MUXF8 を使用す る 方法については、「最初の例」 で説 明 し ます。

最初の例

FPGA SLICEL

に構築 さ れる

8

ビ ッ ト

マルチ プ レ ク サー

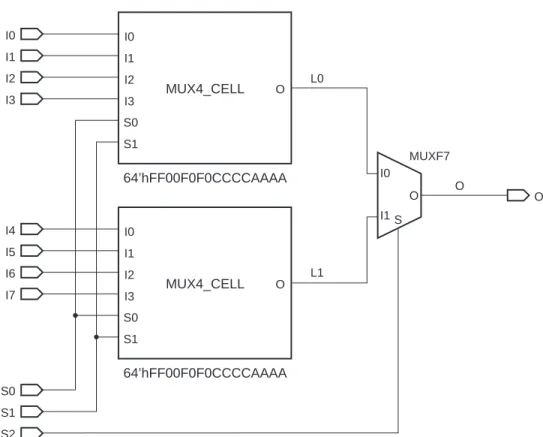

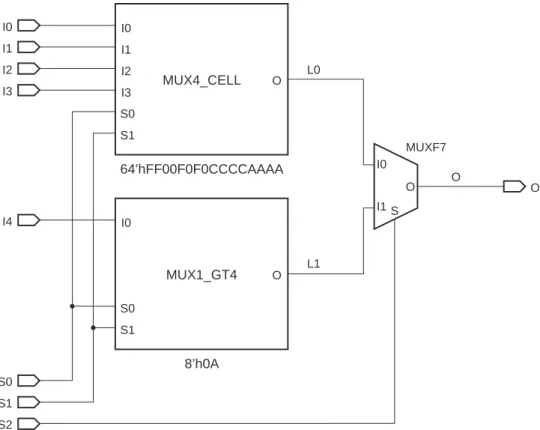

8 ビ ッ ト マルチプ レ ク サーに必要なのは、1 つの LUT6 で構成 さ れ る 2 つのセルデザ イ ンお よ びス ラ イ ス内の MUXF7 BEL のみです。図2 に、4 ビ ッ ト セル (MUX4_CELL) の ロ ジ ッ ク と LUT6 のプ ロ グ ラ ムに必要な INIT パ ラ メ ー タ ーを示 し ます。図3に、2 つの MUX4_CELL と 内部 MUXF7 マルチ プ レ ク サーを組み合わせたマルチプ レ ク サーの ロ ジ ッ ク を示 し ます。 各エ レ メ ン ト で構成 さ れたマルチ プ レ ク サーの HDL コ ー ド には、3 つの イ ン ス タ ン ス し かあ り ません (「 リ フ ァ レ ン ス デザ イ ン」参照)。 ス ラ イ ス の半分にすべての ロ ジ ッ ク が含まれてお り 、 残 り の半分は自由に使用可能です。 配線フ ロ ーは

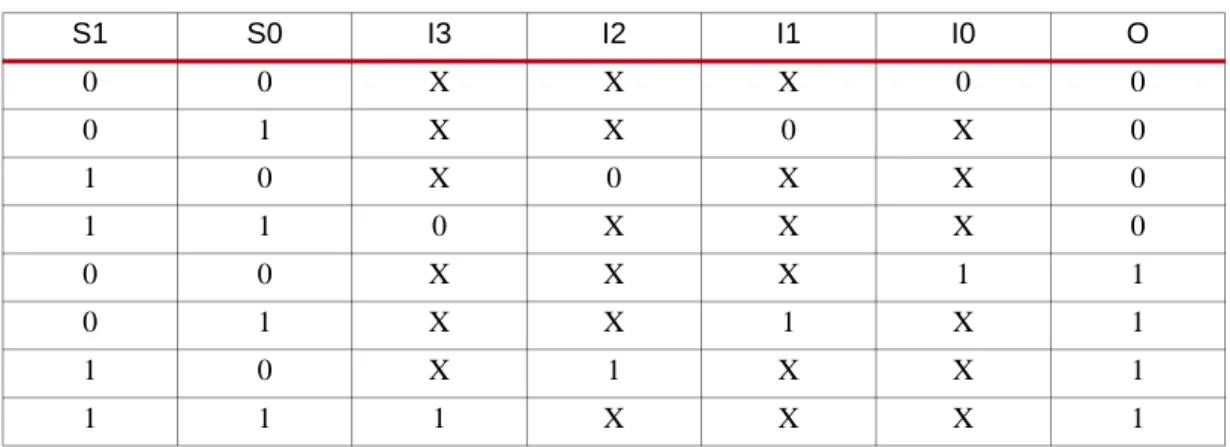

最初の例 表1 に、図2 の MUX4_CELL の真理値表を示 し ます。表2 には、図3 の完成 さ れた 8 ビ ッ ト マルチ プ レ ク サーの真理値表を示 し ます。 複数のエ レ メ ン ト で構成 さ れた複合マルチプ レ ク サーは、 よ り 広いビ ッ ト 幅を構築す る ためにマルチプ レ ク サーを統合 し たセルデザ イ ン と し て扱 う こ と がで き ます。 独立 し た 8 ビ ッ ト マルチプ レ ク サーセ ルを扱 う 場合 と 同様に、 帯域幅が広 く な っ て も イ ン タ ー コ ネ ク ト 配線を追加す る 必要はあ り ません。 ま た、2 つの 8 ビ ッ ト マルチプ レ ク サーは 1 つの ス ラ イ ス に含め る こ と がで き ます。 こ のアプ リ ケーシ ョ ン ノ ー ト の ロ ジ ッ ク 図では、プ ロ グ ラ ム可能な LUT コ ー ド を赤色で表 し てい ます。 カ ス タ マ イ ズ可能な LUT コ ー ド と その生成方法については、「補足資料 A : LUT コ ー ド の生成方法」を 参照 し て く だ さ い。

X-Ref Target - Figure 2

図 2 : MUX4_CELL および LUT6 の INIT 値

X-Ref Target - Figure 3

図 3 : ス ラ イ スベースの 8:1 マルチ プ レ クサー (MUX4_CELL (LUT6) を 2 個 と MUXF7 を 1 個使用)

64’FF00F0F0CCCCAAAA I2 I1 I0 O I4 I5 I3 I1 S0 O LUT6 I2 S1 I0 I3 XAPP522_02_112211 XAPP522_03_112211 I0 I1 O S I0 I1 I2 I3 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I4 I5 I6 I7 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L0 L1 MUXF7 O O S0 S1 S2

最初の例

マルチプ レ ク サーの FPGA への イ ンプ リ メ ン テーシ ョ ンお よ び MUX4_CELL と MUXF7 BEL の詳細

は、「8 ビ ッ ト マルチプ レ ク サーの FPGA イ ンプ リ メ ン テーシ ョ ン : 分析」 お よ び図4 を参照 し て く だ

さ い。

8

ビ ッ ト

マルチ プ レ クサーの

FPGA

イ ン プ リ メ ン テーシ ョ ン : 分析

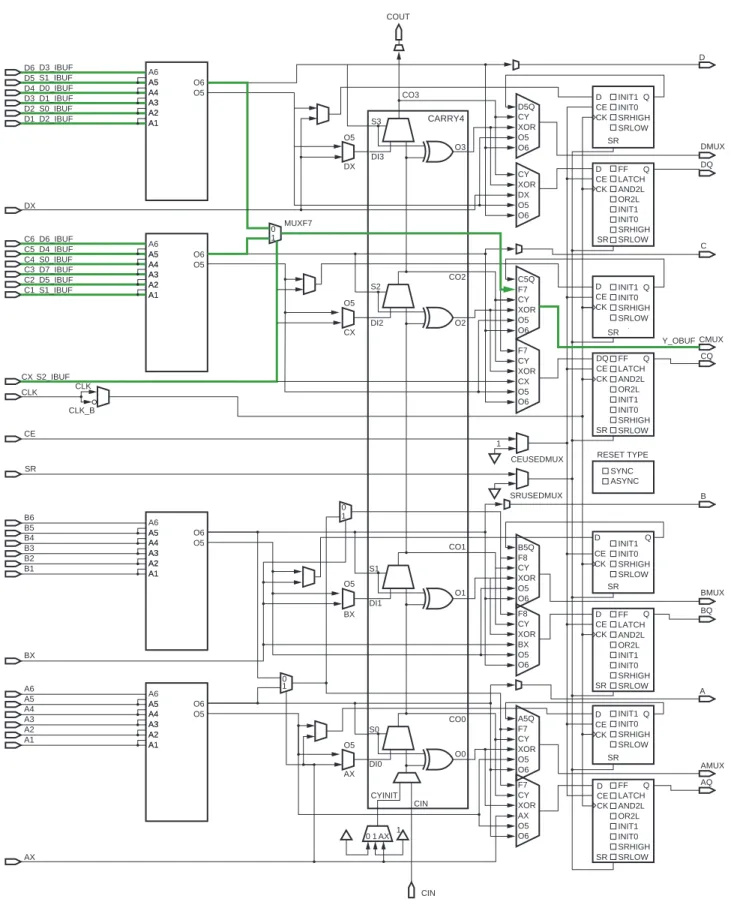

図4に、ISE ツールで ロ ジ ッ ク 合成 と イ ン プ リ メ ン テーシ ョ ン を実行後に FPGA の SLICEL に配置 さ れた 8 ビ ッ ト マルチプ レ ク サーを示 し ます。入力お よ び出力の経路は緑色で表 し てい ます。 ユーザー ロ ジ ッ ク で メ モ リ と し て SLICEM を使用 し ない場合、SLICEL の代わ り に ISE ツールが SLICEM を使用 し て も 同様の結果 と な り ます。 図4の ト ポ ロ ジは、図3の ロ ジ ッ ク 図 と 基本的に同 じ です。 ス ラ イ ス の半分 (上位の C/D LUT6 と 上位 の MUXF) のみを使用 し てい ます。 下半分に同 じ ロ ジ ッ ク を イ ンプ リ メ ン ト す る こ と も 可能です。 ほか のビ ッ ト サ イ ズでの ロ ジ ッ クバ リ エーシ ョ ンについては、「マルチプ レ ク サーの一般的な構築ブ ロ ッ ク 」 を参照 し て く だ さ い。 表 1 : MUX4_CELL の真理値表 : LUT6 に 4 ビ ッ ト マルチ プ レ ク サーを イ ン プ リ メ ン ト し た場合 S1 S0 I3 I2 I1 I0 O 0 0 X X X 0 0 0 1 X X 0 X 0 1 0 X 0 X X 0 1 1 0 X X X 0 0 0 X X X 1 1 0 1 X X 1 X 1 1 0 X 1 X X 1 1 1 1 X X X 1 表 2 : 完全 さ れた 8 ビ ッ ト マルチ プ レ クサーの真理値表 S2 S1 S0 I7 I6 I5 I4 I3 I2 I1 I0 O 0 0 0 X X X X X X X 0 0 0 0 1 X X X X X X 0 X 0 0 1 0 X X X X X 0 X X 0 0 1 1 X X X X 0 X X X 0 1 0 0 X X X 0 X X X X 0 1 0 1 X X 0 X X X X X 0 1 1 0 X 0 X X X X X X 0 1 1 1 0 X X X X X X X 0 0 0 0 X X X X X X X 1 1 0 0 1 X X X X X X 1 X 1 0 1 0 X X X X X 1 X X 1 0 1 1 X X X X 1 X X X 1 1 0 0 X X X 1 X X X X 1 1 0 1 X X 1 X X X X X 1 1 1 0 X 1 X X X X X X 1 1 1 1 1 X X X X X X X 1

最初の例

X-Ref Target - Figure 4

図 4 : FPGA の SLICEL に イ ン プ リ メ ン ト さ れた 8:1 マルチ プ レ ク サー Y_OBUF 1 0 1 0 CLK CLK_B C2 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 A1 AX BX CE A4 A2 A3 A5 CLK A6 B1 B2 B3 B4 B5 B6 SR CX C1 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 C4 C5 C3 C6 D2 D1 D3 DX D4 D5 D6 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 INIT0 INIT1 CK CE D SR DI0 S0 DI1 S1 DI2 S2 DI3 S3 O0 CO0 O1 CO1 O2 CO2 O3 CO3 CYINIT CIN CARRY4 INIT0 INIT1 SRHIGH SRLOW SRHIGH SRLOW CK CE D SR LATCH FF OR2L AND2L CK CE D SR SRHIGH SRLOW CK CE D SR LATCH FF OR2L AND2L CK CE D Q SR SRHIGH SRLOW SYNC ASYNC RESET TYPE SRHIGH SRLOW CK CE DQ SR XAPP522_04_081012 LATCH FF OR2L AND2L INIT0 INIT1 INIT0 INIT1 INIT0 INIT1 SRHIGH SRLOW INIT0 INIT1 INIT0 INIT1 CK CE D SR LATCH FF OR2L AND2L SRHIGH SRLOW INIT0 INIT1 CK CE D Q Q Q Q Q Q Q SR SRHIGH SRLOW O6 O5 XOR CY F7 C5Q CIN AX 1 0 O5 AX 1 1 0 O5 BX O5 CX O6 O5 XOR CY F7 A5Q F7 CY XOR AX O5 O6 F8 CY XOR BX O5 O6 O6 O5 XOR CY F8 B5Q SRUSEDMUX 1 F7 CY XOR CX O5 O6 CEUSEDMUX AMUX BMUX CMUX AQ A B CQ BQ O5 DX CY XOR DX O5 O6 D5Q CY XOR O5 O6 DMUX DQ C D COUT S0_IBUF D7_IBUF S1_IBUF D5_IBUF D4_IBUF D6_IBUF S2_IBUF S0_IBUF D3_IBUF S1_IBUF D1_IBUF D0_IBUF D2_IBUF MUXF7

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

マルチ プ レ ク サー

の一般的な構築ブ

ロ ッ ク

2

N以外のマルチ プ レ クサー用のセル

デザイ ン

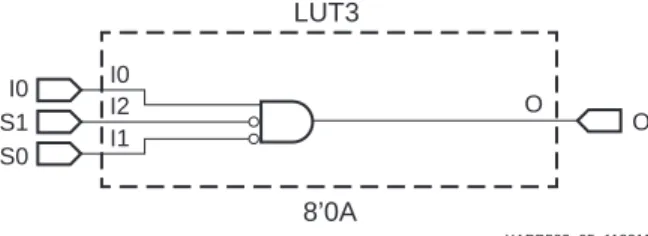

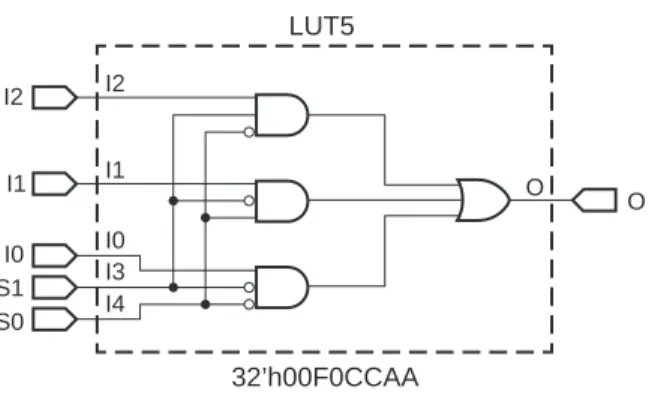

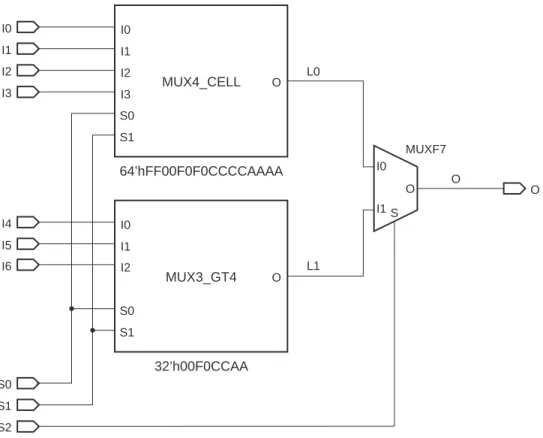

デー タ 配線 ロ ジ ッ ク では、 場合に よ っ ては 2N 以外のデー タ ソ ース を マルチプ レ ク スす る 必要があ り ま す。図3に示す ス ラ イ スベー ス の 8:1 マルチプ レ ク サーのマ ク ロ セルは別の構成セルを使用す る こ と で、 よ り 大規模ま たは小規模なサ イ ズ を イ ン プ リ メ ン ト で き ます。 こ のセ ク シ ョ ン では、2N が 8 ビ ッ ト よ り も 小 さ いマルチプ レ ク サーについて説明 し ます。2Nが 8 よ り も 大 き いマルチプ レ ク サーについ ては、「大規模マルチプ レ ク サー: 概要」 を参照 し て く だ さ い。 図5 ~図8 に、 こ れ ら のセルを示 し ます。2N > 4 のマルチプ レ ク サーでは、 セル MUX1_GT4 (図5) が 1 ビ ッ ト 拡張 さ れます。 こ れは、MUX4_CELL (図8) お よ び MUXF7 BEL と 共に使用 さ れます。 同様 に、図6 ではセル MUX2_GT4 が 2 ビ ッ ト の拡張を提供 し 、図7 ではセル MUX3_GT4 が 3 ビ ッ ト の 拡張を提供 し ます。 こ の ス タ イ ルのマルチプ レ ク サーの入力が 2N よ り も 少ない場合には、 ユーザーはセ レ ク ト 入力に入力 範囲を超え る 組み合わせがあ る 場合の動作を定義 し てお く 必要があ り ます。 た と えば、 セ レ ク ト ラ イ ン に 7 と い う 値があ る 場合の 5:1 マルチプ レ ク サーの出力を指定 し てお き ます。 通常、 デザ イ ンは動作中 に有効な入力か ら 値を選択 し ますが、 合成ツールは こ の状況におけ る 有効な値を判断で き ません。 し た がっ て、 ジ ェ ネ リ ッ ク HDL コ ー ド (例 : CASE 文) で こ の ス タ イ ルのマルチプ レ ク サーを推論す る か、 ま たはプ リ ミ テ ィ ブ を イ ン ス タ ン シエー ト す る な ど し て、セ レ ク ト ラ イ ンのすべての組み合わせに対す る 応答を定義す る 必要があ り ます (例 : VHDL の場合は 「when others」 、Verilog の場合は 「default」 な ど)。図5、図6、図7 では、 セ レ ク ト ラ イ ン の値が入力数 よ り も 大 き い場合に、 マルチプ レ ク サー出力が Low (0) にな る よ う に定義 さ れてい ます。最適なデザ イ ンでは、すべての未使用入力を Dont't Care (例 : 'X) と し て扱 う ため、S0 ま たは S1 を LUT へ配線す る 必要があ り ません。 た と えば、図9 に示す下位 の LUT で I4 入力が単に MUXF7 へ渡 さ れ る 場合は、4 ~ 7 ま での ど の よ う な組み合わせ (例 : 1xx) に 対 し て も こ の入力が選択 さ れます。

X-Ref Target - Figure 5

図 5 : N > 4 よ り 大規模なマルチ プ レ クサー用の 1 ビ ッ ト セル (MUX1_GT4)

X-Ref Target - Figure 6

図 6 : N > 4 よ り 大規模なマルチ プ レ ク サー用の 2 ビ ッ ト セル (MUX2_GT4) 8’0A I0 I2 I1 S0 O O LUT3 S1 I0 XAPP522_05_112211 16’00CA I1 I0 O I3 I2 I1 S0 O LUT4 S1 I0 XAPP522_06_112211

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

2

N以外のマルチ プ レ クサーの例

図5、図6、図7 に示 し た LUT ベース のセルを図8 に示 し た MUXF7 と 4:1 マルチプ レ ク サーを イ ン プ リ メ ン ト し た LUT を組み合わせて使用す る こ と で、5 ビ ッ ト (図9)、6 ビ ッ ト (図10)、 お よ び 7 ビ ッ ト 入力のマルチプ レ ク サー (図11) を構築で き ます。 図9の 5 ビ ッ ト マルチプ レ ク サーの例は、6ページ の図3 に示 し た 8 ビ ッ ト の例で使用 さ れて い る MUX4_CELL のいずれか一方を 1 ビ ッ ト の拡張セル MUX1_GT4 に置 き 換え た も のです。 同様に、6 ビ ッ ト (図10) と 7 ビ ッ ト (図11) マルチプ レ ク サーでは、2 ビ ッ ト と 3 ビ ッ ト の拡張セル (MUX2_GT4 お よ び MUX3_GT4) を それぞれ使用 し てい ます。 こ れ ら の ロ ジ ッ ク 回路は、図4で説明 し た ス ラ イ ス半分を使用す る イ ンプ リ メ ン テーシ ョ ン と ま っ た く 同 じ よ う に FPGA に イ ン プ リ メ ン ト さ れますが、 配線数は大幅に少な く な っ てい ます。LUT を プ ロ グ ラ ムす る ための INIT コー ド のエン コーデ ィ ン グは表2 と 類似 し てい ますが、 使用 さ れ る 入力やセ レ ク ト コ ー ド 数は減少 し ます。選択 さ れない場合には自動的に 0 を出力す る よ う 、各セル デザ イ ンは 2 ビ ッ ト セ レ ク ト を採用 し てい ます。 こ のセ ク シ ョ ンで説明す る 2N < 8 の小規模マルチプ レ ク サーは、ス イ ッ チン グ動作を ス ラ イ ス内で実行 す る 機能的な統合体 と し て含ま れ、 その方法は本質的に柔軟性に優れ、LUT ベース のセルデザ イ ン を 使用す る モジ ュ ール形式です。 高帯域幅デー タ パ ス には大規模マルチプ レ ク サーが必要 と な り 、 こ れに ついては 「大規模マルチプ レ ク サー: 概要」 で詳 し く 説明 し ます。X-Ref Target - Figure 7

図 7 : N > 4 よ り 大規模なマルチ プ レ クサー用の 3 ビ ッ ト セル (MUX3_GT4)

X-Ref Target - Figure 8

図 8 : N > 4 よ り 大規模なマルチ プ レ ク サー用の 4 ビ ッ ト セルまたはス タ ン ド ア ロ ン (MUX4_CELL) 32’h00F0CCAA I2 I1 I0 O I3 I4 I1 S0 O LUT5 I2 S1 I0 XAPP522_07_112211 64’FF00F0F0CCCCAAAA I2 I1 I0 O I4 I5 I3 I1 S0 O LUT6 I2 S1 I0 I3 XAPP522_08_112211

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

X-Ref Target - Figure 9

図 9 : セル MUX4_CELL および MUX1_GT4 を使用する 5 ビ ッ ト マルチ プ レ ク サー

X-Ref Target - Figure 10

XAPP522_09_112211 I0 I1 O S I0 I1 I2 I3 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I4 I0 S0 S1 O 8’h0A MUX1_GT4 L0 L1 MUXF7 O O S0 S1 S2 XAPP522_10 _112211 I0 I1 O S I0 I1 I2 I3 I0 I1 I5 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I4 I0 S0 S1 O 16’h00CA MUX2_GT4 L0 L1 MUXF7 O O S0 S1 S2

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

大規模マルチ プ レ クサー

:

概要

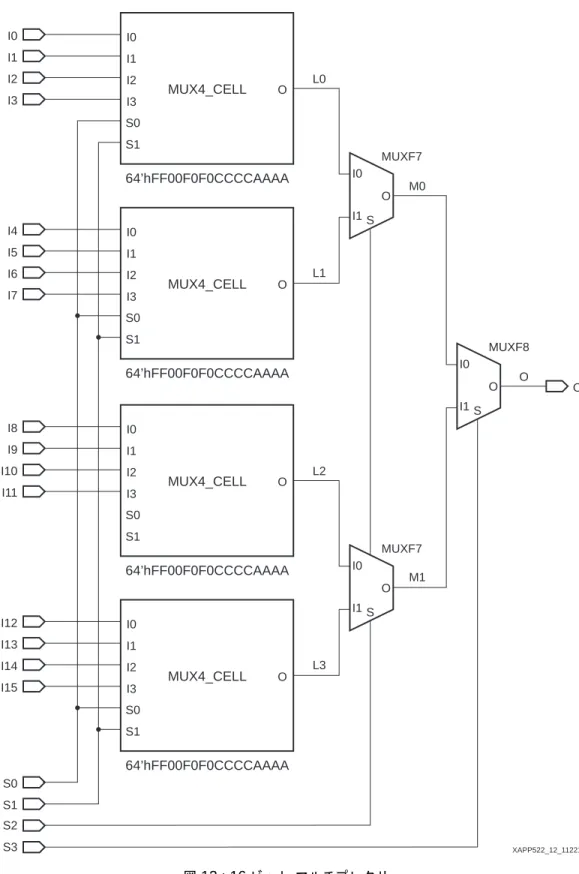

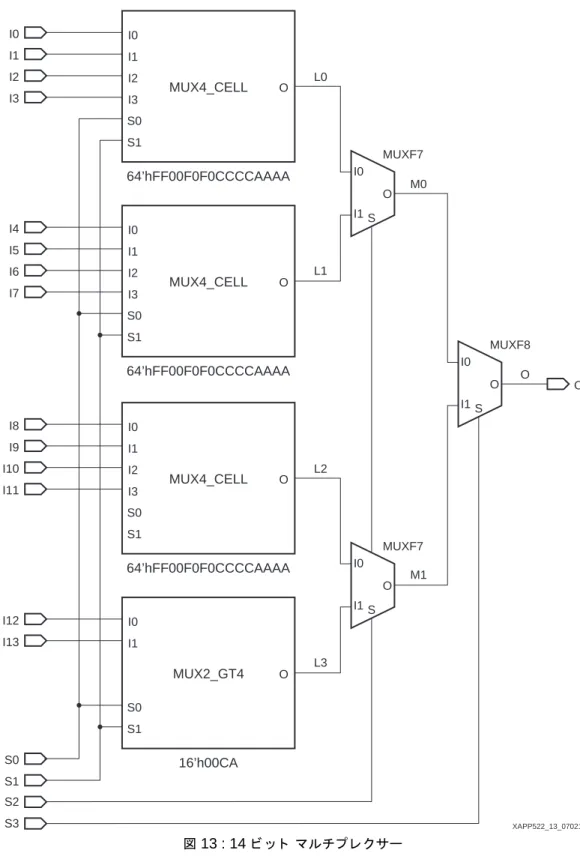

大規模マルチプ レ ク サーは、 さ ら にセルを追加 し て構成 し ま す。MUXF8 BEL を使用 し て6ページの 図3 に示す 8 ビ ッ ト マルチプ レ ク サーを 2 つ結合す る こ と で、1 つの ス ラ イ ス内に 16 ビ ッ ト のマルチ プ レ ク サーを構築で き ます。図12に、 こ の 16 ビ ッ ト マルチプ レ ク サーを示 し ます。3ページの図1の よ う に、MUXF8 のデー タ 入力は ス ラ イ ス内の 2 つの MUXF7 と 直接接続 さ れ、4 つすべての LUT6 を 使用す る 超高速の 4:1 マルチプ レ ク サーを構成 し ます。 こ の よ う な構成に よ り 、 ス ラ イ ス外の配線数を 削減で き ます。 つま り 、16 ビ ッ ト マルチプ レ ク サーでは、 入力か ら 出力へ配線数を 16:1 に圧縮で き ま す。 すべての入力は ス ラ イ ス に入っ て ス ラ イ ス か ら 出力 さ れ る ため、 汎用 イ ン タ ー コ ネ ク ト を追加で使 用す る 必要はあ り ません。 2N < 8 マルチプ レ ク サー と 同様に、16 マルチプ レ ク サーを使用 し て 2N < 16 のほかのバ リ エーシ ョ ン も 可能です。 た と えば、図13 の 14 ビ ッ ト マルチプ レ ク サーの例では、16 ビ ッ ト マルチプ レ ク サー (図12) の最上位ビ ッ ト 位置にあ る MUX4_CELL の代わ り に MUX2_GT4 セルを使用 し てい ます。 た だ し 、MUXF7 出力のみが MUXF8 入力へ接続で き 、MUXF7 入力は隣接配置 さ れた LUT 出力か ら 配 線す る 必要があ る こ と に注意 し て く だ さ い。 その結果、 た と え 9 入力のみの場合で も 、1 つの ス ラ イ ス で こ の タ イ プのマルチプ レ ク サーが構築 さ れます。 し たがっ て、 各ス ラ イ ス内に収ま る 8:1 マルチプ レ ク サーや 16:1 マルチプ レ ク サーの入力を最大限に活用で き る デザ イ ンが構築可能です。デザ イ ンに よ っ ては、ジ ェ ネ リ ッ ク HDL を使用 し て MUXF7 ま たは MUXF8 の出力へ配線 さ れてい る フ リ ッ プ フ ロ ッ プの位置にパ イ プ ラ イ ン レ ジ ス タ を挿入す る こ と で、 大規模マルチプ レ ク サーを分解で き ます。 「16 ビ ッ ト マルチプ レ ク サーの FPGA イ ンプ リ メ ン テーシ ョ ン」 では、図12 に示すマルチプ レ ク サー

を実現す る FPGA BEL の内部接続について説明 し ます。 通常、VHDL お よ び Verilog で CASE 文を使 用す る 場合、 すべての ス テー ト (例 : 必要に応 じ て 「when others」 ま たは 「default」 を使用) が定義 さ れてい る 限 り 、図12お よ び図13と 同 じ 回路が合成 さ れます。 プ リ ミ テ ィ ブ を イ ン ス タ ン シエー ト す る

X-Ref Target - Figure 11

図 11 : セル MUX4_CELL および MUX3_GT4 を使用する 7 ビ ッ ト マルチ プ レ クサー XAPP522_11_112211 I0 I1 O S I0 I1 I2 I3 I0 I1 I5 I1 I6 I2 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I4 I0 S0 S1 O 32’h00F0CCAA MUX3_GT4 L0 L1 MUXF7 O O S0 S1 S2

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

X-Ref Target - Figure 12

図 12 : 16 ビ ッ ト マルチ プ レ ク サー XAPP522_12_112211 I0 I1 O S I0 I1 I2 I3 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I4 I5 I6 I7 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L0 L1 MUXF7 S0 S1 S2 S3 I0 I1 O S I8 I9 I10 I11 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I12 I13 I14 I15 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L2 L3 MUXF7 I0 I1 O S M0 M1 MUXF8 O O

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

16

ビ ッ ト

マルチ プ レ クサーの

FPGA

イ ン プ リ メ ン テーシ ョ ン

図14に示す よ う に、16 ビ ッ ト マルチプ レ ク サーの FPGA イ ンプ リ メ ン テーシ ョ ンは、図12の ロ ジ ッ ク 構成 と ト ポ ロ ジ的に類似 し てい ま す。 つ ま り 、 ロ ジ ッ ク 図お よ び FPGA イ ン プ リ メ ン テーシ ョ ン の BEL 間は 1 対 1 です。4 つすべての LUT6 か ら MUXF7 お よ び MUXF8 を通過 し て最終的に出力 さ れ る ま での配線経路を緑色で表 し てい ます。

X-Ref Target - Figure 13

図 13 : 14 ビ ッ ト マルチ プ レ ク サー XAPP522_13_070212 I0 I1 O S I0 I1 I2 I3 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I4 I5 I6 I7 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L0 L1 MUXF7 S0 S1 S2 S3 I0 I1 O S I8 I9 I10 I11 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I12 I13 I0 I1 S0 S1 O 16’h00CA MUX2_GT4 L2 L3 MUXF7 I0 I1 O S M0 M1 MUXF8 O O

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

X-Ref Target - Figure 14

図 14 : FPGA SLICEL の 16 ビ ッ ト マルチ プ レ ク サー イ ン プ リ メ ン テーシ ョ ン Y_OBUF 1 0 1 0 CLK CLK_B C2 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 A1 AX BX CE A4 A2 A3 A5 CLK A6 B1 B2 B3 B4 B5 B6 SR CX C1 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 C4 C5 C3 C6 D2 D1 D3 DX D4 D5 D6 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 INIT0 INIT1 CK CE D SR DI0 S0 DI1 S1 DI2 S2 DI3 S3 O0 CO0 O1 CO1 O2 CO2 O3 CO3 CYINIT CIN CARRY4 INIT0 INIT1 SRHIGH SRLOW SRHIGH SRLOW CK CE D SR LATCH FF OR2L AND2L CK CE D SR SRHIGH SRLOW CK CE D SR LATCH FF OR2L AND2L CK CE D Q SR SRHIGH SRLOW SYNC ASYNC RESET TYPE SRHIGH SRLOW CK CE DQ SR XAPP522_14_081012 LATCH FF OR2L AND2L INIT0 INIT1 INIT0 INIT1 INIT0 INIT1 SRHIGH SRLOW INIT0 INIT1 INIT0 INIT1 CK CE D SR LATCH FF OR2L AND2L SRHIGH SRLOW INIT0 INIT1 CK CE D Q Q Q Q Q Q Q SR SRHIGH SRLOW O6 O5 XOR CY F7 C5Q CIN AX 1 0 O5 AX 1 1 0 O5 BX O5 CX O6 O5 XOR CY F7 A5Q F7 CY XOR AX O5 O6 F8 CY XOR BX O5 O6 O6 O5 XOR CY F8 B5Q SRUSEDMUX 1 F7 CY XOR CX O5 O6 CEUSEDMUX AMUX BMUX CMUX AQ A B CQ BQ O5 DX CY XOR DX O5 O6 D5Q CY XOR O5 O6 DMUX DQ C D COUT S0_IBUF D7_IBUF S1_IBUF D5_IBUF D4_IBUF D6_IBUF S0_IBUF D3_IBUF S1_IBUF D1_IBUF D0_IBUF D2_IBUF S0_IBUF D15_IBUF S1_IBUF D13_IBUF D12_IBUF D14_IBUF S2_IBUF S0_IBUF D11_IBUF S1_IBUF D9_IBUF D8_IBUF D10_IBUF Y_OBUF S3_IBUF S2_IBUF MUXF7 MUXF8 MUXF7

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

64

ビ ッ ト 以上のマルチ プ レ クサー

2Nが 16 ビ ッ ト (1 つの ス ラ イ ス で対応可) を超え る 場合は、 ス ラ イ ス を追加す る 必要があ り ます。 こ れ については、図15 に示す 64:1 マルチプ レ ク サーを使用 し て説明で き ます。1 つの LUT へ ロ ジ ッ ク を 接続す る には、4 つの ス ラ イ ス か ら の 4 本の配線のみ必要です。 入力か ら 出力へのパス のみ 2 つの LUT を通過 し ます。MUXF7/MUXF8 の遅延は配線に比べ る と わずかです。 こ の効率的な イ ンプ リ メ ン テー シ ョ ンの鍵 と な る のは、64:1 マルチプ レ ク サーが 4 つの 16:1 マルチプ レ ク サーに分解 さ れてお り 、 そ れ ら の後に 4:1 マルチプ レ ク サーがあ る こ と です。プ リ ミ テ ィ ブ を イ ン ス タ ン シエー ト す る と 、図15 と ま っ た く 同 じ よ う に イ ンプ リ メ ン ト さ れます。 ジ ェ ネ リ ッ ク HDL で CASE 文を 1 つ使用 し て 64:1 マ ルチプ レ ク サーを推論 し た場合で も 同 じ 構造 と な り ますが、 効率性に劣 る 別の構造が推論 さ れ る可能性 も あ り ます。 大規模マルチプ レ ク サーが適切に分解 さ れ、 複数の CASE 文で記述 さ れてい る 場合には、 ジ ェ ネ リ ッ ク コ ー ド で も 充分です。 ただ し 、 通常は合成ツールに よ っ てすべてが再びマージ さ れ る こ と を回避す る ために、 各ス テージにパ イ プ ラ イ ン を挿入ま たは属性を適用す る 必要があ り ます。 2N = 8 お よ び 2N = 16 マルチプ レ ク サーの よ う に、9ページの図5 ~ 10ページの図8 のセルを使用す る こ と で、図15をベース と し た 2N < 64 マルチプ レ ク サーの ロ ジ ッ ク バ リ エーシ ョ ンが可能です。 こ の手法ではビ ッ ト 幅を拡張で き ます。図16 に実際の例を示 し ます。 こ の図では、図15 の 64 ビ ッ ト マ ルチプ レ ク サーを 72 イ ン ス タ ン ス使用 し て統合 し 、72x64 ビ ッ ト (4608:72) マルチプ レ ク サーを構築 し てい ます。 こ の ロ ジ ッ ク は、100G ネ ッ ト ワ ー ク アプ リ ケーシ ョ ンで 64 個のブ ロ ッ ク RAM か ら の 64 ビ ッ ト お よ び 8 ビ ッ ト ECC デー タ を配線す る 場合に使用で き ます。 図15 の 64:1 マルチプ レ ク サーには 4¼ 個の ス ラ イ ス が必要で、 各 16:1 マルチプ レ ク サーに 1 個の ス ラ イ ス を使用 し 、組み合わせ る 4:1 マルチプ レ ク サーには LUT を 1 つ使用 し ます。図16の よ う に 64:1 マルチプ レ ク サーを 72 回複製す る には 306 個の ス ラ イ ス が必要です。 こ れ ら の 4:1 マルチプ レ ク サー の イ ンプ リ メ ン ト に使用 さ れ る LUT は 18 個の ス ラ イ ス に含め る こ と がで き ますが、実際には配線の長 さ 限 り 短 く す る ため、 こ の と お り にな ら ない こ と も 考え ら れます。マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

X-Ref Target - Figure 15

図 15 : 64 ビ ッ ト マルチ プ レ ク サー XAPP522_15_081012 I0 I1 O S I0 I1 I2 I3 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I4 I5 I6 I7 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L0 L1 MUXF7 S0 S1 S2 S3 S4 S5 I0 I1 O S I8 I9 I10 I11 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I12 I13 I14 I15 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L2 L3 MUXF7 I0 I1 O S M0 M1 MUXF8 N0 I0 I1 O S I16 I17 I18 I19 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I20 I21 I22 I23 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L4 L5 MUXF7 I0 I1 O S I24 I25 I26 I27 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I28 I29 I30 I31 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L6 L7 MUXF7 I0 I1 O S M2 M3 MUXF8 N1 I0 I1 O S I32 I33 I34 I35 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I36 I37 I38 I39 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L8 L9 MUXF7 I0 I1 O S I40 I41 I42 I43 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I44 I45 I46 I47 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L10 L11 MUXF7 I0 I1 O S M4 M5 MUXF8 N2 I0 I1 O S I48 I49 I50 I51 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I52 I53 I54 I55 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L12 L13 MUXF7 I0 I1 O S I56 I57 I58 I59 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL I60 I61 I62 I63 I0 I1 I2 I3 S0 S1 O 64’hFF00F0F0CCCCAAAA MUX4_CELL L14 L15 MUXF7 I0 I1 O S M6 M7 MUXF8 N3 I0 I1 I2 I3 S0 S1 O O 64’hFF00F0F0CCCCAAAA MUX4_CELL O

マルチ プ レ ク サーの一般的な構築ブ ロ ッ ク

X-Ref Target - Figure 16

図 16 : 72 x 64 ビ ッ ト マルチ プ レ クサー (72 個の MUX64 イ ン ス タ ン ス を使用) INPUTS (4608-bits) 218 in bits select 218 out bits 219 in bits select 219 out bits 220 in bits select 220 out bits 221 in bits select 221 out bits 222 in bits select 222 out bits 223 in bits select 223 out bits 224 in bits select 224 out bits 225 in bits select 225 out bits 226 in bits select 226 out bits 227 in bits select 227 out bits 228 in bits select 228 out bits 229 in bits select 229 out bits 230 in bits select 230 out bits 231 in bits select 231 out bits 232 in bits select 232 out bits 233 in bits select 233 out bits 234 in bits select 234 out bits 235 in bits select 235 out bits 236 in bits select 236 out bits 237 in bits select 237 out bits 238 in bits select 238 out bits 239 in bits select 239 out bits 240 in bits select 240 out bits 241in bits select 241 out bits 242 in bits select 242 out bits 243 in bits select 243 out bits 244 in bits select 244 out bits 245 in bits select 245 out bits 246 in bits select 246 out bits 247 in bits select 247 out bits 248 in bits select 248 out bits 249 in bits select 249 out bits 250 in bits select 250 out bits 251 in bits select 251 out bits 252 in bits select 252 out bits 253 in bits select 253 out bits 20 in bits select 20 out bits 21 in bits select 21 out bits 22 in bits select 22 out bits 23 in bits select 23 out bits 24 in bits select 24 out bits 25 in bits select 25 out bits 26 in bits select 26 out bits 27 in bits select 27 out bits 28 in bits select 28 out bits 29 in bits select 29 out bits 210 in bits select 210 out bits 211 in bits select 211 out bits 212 in bits select 212 out bits 213 in bits select 213 out bits 214 in bits select 214 out bits 215 in bits select 215 out bits 216 in bits select 216 out bits 217 in bits select 217 out bits 254 in bits select 254 out bits 255 in bits select 255 out bits 256 in bits select 256 out bits 257 in bits select 257 out bits 258 in bits select 258 out bits 259 in bits select 259 out bits 260 in bits select 260 out bits 261 in bits select 261 out bits 262 in bits select 262 out bits 263 in bits select 263 out bits 264 in bits select 264 out bits 265 in bits select 265 out bits 266 in bits select 266 out bits 267 in bits select 267 out bits 268 in bits select 268 out bits 269 in bits select 269 out bits 270 in bits select 270 out bits 271 in bits select 271 out bits SELECTS (6-bits) OUTPUTS (72-bits) XAPP522_16_081112 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 MUX64 I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O I0-I63 S0-S5 O

別手段 と し てのデー タ セ レ ク タ ー

別手段 と し ての

デー タ

セ レ ク タ ー

2

Nマルチ プ レ クサーの代替

: 1-of-N

デー タ

セ レ ク タ ー

一部のシ ス テ ム アプ リ ケーシ ョ ン では、 デー タ セ レ ク ト 信号を生成す る 制御 ロ ジ ッ ク がバ イ ナ リ エン コ ーデ ィ ン グ機能を提供 し ないため、 バ イ ナ リ エ ン コ ーデ ィ ン グ用に ロ ジ ッ ク を追加す る 必要があ り 、 こ の よ う な場合にはデー タ パ ス が低速化 し ます。 例 と し て、BRAM メ モ リ な ど複数のパ ラ レル デー タ レーン があ る 場合な ど が挙げ ら れ、 1 つの レーン上のデー タ に特定のエ ン コ ーデ ィ ン グがあ り 、 全レー ン上のデー タ 集合体が ど の よ う に順序付け ら れ る べ き か を示 し ま す。 エ ン コ ーデ ィ ン グ パ タ ーン のパ タ ーン検出 ロ ジ ッ ク は、 プ ラ イ オ リ テ ィ エン コ ーデ ィ ン グ と 類似 し てお り 、1-of-N 信号を生成 し 、N ラ イ ン中の 1 つの制御 ラ イ ンに よ っ て配線 さ れ る デー タ が選択 さ れます。 こ のセ レ ク ト 制御は、 常に 1 つ のセ レ ク ト ラ イ ンのみア ク テ ィ ブ (High) にな る ワ ン ホ ッ ト エン コー ド と し て も 記述で き ます。ただ し 、 プ ラ イ オ リ テ ィ エン コ ーダーでは、選択 し たデー タ に対 し て最優先順位が割 り 当て ら れたセ レ ク ト ラ イ ンがあ る と 、2 つ以上のセ レ ク ト ラ イ ンが同時にア ク テ ィ ブにな り ます。 図18 に、1-of-12 デー タ セ レ ク タ ーの効率的な イ ンプ リ メ ン テーシ ョ ン を示 し ます。 こ れは、1 つの ス ラ イ ス に イ ンプ リ メ ン ト 可能な最大規模のデー タ セ レ ク タ ーです。 反転出力付 き の 1-of-3 デー タ セ レ ク タ ーを イ ン プ リ メ ン ト す る よ う 各 LUT を プ ロ グ ラ ム し ます。 こ の場合、 セ レ ク ト 制御は ワ ン ホ ッ ト と し て扱われますが、 同時に 2 つ以上のセ レ ク ト 入力がア ク テ ィ ブ (High) にな る 場合に必要な動作 (優 先順位) を与え る よ う に LUT を プ ロ グ ラ ム で き ます。 セ レ ク ト 制御の 1 つが High の場合、LUT の出 力は該当す る デー タ 入力の反転 ロ ジ ッ ク レベル と な り ま すが、3 つすべてのセ レ ク ト 制御信号が Low の場合には、LUT の出力が強制的に High と な り ます。 こ れは 1-of-3 デー タ セ レ ク タ ーでは予期 し な い動作 と し て現れますが、 CARRY4 ブ ロ ッ ク 内の MUXCY エ レ メ ン ト お よ び専用キ ャ リ ー チ ェーン で 構築 さ れた組み合わせ段階では問題 と な り ます。各 LUT か ら の出力がそれぞれの MUXCY のセ レ ク ト 入力を制御 し ます。DI 入力は永久的に High (1) 駆動 さ れ、 チ ェ ーン の一番下 (開始点) にあ る CI 入力は永久的に Low (0) 駆動 さ れ ます。 こ の配置は、 4 入力の NAND ゲー ト と し て キ ャ リ ーチ ェーン を構成 し ます。S 入力のいずれかが Low の場合は 1 が

選択 さ れ、 キ ャ リ ーチ ェ ーンの一番上の出力ま で渡 さ れ ます。S 入力がすべて High の場合はすべての MUXCY がそれぞれの CI 入力を選択 し 、 一番下の 0 がチ ェーンの一番上の出力ま で伝搬 さ れます。

セ レ ク ト 信号 S4 のみが ア ク テ ィ ブ (High) の場合におけ る 1-of-12 デー タ セ レ ク タ ーの動作につい て考え てみ ま す。LUTA の出力は High で、 一番下の MUXCY では 0 を選択 し て次のチ ェ ーンへ と

伝搬 し ま す。S4 は ア ク テ ィ ブで あ る た め、LUTB の出力は D4 デー タ 入力に現れ る レ ベルの反転 と な り ま す。 し たが っ て、D4 が Low の と き は LUTB の出力は High と な り 、 関連す る MUXCY では CI が選択 さ れ、 引 き 続 き 0が キ ャ リ ーチ ェ ー ン で伝搬 さ れ ま す。 反対に、D4 が High の と き には LUTB 出力が Low と な り 、MUXCY では DI が選択 さ れ る ため、 キ ャ リ ーチ ェ ーン で 1 が伝搬 さ れ

ま す。 つ ま り 、 キ ャ リ ーチ ェ ーン で伝搬 さ れ る ロ ジ ッ ク レ ベルは、D4 入力に適用 さ れ る ロ ジ ッ ク レ ベル を示 し ま す。LUTC と LUTD の出力が共に High の場合は、 こ の レ ベルがチ ェ ーン の一番上の出 力 ま で伝搬 さ れ ま す。

別手段 と し てのデー タ セ レ ク タ ー

デー タ

セ レ ク タ ーの拡張

こ のセ ク シ ョ ン で説明す る デー タ セ レ ク タ ーは、 ス ラ イ ス を垂直にカ ス ケー ド 接続 し て拡張で き ます。 入力 と 出力の間に配線は追加 さ れません。 構築可能な最大サ イ ズは、 タ ーゲ ッ ト FPGA の垂直カ ラ ムの 高 さ に よ っ て異な り ます。 ス ラ イ ス間のキ ャ リ ーチ ェーンは非常に高速であ る ため、大規模なデー タ セ レ ク タ ーで生 じ る 遅延追加はほ と ん ど あ り ません (図17 参照)。1-of-N

デー タ

セ レ ク タ ー と

2

Nマルチ プ レ クサーの ト レー ド オ フ

1-of-N デー タ セ レ ク タ ー と 2Nマルチプ レ ク サーの ト レー ド オ フ の 1 つは、 信号速度 と 集積度です。 た と えば、2N が 16 以上のマルチプ レ ク サーは、 配線を追加 し て LUT を も う 1 つ通過す る 必要があ る た めデー タ セ レ ク タ ー よ り も 低速です。 デー タ セ レ ク タ ーはいかな る サ イ ズの場合で も 配線を追加す る 必要がな く 、1 つの LUT を通過す る だけです。 その一方で、 集積度の点ではデー タ セ レ ク タ ーが劣 り ます。1-of-N ソ リ ュ ーシ ョ ンは、 各ス ラ イ ス に最大 12 ビ ッ ト し か含め る こ と がで き ませんが、2Nマル チプ レ ク サーは各ス ラ イ ス に最大 16 ビ ッ ト を含め る こ と がで き ます。 1-of-N を確実に イ ンプ リ メ ン ト す る 唯一の方法は、 プ リ ミ テ ィ ブ を イ ン ス タ ン シエー ト す る こ と です。 1-of-N の性質上、 デザ イ ンに適用す る ま でには多少時間がかか り ますが、 通常は利点を伴 う ため検討す る 価値はあ り ます。 特に、 プ ラ イ オ リ テ ィ エン コ ーデ ィ ン グ を有効にす る よ う に 1-of-N を構成 し た場 合に優れた利点を も た ら し ます。 必要な フ ァ ン ク シ ョ ン を構築す る よ う 各 LUT を プ ロ グ ラ ム し 、 最終 出力に一番近いチ ェーンの最上位が優先 さ れ る よ う に し ます。X-Ref Target - Figure 17

図 17 : 1-of-N デー タ セ レ ク タ ーの拡張 Slice X1Y1 COUT COUT CIN CIN Slice X0Y1 CLB Slice X1Y0 COUT COUT Slice X0Y0 CLB Slice X3Y1 COUT COUT CIN CIN Slice X2Y1 CLB Slice X3Y0 COUT COUT Slice X2Y0 CLB XAPP522_17_070812

別手段 と し てのデー タ セ レ ク タ ー

N=12

の

1-of-N

デー タ

セ レ ク タ ーの

FPGA

イ ン プ リ メ ン テーシ ョ ン

図19に、図18のデー タ セ レ ク タ ーの FPGA イ ンプ リ メ ン テーシ ョ ン を示 し ます。 適切な配線経路を 緑色で表 し てい ます。

ロ ジ ッ ク 図に表 し た LUT ベー ス のセルお よ び CARRY4 ブ ロ ッ ク 内の BEL は、 ト ポ ロ ジ的に実際の

X-Ref Target - Figure 18

図 18 : 8 ビ ッ ト の 1-of-N デー タセ レ ク タ ー DI CI S O O LUTD C2 C1 C0 MUXCY 64’h0000000F003355FF O6 DI CI S O LUTC MUXCY 64’h0000000F003355FF DI CI S O LUTB MUXCY 64’h0000000F003355FF I5 S9 D11 S11 S10 D10 D9 “1” “0” “1” “1” “1” I4 I3 I2 O6 DI CI S O I1 I0 I5 S6 D8 S8 S7 D7 D6 I4 I3 I2 O6 I1 I0 I5 S3 D5 S5 S4 D4 D3 I4 I3 I2 I1 I0 O6 I5 S0 D2 S2 S1 D1 D0 I4 I3 I2 I1 I0 LUTA MUXCY 64’h0000000F003355FF XAPP522_18_071012

別手段 と し てのデー タ セ レ ク タ ー

X-Ref Target - Figure 19

図 19 : 12 ビ ッ ト の 1-of-N デー タ セ レ ク タ ーの FPGA イ ン プ リ メ ン テーシ ョ ン 1 0 1 0 CLK CLK_B C2 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 A1 AX BX CE A4 A2 A3 A5 CLK A6 B1 B2 B3 B4 B5 B6 SR CX C1 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 A1 A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 C4 C5 C3 C6 D2 D1 D3 DX D4 D5 D6 S2_IBUF S1_IBUF S0_IBUF D2_IBUF D1_IBUF D0_IBUF A1A2 A3 A4 A5 A6 O6 A1 A2 A3 A4 A5 O5 INIT0 INIT1 CK CE D SR DI0 S0 DI1 S1 DI2 S2 DI3 S3 O0 CO0 O1 CO1 O2 CO2 O3 CO3 CYINIT CIN CARRY4 INIT0 INIT1 SRHIGH SRLOW SRHIGH SRLOW CK CE D SR LATCH FF OR2L AND2L CK CE D SR SRHIGH SRLOW CK CE D SR LATCH FF OR2L AND2L CK CE D Q SR SRHIGH SRLOW SYNC ASYNC RESET TYPE SRHIGH SRLOW CK CE DQ SR XAPP522_19_072312 LATCH FF OR2L AND2L INIT0 INIT1 INIT0 INIT1 INIT0 INIT1 SRHIGH SRLOW INIT0 INIT1 INIT0 INIT1 CK CE D SR LATCH FF OR2L AND2L SRHIGH SRLOW INIT0 INIT1 CK CE D Q Q Q Q Q Q Q SR SRHIGH SRLOW O6 O5 XOR CY F7 C5Q CIN AX 1 0 O5 AX 1 1 0 O5 BX O5 CX O6 O5 XOR CY F7 A5Q F7 CY XOR AX O5 O6 F8 CY XOR BX O5 O6 O6 O5 XOR CY F8 B5Q SRUSEDMUX 1 F7 CY XOR CX O5 O6 CEUSEDMUX AMUX BMUX CMUX AQ A B CQ BQ O5 DX CY XOR DX O5 O6 D5Q CY XOR O5 O6 DMUX DQ C D COUT GLOBAL_LOGIC1 GLOBAL_LOGIC1 GLOBAL_LOGIC1 GLOBAL_LOGIC1 O_OBUF S5_IBUF S4_IBUF S3_IBUF D5_IBUF D4_IBUF D3_IBUF S8_IBUF S7_IBUF S6_IBUF D8_IBUF D7_IBUF D6_IBUF S11_IBUF S10_IBUF S9_IBUF D11_IBUF D10_IBUF D9_IBUF

一般的な設計手順

一般的な設計手順

実行内容

:

ス イ ッ チ ング動作の位置、 フ ァ ン イ ン圧縮の最大化

3ページの図1 に示 し た各ス ラ イ ス には最大 29 個 (24 個ではない) の同時入力を含め る こ と がで き ます

(4 つの LUT の 24 入力、AX、BX、CX、DX、CIN、 お よ び ロ ーカ ル 0/1)。CARRY4 ブ ロ ッ ク 内の キ ャ リ ー チ ェ ーン を使用 し た場合、付加的な ロ ジ ッ ク ス イ ッ チン グは LUT6 リ ソ ース の直後に高速で 動作で き る ため、 同時入力の効果が増大 し ます。 基本的な概念は、 シ ン グル ラ ン ク 内で よ り 多 く の ロ ジ ッ ク を実行、 つま り ス ラ イ ス を最大限に活用す る こ と です。 シ ン グル ラ ン ク で よ り 多 く の ロ ジ ッ ク ス イ ッ チン グ を行 う こ と に よ り 、LUT 総数の削減、 LUT 遅延の削減、 お よ び ロ ジ ッ ク フ ァ ン イ ンの圧縮が可能にな り ます。 デー タ パ ス の ロ ジ ッ ク フ ァ ン ク シ ョ ン結果を判断す る ための ス イ ッ チ ン グ動作を 1 つの ス ラ イ ス 内に で き る だけ多 く 含め る こ と で、外部配線 リ ソ ース を節約で き ます。結果 と し て、 よ り 多 く の汎用 イ ン タ ー コ ネ ク ト をデー タ や制御用に確保で き ます。 ス ラ イ ス内の イ ン タ ー コ ネ ク ト お よ び CARRY4 内の ロ ー カル キ ャ リ ーチ ェ ーンは非常に高速です。 基幹 と な る こ れ ら の ス ラ イ ス リ ソ ース が汎用 イ ン タ ー コ ネ ク ト と 競合す る こ と はあ り ません。

方法

:

ス ト ラ ク チ ャ

HDL

形式で

BEL

を記述 し 、 よ り 大規模なデザイ ン を構築

ビヘ イ ビ ア HDL を入力 と す る 合成ツールでは、こ のアプ リ ケーシ ョ ン ノ ー ト で説明す る すべてのデー タ 配線 ロ ジ ッ ク フ ァ ン ク シ ョ ンは推論で き ま せん。1 つには、CARRY4 ブ ロ ッ ク の BEL の目的は名 目上、 演算機能を高速化す る ためであ り 、 こ れは HDL コ ー ド に演算子で記述 さ れ ま す。 し たが っ て、 たいていの場合は高速化のために算術演算子の イ ン プ リ メ ン テーシ ョ ン が優先 さ れ ます。HDL で記述 さ れたデー タ 配線演算子は非常に少ないため、 その よ う な フ ァ ン ク シ ョ ンは BEL に推論 さ れに く いの が現実です。 ま た、 デー タ 配線は空間的広が り を持つ傾向があ る ため (速度 も 重要ではあ り ますが)、 構 造的な入力が よ り 優先 さ れ ま す。 こ の複雑な状況の対処方法は、 ス ト ラ ク チ ャ HDL を使用 し て必要な フ ァ ン ク シ ョ ン を直接指定す る こ と です。 こ のアプ リ ケーシ ョ ン ノ ー ト で説明 し た と お り 、 必要な BEL で構成 さ れたセルデザ イ ン を作 成 し 、 それを柔軟に活用 し ます。 セル デザ イ ン を マ ク ロ セルに統合 し 、 ユーザー ロ ジ ッ ク の イ ン ス タ ン ス にビ ッ ト ス ラ イ ス と し て利用で き ます。 こ の手順は、図20の③と な り ます。 こ のアプ リ ケーシ ョ ン ノ ー ト に示す例では、 すべて HDL 形式で記述 さ れてい ます (「 リ フ ァ レ ン スデザ イ ン」参照)。 複数 ビ ッ ト ス ラ イ ス を結合す る 手順④は、 ス ト ラ ク チ ャ HDL 形式で記述 さ れた イ ン ス タ ン ス を使用、 あ る いは generate 文を使用 し て実行で き ます。X-Ref Target - Figure 20

図 20 : 一般的な設計手順 Determine Slice Resources that Assist in Problem Design Bitslice Cells Using Slice BELs XAPP522_20_071012 Implement Bitslices in Structural HDL Aggregate Bitslices in HDL

1

2

3

4

リ フ ァ レ ン スデザイ ン

リ フ ァ レ ン ス

デザイ ン

リ フ ァ レ ン ス デザ イ ン フ ァ イ ルは、 次のサ イ ト か ら ダ ウ ン ロ ー ド で き ます。 https://secure.xilinx.com/webreg/clickthrough.do?cid=191148 表3 に、 リ フ ァ レ ン ス デザ イ ンの詳細を示 し ます。ま と め

こ のアプ リ ケーシ ョ ン ノ ー ト では、 ス ラ イ ス内の BEL を直接使用 し て よ り 多 く の ス イ ッ チン グ動作を 行 う こ と で、 多 く の汎用配線 リ ソ ース が節約 さ れ、 高速化が可能 と な る だけでな く 、 結果の確定性を向 上 さ せる こ と がで き る こ と を説明 し て き ま し た。 ス ト ラ ク チ ャ HDL で BEL を指定す る こ と に よ り 、 ス ラ イ スへ直接ア ク セ ス で き る よ う にな り ます。 ビ ッ ト 数を多 く 含むデー タ パス重視のシ ス テ ム デザ イ ン では、 単に ビヘ イ ビ ア HDL 形式で指定 し た ロ ジ ッ ク で得 る 効果 よ り も 、 こ れ ら の手法を使用 し た場合 の方が効果的な イ ンプ リ メ ン テーシ ョ ンが実現で き ます。 表 3 : リ フ ァ レ ン スデザイ ンの詳細 パ ラ メ ー タ ー 説明 全般 開発者 Ken Chapman タ ーゲ ッ ト デバ イ ス (ス テ ッ ピ ン グ レベル、ES、 プ ロ ダ ク シ ョ ン、 ス ピー ド グ レー ド) プ ロ ダ ク シ ョ ンの Spartan-6 FPGA、 FPGA、 お よ び 7 シ リ ーズFPGA ソ ース コ ー ド の提供 あ り ソ ース コ ー ド の形式 VHDL お よ び Verilog 既存のザ イ リ ン ク ス アプ リ ケーシ ョ ン ノ ー ト/リ フ ァ レ ン ス デザ イ ン、CORE Generator ツール、サー ド パー テ ィ か ら デザ イ ンへの コ ー ド/IP の使用 な し シ ミ ュ レーシ ョ ン 機能シ ミ ュ レーシ ョ ンの実施 あ り タ イ ミ ン グシ ミ ュ レーシ ョ ンの実施 な し 機能お よ び タ イ ミ ン グ シ ミ ュ レーシ ョ ンでのテ ス ト ベ ンチの利用 あ り テ ス ト ベンチの形式 VHDL 使用 し た シ ミ ュ レー タ ソ フ ト ウ ェ ア/バージ ョ ン ISim v14.1 SPICE/IBIS シ ミ ュ レーシ ョ ンの実施 N/A イ ンプ リ メ ン テーシ ョ ン 使用 し た合成 ソ フ ト ウ ェ ア ツール/バージ ョ ン XST v14.1 お よ びVivado Design Suite 2012.1 使用 し た イ ン プ リ メ ン テーシ ョ ン ソ フ ト ウ ェ ア ツ ー

ル/バージ ョ ン

ISE Design Suite v14.1 お よ び ISE Design Suite 2012.1 ス タ テ ィ ッ ク タ イ ミ ン グ解析の実施 あ り

ハー ド ウ ェ ア検証

ハー ド ウ ェ ア検証の実施 あ り

改訂履歴

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。Notice of

Disclaimer

The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products.To the maximum extent permitted by applicable law:(1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications.You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent.Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx.Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:http://www.xilinx.com/warranty.htm#critapps.

Automotive

Applications

Disclaimer

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO:(I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY.CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

本資料は英語版 (v1.1) を翻訳し た も ので、 内容に相違が生じ る場合には原文を優先し ます。 資料によ っては英語版の更新に対応し ていない も のがあ り ます。 日本語版は参考用 と し てご使用の上、 最新情報につき ま し ては、 必ず最新英語版をご参照 く だ さ い。 こ の資料に関する フ ィ ー ド バ ッ クおよび リ ン ク などの問題につき ま し ては、jpn_trans_feedback@xilinx.com までお知らせ く だ さ い。 いただき ま し たご意見を参考に早急に対応させていただき ます。 なお、 こ の メ ール ア ド レ スへのお問い合わせは受け付けてお り ません。 あ ら か じめご了承 く だ さ い。 日付 バージ ョ ン 内容 2012 年 8 月 8 日 1.0 初版 リ リ ース 2012 年 8 月 30 日 1.1 「FPGA ス ラ イ ス の構築ブ ロ ッ ク : 内部 を 見 る 」 の内容 を 変更。 「FPGA SLICEL に構築 さ れ る 8 ビ ッ ト マルチプ レ ク サー」の表題 を変更。図1、図4、 お よ び図14 の タ イ ト ルを変更 し 、 表示項目 を追加。図14 の MUXF7 と MUXF8 間の MUX 信号を緑色でハ イ ラ イ ト 。図15 お よ び図16 の表示を変更。

補足資料 A : LUT コ ー ド の生成方法

補足資料

A :

LUT

コ ー ド の生成方法

LUT

を使用する イ ン プ リ メ ン テーシ ョ ン

3ページの図1 に、FPGA SLICEL ブ ロ ッ ク 図の中にあ る LUT を示 し てい ます。SLICEM では メ モ リ

エ レ メ ン ト と し て LUT を使用で き ますが、ロ ジ ッ ク 機能 と し て LUT をプ ロ グ ラ ムす る と い う 目的でい う と 、 実際の SLICEM は SLICEL と 基本的に同 じ です。 ス ラ イ ス LUT は、FPGA デバ イ ス 内のプ ロ グ ラ マブル ロ ジ ッ ク 機能を結合す る 役割を果たすため、 シ ス テ ムデザ イ ン を構築す る 上で必要な機能 を実現 さ せ る ための重要な要素です。 リ フ ァ レ ン ス デザ イ ンの よ う に、LUT は HDL で記述 し た 16 進 数の初期化 コ ー ド を用いて構成で き ます ( 「 リ フ ァ レ ン スデザ イ ン」 参照)。 こ れ ら の コ ー ド は、 与え ら れた入力セ ッ ト に対 し て特定の ロ ジ ッ ク 出力を提供す る よ う に LUT を プ ロ グ ラ ム し ます。 ビヘ イ ビ ア HDL 合成を実行す る と 、 コ ー ド を直接入力 し な く て も 自動的に コ ン フ ィ ギ ュ レーシ ョ ン さ れます (合成 で実行 さ れ る)。 ただ し 、 デー タ パ ス関連機能用に特定の フ ァ ン ク シ ョ ン を構築す る 場合は、LUT コ ー ド を直接ユーザーが作成可能です。

4:1

マルチ プ レ クサーの例

図21に、 ゲー ト プ リ ミ テ ィ ブ付 き 4:1 マルチプ レ ク サーの ロ ジ ッ ク を示 し ます。LUT は実際には こ こ に示す よ う なゲー ト を イ ンプ リ メ ン ト し ません。代わ り に LUT の柔軟性を利用 し 、6 つの入力 (S0、S1、 お よ び I0 ~ I3) を持つフ ァ ン ク シ ョ ン の出力 O を生成 し ます。LUT6 では、 任意のゲー ト 制御が可能 です (最大 6 入力)。6 入力信号で最大 26 通 り の ロ ジ ッ ク フ ァ ン ク シ ョ ンが実現可能であ り 、 こ のマル チプ レ ク サーは LUT6 をすべて活用 し てい ます。表4に、6 つの入力 と その出力の関係を真理値表に示 し ます。 表4に、図21の 4:1 マルチプ レ ク サーの真理値表を示 し ます。LUT の ロ ジ ッ ク 入力は表中の一番上に 示 し てい ます。 ま た、LUT に正 し く 並べ ら れた入力 (I0 ~ I5) は、図21 の LUT 境界内お よ び表中に示 し てい ます。ロ ジ ッ ク 入力の名前は任意で付け る こ と がで き ますが、 こ の例では、 ザ イ リ ン ク ス ラ イ ブ ラ リ プ リ ミ テ ィ ブ と 同 じ 名前を使用 し てい ます。 た と えば、 マルチプ レ ク サー入力 I0 は LUT ピ ン I0 へ接続 さ れますが、 入力 S0 は LUT ピ ン I5 へ接続 さ れます。 一番左の列は、 有効なすべての入力 ロ ジ ッ ク ス テー ト を表 し た 2 進数 コ ー ド の10 進数 イ ンデ ッ ク ス で す。 説明上、 表中の 4 つの影付 き 部分は、 セ レ ク ト 入力 S0-S1 で選択 さ れ る 入力を示 し てい ます。 こ の 入力が出力 O へ渡 さ れ、 こ れがマルチプ レ ク サー機能 と な り ます。LUT は例外な く プ ロ グ ラ ム可能で す。 ど の よ う な入力順序で も 使用可能であ り 、 任意の機能を実現す る ために出力ビ ッ ト の ス テー タ ス を 変え る こ と がで き ます。 マルチプ レ ク サーの表形式を LUT の 16 進数 コ ー ド に変換す る 一般的な手法は次の と お り です。 • LUT のすべての可能な入力 ス テー ト を考慮す る こ と を仮定 し 、実行 さ れ る フ ァ ン ク シ ョ ン のすべ ての出力を表に ま と め ま す。表4に、4:1 マルチプ レ ク サーの真理値表の例を示 し ま す。X-Ref Target - Figure 21

図 21 : 4:1 マルチ プ レ ク サーセルの LUT6 イ ン プ リ メ ン テーシ ョ ン 64’FF00F0F0CCCCAAAA I2 I1 I0 O I4 I5 I3 I1 S0 O LUT6 I2 S1 I0 I3 XAPP522_21_070312