Spartan-6 FPGA

コ ネ ク テ ィ ビ テ ィ

キ ッ ト

ス タ ー ト ア ッ プ

ガ イ ド

display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© Copyright 2009–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

本資料は英語版 (v1.4) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。 日本語版は参考用 と し て ご使用の上、 最新情報につ き ま し ては、 必ず最新英語版を ご参照 く だ さ い。 こ の資料に関す る フ ィ ー ド バ ッ ク お よ び リ ン ク な ど の問題につ き ま し ては、jpn_trans_feedback@xilinx.comま でお知 ら せ く だ さ い。 いただ き ま し た ご意見を参考に早急に対応 さ せていただ き ます。 なお、 こ の メ ールア ド レ スへのお問い合わせは受け 付けてお り ません。 あ ら か じ めご了承 く だ さ い。

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます 日付 バージ ョ ン 説明 2009 年 12 月 8 日 1.0 初版 リ リ ース 2009 年 12 月 18 日 1.1 図 1を変更。13 ページの ス テ ッ プ 3を追加。図 2の下のハー ド ウ ェ ア設定方法に概要 を追加。14 ページの ス テ ッ プ 5で、ス テ ッ プ bのジ ャ ンパを J27 に変更、ス テ ッ プ c に ON は下側 と い う 補足を追加。図 3、図 4お よ び図 41の写真を変更。16 ページの ス テ ッ プ 8お よ び18 ページの ス テ ッ プ 11の前に概要のパ ラ グ ラ フ を追加。図 15を変更。22 ページの ス テ ッ プ dの MAC ア ド レ ス の例を変更。「Spartan-6 FPGA コ ネ ク

テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンの検証」に概要のパ ラ グ ラ フ を追加。25

ページの ス テ ッ プ 2のデー タ 送信お よ びパケ ッ ト サ イ ズのオプシ ョ ン を変更。30 ペー

ジの ス テ ッ プ 4を追加。30 ページの ス テ ッ プ 5で、 ス テ ッ プ aを変更 し 、 ス テ ッ プ c

お よ び ス テ ッ プ d を 追加。31 ペー ジ の ス テ ッ プ b のデ ィ レ ク ト リ パ ス を 変更。

「Spartan-6 FPGA IBERT リ フ ァ レ ン ス デ ザ イ ン で 設 計 を 開 始」 の 個条書 き よ り

IBERT デザ イ ン例の項目を削除。「IBERT デモのハー ド ウ ェ ア設定方法」 の概要のパ

キ ッ ト の内容」 よ り ア ッ プデー ト DVD を削除。図 1の、DDR3 リ ン ク 速度を変更。

「ISE Design Suite の イ ン ス ト ール と ラ イ セ ン ス取得」の 「 イ ン ス ト ールツール」 のセ ク シ ョ ン を 2 つの新規パ ラ グ ラ フ に変更。29 ページの ス テ ッ プ 7のパ ス 名か ら ISE Design Suite の リ リ ース番号を削除。30 ページのス テ ッ プ 4c の コ マ ン ド を変更。31 ページのス テ ッ プ 7d、Windows ベース の ス ク リ プ ト か ら 「ダブル ク リ ッ ク 」 を削除。 「次の ス テ ッ プ」のセ ク シ ョ ン を追加。 2010 年 8 月 10 日 1.3 30 ページのス テ ッ プ 4c、表 1、図 32のmig_v3_4をmig_v3_5に変更。表 1お よ び図 34のgig_eth_pcs_pma_v10_4をgig_eth_pcs_pma_v10_5に変更。 2010 年 10 月 5 日 1.4 AXI プ ロ ト コ ルの情報を追加。

改訂履歴. . . 2

このガ イ ド について

その他の リ ソ ース . . . 7 その他のサポー ト . . . 7Spartan-6 FPGA

コ ネ ク テ ィ ビ テ ィ

キ ッ ト

は じ めに. . . 9 コ ネ ク テ ィ ビ テ ィ キ ッ ト の内容. . . 9 同梱内容. . . .9 オン ラ イ ン よ り 入手で き る も の. . . .10 コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンデモの概要. . . 11 ボー ド お よ び コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンの特徴 . . . .11 コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンデモのハー ド ウ ェ ア設定方法. . . .13 Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンの検証 . . . 24ISE Design Suite の イ ン ス ト ール と ラ イ セ ン ス取得 . . . 27

ツールお よ び IP ラ イ セ ン ス のダ ウ ン ロ ー ド と イ ン ス ト ール. . . .27 コ ネ ク テ ィ ビ テ ィ デザ イ ン変更の準備完了. . . 29 Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンの変更 . . . 30 ハー ド ウ ェ アの変更. . . .30 テ ス ト 設定 . . . .32 ソ フ ト ウ ェ アの変更. . . .32 次の ス テ ッ プ. . . 33 コ ネ ク テ ィ ビ テ ィ TRD モジ ュ ール. . . .33 PCI Express . . . .35

Packet DMA (AXI4 イ ン タ ーフ ェ イ ス ラ ッ パーに よ る) . . . .36

マルチポー ト 仮想 FIFO お よ び メ モ リ コ ン ト ロ ー ラ ーブ ロ ッ ク . . . .37

イ ーサネ ッ ト . . . .37

ソ フ ト ウ ェ アデバ イ ス ド ラ イ バーお よ び ソ フ ト ウ ェ ア アプ リ ケーシ ョ ン/GUI の フ ァ イ ルお よ びス ク リ プ ト. . . .38

コ ネ ク テ ィ ビ テ ィ TRD のシ ミ ュ レーシ ョ ン . . . .39

Northwest Logic 社製 DMA IP の再利用 . . . .39

コ ネ ク テ ィ ビ テ ィ TRD の変更 . . . .39

Spartan-6 FPGA IBERT リ フ ァ レ ン スデザ イ ン で設計を開始 . . . 40

IBERT デモのハー ド ウ ェ ア設定方法 . . . .41

リ フ ァ レ ン スデザ イ ンフ ァ イ ル . . . 49

イ ン ス ト ール完了 . . . 49

こ の ス タ ー ト ア ッ プ ガ イ ド で は Spartan®-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト の内容 を 紹介 し 、

Spartan-6 FPGA で GTP ト ラ ン シーバ と LogiCORE™ IP を使用す る コ ネ ク テ ィ ビ テ ィ シ ス テ ムの

開発を開始す る 方法について解説 し ます。

その他の リ ソ ース

その他の資料は、 次のザ イ リ ン ク ス ウ ェ ブサ イ ト か ら 入手で き ます。 http://japan.xilinx.com/support/documentation/index.htm シ リ コ ンや ソ フ ト ウ ェ ア、IP に関す る ア ンサーデー タ ベース を検索 し た り 、 テ ク ニ カルサポー ト の ウ ェ ブケース を開 く 場合は、 次の ウ ェ ブサ イ ト にア ク セ ス し て く だ さ い。 http://japan.xilinx.com/support 製品 ラ イ セ ン ス フ ァ イ ルの イ ン ス ト ール と 使用方法に関す る テ ク ニ カルサポー ト は、 上記 ウ ェ ブ サ イ ト にア ク セ ス し て く だ さ い。 次の よ う な リ ソ ース を提供 し てい ます。 • テ ク ニ カルサポー ト に イ ン タ ーネ ッ ト 経由で問い合わせが可能な ウ ェ ブケース (電話サポー ト の情報 も 掲載) • ア ンサーデータベースのカ テ ゴ リ か ら も 簡単に検索可能なア ンサーブ ラ ウ ザ • ユーザーコ ミ ュ ニテ ィ で興味のあ る ト ピ ッ ク について議論す る フ ォー ラ ム • 講師に よ る講義や録音版 E- ラーニン グなどの各種 ト レーニングその他のサポー ト

購入 さ れた製品に関す る ご質問は、各地域のカ ス タ マーサービ ス担当者ま で電子 メ ールでお問い合 わせ く だ さ い。 • カナダ、 米国、 南米 : isscs_cases@xilinx.com • 欧州、 中東、 ア フ リ カ : eucases@xilinx.com • 日本を含むア ジ ア太平洋地域 : apaccase@xilinx.comSpartan-6 FPGA

は じ めに

Spartan®-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト は、 コ ネ ク テ ィ ビ テ ィ シ ス テ ムの迅速かつ効率的な開 発 を サ ポー ト し ま す。 こ の使いやすい包括的な コ ネ ク テ ィ ビ テ ィ 開発お よ びデモの環境は、PCI Express®や イ ーサネ ッ ト な ど一般的な規格ベース のプ ロ ト コ ルを用い る デザ イ ン向けに Spartan-6 フ ァ ミ リ を使用 し ます。 こ のキ ッ ト では、 低コ ス ト なプ ロ ト コ ルブ リ ッ ジ を イ ンプ リ メ ン ト し 、 さ ま ざ ま な市場分野で LVDS 通信な ど に代わ る 高効率な通信向けの設計が可能です。 メ モ : こ のガ イ ド に掲載 さ れてい る 図は代表例であ り 、 一般的な情報を提供す る こ と を目的 と し て い ます。 最新の情報は、 ザ イ リ ン ク ス ISE® Design Suite で確認 し て く だ さ い。コ ネ ク テ ィ ビ テ ィ

キ ッ ト の内容

こ のセ ク シ ョ ンではキ ッ ト の内容について説明 し 、 ザ イ リ ン ク ス の ウ ェ ブサ イ ト か ら 入手で き る リ ソ ース について も 紹介 し ます。同梱内容

• Spartan-6 FPGA XC6SLX45T-3 を搭載 し た SP605 評価ボー ド と 次の付属品 • 12V ユニバーサル電源 • USB A/Mini-B ケーブル 2 本 (ダ ウ ン ロ ー ド お よ びデバ ッ グ用) • イ ーサネ ッ ト CAT5 ケーブル 1 本 • DVI-VGA ア ダプ タ ー 1 個 • SMA ケーブル 4 本 • CompactFlash カー ド (512MB) 1 枚• ザ イ リ ン ク ス ISE Design Suite の DVD

• ISE Simulator を含む ISE Foundation™

• PlanAhead™ デザ イ ン解析ツール

• エンベデ ッ ド 開発キ ッ ト (EDK)

• Xilinx Platform Studio (XPS)

• Spartan-6 LXT FPGA 用の Northwest Logic 社 x1 PCIe Packet DMA IP コ アの製品ネ ッ ト リ ス ト ラ イ セ ン ス 1 シー ト (ノ ー ド ロ ッ ク ラ イ セ ン ス) • Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト 資料 • ウ ェ ルカ ム レ タ ー (ザ イ リ ン ク ス か ら のご挨拶文) • ハー ド ウ ェ ア設定ガ イ ド • ス タ ー ト ア ッ プガ イ ド (こ のマニ ュ アル)

オ ン ラ イ ン よ り 入手で き る も の

次については、 ザ イ リ ン ク ス の ウ ェ ブサ イ ト へア ク セ ス し て く だ さ い。• ISE Design Suite : Embedded Edition の ラ イ セ ン ス

• http://japan.xilinx.com/getproduct

• http://japan.xilinx.com/tools/faq.htm

• Northwest Logic 社の Spartan-6 FPGA 用 DMA IP コ アの ラ イ セ ン ス

• ザ イ リ ン ク ス が提供す る ラ イ セ ン ス : http://japan.xilinx.com/getproduct • 使用権許諾契約 : Northwest Logic 社の IP 使用権許諾契約 • 資料や リ フ ァ レ ン スデザ イ ンが掲載 さ れた開発キ ッ ト のホームページ • http://japan.xilinx.com/s6connkit • こ のページか ら は、 次の情報を入手で き ます。 - USB メ モ リ の内容 (USB に含まれるデータ の最新バージ ョ ン を入手可能) - 回路図、 ガーバー、 ボー ド 部品表 (BOM) - その他の詳細な資料 • テ ク ニ カルサポー ト • http://japan.xilinx.com/support

コ ネ ク テ ィ ビ テ ィ

タ ーゲ ッ ト

リ フ ァ レ ン ス

デザイ ン

デモの概要

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト の SPI x4 フ ラ ッ シ ュ には、 コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ

ト リ フ ァ レ ン スデザ イ ン (TRD) の構築済みデモが格納 さ れてい ます。 こ れはほかの ツールの イ ン ス ト ール前に動作 さ せ る こ と がで き 、Spartan-6 FPGA LX45T を使用す る コ ネ ク テ ィ ビ テ ィ TRD

のデモ を実行す る こ と で、SP605 評価ボー ド の機能を確認で き ます。

ボー ド および コ ネ ク テ ィ ビ テ ィ

タ ーゲ ッ ト

リ フ ァ レ ン ス

デザイ ンの特徴

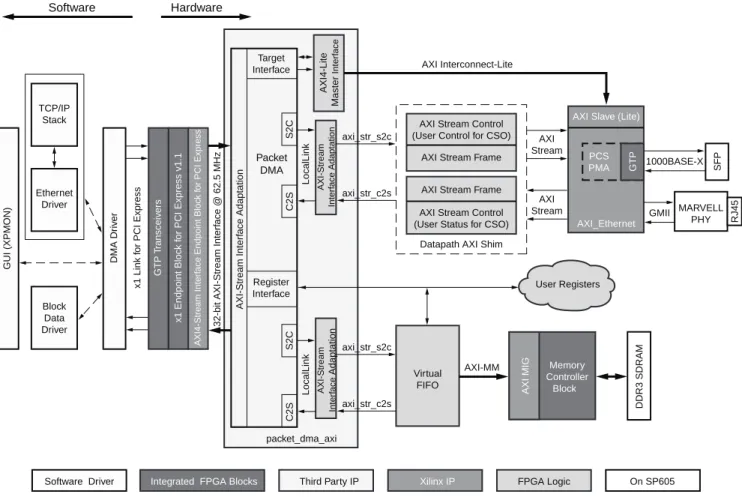

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ リ フ ァ レ ン スデザ イ ン (図 1参照) は、PCI Express エン ド ポ イ

ン ト ブ ロ ッ ク 、GTP ト ラ ン シーバー、 サー ド パーテ ィ や自社開発 IP コ ア と 連動す る メ モ リ コ ン ト ロ ー ラ ーブ ロ ッ ク な ど、Spartan-6 FPGA に統合 さ れた主要 コ ン ポーネ ン ト のデモ も 提供 し ます。 コ ネ ク テ ィ ビ テ ィ TRD は、AXI4 プ ロ ト コ ル IP コ ア を使用 し た も の と 、 レ ガシーイ ン タ ーフ ェ イ ス (LocalLink な ど) IP コ ア を使用 し た も のの 2 つのバージ ョ ンで提供 さ れてい ます。 AXI4 プ ロ ト コ ルバージ ョ ン のデザ イ ン では、 すべて AXI4 イ ン タ ーフ ェ イ ス に対応す る IP コ ア を 使 用 し ま す。 具 体 的 に は、AXI4-Stream ユ ー ザ ー イ ン タ ー フ ェ イ ス 対 応 LogiCORE™ IP

Spartan-6 FPGA Integrated Endpoint Block for PCI Express、AXI4 イ ン タ ー フ ェ イ ス 対 応

Northwest 社 Logic Packet DMA、AXI_Ethernet コ ア、AXI4 ユ ー ザ ー イ ン タ ー フ ェ イ ス 対応

Memory Interface Generator を使用 し ます

AXI4 プ ロ ト コ ル非対応バージ ョ ンのデザ イ ンでは、ト ラ ンザ ク シ ョ ン層 (TRN) ユーザーイ ン タ ー

フ ェ イ ス対応 LogiCORE IP Spartan-6 FPGA Integrated Endpoint Block for PCI Express、Northwest

社 Logic Packet DMA、XPS-LL-TEMAC IP コ ア (ト ラ イ モー ド イ ーサネ ッ ト MAC IP を使用)、

Spartan-6 メ モ リ コ ン ト ロ ー ラ ーブ ロ ッ ク 用 Memory Interface Generator IP を使用 し ます。

メ モ : こ のガ イ ド では、AXI4 プ ロ ト コ ルバージ ョ ンの TRD の場合について解説 し ます。AXI4 プ ロ ト コ ル非対応バージ ョ ン と の相違点は適宜説明 し ます。

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD には次の コ ン ポーネ ン ト が含まれます。

• 1 レーンの LogiCORE IP Spartan-6 FPGA Integrated Endpoint Block for PCI Express

• ト ラ ンザ ク シ ョ ン層パケ ッ ト (TLP) の使用率か ら PCIe®のデー タ 帯域幅を追跡す る

Preformance Monitor

• マルチチ ャ ネル DMA であ る Northwest Logic 社の Packet DMA for PCI Express

• 独立 し た受信パス (カー ド か ら シ ス テ ム : C2S チ ャ ネル) と 送信パス (シ ス テ ムか ら カー ド : S2C チ ャ ネル) に よ る全二重動作をサポー ト

• LocalLink の よ う にバ ッ ク エン ド でパケ ッ ト 用 イ ン タ ーフ ェ イ ス を提供

• 送受信両方向のデー タ 転送をモニ タ ー

• ユーザー定義の レ ジ ス タ にア ク セ スす る 制御プ レーン イ ン タ ーフ ェ イ ス を提供

適合層は AXI4 イ ン タ ーフ ェ イ ス に準拠す る ために Packet DMA IP を中心に構築 さ れてい ま

す。 従来の LocalLink ベース のユーザース ト リ ー ミ ン グ イ ン タ ーフ ェ イ ス は AXI4-Stream イ ン タ ーフ ェ イ ス に置 き 換え ら れ、制御プ レーンの タ ーゲ ッ ト イ ン タ ーフ ェ イ ス は AXI4-Lite の マ ス タ ーが提供 し ます。 • マルチポー ト 仮想 FIFO Spartan-6 FPGA の メ モ リ コ ン ト ロ ー ラ ーブ ロ ッ ク と 外部の DDR3 メ モ リ デバ イ ス を使用す る 非常に効率的な層を構成 し ます。

X-Ref Target - Figure 1

図 1 : Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ リ フ ァ レ ン スデザイ ンのブ ロ ッ ク図 UG665_01_092810 Packet DMA C2S S2C C2S S2C Target Interface AXI4-Lite Master Interf ace axi_str_s2c AXI Stream AXI Interconnect-Lite 1000BASE-X GMII AXI Stream axi_str_c2s axi_str_s2c axi_str_c2s LocalLink packet_dma_axi x1 Link f or PCI Express

Third Party IP Xilinx IP FPGA Logic Software Driver

32-bit AXI-Stream Interf

ace @ 62.5 MHz AXI-Stream Interf ace Adaptation Register Interface Virtual FIFO

AXI Stream Control (User Control for CSO)

AXI Slave (Lite)

AXI_Ethernet

MARVELL PHY RJ45

AXI Stream Frame

AXI Stream Control (User Status for CSO)

AXI Stream Frame

Datapath AXI Shim

AXI-MM User Registers GTP T ransceiv ers x1 Endpoint Bloc k f or PCI Express v1.1 AXI4-Stream Interf

ace Endpoint Bloc

k f or PCI Express DMA Dr iv er GUI (XPMON) Block Data Driver Ethernet Driver TCP/IP Stack

Integrated FPGA Blocks On SP605

Memory Controller Block AXI MIG DDR3 SDRAM Software Hardware LocalLink AXI-Stream Interf ace Adaptation GTP SFP PCS PMA AXI-Stream Interf ace Adaptation

• AXI4-Lite ス レーブ イ ン タ ーフ ェ イ ス を備え た AXI_Ethernet IP コ ア (ト ラ イ モー ド イ ーサ ネ ッ ト MAC を使用)

イ ーサネ ッ ト アプ リ ケーシ ョ ンは、 次の 2 つのモー ド で実行で き ます。

• オン ボー ド の外部 PHY を使用す る GMII モー ド

• Spartan-6 FPGA の GTP ト ラ ン シーバーを使用す る 1000BASE-X モー ド 。 こ の場合、

AXI_Ethernet IP コ ア の パ ラ メ ー タ ー オ プ シ ョ ン に よ っ て 1000BASE-X PCS-PMA

LogiCORE IP も 有効にす る 必要があ り ます。 • AXI4 プ ロ ト コ ルに対応 し ていないバージ ョ ンの場合、 こ の IP は外部接続 さ れ、 XPS-LL-TEMAC IP コ アの一部にはな り ません。 AXI4 プ ロ ト コ ルバージ ョ ンの TRD では、 レ ジ ス タ をプ ロ グ ラ ムす る 制御プ レーン イ ン タ ー フ ェ イ ス に AXI4-Lite を使用 し ます。 一方、AXI4 プ ロ ト コ ルに対応 し ていないバージ ョ ン で は、PLBv46 が レ ジ ス タ プ ロ グ ラ ムの制御プ レーン イ ン タ ーフ ェ イ ス にな り ます。

コ ネ ク テ ィ ビ テ ィ

タ ーゲ ッ ト

リ フ ァ レ ン ス

デザイ ン

デモのハー ド ウ ェ ア

設定方法

こ こ では、 コ ネ ク テ ィ ビ テ ィ TRD のデモを実行す る ための、 ハー ド ウ ェ ア設定方法を説明 し ます。 1. こ のデモでは、PCIe と ギガ ビ ッ ト イ ーサネ ッ ト プ ロ ト コ ル間のブ リ ッ ジ ン グ機能の概要を示 し ます。 ま た、 オン ボー ド の DDR3 メ モ リ デバ イ スへのア ク セ ス も 可能です。 こ のデモ を実行す る には次が必要です。 • Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト• x1 PCIe ス ロ ッ ト 付 き のマザーボー ド 、CD ROM ド ラ イ ブ、USB ポー ト のあ る PC シ ス

テ ム

• モニ タ ー、 キーボー ド 、 マ ウ ス

• 稼働中の イ ーサネ ッ ト 接続 (可能な ら ばギガ ビ ッ ト イ ーサネ ッ ト)

• Linux OS : Fedora 10 LiveCD

2. 代替デモの実行

手順 1に示すいずれかが揃っ ていない場合は、40 ページの 「Spartan-6 FPGA IBERT リ フ ァ レ

ン スデザ イ ン で設計を開始」 を参照 し て、Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト に付属す る SP605 ボー ド を別の方法で立ち上げます。 すべてが用意で き た場合は、手順 3へ進み PCIe と ギガ ビ ッ ト イ ーサネ ッ ト プ ロ ト コ ル間のブ リ ッ ジ ン グのデモ設定を続けて く だ さ い。 3. ハー ド ウ ェ ア設定の手順に従い、Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト を起動済みの場合 は、24 ページの 「Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンの検 証」 に進みます。 設定が完了 し ていない場合は、手順 4か ら 作業を継続 し て く だ さ い。

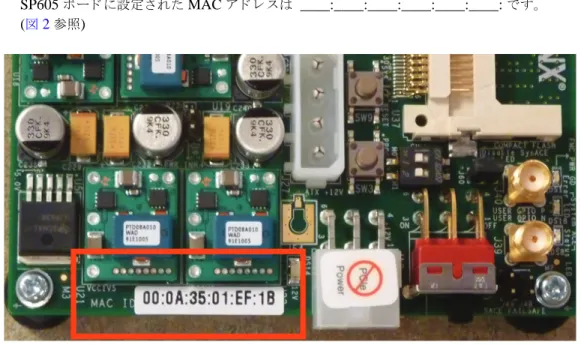

4. 次に、 デモで使用す る MAC ア ド レ ス を記入 し ます。 SP605 ボー ド に設定 さ れた MAC ア ド レ ス は ____:____:____:____:____:____: です。 (図 2参照) 次の 2 つの手順では、ネ ッ ト ワ ー ク イ ン タ ーフ ェ イ ス コ ン ト ロ ー ラ ー機能を有効に し て、Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD を使用で き る よ う に SP605 ボー ド を設定 し ます。 5. ハー ド ウ ェ ア設定 I – 電源 コ ネ ク タ ーを接続 し ます。 a. PC シ ス テ ムの電源を切 り ます。 b. PC シ ス テ ムの 12V ATX 電源の未使用 4 ピ ン電源 コ ネ ク タ ー (CD ROM に接続 さ れてい る も の と 同様) を ボー ド (J27) に接続 し ます (図 3参照)。 c. 電源ス イ ッ チ SW2 を ON (下側) の位置に し ます。

X-Ref Target - Figure 2

図 2 : SP605 ボー ド の MAC ア ド レ ス

X-Ref Target - Figure 3

図 3 : 12V ATX 電源 コ ネ ク タ ー

UG665_02_112409

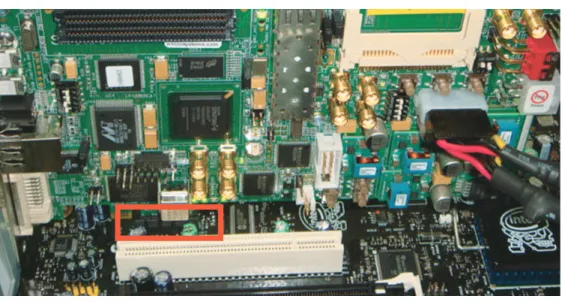

6. ハー ド ウ ェ ア設定 II – SP605 ボー ド を PCI Express の空 き ス ロ ッ ト に挿入 し ます。

a. PC シ ス テ ムのマザーボー ド 上で ス ロ ッ ト の位置を確認 し ます。

b. SP605 ボー ド の PCIe x1 エ ッ ジ コ ネ ク タ ーを PCI Express ス ロ ッ ト に挿入 し ます

(図 4参照)。 c. イ ーサネ ッ ト LAN ケーブルを RJ-45 ス ロ ッ ト に接続 し ます。 ケーブルの も う 一端は イ ー サネ ッ ト の壁面 ソ ケ ッ ト に接続 し ま す。PC シ ス テ ム のほかの イ ーサネ ッ ト 接続はすべて 取 り 外すか、 無効に し て く だ さ い。 d. こ のデモでは、 電源を入れ る と 、 あ ら か じ め SPI x4 フ ラ ッ シ ュ に格納 さ れた PCIe - ギガ ビ ッ ト イ ーサネ ッ ト デザ イ ンに よ っ て FPGA がプ ロ グ ラ ム さ れます。 7. CD ROM か ら ブー ト さ れ る よ う にデス ク ト ッ プ PC を設定 し ます。 a. PC シ ス テ ムの電源を入れて、 初期 BIOS 画面に次の操作用のキーを選択す る プ ロ ンプ ト が表示 さ れ る のを待ち ます。 - ブー ト メ ニ ュ ー、 ま たは - BIOS 設定ユーテ ィ リ テ ィ b. こ の よ う なプ ロ ンプ ト が表示 さ れない場合は、PC メ ーカーのマニ ュ アルを参照 し て く だ さ い。 ほ と ん ど のシ ス テ ムで使用す る キーは F12、F2、F1、 ま たは Delete です。 c. CD ROM が最初にブー ト さ れ る よ う に、 ブー ト メ ニ ュ ーま たは BIOS ブー ト 順の設定を 変更 し ます。

d. CD ROM の取 り 出 し 口を開いて、Fedora 10 LiveCD を挿入 し ます。

e. 変更を保存 し て、 ブー ト メ ニ ュ ーま たは BIOS 設定の画面を終了 し ます。

f. PC シ ス テ ムが CD ROM か ら ブー ト さ れます。

X-Ref Target - Figure 4

図 4 : PCI Express のス ロ ッ ト 位置確認 と SP605 ボー ド の挿入

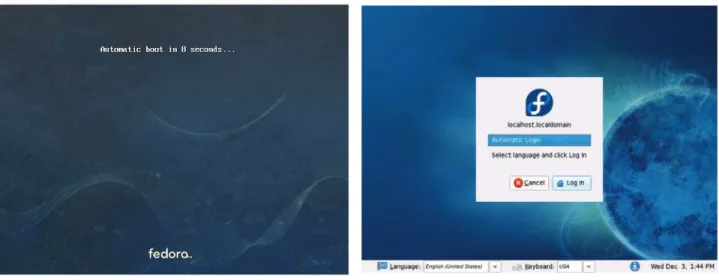

次の 3 つの手順では、PC シ ス テ ムが Linux オペレーテ ィ ン グシ ス テ ム (Fedora 10 LiveCD) でブー ト さ れ、SP605 ボー ド ハー ド ウ ェ ア と ソ フ ト ウ ェ アアプ リ ケーシ ョ ン を接続す る デバ イ ス ド ラ イ バーが読み込まれます。 8. Fedora OS Live が起動 し 、 自動的に ロ グ イ ン し ます。 a. 電源を入れ る と図 5の画面が表示 さ れます。 こ の画面が表示 さ れ る ま で、 シ ス テ ム構成に 応 じ て 2 ~ 3 分かか り ます。 b. [Login] を ク リ ッ ク し てシ ス テ ムに ロ グ イ ン し ます。 シ ス テ ム構成に応 じ て 1 ~ 2 分かか り ます。 9. USB メ モ リ の内容を コ ピー し ます。 a. キ ッ ト に付属す る USB メ モ リ に リ フ ァ レ ン スデザ イ ン フ ァ イ ルが保存 さ れてい ます。 b. USB メ モ リ を PC シ ス テ ムの USB コ ネ ク タ ーに挿入 し ます。 c. USB ド ラ イ ブが Fedora 10 オペレーテ ィ ン グシ ス テ ム でマ ウ ン ト さ れ る ま で待ち ます。マ ウ ン ト さ れ る と 、 デス ク ト ッ プ上にア イ コ ンが表示 さ れます。 d. USB ド ラ イ ブのア イ コ ン をダブル ク リ ッ ク し て、s6_pcie_dma_ddr3_gbe_axiフ ォ ルダー を ユーザーのホーム フ ォ ルダー/デ ィ レ ク ト リ に コ ピー し ま す。AXI4 プ ロ ト コ ル非対応 バージ ョ ンの TRD は、s6_pcie_dma_ddr3_gbe と い う 名前のデザ イ ン フ ォ ルダーに保 存 さ れてい る こ と に注意 し て く だ さ い。 ただ し 、 デ ィ レ ク ト リ 構造や一般的な設定方法は 2 つのデザ イ ンで共通です。 e. USB ド ラ イ ブのマ ウ ン ト を解除す る には、USB ド ラ イ ブのア イ コ ン を右 ク リ ッ ク し て [Unmount Volume] を選択 し ます。

X-Ref Target - Figure 5

図 5 : Fedora の画面

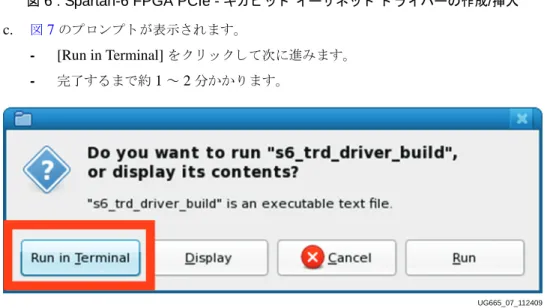

10. ド ラ イ バーを コ ンパ イ ル し て、 カーネルモジ ュ ールを挿入 し ます。 a. s6_pcie_dma_ddr3_gbe_axiフ ォ ルダーに移動 し ます。 b. [s6_trd_driver_build] を ダブル ク リ ッ ク し て、 カーネル オブジ ェ ク ト と GUI を作成 し ま す (図 6)。 完了す る ま で 1 ~ 2 分かか り ます。 c. 図 7のプ ロ ンプ ト が表示 さ れます。 - [Run in Terminal] を ク リ ッ ク し て次に進みます。 - 完了す る ま で約 1 ~ 2 分かか り ます。 d. タ ー ミ ナル画面を ス ク ロ ール し てエ ラ ーがない こ と を確認 し ます。 エ ラ ーがなければ、 任 意のキーを押 し て タ ー ミ ナル ウ ィ ン ド ウ を終了 し ます。

X-Ref Target - Figure 6

図 6 : Spartan-6 FPGA PCIe - ギガ ビ ッ ト イ ーサネ ッ ト ド ラ イバーの作成/挿入

X-Ref Target - Figure 7

図 7 : s6_trd_driver_build の実行

UG665_06_090810

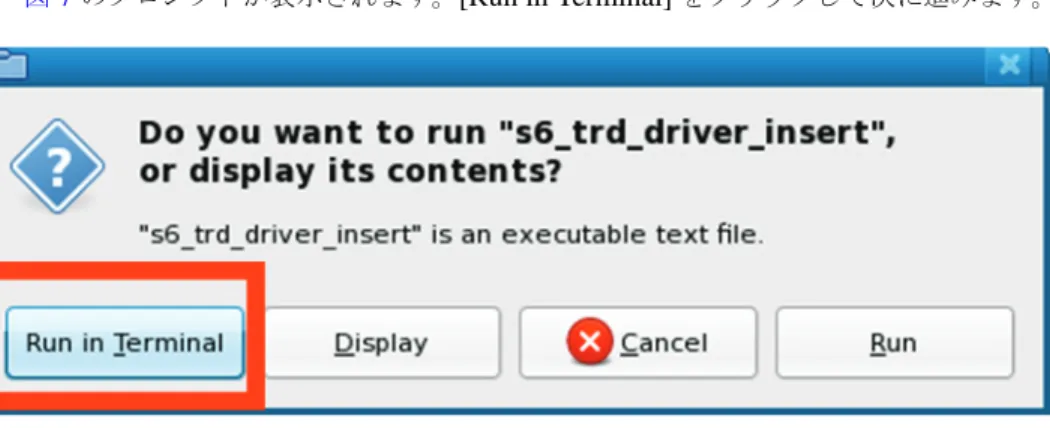

e. [s6_trd_driver_insert] を ダブル ク リ ッ ク し て、 ド ラ イ バーモジ ュ ールを カーネルに挿入 し ます (図 8を参照)。 f. 図 7のプ ロ ンプ ト が表示 さ れます。[Run in Terminal] を ク リ ッ ク し て次に進みます。 g. タ ー ミ ナル画面を ス ク ロ ール し てエ ラ ーがない こ と を確認 し ます。 エ ラ ーがなければ、 任 意のキーを押 し て タ ー ミ ナル ウ ィ ン ド ウ を終了 し ます。 次の 5 つの手順では、SP605 への イ ーサネ ッ ト LAN 接続を設定 し 、 ネ ッ ト ワー ク イ ン タ ーフ ェ イ ス コ ン ト ロ ー ラ ーが機能す る よ う に環境設定 し ます。 11. ネ ッ ト ワー ク 設定 I – ネ ッ ト ワー ク 環境を設定 し ます。 新 し いネ ッ ト ワー クデバ イ ス を追加 し ます。 • ネ ッ ト ワー ク 設定の GUI を開 き ます。

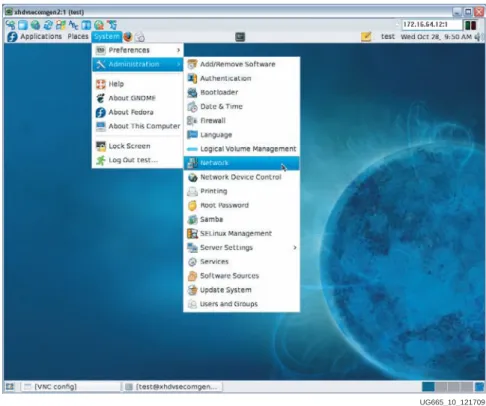

• [System] → [Administration] → [Network] を ク リ ッ ク し ます (図 10参照)。

X-Ref Target - Figure 8

図 8 : ド ラ イバーモ ジ ュ ールを カ ーネルに挿入する ためのフ ァ イル

X-Ref Target - Figure 9

図 9 : s6_trd_driver_insert の実行

UG665_08_090810

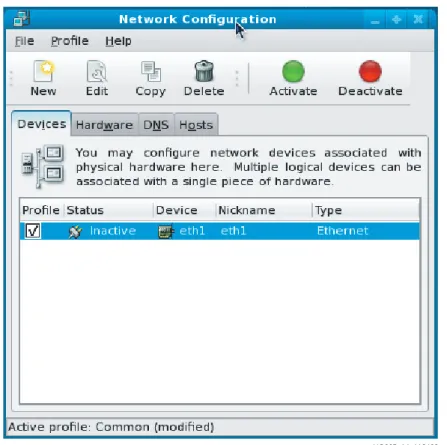

12. ネ ッ ト ワー ク 設定 II – 新規デバ イ ス を作成 し ます。

[Hardware] タ ブには、認識 さ れたハー ド ウ ェ アデバ イ ス が表示 さ れます。 こ のガ イ ド の フ ロ ー

例では SP605 ボー ド が eth1 と い う 名前で認識 さ れてい ます (図 12参照)。

X-Ref Target - Figure 10

図 10 : ネ ッ ト ワー ク設定 GUI の起動 メ ニ ュ ー

X-Ref Target - Figure 11

図 11 : [Network Configuration] ダ イ ア ロ グ

UG665_10_121709

a. [Devices] タ ブには何 も 表示 さ れてい ません。

[Devices] タ ブ (図 13を参照) に SP605 ボー ド が表示 さ れ る よ う にす る には、 新たに イ ー

サネ ッ ト 接続を作成す る 必要があ り ます。

- [Devices] タ ブ を ク リ ッ ク し ます。

- [New] → [Create New Ethernet Connection] を ク リ ッ ク し ます。

13. ネ ッ ト ワー ク 設定 III – 新規 イ ーサネ ッ ト 接続を作成 し ます。

a. 画面に表示 さ れ る 指示に従い、 設定プ ロ セ ス を完了 さ せます。 既に イ ーサネ ッ ト 接続が稼 働 し てい る 場合、こ の NIC は イ ン タ ーフ ェ イ ス eth1 と し て検出 さ れます。[eth1] を ク リ ッ

ク し ます。

X-Ref Target - Figure 12

図 12 : [Hardware] タ ブ

X-Ref Target - Figure 13

図 13 : [Devices] タ ブ

UG665_12_120109

メ モ : SP605 ボー ド が常に eth1 と し て識別 さ れ る わけではあ り ま せん。 識別名は、 シ ス テ ム上の既存の イ ーサネ ッ ト イ ン タ ーフ ェ イ ス に よ っ て異な り ます。 b. IP ア ド レ ス はネ ッ ト ワ ー ク 設定に応 じ て静的ま たは動的に割 り 当て ら れます。 - ネ ッ ト ワー ク 上の IP ア ド レ ス割 り 当て方法を把握 し 、 必要なネ ッ ト ワー ク 環境を設 定す る には、 ネ ッ ト ワー ク 管理者に問い合わせて く だ さ い。 - その指示に従い、DHCP 構成のために適切な DNS 設定を入力 し ます。

c. [File] → [Save] を ク リ ッ ク し て変更を保存 し 、[OK] を ク リ ッ ク し て変更を承認 し ます。

d. 設定が完了す る と 、図 14の画面が表示 さ れます。

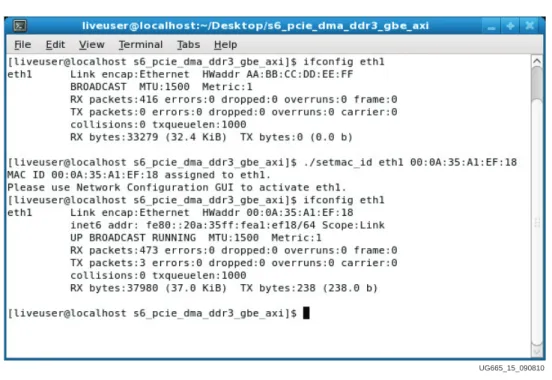

14. ネ ッ ト ワー ク 設定 IV – MAC ア ド レ ス を割 り 当て ます。

a. [Applications] → [System Tools] → [Terminal] を ク リ ッ ク し て タ ー ミ ナルを起動 し ます。

b. s6_pcie_dma_ddr3_gbe_axiデ ィ レ ク ト リ に移動 し ます。 $ cd s6_pcie_dma_ddr3_gbe_axi

X-Ref Target - Figure 14

図 14 : 新規イ ーサネ ッ ト 接続

c. ifconfig ユーテ ィ リ テ ィ に よ っ てデバ イ ス を確認 し ます (図 15参照)。

$ /sbin/ifconfig eth1

d. 付属の ス ク リ プ ト を実行 し て、 デザ イ ン内の イ ーサネ ッ ト MAC に MAC ア ド レ ス を設定 し ます。13 ページの手順 3で調べた MAC ア ド レ ス を使用 し ます。

$ ./setmac_id eth1 <SP605_MAC_ID>

例 : ./setmac_id eth1 00:01:02:03:04:05

e. MAC ID の割 り 当て後に ifconfig ユーテ ィ リ テ ィ を再実行 し て、NIC に MAC ID が割 り

当て ら れてい る こ と を確認 し ます。

$ /sbin/ifconfig eth1

X-Ref Target - Figure 15

図 15 : NIC に MAC ア ド レ ス を割 り 当て ます。

15. ネ ッ ト ワー ク 設定 V – イ ーサネ ッ ト 接続を ア ク テ ィ ブに し ます。

a. ネ ッ ト ワー ク 設定の GUI を開 き ます。

b. [Activate] ボ タ ン を ク リ ッ ク し て イ ーサネ ッ ト イ ン タ ーフ ェ イ ス を ア ク テ ィ ブに し ます

(図 16参照)。

c. イ ン タ ーネ ッ ト のプ リ フ ァ レ ン ス を設定 し ます。

- [System] → [Preferences] → [Internet and Network Proxy] → [Network Proxy] を ク

リ ッ ク し ます。

- こ れ ら の設定の詳細は、 ネ ッ ト ワー ク 管理者に問い合わせて く だ さ い。

d. 以上の設定に よ っ て、 イ ン タ ーネ ッ ト を参照で き る よ う にな り ま し た。

- [Applications] → [Internet] → [Firefox Web Browser] を ク リ ッ ク し て ウ ェ ブブ ラ ウ

ザーを起動 し ます。 - ブ ラ ウ ザーの ウ ィ ン ド ウ が画面に表示 さ れ る ま で、 シ ス テ ム構成に応 じ て 1 ~ 2 分か か り ます。 こ れで手順は終了です。Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト の設定が完了 し 、 構築済みコ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン ス デザ イ ンのデモを テ ス ト し ま し た。デザ イ ンでは、PCI Express 用の内蔵ブ ロ ッ ク (x1 PCI Express v1.1 仕様準拠の コ ン フ ィ ギ ュ レーシ ョ ン)、 イーサネ ッ ト 用 LogiCORE IP モジ ュ ール、 オ ン ボー ド の DDR3 メ モ リ と 接続す る 内蔵 メ モ リ コ ン ト ロ ー ラ ーブ

ロ ッ ク を中心に設計 さ れた仮想 FIFO メ モ リ コ ン ト ロ ー ラ ー、 お よ び PCI Express 用のサー ド パー テ ィ 製 DMA コ ン ト ロー ラ ーが使用 さ れてい ます。

X-Ref Target - Figure 16

図 16 : Spartan-6 FPGA NIC のア ク テ ィ ブ化

Spartan-6 FPGA

コ ネ ク テ ィ ビ テ ィ

タ ーゲ ッ ト

リ フ ァ レ ン ス

デザイ ンの

検証

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD はパフ ォーマ ン ス と ス テー タ ス を監視す る モニ タ ーアプ リ ケーシ ョ ンお よ び GUI を提供 し ます。 こ のアプ リ ケーシ ョ ン を使用 し て、 さ ま ざ ま な シ ス テ ム パ ラ メ ー タ ーの最適化を試み る こ と がで き ます。 こ こ では、 メ モ リ - PCI Express 間 イ ン タ ーフ ェ イ ス の主なパフ ォーマ ン ス基準について解説 し ます。 Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD を検証す る には、 次の手順に従っ て く だ さ い。 1. Performance Monitor か ら コ ネ ク テ ィ ビ テ ィ ターゲ ッ ト リ フ ァ レ ン スデザ イ ン を起動し ます。 a. s6_pcie_dma_ddr3_gbe_axiフ ォ ルダーに移動 し ます。b. [s6_trd_app_gui] を ダブル ク リ ッ ク し て、Xilinx Performance & Status Monitor の GUI を

起動 し ます。

c. 図 18に示すプ ロ ンプ ト が表示 さ れます。[Run in Terminal] を ク リ ッ ク し て次に進みます。

X-Ref Target - Figure 17

図 17 : Xilinx Performance & Status Monitor の GUI を起動する ための フ ァ イル

X-Ref Target - Figure 18

図 18 : s6_trd_app_gui の実行

UG665_17_090810

2. Performance Monitor でテ ス ト を設定 し ます。 a. デー タ 転送には 2 つのオプシ ョ ンがあ り ます。 - ネ ッ ト ワー クパ ス イ ーサネ ッ ト への接続が既に存在す る ため、 ネ ッ ト ワ ー ク パ ス (イ ーサネ ッ ト) のオ プシ ョ ンは こ の GUI イ ン タ ーフ ェ イ ス か ら 設定で き ません。 - メ モ リ パ ス (DDR3) b. パケ ッ ト サ イ ズには、 次のオプシ ョ ンがあ り ます。 - メ モ リ パ ス (DDR3) 最小パケ ッ ト サ イ ズ : 256 ~ 4096 の値を選択 最大パケ ッ ト サ イ ズ : 256 ~ 4096 の値を選択 3. テ ス ト を実行 し 、Performance Monitor でペ イ ロ ー ド の統計情報を確認 し ます。 a. [Start Test] を ク リ ッ ク し て、 パフ ォーマ ン ステ ス ト を開始 し ます。 b. ペ イ ロ ー ド の統計情報か ら 、DMA エ ン ジ ンのネ ッ ト ワ ー ク パス (イ ーサネ ッ ト) お よ び メ モ リ パ ス (DDR3) チ ャ ネル上のデー タ 転送状況を確認 し ます (図 19参照)。

X-Ref Target - Figure 19

図 19 : DDR3 メ モ リ イ ン タ ー フ ェ イ スのパフ ォ ーマ ン ス

4. Performance Monitor 上で PCIe の統計情報を確認 し ます (図 20参照)。

[PCIe Statistics] を ク リ ッ ク し て、PCIe イ ン タ ーフ ェ イ ス上のデー タ 転送数を表示 し ます。

5. シ ス テ ム ス テー タ ス を確認 し ます (図 21参照)。

[System Status] を ク リ ッ ク し て、 次を確認 し ます。

• PCIe リ ン ク ス テー タ ス、 ベン ダー ID、 デバ イ ス ID 情報

• イ ーサネ ッ ト お よ び DDR3 イ ン タ ーフ ェ イ ス の DMA デー タ/チ ャ ネルア ク テ ィ ビ テ ィ

X-Ref Target - Figure 20

図 20 : PCIe イ ン タ ー フ ェ イ スのパフ ォ ーマ ン ス

こ れで手順は終了です。構築済みデモデザ イ ン を使用 し て Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト のシ ス テ ムパフ ォーマ ン ス を検証 し ま し た。 こ のデザ イ ンでは、PCI Express 用の内蔵ブ ロ ッ ク

(x1 PCI Express v1.1 仕様準拠の コ ン フ ィ ギ ュ レーシ ョ ン)、 イ ーサネ ッ ト 用 LogiCORE IP、 オ ン

ボー ド の DDR3 メ モ リ と 接続す る 内蔵 メ モ リ コ ン ト ロ ー ラ ーブ ロ ッ ク を中心に設計 さ れた仮想

FIFO メ モ リ コ ン ト ロ ー ラ ー、 お よ び PCI Express 用のサー ド パーテ ィ 製 DMA コ ン ト ロ ー ラ ーが

使用 さ れてい ます。

ISE Design Suite

のイ ン ス ト ール と ラ イ セ ン ス取得

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト には、デバ イ ス が Spartan-6 LX45T FPGA に ロ ッ ク さ れ

た ISE Design Suite: Embedded Edition の全機能を使用可能な ラ イ セ ン ス が付属 し てい ます。 ソ フ

ト ウ ェ アは、DVD か ら イ ン ス ト ールす る か、 次の ウ ェ ブサ イ ト か ら イ ン ス ト ー ラ ーを ダ ウ ン ロ ー ド し て イ ン ス ト ールで き ます。http://japan.xilinx.com/support/download/index.htm イ ン ス ト ールお よ び ラ イ セ ン ス取得に関す る 詳細は、次のザ イ リ ン ク ス資料サ イ ト か ら 『ISE Design Suite : イ ン ス ト ール、 ラ イ セ ン ス、 リ リ ース ノ ー ト 』 (UG631) を参照 し て く だ さ い。 http://japan.xilinx.com/support/documentation

ツールおよび

IP

ラ イ セ ン スのダウン ロー ド と イ ン ス ト ール

こ の コ ネ ク テ ィ ビ テ ィ キ ッ ト には、ISE Design Suite : Embedded Edition お よ び 1 年以内のすべて の関連ア ッ プデー ト に対す る ノ ー ド ロ ッ ク ラ イ セ ン ス が付属 し てい ます。 さ ら に、Spartan-6 LXT

X-Ref Target - Figure 21

図 21 : シ ス テムス テー タ ス情報

Northwest 社 の PCI Express 用 Logic Packet DMA IP コ ア の 製品 ネ ッ ト リ ス ト フ ァ イ ル は、

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト に付属す る USB メ モ リ に保存 さ れてい ます。 ラ イ セ ン

ス は、 次に示す取得手順を完了す る と ア ク テ ィ ブにな り ます。 こ の ラ イ セ ン ス に よ っ て、 製品ネ ッ ト リ ス ト か ら 任意の Spartan-6 FPGA を タ ーゲ ッ ト に選択で き る よ う にな り ます。

ISE Design Suite お よ び Northwest Logic IP の ラ イ セ ン ス を PC にダ ウ ン ロ ー ド し て イ ン ス ト ール

す る 手順は次の と お り です。 1. 次のザ イ リ ン ク ス ソ フ ト ウ ェ ア登録お よ び ラ イ セ ン ス取得サ イ ト にア ク セ ス し ます。 http://japan.xilinx.com/getproduct 2. 既存のア カ ウ ン ト で ロ グ イ ンす る か、 必要であれば新規ア カ ウ ン ト を作成 し ます (図 22参照)。 3. ロ グ イ ンす る と 納品先住所を確認す る 画面が表示 さ れ る 場合があ り ます。 納品先住所を確認ま たは更新 し た ら 、[Next] を ク リ ッ ク し ます。 4. 次のチ ェ ッ ク ボ ッ ク ス を オンに し ます (図 23参照)。

• ISE Design Suite: Embedded Spartan-6 LX45T Device Locked Edition

• Spartan-6 FPGA Connectivity Kit, NWL x1 Packet DMA Back End Core, Node-Locked

License, Single Seat

[Generate Node-Locked License] を ク リ ッ ク し ます。

X-Ref Target - Figure 22

図 22 : ザイ リ ン ク ス製品ダウン ロー ド お よび ラ イ セ ン ス提供サイ ト

X-Ref Target - Figure 23

図 23 : 新規 ラ イ セ ン ス フ ァ イルの作成

UG665_22_112409

5. 指示に従っ て、 ホ ス ト OS 情報お よ びホ ス ト ID (デ ィ ス ク のシ リ アル番号ま たは MAC ア ド レ ス) を入力 し て ラ イ セ ン ス を生成 し ます。

6. [Manage Licenses] タ ブを ク リ ッ ク し て、 ラ イ セ ン ス フ ァ イ ルを ダ ウ ン ロ ー ド し ます。 ま たは、

電子 メ ールに添付 さ れた ラ イ セ ン ス フ ァ イ ルを確認 し ます。

7. [ス タ ー ト]→[すべてのプ ロ グ ラ ム]→[ISE Design Suite]→[Manage Xilinx Licenses] を ク リ ッ ク し 、[Copy License] を ク リ ッ ク し て Xilinx License Manager を起動 し 、 コ ン ピ ュ ー タ に ラ イ セ ン ス を イ ン ス ト ール し ます (図 24参照)。

こ れで、ISE Design Suite : Embedded Edition を使用 し て Spartan-6 LX45T FPGA リ ソ ース を使用 す る コ ネ ク テ ィ ビ テ ィ シ ス テ ム を作成ま たは変更で き る よ う にな り ま し た。

イ ン ス ト ールお よ び ラ イ セ ン ス 取得に関す る 詳細は、 次の リ ン ク か ら 『ISE Design Suite : イ ン ス ト ール、 ラ イ セ ン ス、 リ リ ース ノ ー ト 』 (UG631) を参照 し て く だ さ い。

http://japan.xilinx.com/support/documentation

こ れで手順は終了です。ISE Design Suite ツールお よ び Northwest Logic 社の DMA IP コ アの イ ン ス ト ールが完了 し 、 ツールの Embedded Edition と コ アの ラ イ セ ン ス が設定 さ れま し た。

コ ネ ク テ ィ ビ テ ィ

デザイ ン変更の準備完了

FPGA ベース の コ ネ ク テ ィ ビ テ ィデモの設定 と 検証、お よ び ISE Design Suite : Embedded Edition

の イ ン ス ト ールが完了 し たので、Spartan-6 FPGA LX45T の コ ネ ク テ ィ ビ テ ィ デザ イ ンが変更で き る よ う にな り ま し た。 こ こ では、 ザ イ リ ン ク ス ツールのシ ンプルな フ ロ ーお よ び Spartan-6 FPGA

コ ネ ク テ ィ ビ テ ィ キ ッ ト と コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンに適用す る 設計手 法について解説 し ます。

X-Ref Target - Figure 24

図 24 : [Manage Xilinx Licenses] タ ブ

Spartan-6 FPGA

コ ネ ク テ ィ ビ テ ィ

タ ーゲ ッ ト

リ フ ァ レ ン ス

デザイ ンの

変更

こ のセ ク シ ョ ンでは、 次の 2 つのデザ イ ン変更方法を説明 し ます。 • ハー ド ウ ェ アお よ び RTL の変更 • ソ フ ト ウ ェ アお よ び ド ラ イ バーの変更ハー ド ウ ェ アの変更

こ こ では、 ハー ド ウ ェ アの変更方法を説明 し ます。PCI Express のベン ダー ID を変更 し ます。 RTL デザ イ ン を変更お よ び イ ンプ リ メ ン ト す る には、 次の手順に従っ て く だ さ い。 1. ザ イ リ ン ク ス のデザ イ ン ツールが イ ン ス ト ール さ れてい る PC シ ス テ ム ま たは ラ ッ プ ト ッ プ を使用 し ます。 2. 付属の USB メ モ リ に保存 さ れた内容を、こ のマシ ンの ロ ーカルデ ィ レ ク ト リ に コ ピー し ます。 3. デザ イ ン を変更 し ます。 a. s6_pcie_dma_ddr3_gbe_axi/design/source/デ ィ レ ク ト リ に移動 し ます。 b. s6_pcie_dma_ddr3_gbe_axi.vフ ァ イ ルを編集 し ます。 c. CFG_VEN_ID と い う 文字列を検索 し ます。d. こ の行の英数字 10EE を、PCI-SIG か ら 割 り 当て ら れたベン ダー ID に変更 し ます (10EE

はザ イ リ ン ク ス のベン ダー ID)。 こ の値を 19AA に変更 し ます。 こ の変更に よ っ て、 先ほ ど の行は次の よ う にな り ます。

localparam [15:0] CFG_VEN_ID = 16'h19AA;

e. 変更を保存 し て終了 し ます。 4. デザ イ ン を構築 し イ ンプ リ メ ン ト し ます。 a. タ ー ミ ナル ウ ィ ン ド ウ を開 き ます。 ツール向けにザ イ リ ン ク ス環境を設定 し ます。 b. s6_pcie_dma_ddr3_gbe_axi/design/implement/デ ィ レ ク ト リ に移動 し ます。 c. オペレーテ ィ ン グシ ス テ ムに応 じ て、 次の手順に従い ます。 - Linux の場合 : linデ ィ レ ク ト リ に移動 し て、 次の コ マ ン ド を コ マ ン ド ラ イ ンか ら 実 行 し ます。

$ ./implement_gmii.sh (Marvell PHY を使用 し た GMII デザ イ ンの場合)

- Windows の場合 : nt デ ィ レ ク ト リ に移動 し て、implement_gmii.bat を実行 し ます

(Marvell PHY を使用す る GMII デザ イ ンの場合)

d. デザ イ ンの イ ンプ リ メ ン テーシ ョ ンが正常に終了す る と 、次の FPGA プ ロ グ ラ ミ ン グフ ァ イ ルを含むresultsフ ォ ルダーが生成 さ れます。 - FPGA プ ロ グ ラ ミ ン グの ビ ッ ト フ ァ イ ル : <フ ァ イ ル名>.bit (こ の場合、sp605_use_gmii.bit) - SPI x4 フ ラ ッ シ ュ のプ ロ グ ラ ミ ン グ MCS フ ァ イ ル : <フ ァ イ ル名>.mcs (こ の場合、sp605_use_gmii.mcs) 5. FPGA を プ ロ グ ラ ム し ます。 a. SP605 ボー ド が PC シ ス テ ムに装着 さ れた ま ま の場合は、PC シ ス テ ム を シ ャ ッ ト ダ ウ ン し て SP605 ボー ド を取 り 外 し ます。

b. SPI x4 フ ラ ッ シ ュ を使用 し て FPGA をプ ロ グ ラ ムす る には、モー ド ス イ ッ チ (SW1) の設 定を、M0 = 1 お よ び M1 = 0 に変更 し ます。 c. ジ ャ ンパー J46 が ON にな っ てい る こ と (ジ ャ ンパーが所定の位置にあ る こ と) を確認 し ます。 d. SP605 のほかの ス イ ッ チお よ びジ ャ ンパーの設定は、『SP605 ハー ド ウ ェ アユーザーガ イ ド 』 (UG526) に記載 さ れてい る 工場出荷時のデフ ォ ル ト 設定の ま ま に し て く だ さ い。 6. ボー ド を設定 し ます。

a. mini USB ケーブルを USB-JTAG コ ネ ク タ ーに接続 し ます (図 25参照)。USB ケーブルの

も う 一端は、 ザ イ リ ン ク ス のデザ イ ンツールが イ ン ス ト ール さ れてい る PC シ ス テ ム ま た は ラ ッ プ ト ッ プに接続 し ます。 b. 付属の AC 電源ア ダプ タ ーを使用 し て 6 ピ ン コ ネ ク タ ーに 12V 電源を供給 し ます。 7. オン ボー ド の SPI x4 フ ラ ッ シ ュ を プ ロ グ ラ ム し ます。 a. タ ー ミ ナル ウ ィ ン ド ウ を開 き ます。 b. s6_pcie_dma_ddr3_gbe_axi/design/reference/configuration デ ィ レ ク ト リ に 移動 し ます。 c. イ ンプ リ メ ン テーシ ョ ンデ ィ レ ク ト リ か ら こ のデ ィ レ ク ト リ に FPGA プ ロ グ ラ ミ ン グ フ ァ イ ルを コ ピー し ます。 - FPGA プ ロ グ ラ ミ ン グの ビ ッ ト フ ァ イ ル : <フ ァ イ ル名>.bit - SPI x4 フ ラ ッ シ ュ のプ ロ グ ラ ミ ン グ MCS フ ァ イ ル : <フ ァ イ ル名>.mcs d. コ マ ン ド プ ロ ンプ ト で FPGA プ ロ グ ラ ミ ン グ ス ク リ プ ト を実行 し ます。 完了す る ま で約 4 ~ 5 分かか り ます。

- $ impact -batch spi_program.cmd (Linux ベース のマシ ンの場合)

- $ spi_program.bat (Windows ベース のマシ ンの場合)

X-Ref Target - Figure 25

図 25 : USB ケーブルの接続

e. コ マ ン ド シ ェ ルが起動 さ れます。 正常に終了す る と 、 「Programmed successfully」 と い う メ ッ セージが表示 さ れます (図 26参照)。

f. 電源をオ フ に し て電源 コ ネ ク タ ーを取 り 外 し ます。

g. mini USB ケーブルを慎重に取 り 外 し ます。

こ れで Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD が変更 さ れ、SPI x4 フ ラ ッ シ ュ にプ ロ グ ラ ム

さ れま し た。 今後は電源投入時に、 自動的に こ のデザ イ ン で コ ン フ ィ ギ ュ レーシ ョ ン さ れ る よ う にな り ます。

テ ス ト 設定

PC シ ス テ ム にボー ド を装着 し 、 変更 し たデザ イ ン で FPGA を コ ン フ ィ ギ ュ レーシ ョ ンす る には、 13 ページの 「 コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンデモのハー ド ウ ェ ア設定方法」 の手順 1か ら手順 8に従い ます。ソ フ ト ウ ェ アの変更

こ こ では、 ソ フ ト ウ ェ アの変更方法を説明し ます。PCI Express のベンダー ID を変更し ます。 ソ フ ト ウ ェ アデザ イ ン を変更す る には、 次の手順に従っ て く だ さ い。 1. SP605 評価ボー ド が装着 さ れた PC シ ス テ ム を使用 し ます。 2. 付属の USB メ モ リ に保存 さ れた内容を、こ のマシ ンの ロ ーカルデ ィ レ ク ト リ に コ ピー し ます。 a. s6_pcie_dma_ddr3_gbe_axi/driver/xdma/デ ィ レ ク ト リ に移動 し ます。 b. xdma_base.cフ ァ イ ルを編集 し ます。 c. #define PCI_VENDOR_ID_DMA と い う 文字列を検索 し ます。 - こ の行の英数字 10EE を、PCI-SIG か ら 割 り 当て ら れたベン ダー ID に変更 し ます (10EE はザ イ リ ン ク ス のベン ダー ID)。 - こ の値を 19AA に変更 し ます。 - 変更を保存 し て終了 し ます。X-Ref Target - Figure 26

図 26 : SP605 ボー ド のプ ログ ラ ミ ング

3. ド ラ イ バーを コ ンパ イ ル し て、 カーネルモジ ュ ールを挿入 し ます。 a. s6_pcie_dma_ddr3_gbe_axiデ ィ レ ク ト リ に移動 し ます。 b. [s6_trd_driver_build] を ダブル ク リ ッ ク し て、 カーネル オブジ ェ ク ト と GUI を作成 し ま す (図 6参照)。 図 7に示すプ ロ ンプ ト が表示 さ れます。[Run in Terminal] を ク リ ッ ク し て次に進みます。 c. [s6_trd_driver_insert] を ダブル ク リ ッ ク し て、 ド ラ イ バーモジ ュ ールを カーネルに挿入 し ます (図 8参照)。 図 9に示すプ ロ ンプ ト が表示 さ れます。[Run in Terminal] を ク リ ッ ク し て次に進みます。 4. 13 ページの「 コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン スデザ イ ンデモのハー ド ウ ェ ア設定方 法」 の手順 11か ら手順 15に従い、 変更 し た設定を確認 し ます。 5. 24 ページの 「Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン ス デザ イ ンの検証」 の手順 1か ら手順 5に従い、 変更 し たデザ イ ンのパフ ォーマ ン ス を検証 し ます。 6. シ ス テ ム ス テー タ ス を確認 し ます。 [System Status] を ク リ ッ ク し て、 次を確認 し ます。 - PCIe リ ン ク ス テー タ ス、 ベン ダー ID、 デバ イ ス ID 情報 - ベン ダー ID の ス テー タ スは こ の画面に表示 さ れます。 先ほ ど のハー ド ウ ェ ア変更に 伴い、19AA と な っ てい る はずです。 こ れで手順は終了です。 コ ネ ク テ ィ ビ テ ィ TRD を 使用す る Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト の設定がすべて終了 し 、 シ ス テ ムパフ ォーマ ン ス を評価 し ま し た。 ま た、 コ ネ ク テ ィ ビ テ ィ TRD を変更す る ザ イ リ ン ク ス のデザ イ ン フ ロ ーを確認 し ま し た。 こ のデザ イ ンは、PCI Express 用 の 内蔵 ブ ロ ッ ク (x1 PCI Express v1.1 仕様準拠 の コ ン フ ィ ギ ュ レ ー シ ョ ン)、 イ ー サ ネ ッ ト 用 LogiCORE IP、 オン ボー ド の DDR3 メ モ リ と 接続す る 内蔵 メ モ リ コ ン ト ロ ー ラ ーブ ロ ッ ク を中心

に設計 さ れた仮想 FIFO メ モ リ コ ン ト ロ ー ラ ー、 お よ び PCI Express 用のサー ド パーテ ィ 製 DMA

コ ン ト ロ ー ラ ーな ど か ら 構成 さ れてい ます。

次のス テ ッ プ

コ ネ ク テ ィ ビ テ ィ

TRD

モ ジ ュ ール

こ のセ ク シ ョ ンでは、デザ イ ン内の さ ま ざ ま なブ ロ ッ ク におけ る デザ イ ンモジ ュ ール と ソ ースフ ァ イ ル間の相関関係概要を示 し ます。Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD の詳細なブ ロ ッ ク 図は 12 ページの図 1を参照 し て く だ さ い。表 1に、 各モジ ュ ールのデザ イ ン フ ァ イ ルを示 し ます。こ れ ら のモジ ュールの詳細機能は、AXI4 プ ロ ト コルに対応し てい る かに よ っ て、 『Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ ターゲ ッ ト リ フ ァ レ ン スデザ イ ンユーザーガ イ ド (AXI4 バージ ョ ン)』 (UG399) ま たは 『Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン ス デザ イ ンユーザーガ イ ド 』 (UG392) の 「機能の説明」 の章を参照し て く だ さ い。 表 1 : Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD デザイ ン フ ァ イルの構成 モ ジ ュ ール名 ソ ースフ ァ イル/デ ィ レ ク ト リ LogiCORE IP コ ネ ク テ ィ ビ テ ィ TRD ソ ース 最上位モジ ュ ール : Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD s6_pcie_dma_ddr3_gbe_axi (AXI4 プ ロ ト コ ルバージ ョ ン) s6_pcie_dma_ddr3_gbe (AXI4 プ ロ ト コ ル非対応バージ ョ ン) ? PCI Express (x1) s6_pcie_axi_st (AXI4 プ ロ ト コ ルバージ ョ ン) s6_pcie_ip (AXI4 プ ロ ト コ ル非対応バージ ョ ン) ? (PCIe 用エン ド ポ イ ン ト コ ア - CORE Generator 出力)

Packet DMA dma ネ ッ ト リ ス ト

(Northwest Logic 社提供) マルチポー ト 仮想 FIFO memory_app ? メ モ リ コ ン ト ロ ー ラ ー ブ ロ ッ ク mig_axi_mm (AXI4 プ ロ ト コ ルバージ ョ ン) mig_ip (AXI4 プ ロ ト コ ル非対応バージ ョ ン) ? (MIG - CORE Generator 出力) イ ーサネ ッ ト - GMII イ ン タ ーフ ェ イ ス axi_ethernet_v1_00_a (AXI4 プ ロ ト コ ルバージ ョ ン) xps_ll_temac_v2_03_a, network_app (AXI4 プ ロ ト コ ル非対応バージ ョ ン) ? (イ ーサネ ッ ト コ ア- EDK IP の出力) ? イ ーサネ ッ ト 1000BASE-X gig_eth_pcs_pma_ip (AXI4 プ ロ ト コ ル非対応バージ ョ ン) ? (1000BASE-X PCS/PMA - CORE Generator 出力) ? ク ロ ッ キ ン グ、 リ セ ッ ト 、 レ ジ ス タ イ ン タ ーフ ェ イ ス common ? ソ フ ト ウ ェ アデバ イ ス ド ラ イ バー driver ? ソ フ ト ウ ェ ア アプ リ ケーシ ョ ン/GUI xpmon ?

PCI Express

図 27に PCI Express のデザ イ ンモジ ュ ール、図 28にデザ イ ン フ ァ イ ルの構成を示 し ます。

X-Ref Target - Figure 27

図 27 : PCI Express のデザイ ンモ ジ ュ ール

X-Ref Target - Figure 28

図 28 : PCI Express のデザイ ン フ ァ イル

x1 Link f

or

PCI Express

32-bit AXI4-Stream Interf

ace @ 62.5 MHz

GTP T

ransceiv

ers

x1 Endpoint Bloc

k f

or PCI Express v1.1

Wr

apper f

or PCI Express

UG665_42_092810 s6_pcie_dma_ddr3_gbe_axi design coregen_ip s6_pcie_axi_st UG665_43_090810Packet DMA (AXI4

イ ン タ ー フ ェ イ ス

ラ ッ パーに よ る

)

図 29に Packet DMA のデザ イ ンモジ ュ ール、図 30にデザ イ ン フ ァ イ ルの構成を示 し ます。

X-Ref Target - Figure 29

図 29 : Packet DMA のデザイ ンモ ジ ュ ール

X-Ref Target - Figure 30

図 30 : Packet DMA のデザイ ン フ ァ イル Packet DMA C2S S2C C2S S2C Target Interface AXI4-Lite Master axi_str_s2c axi_str_c2s axi_str_s2c axi_str_c2s LocalLink AXI4-Stream Interf ace Adaptation packet_dma_axi

32-bit AXI4-Stream Interf

ace AXI4-Stream Interf ace Adaptation Register Interface ug665_44_092810 LocalLink AXI4-Stream Interf ace Adaptation s6_pcie_dma_ddr3_gbe_axi design ip_cores dma UG665_45_090810

マルチポー ト 仮想

FIFO

および メ モ リ

コ ン ト ロー ラ ー

ブ ロ ッ ク

図 31にマルチポー ト 仮想 FIFO お よ び メ モ リ コ ン ト ロ ー ラ ーブ ロ ッ ク のデザ イ ンモジ ュ ール、

図 32にデザ イ ン フ ァ イ ルの構成を示 し ます。

イ ーサネ ッ ト

図 33に イ ーサネ ッ ト のデザ イ ンモジ ュ ールを示 し ます。

X-Ref Target - Figure 31

図 31 : マルチポー ト 仮想 FIFO および メ モ リ コ ン ト ロー ラ ーブ ロ ッ ク のデザイ ン モ ジ ュ ール

X-Ref Target - Figure 32

図 32 : マルチポー ト 仮想 FIFO および メ モ リ コ ン ト ロー ラ ーのデザイ ン フ ァ イル UG665_46_092910 Virtual FIFO Layer AXI-MM User Interface @62.5 MHz 16-bit DDR3 @667 Mb/s 32-bit AXI4-Stream Interface @62.5 MHz Memory Controller Block MIG Wr apper (AXI4 Protocol V ersion ) SDRAM UG665_47_090810 s6_pcie_dma_ddr3_gbe_axi design source memory_app ip_cores mig_axi_mm

X-Ref Target - Figure 33

図 33 : イ ーサネ ッ ト のデザイ ン モ ジ ュ ール axi_str_s2c AXI Stream 1000BASE-X GMII AXI Stream axi_str_c2s

AXI Stream Control (User Control for CSO)

AXI Slave (Lite)

AXI_Ethernet

MARVELL PHY RJ45

AXI Stream Frame

AXI Stream Control (User Status for CSO)

AXI Stream Frame

Datapath AXI Shim

GTP SFP

PCS PMA

ソ フ ト ウ ェ ア

デバイ ス

ド ラ イバーおよび ソ フ ト ウ ェ ア

ア プ リ ケーシ ョ ン

/GUI

のフ ァ

イルおよびス ク リ プ ト

図 34に、 ソ フ ト ウ ェ アデバ イ ス ド ラ イ バーお よ び ソ フ ト ウ ェ ア アプ リ ケーシ ョ ン/GUI の フ ァ イ ル と ス ク リ プ ト のデザ イ ンモジ ュ ールを示 し ます。図 35には、 それ ら の フ ァ イ ル構成を示 し ます。

X-Ref Target - Figure 34

図 34 : ソ フ ト ウ ェ アデバイ ス ド ラ イバーお よび ソ フ ト ウ ェ ア ア プ リ ケーシ ョ ン/

GUI のデザイ ンモ ジ ュ ール

X-Ref Target - Figure 35

図 35 : ソ フ ト ウ ェ アデバイ ス ド ラ イバーおよび ソ フ ト ウ ェ ア ア プ リ ケーシ ョ ン/GUI の フ ァ イル UG665_50_060110 x1 Link f or PCI Express DMA Driver (Linux) Blockdata Driver (Linux) Ethernet Driver (Linux) GUI TCP Stack UG665_51_090810 s6_pcie_dma_ddr3_gbe_axi driver xblockdata xdma xgbeth html Makefile xpmon s6_trd_driver_build s6_trd_driver_insert s6_trd_driver_remove s6_trd_app_gui

コ ネ ク テ ィ ビ テ ィ

TRD

のシ ミ ュ レーシ ョ ン

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD には、 完全なシ ミ ュ レーシ ョ ン環境が用意 さ れてい ます。

シ ミ ュ レーシ ョ ン環境お よ び関連す る シ ミ ュ レーシ ョ ンフ ァ イ ルの詳細は、AXI4 プ ロ ト コ ルに対 応 し てい る かに よ っ て、 『Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン ス デザ イ ン ユーザーガ イ ド (AXI4 バージ ョ ン)』 (UG399) ま たは 『Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ タ ー ゲ ッ ト リ フ ァ レ ン スデザ イ ンユーザーガ イ ド 』 (UG392) の 「概要」 の章にあ る 「シ ミ ュ レーシ ョ ン」 を参照 し て く だ さ い。

Northwest Logic

社製

DMA IP

の再利用

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト に含まれ る PCI Express 用の Packet DMA Controller IP

コ ア には、Northwest Logic の製品ネ ッ ト リ ス ト 用の フルシー ト の ノ ー ド ロ ッ ク ラ イ セ ン ス が設

定 さ れてい ます。 こ の 32 ビ ッ ト の DMA IP コ アは Spartan-6 FPGA アーキ テ ク チ ャ 向けに最適化 さ れてお り 、 すべての Spartan-6 FPGA を タ ーゲ ッ ト デバ イ ス と で き ます。 ま た、 Spartan-6 FPGA

デザ イ ン であれば、 複数のプ ロ ジ ェ ク ト で再利用可能です。DMA コ ン ト ロ ー ラ ーデザ イ ン には、 次の も のが含まれます。

• シ ミ ュ レーシ ョ ンモデル

• ハー ド ウ ェ ア評価ネ ッ ト リ ス ト (12 時間に制限) • 製品ネ ッ ト リ ス ト フ ァ イ ル

• Northwest Logic 社の DMA Controller IP の ラ イ セ ン ス は、 ノ ー ド ロ ッ ク ラ イ セ ン ス で

1 シー ト です。 • 完全な製品ネ ッ ト リ ス ト に対す る ラ イ セ ン ス は、OMS ラ イ セ ン ス取得シ ス テ ムに よ っ て 取得 し ます。 キ ッ ト 購入時に送付 さ れ る 電子 メ ールに、 製品に関連す る ラ イ セ ン ス フ ァ イ ルのダ ウ ン ロ ー ド についての指示が記載 さ れてい ます。 こ れ ら の製品ネ ッ ト リ ス ト フ ァ イ ルの ロ ッ ク を解除す る ために、 ラ イ セ ン ス フ ァ イ ル処理は必須の手順です。 • Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト を購入する と 、 その ラ イ フ タ イ ムが終了ま で、 DMA Controller IP に関連す る すべてのア ッ プデー ト に対 し て も ラ イ セ ン ス が供与 さ れ ま

す。Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト の ラ イ フ タ イ ムが終了後に、DMA Controller

IP ラ イ セ ン ス の延長、 メ ン テナン ス、 サポー ト 、 ア ッ プ グ レー ド が必要にな っ た場合は、

Northwest Logic 社に直接お問い合わせ く だ さ い。

Northwest Logic 社製 PCIe Packet DMA IP コ アの完全製品版に対す る デザ イ ン変更や追加 ラ イ セ

ン ス取得については、http://www.nwlogic.com/packetdmaを参照 し て く だ さ い。

コ ネ ク テ ィ ビ テ ィ

TRD

の変更

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ TRD は、シ ス テ ム設計者がデザ イ ン を拡張 し た り 変更す る 際の

枠組み と な り ます。 カ ス タ ム IP やデザ イ ン ブ ロ ッ ク を使用す る デザ イ ンの強化、 変更、 再構築に ついては、AXI4 プ ロ ト コ ルに対応 し てい る かに よ っ て、 『Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ タ ー ゲ ッ ト リ フ ァ レ ン スデザ イ ン ユーザー ガ イ ド (AXI4 バージ ョ ン)』 (UG399) ま たは 『Spartan-6

FPGA コ ネ ク テ ィ ビ テ ィ タ ーゲ ッ ト リ フ ァ レ ン ス デザ イ ンユーザーガ イ ド 』 (UG392) の 「TRD

Spartan-6 FPGA IBERT

リ フ ァ レ ン ス

デザイ ン で設計を開始

Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト の CompactFlash には、IBERT (Integrated Bit Error Ratio

Test) の リ フ ァ レ ン スデザ イ ンが含まれてい ます。デモは、2.5Gb/s の ラ イ ン レー ト で動作す る GTP

ト ラ ン シーバーを用いた Spartan-6 LXT デバ イ ス の機能を示す こ と を目的 と し てい ます。

Spartan-6 FPGA IBERT リ フ ァ レ ン スデザ イ ンには次の 3 つの コ ン ポーネ ン ト があ り ます。

• 2.5Gb/s で動作す る Spartan-6 FPGA GTP ト ラ ン シーバー

• IBERT v2.0 リ フ ァ レ ン スデザ イ ン (IP生成には CORE Generator ツールを使用)

デザ イ ン には PRBS (疑似乱数ビ ッ ト 列) パ タ ーン ジ ェ ネ レー タ ーお よ びチ ェ ッ カー も 含 ま れ ます。

• IBERT リ フ ァ レ ン スデザ イ ンでは、 次のチ ャ ネルを介 し て Spartan-6 FPGA LX45T の 4 つの

GTP ト ラ ン シーバーへア ク セ ス し ます。 • SFP • SMA • PCIe • FMC_LPC (ト ラ ン シーバー出力は FMC-LPC コ ネ ク タ ーの ピ ンに接続 さ れてい ます) メ モ : デモでは、SMA 外部ループバ ッ ク を含む場合のみ示 し てい ます。

IBERT

デモのハー ド ウ ェ ア設定方法

こ こ では、IBERT リ フ ァ レ ン スデザ イ ン のデモ を実行す る ためのハー ド ウ ェ ア設定方法を説明 し

ます。IBERT リ フ ァ レ ン スデザ イ ンは、CompactFlash に FPGA プ ロ グ ラ ミ ン グ フ ァ イ ル と し て

格納 さ れてい ます。

1. デモ を実行す る には次が必要です。

• Spartan-6 FPGA コ ネ ク テ ィ ビ テ ィ キ ッ ト

• USB ポー ト を搭載 し た PC シ ス テ ム

• デ ィ ス プ レ イ 、 キーボー ド 、 マ ウ ス

• PC シ ス テ ムに イ ン ス ト ール さ れた ISE Design Suite 2. ボー ド 設定 I – SP605 ボー ド に CompactFlash を装着 し ます。

キ ッ ト に付属す る CompactFlash を使用 し ます (図 36参照)。

X-Ref Target - Figure 36

図 36 : キ ッ ト 付属の CompactFlash の SP605 ボー ド への装着

3. ボー ド 設定 II – CompactFlash か ら IBERT デザ イ ン を読み込むために DIP ス イ ッ チ S1 を設定 し ます (図 37参照)。 a. S1_1 : ON b. S1_2 : OFF c. S1_3 : OFF d. S1_4 : ON 4. ボー ド 設定 III – SP605 ボー ド に USB ケーブルを接続 し ます (図 38参照)。

a. 付属の USB Type-A/Mini-B ケーブルを SP605 ボー ド の USB JTAG コ ネ ク タ ーに接続 し

ます。

b. ケーブルの も う 一端は PC シ ス テ ムに接続 し ます。

X-Ref Target - Figure 37

図 37 : CompactFlash 内の IBERT デザイ ンによ る FPGA の設定

X-Ref Target - Figure 38

図 38 : SP605 ボー ド の USB-JTAG コ ネ ク タ ーへの USB ケーブル接続

UG665_28_112909

5. ボー ド 設定 IV – SMA ケーブルを使用 し て SMA ピ ンに接続 さ れてい る ト ラ ン シーバーチ ャ ネルをループバ ッ ク し ます。

a. J32 と J34 を接続 し ます (図 39参照)。

b. J33 と J35 を接続 し ます (図 40参照)。

X-Ref Target - Figure 39

図 39 : SMA ト ラ ン シーバーチ ャ ネルの外部ループバ ッ ク 設定 - I

X-Ref Target - Figure 40

図 40 : SMA ト ラ ン シーバーチ ャ ネルの外部ループバ ッ ク 設定 - II

UG665_30_112909

6. ボー ド 設定 V – 電源 コ ネ ク タ ーを接続 し ます。

a. 付属の電源の コ ネ ク タ ーを図 41に示す よ う に SP605 ボー ド に接続 し ます。

b. 電源ス イ ッ チ SW2 を ON の位置に切 り 替え ます。

7. ボー ド 設定 VI – IBERT デザ イ ン を CompactFlash か ら FPGA に読み込みます。

a. ス イ ッ チ SW9 を押 し て、CompactFlash か ら コ ン フ ィ ギ ュ レーシ ョ ン を開始 し ます。

b. DONE LED の点灯に よ って、FPGA に IBERT デザ イ ンが読み込まれた こ と を確認し ます。

X-Ref Target - Figure 41

図 41 : SP605 ボー ド への電源投入

X-Ref Target - Figure 42

図 42 : IBERT リ フ ァ レ ン スデザイ ンのプ ロ グ ラ ムが完了 し た FPGA

UG665_32_121509

8. IBERT リ フ ァ レ ン ス デザ イ ン フ ァ イ ルは、 キ ッ ト に付属す る USB メ モ リ に保存 し て提供 さ れます。 付属の USB メ モ リ の内容を コ ピー し ます。 a. USB メ モ リ を PC シ ス テ ムの USB コ ネ ク タ ーに挿入 し ます。 b. USB ド ラ イ ブがオペレーテ ィ ン グ シ ス テ ム でマ ウ ン ト さ れ る ま で待ち ます。 マ ウ ン ト さ れ る と 、 デス ク ト ッ プ上にア イ コ ンが表示 さ れます。 c. USB ド ラ イ ブに移動 し て、SP605_Ibert_Reference_Design フ ォ ルダーを ロ ーカル デ ィ レ ク ト リ に コ ピー し ます。 d. USB メ モ リ を取 り 外 し ます。

9. ChipScope Pro Analyzer ウ ィ ン ド ウ を開 き ます。

a. [すべてのプ ロ グ ラ ム] → [Xilinx ISE Design Suite] → [ChipScope Pro] → [Analyzer] を ク リ ッ ク し ます。

b. [Open Cable] ボ タ ン を ク リ ッ ク し ます (図 43参照)。

10. ChipScope Pro Analyzer のプ ロ ジ ェ ク ト を開き ます (図 44参照)。

a. [File] → [Open Project] を ク リ ッ ク し ます。

b. SP605_Ibert_Reference_Designフ ォ ルダーに移動 し ます。

c. sp605_ibert.cpj を ク リ ッ ク し ます。

X-Ref Target - Figure 43

図 43 : ChipScope Pro Analyzer ウ ィ ン ド ウの起動

X-Ref Target - Figure 44

![図 12 : [Hardware] タ ブ](https://thumb-ap.123doks.com/thumbv2/123deta/5999222.578190/20.918.374.703.112.443/図12Hardwareタブ.webp)