© Copyright 2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the

概要

放送業界向けの映像機器には、SMPTE (Society of Motion Picture and Television Engineers) SDI (Serial Digital Interface) 規格が広 く 使用 さ れてい ます。 こ の イ ン タ ーフ ェ イ ス は、 放送局ス タ ジオや映像制作 会社で使用 さ れてお り 、 非圧縮のデジ タ ル映像 と 多重音声チ ャ ネルな ど の埋め込まれた補助デー タ を共 に伝送 し ます。ザ イ リ ン ク ス の SMPTE SD/HD/3G-SDI LogiCORE™ IP は、 デバ イ ス固有の制御機能を持た ない一般 的な SDI 受信/送信デー タ パ ス です。 こ のアプ リ ケーシ ョ ン ノ ー ト では、 完全な SDI イ ン タ ーフ ェ イ ス を構築す る ために、Artix®-7 FPGA GTP ト ラ ン シーバー と SMPTE SD/HD/3G-SDI LogiCORE IP を 合わせて使用す る ための制御 ロ ジ ッ ク を含むモジ ュ ールを提供 し ます。 ま た、 ザ イ リ ン ク ス の Artix-7 FPGA AC701 評価ボー ド を使用す る SDI の設計例をい く つか紹介 し ます。

こ のアプ リ ケーシ ョ ン ノ ー ト で使用 さ れ る 用語については、66ページの 「用語解説」 を参照 し て く だ さ い。SMPTE 規格は69ページの 「参考資料」 に一覧表示 し 、SMPTE の資料番号 も 記載 し てい ます。

は じ めに

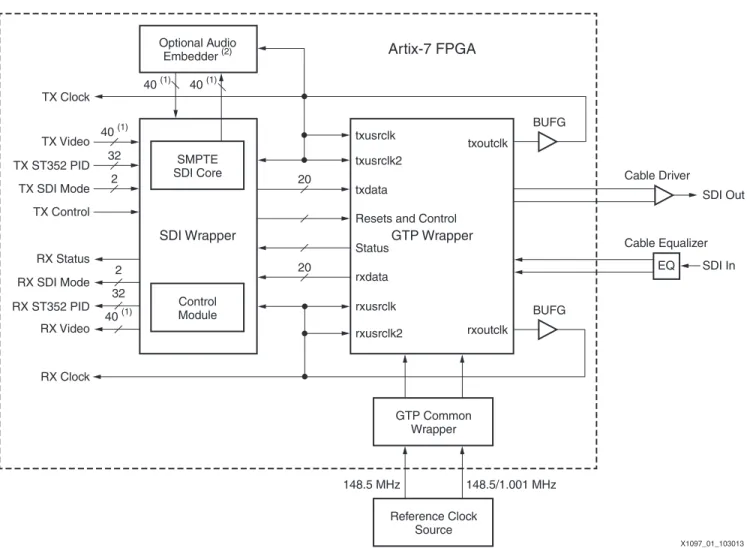

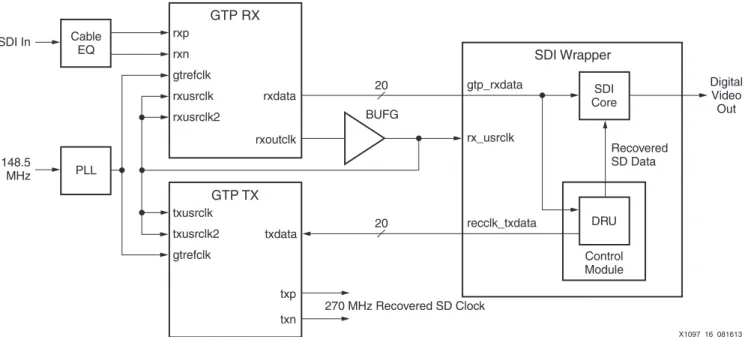

ザ イ リ ン ク ス の SMPTE SD/HD/3G-SDI LogiCORE IP (以下、SDI コ ア と い う) は、Artix-7 FPGA GTPト ラ ン シーバー と 接続す る こ と で、SMPTE SD-SDI、HD-SDI、 お よ び 3G-SDI 規格 を サ ポー ト す る SDI イ ン タ ー フ ェ イ ス を実装で き ま す。SDI コ ア と GTP ト ラ ン シーバーを接続 し て完全な SDI イ ン タ ーフ ェ イ ス を実装す る には、 ロ ジ ッ ク を追加す る 必要が あ り ま す。 こ のア プ リ ケーシ ョ ン ノ ー ト で は、 こ の付加的な制御 ロ ジ ッ ク と イ ン タ ーフ ェ イ ス ロ ジ ッ ク について説明 し 、 必要 と な る 制御モジ ュ ー ルお よ び イ ン タ ーフ ェ イ スモジ ュ ールを Verilog と VHDL の両言語で提供 し ます。 デバ イ ス固有の制御 ロ ジ ッ ク の主な機能は次の と お り です。 • GTP ト ラ ン シーバーの リ セ ッ ト ロ ジ ッ ク • 3 つの SDI 規格をサポー ト す る ために、GTP RX/TX シ リ アル ク ロ ッ ク 分周器を動的に切 り 換え る 機能 • HD-SDI お よ び 3G-SDI 規格の 2 つの異な る ビ ッ ト レー ト をサポー ト す る ために、TX の基準 ク ロ ッ ク を動的に切 り 換え る 機能 • 1.485Gb/s お よ び 1.485/1.001Gb/s (HD-SDI モー ド の場合) • 2.97Gb/s お よ び 2.97/1.001Gb/s (3G-SDI モー ド の場合) • SD-SDI モー ド の場合にデー タ を回復 さ せ る デー タ リ カバ リ ユニ ッ ト • RX で受信 し てい る ビ ッ ト レー ト (1/1 ビ ッ ト レー ト 信号ま たは 1/1.001 ビ ッ ト レー ト 信号) を判 断す る RX ビ ッ ト レー ト 検出機能 こ のアプ リ ケーシ ョ ン ノ ー ト は、GTP ト ラ ン シーバー用制御モジ ュ ールの イ ン ス タ ン ス と SDI コ アの イ ン ス タ ン ス、 お よ びそれ ら に必要な接続を含む ラ ッ パーフ ァ イ ル も 提供 し てい ます。 こ れを利用す る こ と で、SDI イ ン タ ーフ ェ イ ス を簡単に構築で き ます。 こ のアプ リ ケーシ ョ ン ノ ー ト で使用す る 用語を次に示 し ます。図1の簡略ブ ロ ッ ク 図では、 さ ま ざ ま な コ ン ポーネ ン ト を組み合わせて SDI イ ン タ ーフ ェ イ ス を形成 し てい る こ と を示 し てい ます。

• SDI コ ア と は、CORE Generator™ ツールま たは Vivado® IP カ タ ロ グで生成 さ れ る SMPTE SD/HD/3G-SDI コ アの こ と をいい ます。

XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 2 • 制御モジ ュ ール と は、GTP ト ラ ン シーバーが SMPTE SDI コ ア を使用 し て SDI イ ン タ ーフ ェ イ ス を実装す る 際に必要 と な る さ ま ざ ま なデバ イ ス固有の機能を実装す る モジ ュ ールです。 こ のアプ リ ケーシ ョ ン ノ ー ト では、 制御モジ ュ ールを ソ ース コ ー ド 形式で提供 し ます。

• SDI ラ ッ パーは、SDI コ アや制御モジ ュ ールを イ ン ス タ ン シエー ト し て相互接続す る ための ラ ッ パーモジ ュ ールです。 こ のアプ リ ケーシ ョ ン ノ ー ト では、SDI ラ ッ パーを ソ ース コ ー ド 形式で提 供 し ます。

• GTP ラ ッ パーは、7 Series FPGAs Transceivers Wizard (CORE Generator お よ び Vivado IP カ タ ロ グで利用可能) で生成 さ れた GTP ト ラ ン シーバー用の ラ ッ パーフ ァ イ ルです。

• GTP コ モン ラ ッ パーは、7 Series FPGAs Transceivers Wizard で生成 さ れた GTP ト ラ ン シーバー コ モン ブ ロ ッ ク 用の ラ ッ パーフ ァ イ ルです。 こ の ラ ッ パーフ ァ イ ルには、 ク ワ ッ ド 内の GTP ト ラ ン シーバーにシ リ アルク ロ ッ ク を供給す る 2 つの PLL が含まれてい ます。 図1について説明 し ます。 1. こ れ ら の 40 ビ ッ ト バ ス は、 実際には 4 つのバ ス で構成 さ れてお り 、10 ビ ッ ト 幅のバ ス がぞれぞれ 異な る SDI デー タ ス ト リ ーム を伝搬 し ます。 ア ク テ ィ ブなデー タ ス ト リ ーム数、 つま り バ ス数は、 SDI モー ド に よ っ て異な り ます。 た と えば、SD-SDI モー ド では 10 ビ ッ ト のデー タ ス ト リ ームが 1 つ し かア ク テ ィ ブにな り ませんが、HD-SDI モー ド ではそれが 2 つア ク テ ィ ブにな り ます。 2. オプシ ョ ンのオーデ ィ オ エンベ ッ ダーは単独コ アであ り 、SDI コ アには含まれてい ません。 ま た、 こ のアプ リ ケーシ ョ ン ノ ー ト では説明 し てい ません。 X-Ref Target - Figure 1

図 1 : 完成 し た SDI RX/TX イ ン タ ー フ ェ イ スのブ ロ ッ ク図 X1097_01_103013 SDI Out BUFG BUFG SMPTE SDI Core Optional Audio Embedder(2)

SDI Wrapper GTP Wrapper

Artix-7 FPGA

Control Module Reference Clock Source Cable Driver txusrclk rxusrclk txusrclk2 rxusrclk2 txdata rxdataResets and Control Status txoutclk rxoutclk Cable Equalizer SDI In EQ 40 (1) 148.5 MHz 148.5/1.001 MHz 32 2 20 40 (1) TX Clock RX Clock TX Video RX Video TX ST352 PID RX ST352 PID TX SDI Mode TX Control RX Status RX SDI Mode 40 (1) 40 (1) 32 2 20 GTP Common Wrapper

該当 し ま せん。 異な る GTP ト ラ ン シーバーの RX/TX ユニ ッ ト を同 じ SDI ラ ッ パーへ接続で き ま す。 SDI RX のみ、 あ る いは SDI TX のみ必要な場合は、 合成段階で制御モジ ュ ール と SDI コ アの未使用部 分が最適化に よ っ て除去 さ れます。

こ のアプ リ ケーシ ョ ン ノ ー ト では、SDI コ ア を使用す る 2 つのデモアプ リ ケーシ ョ ン例を紹介 し ます。 こ れ ら の ア プ リ ケーシ ョ ン は AC701 評価ボー ド を使用 し て実行 さ れ ま す。SDI の物理的な イ ン タ ー フ ェ イ ス と し て、Inrevium 社製 SDI FPGA メ ザニ ン カー ド (FMC) も 必要です。

Artix-7

GTP

ト ラ

ン シーバーを使用

し て

SDI

イ ン タ ー

フ ェ イ ス を実現

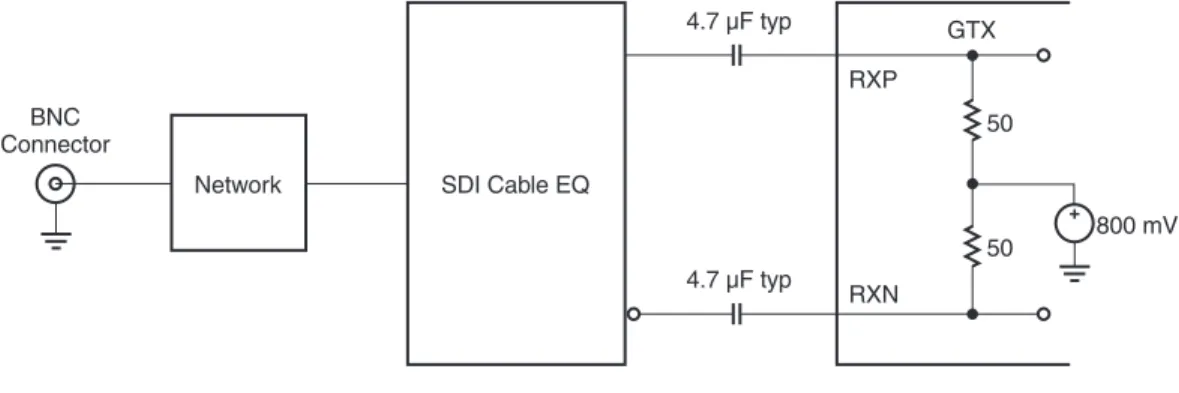

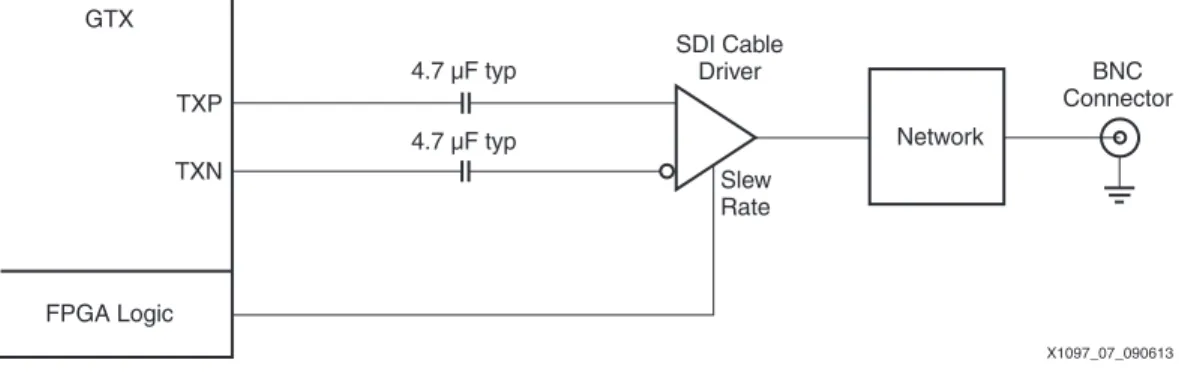

こ のセ ク シ ョ ン では、 『7シ リ ーズFPGA GTP ト ラ ン シーバーユーザーガ イ ド 』 (UG482) を補足す る 内容を提供 し ます。 特に SDI アプ リ ケーシ ョ ンにおいて重要な GTP ト ラ ン シーバーの特長お よ び動作 要件について説明 し ます。 こ のアプ リ ケーシ ョ ン ノ ー ト の GTP ト ラ ン シーバーポー ト に関 し ては、 『7シ リ ーズFPGA GTP ト ラ ン シーバーユーザーガ イ ド 』 で使用 さ れてい る 命名規則に従い ます。 こ の規則は、 ポー ト のベース ネー ム にのみ使用 し ます。GTP ラ ッ パーの作成に 7 Series FPGAs Transceivers Wizard (以下、 ウ ィ ザー ド と い う) を使用 し た場合、 すべての入力ポー ト には、 名前の後ろ に _in が追加 さ れ、 すべての出力ポー ト には _out が追加 さ れ ま す。 た と えば、 こ のアプ リ ケーシ ョ ン内で txrate ポー ト 名について言及す る 場合、GTP ラ ッ パー内での実際の名前は、GTP ト ラ ン シーバーの txrate ポー ト では txrate_in と な り ま す。 バージ ョ ン 3.0 以降の ウ ィ ザー ド では、 最上位 GTP ラ ッ パーのすべての GTP ポー ト 名が小文字で示 さ れますが、 こ れは Vivado ツールを使用 し た場合のみです。ISE® ツールバージ ョ ンの ウ ィ ザー ド では、 ポー ト 名はすべて大文字で示 さ れます。 こ のアプ リ ケーシ ョ ン ノ ー ト の GTP ポー ト 名はすべて小文字 で示 さ れてい ます。 デモン ス ト レーシ ョ ンの ソ ース コ ー ド フ ァ イ ルは、Vivado お よ び ISE の両ツール と 互換性があ る バージ ョ ンで提供 さ れます。 ま た、GTP ポー ト 名についてはツールに応 じ て適宜大文字 ま たは小文字が使用 さ れます。 バージ ョ ン 3.0 以降の ウ ィ ザー ド では、GTP ク ワ ッ ド 用の 2 つの PLL を含む GTP コ モン ラ ッ パーは 独立 し てお り 、 メ イ ン の GTP ラ ッ パーには含ま れ ません。 こ れは、Vivado ツールの場合のみで、ISE ツールには該当 し ません。 GTP ト ラ ン シーバーを使用す る アプ リ ケーシ ョ ンには、 さ ま ざ ま な ク ロ ッ ク があ り ます。 デー タ ス ト リ ーム にデー タ を追加 し た り 削除 し て ク ロ ッ ク を補正で き ない SDI プ ロ ト コ ルの場合は、 アプ リ ケー シ ョ ン内で ク ロ ッ ク が ど の よ う に生成お よ び使用 さ れ る かに細心の注意が必要です。GTP ト ラ ン シー バーを駆動す る には基準 ク ロ ッ ク が必要です。GTP ク ワ ッ ド にあ る PLL (位相 ロ ッ クループ) が基準 ク ロ ッ ク を 使用 し て、 各 ト ラ ン シ ーバーの受信部お よ び送信部用の シ リ ア ル ク ロ ッ ク を 生成 し ま す。 4ページの 「GTP 基準 ク ロ ッ ク 」 で詳 し く 説明す る よ う に、GTP ト ラ ン ス ミ ッ タ ーのシ リ アルビ ッ ト レー ト は、 供給 さ れ る 基準 ク ロ ッ ク の整数倍 と な り ます。 さ ら に、SDI ト ラ ン ス ミ ッ タ ーデー タ パ ス の 入力に与え ら れ る ビデオデー タ レー ト は、GTP ト ラ ン ス ミ ッ タ ーで使用 さ れ る 基準 ク ロ ッ ク 周波数 と 正確に一致す る (ま たは正確な整数倍 と な る) 必要があ り ます。 し たがっ て、送信 さ れ る ビデオス ト リ ー ムのデー タ レー ト へ周波数が確実に固定す る よ う に、 ト ラ ン ス ミ ッ タ ーの基準 ク ロ ッ ク を生成す る 設計 を行 う 必要があ り ます。 GTP ト ラ ン ス ミ ッ タ ーは、 その txoutclk ポー ト へ供給 さ れ る デー タ の ワ ー ド レー ト と ま っ た く 同 じ 周 波数の ク ロ ッ ク を txdata に出力 し ま す。 こ の txoutclk は、 シ リ アル ク ロ ッ ク が PLL に よ っ て ワ ー ド レー ト と 等 し く な る よ う に分周 さ れ る こ と で、GTP ト ラ ン ス ミ ッ タ ー内で生成 さ れます。 大抵のアプ リ ケーシ ョ ン では、GTP ト ラ ン シーバーか ら の txoutclk は、 グ ロ ーバル (BUFG) ま た は リ ージ ョ ナル (BUFR) ク ロ ッ ク バ ッ フ ァ ーを介 し 、 その後 SDI ト ラ ン ス ミ ッ タ ーデー タ パ スお よ び GTP ト ラ ン ス ミ ッ タ ーの txusrclk お よ び txusrclk2 ク ロ ッ ク 入力への ク ロ ッ ク 供給に使用 さ れ ます。txoutclk か ら 直 接派生 し た ク ロ ッ ク 以外 も 、SDI ト ラ ン ス ミ ッ タ ーデー タ パ スお よ び GTP ト ラ ン ス ミ ッ タ ーの txusrclk ポー ト と txusrclk2 ポー ト の ク ロ ッ ク ソ ー ス と し て使用で き ま す。GTP ト ラ ン ス ミ ッ タ ーの浅い TX バ ッ フ ァ ーは、txdata ポー ト に供給 さ れ る デー タ と GTP ト ラ ン ス ミ ッ タ ーの内部 ク ロ ッ ク 間の位相差XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 4 を許容 し ます。 し か し 、 入力 さ れ る デー タ と GTP ト ラ ン ス ミ ッ タ ーの内部 ク ロ ッ ク 周波数 (txoutclk で 表 さ れ る) 間の周波数差は、即座に TX バ ッ フ ァ ーのア ン ダーフ ロ ー/オーバーフ ロ ーを引 き 起 こ すため、 GTP ト ラ ン ス ミ ッ タ ーで生成 さ れ る シ リ アルビ ッ ト ス ト リ ームにエ ラ ーが生 じ ます。し たがっ て、GTP ト ラ ン ス ミ ッ タ ーの txdata ポー ト へ供給 さ れ る デー タ レー ト (txusrclk お よ び txusrclk2 ク ロ ッ ク の周 波数で表 さ れ る) と GTP ト ラ ン ス ミ ッ タ ーの内部デー タ レー ト (ト ラ ン ス ミ ッ タ ーの基準 ク ロ ッ ク で設 定 さ れ、xoutclk 周波数で表 さ れ る) は、 正確に一致 さ せ る 必要があ り ます。 ただ し 、GTP レ シーバーの基準 ク ロ ッ ク は入力 さ れ る SDI 信号のビ ッ ト レー ト と 正確な関係を持つ必 要はあ り ません。 こ れは、GTP レ シーバーの ク ロ ッ ク デー タ リ カバ リ (CDR) ユニ ッ ト が、 基準 ク ロ ッ ク 周波数に よ る 設定どお り に公称ビ ッ ト レー ト か ら 最大 ±1250ppm で ビ ッ ト レー ト を受信で き る ため です。 こ のため、 入力 さ れ る SDI 信号 と 正確な周波数関係を持たない ロ ーカルのオシ レー タ ーで レ シー バー基準 ク ロ ッ ク が生成可能にな り ます。GTP レ シーバーは、 入力 さ れ る SDI ビ ッ ト レー ト に周波数 ロ ッ ク さ れた リ カバ リ ク ロ ッ ク を生成 し ます。 こ の ク ロ ッ ク は、GTP ト ラ ン シーバーの rxoutclk ポー ト の出力です。 こ のアプ リ ケーシ ョ ン ノ ー ト で後ほ ど詳 し く 説明 し ますが、rxoutclk は、HD-SDI お よ び 3G-SDI 信号を受信す る 際の真の リ カバ リ ク ロ ッ ク であ り 、SD-SDI 信号を受信す る 際の ク ロ ッ ク で はあ り ません。 通常、rxoutclk は、 グ ロ ーバルま たは リ ージ ョ ナルバ ッ フ ァ ーを介 し 、 その後 GTP レ シーバーの rxusrclk お よ び rxusrclk2 ポー ト へ供給 さ れて、SDI レ シーバーデー タ パ ス用の ク ロ ッ ク と し て使用 さ れます。 SDI ア プ リ ケーシ ョ ン には、 も う 1 つ ク ロ ッ ク が必要です。 こ れは フ リ ー ラ ン ニ ン グ の固定周波数 ク ロ ッ ク であ り 、DRP ト ラ ン シーバーの DRP (ダ イ ナ ミ ッ ク リ コ ン フ ィ ギ ュ レーシ ョ ンポー ト) 用 ク ロ ッ ク と し て使用 さ れます。 通常、 こ れ と 同 じ ク ロ ッ ク が SDI ラ ッ パーの制御モジ ュ ールに供給 さ れ、 タ イ ミ ン グ制御に使用 さ れます。 ザ イ リ ン ク ス では 10MHz 以上にす る こ と を推奨 し てい ます。 こ の ク ロ ッ ク の周波数は、SDI アプ リ ケーシ ョ ンのその他の ク ロ ッ ク やデー タ レー ト に対 し て特定の関連性を持つ 必要はあ り ません。SDI モー ド を変更 し た際に、 こ の ク ロ ッ ク の周波数を変更 し ないで く だ さ い。 常に 同 じ 公称周波数で動作す る 必要があ り ます。 ま た、SDI アプ リ ケーシ ョ ンがア ク テ ィ ブな間は停止 さ せ る こ と も で き ません。 こ の ク ロ ッ ク は、 デバ イ ス内のすべての SDI イ ン タ ーフ ェ イ ス で使用可能です。

GTP

基準ク ロ ッ ク

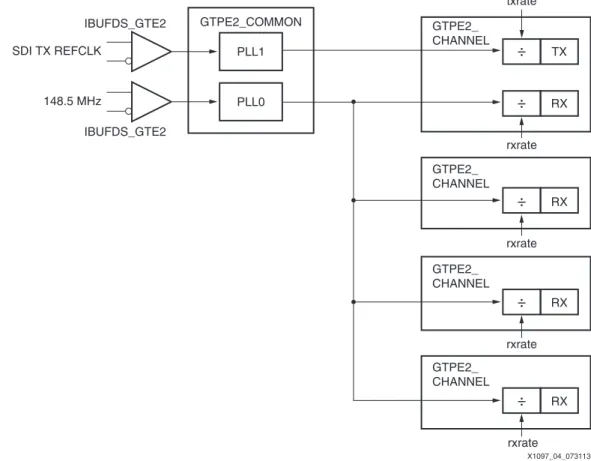

Artix-7 FPGA GTP ト ラ ン シ ー バ ー は、 ク ワ ッ ド に 分 け ら れ て い ま す。 各 ク ワ ッ ド に は 4 つ の GTPE2_CHANNEL ト ラ ン シ ー バ ー プ リ ミ テ ィ ブ、 お よ び 2 つ の PLL (PLL0 と PLL1) を 含 む GTPE2_COMMON プ リ ミ テ ィ ブが 1 つあ り ます (図2を参照)。 こ れ ら 2 つの PLL か ら の ク ロ ッ ク の みが、その ク ワ ッ ド にあ る 4 つの レ シーバー と 4 つの ト ラ ン シーバーすべてに対 し てシ リ アル ク ロ ッ ク と し て使用で き ます。後で説明 し ますが、こ れに よ っ て SDI アプ リ ケーシ ョ ンに一部の限界が生 じ ます。 ク ワ ッ ド 内の各レ シーバーお よ び ト ラ ン シーバーユニ ッ ト では、PLL0 ま たは PLL1 のいずれかか ら の ク ロ ッ ク を使用す る か を個別に設定で き ます。 さ ら に、 こ れ ら のユニ ッ ト はシ リ アルク ロ ッ ク ソ ー ス を PLL0 と PLL1 間で動的に切 り 替え可能です。 こ の動的切 り 換え機能は、SDI アプ リ ケーシ ョ ンに特 に有用です。一般的な SDI ア プ リ ケーシ ョ ン では、5 つの異な る ビ ッ ト レ ー ト を サポー ト す る ために GTP ト ラ ン シーバーが必要です。 • 270Mb/s (SD-SDI の場合) • 1.485Gb/s (HD-SDI の場合) • 1.485/1.001Gb/s (~ 1.4835Gb/s) (HD-SDI の場合) • 2.97Gb/s (3G-SDI の場合) • 2.97/1.001Gb/s (~ 2.967Gb/s) (3G-SDI の場合) GTP ト ラ ン シーバーの RX 部に含ま れ る CDR ユニ ッ ト は、 基準周波数か ら 最大 ±1250ppm の ビ ッ ト レー ト を受信で き ます。HD-SDI の 2 つのビ ッ ト レー ト の差は正確に 1000ppm であ り 、 同様に 2 つの 3G-SDI ビ ッ ト レー ト の差 も 1000ppm であ る ため、1 つの基準 ク ロ ッ ク 周波数を用いて 5 つすべての SDI ビ ッ ト レー ト を受信で き ます。 一方、GTP ト ラ ン シーバーの TX 部では、5 つすべての SDI ビ ッ ト レー ト をサポー ト す る ために 2 つ の基準周波数が必要です。 こ れは、 ト ラ ン ス ミ ッ タ ーは通常は供給 さ れ る 基準 ク ロ ッ ク 周波数の正確な SDI 2 図 2 : GTP ト ラ ン シーバーの ク ワ ッ ド コ ン フ ィ ギ ュ レーシ ョ ン X1097_02_081513 RX TX RX TX PLL0 RX TX GTPE2_COMMON REFCLK Distribution PLL1 RX TX IBUFDS_GTE2 IBUFDS_GTE2

XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 6 ク ロ ッ ク を GTP ク ワ ッ ド へ供給 し ます。 こ れ ら の ク ロ ッ ク のいずれか一方を RX の基準 ク ロ ッ ク と し て使用 し 、 両方を TX の基準 ク ロ ッ ク と し て使用 し ま す。 通常、2 つの基準 ク ロ ッ ク の組み合わせは、 148.5MHz と 148.5/1.001MHz です。 GTP の基準 ク ロ ッ ク ソ ース は、アプ リ ケーシ ョ ンに よ っ て大 き く 異な り ます。 レ シーバーの基準 ク ロ ッ ク ソ ース は、入力 さ れ る SDI ビ ッ ト レー ト と 正確に一致す る 必要がないため、ロ ーカルのオシ レー タ ー で対応で き ます。 一方、GTP ト ラ ン ス ミ ッ タ ーの ラ イ ン レー ト は、 常に基準 ク ロ ッ ク 周波数の整数倍 であ る ため、 ト ラ ン ス ミ ッ タ ーの基準 ク ロ ッ ク 周波数は、 送信 さ れ る デー タ のデー タ レー ト と 正確な関 係を持つ必要があ り ます。 ほ と ん ど の場合、 ト ラ ン ス ミ ッ タ ーの基準 ク ロ ッ ク はゲ ン ロ ッ ク PLL で生 成 さ れ る ため、 ス タ ジオのビデオ基準信号か ら GTP ト ラ ン ス ミ ッ タ ーラ イ ン レー ト を生成 し ます。 ア プ リ ケーシ ョ ン ノ ー ト に含まれ る SDI パ ス ス ルーデモン ス ト レーシ ョ ン な ど の特殊な場合、 ト ラ ン ス ミ ッ タ ーラ イ ン レー ト は、SDI 信号を受信 し てい る GTP レ シーバーの リ カバ リ ク ロ ッ ク か ら 生成 さ れ ま す。 その よ う な場合、 ト ラ ン ス ミ ッ タ ーの基準 ク ロ ッ ク と し て使用す る 前に、 外部 PLL を使用 し て リ カバ リ ク ロ ッ ク のジ ッ タ ーを軽減す る 必要があ り ます。 一般的な SDI アプ リ ケーシ ョ ンでは、SDI イ ン タ ーフ ェ イ ス を実装 し てい る 各 ク ワ ッ ド 内で 2 つの基準 ク ロ ッ ク の一方を PLL0 へ接続 し 、 も う 一方を PLL1 へ接続 し ま す。 ク ワ ッ ド 内に あ る 各 ト ラ ン シー バーの RX ユニ ッ ト は、 いずれかの PLL か ら の ク ロ ッ ク を使用す る よ う に設定で き ます。TX ユニ ッ ト は、 その と き に必要な ビ ッ ト レー ト に基づいて、PLL0 か ら の ク ロ ッ ク と PLL1 か ら の ク ロ ッ ク を動的 に切 り 換え る こ と がで き ます。GTP txsysclksel ポー ト を使用 し て TX ユニ ッ ト の ク ロ ッ ク ソ ー ス を 2 つの PLL か ら 選択 し ます。図3に、 こ の一般的な SDI アプ リ ケーシ ョ ンの コ ン フ ィ ギ ュ レーシ ョ ン を 示 し ます。 こ の図では、 イ ンプ リ メ ン テーシ ョ ン で動的に使用 さ れないマルチプ レ ク サーを配線に置 き 換えてお り 、 ク ワ ッ ド 間の基準 ク ロ ッ ク 配線は表示 し てい ません。

ま た、 各 GTP RX お よ び TX ユニ ッ ト には、 選択 し た ク ロ ッ ク を指定可能な 2 の累乗の整数値で分周 す る シ リ アルク ロ ッ ク 分周器があ り ます。 こ れに よ っ て、 た と えば、 ク ワ ッ ド 内のすべての RX ユニ ッ ト は片方の PLL か ら の同 じ ク ロ ッ ク 周波数を使用 し なが ら も 、 異な る シ リ アルク ロ ッ ク 分周値を用い て異な る ラ イ ン レー ト で動作で き る よ う にな り ます。3G-SDI ビ ッ ト レー ト は HD-SDI ビ ッ ト レー ト の 2 倍の速度 と な る ため、 こ の機能は SDI イ ン タ ーフ ェ イ ス に非常に有効です。270Mb/s SD-SDI の場 合、GTP ト ラ ン シーバーは 11 倍のオーバーサ ン プ リ ン グテ ク ニ ッ ク に よ っ て 3G-SDI ラ イ ン レー ト で動作 し ます。 こ のため、 各 RX ユニ ッ ト 内で 2 の累乗値で指定 し た異な る 2 つの分周器を使用す る こ と で、片方の PLL か ら 供給 さ れ る 1 つの RX ク ロ ッ ク 周波数ですべての SDI ビ ッ ト レー ト を受信可能 です。 ま た、TX ユニ ッ ト で も 、2 の累乗値で指定 し た異な る 2 つの分周器を用いて ク ロ ッ ク ソ ース を 分周で き る ため、 基準 ク ロ ッ ク 周波数を 2 つ使用す る だけですべての SDI ビ ッ ト レー ト の送信が可能 です。RX お よ び TX ユニ ッ ト のシ リ アル ク ロ ッ ク 分周器の値は、 各 GTP ト ラ ン シーバーの rxrate お よ び txrate ポー ト を利用 し て動的に変更可能です。 図3に示す コ ン フ ィ ギ ュ レーシ ョ ンは、 ほ と ん ど の SDI アプ リ ケーシ ョ ン に最適な ソ リ ュ ーシ ョ ン で す。 その理由は、 次の と お り です。 • レ シーバーは、1 つの固定 さ れた基準 ク ロ ッ ク 周波数か ら すべての SDI ビ ッ ト レー ト を受信で き 、 片方の PLL が ク ワ ッ ド 内のすべての レ シーバーへ基準 ク ロ ッ ク か ら 生成 さ れたシ リ アル ク ロ ッ ク を供給 し ます。 図 3 : SDI 用の GTP 基準 ク ロ ッ クのイ ン プ リ メ ン テーシ ョ ン (一般的な場合) RX TX txrate rxrate PLL1 PLL0 148.5 MHz 148.5/1.001 MHz IBUFDS_GTE2 CHANNEL GTPE2_ CHANNEL txsysclksel GTPE2_ CHANNEL GTPE2_ CHANNEL RX TX txrate rxrate txsysclksel RX X1097_03_073113 TX txrate rxrate txsysclksel RX TX

÷

÷

÷

÷

÷

÷

÷

÷

txrate txsysclkselXAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 8 • ト ラ ン ス ミ ッ タ ーは、 サポー ト さ れてい る すべての SDI ビ ッ ト レー ト で送信す る のに必要な 2 つ のシ リ アル ク ロ ッ ク を得 る ため、2 つの PLL か ら の ク ロ ッ ク を動的に切 り 換え る こ と がで き ます。 • ク ワ ッ ド 内の 4 つの レ シーバー と 4 つの ト ラ ン ス ミ ッ タ ーは完全に独立 し てお り 、 それぞれ異な る SDI ビ ッ ト レー ト で動作で き 、 ほかの RX や TX ユニ ッ ト へ干渉す る こ と な く ビ ッ ト レー ト を動 的に切 り 換え る こ と も 可能です。 • ゲン ロ ッ ク 機能を搭載 し た アプ リ ケーシ ョ ン では、 同期 リ フ ァ レ ン ス入力信号か ら 必要な 2 つの基 準 ク ロ ッ ク 周波数を最新のゲン ロ ッ ク PLL が同時に提供で き ます。 SDI アプ リ ケーシ ョ ンに よ っ ては、SDI ト ラ ン ス ミ ッ タ ーが同 じ 公称ビ ッ ト レー ト で送信 し ていて も 、 わずかに異な る ビ ッ ト レー ト で動作す る 場合があ り ます。 こ れは、 各 TX の ビ ッ ト レー ト が、 関連す る SDI RX で受信 さ れ る SDI のビ ッ ト レー ト と 正確に一致 し なければな ら ない SDI ルー タ ーで よ く 見 ら れます。同 じ 公称ビ ッ ト レー ト で送信す る 2 つの ト ラ ン ス ミ ッ タ ーのビ ッ ト レー ト は、実際、数 ppm 異な り ます。こ の よ う な アプ リ ケーシ ョ ンは Artix-7 FPGA の GTP ク ワ ッ ド 構造でのサポー ト が難 し い ため、各 ク ワ ッ ド で使用で き る PLL が多い GTX/GTH ト ラ ン シーバーを備えた 7シ リ ーズデバ イ ス を 使用す る か、 ま たは PICXO (Phase Interpolation Control Oscillator) を GTX/GTH ト ラ ン シーバーに転 用 さ せた 7シ リ ーズデバ イ ス を使用す る 方が よ り 適 し てい る こ と があ り ます。 すべての レ シーバーでは片方の PLL か ら の割 り 込みな し のシ リ アル ク ロ ッ ク が必要 と な る ため、SDI ルー タ ーの よ う な アプ リ ケーシ ョ ン で TX シ リ アルク ロ ッ ク を供給す る には ク ワ ッ ド 内の も う 片方の PLL し か利用で き ません。 し たがっ て、 こ の よ う な アプ リ ケーシ ョ ン では、 各 TX ユニ ッ ト に個別のシ リ アルク ロ ッ ク が供給 さ れ る 、 次の 2 つの GTP ク ワ ッ ド 構成 し かサポー ト し ません。 • 片方の PLL か ら のシ リ アルク ロ ッ ク を使用す る 4 つの レ シーバー、お よ び も う 片方の PLL か ら の シ リ アルク ロ ッ ク を使用す る 1 つの ト ラ ン ス ミ ッ タ ー (図4を参照) • それぞれが別の PLL か ら のシ リ アル ク ロ ッ ク を使用す る 2 つの ト ラ ン ス ミ ッ タ ー、 お よ びア ク テ ィ ブな レ シーバーはな し (図5を参照)

X-Ref Target - Figure 4

図 4 : GTP ク ワ ッ ド 内の 4 つの RX と 1 つの TX TX RX txrate rxrate GTPE2_COMMON PLL1 PLL0 SDI TX REFCLK 148.5 MHz IBUFDS_GTE2 IBUFDS_GTE2 GTPE2_ CHANNEL GTPE2_ CHANNEL GTPE2_ CHANNEL GTPE2_ CHANNEL RX rxrate X1097_04_073113 RX rxrate RX

÷

÷

÷

÷

÷

rxrateリ セ ッ ト

『7シ リ ーズFPGA GTP ト ラ ン シーバーユーザーガ イ ド 』 (UG482) で説明 さ れてい る よ う に、GTP ト ラ ン シーバーには固有の リ セ ッ ト 要件があ り ます。GTP ト ラ ン シーバーでは、2 つの PLL の リ セ ッ ト 、 gttxreset、 ま たは gtrxreset と 、rxrate な ど一部の GTP ポー ト の動的変更に よ る リ セ ッ ト 間におけ る シー ケ ン ス に注意が必要です。 こ れ ら の イ ベン ト をすべて適切に調整 し な ければ、GTP ト ラ ン シーバーが SDI に対 し て正 し く 機能 し ない、 つま り 、FPGA を リ コ ン フ ィ ギ ュ レーシ ョ ンす る こ と で し か回復で き ない状態にな る 可能性があ り ます。 こ のアプ リ ケーシ ョ ン ノ ー ト で提供す る 制御モジ ュ ールは、GTP ト ラ ン シーバーが確実かつ適切に動作す る よ う こ れ ら の要件をすべて満た し ます。

GTP

初期化シーケ ン ス FPGA コ ン フ ィ ギ ュ レ ー シ ョ ン 直 後、SDI 制 御 モ ジ ュ ー ル が GTP ト ラ ン シ ー バ ー の GTPE2_COMMON PLL お よ び RX 部 と TX 部の初期化シーケ ン ス を実行 し ます。RX お よ び TX の初 期化シーケ ン ス は共通です。 制御モジ ュ ールには、GTP ト ラ ン シーバーの RX 部お よ び TX 部に対 し て 別々に初期化シーケ ン ス を実行す る 個別の ス テー ト マシ ンがあ り ます。 次の手順は、RX 初期化シーケ ン ス につい て説明 し て い ま す。TX 初期化 シ ー ケ ン ス の手順は、gttxreset、tx_refclk_stable、 お よ び txresetdone 信号がそれぞれ gtrxreset、rx_refclk_stable、 お よ び rxresetdone 信号に置 き 換わ る 以外は こ れ と 同 じ です。1. FPGA コ ン フ ィ ギ ュ レーシ ョ ン後に 500ns 以上待機 し た ら 、pllreset 信号お よ び gtrxreset 信号を ア サー ト し ます。

2. rx_refclk_stable 入力がアサー ト さ れ る ま で待機 し 、pllreset を ネゲー ト し ます。 3. plllock 信号がアサー ト さ れ る ま で待機 し 、gtrxreset 信号を ネゲー ト し ます。

4. rxresetdone 信号がアサー ト さ れ る ま で待機 し 、 初期化シーケ ン ス が完了 し た こ と を示 し ます。 GTP の txuserrdy 入力お よ び rxuserrdy 入力は適切に制御す る 必要が あ り ま す。 こ れ ら の信号は共に SDI ラ ッ パーに よ っ て生成 さ れ ま す。SDI ラ ッ パーは、gttxreset が ネ ゲー ト さ れ る と 、txuserrdy を txusrclk の 5 サ イ ク ル間アサー ト し ます。 同様に、gtrxreset がネゲー ト さ れ る と 、rxuserrdy を rxusrclk の 5 サ イ ク ル間アサー ト し ます。 条件が満た さ れ る ま で初期化シーケ ン ス が待機 し てい る手順2、手順3、 お よ び手順4では、 タ イ ム ア ウ ト カ ウ ン タ ーが動作 し てい ます。 待機条件が満た さ れ る 前に タ イ ム ア ウ ト カ ウ ン タ ーが終了す る と 、 ス テー ト マシ ンが タ イ ム ア ウ ト ス テー ト に遷移 し 、 リ ト ラ イ カ ウ ン タ ーを イ ン ク リ メ ン ト し てか ら 初 期化シーケ ン ス に戻 り 、 シーケ ン ス を再開 し ます。 タ イ ム ア ウ ト が多数発生 し た こ と が原因で リ ト ラ イ カ ウ ン タ ーが最大カ ウ ン ト に達す る と 、 初期化シーケ ン ス にエ ラ ーが発生 し 、 ス テー ト マシ ンがエ ラ ー ス テー ト に遷移 し て初期化シーケ ン ス のエ ラ ーを示 し ます。 リ ト ラ イ 可能な最大回数は、SDI ラ ッ パー のパ ラ メ ー タ ー/ジ ェ ネ リ ッ ク で指定 し ます。 図 5 : GTP ク ワ ッ ド 内の 2 つの独立 し た TX TX txrate txrate PLL0 TX REFCLK 2 IBUFDS_GTE2 GTPE2_ CHANNEL X1097_05_073113

÷

XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 10

PLL

リ セ ッ ト FPGA コ ン フ ィ ギ ュ レ ーシ ョ ン 後に自動的に実行 さ れ る 初期化シーケ ン ス での リ セ ッ ト だけ で な く 、 GTPE2_COMMON 内の片方の PLL へ供給 さ れ る 基準 ク ロ ッ ク に対 し て周波数が変更 さ れた場合や割 り 込みが発生 し た場合は常に、 その PLL を リ セ ッ ト す る 必要があ り ま す。 こ の リ セ ッ ト は、 対象 と な る PLL を基準 ク ロ ッ ク に対 し て強制的に再度 ロ ッ ク す る 目的で必要です。PLL リ セ ッ ト を実行す る た めに、GTP ラ ッ パーの pll0reset 入力 と pll1reset 入力が SDI 制御モ ジ ュ ールに よ っ て制御 さ れ ま す。 ユーザーアプ リ ケーシ ョ ンは pll0reset ま たは pll1reset を直接アサー ト で き ません。SDI 制御モジ ュ ー ルが単独で pll0reset 信号お よ び pll1reset 信号を制御す る 必要があ り ます。 一方、 ユーザーアプ リ ケー シ ョ ンでは、PLL リ セ ッ ト が必要な タ イ ミ ン グ を判断 し 、対象 と な る PLL の リ セ ッ ト 、お よ びその PLL か ら のシ リ アル ク ロ ッ ク を使用す る GTP RX お よ び/ま たは TX ユニ ッ ト すべての リ セ ッ ト を要求 し ま す。SDI 制御モジ ュ ールには、GTP RX (rx_gtp_full_reset) お よ び GTP TX (tx_gtp_full_reset) の完全な リ セ ッ ト を要求す る ためにアプ リ ケーシ ョ ンが使用す る 2 つの入力があ り ます。 こ れ ら の入力のいずれか を アサー ト す る と 、制御モジ ュ ールの リ セ ッ ト ス テー ト マシ ンが適宜 GTP ト ラ ン シーバーの RX 部ま たは TX 部の完全な初期化シーケ ン ス を実行 し ます (関連す る PLL の リ セ ッ ト を含む)。PLL が使用す る 基準 ク ロ ッ ク に割 り 込みが発生 し た り 、 変更が加え ら れた場合は常に こ れ ら の初期化シーケ ン ス が実 行 さ れ る よ う 、ユーザーアプ リ ケーシ ョ ン で rx_gtp_full_reset 入力お よ び tx_gtp_full_reset 入力を正 し く 制御す る 必要があ り ます。 制御モジ ュ ールへの rx_refclk_stable 入力お よ び tx_refclk_stable 入力が正 し く 制御 さ れ る か ど う かは ユーザーアプ リ ケーシ ョ ン が担い ま す。 こ れ ら の入力信号は、PLL への基準 ク ロ ッ ク が安定 し てい る 場合にのみアサー ト し な ければな り ま せん。 すでに説明 し た と お り 、 こ れ ら の入力が PLL リ セ ッ ト の ネ ゲ ー ト 前 に ア サ ー ト さ れ る ま で、 初期化 シ ー ケ ン ス は待機 し ま す。rx_refclk_stable 入力 ま た は tx_refclk_stable 入力のネゲー ト に よ っ て、 対象 と な る PLL の リ セ ッ ト が開始 さ れ る わけではあ り ませ ん。 制御モ ジ ュ ールへの rx_gtp_full_reset 入力お よ び tx_gtp_full_reset 入力が ア サー ト さ れ る こ と に よ っ てのみ、PLL リ セ ッ ト は開始 し ます。rx_refclk_stable お よ び tx_refclk_stable は、rx_gtp_full_reset ま たは tx_gtp_full_reset のアサー ト に よ っ て初期化シーケ ン ス が開始 さ れた後にのみ使用 し ます。

GTP TX

の リ セ ッ ト GTP の TX 部の リ セ ッ ト が必要 と な る 状況は次の 3 つです。 • GTP TX へシ リ アル ク ロ ッ ク を供給す る PLL が リ セ ッ ト さ れ る 場合は、gttxreset ポー ト を使用 し て TX 部を必ず リ セ ッ ト し ます。 こ の リ セ ッ ト は、SDI 制御モジ ュ ールに よ る FPGA コ ン フ ィ ギ ュ レーシ ョ ン後、 お よ びユーザーアプ リ ケーシ ョ ン で SDI 制御モジ ュ ールへの tx_gtp_full_reset が アサー ト さ れ る たびに自動的に実行 さ れ、 こ の結果、PLL お よ び GTP TX の両方が リ セ ッ ト さ れ ます。 • GTP gttxreset 入力は、txsysclksel ポー ト が動的に変更 さ れてい る 間アサー ト す る 必要があ り ます。 txsysclksel ポー ト を使用 し 、GTPE2_COMMON ブ ロ ッ ク にあ る 2 つの PLL のいずれを GTP TX のシ リ アル ク ロ ッ ク ソ ー ス と し て使用す る か を選択 し ま す。 ク ワ ッ ド に あ る 各 GTP ト ラ ン シー バーは、 固有の txsysclksel ポー ト を備え てお り 、2 つの PLL のシ リ アル ク ロ ッ ク ソ ース を個別に 切 り 替え る こ と がで き ます。txsysclksel ポー ト はアプ リ ケーシ ョ ンで直接制御で き ません。SDI 制 御モジ ュ ールが、tx_m 入力の変更を受け て GTP ト ラ ン シーバーの txsysclksel ポー ト を動的に変 更 し ま す。 制御モジ ュ ールは、tx_m 入力への変更を検出す る と ま ず gttxreset 信号を アサー ト し 、 その後 txsysclksel を 変更 し て か ら gttxreset を ネ ゲー ト し ま す。 こ の シーケ ン ス は、GTP ト ラ ン シ ーバー が txresetdone 出力 を ア サ ー ト し て 終了 し ま す。 こ の 時点 で SDI 制御 モ ジ ュ ール は、 tx_change_done 出力を アサー ト し て txsysclksel が変更 さ れた こ と を示 し ます。 • txrate 入力ポー ト が動的に変更 さ れ る と 、GTP TX は GTP ト ラ ン シーバー自身に よ っ て必ず自動的 に リ セ ッ ト さ れます。txrate は、GTP TX のシ リ アル ク ロ ッ ク 分周器を制御 し ます。 ユーザーアプ リ ケーシ ョ ンでは txrate を直接変更で き ません。tx_mode 入力ポー ト の変更を受け、 適切な場合は SDI 制御モジ ュ ールが txrate を変更 し ます。GTP リ セ ッ ト 、txsysclksel お よ び txrate の動的変更な ど の動作はすべて、互いに干渉 し ない よ う に SDI 制御モジ ュ ールの TX 制御ス テー ト マシ ンに よ っ て調整 さ れます。 こ の よ う な干渉を回避す る こ と が重 要なため、 ユーザーアプ リ ケーシ ョ ンでは こ れ ら を直接制御 し ない よ う に し 、SDI 制御モジ ュ ールに制 御 さ せます。

SDI ラ ッ パーには TX 部の リ セ ッ ト 入力が 3 つあ り ます。

• tx_rst : High にアサー ト さ れ る と 、SDI コ アにあ る SDI TX デー タ パス を リ セ ッ ト し ます。 • tx_gtp_full_reset : High にアサー ト さ れ る と 、TX に関連す る PLL を リ セ ッ ト し てか ら 、GTP の TX 部 (gttxreset) を リ セ ッ ト し ます。2 つの リ セ ッ ト の こ の よ う なシーケ ン ス に よ り 、PLL リ セ ッ ト が完了 し て PLL が基準 ク ロ ッ ク に ロ ッ ク さ れ る ま で gttxreset は完了 し ません。 • tx_gtp_reset : High にアサー ト さ れ る と 、GTP ト ラ ン シーバーの TX 部のみを リ セ ッ ト し ます。 gttxreset シ ー ケ ン ス の 開 始 時 に PLL が ロ ッ ク さ れ て い な い 場 合、PLL が ロ ッ ク さ れ る ま で gttxreset シーケ ン ス は完了 し ません。

GTP RX

の リ セ ッ ト RX リ セ ッ ト は TX リ セ ッ ト よ り も 複雑であ る ため、 さ ら に注意深 く 制御す る 必要があ り ます。TX 部 と 同様に、 ユーザーアプ リ ケーシ ョ ンでは、 こ のセ ク シ ョ ン で説明 し たすべての動作が互いに干渉 し な い よ う に SDI 制御モジ ュ ールに よ っ て慎重に調整 さ れます。 GTP RX 部の リ セ ッ ト が必要 と な る 状況は次の と お り です。 • GTP RX へシ リ アル ク ロ ッ ク を供給す る PLL が リ セ ッ ト さ れ る 場合は、gtrxreset ポー ト を使用 し て RX 部を必ず リ セ ッ ト し ます。 こ の リ セ ッ ト は、SDI 制御モジ ュ ールに よ る FPGA コ ン フ ィ ギ ュ レーシ ョ ン後、 お よ びユーザーアプ リ ケーシ ョ ン で SDI 制御モジ ュ ールへの rx_gtp_full_reset が アサー ト さ れ る たびに自動的に実行 さ れ、 こ の結果、PLL お よ び GTP RX の両方が リ セ ッ ト さ れ ま す。 何 ら か の 理 由 で gtrxreset 信 号 を 使 用 し て GTP RX を リ セ ッ ト す る 場 合 は、 『7シ リ ー ズFPGA GTP ト ラ ン シーバーユーザーガ イ ド 』 (UG482) に記載 さ れてい る よ う に特定のシーケ ン ス を実行す る 必要があ り ます。 こ のシーケ ン ス には、 シーケ ン ス の一部を実行中に DRP ポー ト を使用 し て DRP ア ド レ ス 0x011のビ ッ ト 11 を ク リ ア し た後、 元の値に戻す こ と な ど が含まれま す。 通常の SDI 動作では、 こ の ビ ッ ト を 1 に し ま す。GTP ラ ッ パーに あ る ス テー ト マ シ ン は、 gtrxreset がアサー ト さ れ る と 常に こ の完全なシーケ ン ス を実行 し ます。 • rxrate ポー ト が動的に変更 さ れ る 場合は、 『7シ リ ーズFPGA GTP ト ラ ン シーバーユーザー ガ イ ド 』 で rxrate 変更の事例で記載 さ れてい る よ う に特定のシーケ ン ス が必ず必要にな り ま す。 こ の シーケ ン ス には、 シーケ ン ス の一部を実行中に DRP ア ド レ ス 0x011のビ ッ ト 11 を ク リ アす る こ と な ど が含まれます。GTP ト ラ ン シーバーの PMA 部は、 こ の rxrate 変更シーケ ン ス の実行中に リ セ ッ ト さ れ ま す。GTP ラ ッ パーにあ る ス テー ト マ シ ンは、rxrate が変更 さ れ る と 常に こ の完全な シーケ ン ス を実行 し ます。 • GTP RX の CDR 設定が変更 さ れ る 場合は、gtrxreset ポー ト を使用 し て RX 部を必ず リ セ ッ ト し ま す。 現在の SDI モー ド (SD-SDI、HD-SDI、 ま たは 3G-SDI) に基づいて正 し く GTP CDR を設定 す る ために SDI 制御モジ ュ ールは次の 2 つの方法を用い ます。RX モー ド が SD-SDI の場合、GTP ト ラ ン シーバーの rxcdrhold ポー ト がアサー ト さ れ ます。SD-SDI ま たは 3G-SDI モー ド のいずれ かか ら HD-SDI モー ド に切 り 替え る 場合、 も し く は HD-SDI モー ド か ら SD-SDI ま たは 3G-SDI モー ド に切 り 替え る 場合、GTP ト ラ ン シーバーの RXCDR_CFG 属性が DRP を介 し て動的に変更 さ れます。rxcdrhold ま たは RXCDR_CFG 属性のいずれかが変更 さ れ る と 、その後に gtrxreset シー ケ ン ス が続 き ます。 さ ら に、 ユーザーアプ リ ケーシ ョ ンは、SDI 制御モジ ュ ールの rx_gtp_reset 入力ポー ト を アサー ト し て GTP RX の リ セ ッ ト を要求で き ます。 こ れに よ り 、GTP RX が使用す る PLL を リ セ ッ ト す る こ と な く gtrxreset シーケ ン ス が開始 さ れます。XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 12 SDI アプ リ ケーシ ョ ン で GTP DRP の使用が必要にな る シーケ ン ス には、gtrxreset、rxrate の変更、 お よ び RXCDR_CFG 属性の変更の 3 つがあ り ます。こ れ ら の各シーケ ン ス はそれぞれ別の ス テー ト マシ ンで制御 さ れます。gtrxreset お よ び rxrate の変更は、GTP ラ ッ パー内の個別ス テー ト マシ ンが制御 し ます。RXCDR_CFG の変更については、SDI 制御モジ ュ ールが対応 し ます。GTP ラ ッ パー内にあ る 2 つの ス テー ト マシ ンはそれぞれの DRP バ ス の動作を互いに調整 し ないため、gtrxreset シーケ ン スお よ び rxrate 変更シーケ ン ス が重複 し 得 る 場合は互いに干渉す る 可能性があ り ます。GTP ラ ッ パーには、 こ れ ら シーケ ン ス の重複を回避 し た り 、RXCDR_CFG を変更す る ために SDI 制御ス テー ト マシ ンが実行 す る DRP サ イ ク ルの干渉を回避す る 方法が本来備わっ てい ません。GTP ラ ッ パーの gtrxreset 入力がア サー ト さ れ る と 、rxrate 変更ス テー ト マシ ン な ど その他の ス テー ト マシ ンが DRP の読み出 し ま たは書 き 込みサ イ ク ル中であ っ て も 、GTP ラ ッ パー内にあ る gtrxreset ス テー ト マシ ンは非同期 GTP DRP 信 号の完全な制御 と みな し ま す。 こ のため、gtrxreset、rxrate の変更、 お よ び RXCDR_CFG 属性の変更 は、 慎重に調整す る 必要があ り ま す。 こ の よ う な調整は、SDI 制御モジ ュ ールが実行 し ま す。 つ ま り 、 ユーザーアプ リ ケーシ ョ ン で gtrxreset のアサー ト や rxrate ポー ト の変更を直接実行 し ない こ と が重要 です。 ユーザーアプ リ ケーシ ョ ン では、 こ の よ う な動作はすべて SDI 制御モジ ュ ールを介 し て要求す る 必要があ り ます。 直接実行す る と 、DRP ア ド レ ス 0x011の ビ ッ ト 11 が 0 に変更 さ れ、FPGA が リ コ ン フ ィ ギ ュ レーシ ョ ン さ れ る ま で 0 の ま ま と な り ます。 結果、FPGA が リ コ ン フ ィ ギ ュ レーシ ョ ン さ れ る ま で、GTP RX は SDI 信号を受信で き な く な り ます。 GTP ラ ッ パーの rxrate 変更ス テー ト マシ ンのデザ イ ンは、FPGA コ ン フ ィ ギ ュ レーシ ョ ン後の初期化 シーケ ン ス中 rxrate ポー ト に対 し て別の要件を課 し ます。GTP ラ ッ パーへの rxrate ポー ト は、GTP RX の初期化シーケ ン ス が完了す る ま で、 値をすべて 0 に保持す る 必要があ り ます。rxrate 変更ス テー ト マ シ ンの rxrate 変更検出 ロ ジ ッ ク は、 比較レ ジ ス タ で000を指定 し て FPGA コ ン フ ィ ギ ュ レーシ ョ ンか ら 生成 さ れ ま す。FPGA コ ン フ ィ ギ ュ レ ーシ ョ ン完了直後の rxrate の値が000でない場合、GTP RX 初期化シーケ ン ス が完了 し ていな く て も rxrate 変更シーケ ン ス が開始 さ れます。そ し て、rxrate 変更シー ケ ン スお よ び gtrxreset シーケ ン ス が互いに干渉 し 、GTP RX は SDI を受信で き ない状態に放置 さ れ る 可能性があ り ます。FPGA が リ コ ン フ ィ ギ ュ レーシ ョ ン さ れ る ま で、GTP RX は こ の状態に留ま っ て し ま い ます。 こ の よ う な状況を回避す る ために、GTP RX の初期化シーケ ン ス が完了す る ま で SDI 制御モジ ュ ールは GTP rxrate ポー ト の値をすべて 0 に し ます。ただ し 、 こ れには間接的な作用が伴い ます。rxrate は、GTP ト ラ ン シーバーに よ っ て生成 さ れた rxoutclk の周波数を決定す る GTP RX シ リ アル ク ロ ッ ク 分周器を 制御 し ま す。rxoutclk は、SDI コ ア の RX ロ ジ ッ ク すべて に ク ロ ッ ク を 供給す る た めに使用 し ま す。 rxrate がすべて 0 に設定 さ れてい る 場合、 分周値が 1 のシ リ アルク ロ ッ ク 分周器が選択 さ れます。 こ の 分周値は、 通常の SDI 動作中で使用 さ れ る こ と はあ り ません。 通常の SDI 動作では、rxrate ポー ト を常 に使用 し て ク ロ ッ ク 分周値に 2 ま たは 4 が選択 さ れます。 し たがっ て、FPGA コ ン フ ィ ギ ュ レーシ ョ ン 直後に発生す る GTP RX の初期化シーケ ン ス では、rxoutclk の周波数が 297MHz にな り ます。 通常動 作では、rxoutclk の周波数が 148.5MHz を超え る こ と はあ り ません。 一般に、rxoutclk には 148.5MHz と い う ク ロ ッ ク 周期制約が適用 さ れ、rxoutclk が こ の ク ロ ッ ク 周期を超え て動作す る こ と はない と 想定 し て FPGA デザ イ ンは実装 さ れます。Artix-7 FPGA は 297MHz の周波数で実行す る SDI コ アに対応 で き る 十分な速度を備えていないため、297MHz の ク ロ ッ ク 周期制約を rxoutclk に適用す る オプシ ョ ン は用意 さ れてい ません。こ の問題を回避す る ため、FPGA コ ン フ ィ ギ ュ レーシ ョ ンが終了 し てか ら rxrate が有効な値に正 し く 変更 さ れて rxoutclk が 148.5MHz 以下の速度で動作す る ま で、SDI 制御モジ ュ ー ルは SDI コ アの RX 部を リ セ ッ ト に保持 し ます。

SDI ラ ッ パーには RX 部の リ セ ッ ト 入力が 3 つあ り ます。

• rx_rst : High にアサー ト さ れ る と 、SDI コ アにあ る SDI RX デー タ パ ス を リ セ ッ ト し ます。 • rx_gtp_full_reset : High にアサー ト さ れ る と 、RX に関連す る PLL を リ セ ッ ト し てか ら 、GTP

ト ラ ン シーバーの RX 部 (gtrxreset) を リ セ ッ ト し ます。2 つの リ セ ッ ト の こ の よ う なシーケ ン ス に よ り 、PLL リ セ ッ ト が完了 し て PLL が基準 ク ロ ッ ク に ロ ッ ク さ れ る ま で gtrxreset は完了 し ません。

• rx_gtp_reset : High にアサー ト さ れ る と 、GTP ト ラ ン シーバーの RX 部 (gtrxreset) のみを リ セ ッ ト し ます。gtrxreset シーケ ン ス の開始時に PLL が ロ ッ ク さ れていない場合、PLL が ロ ッ

ン完了後、SDI ラ ッ パーが GTP ト ラ ン シーバーの RX 部お よ び TX 部の初期化シーケ ン ス を実行 し ま す。PLL は こ のシーケ ン ス中に リ セ ッ ト さ れます。 ま た、 基準 ク ロ ッ ク に対 し て割 り 込みが発生 し た り 周波数が変更 さ れた場合 も 、PLL を リ セ ッ ト す る 必要があ り ます。 SDI イ ン タ ー フ ェ イ ス の実装に使用 さ れ る ク ワ ッ ド 内の各 ト ラ ン シ ーバーに は個別の SDI 制御 モ ジ ュ ールを利用 し ます。 こ れ ら の各モジ ュ ールは、PLL の リ セ ッ ト お よ びモニ タ ー用の入力ポー ト と 出 力ポー ト を提供 し ます。同 じ ク ワ ッ ド 内にあ る 複数の ト ラ ン シーバーが SDI イ ン タ ーフ ェ イ ス に使用 さ れ る 場合、GTP ラ ッ パーお よ び SDI ラ ッ パーの PLL ポー ト を正 し く 接続す る 必要があ り ますが、 こ れ ら の接続要件はアプ リ ケーシ ョ ンに よ っ て異な り ます。 こ のセ ク シ ョ ンでは、SDI アプ リ ケーシ ョ ンの PLL 使用モデルについて説明 し ます。 こ れ ら の使用モデルでは、SDI ラ ッ パーの次の信号を利用 し てい ます。 • gtp_rxpllreset : GTP RX で使用 さ れ る PLL を リ セ ッ ト す る ために用い る SDI ラ ッ パーか ら の出力 ポー ト です。 • gtp_txpllreset : GTP TX で使用 さ れ る PLL を リ セ ッ ト す る ために用い る SDI ラ ッ パーか ら の出力 ポー ト です。

• gtp_rxplllock : pll0lock ま たは pll1lock GTP コ モン ラ ッ パー出力に よ っ て適宜駆動 さ れ る SDI ラ ッ パーへの入力ポー ト です。

• gtp_common_wrapper : pll0lock ま たは pll1lock GTP ト ラ ン シーバー出力に よ っ て適宜駆動 さ れ る SDI ラ ッ パーへの入力ポー ト です。

• rx_refclk_stable : GTP RX シ リ アル ク ロ ッ ク を供給 し てい る 片方の PLL への基準 ク ロ ッ ク が安定 し てい る 場合にのみ High にアサー ト す る SDI ラ ッ パーへの入力ポー ト です。

• tx_refclk_stable : GTP TX シ リ アル ク ロ ッ ク を供給 し てい る 片方の PLL ま たは両方の PLL への 基準 ク ロ ッ ク が安定 し てい る 場合にのみ High にアサー ト す る SDI ラ ッ パーへの入力ポー ト です。 • rx_gtp_full_reset and rx_gtp_reset : ユーザーアプ リ ケーシ ョ ンか ら SDI ラ ッ パーへの RX 部の リ

セ ッ ト 要求入力です。

• tx_gtp_full_reset and tx_gtp_reset : ユーザーアプ リ ケーシ ョ ンか ら SDI ラ ッ パーへの TX 部の リ セ ッ ト 要求入力です。

SDI

ア プ リ ケーシ ョ ンの

GTP PLL

の使用例

使用モデル1 :

ク ワ ッ ド 内で1

つの ト ラ ン シーバーがア ク テ ィ ブ で、TX

がPLL0

お よびPLL1

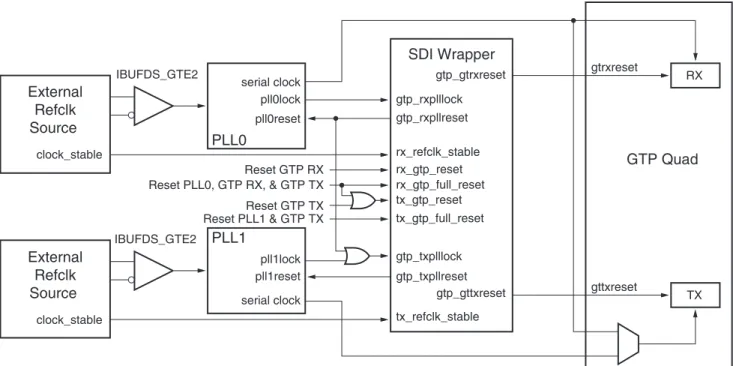

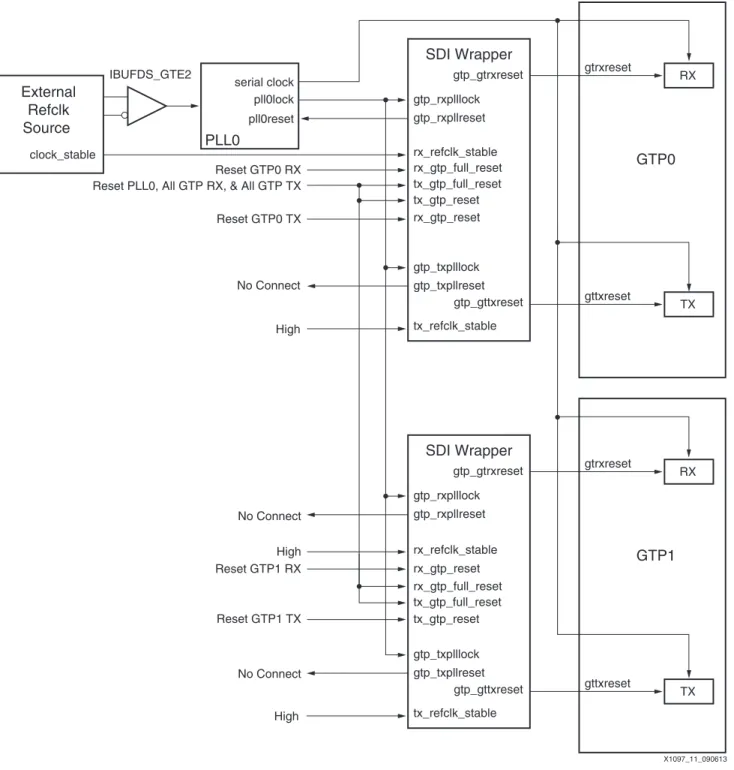

の両方を使用する場合 ク ワ ッ ド 内で 1 つの ト ラ ン シーバーがア ク テ ィ ブであ り 、TX ユニ ッ ト が PLL0 お よ び PLL1 を動的に 切 り 替え る 場合、SDI 制御モジ ュ ールの RX 部は GTP RX で使用 さ れ る PLL を制御す る 必要があ り ま す。SDI 制御モジ ュ ールの TX 部は片方の PLL の リ セ ッ ト を制御 し ますが、 ロ ッ ク ス テー タ ス につい ては両 PLL を監視 し ます。図6に接続図を示 し ます。 こ の図では、PLL0 が GTP RX お よ び GTP TX の両方で使用 さ れ る コ モン PLL と し て示 さ れ、PLL1 が GTP TX でのみ使用 さ れ る 2 つ目の PLL と し て示 さ れてい ます。 同様に、PLL1 を コ モン PLL と し て使用 し 、PLL0 を GTP TX でのみ使用 さ れ る 2 つ目の PLL と す る こ と も で き ます。XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 14 次の接続が必要です。

• SDI ラ ッ パーの gtp_rxpllreset 出力は、RX が使用す る PLL の pllreset に接続 し ます。 • SDI ラ ッ パーの gtp_txpllreset 出力は、 片方の PLL の pllreset に接続 し ます。

• SDI ラ ッ パーの gtp_rxplllock 入力は、RX が使用す る PLL の plllock に接続 し ます。 • SDI ラ ッ パーの gtp_txplllock 入力は、plllock の両信号の ロ ジ ッ ク OR に よ っ て駆動 し ます。 • RX が使用す る PLL への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、SDI ラ ッ パーの rx_refclk_stable 入力を High にアサー ト し ます。 • 片方の PLL (RX が使用 し ない PLL) への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、SDI ラ ッ パーの tx_refclk_stable 入力を High にアサー ト し ます。 • 基準 ク ロ ッ ク に対す る 変更や割 り 込みが発生 し たため コ モン PLL を リ セ ッ ト す る 必要があ る 場合 は、SDI ラ ッ パーの rx_gtp_full_reset 入力を アサー ト し て コ モン PLL と GTP RX の両方を リ セ ッ ト し ます。 ま た、SDI ラ ッ パーの tx_gtp_reset 入力 も アサー ト し て も う 一方の PLL を リ セ ッ ト せ ずに GTP TX を リ セ ッ ト し ます。 • 基準 ク ロ ッ ク に対す る 変更や割 り 込みが発生 し たため TX のみが使用す る PLL を リ セ ト す る 必要 があ る 場合は、SDI ラ ッ パーの tx_gtp_full_reset 入力を アサー ト し て PLL お よ び GTP TX の両方 を リ セ ッ ト し ます。 使用モデル

2 :

ク ワ ッ ド 内で1

つの ト ラ ン シーバーがア ク テ ィ ブ で、RX

およびTX

が別のPLL

を使用する場合 ク ワ ッ ド 内で 1 つの ト ラ ン シーバーがア ク テ ィ ブであ り 、GTP RX お よ び TX がそれぞれ別の PLL を 使用す る 場合の接続図を図7に示 し ます。 こ の図では、PLL0 が GTP RX のシ リ アルク ロ ッ ク ソ ース と し て示 さ れ、PLL1 が GTP TX のシ リ アルク ロ ッ ク ソ ース と し て示 さ れてい ます。 ただ し 、PLL1 は GTP RX に使用 さ れ、PLL0 は GTP TX に使用 さ れ る と い う 簡単な構成です。X-Ref Target - Figure 6

図 6 : PLL の使用モデル 1

External

Refclk

Source

clock_stable IBUFDS_GTE2 pll0lock pll0reset gtp_rxplllock gtp_rxpllreset rx_refclk_stable IBUFDS_GTE2 pll1lock pll1reset gtp_txplllock gtp_txpllreset tx_refclk_stableSDI Wrapper

GTP Quad

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset serial clockPLL0

serial clockPLL1

RX TX rx_gtp_full_reset tx_gtp_full_reset Reset PLL0, GTP RX, & GTP TX Reset PLL1 & GTP TX tx_gtp_reset rx_gtp_reset Reset GTP RX Reset GTP TXExternal

Refclk

Source

clock_stable X1097_06_090613次の接続が必要です。

• SDI ラ ッ パーの gtp_rxpllreset 出力は、RX が使用す る PLL の pllreset に接続 し ます。 • SDI ラ ッ パーの gtp_txpllreset 出力は、TX が使用す る PLL の pllreset に接続 し ます。 • SDI ラ ッ パーの gtp_rxplllock 入力は、RX が使用す る PLL の plllock に よ っ て駆動 し ます。 • SDI ラ ッ パーの gtp_txplllock 入力は、TX が使用す る PLL の plllock に よ っ て駆動 し ます。 • RX が使用す る PLL への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、SDI ラ ッ パーの rx_refclk_stable 入力を High にアサー ト し ます。 • TX が使用す る PLL への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、SDI ラ ッ パーの tx_refclk_stable 入力を High にアサー ト し ます。 • 基準 ク ロ ッ ク に対す る 変更や割 り 込みが発生 し たため RX が使用す る PLL を リ セ ッ ト す る 必要が あ る 場合は、SDI ラ ッ パーの rx_gtp_full_reset 入力を アサー ト し て PLL お よ び GTP RX の両方を リ セ ッ ト し ます。 • 基準 ク ロ ッ ク に対す る 変更や割 り 込みが発生 し たため TX が使用す る PLL を リ セ ッ ト す る 必要が あ る 場合は、SDI ラ ッ パーの tx_gtp_full_reset 入力を アサー ト し て PLL お よ び GTP TX の両方を リ セ ッ ト し ます。 使用モデル

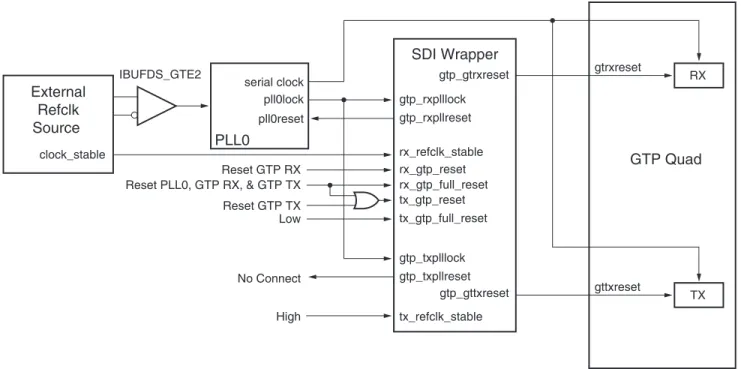

3 :

ク ワ ッ ド 内で1

つの ト ラ ン シーバーがア ク テ ィ ブ で、RX

およびTX

が同 じPLL

を使用する場合 ク ワ ッ ド 内で 1 つの ト ラ ン シーバーがア ク テ ィ ブであ り 、GTP RX お よ び TX が同 じ PLL を使用す る 場合、SDI 制御モジ ュ ールの RX 部を用いてその PLL を リ セ ッ ト し ます。ただ し 、GTP RX お よ び GTP TX の両方が PLL の ロ ッ ク ス テー タ ス を監視す る 必要があ り ます (図8 を参照)。 こ の図では PLL0 が 使用 さ れてい ますが、PLL1 を利用す る こ と も で き ます。 図 7 : PLL の使用モデル 2External

Refclk

Source

clock_stable IBUFDS_GTE2 pll0lock pll0reset gtp_rxplllock gtp_rxpllreset rx_refclk_stable IBUFDS_GTE2 pll1lock pll1reset gtp_txplllock gtp_txpllreset tx_refclk_stableSDI Wrapper

GTP Quad

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset serial clockPLL0

serial clockPLL1

RX TX rx_gtp_full_reset tx_gtp_full_reset Reset GTP TX Reset PGTP TX tx_gtp_reset rx_gtp_reset Reset PLL0 & GTP RX Reset PLL1 & GTP TXExternal

Refclk

Source

clock_stable X1097_07_081613XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 16 次の接続が必要です。

• SDI ラ ッ パーの gtp_rxpllreset 出力は、PLL の pllreset に接続 し ます。 • SDI ラ ッ パーの gtp_txpllreset 出力は未接続に し ます。

• SDI ラ ッ パーの gtp_rxpllock 入力は、PLL の plllock に よ っ て駆動 し ます。 • SDI ラ ッ パーの gtp_txplllock 入力は、PLL の plllock に よ っ て駆動 し ます。

• PLL への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、SDI ラ ッ パーの rx_refclk_stable 入力を High にアサー ト し ます。

• SDI ラ ッ パーの tx_refclk_stable 入力は High に接続 し ます。

• 基準 ク ロ ッ ク に対す る 変更や割 り 込みが発生 し たため PLL を リ セ ッ ト す る 必要があ る 場合は、SDI ラ ッ パーの rx_gtp_full_reset 入力を アサー ト し て PLL と GTP RX の両方を リ セ ッ ト し ます。ま た、 SDI ラ ッ パーの tx_gtp_reset 入力 も アサー ト し て GTP TX を リ セ ッ ト し ます。 使用モデル

4 : 1

つの ク ワ ッ ド 内で複数の ト ラ ン シーバーがア ク テ ィ ブ で、 すべてのRX

が 同 じPLL

を使用 し 、 すべてのTX

が2

つのPLL

を使用する場合 こ の使用モデルは、 ク ワ ッ ド 内で複数の ト ラ ン シーバーがア ク テ ィ ブで、 いずれ も SDI イ ン タ ーフ ェ イ ス を実装 し てい る 一般的な例です。 ク ワ ッ ド 内のア ク テ ィ ブな GTP RX ユニ ッ ト はすべて同 じ PLL か ら のシ リ アル ク ロ ッ ク を使用 し ます。 ク ワ ッ ド 内のア ク テ ィ ブな GTP TX ユニ ッ ト はすべて、2 つの PLL を動的に切 り 替え ます。図9に、 こ の使用例のモジ ュ ールを示 し ます。SDI ラ ッ パーの 1 つが PLL マ ス タ ー と し て指定 さ れ、PLL リ セ ッ ト を制御 し ます。X-Ref Target - Figure 8

図 8 : PLL の使用モデル 3

External

Refclk

Source

clock_stable IBUFDS_GTE2 pll0lock pll0reset gtp_rxplllock gtp_rxpllreset rx_refclk_stable gtp_txplllock gtp_txpllreset tx_refclk_stableSDI Wrapper

GTP Quad

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset serial clockPLL0

RX TX rx_gtp_full_reset tx_gtp_full_reset Reset PLL0, GTP RX, & GTP TX Low tx_gtp_reset rx_gtp_reset Reset GTP RX Reset GTP TX High No Connect X1097_08_081613次の接続が必要です。

• PLL マ ス タ ー SDI ラ ッ パーの gtp_rxpllreset 出力は、RX ユニ ッ ト が使用す る PLL の pllreset に接 続 し ます。 その他の SDI ラ ッ パーの gtp_rxpllreset 出力は未接続に し ます。

• PLL マ ス タ ー SDI ラ ッ パーの gtp_txpllreset 出力は、 も う 一方の PLL の pllreset に接続 し ます。 そ の他の SDI ラ ッ パーの gtp_txpllreset 出力は未接続に し ます。

• すべての SDI ラ ッ パーの gtp_rxplllock 入力は、RX ユニ ッ ト が使用す る PLL の plllock に よ っ て 駆動 し ます。 図 9 : PLL の使用モデル 4

External

Refclk

Source

clock_stable IBUFDS_GTE2 pll0lock pll0reset gtp_rxplllock gtp_rxpllreset rx_refclk_stable IBUFDS_GTE2 pll1lock pll1reset gtp_txplllock gtp_txpllreset tx_refclk_stableSDI Wrapper

GTP0

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset serial clockPLL0

serial clockPLL1

RX TX rx_gtp_full_reset tx_gtp_full_reset Reset PLL0, All GTP RX, & All GTP TXReset PLL1 & All GTP TX

tx_gtp_reset rx_gtp_reset Reset GTP0 RX Reset GTP0 TX

External

Refclk

Source

clock_stable gtp_rxplllock gtp_rxpllreset rx_refclk_stable gtp_txplllock gtp_txpllreset tx_refclk_stableSDI Wrapper

GTP1

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset RX TX rx_gtp_full_reset tx_gtp_full_reset No Connect tx_gtp_reset rx_gtp_reset Reset GTP0 RX High No Connect Reset GTP1 TX High X1097_09_090713XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 18 • すべての SDI ラ ッ パーの gtp_txplllock 入力は、plllock の両信号の ロ ジ ッ ク OR に よ っ て駆動 し ま

す。

• RX が使用す る PLL への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、PLL マ ス タ ー SDI ラ ッ パ ー の rx_refclk_stable 入 力 を High に ア サ ー ト し ま す。 そ の 他 す べ て の SDI ラ ッ パ ー の rx_refclk_stable 入力は High に接続 し ます。

• 片方の PLL (RX が使用 し ない PLL) への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、PLL マ ス タ ー SDI ラ ッ パーの tx_refclk_stable 入力を High にアサー ト し ます。 その他の SDI ラ ッ パーの tx_refclk_stable 入力は High に接続 し ます。 • 基準 ク ロ ッ ク に対す る 変更や割 り 込みが発生 し たため コ モン PLL (RX お よ び TX ユニ ッ ト すべて が使用) を リ セ ッ ト す る 必要があ る 場合は、PLL マ ス タ ー SDI ラ ッ パーの rx_gtp_full_reset 入力を アサー ト し ます。 その他の GTP RX ユニ ッ ト も リ セ ッ ト す る 必要があ る 場合、 それ ら GTP RX ユ ニ ッ ト の rx_gtp_full_reset 入力 ま たは rx_gtp_reset 入力を アサー ト し て リ セ ッ ト で き ます。 ま た、 すべての SDI ラ ッ パーの tx_gtp_reset 入力 も アサー ト し て 2 つ目の PLL を リ セ ッ ト せずに GTP TX ユニ ッ ト を リ セ ッ ト し ます。 • 基準 ク ロ ッ ク に対す る 変更や割 り 込みが発生 し たため コ モン PLL (RX お よ び TX ユニ ッ ト すべて が使用) を リ セ ッ ト す る 必要が あ る 場合は、PLL マ ス タ ー SDI ラ ッ パーの tx_gtp_reset 入力を ア サー ト し ます。その他の GTP TX ユニ ッ ト も リ セ ッ ト す る 必要があ る 場合、それ ら GTP TX ユニ ッ ト の tx_gtp_full_reset 入力ま たは tx_gtp_reset 入力を アサー ト し て リ セ ッ ト で き ます。 使用モデル

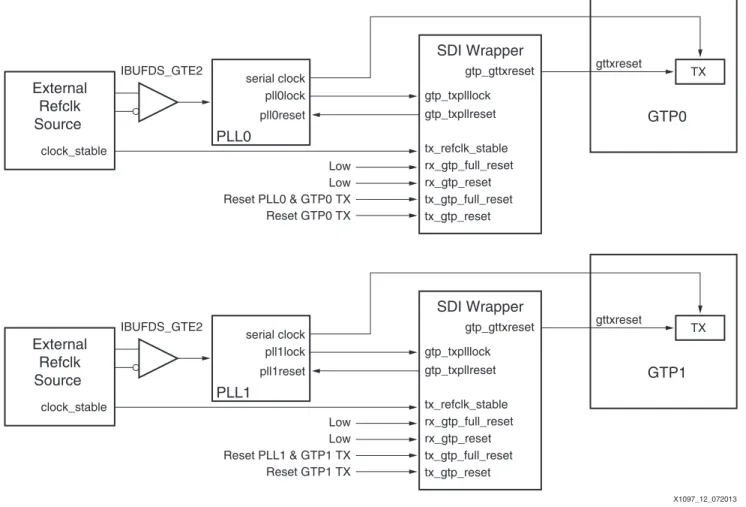

5 : 1

つの ク ワ ッ ド 内で複数の ト ラ ン シーバーがア ク テ ィ ブ で、 すべてのRX

が1

つのPLL

を使用 し 、 すべてのTX

が も う1

つのPLL

を使用する場合 こ の使用モデルは、1 つの GTP ク ワ ッ ド 内で複数の ト ラ ン シーバーがア ク テ ィ ブな場合の例です。ク ワ ッ ド 内にあ るすべての GTP RX ユニ ッ ト のシ リ アル ク ロ ッ ク が片方の PLL か ら 供給 さ れ、 その ク ワ ッ ド 内にあ るすべての GTP TX ユニ ッ ト のシ リ アルク ロ ッ ク は も う 片方の PLL か ら 供給 さ れます (図10を 参照)。1 つの SDI ラ ッ パーが PLL マ ス ター と し て指定 さ れ、PLL リ セ ッ ト を制御 し ます。次の接続が必要です。

• PLL マ ス タ ー SDI ラ ッ パーの gtp_rxpllreset 出力は、 ク ワ ッ ド 内のすべての GTP RX ユニ ッ ト が 使用す る PLL の pllreset に接続 し ます。

• PLL マ ス タ ー SDI ラ ッ パーの gtp_txpllreset 出力は、 ク ワ ッ ド 内のすべての GTP TX ユニ ッ ト が 使用す る PLL の pllreset に接続 し ます。

• すべての SDI ラ ッ パーの gtp_rxplllock 入力は、RX ユニ ッ ト が使用す る PLL の plllock に よ っ て 駆動 し ます。 図 10 : PLL の使用モデル 5

External

Refclk

Source

clock_stable IBUFDS_GTE2 pll0lock pll0reset gtp_rxplllock gtp_rxpllreset rx_refclk_stable IBUFDS_GTE2 pll1lock pll1reset gtp_txplllock gtp_txpllreset tx_refclk_stableSDI Wrapper

GTP0

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset serial clockPLL0

serial clockPLL1

RX TX tx_gtp_full_resetReset PLL1 & All GTP TX Reset PLL0 & All GTP RX

tx_gtp_reset rx_gtp_reset rx_gtp_full_reset Reset GTP0 RX Reset GTP0 TX

External

Refclk

Source

clock_stable gtp_rxplllock gtp_rxpllreset rx_refclk_stable gtp_txplllock gtp_txpllreset tx_refclk_stableSDI Wrapper

GTP1

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset RX TX rx_gtp_full_reset tx_gtp_full_reset No Connect tx_gtp_reset rx_gtp_reset Reset GTP1 RX High No Connect Reset GTP1 TX High X1097_10_072013XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 20 • すべての SDI ラ ッ パーの gtp_txplllock 入力は、TX ユニ ッ ト が使用す る PLL の plllock に よ っ て

駆動 し ます。

• RX ユニ ッ ト が使用す る PLL への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、PLL マ ス タ ー SDI ラ ッ パーの rx_refclk_stable 入力を High にアサー ト し ます。 その他すべての SDI ラ ッ パーの rx_reflk_stable 入力は High に接続 し ます。

• TX ユニ ッ ト が使用す る PLL への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、PLL マ ス タ ー SDI ラ ッ パーの tx_refclk_stable 入力を High にアサー ト し ます。 その他すべての SDI ラ ッ パーの tx_refclk_stable 入力は High に接続 し ます。 • RX ユニ ッ ト が使用す る PLL を リ セ ッ ト す る 必要があ る 場合は、PLL マ ス タ ー SDI ラ ッ パーの rx_gtp_full_reset 入力を アサー ト し ます。 その他の GTP RX ユニ ッ ト も リ セ ッ ト す る 必要があ る 場 合、 それ ら GTP RX ユニ ッ ト の rx_gtp_full_reset 入力ま たは rx_gtp_reset 入力を アサー ト し て リ セ ッ ト で き ます。 • TX ユニ ッ ト が使用す る PLL を リ セ ッ ト す る 必要があ る 場合は、PLL マ ス タ ー SDI ラ ッ パーの tx_gtp_full_reset 入力を アサー ト し ます。 その他の GTP TX ユニ ッ ト も リ セ ッ ト す る 必要があ る 場 合、 それ ら GTP TX ユニ ッ ト の tx_gtp_full_reset 入力 ま たは tx_gtp_reset 入力を アサー ト し て リ セ ッ ト で き ます。 使用モデル

6 : 1

つの ク ワ ッ ド 内で複数の ト ラ ン シーバーがア ク テ ィ ブ で、 すべてのRX

お よびTX

ユニ ッ ト が1

つの コ モ ンPLL

を使用する場合 こ の使用モデルは、1 つの GTP ク ワ ッ ド 内で複数の ト ラ ン シーバーがア ク テ ィ ブで、 その ク ワ ッ ド 内の すべての RX お よ び TX ユニ ッ ト が 1 つの PLL か ら 供給 さ れ る シ リ アルク ロ ッ ク を使用 し てい る 場合 の例です (図11を参照)。1 つの SDI ラ ッ パーが PLL マ ス タ ー と し て指定 さ れ、SDI ラ ッ パーの RX 部 が PLL リ セ ッ ト を制御 し ます。次の接続が必要です。

• PLL マ ス タ ー SDI ラ ッ パーの gtp_rxpllreset 出力は、PLL の pllreset に接続 し ます。 その他すべて の SDI ラ ッ パーの gtp_rxpllreset 出力は未接続に し ます。

• すべての SDI ラ ッ パーの gtp_txpllreset 出力は未接続に し ます。

• すべての SDI ラ ッ パーの rx_pllock 入力は、PLL の plllock に よ っ て駆動 し ます。 • すべての SDI ラ ッ パーの gtp_txplllock 入力は、PLL の plllock に よ っ て駆動 し ます。

図 11 : PLL の使用モデル 6

External

Refclk

Source

clock_stable IBUFDS_GTE2 pll0lock pll0reset gtp_rxplllock gtp_rxpllreset rx_refclk_stable No Connect gtp_txplllock gtp_txpllreset tx_refclk_stableSDI Wrapper

GTP0

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset serial clockPLL0

High RX TX Reset GTP0 TXReset PLL0, All GTP RX, & All GTP TX

tx_gtp_reset rx_gtp_reset tx_gtp_full_reset rx_gtp_full_reset Reset GTP0 RX gtp_rxplllock gtp_rxpllreset rx_refclk_stable gtp_txplllock gtp_txpllreset tx_refclk_stable

SDI Wrapper

GTP1

gtp_gtrxreset gtp_gttxreset gtrxreset gttxreset RX TX rx_gtp_full_reset tx_gtp_full_reset No Connect tx_gtp_reset rx_gtp_reset Reset GTP1 RX High No Connect Reset GTP1 TX High X1097_11_090613XAPP1097 (v1.0) 2013 年 12 月 5 日 japan.xilinx.com 22 • PLL への基準 ク ロ ッ ク ソ ース が安定 し てい る 場合にのみ、PLL マ ス タ ー SDI ラ ッ パーの rx_refclk_stable 入力は High にア サー ト し ま す。 その他すべての SDI ラ ッ パーの rx_reflk_stable 入力は High に接続 し ます。

• すべての SDI ラ ッ パーの tx_refclk_stable 入力は High に接続 し ます。

• PLL を リ セ ッ ト す る 必要があ る 場合は、PLL マ ス タ ー SDI ラ ッ パーの rx_gtp_full_reset 入力を ア サー ト し ます。 ま た、 その他の SDI ラ ッ パーの rx_gtp_full_reset ま たは rx_gtp_reset を アサー ト し て そ れ ら に関連す る GTP RX ユ ニ ッ ト を リ セ ッ ト し ま す。 さ ら に、 すべ て の SDI ラ ッ パーの gtp_tx_full_reset ま たは gtp_tx_reset 入力を アサー ト し てそれ ら に関連す る GTP TX ユニ ッ ト を リ セ ッ ト し ます。 使用モデル

7 :

ク ワ ッ ド 内で2

つの ト ラ ン シーバーがア ク テ ィ ブ で、 それ ら の両方がSDI

TX

のみを実装 し 、 それぞれ別のPLL

を使用 し てい る場合 こ の使用モデルは、1 つの GTP ク ワ ッ ド 内で 2 つの ト ラ ン シーバーがア ク テ ィ ブで、各 ト ラ ン シーバー が SDI TX し か実装 し ていない場合の例です。 ア ク テ ィ ブな SDI RX ユニ ッ ト はあ り ません。 ア ク テ ィ ブな GTP TX は、 それぞれ別の PLL を使用 し ます。 こ の例は、 各 TX ユニ ッ ト が独自の PLL を、 た と えば SDI ルー タ ー内に持たなければな ら ない場合な ど に使用 し ます。図12に こ の例を示 し ます。 次の接続が必要です。• 各 SDI ラ ッ パーの gtp_txpllreset 出力は、 関連す る PLL の pllreset にそれぞれ接続 し ます。 • SDI ラ ッ パーの gtp_rxpllreset 出力は未接続に し ます。

• 各 SDI ラ ッ パーの gtp_txplllock 入力は、 関連す る PLL の plllock 出力に接続 し ます。 X-Ref Target - Figure 12

図 12 : PLL の使用モデル 7