© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-1

出力コンペア

セクション 16. 出力コンペア

ハイライト

本セクションには以下の主要項目を記載しています。 16.1 はじめに ... 16-2 16.2 出力コンペアレジスタ ... 16-3 16.3 動作 ... 16-6 16.4 割り込み ... 16-33 16.5 I/O ピンの制御 ... 16-34 16.6 省電力モードとデバッグモード時の動作 ... 16-35 16.7 各種リセットの影響 ... 16-35 16.8 出力コンペアのアプリケーション例 ... 16-36 16.9 設計のヒント ... 16-38 16.10 関連アプリケーション ノート ... 16-39 16.11 改訂履歴 ... 16-40 注意: この日本語版文書は参考資料としてご利用ください。最新情報は必ずオリジ ナルの英語版をご参照願います。16.1

はじめに

出力コンペア モジュールは、選択されたタイムベース イベントへの応答として単発または連 続パルスを生成するために主として使われます。 出力コンペア モジュールの主な特長として下記が挙げられます。 • デバイスに複数の出力コンペア モジュールを内蔵 • シングルおよびダブルコンペア モード • 単発または連続出力パルスの生成 • パルス幅変調 (PWM) モード • コンペアイベント時の割り込み生成 ( プログラマブル ) • ハードウェアによる PWM フォルト検出と自動的な出力無効化 • 16 または 32 ビット タイムベースの選択 ( プログラマブル ) • 2 つの 16 ビット タイムベースのいずれか一方、または両方を組み合わせた 32 ビット タイ ムベースを使って動作 図16-1に出力コンペア モジュールのブロック図を示します。 図 16-1: 出力コンペア モジュールのブロック図 Note: ファミリ リファレンス マニュアルの本セクションは、デバイス データシートの補 足を目的としています。本書の内容はPIC32 ファミリの一部のデバイスには対応 していません。 本書の内容がお客様のご使用になるデバイスに対応しているかどうかは、最新デ バイス データシート内の「出力コンペア」の冒頭に記載している注意書きでご確 認ください。 デバイス データシートとファミリ リファレンス マニュアルの各セクションは、マ イクロチップ社のウェブサイト(http://www.microchip.com) でご覧になれます。 OCxR(1) Comparator Output Logic SR Q OCM<2:0> Output Enable OCx(1)Set Flag bit OCxIF(1) OCxRS(1) Mode Select 3 0 1 OCTSEL 0 1 16 16 OCFA or OCFB(2) TMR register inputs

from time bases(3)

Period match signals from time bases(3)

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-3

出力コンペア

16.2

出力コンペアレジスタ

各出力コンペア モジュールには下記の特殊機能レジスタ (SFR) が割り当てられています。 • OCxCON: 出力コンペア x 制御レジスタ • OCxR: 出力コンペア x コンペアレジスタ • OCxRS: 出力コンペア x セカンダリ コンペアレジスタ 表16-1に、出力コンペアに関連する全てのレジスタの要約を示します。この表の後に各レジス タの詳細な説明を記載しています。 Note: PIC32 ファミリの各デバイスは 1 つまたは複数の出力コンペア モジュールを内蔵 しています。ピン、制御 / ステータスビット、レジスタの名前に含まれる添え字 「x」は出力コンペア モジュールの番号を表します。詳細は各デバイスのデータシー トを参照してください。 表 16-1: 出力コンペア SFR の要約 名称 Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0 OCxCON(1,2,3) 31:24 — — — — — — — — 23:16 — — — — — — — — 15:8 ON — SIDL — — — — —7:0 — — OC32 OCFLT OCTSEL OCM<2:0>

OCxR(1,2,3) 31:24 OCxR<31:24> 23:16 OCxR<23:16> 15:8 OCxR<15:8> 7:0 OCxR<7:0> OCxRS(1,2,3) 31:24 OCxRS<31:24> 23:16 OCxRS<23:16> 15:8 OCxRS<15:8> 7:0 OCxRS<7:0> 凡例 : — = 未実装、「0」として読み出し Note 1: このレジスタに対応するクリアレジスタのアドレスは0x4 バイト オフセットしています。クリアレジスタは、対応す るレジスタの名前の後に「CLR」を追加した名前を持ちます ( 例 : OCxCONCLR)。クリアレジスタの任意のビットに 「1」を書き込むと、対応するレジスタの対応するビットがクリアされます。クリアレジスタからの読み出しは無視さ れます。 2: このレジスタに対応するセットレジスタのアドレスは0x8 バイト オフセットしています。セットレジスタは、対応す るレジスタの名前の後に「SET」を追加した名前を持ちます ( 例 : OCxCONSET)。セットレジスタの任意のビットに 「1」を書き込むと、対応するレジスタの対応するビットがセットされます。セットレジスタからの読み出しは無視さ れます。 3: このレジスタに対応する反転レジスタのアドレスは0xC バイト オフセットしています。反転レジスタは、対応するレ ジスタの名前の後に「INV」を追加した名前を持ちます ( 例 :OCxCONINV)。反転レジスタの任意のビットに「1」を書 き込むと、対応するレジスタの対応するビットが反転します。反転レジスタからの読み出しは無視されます。

レジスタ 16-1: OCxCON: 出力コンペア x 制御レジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

31:24 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

23:16 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

15:8 R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0

ON(1) — SIDL — — — — —

7:0 U-0 U-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0

— — OC32 OCFLT(2) OCTSEL OCM<2:0>

凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知 bit 31-16 未実装 :「0」として読み出し bit 15 ON: 出力コンペア モジュール ON ビット(1) 1 = 出力コンペア モジュールを有効にする 0 = 出力コンペア モジュールを無効にする ( この状態では電流を消費せず、SFR の変更が可能です ) このビットをセットまたはクリアしても、このレジスタ内の他のビットの状態には影響しません。 bit 14 未実装 :「0」として読み出し bit 13 SIDL: アイドルモード時停止ビット 1 = CPU がアイドルモードに移行した時に動作を停止する 0 = アイドルモード中も動作を継続する bit 12-6 未実装 :「0」として読み出し bit 5 OC32: 32 ビット コンペアモード ビット 1 = OCxR<31:0> および / または OCxRS<31:0> を使って 32 ビットタイマ源と比較する 0 = OCxR<15:0> および OCxRS<15:0> を使って 16 ビットタイマ源と比較する bit 4 OCFLT: PWM フォルト条件ステータスビット(2) 1 = PWM フォルト条件が発生した ( ハードウェアでのみクリア ) 0 = PWM フォルト条件は発生していない bit 3 OCTSEL: 出力コンペアタイマ選択ビット 1 = Timer3 をこの出力コンペア モジュールのクロック源として使う 0 = Timer2 をこの出力コンペア モジュールのクロック源として使う 出力コンペア モジュール向けに使えるタイムベースについては各デバイスのデータシートを参照してく ださい。 bit 2-0 OCM<2:0>: 出力コンペアモード選択ビット 111 = OCx を PWM モードにし、フォルトピンを有効にする 110 = OCx を PWM モードにし、フォルトピンを無効にする

101 = OCx ピンを LOW に初期化し、OCx ピンで連続出力パルスを生成する 100 = OCx ピンを LOW に初期化し、OCx ピンで単発出力パルスを生成する 011 = コンペアイベントで OCx ピンをトグルする

010 = OCx ピンを HIGH に初期化し、コンペアイベントで OCx ピンを LOW にする 001 = OCx ピンを LOW に初期化し、コンペアイベントで OCx ピンを HIGH にする 000 = 出力コンペア モジュールを無効にする ( 電流は消費し続けます )

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-5

出力コンペア

レジスタ 16-2: OCxR: 出力コンペア x コンペアレジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0 31:24 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 OCR<31:24> 23:16 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 OCR<23:16> 15:8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 OCR<15:8> 7:0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 OCR<7:0> 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知bit 31-16 OCxR<31:16>: 32 ビット コンペア値の上位 16 ビットを格納 (OC32 (OCxCON<5>) = 1 の場合 )

bit 15-0 OCxR<15:0>: 32 ビット コンペア値の下位 16 ビット (OC21 = 1 の場合 )、または、16 ビット コンペア値 ( OC32 = 0 の場合 ) を格納 レジスタ 16-3: OCxRS: 出力コンペア x セカンダリ コンペアレジスタ ビット レンジ Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0 31:24 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 OCRS<31:24> 23:16 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 OCRS<23:16> 15:8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 OCRS<15:8> 7:0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 OCRS<7:0> 凡例 : R = 読み出し可能ビット W = 書き込み可能ビット U = 未実装ビット、「0」として読み出し -n = POR 時の値 1 = ビットはセット 0 = ビットはクリア x = ビットは未知

bit 31-16 OCxRS<31:16>: 32 ビット コンペア値の上位 16 ビットを格納 (OC32 (OCxCON<5>) = 1 の場合 )

bit 15-0 OCxRS<15:0>: 32 ビット コンペア値の下位 16 ビット (OC21 = 1 の場合 )、または、16 ビット コンペア 値( OC32 = 0 の場合 ) を格納

16.3

動作

各出力コンペア モジュールは下記の動作モードを備えます。 • シングルコンペア一致モード - 出力を HIGH に駆動 - 出力を LOW に駆動 - 出力をトグル • ダブルコンペア一致モード - 単発出力パルス - 連続出力パルス • パルス幅変調モード - フォルト保護入力なし - フォルト保護入力あり16.3.1

シングルコンペア一致モード

OCM<2:0> 制御ビット (OCxCON<2:0>) を「001」、「010」、「011」のいずれかに設定すると、 対応する出力コンペア チャンネルは 3 種類あるシングル出力コンペア一致モードのいずれかに 設定されます。コンペア タイムベースも有効にする必要があります。 シングルコンペア モードでは、OCxR レジスタの値と選択したタイマレジスタ (TMRy) のイン クリメント値を比較します。コンペア一致が発生すると、下記のいずれかのイベントが発生し ます。• コンペア一致時に OCx ピンを初期状態の LOW から HIGH に駆動し、割り込みを生成する • コンペア一致時に OCx ピンを初期状態の HIGH から LOW に駆動し、割り込みを生成する • コンペア一致時に OCx ピンの状態をトグルする ( トグルイベントは繰り返し発生し、そのた

びに割り込みを生成します)

Note 1: モードを切り換える前にユーザ アプリケーションで出力コンペア モジュールを OFF にする (OCM<2:0> ビット (OCxCON<2:0>) をクリアする ) 必要があります。 モジュールの動作中にモードを切り換えると予期せぬ結果が生じる可能性があり ます。

2: 本書では、選択したタイマ源に対応する SFR の名称に添え字「y」を使います。 例えばPRy は選択したタイマ源の周期レジスタ、TyCON は選択したタイマ源の タイマ制御レジスタです。

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-7

出力コンペア

16.3.1.1 コンペア モード - 出力を HIGH に駆動

モジュールをこのモードで動作させるには、OCM<2:0> 制御ビットを「001」に設定します。 コンペア タイムベースも有効にする必要があります。このモードを有効にすると、出力ピン OCx は LOW に初期化され、TMRy と OCxR レジスタ間のコンペア一致が発生するまで LOW を維持します。図16-2と図16-3の下記のタイミング イベントに注目してください。

• コンペア タイムベースと OCxR レジスタ間のコンペア一致が発生すると、1 周辺モジュール 用クロック後に OCx ピンが HIGH に駆動されます。OCx ピンはモードが変更されるかモ ジュールが無効になるまでHIGH のままです。

• コンペア タイムベースは対応する周期レジスタの値に一致するまでインクリメントし続け、 一致すると次のPBCLKで0x0000 にリセットします。

• OCx ピンが HIGH になると、対応するチャンネル割り込みフラグ OCxIF がセットされます ( 各出力コンペア チャンネルの割り込みフラグビットの位置については IFS0 レジスタの説 明を参照してください)。 図 16-2: シングルコンペアモード : コンペア一致イベントで OCx ピンを HIGH に駆動 (16 ビットモード ) 図 16-3: シングルコンペアモード : コンペア一致イベントで OCx ピンを HIGH に駆動 (32 ビットモード ) OCxIF 4000 0001 3001 3002 3003 3004 3000 TMRy 0000 Cleared by User 1 PBCLK Period 4000 3002 PRy OCxR 3FFF OCx pin

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 OCxIF 0004: 0000: 0003: 0003: 0003: 0003: 0003: TMRy 0000: Cleared by User 1 PBCLK Period 0004: 0003: PRy OCxR 0003: OCx pin

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 0002 0000 0001 0002 0003 0004 0000 0000 FFFF 0000 0001

16.3.1.2 コンペア モード - 出力を LOW に駆動

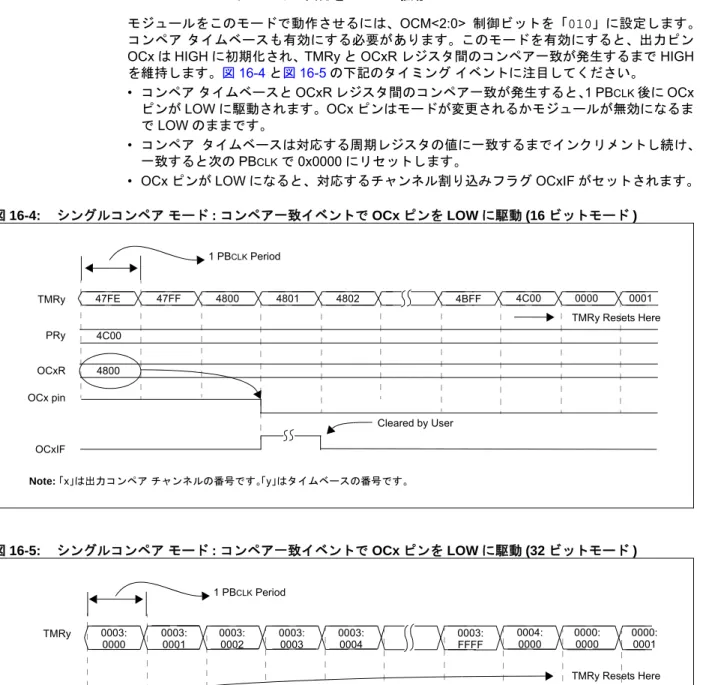

モジュールをこのモードで動作させるには、OCM<2:0> 制御ビットを「010」に設定します。 コンペア タイムベースも有効にする必要があります。このモードを有効にすると、出力ピン OCx は HIGH に初期化され、TMRy と OCxR レジスタ間のコンペア一致が発生するまで HIGH を維持します。図16-4と図16-5の下記のタイミング イベントに注目してください。 • コンペア タイムベースと OCxR レジスタ間のコンペア一致が発生すると、1 PBCLK後にOCx ピンがLOW に駆動されます。OCx ピンはモードが変更されるかモジュールが無効になるま でLOW のままです。 • コンペア タイムベースは対応する周期レジスタの値に一致するまでインクリメントし続け、 一致すると次のPBCLKで0x0000 にリセットします。

• OCx ピンが LOW になると、対応するチャンネル割り込みフラグ OCxIF がセットされます。 図 16-4: シングルコンペア モード : コンペア一致イベントで OCx ピンを LOW に駆動 (16 ビットモード ) 図 16-5: シングルコンペア モード : コンペア一致イベントで OCx ピンを LOW に駆動 (32 ビットモード ) OCxIF 4C00 0001 47FF 4800 4801 4802 47FE TMRy 0000 Cleared by User 1 PBCLK Period 4C00 4800 PRy OCxR 4BFF OCx pin

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 OCxIF 0004: 0000: 0003: 0003: 0003: 0003: 0003: TMRy 0000: Cleared by User 1 PBCLK Period 0004: 0003: PRy OCxR 0003: OCx pin

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 0002 0000 0001 0002 0003 0004 0000 0000 FFFF 0000 0001

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-9

出力コンペア

16.3.1.3 シングルコンペア モード - 出力をトグル

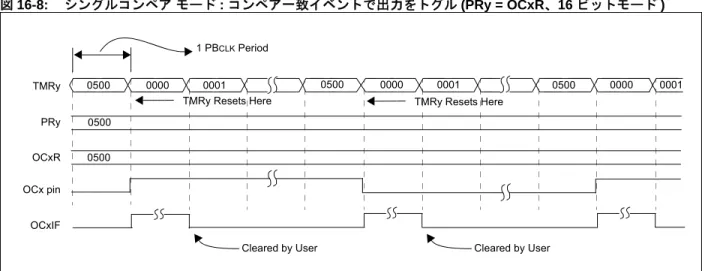

モジュールをこのモードで動作させるには、OCM<2:0> 制御ビットを「011」に設定します。 加えて、Timer2 または Timer3 を選択して有効にする必要があります。このモードを有効にす ると、出力ピンOCx は LOW に初期化され、その後タイマと OCxR レジスタ間の一致イベント が発生するたびにピンの状態がトグルします。図16-6、図16-7、図16-8、図16-9の下記のタ イミング イベントに注目してください。 • コンペア タイムベースと OCxR レジスタ間のコンペア一致が発生すると、1 PBCLK後にOCx ピンの状態がトグルします。トグル後のOCx ピンの状態は、次のトグルイベントが発生する か、モードが変更されるか、モジュールが無効になるまで持続します。 • コンペア タイムベースは対応する周期レジスタの値に一致するまでインクリメントし続け、 一致すると次のPBCLKで0x0000 にリセットします。 • OCx ピンがトグルすると、対応するチャンネル割り込みフラグ OCxIF がセットされます。 図 16-6: シングルコンペア モード : コンペア一致イベントで OCx ピンをトグル (16 ビットモード ) 図 16-7: シングルコンペア モード : コンペア一致イベントで OCx ピンをトグル (32 ビットモード ) Note: デバイスリセットが発生すると、内部のOCx ピン出力ロジックは論理「0」に設定 されます。ただし、トグルモード向けにOCx ピンの初期状態をユーザ アプリケー ションで設定する事ができます。例 16-1と例 16-2に、トグルモード動作向けに OCx ピンの初期状態を定義するためのサンプルコードを示します。 OCxIF 0500 0501 0502 0600 0500 TMRy 1 PBCLK Period 0600 0500 PRy OCxR 0001 OCx pin

TMRy Resets Here

0000 0501 0502 Cleared by User Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 OCxIF 0005: 0005: 0005: 0006: 0000: 0005: TMRy 0005: Cleared by User 1 PBCLK Period 0006: 0005: PRy OCxR 0000: OCx pin

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 0000

0000 0001 0002 0000 0000

0000

図 16-8: シングルコンペア モード : コンペア一致イベントで出力をトグル (PRy = OCxR、16 ビットモード ) 図 16-9: シングルコンペア モード : コンペア一致イベントで出力をトグル (PRy = OCxR、32 ビットモード ) 例 16-1: コンペアモードでのトグルモードのピン状態のセットアップ (16 ビットモード ) OCxIF 0500 0000 0001 0500 0500 TMRy 1 PBCLK Period 0500 0500 PRy OCxR 0001 OCx pin

TMRy Resets Here

0000 0000 0001

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。

Cleared by User Cleared by User

OCxIF 0000: 0000: 0000: 0005: 0000: 0005: TMRy 0005: Cleared by User 1 PBCLK Period 0005: 0005: PRy OCxR 0000: OCx pin

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 0000 0000 0000 0001 0000 0000 0000 0001 0000 0000 Cleared by User

// The following code example illustrates how to define the initial // OC1 pin state for the output compare toggle mode of operation.

// Toggle mode with initial OC1 pin state set low

OC1CON = 0x0001;// Configure module for OC1 pin low, toggle high OC1CONSET = 0x8000;// Enable OC1 module

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-11

出力コンペア

例 16-2: コンペアモードでのトグルモードのピン状態のセットアップ (32 ビットモード ) 例16-3と例16-4に、シングルコンペア モードでのトグルイベントの設定と割り込みサービス のサンプルコードを示します。 例 16-3: コンペアモードでのトグルのセットアップと割り込みサービス (16 ビットモード ) // The following code example illustrates how to define the initial// OC1 pin state for the output compare toggle mode of operation. // Toggle mode with initial OC1 pin state set low

OC1CON = 0x0021;// Configure module for OC1 pin low, toggle high, // 32-bit mode

OC1CONSET = 0x8000;// Enable OC1 module

// The following code example will set the Output Compare 1 module // for interrupts on the toggle event and select Timer2 as the clock // source for the compare time base.

T2CON = 0x0010;// Configure Timer2 for a prescaler of 2 OC1CON = 0x0000;// Turn off OC1 while doing setup. OC1CON = 0x0003;// Configure for compare toggle mode OC1R = 0x0500;// Initialize Compare Register 1 PR2 = 0x0500;// Set period

// Configure int

IFS0CLR = 0x0040;// Clear the OC1 interrupt flag IEC0SET = 0x040;// Enable OC1 interrupt

IPC1SET = 0x001C0000;// Set OC1 interrupt priority to 7, // the highest level

IPC1SET = 0x00030000;// Set Subpriority to 3, maximum T2CONSET = 0x8000;// Enable Timer2

OC1CONSET = 0x8000;// Enable OC1

// Example code for Output Compare 1 ISR:

void __ISR(_OUTPUT_COMPARE_1_VECTOR, ipl7) OC1_IntHandler (void) {

// insert user code here

IFS0CLR = 0x0040; // Clear the OC1 interrupt flag }

例 16-4: コンペアモードでのトグルのセットアップと割り込みサービス (32 ビットモード ) // The following code example will set the Output Compare 1 module

// for interrupts on the toggle event and select the Timer2/Timer3 pair as // the 32-bit as the clock source for the compare time base.

T2CON = 0x0018;// Configure Timer2 for 32-bit operation // with a prescaler of 2.The Timer2/Timer3

// pair is accessed via registers associated // with the Timer2 register

OC1CON = 0x0000;// Turn off OC1 while doing setup. OC1CON = 0x0023;// Configure for compare toggle mode OC1R = 0x00500000;// Initialize Compare Register 1 PR2 = 0x00500000;// Set period (PR2 is now 32-bits wide)

// configure int

IFS0CLR = 0x00000040;// Clear the OC1 interrupt flag IFS0SET = 0x00000040;// Enable OC1 interrupt

IPC1SET = 0x001C0000;// Set OC1 interrupt priority to 7, // the highest level

IPC1SET = 0x00030000;// Set Subpriority to 3, maximum T2CONSET = 0x8000;// Enable Timer2

OC1CONSET = 0x8000;// Enable OC1

// Example code for Output Compare 1 ISR:

void__ISR (_OUTPUT_COMPARE_1_VECTOR, ipl7) OC1_IntlHandler (void) {

// Insert user code here

IFS0CLR = 0x0040; // Clear the OC1 interrupt flag }

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-13

出力コンペア

16.3.2

ダブルコンペア一致モード

OCM<2:0> 制御ビットを「100」または「101」に設定すると、対応する出力コンペア チャン ネルは下記の2 つのダブルコンペア一致モードのいずれかに設定されます。 • 単発出力パルスモード • 連続出力パルスモード ダブルコンペア一致モードの場合、モジュールはコンペア一致イベント用にOCxR レジスタとOCxRS レジスタを使います。タイマ TMRy のインクリメント値と OCxR レジスタ間でコンペ ア一致イベントが発生すると、OCx ピンでパルスの立ち上がり ( 前縁 ) エッジが生成されます。 このタイマがさらにインクリメントしてOCxRS レジスタとの間でコンペア一致イベントが発 生すると、OCx ピンでパルスの立ち下がり ( 後縁 ) エッジが生成されます。 16.3.2.1 ダブルコンペア モード : 単発出力パルス 出力コンペアモジュールを単発出力パルスモードに設定するには、OCM<2:0> 制御ビットを 「100」に設定します。加えてコンペア タイムベースを選択して有効にする必要があります。

このモードを有効にすると、出力ピンOCx は LOW に初期化され、タイムベースと OCxR レ ジスタ間のコンペア一致が発生するまでLOW を維持します。図16-10、図16-11、図16-12、

図16-13の下記のタイミング イベントに注目してください。

• コンペア タイムベースと OCxR レジスタ間のコンペア一致が発生すると、1 周辺モジュール 用クロック後にOCx ピンが HIGH に駆動されます。OCx ピンは、タイムベースと OCxRS

レジスタ間で次の一致イベントが発生するまで HIGH のままです。一致するとピンは LOW に駆動されます。OCx ピンはモードが変更されるかモジュールが無効になるまで LOW のま まです。 • コンペア タイムベースは対応する周期レジスタの値に一致するまでインクリメントし続け、 一致すると次の命令クロックで0x0000 にリセットします。 • タイムベース周期レジスタの値が OCxRS レジスタの値よりも小さい場合、パルスの立ち下 がりエッジは生成されません。OCx ピンは OCxRS ≤ PRy が成立するか、モードが変更され るか、リセット条件が発生するまでHIGH のままです。 • OCx ピンが LOW になると ( 単発パルスの立ち下がりエッジが発生すると )、対応するチャン ネル割り込みフラグOCxIF がセットされます。 図16-10と図16-11は一般的なダブルコンペア モードによる単発出力パルスの生成を示していま す。図16-12はOCxRS > PRy の場合のタイミング例を示しています。この例では、コンペア タ イムベースは0x4100 までインクリメントする前にリセットするため、パルスの立ち下がりエッ ジは発生しません。

図 16-10: ダブルコンペア モード (16 ビットモード ) 図 16-11: ダブルコンペア モード (32 ビットモード ) OCxIF 0000 3001 3002 3003 3004 3000 TMRy 4000 Cleared by User Note 1: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 2: OCxR = コンペアレジスタ、OCxRS = セカンダリ コンペアレジスタ 1 PBCLK Period 4000 3000 PRy OCxR 3006 OCx pin

TMRy Resets Here

3003 OCxRS 3005 OCxIF 0000: 0003: 0003: 0003: 0003: 0003: TMRy 0004: 1 PBCLK Period 0004: 0003: PRy OCxR 0003: OCx pin

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 0000 0000 0001 0002 0004 0005 0000 0006 0000 0000 Cleared by User 0003: 0003 0003: OCxRS 0003

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-15

出力コンペア

図 16-12: ダブルコンペア モード : 単発出力パルス (OCxRS > PRy、16 ビットモード ) 図 16-13: ダブルコンペア モード : 単発出力パルス (OCxRS > PRy、32 ビットモード ) OCxIF 0000 3001 3002 3003 3004 3000 TMRy 4000 1 PBCLK Period 4000 3000 PRy OCxR 3006 OCx pinTMRy Resets Here

4100 OCxRS

3005

Note 1: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。

2: OCxR = コンペアレジスタ、OCxRS = セカンダリ コンペアレジスタ

Compare Interrupt does not occur

OCxIF 0000: 0003: 0003: 0003: 0003: 0003: TMRy 0004: 1 PBCLK Period 0004: 0003: PRy OCxR 0003: OCx pin

TMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 0000 0000 0001 0002 0004 0005 0000 0006 0000 0000 0003: 0003 0004: OCxRS 1000

16.3.2.2 単発出力パルス生成の設定方法 OCM<2:0> 制御ビット (OCxCON<2:0>) を「100」に設定すると、対応する出力コンペア チャ ンネルはOCx ピンを LOW 状態に初期化し、単発出力パルスを生成します。 単発出力パルスを生成するには下記の手順が必要です( この手順はタイマ源が最初 OFF である 事を前提としていますが、これはモジュールを動作させるための必要条件ではありません)。 1. 周辺モジュール用クロックサイクル時間を決定します。 2. TMRy 開始値 (0x0000) から出力パルス立ち上がりエッジまでの時間を計算します。 3. パルス立ち上がりエッジまでの時間と目標パルス幅に基づいてパルス立ち下がりエッジま での時間を計算します。 4. 上記ステップ 2 および 3 で計算した値をそれぞれコンペアレジスタ OCxR とセカンダリ コ ンペアレジスタOCxRS に書き込みます。 5. タイマ周期レジスタ PRy の値をセカンダリ コンペアレジスタ OCxRS 以上の値に設定しま す。

6. OCM<2:0> を「100」に設定し、OCTSEL ビット (OCxCON<3>) で適切なタイマ源を選択 します。この時点でOCx ピンは LOW に駆動されます。

7. タイマを有効にします (ON 制御ビット (TxCON<15>) = 1)。

8. TMRy と OCxR の間で最初の一致が発生すると、OCx ピンが HIGH に駆動されます。 9. その後もタイマ TMRy はインクリメントし続け、今度はセカンダリ コンペアレジスタ

OCxRS と一致した時に OCx ピンが HIGH から LOW に遷移してパルスの立ち下がり ( 後縁 )

エッジが発生します。これ以降OCx ピンでパルスは発生せず、ピンは LOW のままです。 2 回目のコンペア一致イベントが発生すると OCxIF 割り込みフラグビットがセットされて 割り込みが発生します (OCxIE ビットをセットしてこの割り込みを有効にしている場合 )。 周辺モジュール割り込みの詳細はセクション 8.「割り込み」(DS61108) を参照してください。 10. もう一度単発パルス出力を生成するには、必要に応じてタイマおよびコンペアレジスタの 設定を変更した後に、OCM<2:0> 制御ビット (OCxCON<2:0>) を「100」に設定するため の書き込みを実行する必要があります。タイマの無効化/ 再有効化と TMRy レジスタのク リアは必須ではありませんが、それらの実行はイベント時間の区切りがはっきりわかるこ とからパルスの設定に有効かもしれません。 出力パルスの立ち下がりエッジの後で出力コンペア モジュールを無効にする必要はありませ ん。次のパルス生成はOCxCON レジスタに値を再度書き込む事により開始できます。

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-17

出力コンペア

例16-5と例16-6に、単発出力パルスイベントの設定用サンプルコードを示します。 例 16-5: 単発出力パルスのセットアップと割り込みサービス (16 ビットモード )

// The following code example will set the Output Compare 1 module // for interrupts on the single pulse event and select Timer2 // as the clock source for the compare time base.

T2CON = 0x0010;// Configure Timer2 for a prescaler of 2 OC1CON = 0x0000;// Turn off OC1 while doing setup. OC1CON = 0x0004;// Configure for single pulse mode OC1R = 0x3000;// Initialize primary Compare Register OC1RS = 0x3003;// Initialize secondary Compare Register PR2 = 0x3003;// Set period (PR2 is now 32-bits wide)

// configure int

IFS0CLR = 0x00000040;// Clear the OC1 interrupt flag IFS0SET = 0x00000040;// Enable OC1 interrupt

IPC1SET = 0x001C0000;// Set OC1 interrupt priority to 7, // the highest level

IPC1SET = 0x00030000;// Set Subpriority to 3, maximum T2CONSET = 0x8000;// Enable Timer2

OC1CONSET = 0x8000;// Enable OC1

// Example code for Output Compare 1 ISR:

void__ISR(_OUTPUT_COMPARE_1_VECTOR, ipl7) OC1_IntHandler (void) {

// Insert user code here

IFS0CLR = 0x0040; // Clear the OC1 interrupt flag }

例 16-6: 単発出力パルスのセットアップと割り込みサービス (32 ビットモード ) // The following code example will set the Output Compare 1 module // for interrupts on the single pulse event and select Timer2 // as the clock source for the compare time base.

T2CON = 0x0018;// Configure Timer2 for 32-bit operation // with a prescaler of 2.The Timer2/Timer3

// pair is accessed via registers associated // with the Timer2 register

OC1CON = 0x0000;// Turn off OC1 while doing setup. OC1CON = 0x0004;// Configure for single pulse mode OC1R = 0x00203000;// Initialize primary Compare Register OC1RS = 0x00203003;// Initialize secondary Compare Register PR2 = 0x00500000;// Set period (PR2 is now 32-bits wide) // configure int

IFS0CLR = 0x00000040;// Clear the OC1 interrupt flag IFS0SET = 0x00000040;// Enable OC1 interrupt

IPC1SET = 0x001C0000;// Set OC1 interrupt priority to 7, // the highest level

IPC1SET = 0x00030000;// Set Subpriority to 3, maximum T2CONSET = 0x8000;// Enable Timer2

OC1CONSET = 0x8000;// Enable OC1

// Example code for Output Compare 1 ISR:

void__ISR(_OUTPUT_COMPARE_1_VECTOR, ipl7) OC1_IntHandler (void) {

// insert user code here

IFS0CLR = 0x0040; // Clear the OC1 interrupt flag }

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-19

出力コンペア

16.3.2.3 ダブルコンペア モードで単発出力パルスを生成する場合の特殊なケース OCxR、OCxRS、PRy 値の大小関係によっては、出力コンペア モジュールに特殊な条件が発 生する事に注意が必要です。表 16-2 に、そのような特殊な条件と、それらによって生じるモ ジュールの挙動を示します。 表 16-2: ダブルコンペア モードで単発出力パルスを生成する場合の特殊なケース SFR の 論理的関係 特殊な条件 動作 OCx ピンの出力 PRy ≥ OCxRS かつ OCxRS > OCxR OCxR = 0 TMRy = 0 に初期化 最初に TMRy が 0x0000 から PRy までカウントする間 OCx は LOW のままであり、パルスは生成されない。周 期一致によりTMRy がゼロにリセットすると、OCx ピン はOCxR との一致により HIGH に遷移する。次に TMRy がOCxRS に一致すると、OCx ピンは LOW に遷移し、そ の状態を維持する。2 回目のコンペア一致の結果として OCxIF ビットがセットされる。他に下記の初期条件も考慮する必要がある:

- TMRy = PRy (PRy > 0) に初期化、かつ、OCxR = 0 に設定

パルスはPRy レ ジスタの値 に応 じて遅延する

PRy ≥ OCxR かつ

OCxR ≥ OCxRS OCxR ≥ 1 かつPRy ≥ 1 TMRy が OCxR までカウントアップしてコンペア一致イベント(TMRy = OCxR) が発生すると OCx ピンは HIGH に駆動される。TMRy は引き続きカウントし続け、周期 一致(PRy = TMRy) 時にリセットする。タイマは 0x0000 からカウントを再開し、OCxRS までカウントアップす る。コンペア一致イベント(TMRy = OCxRS) が発生する とOCx ピンは LOW に駆動される。2 回目のコンペア一 致の結果としてOCxIF ビットがセットされる。 パルスを生成 OCxRS > PRy かつ PRy ≥ OCxR なし OCx ピンで立ち上がりエッジだけが生成される。OCxIF ビットはセットされない。 立ち上がり エッ ジ/HIGH へ遷移 OCxR > PRy なし サポートされないモード。タイマは一致条件の前にリ セットする。 LOW のまま 凡例 : OCxR = コンペアレジスタ OCxRS = セカンダリ コンペアレジスタ TMRy = Timeryのカウント

PRy = Timery の周期レジスタ

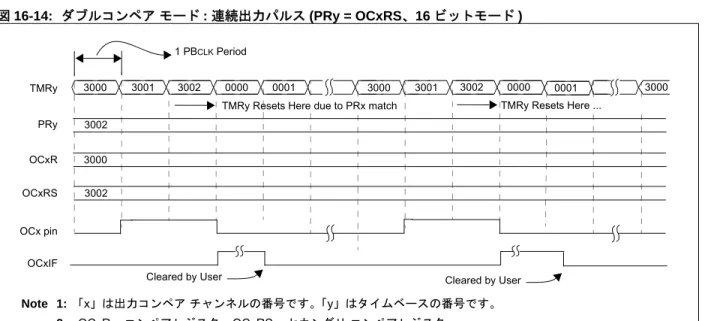

16.3.2.4 ダブルコンペア モード : 連続出力パルス

出力コンペア モジュールをこのモードで動作させるには、OCM<2:0> 制御ビットを「101」に 設定します。加えてコンペア タイムベースを選択して有効にする必要があります。このモー ドを有効にすると、出力ピンOCx は LOW に初期化され、コンペア タイムベースと OCxR レ ジスタ間のコンペア一致が発生するまでLOW を維持します。図16-14、図16-15、図16-16、

図16-7の下記のタイミング イベントに注目してください。

• コンペア タイムベースと OCxR レジスタ間のコンペア一致が発生すると、1PBCLK後にOCx ピンがHIGH に駆動されます。OCx ピンは、タイムベースと OCxRS レジスタ間で次の一致 イベントが発生するまでHIGH を維持し、一致すると LOW に駆動されます。OCx ピンは上 記のLOW から HIGH および HIGH から LOW への遷移によるパルス生成を繰り返します ( ユー ザによる介入は不要)。 • OCx ピンの連続的なパルス生成は、モードが変更されるかモジュールが無効になるまで続き ます。 • コンペア タイムベースは対応する周期レジスタの値に一致するまでインクリメントし続け、 一致すると次の命令クロックで0x0000 にリセットします。 • コンペア タイムベース周期レジスタの値が OCxRS レジスタの値よりも小さい場合、立ち下 がりエッジは生成されません。この場合、OCx ピンはモードが変更されるかデバイスがリ セットするまでHIGH のままです。 • OCx ピンが LOW になると ( 単発パルスの立ち下がりエッジが発生すると )、対応するチャン ネル割り込みフラグOCxIF がセットされます。 図16-14と図16-15はダブルコンペア モードで連続出力パルスを生成する場合の一般的動作を 示しています。図16-16はOCxRS > PRy の場合のタイミング例を示しています。この例では、 タイムベースはOCxRS の値に一致する前にリセットするため、パルスの立ち下がりエッジは 発生しません。 図 16-14: ダブルコンペア モード : 連続出力パルス (PRy = OCxRS、16 ビットモード ) Note 1: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 2: OCxR = コンペアレジスタ、OCxRS = セカンダリ コンペアレジスタ OCxIF 0000 3001 3002 0000 0001 3000 TMRy 3002 Cleared by User 1 PBCLK Period 3002 3000 PRy OCxR 3000 OCx pin 3002 OCxRS 3001 0001 3000

TMRy Resets Here due to PRx match TMRy Resets Here ...

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-21

出力コンペア

図 16-15: ダブルコンペア モード : 連続出力パルス (PRy = OCxRS、32 ビットモード ) 図 16-16: ダブルコンペア モード : 連続出力パルス (OCxRS > PRy 、16 ビットモード ) OCxIF 0000: 0003: 0000: 0003: TMRy 0000: 1 PBCLK Period 0003: 0003: PRy OCxR 0003: OCx pinTMRy Resets Here

Note: 「x」は出力コンペア チャンネルの番号です。「y」はタイムベースの番号です。 0000 0000 0001 0000 0001 0001 0001 0002 Cleared by User 0000: 0001 0003: OCxRS 0001 0000: 0000 0003: 0000 TMRy Resets Here

Cleared by User

Note 1: OCxRS レジスタの値を周期レジスタ (PRy) の値以下に変更するまで OCx ピンは HIGH のままであり、OCxIF はセッ

16.3.2.5 連続出力パルス生成の設定方法 OCM<2:0> 制御ビットを「101」に設定すると、対応する出力コンペア チャンネルは OCx ピ ンをLOW に初期化し、コンペア一致イベントが発生するたびに出力パルスを繰り返し生成し ます。 連続出力パルスを生成するようモジュールを設定するには下記の手順が必要です( これらの手 順はタイマ源が最初OFF である事を前提としていますが、これはモジュールを動作させるため の必要条件ではありません)。 1. 周辺モジュール用クロックサイクル時間を決定します。この際、タイマソースへの外部ク ロック周波数( 使用する場合 ) と、タイマ プリスケーラ設定を考慮する必要があります。 2. TMRy 開始値 (0x0000) から出力パルス立ち上がりエッジまでの時間を計算します。 3. パルス立ち上がりエッジまでの時間と目標パルス幅に基づいてパルス立ち下がりエッジま での時間を計算します。 4. 上記ステップ 2 および 3 で計算した値をそれぞれコンペアレジスタ OCxR とセカンダリ コ ンペアレジスタOCxRS に書き込みます。 5. タイマ周期レジスタ PRy の値をセカンダリ コンペアレジスタ OCxRS 以上の値に設定しま す。

6. OCM<2:0> を「101」に設定し、OCTSEL ビット (OCxCON<3>) で適切なタイマ源を選択 します(16 ビットモードのみ )。この時点で OCx ピンは LOW に駆動されます。

7. TON ビット (TyCON<15>) を「1」にセットしてコンペア タイムベースを有効にします。 8. TMRy と OCxR の間で最初の一致が発生すると、OCx ピンが HIGH に駆動されます。 9. その後もコンペア タイムベース TMRy はインクリメントし続け、今度はセカンダリ コン

ペアレジスタOCxRS と一致した時に OCx ピンが HIGH から LOW に遷移してパルスの立 ち下がり( 後縁 ) エッジが発生します。 10. 2 回目のコンペア一致イベントの結果として OCxIF 割り込みフラグビットがセットされま す。 11. コンペア タイムベースが対応する周期レジスタに一致すると、TMRy レジスタは 0x0000 にリセットした後にカウントを再開します。 12. ステップ 8 ~ 11 を繰り返す事により、パルス生成を無限に繰り返します。OCxIF フラグは OCxRS と TMRy 間のコンペア一致イベントが発生するたびにセットされます ( 各チャンネ ルの割り込みフラグのビット位値についてはIFS0 レジスタの説明を参照 )。

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-23

出力コンペア

例16-7と例16-8に、連続出力パルスイベントの設定用サンプルコードを示します。 例 16-7: 連続出力パルスのセットアップと割り込みサービス (16 ビットモード )

// The following code example will set the Output Compare 1 module // for interrupts on the continuous pulse event and select Timer2 // as the clock source for the compare time-base.

T2CON = 0x0010;// Configure Timer2 for a prescaler of 2 OC1CON = 0x0000;// Disable OC1 module

OC1CON = 0x0005;// Configure OC1 module for Pulse output OC1R = 0x3000;// Initialize Compare Register 1

OC1RS = 0x3003;// Initialize Secondary Compare Register 1 PR2 = 0x5000;// Set period

// configure int

IFS0CLR = 0x00000040;// Clear the OC1 interrupt flag IFS0SET = 0x00000040;// Enable OC1 interrupt

IPC1SET = 0x001C0000;// Set OC1 interrupt priority to 7, // the highest level

IPC1SET = 0x00030000;// Set Subpriority to 3, maximum T2CONSET = 0x8000;// Enable Timer2

OC1CONSET = 0x8000;// Enable OC1

// Example code for Output Compare 1 ISR:

void__ISR(_OUTPUT_COMPARE_1_VECTOR, ipl7) OC1_IntHandler (void) {

// insert user code here

IFS0CLR= 0x0040; // Clear the OC1 interrupt flag }

例 16-8: 連続出力パルスのセットアップと割り込みサービス (32 ビットモード ) // The following code example will set the Output Compare 1 module // for interrupts on the continuous pulse event and select Timer2 // as the clock source for the compare time-base.

T2CON = 0x0018;// Configure Timer2 for 32-bit operation // with a prescaler of 2.The Timer2/Timer3

// pair is accessed via registers associated // with the Timer2 register

OC1CON = 0x0000;// disable OC1 module

OC1CON = 0x0005;// Configure OC1 module for Pulse output OC1R = 0x3000;// Initialize Compare Register 1

OC1RS = 0x3003;// Initialize Secondary Compare Register 1 PR2 = 0x00500000;// Set period (PR2 is now 32-bits wide)

// configure int

IFS0CLR = 0x00000040;// Clear the OC1 interrupt flag IFS0SET = 0x00000040;// Enable OC1 interrupt

IPC1SET = 0x001C0000;// Set OC1 interrupt priority to 7, // the highest level

IPC1SET = 0x00030000;// Set Subpriority to 3, maximum T2CONSET = 0x8000;// Enable Timer2

OC1CONSET = 0x8000;// Enable OC1

// Example code for Output Compare 1 ISR:

void__ISR(_OUTPUT_COMPARE_1_VECTOR, ipl7) OC1_IntHandler (void) {

// insert user code here

IFS0CLR = 0x0040; // Clear the OC1 interrupt flag }

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-25

出力コンペア

16.3.2.6 ダブルコンペア モードで連続出力パルスを生成する場合の特殊なケース OCxR、OCxRS、PRy 値の大小関係によっては、出力コンペア モジュールが予期せぬ結果を 生じる場合があります。表16-3に、そのような特殊なケースと、それらによって生じるモジュー ルの挙動を示します。 表 16-3: ダブルコンペア モードで連続出力パルスを生成する場合の特殊なケース(1) SFR の 論理的関係 特殊な条件 動作 OCx ピンの出力 PRy ≥ OCxRS かつ OCxRS > OCxR OCxR = 0 TMRy = 0 に初期 化 最初にTMRy が 0x0000 から PRy までカウントす る間OCx は LOW のままであり、パルスは生成され ない。周期一致によりTMRy がゼロにリセットする と、OCx ピンは HIGH に遷移する。次に TMRy が OCxRS に一致すると、OCx ピンは LOW に遷移す る。OCxR = 0 かつ PRy = OCxRS の場合、ピンは 1 クロックサイクル LOW を維持した後に HIGH に 駆動され、次に TMRy が OCxRS に一致するまで HIGH を維持する。2 回目のコンペア一致の結果と してOCxIF ビットがセットされる。他に下記の2 つの初期条件も考慮する必要がある : - TMRy = PRy (PRy > 0) に初期化、かつ、OCxR = 0 に設定 連続パルスを生成す るが、最初のパルス はPRy レジスタの値 に応じて遅延する PRy ≥ OCxR かつ

OCxR ≥ OCxRS OCxR ≥ 1 かつPRy ≥ 1 TMRy が OCxR までカウントアップしてコンペア一致イベント(TMRy = OCxR) が発生すると OCx ピン はHIGH に駆動される。TMRy は引き続きカウント し続け、周期一致(PRy = TMRy) 時にリセットする。 タイマは0x0000 からカウントを再開し、OCxRS ま で カ ウン ト ア ッ プ す る。コ ン ペ ア 一 致 イ ベ ン ト (TMRy = OCxRS) が発生すると OCx ピンは LOW に

駆動される。2 回目のコンペア一致の結果として OCxIF ビットがセットされる。 連続パルスを生成 OCxRS > PRy かつ PRy ≥ OCxR なし OCxRS レジスタの値を周期レジスタ (PRy) 以下の 値に変更するまで、OCx ピンでは 1 回の状態遷移 しか発生しない。それまで OCxIF はセットされな い。 立ち上がりエッジで HIGH へ遷移 OCxR > PRy なし サポートされないモード。タイマは一致条件の前に リセットする。 LOW のまま

凡例 : OCxR = コンペアレジスタ OCxRS = セカンダリ コンペアレジスタ TMRy = Timery のカウント PRy = Timery の周期レジスタ

16.3.3

パルス幅変調モード

OCM<2:0> 制御ビットを「110」または「111」に設定すると、対応する出力コンペア チャン ネルの動作はPWM モードに設定されます。 下記の2 つの PWM モードが存在します。 • フォルト保護入力なし PWM • フォルト保護入力あり PWM OCFA または OCFB フォルト入力ピンは「フォルト保護入力あり PWM」モードで使います。 このモードでは、OCFx ピンで論理レベル「0」( 非同期 ) が発生すると、対応する PWM チャ ンネルがシャットダウンします。16.3.3.1「フォルト保護入力ピンを使う PWM モード」を参 照してください。 PWM モードでは、OCxR レジスタは読み出し専用のスレーブ デューティサイクル レジスタと して機能し、OCxRS レジスタはバッファレジスタとして機能します。ユーザは OCxRS レジ スタに書き込む事によってPWM デューティサイクルを更新できます。PWM 周期の最後でタ イマが周期レジスタに一致するたびに、デューティサイクル レジスタ OCxR に OCxRS レジス タの値が転送されます。TyIF 割り込みフラグは PWM 周期の境界で毎回セットされます。 出力コンペア モジュールを PWM 動作向けに設定するには、以下の手順を実行する必要があり ます。 1. 選択したタイマ周期レジスタ (PRy) に書き込む事によって PWM 周期を設定する。 2. OCxRS レジスタに書き込む事によって PWM デューティサイクルを設定する。 3. OCxR レジスタに初期の PWM デューティサイクルを書き込む。 4. 必要に応じて、タイマと出力コンペア モジュールの割り込みを有効にする (PWM フォルト ピンを使う場合、出力コンペア割り込みが必要です)。 5. 出力コンペアモード ビット OCM<2:0> (OCxCON<2:0>) に書き込む事により、出力コンペ ア モジュールを 2 つある PWM 動作モードのいずれかに設定する。6. TMRy プリスケール値を設定し、TON ビット (TxCON<15>) を「1」にセットする事により タイムベースを有効にする。 図16-17に、PWM 出力波形の例を示します。 図 16-17: PWM 出力波形 Note: 出力コンペア モジュールを有効にする前に OCxR レジスタを初期設定する必要が あります。モジュールがPWM モードで動作中、OCxR レジスタは読み出し専用の デューティサイクル レジスタとして機能します。OCxR レジスタの保持値は最初 のPWM 周期の PWM デューティサイクルとして使われます。デューティサイクル バッファレジスタOCxRS の値は、タイムベース周期一致が発生するまで OCxRS レジスタに転送されません。 Period = (PRy + 1)

Duty Cycle = (OCxRS)

Timery がクリアされ、新しいデューティサイクル値が OCxRS から OCxR に転送される。

タイマ値がOCxR レジスタ値と一致し、OCx ピンは LOW に駆動される。

タイマがオーバーフローし、OCxRS の値が OCxR に転送され、OCx ピンは HIGH に駆動される。

2 1 3 2 3 1 TyIF 割り込みフラグがセットされる。

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-27

出力コンペア

16.3.3.1 フォルト保護入力ピンを使う PWM モード OCM<2:0> 制御ビットを「111」に設定すると、対応する出力コンペア チャンネルの動作は PWM モードに設定されます。このモードでは、16.3.3「パルス幅変調モード」に記載した全て の機能に加えて入力フォルト保護機能が有効になります。フォルト保護にはOCFA ピンと OCFB ピンを使います。OCFA ピンは出力コンペア チャンネ ル1 ~ 4 に対応し、OCFB ピンは出力コンペア チャンネル 5 に対応します。 OCFA/OCFB ピンで論理「0」を検出すると、対応する PWM 出力ピンは 3 ステートになりま す。ユーザは、PWM ピンにプルダウンまたはプルアップ抵抗を適用する事により、フォルト 条件が発生した時に PWM ピンを適切な状態にできます。PWM 出力は即時にシャットダウン し、デバイスのクロック源から切断されます。この状態は下記の両条件が成立するまで続きま す。 1. 外部フォルト条件が解除された 2. 適切なモードビット (OCM<2:0> ビット (OCxCON<2:0>)) への書き込みによって PWM モー ドが再度有効にされた フォルト条件の結果として、対応する割り込みフラグビットOCxIF がセットされ、割り込みが 生成されます( 割り込みを有効にしている場合 )。フォルト条件を検出すると、OCFLT ビット (OCxCON<4>) が HIGH( 論理「1」) にセットされます。このビットは読み出し専用であり、外 部フォルト条件が解除され適切なモードビット(OCM<2:0> (OCxCON<2:0>)) への書き込みに よってPWM モードが再度有効にされるまでクリアされません。 16.3.3.2 PWM 周期 PWM 周期は Timery 周期レジスタ (PRy) に書き込む事により指定します。PWM 周期は下式で 計算できます。 式 16-1: PWM 周期の計算 PWM 周期は、周期レジスタのビット幅を超えない範囲で設定する必要があります (16 ビット モードでは16 ビット幅、32 ビットモードでは 32 ビット幅 )。計算で求めた周期が大きすぎる 場合、オーバーフローを防ぐためにより大きなプリスケーラを選択する必要があります。PWM 分解能を可能な限り高くするには、オーバーフローしない範囲で最小のプリスケーラを選択し ます。 Note: 外部フォルトピンを有効にして使う場合、デバイスがスリープまたはアイドルモー ド中であってもフォルトピンは対応するOCx 出力ピンを制御し続けます。

PWM Period = [(PR + 1)

•

TPB•

(TMR Prescale Value)] PWM Frequency = 1/[PWM Period]Note: PRy 値を N とした場合、PWM 周期は [N + 1] タイムベース カウントサイクルです。 例えばPRy レジスタに「7」を書き込んだ場合の PWM 周期は 8 タイムベースサイ クルです。

16.3.3.3 PWM デューティ サイクル PWM デューティ サイクルは OCxRS レジスタに書き込む事により指定します。OCxRS レジス タはいつでも書き込み可能ですが、PRy と TMRy が一致するまで ( すなわち 1 周期が終了する まで) デューティ サイクル値は OCxRS から OCxR へラッチされません。これは PWM デュー ティ サイクルにダブルバッファを提供し、PWM 動作のグリッチを防ぐために重要な働きをし ます。PWM モードでは、OCxR レジスタは読み出し専用です。 PWM デューティ サイクルの重要境界条件を以下に挙げます。

• デューティ サイクルレジスタ OCxR に 0000h を書き込むと、OCx ピンは LOW のままになる (0% デューティ サイクル )

• OCxRS の値がタイマ周期レジスタ PRy よりも大きい場合、ピンは HIGH のままになる (100% デューティ サイクル )

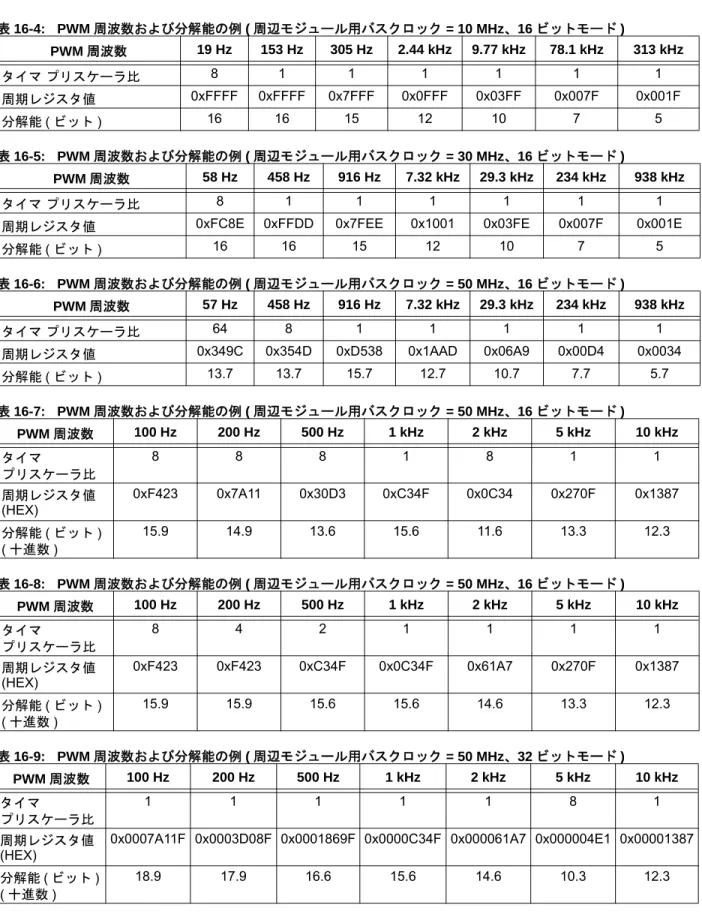

• OCxR が PRy に等しい場合、OCx ピンは 1 タイムベースカウント値だけ LOW になり、他の 全てのカウント値ではHIGH になる 図16-18と図16-19にPWM モードの詳細なタイミングを示します。表16-4~表16-9に、各 周辺モジュール用バス周波数におけるPWM 周波数と分解能を示します。 式 16-2: 最高 PWM 分解能の計算式 式 16-3: PWM 周期および分解能の計算式

(

)

Maximum PWM Resolution (bits) =

FPB

FPWM

•

TMRy•

Prescaler bitslog10

log10(2)

目標PWM 周波数 = 52.08 kHz FPB = 10 MHz Timer2 プリスケーラ設定 : 1:1

1/52.08 kHz = (PR2 + 1)

•

TPB•

(Timer2 prescale value) 19.20 s = (PR2 + 1)•

0.1 s•

(1) PR2 = 191 周辺モジュール用バスクロック周波数が10 MHz の場合、PWM 周波数 52.08 kHz で使える . 1/52.08 kHz = 2PWMRESOLUTION•

1/10 MHz•

1 19.20 s = 2PWMRESOLUTION•

100 ns•

1 192 = 2PWMRESOLUTIONlog10(192) = (PWM Resolution)

•

log10(2)PWM Resolution = 7.6 bits

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-29

出力コンペア

図 16-18: PWM 出力のタイミング (16 ビットモード ) 図 16-19: PWM 出力のタイミング (32 ビットモード ) 0002 0000 0001 0002 0003 0005 TMR3 0001 1 PBCLK Period 0005 0002 PR3 OCxR 0005 OCx pin 0002 OCxRS 0000 0003 0005 0004 0004 0001User Code Writes New Value to OCxRS In ISR 0001

Hardware Loads New Duty Cycle Here

Note 1: 「x」は出力コンペア チャンネルの番号です。

2: OCxR = コンペアレジスタ、OCxRS = セカンダリ コンペアレジスタ

T3IF is Set

OCxR = OCxRS T3IF is Set

OCxR = OCxRS 0000: 0000: 0000: 0000: 0000: 0005: TMR2 0000: 1 PBCLK Period 0000: 0000: PR2 OCxR 0000: OCx pin

Hardware Loads New Duty Cycle Here

Note: 「x」は出力コンペア チャンネルの番号です。 0002 0000 0000 0001 0003 0004 0005 0005 0001 0002 0000: 0002 0000: OCxRS 0002 0000: 0000 0000: 0001 0000: 0001 User Code Writes New Value to OCxRS in ISR

表 16-4: PWM 周波数および分解能の例 ( 周辺モジュール用バスクロック = 10 MHz、16 ビットモード ) PWM 周波数 19 Hz 153 Hz 305 Hz 2.44 kHz 9.77 kHz 78.1 kHz 313 kHz タイマ プリスケーラ比 8 1 1 1 1 1 1 周期レジスタ値 0xFFFF 0xFFFF 0x7FFF 0x0FFF 0x03FF 0x007F 0x001F 分解能( ビット ) 16 16 15 12 10 7 5 表 16-5: PWM 周波数および分解能の例 ( 周辺モジュール用バスクロック = 30 MHz、16 ビットモード ) PWM 周波数 58 Hz 458 Hz 916 Hz 7.32 kHz 29.3 kHz 234 kHz 938 kHz タイマ プリスケーラ比 8 1 1 1 1 1 1

周期レジスタ値 0xFC8E 0xFFDD 0x7FEE 0x1001 0x03FE 0x007F 0x001E

分解能( ビット ) 16 16 15 12 10 7 5 表 16-6: PWM 周波数および分解能の例 ( 周辺モジュール用バスクロック = 50 MHz、16 ビットモード ) PWM 周波数 57 Hz 458 Hz 916 Hz 7.32 kHz 29.3 kHz 234 kHz 938 kHz タイマ プリスケーラ比 64 8 1 1 1 1 1 周期レジスタ値 0x349C 0x354D 0xD538 0x1AAD 0x06A9 0x00D4 0x0034 分解能( ビット ) 13.7 13.7 15.7 12.7 10.7 7.7 5.7 表 16-7: PWM 周波数および分解能の例 ( 周辺モジュール用バスクロック = 50 MHz、16 ビットモード ) PWM 周波数 100 Hz 200 Hz 500 Hz 1 kHz 2 kHz 5 kHz 10 kHz タイマ プリスケーラ比 8 8 8 1 8 1 1 周期レジスタ値 (HEX) 0xF423 0x7A11 0x30D3 0xC34F 0x0C34 0x270F 0x1387 分解能( ビット ) ( 十進数 ) 15.9 14.9 13.6 15.6 11.6 13.3 12.3 表 16-8: PWM 周波数および分解能の例 ( 周辺モジュール用バスクロック = 50 MHz、16 ビットモード ) PWM 周波数 100 Hz 200 Hz 500 Hz 1 kHz 2 kHz 5 kHz 10 kHz タイマ プリスケーラ比 8 4 2 1 1 1 1 周期レジスタ値 (HEX) 0xF423 0xF423 0xC34F 0x0C34F 0x61A7 0x270F 0x1387 分解能( ビット ) ( 十進数 ) 15.9 15.9 15.6 15.6 14.6 13.3 12.3 表 16-9: PWM 周波数および分解能の例 ( 周辺モジュール用バスクロック = 50 MHz、32 ビットモード ) PWM 周波数 100 Hz 200 Hz 500 Hz 1 kHz 2 kHz 5 kHz 10 kHz タイマ プリスケーラ比 1 1 1 1 1 8 1 周期レジスタ値 (HEX)

0x0007A11F 0x0003D08F 0x0001869F 0x0000C34F 0x000061A7 0x000004E1 0x00001387 分解能( ビット )

( 十進数 )

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-31

出力コンペア

例16-9と例16-10に、PWM モード動作向けの設定および割り込みサービスのサンプルコード

を示します。

例 16-9: PWM モードのセットアップと割り込みサービス (16 ビットモード ) // The following code example will set the Output Compare 1 module // for PWM mode with Fault pin disabled and for 50% duty cycle. // Timer2 is selected as the clock for the PWM time base, and Timer2 // interrupts are enabled.

#include <plib.h> int main(void) {

INTEnableSystemMultiVectoredInt(); // Enable system wide interrupt to // multivectored mode.

OC1CON = 0x0000; // Turn off the OC1 when performing the setup OC1R = 0x0064; // Initialize primary Compare register

OC1RS = 0x0064; // Initialize secondary Compare register OC1CON = 0x0006; // Configure for PWM mode without Fault pin

// enabled PR2 = 0x00C7; // Set period

// Configure Timer2 interrupt.Note that in PWM mode, the // corresponding source timer interrupt flag is asserted. // OC interrupt is not generated in PWM mode.

IFS0CLR = 0x00000100; // Clear the T2 interrupt flag IEC0SET = 0x00000100; // Enable T2 interrupt

IPC2SET = 0x0000001C; // Set T2 interrupt priority to 7 T2CONSET = 0x8000; // Enable Timer2

OC1CONSET = 0x8000; // Enable OC1 while(1); // Never return }

// Example code for Timer2 ISR

void __ISR(_TIMER_2_VECTOR, ipl7) T2_IntHandler (void) {

// Insert user code here

IFS0CLR = 0x0100; // Clearing Timer2 interrupt flag }

例 16-10: PWM モードのセットアップと割り込みサービス (32 ビットモード ) // The following code example will set the Output Compare 1 module // for PWM mode with Fault pin disabled and for 50% duty cycle. // Timer2 and Timer3 are selected as the clocks for the PWM time base // in 32-bit mode, and Timer3 interrupts are enabled.

#include <plib.h> int main(void) {

INTEnableSystemMultiVectoredInt();// Enable system wide interrupt to multivectored mode. OC1CON = 0x0000; // Turn off the OC1 when performing the setup

OC1R = 0x00638000; // Initialize primary Compare register OC1RS = 0x00638000; // Initialize secondary Compare register

OC1CON = 0x0006; // Configure for PWM mode without Fault pin enabled T2CONSET = 0x0008; // Enable 32-bit Timer mode

PR2 = 0x00C6FFFF; // Set period

// Configure Timer3 interrupt.Note that in PWM mode, the corresponding source timer // interrupt flag is asserted.OC interrupt is not generated in PWM mode.

IFS0CLR = 0x00001000; // Clear the T3 interrupt flag IEC0SET = 0x00001000; // Enable T3 interrupt

IPC3SET = 0x0000001C; // Set T3 interrupt priority to 7 T2CONSET = 0x8000; // Enable Timer2

OC1CONSET = 0x8020; // Enable OC1 in 32-bit mode. while(1); // Never return

}

// Example code for Timer3 ISR:

void __ISR(_TIMER_3_VECTOR, ipl7) T3_IntHandler (void) {

// Insert user code here

IFS0CLR = 0x1000; // Clearing Timer3 interrupt flag }

© 2013 Microchip Technology Inc. DS61111E_JP - p. 16-33

出力コンペア

16.4

割り込み

各出力コンペア チャンネルは、専用の割り込みビット OCxIF と対応する割り込みイネーブル / マスクビットOCxIE を備えています。これらのビットは、割り込み要因を特定するためと、対 応する割り込み要因を有効または無効にするために使います。各チャンネルの優先度も別々に 設定できます。 出力コンペア チャンネルが割り込み生成イベントとして定義されている一致条件を検出する と、OCxIF ビットがセットされます。OCxIF ビットは、対応する OCxIE ビットの状態に関係なくセットされます。必要に応じてソフトウェアでOCxIF ビットをポーリングできます。

OCxIEビットは、対応するOCxIFビットがセットされた時のベクタ割り込みコントローラ(VIC) の挙動を定義するために使います。OCxIE ビットがクリアされている場合、対応する OCxIF ビットがセットされても、VIC モジュールは CPU 割り込みを生成しません。OCxIE ビットが セットされている場合、対応するOCxIF ビットがセットされると VIC モジュールは CPU に対 して割り込みを生成します( 後述の優先度と副優先度に従う )。 特定の割り込みをサービスするルーチンは、サービスルーチンを完了する前に、対応する割り 込みフラグビットをクリアする必要があります。 各出力コンペア チャンネルの割り込み優先度は OCxIP<2:0> ビットを使って別々に設定できま す。この優先度はその割り込み要因が属するグループの優先度を定義します。各優先度グルー プは7 ( 最優先 ) から 0 ( 割り込みを生成しない ) の優先度を持ちます。ある割り込みをサービ スしている時に、これよりも高い優先度を持つグループに属する割り込みが発生した場合、サー ビス中の割り込みは保留されます。 副優先度ビットにより、同一優先度グループに属する割り込み要因に異なる優先度を設定でき ます。副優先度の値(OCxIS<1:0>) は、3 ( 最優先 ) から 0 ( 最低優先度 ) の間で設定できます。 ある割り込みのサービス中に、優先度グループが同じで副優先度がより高い割り込みが発生し ても、サービス中の副優先度の低い割り込みは保留されません。 複数の割り込み要因に同一の優先度と副優先度を割り当てる事もできます。そのように設定し た複数の割り込みが同時に発生した場合、それらの各割り込み要因が持つ自然順序優先度に よって、生成される割り込みが決まります。自然順序優先度は、割り込み要因のベクタ番号に 基づきます。ベクタ番号が小さいほど割り込みの自然順序優先度は高くなります。自然順序優 先度に従って保留された割り込み要因は、サービス中の割り込みの割り込みフラグがクリアさ れた後に、優先度、副優先度、自然順序優先度に基づいて順番に割り込みを生成します。 有効な割り込みが発生すると、CPU はその割り込みに割り当てられているベクタへジャンプし ます。割り込みのベクタ番号がそのまま自然優先順位となります。CPU はジャンプ先のベクタ アドレスからコードの実行を始めます。このベクタアドレスにおけるユーザコードは、必要な 動作( デューティサイクルのリロード、割り込みフラグのクリア等 ) を全て実行した後に終了 する必要があります。ベクタアドレス テーブルの詳細はセクション 8.「割り込み」(DS61108) を参照してください。

16.5

I/O ピンの制御

有効にした出力コンペア モジュールは I/O ピンの方向を制御します。出力コンペア モジュール を無効にすると、I/O ピンの制御は対応する LAT および TRIS 制御ビットの設定に従います。 「フォルト保護入力あり」のPWM モードを有効にする場合、対応する TRIS SFR ビットをセッ トする事により、OCFx フォルトピンを入力として設定する必要があります。PWM フォルト モードを選択しても、OCFx フォルト入力ピンは自動的に入力として設定されません。 表 16-10: 出力コンペア モジュール 1 ~ 5 に割り当てられているピン ピン名 モジュール 制御 ピン タイプ バッファ タイプ 内容 OC1 ON O — 出力コンペア/PWM チャンネル 1 OC2 ON O — 出力コンペア/PWM チャンネル 2 OC3 ON O — 出力コンペア/PWM チャンネル 3 OC4 ON O — 出力コンペア/PWM チャンネル 4 OC5 ON O — 出力コンペア/PWM チャンネル 5 OCFA ON I ST PWM フォルト保護 A 入力 ( チャンネル 1 ~ 4 用 ) OCFB ON I ST PWM フォルト保護 B 入力 ( チャンネル 5 用 ) 凡例 : ST = CMOS レベルのシュミットトリガ入力 I = 入力O = 出力