XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 1 © Copyright 2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

概要

こ のアプ リ ケーシ ョ ン ノ ー ト では、7 シ リ ーズ FPGA が備え る 専用の SelectIO™ テ ク ノ ロ ジデシ リ ア ラ イ ザー コ ン ポーネ ン ト (ISERDESE2 プ リ ミ テ ィ ブ) を使用 し 、 シ リ アル LVDS (低電力差動信号) 出 力を用いて アナ ロ グデジ タ ルコ ンバー タ ー (ADC) と 接続す る 方法を説明 し ます。リ フ ァ レ ン スデザ イ ンは、 高速シ リ アル LVDS 出力を備えた ADC へ Kintex™-7 FPGA を接続す る 基 本の LVDS イ ン タ ーフ ェ イ ス と な っ てい ます。

は じ めに

最近の高速 ADC は、12、14、 ま たは 16 ビ ッ ト の分解能を提供 し 、 通常はシ ン グルパ ッ ケージ内に複 数個の コ ンバー タ ーが含まれてい ます。パ ッ ケージ内の各 コ ンバー タ ーは ス タ ン ド ア ロ ン モー ド で使用 で き ますが、 複数の コ ンバー タ ーを組み合わせて イ ン タ ー リ ーブモー ド で使用す る こ と で、 変換 (サン プル) 速度 2 倍ま たは 4 倍にで き ます。 ス タ ン ド ア ロ ンモー ド と イ ン タ ー リ ーブモー ド のいずれの場合で も 、 イ ン タ ーフ ェ イ ス先のデバ イ ス への接続 と し て、 物理的シ リ アル出力を 1 つま たは 2 つ使用で き ます。1 組の差動出力はデー タ レーン と 呼ばれてい ます。1 デー タ レーン を使用す る と い う こ と は、 コ ンバー タ ーが 1 ワ イ ヤモー ド で使用 さ れ、2 デー タ レーンでは 2 ワ イ ヤモー ド で使用 さ れ る こ と を意味 し ます。 すべてのデー タ 出力の組み合 わせには、常に高速ビ ッ ト ク ロ ッ ク と サンプルレー ト フ レームク ロ ッ ク がそれぞれ 1 つずつあ り ます。 1 ワ イ ヤモー ド は、SDR お よ び DDR コ ン フ ィ ギ ュ レーシ ョ ン モー ド で使用 さ れますが、2 ワ イ ヤモー ド は DDR モー ド のみです。 1 ワ イ ヤモー ド では内部接続数を抑え る こ と が可能で、 通常はパ ッ ケージ内の各 コ ンバー タ ーに対 し て 1 デー タ レーン を使用 し ます。 ま た、 こ のモー ド では 1 つの コ ンバー タ ーのデー タ を出力 し た り 、 ま た は イ ン タ ー リ ーブ方式で 2 つの コ ンバー タ ーのデー タ を出力で き ます。 1 ワ イ ヤモー ド での 2 つの コ ンバー タ ーの例 • 一方の コ ンバー タ ーはビ ッ ト ク ロ ッ ク の立ち上が り エ ッ ジでデー タ を出力 し 、 も う 一方は ク ロ ッ ク の立ち下が り エ ッ ジでデー タ を出力す る 。 • ビ ッ ト ク ロ ッ ク レー ト が 2 倍にな る ため、 こ れはあ ま り 使用 さ れない。 2 ワ イ ヤモー ド では、ADC と イ ン タ ーフ ェ イ ス先のデバ イ ス間の接続数が 2 倍にな り ますが、 ビ ッ ト ク ロ ッ ク を 2 分周す る こ と で大 き な利点を得 る こ と がで き ます。 シ ン グル コ ンバー タ ーの場合、 ビ ッ ト ク ロ ッ ク の周波数を変更せずにサンプル ク ロ ッ ク を 2 倍に し た り 、 ビ ッ ト ク ロ ッ ク を 2 分周 し てサンプルク ロ ッ ク レー ト を その ま ま保持で き ます。 ど ち ら の場合で も 、 デー タ は 2 つのデー タ レーンで イ ン タ ー リ ーブ方式で出力 さ れます。FPGA の SelectIO テ ク ノ ロ ジに よ る デシ リ ア ラ イ ザー コ ン ポーネ ン ト は、ISERDESE2 プ リ ミ テ ィ ブ と し て構成 さ れます。2 つの ISERDESE2 を SDR モー ド で使用 し て、DDR 信号を キ ャ プチ ャ し ます。 一方の ISERDESE2 は、 ビ ッ ト ク ロ ッ ク (CLK) の立ち上が り エ ッ ジで、 も う 一方の ISERDESE2 は立 ち下が り エ ッ ジで ク ロ ッ ク さ れます。 こ の方法では、 各 ISERDESE2 が 8 ビ ッ ト を キ ャ プチ ャ で き る た め、 最大 16 ビ ッ ト を キ ャ プチ ャ 可能です。 XAPP524 (v1.0) 2012 年 8 月 7 日

シ リ アル

LVDS

高速

ADC

イ ン タ ー フ ェ イ ス

著者 : Marc DefossezFPGA

の リ ソ ース

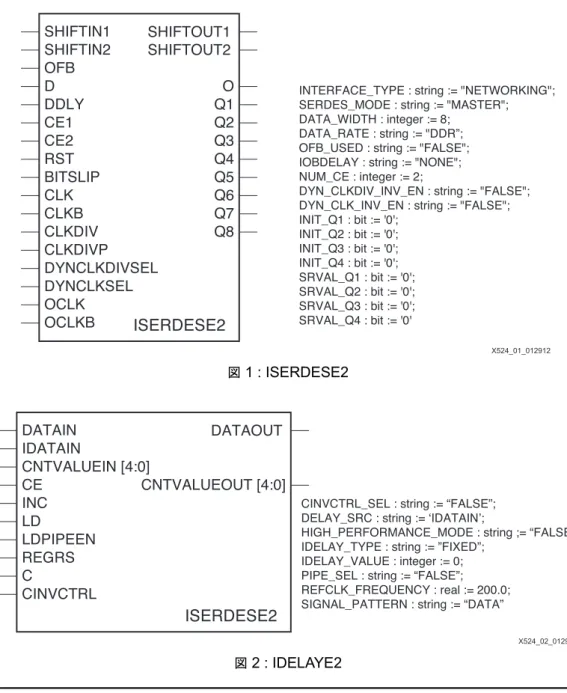

7 シ リ ーズ FPGA には、HR (High Range) バン ク と HP (High Performance) バン ク があ り ます。ADC イ ン タ ーフ ェ イ ス で重要な点は、ISERDESE2 (図1) と IDELAYE2 (図2) コ ン ポーネ ン ト は HR と HP の両バン ク で利用で き る と い う こ と です。HR バン ク は 2.5V の LVDS を、HP バン ク は 1.8V の LVDS をサポー ト し ます (VCCOレベル)。 こ れ ら の HR/HP I/O バン ク 、 お よ び ISERDESE2/IDELAYE2 コ ン ポーネ ン ト に関す る 詳細は、 『7 シ リ ーズ FPGA SelectIO リ ソ ース ユーザーガ イ ド 』 (UG471) を参照 し て く だ さ い。ADC LVDS

イ ン タ ー フ ェ イ ス

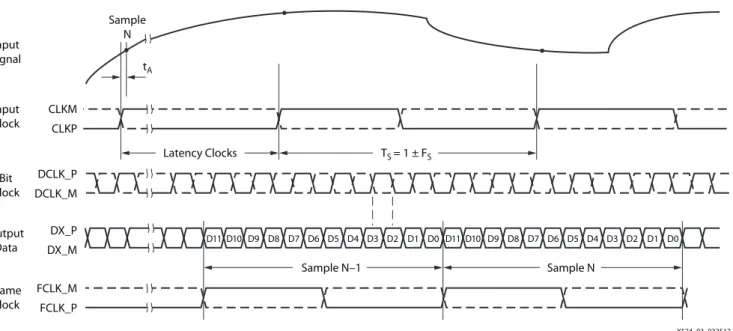

多 く の ADC は、 シ リ ア ラ イ ズ さ れた LVDS イ ン タ ーフ ェ イ ス を使用 し て、 コ ン ポーネ ン ト パ ッ ケージ 内の各 ADC で 1 つま たは 2 つの LVDS チ ャ ネルを介 し て FPGA へデジ タ ルデー タ を送 り ます。図3 に、 アナ ロ グ入力信号、 入力 ク ロ ッ ク 、 ビ ッ ト ク ロ ッ ク 、 お よ びフ レ ーム ク ロ ッ ク を示 し ます。 レ イ テ ン シ期間の終了後、アナ ロ グ信号の Sample N がデジ タ ル形式に変換 さ れて ADC 出力に現れます。ア ナ ロ グ信号は、12 ビ ッ ト の ADC 分解能でデジ タ ル、 シ リ アルデー タ ス ト リ ームに変換 さ れ、高速ビ ッ ト ク ロ ッ ク お よ び同期 (フ レーム) ク ロ ッ ク と 共に現れます。 X-Ref Target - Figure 1図 1 : ISERDESE2

X-Ref Target - Figure 2

図 2 : IDELAYE2

INTERFACE_TYPE : string := "NETWORKING"; SERDES_MODE : string := "MASTER"; DATA_WIDTH : integer := 8;

DATA_RATE : string := "DDR”; OFB_USED : string := "FALSE"; IOBDELAY : string := "NONE"; NUM_CE : integer := 2;

DYN_CLKDIV_INV_EN : string := "FALSE"; DYN_CLK_INV_EN : string := "FALSE"; INIT_Q1 : bit := '0'; INIT_Q2 : bit := '0'; INIT_Q3 : bit := '0'; INIT_Q4 : bit := '0'; SRVAL_Q1 : bit := '0'; SRVAL_Q2 : bit := '0'; SRVAL_Q3 : bit := '0'; SRVAL_Q4 : bit := '0'

ISERDESE2

SHIFTIN1

SHIFTIN2

OFB

D

DDLY

CE1

CE2

RST

BITSLIP

CLK

CLKB

CLKDIV

CLKDIVP

DYNCLKDIVSEL

DYNCLKSEL

OCLK

OCLKB

O

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

SHIFTOUT1

SHIFTOUT2

X524_01_012912CINVCTRL_SEL : string := “FALSE”; DELAY_SRC : string := ‘IDATAIN’;

HIGH_PERFORMANCE_MODE : string ;= “FALSE’; IDELAY_TYPE : string := ”FIXED”;

IDELAY_VALUE : integer := 0; PIPE_SEL : string := “FALSE”; REFCLK_FREQUENCY : real := 200.0; SIGNAL_PATTERN : string := “DATA”

ISERDESE2

DATAIN

IDATAIN

CNTVALUEIN [4:0]

CE

INC

LD

LDPIPEEN

REGRS

C

CINVCTRL

CNTVALUEOUT [4:0]

DATAOUT

X524_02_012912XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 3 フ レーム ク ロ ッ ク (FCLK) は、ADC サンプルク ロ ッ ク がデジ タ ル化 さ れて位相シ フ ト さ れた信号です。 FCLK はシ リ アルデー タ と 位相が揃っ てお り 、 すべてのサンプルデー タ ビ ッ ト は、1 つの フ レーム ク ロ ッ ク 周期内に収ま り ます。 高速ビ ッ ト ク ロ ッ ク (DCLK) は、 デー タ お よ び FCLK に対 し て 90°位相 シ フ ト し た信号 と し て現れます。 1 ワ イ ヤ モー ド の場合、 パ ッ ケージ内の コ ンバー タ ー と 同数のデー タ チ ャ ネルが あ り ま す。2 ワ イ ヤ モー ド の場合、 デー タ は各 コ ンバー タ ーで 2 つのデー タ チ ャ ネルに分かれ ま す。DCLK の周波数は、 ADC の分解能お よ びサンプルレー ト で決ま り ます。 し たがっ て、ADC は、 パ ッ ケージ内の各 コ ンバー タ ーに対 し て 1 つま たは 2 つのデー タ レーン を提供 し ますが、DCL と FCLK については 1 つずつ し か 提供 し ません。

LVDS I/O の最大速度は、DCLK が FPGA ロ ジ ッ ク 内ま たは ISERDESE2 内の FF を ト グルで き る 最大 速度で決ま り ます。 し たがっ て、1 ワ イ ヤイ ン タ ーフ ェ イ ス のシ ン グルチ ャ ネル LVDS ADC の最大サ ンプル速度には制限があ り ます。 式1か ら 、1 ワ イ ヤ DDR モー ド のシ ン グル ADC の ビ ッ ト ク ロ ッ ク レー ト が求め ら れ ま す。 た と え ば、16 ビ ッ ト 、1 ワ イ ヤ モ ー ド 、150Ms/s デ バ イ ス の ビ ッ ト ク ロ ッ ク 周 波 数 は、 (16 × 150) / 2 = 1,200 MHz と な り 、2.4Gb/s ビ ッ ト レ ー ト に相当 し ま す。 物理的に 1 デー タ レ ーン (1 ワ イ ヤ) で こ れ ら の ク ロ ッ ク レー ト は、すべての FPGA ス ピー ド グ レー ド の LVDS I/O に対 し て高 すぎ ます。2 ワ イ ヤ イ ン タ ーフ ェ イ ス ソ リ ュ ーシ ョ ン では、 各 ADC で 2 つの物理的デー タ レーン (2 ワ イ ヤ) を使用 し ます。 こ れに よ り 、 デー タ ス ループ ッ ト レー ト は 2 倍にな り 、 ビ ッ ト ク ロ ッ ク レー ト を抑え る こ と がで き ま す。 式 1 シ ン グルデー タ レーン、16 ビ ッ ト 、150Ms/s ADC を 2 ワ イ ヤモー ド (各 ADC に対 し て物理的に 2 つ の レーン を使用) で使用す る と 、 ビ ッ ト ク ロ ッ ク レー ト は 600MHz にな り ます (式

2

)。 こ の よ う な高 速 ADC は、FPGA へ接続で き ます。 式 2 X-Ref Target - Figure 3図 3 : シ ングルチ ャ ネルの コ ンバー タ ーのセ ッ ト ア ッ プ Sample N X524_03_032512 Input Signal Input Clock CLKM Latency Clocks Sample N–1 Sample N D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 TS = 1 ± FS CLKP FCLK_M FCLK_P DCLK_P DCLK_M DX_P DX_M Bit Clock Frame Clock Output Data tA ADC_resolution Sample_rate× 2 1 (wire)× --- = bit_clock (MHz) ADC_resolution Sample_rate× 2 2 (wire)× --- = bit_clock (MHz)

図4に、1 ワ イ ヤイ ン タ ーフ ェ イ ス モー ド での 14 ビ ッ ト/16 ビ ッ ト ADC の タ イ ミ ン グ図を示 し ます。 図5には、2 ワ イ ヤ イ ン タ ーフ ェ イ ス モー ド での 14 ビ ッ ト/16 ビ ッ ト ADC の タ イ ミ ン グ図を示 し ま す。 デー タ は、LVDS チ ャ ネルを介 し て ADC か ら 転送 さ れ、MSB ま たは LSB 順にビ ッ ト 単位ま たは バ イ ト 単位で揃え ら れます。 1 ワ イ ヤ イ ン タ ーフ ェ イ ス は、2 ワ イ ヤ イ ン タ ーフ ェ イ ス よ り も 速度の問題に直面 し 易 く な り ます。1 ワ イ ヤモー ド の リ フ ァ レ ン スデザ イ ンでは、 最大 16 ビ ッ ト の ADC 分解能をサポー ト し 、 サンプ リ ン グ レー ト は最大約 85Ms/s です。2 ワ イ ヤモー ド の リ フ ァ レ ン ス デザ イ ンがサポー ト す る ADC 分解能 は 1 ワ イ ヤモー ド と 同 じ ですが、 サンプ リ ン グ レー ト は最大 160 Ms/s ま で対応可能です。 リ フ ァ レ ン スデザ イ ンは、 柔軟性に優れた完全なモジ ュ ールデザ イ ン手法を取 り 入れてい る ため、 周 波数、 分解能、 ま たはチ ャ ネル数、 あ る いは こ れ ら をすべて変更で き ます。

注記 : ADC の設定は、SPI か ら 制御お よ びプ ロ グ ラ ムで き ます。 こ のアプ リ ケーシ ョ ン ノ ー ト では SPI について説明 し てい ませんが、 リ フ ァ レ ン スデザ イ ンには SPI リ ン ク 経由で ADC をプ ロ グ ラ ム で き る よ う に、UART-USB リ ン ク を介 し て FPGA を PC へ接続す る サンプルデザ イ ンが含まれてい ます。 X-Ref Target - Figure 4

図 4 : 1 ワ イ ヤモー ド での 14 ビ ッ ト/16 ビ ッ ト ADC - 4x ビ ッ ト ク ロ ッ ク 出力の波形

Sample N Data bit in MSB first mode Data bit in LSB first mode Input Clock CLKP Frame Clock FCLKP at 1X Bit Clock 8X DCLKP 16X Serial

Factor Output Data

DX_P, DX_M D12(D3) D11 (D4) D10 (D5) D9 (D6) D8 (D7) D7 (D8) D6 (D9) D5 (D10) D4 (D11) D3 (D12) D2 (D13) D1 (0) D0 (0) 0 (D0) 0 (D1) D13 (D2) D13 (D2) 0 (D1) 0 (D0) Sample N+1 X524_04_032512

X-Ref Target - Figure 5

図 5 : 2 ワ イ ヤモー ド での 14 ビ ッ ト/16 ビ ッ ト ADC - 4x ビ ッ ト ク ロ ッ ク 出力の波形 X524_05_032512 FCLK DCLK Dx0P, Dx0M Bytewise Mode Bitwise Mode Dx1P, Dx1M Dx0P, Dx0M Dx1P, Dx1M (D14)D3 D9 (D14) D5 (D13) D7 (D12) D9 (D11) D11 (D10) D13 (D9) D8 (0) D1 (0) 0 (D8) 0 (D8) D14 (D9) D1 (D6) D1 (D6) D2 (D5) D3 (D4) D4 (D3) D5 (D2) D6 (D1) D0 (D7) D0 (D7) D7 (D0) D7 (D0) D6 (D1) D9 (0) D9 (0) D10 (D13) D11 (D12) D12 (D11) D13 (D10) 0 (D9) D8 (0) D8 (0) D0 (D8) 0 (D8) D0 (D9) D2 (D12) D2 (D12) D4 (D10) D6 (D8) D8 (D6) D10 (D4) D12 (D2) D0 (0) D0 (0) 0 (D0) 0 (D0) D12 (D2)

XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 5

ビ ッ ト

ク ロ ッ ク

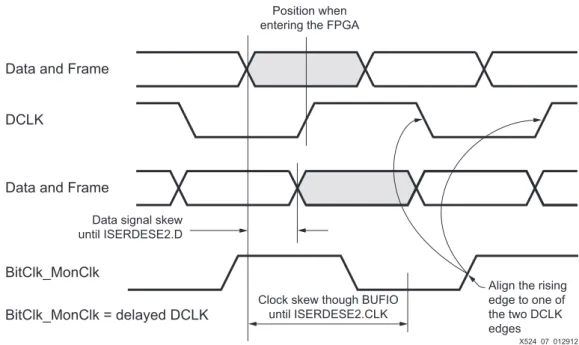

ビ ッ ト ク ロ ッ ク レー ト は、式1か ら 求め ら れます。16 ビ ッ ト 、200 Ms/s の 1 ワ イ ヤ ADC モー ド の場 合、DDR ビ ッ ト ク ロ ッ ク レー ト は 1,600MHz です。注記 : 式1 を用いて Adc_resolution お よ び Bit_Clock か ら サンプルレー ト を計算す る 場合、ADC が 2 ワ イ ヤモー ド の と き は Wire_Interface を 2 に、1 ワ イ ヤモー ド の と き は 1 に設定 し て く だ さ い。 1 ワ イ ヤの ADC ビ ッ ト ク ロ ッ ク レー ト は、7 シ リ ーズ FPGA の CC (ク ロ ッ ク 兼用) 入力ピ ンお よ び こ のデザ イ ンで使用 さ れ る リ ージ ョ ナルク ロ ッ ク ツ リ ーには速すぎ ます。 し たがっ て、ADC は 2 ワ イ ヤ モー ド で使用 し ます。2 ワ イ ヤモー ド の場合、ADC のデー タ は各 コ ンバー タ ーで 2 つの LVDS チ ャ ネ ルに分かれます。 つま り 、 ビ ッ ト ク ロ ッ ク が 2 分周 さ れます。 た と えば、2 ワ イ ヤ ADC モー ド で コ ン バー タ ーが 16 ビ ッ ト 、200Ms/s の場合、 ビ ッ ト ク ロ ッ ク レー ト は 800MHz と な り ます。 表1に、 イ ン タ ーフ ェ イ ス の ワ イ ヤ数、ADC 分解能別のビ ッ ト ク ロ ッ ク 、 お よ びサンプル ク ロ ッ ク の パ ラ メ ー タ ー別の関係を例 と し て示 し ます。式1を使用す る と 、 既知のパ ラ メ ー タ ー値か ら 値を簡単に 計算で き ます。 ADC か ら 提供 さ れ る ビ ッ ト ク ロ ッ ク は、 デー タ 信号お よ びフ レーム信号に対 し て 90° 位相がずれてい ます。 パ ッ ケージパ ッ ド か ら 各 ISERDESE2 の D 入力ま での遅延はすべての信号で同 じ にな る ため、 設計者 は PCB レ イ ア ウ ト を適切に設計 し て、FPGA へ到達す る ま で常に こ の位相関係を保つ よ う に し ます。 FPGA グ リ ッ ド 内では配線や ク ロ ッ クバ ッ フ ァ ーの遅延があ る ため、デー タ 信号お よ びフ レーム信号を キ ャ プチ ャ で き る よ う に DCLK の位置を調整す る 必要があ り ます (図6)。 表 1 : ADC パラ メ ー タ ーの関係 分解能 (ビ ッ ト) サン プル レー ト (MHz) イ ン タ ー フ ェ イ スの 種類 ビ ッ ト ク ロ ッ ク (MHz) コ メ ン ト 12 80 1 ワ イ ヤ 480 可 125 2 ワ イ ヤ 375 可 14 125 1 ワ イ ヤ 875 不可 (2 ワ イ ヤモー ド が必要) 150 2 ワ イ ヤ 525 可 16 125 2 ワ イ ヤ 500 可 200 2 ワ イ ヤ 800 可 (最速の ス ピー ド グ レー ド が必要) 注記 : 14 ビ ッ ト 分解能の ADC は、16 ビ ッ ト 出力モー ド で動作す る 場合があ り ます。 こ の と き 、2 ビ ッ ト のデー タ は、 ダ ミ ービ ッ ト あ る いはオーバーフ ロ ーを示すために使用 さ れます。 ク ロ ッ ク レー ト の計算では、 分解能パ ラ メ ー タ ーに 16 ビ ッ ト を使用 し て く だ さ い。

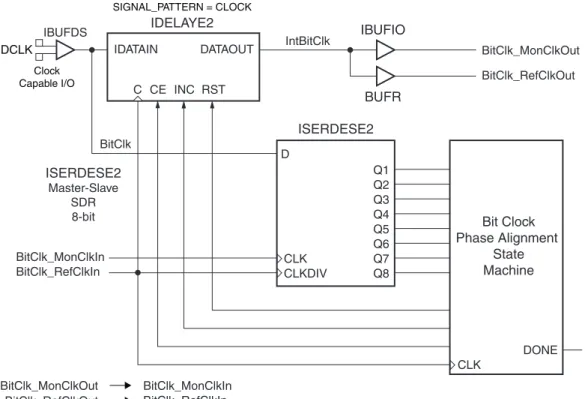

ADC か ら の DCLK は、 さ ま ざ ま なモー ド で使用 さ れ る IDELAYE2 を介 し て BUFIO お よ び BUFR の 入 力 へ 配 線 さ れ ま す (図6)。DCLK は BitClk_MonClk (位 相 が 揃 え ら れ た DCLK) に な り 、 BitClk_RefClk は再構築 さ れた フ レーム ク ロ ッ ク (FCLK) にな り ます。 ま た、DCLK は、IDELAYE2

と 同 じ I/O タ イ ルにあ る ISERDESE2 の D 入力へ も デー タ と し て適用 さ れます。

BitClk_MonClk と BitClk_RefClk は、 イ ン タ ーフ ェ イ ス で使用 さ れ る すべての ISERDESE2 コ ン ポー ネ ン ト の CLK お よ び CLKDIV 入力へ配線 さ れ、 ま た DCLK を使用す る ISERDESE2 へデー タ 入力 と し て配線 さ れます。 基本的に、DCLK はその遅延バージ ョ ン を ク ロ ッ ク と し て使用す る ISERDESE2 で、 それ自体を レ ジ ス タ し ま す。 こ れに よ っ て、 設計者は DCLK の立ち上が り お よ び立ち下が り エ ッ ジの位置を特定で き る ため、 ビ ッ ト ク ロ ッ ク 位相ア ラ イ メ ン ト ス テー ト マシ ン を用いて、DCLK ク ロ ッ ク サ イ ク ルの ど こ に で も ISERESE2 の CLK お よ び CLKDIV 入力 ク ロ ッ ク を位置 さ せ る こ と がで き ます。

BitClk_MonClkOut お よ び BitClk_RefClkOut は、 高い階層レベルで ISERDESE2 すべての CLK お よ び CLKDIV 入力 と 接続 し て お り 、 ま た ビ ッ ト ク ロ ッ ク ア ラ イ メ ン ト 階層 レ ベ ル の CLK お よ び CLKDIV 入力へ も 接続 し てい ます。こ の レベルの CLK 入力お よ び CLKDIV 入力は、BitClk_MonClkIn お よ び BitClk_RefClkIn です。

注 記 : こ の 資 料 内 の BitClk_MonClk お よ び BitClk_RefClk は、BitClk_MonClkOut か ら BitClk_MonClkIn 間、お よ び BitClk_RefClkOut か ら BitClk_RefClkIn 間の接続を それぞれ示 し てい ま す。 ビ ッ ト ク ロ ッ ク 位相ア ラ イ メ ン ト ス テー ト マシ ンは、 ISERDESE2 の出力お よ びデシ リ ア ラ イ ズ さ れ パ ラ レルで取得 さ れた ク ロ ッ ク ビ ッ ト を モニ タ リ ン グ し ます。 取得 し たすべてのビ ッ ト が同 じ (すべて 0 ま たはすべて 1) 場合、 ス テー ト マシ ンは IDELAY2 を イ ン ク リ メ ン ト/デ ク リ メ ン ト し て内部 ク ロ ッ ク と 外部 ク ロ ッ ク の位相を揃え ま す。 遅延 タ ッ プ数を イ ン ク リ メ ン ト ま たはデ ク リ メ ン ト す る こ と で、 ISERDESE2 の CLK に対す る 遅延が増減 し ます。

X-Ref Target - Figure 6

図 6 : ビ ッ ト ク ロ ッ ク のア ラ イ メ ン ト セ ッ ト ア ッ プ IBUFDS IDATAIN D CLK CLKDIV BitClk_MonClkOut IntBitClk BitClk Master-Slave SDR 8-bit BitClk_RefClkOut Q7 Q8 Q6 CLK DONE Q5 Q4 Q3 Q2 Q1 DATAOUT RST INC CE C BitClk_MonClkIn BitClk_RefClkIn BitClk_MonClkOut BitClk_RefClkOut BitClk_MonClkIn BitClk_RefClkIn X524_06_060412 IDELAYE2 ISERDESE2 ISERDESE2 IBUFIO BUFR Bit Clock Phase Alignment State Machine Clock Capable I/O SIGNAL_PATTERN = CLOCK DCLK

XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 7

ス テー ト

マ シ ン動作の制御

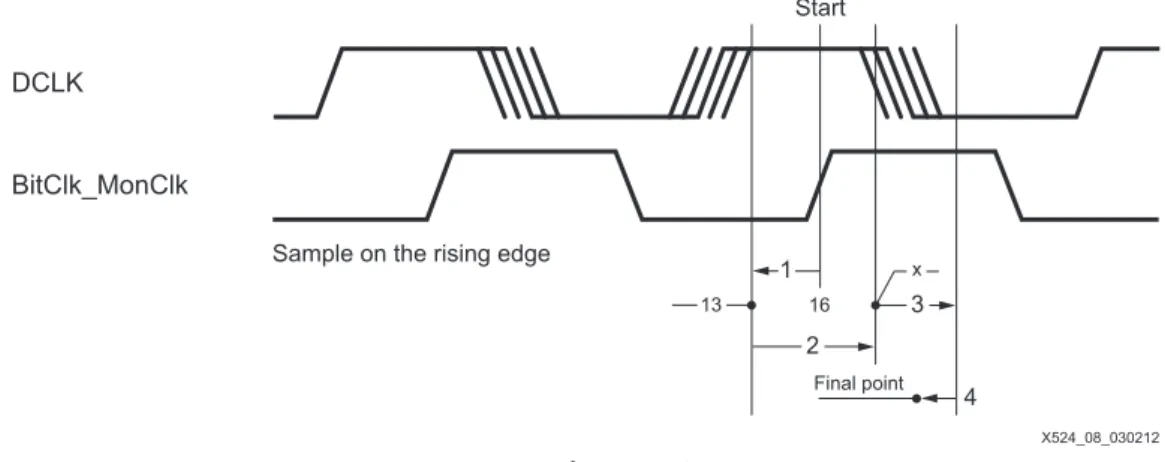

ビ ッ ト ク ロ ッ ク ア ラ イ メ ン ト ス テー ト マシ ンは、CLKDIV (BitClk_RefClk) の立ち上が り エ ッ ジで 動作 し 、 プ リ セ ッ ト さ れ た タ ッ プ 16 の IDELAYE2 遅延か ら 開始 し ま す。7 シ リ ー ズFPGA では、 IDELAYCTRL コ ン ポーネ ン ト へ適用す る 基準周波数が 200MHz (±10 MHz) の場合、IDELAYE2 遅 延 ラ イ ン は 78ps 単位で最大 32 タ ッ プの遅延が可能です。 基準周波数が 300MHz (±10 MHz) の と き の タ ッ プ遅延は 57ps です (300MHz は、 ス ピ ー ド グ レ ー ド が -2 で 03 コ ン ポーネ ン ト の場合のみ)。 こ の場合、 各 IDELAYE2 の合計遅延は 2.5ns と な り ます。MMCME2 お よ び IDELAYCTRL が ロ ッ ク さ れて準備が整っ た状態にな る と 、 ス テー ト マシ ンは DCLK の位置の検出を開始 し ます。 ス テー ト マシ ンの動作について説明す る 前に、 次の こ と を知っ てお く 必要があ り ます。 • DCLK は、FCLK お よ びデー タ 信号に対 し て 90° 位相がずれてい ます。 • ADC に よ っ て、DCLK はデフ ォ ル ト で有効なデー タ ア イ の中央に位置 し ます。 • FPGA への入力で、デー タ お よ びフ レーム信号が ISERDESE2 の D 入力へ配線 さ れ、ビ ッ ト ク ロ ッ ク が BUFIO お よ び BUFR の入力へ配線 さ れます。• こ の場合、DCLK が BUFIO/BUFR を通っ て ISERDESE2 の CLK お よ び CLKDIV 入力へ配 線 さ れ る と 、 デー タ お よ びフ レーム信号 と は異な る ス キ ュ ーが生 じ ます。 • ク ロ ッ ク はデー タ 有効ア イ の中央にデフ ォ ル ト で位置す る ため、それを変更す る 必要はあ り ません。 つま り 、DCLK を元の位置に戻すだけで十分です (図7)。 • DCLK には若干のジ ッ タ ーがあ り ます。 こ れは高精度のサンプルク ロ ッ ク か ら 派生 し てい る ため、 ジ ッ タ ーはわずかです。 • 78ps 単位で 32 タ ッ プの場合、IDELAYE2 は

~

2.5ns (2.496ns) です (IDELAYCTRL の基準 ク ロ ッ ク が 200MHz の場合)。 • つま り 、400MHz でジ ッ タ ーのない完璧な ク ロ ッ ク をサンプルで き る こ と にな り ますが、 実際 に そ の よ う な ジ ッ タ ーの な い ク ロ ッ ク は存在 し ま せん。350ps の ジ ッ タ ー を 考慮 し た場合、 IDELAYE2 は特別な手法を使用せずに 470MHz の ク ロ ッ ク をサンプル可能です。 • ク ロ ッ ク の位置をデー タ 有効ア イ の中央に再調整す る 必要がないため、2 つの ク ロ ッ ク エ ッ ジの検 出は不要です。 • ビ ッ ト ク ロ ッ ク は、 すでにデー タ 有効ア イ の中央に位置 し てい ます。 • 内部ビ ッ ト ク ロ ッ ク の位相が揃え ら れ る 外部ビ ッ ト ク ロ ッ ク のエ ッ ジは、 必ずレ ジ ス タ さ れ る 必 要があ り ます。 こ れは、 デー タ を キ ャ プチ ャ す る ISERDESE2 の後ろに配置 さ れてい る マルチプ レ ク サーの設定に必要です。ケース 1 サンプ リ ン グは、 ジ ッ タ ー (ク ロ ッ ク の切 り 替わ り) 領域で行われ、DCLK の 1/2 周期は≦ 2.5ns です (図8の波形 A)。 すべての位相ア ラ イ メ ン ト 周期の開始点で、 ス テー ト マシ ンは後方へシ フ ト し (タ ッ プ数の減少)、 各シ フ ト ご と に ISERDESE2 の出力を測定 し て開始地点に戻 り ます。 3 タ ッ プ分後ろへシ フ ト す る と 234ps と な り 、468ps ジ ッ タ ーに相当 し ます。 こ れは、 安定 し た ク ロ ッ ク レベルス テー ト を測定す る のに十分です。 ク ロ ッ ク の 2 つの ス テー ト が交差す る 領域で DCLK がサン プル さ れ る 場合、 ジ ッ タ ーの影響に よ っ て ISERDESE2 の出力は常に異な り ます。 こ の際、BitClk_MonClk はすでに DCLK と 位相が揃っ てい ま す。 こ の BitClk_MonClk ク ロ ッ ク の位相が DCLK の立ち上が り エ ッ ジ ま たは立ち上が り エ ッ ジのいず れに揃っ てい る のか を把握 し てお く こ と が重要です。 デ ク リ メ ン ト 後、ISERDESE2 出力がすべて 1 に な る と 、BitClk_MonClk の位相は DCLK の立ち下が り エ ッ ジに揃っ てい る こ と にな り ま す。 反対に、 ISERDESE2 出力がすべて 0 の と き は、BitClk_MonClk の位相が DCLK の立ち上が り エ ッ ジに揃っ て い る こ と にな り ます。BitClk_MonClk ク ロ ッ ク の位相が揃 う DCLK のエ ッ ジは、 マルチプ レ ク サーの 設定に使用 さ れ る ため、 アプ リ ケーシ ョ ンに伝え る 必要があ り ます。 開始時点の ISERDESE2 の出力がすべて 1 で、 デ ク リ メ ン ト 後の ISERDESE2 の値が安定 し ない、 ま たはすべて 0 にな っ た場合、BitClk_MonClk ク ロ ッ ク の位相は DCLK の立ち上が り エ ッ ジに揃っ てい ます (図8の波形 B)。 開始時点の ISERDESE2 の出力がすべて 0 で、 デ ク リ メ ン ト 後の ISERDESE2 の値が安定 し ない、 ま たはすべて 1 にな っ た場合、BitClk_MonClk ク ロ ッ ク の位相は DCLK の立ち下が り エ ッ ジに揃っ てい ます (図8の波形 C)。

X-Ref Target - Figure 7

図 7 : BUFIO お よび BUFR を通る ク ロ ッ ク スキ ュ ー

DCLK

Position when entering the FPGA

Data signal skew until ISERDESE2.D

Data and Frame

Data and Frame

BitClk_MonClk

Clock skew though BUFIO until ISERDESE2.CLK

X524_07_012912

BitClk_MonClk = delayed DCLK

Align the rising edge to one of the two DCLK edges

XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 9 図8の波形 D は、図8の波形 C の反対です。 最初は出力がすべて 1 で安定 し てい ますが、 デ ク リ メ ン ト 後の出力は不安定、 ま たはすべて 0 にな り ます。つま り 、DCLK の立ち上が り エ ッ ジが検出 さ れます。 開始時の DCLK と BitClk_MonClk は正確には位相が揃っ ていないため、IDELAYE2 を元の開始位置 へ戻す こ と はで き ません。

X-Ref Target - Figure 8

図 8 : サン プルエ ッ ジ を直接検出 (A、B、C、 および D) DCLK

C)

BitClk_MonClk X524_08C_030212 Sample on the rising edge Start 16 13 -3 taps From Q[8:1] stable at 0 to Q[8:1] unstable or stable at 1. Falling edge found1 DCLK

B)

BitClk_MonClk X524_08B_030212 Start 16 13 -3 taps From Q[8:1] unstable to Q[8:1] stable at 1. Falling edge found Sample on the rising edge1

BitClk_MonClk DCLK

D)

X524_08D_030212

Sample on the rising edge

Start 16 13 -3 taps From Q[8:1] stable at 1 to Q[8:1] unstable or stable at 0. Rising edge found

1 BitClk_MonClk DCLK

A)

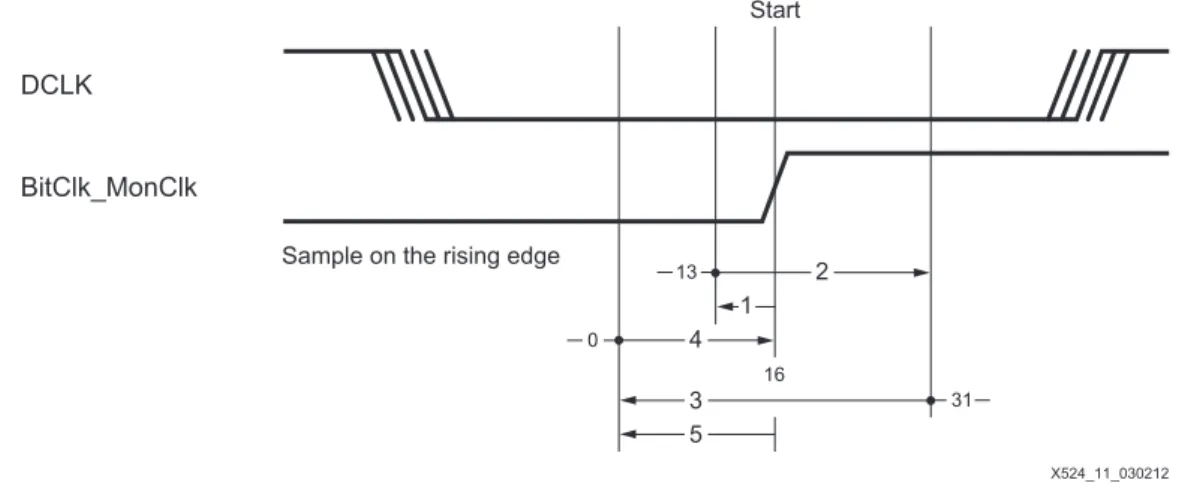

Start 16 13 X524_08A_030212 -3 taps From Q[8:1] unstable to Q[8:1] stable at 0. Rising edge found Sample on the rising edgeケース 2 DCLK の 1/2 周期は≦ 2.5ns で、 開始時点で ISERDESE2 の出力は安定 し てい ます (すべて 1、 ま たは すべて 0) (図9)。 基本的に 「ケース 1」 と 同 じ ですが、 後方へシ フ ト し た場合 (IDELAYE2 の減少)、ISERDESE2 の出力 に変化がな く 、 値はすべて 1 ま たはすべて 0 の ま ま変わ り ません。DCLK は、 ス テー ト が変化す る 領域 か ら 離れた位置でサンプル さ れます。 こ れ ら 最初の ス テ ッ プの後、ISERDESE2 の出力が不安定にな る ま で IDELAYE2 の タ ッ プが増加 し て 再び安定 し ますが、 出力は反対にな り ます。 つま り 、 エ ッ ジが検出 さ れた こ と を意味 し ます。 ISERDESE2 の出力がすべて 0 で不安定な領域を過ぎ た後にすべて 1 を示 し た場合、 立ち上が り エ ッ ジ が検出 さ れてい ます。 一方、 すべて 1 の出力か ら すべて 0 の出力にな っ た場合は、 立ち下が り エ ッ ジが 検出 さ れた こ と を示 し ます。 ISERDESE2 の出力が不安定な動作を示 し た 2 つの領域の中間地点に ク ロ ッ ク を位置 さ せます。 BitClk_MonClk ク ロ ッ ク が ど の DCLK エ ッ ジに揃っ てい る か を把握す る こ と は、 デー タ を正 し く キ ャ プチ ャ す る 上で非常に重要です。 こ の情報に基づいて、ISERDESE2 の後に配置 さ れてい る マルチプ レ ク サーを設定 し ます。 ケース 3 DCLK の 1/2 周期は≦ 2.5ns で、 開始時点で ISERDESE2 の出力は安定 し てい ます (すべて 1、 ま たは すべて 0) (図10)。 ケー ス 1 お よ びケー ス 2 と 同様に、 最初の ス テ ッ プで後方へシ フ ト し て も ク ロ ッ ク エ ッ ジは検出 さ れ ず、IDELAYE2 の タ ッ プ を増加 し て も エ ッ ジはあ り ま せん。IDELAYE2 の最後の タ ッ プ 31 を レ ジ ス タ し 、 タ ッ プ 32 以降に進みます。 タ ッ プ 0 へ戻 り 、 タ ッ プ数を増加 し てい き ます。 エ ッ ジが検出 さ れ る と 、 両 ク ロ ッ ク が揃い ます。 立ち上が り ま たは立ち下が り のいずれのエ ッ ジであ る か を検出す る 方法は、10ページの 「ケース 2」 と 同 じ です。

X-Ref Target - Figure 9

図 9 : 一方向のサン プルエ ッ ジア ラ イ メ ン ト

BitClk_MonClk DCLK

X524_08_030212

Sample on the rising edge

Start 16 x 1 13 2 3 4 Final point

XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 11 ケース 4 DCLK の 1/2 周期は 2.5ns よ り も は る かに長 く 、 安定 し た レベルでサンプル さ れてい ます。 開始点か ら IDELAYE2 の最終地点に到達 し 、 方向転換 し て も エ ッ ジは検出 さ れません (図11)。 DCLK の周期は IDELAYE2 の スパン よ り も 長い こ と にな り ます。 し たがっ て、 デー タ ビ ッ ト の遅延は、IDELAYE2 の ス パン よ り も は る かに長 く な り ます。 ユーザーは、 BitClk_MonClk ク ロ ッ ク を IDELAYE2 タ ッ プ0 へ移動す る 必要があ り ます。DCLK の ス テー ト (すべ て 1 ま たはすべて 0) を レ ジ ス タ し ます。 注記 : こ のアプ リ ケーシ ョ ン ノ ー ト では高速 ADC を対象 と し てい る ため、 長いビ ッ ト 遅延に対応す る 低速 ADC については言及 し てい ません。

フ レーム

ク ロ ッ ク

ADC か ら の LVDS フ レーム ク ロ ッ ク は、 デー タ 信号 と 位相が揃 う 低速動作 ク ロ ッ ク です。 こ の ク ロ ッ ク は、 既知で一定のパ タ ーン を伴 う サ ン プル ク ロ ッ ク のデジ タ ルバージ ョ ン です。 パ タ ーン には、 イ ン タ ー フ ェ イ ス に基づい て異な る 数のデー タ ビ ッ ト が含 ま れ ま す (図4お よ び図5)。 デザ イ ン では、 FPGA 内でキ ャ プチ ャ さ れたデー タ を ト レーニ ン グお よ び揃え る ために フ レ ーム ク ロ ッ ク が使用 さ れ ます。図12に、 基本的な フ レーム検出回路のブ ロ ッ ク レベル図を示 し ます。 X-Ref Target - Figure 10図 10 : 方向転換するサン プルエ ッ ジ ア ラ イ メ ン ト

X-Ref Target - Figure 11

図 11 : 予想 さ れたサン プルエ ッ ジ ア ラ イ メ ン ト

BitClk_MonClk DCLK

X524_10_030212

Sample on the rising edge Start 16 1 3 6 31 0 2 5 4 x 13 Final point BitClk_MonClk DCLK X524_11_030212

Sample on the rising edge

Start 16 1 3 5 31 13 0 2 4

2 つの ISERDESE2 コ ン ポーネ ン ト は、NETWORKING SDR (シ ン グルデー タ レー ト) モー ド で使用 さ れます。 各 ISERDESE2 は、 位置調整 さ れた ビ ッ ト ク ロ ッ ク (DCLK) の異な る エ ッ ジで ク ロ ッ ク さ ます。 ビ ッ ト ク ロ ッ ク (DCLK) が正 し く 揃え ら れ る と 、 フ レームク ロ ッ ク パ タ ーンの検出が開始 さ れ ます。 2 つの ISERDESE2 の出力は、予想 さ れ る フ レーム ク ロ ッ クパ タ ーン を示す固定値 と 比較 さ れます。 こ の固定値が ISERDESE2 の出力 と 一致 し な い場合は、 フ レ ー ム 信号 と すべ て のデー タ 信号に対 し て Bitslip の動作が開始 し ます。Bitslip は、 フ レーム ク ロ ッ ク の ISERDESE2 コ ン ポーネ ン ト の出力 と 予 想 さ れた フ レ ーム ク ロ ッ ク のパ タ ーン が一致す る ま で適用 さ れ ま す。 こ の出力がプ ロ グ ラ ム さ れたパ タ ーン と 一致す る と 、 フ レーム ク ロ ッ ク と デー タ の両方に対す る Bitslip の動作が停止 し ます。 こ れで、 FPGA 内のデー タ お よ びフ レーム ク ロ ッ ク 信号が有効 と 見な さ れます。 ただ し 、 こ れ ら は常に有効であ る と は限 り ません。 Bitslip 動作が複数回実行 さ れた後、ISERDESE2 の構造上、 出力は前のサ イ ク ルで現れた値 と 同 じ 値を 示す こ と がで き る よ う にな り ます。 ト レーニ ン グパ タ ーンがデー タ 内で実行 さ れ る よ う な通常の ソ ース 同期デザ イ ンでは、 こ れは問題にな り ません。 問題 と な る のは、 同期に も かかわ ら ず、 追加で Bitslip 動 作が必要な場合のみです。 一般的な ADC イ ン タ ーフ ェ イ ス では、 ト レーニ ン グパ タ ーン を使用せずに フ レームの同期化を実行す る ため、 同 じ 値を 2 回出力す る ISERDESE2 に よ っ て同期化プ ロ セ ス全体に問題が生 じ ます。 予防措置 を講 じ ずに重複す る 出力が現れた場合、 フ レーム キ ャ プチ ャ 回路は実際に同期 し ていない フ レームパ タ ーン と 同期 し てい る かの よ う に動作 し ます。 こ の間違っ た フ レーム同期に よ る 結果は、 キ ャ プチ ャ し たデー タ 内に影響 し ます。 デー タ を キ ャ プチ ャ す る ISERDESE2 は、 フ レ ーム を キ ャ プチ ャ す る ISERDESE2 と 共にシ フ ト さ れ ま す。 こ のため、 フ レームが間違っ た位置で同期 と 見なす と 、 デー タ 値が不正にな り ます。 し たがっ て、 フ レームア ラ イ メ ン ト 回路では、 こ の問題を回避す る ために重複ニブル検出ス テー ト マシ ン を採用 し てい ます。

X-Ref Target - Figure 12

図 12 : 基本的な フ レーム検出回路 RqrdPattern FrameIn_p FrameIn_n [15:8] [7:0] Register Register

BitSlip_p BitSlip_n P Captured

atter n Sw apMux MsbRegEna LsbRegEna Multiplexer Register

Frame Alignment State Machine

ISERDESE2 ISERDESE2 Register CLKDIV CLK X524_12_060712

XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 13

フ レーム

パ タ ーンのキ ャ プ チ ャ

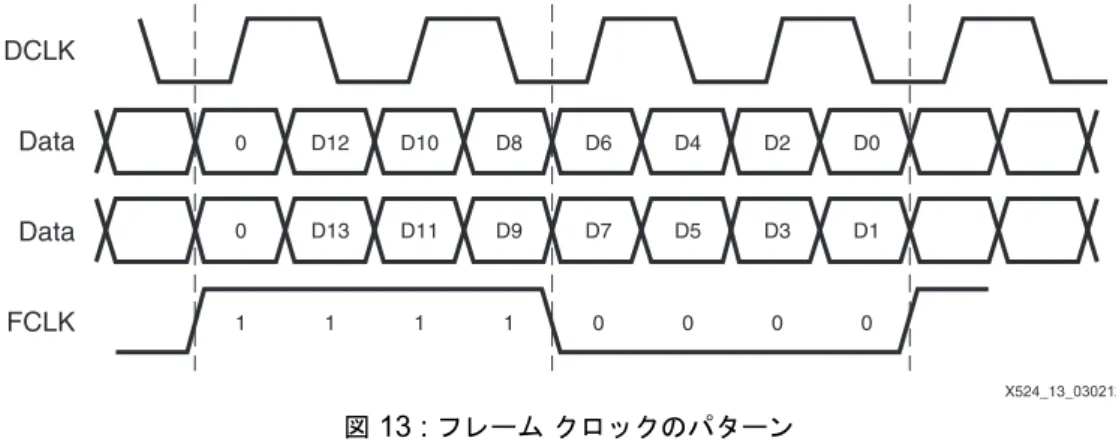

フ レーム ク ロ ッ ク は、一定のデー タ パ タ ーン を繰 り 返すデー タ ス ト リ ーム と し て キ ャ プチ ャ さ れます。 フ レ ーム チ ャ ネル と デー タ チ ャ ネルは位相が揃っ てい る ため、 フ レ ーム ク ロ ッ ク は ト レ ーニ ン グパ タ ーン と し て ま たは実際のデー タ レーン用の同期レーン と し ての使用に適 し てい ます。 キ ャ プチ ャ し た パ タ ーンが既知のパ タ ーン (通常は必ずあ る) と 一致す る よ う に調整で き る 場合、受信デー タ は確実に正 し い フ ォーマ ッ ト にな り ます。 ADC イ ン タ ー フ ェ イ ス が 2 ワ イ ヤモー ド で動作す る 場合、 フ レ ー ム パ タ ー ン は図13 (16 ビ ッ ト 、 DDR、2 ワ イ ヤ) の よ う にな り ます。 キ ャ プチ ャ し た フ レームデー タ を揃え る イ ン タ ーフ ェ イ ス では固 定パ タ ーンが検出 さ れ る ため、 デー タ チ ャ ネルで も 正 し いデー タ が受信 さ れます。 DDR 入力は、SDR モー ド に設定 さ れた 2 つの ISERDESE2 コ ン ポーネ ン ト でキ ャ プチ ャ さ れます。 開 始時点では、最初にキ ャ プチ ャ さ れ る ビ ッ ト は不明です。一方の ISERDESE2 が CLK の立ち上が り エ ッ ジで、も う 一方の ISERDESE2 が CLK の立ち下が り エ ッ ジでデー タ を キ ャ プチ ャ し ます。有効な Bitslip 動作の実行には、 まず 2 つの コ ン ポーネ ン ト のいずれか一方を対象 と し ます。2 つの ISERDESE2 コ ン ポーネ ン ト でキ ャ プチ ャ さ れた値が予想フ レームパ タ ーン と 一致 し ない場合、 も う 1 つの ISERDESE2 に Bitslip 動作を適用 し ます。 こ れは、ピ ン ポ ン型 Bitslip 動作 と し て考え る こ と がで き ます。キ ャ プチ ャ し たデー タ が予想フ レーム パ タ ーン値 と 一致す る 場合は、Bitslip の動作が停止 し 、 正 し い フ レ ーム と デー タ 値がキ ャ プチ ャ さ れます。 フ レーム キ ャ プチ ャ ロ ジ ッ ク は、 デー タ キ ャ プチ ャ ロ ジ ッ ク と 同 じ 構成です。 つま り 、ISERDESE1 の後に レ ジ ス タ 、 マルチプ レ ク サー、 レ ジ ス タ 、 そ し て ワ ー ド ア セ ン ブルレ ジ ス タ が配置 さ れて、 ア プ リ ケーシ ョ ンで フ レームパ タ ーンがチ ェ ッ ク で き る よ う にな っ てい ます。 こ の ロ ジ ッ ク は必ず し も 必 要ではあ り ません。 必須 ロ ジ ッ ク は、 フ レーム ス テー ト マシ ンのみです。Bitslip

動作

図14に、Bitslip 動作を実行せずに ビ ッ ト を キ ャ プチ ャ す る 場合を示 し てい ます。CLK に よ っ て 8 ビ ッ ト がシ リ アル-パ ラ レ ル レ ジ ス タ にキ ャ プチ ャ さ れ る と 、 デー タ は CLKDIV でパ ラ レ ル出力 レ ジ ス タ (Q 出力) へ転送 さ れます。8 ビ ッ ト を キ ャ プチ ャ す る ために、 正 し いデー タ が適切な タ イ ミ ン グで ロ ー ド さ れ る よ う に CLKDIV の周波数は CLK の 1/4 と な り ます。 図15 (SDR 動作) に示すデー タ キ ャ プチ ャ は、ビ ッ ト 値 7 か ら 開始 し てい ます。こ れ ら の ビ ッ ト は CLK の ク ロ ッ ク レー ト でシ リ アル-パ ラ レルレ ジ ス タ へシ フ ト さ れます。 垂直方向に積み重な っ たブ ロ ッ ク が こ の レ ジ ス タ を表 し てい ます。 こ れ ら のブ ロ ッ ク では、 ビ ッ ト 値 7 が最初にシ フ ト さ れ、 一番下に配 置 さ れて終わっ てい ます。 最後にシ フ ト さ れた ビ ッ ト 値は D です。 次の CLKDIV の立ち上が り エ ッ ジでは、シ リ アル-パ ラ レルレ ジ ス タ の コ ン テ ン ツすべてがパ ラ レル出 力ス ト レージ レ ジ ス タ へシ フ ト し ます。 つま り 、 こ の レ ジ ス タ にはDCBA0987 が含 ま れ る よ う にな り ます。 続けて新 し いデー タ がシ リ アル-パ ラ レ ルレ ジ ス タ へシ フ ト し て、 その後パ ラ レ ル出力レ ジ ス タ へ転送 さ れます。 こ のため、CLKDIV の立ち上が り エ ッ ジ ご と に、CLK の立ち上が り エ ッ ジでシ リ ア ル-パ ラ レルレ ジ ス タ へシ フ ト し た 8 ビ ッ ト が ISERDESE2 出力に現れます。X-Ref Target - Figure 13

図 13 : フ レームク ロ ッ クのパ タ ーン X524_13_030212 DCLK FCLK Data Data 0 0 D12 D13 D10 D11 D8 D9 D6 D7 D4 D5 D2 D3 D0 D1 1 1 1 1 0 0 0 0

注記 : 図14では、CLK の立ち上が り エ ッ ジが 8 回到達 し た後、CLKDIV の立ち上が り エ ッ ジで デー タ がパ ラ レルレ ジ ス タ へ転送 さ れます。 Bitslip を使用す る と 、CLK の ク ロ ッ ク レー ト でシ リ アル-パ ラ レ ル レ ジ ス タ にキ ャ プチ ャ さ れたデー タ が CLK の 1 サ イ ク ル遅れてパ ラ レルレ ジ ス タ へ転送 さ れます。 その結果、 シ リ アル-パ ラ レル レ ジ ス タ に よ っ て 1 ビ ッ ト 余計に レ ジ ス タ へシ フ ト す る ため、 反対側の端にあ る 1 ビ ッ ト が失われます。 つ ま り 、 パ ラ レルレ ジ ス タ にキ ャ プチ ャ さ れたデー タ は、1 ビ ッ ト シ フ ト し た状態で現れます。 図15は図14 と 同 じ 動作ですが、2 番目のバ イ ト がシ リ アル-パ ラ レ ルレ ジ ス タ にキ ャ プチ ャ さ れ る と き に Bitslip 動作が実行 さ れます。 こ のため、8 番目のビ ッ ト の受信後ではな く 9 ビ ッ ト の後にパ ラ レル レ ジ ス タ へデー タ が転送 さ れます。 パ タ ーンは 1 ビ ッ ト シ フ ト し た状態で現れます。 シ リ アル-パ ラ レル レ ジ ス タ の一番下にあ る 最初にシ フ ト し た ビ ッ ト が失われます。 ISERDESE2 出力は同 じ デー タ を二度出力す る 場合があ り ます。 こ の動作は、 デー タ ト レ ーニ ン グパ タ ーン で同期化を行 う 一般的な ソ ー ス 同期 イ ン タ ーフ ェ イ ス には影響を与え ま せん。 ト レ ーニ ン グパ タ ーンへの同期化に遅延が生 じ ます。 ADC

X-Ref Target - Figure 14

図 14 : Bitslip 動作な し のビ ッ ト キ ャ プ チ ャ

X-Ref Target - Figure 15

図 15 : Bitslip を使用 し た ビ ッ ト キ ャ プ チ ャ X524_14_060712 X W T S R P N M L K H G F ... ... X W T S R P ... ... X W T S R P N M L K H G F E N M L K H G F E D C B A 0 9 8 7 D C B A 0 9 8 7 P a rallel Ser ial-to-P ar allel E D C B A 0 9 8 7 6

Assume theISERDESE2 captures 8-bit SDR data

CLK CLKDIV

. . .

X524_15_060712 X W T S R P N M L K H G F P N M L K H G F P N M L K H G F E D C B A 0 9 8 7 D C B A 0 9 8 7 E D C B A 0 9 8 7 6Assume the ISERDESE2 captures 8 bits of data

Because of the Bitslip operation, one extra bit is shifted into the serial-to-parallel register (dark gray), and one bit is lost at the other end (black).

The ISERDESE2 output now looks like this.

XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 15 ADC イ ン タ ーフ ェ イ ス は、 フ レーム ク ロ ッ ク 信号を使用 し て同期化 さ れます。 同期 し てい る 間、 その 他すべての信号お よ びデー タ 入力はフ レームパ タ ーン と 共にシ フ ト し ます。 し たが っ て、 フ レーム パ タ ーン と 同期 し てい る と フ レーム回路が誤っ て判断 し た場合、キ ャ プチ ャ し たデー タ が不正 と な り ます。 ISERDESE2 の Bitslip 動 作 は 両 方 の コ ン ポ ー ネ ン ト に 対 し て 同 時 に 実 行 さ れ な い た め、 一 方 の ISERDESE2 は、 も う 一方の ISERDESE2 で Bitslip が実行 さ れ る 前に同 じ デー タ を二度出力す る 可能 性があ り ます。 こ の場合、 同期化は事実上不可能です。 図16に こ れ ら の動作を示 し ます。 • 複数回 Bitslip 動作を実行 し た後、ISERDESE2 コ ン ポーネ ン ト の出力は 3 と E と な り 、 結果はバ イ ト ADです。 • 0011_1110 = 1 0 1 0 1 1 0 1 • 次の出力は C と 1 で、 バ イ ト 52 と な り ます。

• 「_p」 で示 さ れてい る ISERDESE2 が Bitslip 要求を受信 し 、Bitslip 動作を実行 し ます。 その結果 は 1 と E でA9 と な る はずですが、SERDESE2 が C を 2 回出力 し て、結果のバ イ ト はF8 (C と E) と な っ てい ます。 受信 し たバ イ ト のニブルは Bitslip 要求を受信すべ き と き に受信 し なか っ たため、 CLKDIV の 1 サ イ ク ル分遅延 し 、 結果 と し て混在 し たバ イ ト と な っ てい ます。

• 次の CLKDIV エ ッ ジでは、 先の Bitslip 動作が ISERDESE2 出力で実行 さ れ、 結果は1 と 1、 つ ま り 03 と な り ます。 重複ニ ブルの検出 先ほ ど説明 し た、ISERDESE2 が同 じ デー タ を二度出力 し て何 も なか っ たかの よ う に動作を継続す る と い っ た問題を回避す る ために、 小規模な ス テー ト マシ ンが用意 さ れてい ます。 ISERDESE2 の出力デー タ は複数の レ ジ ス タ を通っ て渡 さ れます。 ISERDESE2 の前の出力 と 現在の出力が 1 つ目の レ ジ ス タ の前後で比較 さ れます。 ISERDESE2 が同 じ デー タ を二度出力す る 場合、 前のデー タ と 現在のデー タ は同 じ です。 こ の機能は、 デザ イ ン内にあ る コ ンパレー タ で実行 さ れます。 重複ニブルが検出 さ れ る と 、 その他の レ ジ ス タ か ら デー タ の選択が行われて、 レ ジ ス タ バン ク の出力が 連続 し たデー タ ス ト リ ーム を示 し ます。

X-Ref Target - Figure 16

図 16 : 出力デー タ の重複 X524_16_032612 FrmClkReSync /IntFrmSrdsOut_Isrds_p IntfrmSrdsOut_Isrds_n IntFrmSrdsOut IntFrmDat IntFrmDatSwp FrmClkDat IntFrmEqu_d T X F 0 0 3 C 1 E 1 E 1 E 1 E 8 7 0 E 1 E 1 E 1 F 0 F 0 D5 2A 00 AD 52 F8 03 FC 03 1 56 AB 54 AB 5 AA 7F 00 F8 07 F8 52 A9 56 1 A9 FC 01 FE 0 AA 00AA 00 0000 07 F8 07 F8 52 1 A9 56 A9 FC 01 F O Start of explication

こ のアプ リ ケーシ ョ ン ノ ー ト に付属す る リ フ ァ レ ン スデザ イ ンには、全体の動作を示す MS Excel ス プ レ ッ ド シー ト が含まれてい ます。図17に、 レ ジ ス タ バン ク が ど の よ う に構成 さ れてい る か を示 し ます。 レ ジ ス タバン ク は、1 つの SRL シ フ ト レ ジ ス タ で構成 さ れてい ます。 こ のシ フ ト レ ジ ス タ を使用す る こ と で、 レ ジ ス タ バン ク にあ る レ ジ ス タ の 1 つの出力を選択 し て、 それを マルチプ レ ク サーを通 し て渡 す こ と がで き ます。 こ れは、 ま さ に重複ニブル機能に必要な要素です。SRL は さ ら に、 デザ イ ン をい く つかの CLB に完全 に収め る こ と がで き ます。

デー タ

ADC は、デジ タ ル化 し たデー タ を 1 ワ イ ヤモー ド ま たは 2 ワ イ ヤモー ド で提供 し ます。1 ワ イ ヤの イ ン タ ーフ ェ イ ス では 1 つの差動 LVDS ペア を用いてデー タ を FPGA へ送信 し ますが、2 ワ イ ヤの イ ン タ ーフ ェ イ ス では 1 つの コ ンバー タ ーに対 し て 2 つの LVDS チ ャ ネルを使用 し ます。 コ ンバー タ ーは、1 つ ま たは 2 つの LVDS デー タペアでデー タ を伝送す る 場合、 異な る ビ ッ ト ま たは バ イ ト 構成を使用 し ます。 デー タ は MSB ま たは LSB か ら 順に、 ビ ッ ト ま たはバ イ ト 方向に配列で き ま す。 多 く の ADC は、 こ れ ら のモー ド を選択 し て使用す る ために、SPI イ ン タ ーフ ェ イ ス を介 し て設定 さ れます。 可能な限 り 多 く の ADC に対応す る ため、 こ れ ら のパ ラ メ ー タ ーを利用す る よ う にデー タ イ ン タ ーフ ェ イ ス を設定す る こ と も で き ます。 基本のデー タ イ ン タ ーフ ェ イ ス は 2 つの LVDS デー タ 入力を備え て い ます。 し たがっ て、2 ワ イ ヤモー ド でシ ン グルデー タ チ ャ ネル、 ま たは 1 ワ イ ヤモー ド でデ ュ アル デー タ チ ャ ネル と し て設定で き ます。 基本的な イ ン タ ーフ ェ イ ス のデー タ 出力は、1 ワ イ ヤ ま たは 2 ワ イ ヤの選択に従い ます。1 ワ イ ヤモー ド の場合、32 ビ ッ ト 出力バ ス が 2 つの 16 ビ ッ ト バス に分割 さ れます。 下位の 16 ビ ッ ト がチ ャ ネル 0、 上位の 16 ビ ッ ト がチ ャ ネル 1 と な り ます。2 ワ イ ヤモー ド の場合、32 ビ ッ ト 出力は上位 と 下位の 16 ビ ッ ト セグ メ ン ト で 1 つのデー タ を表 し ます。 リ フ ァ レ ン スデザ イ ンでは、 上位 16 ビ ッ ト (MSB) が 使用 さ れてい ます (図18)。X-Ref Target - Figure 17

図 17 : 重複ニ ブルレ ジ ス タ バン ク X524_17_032612 addr IntRegOutOne IntRegOutOne DataIn IntAddr[4:0] IntAddr[4:0] IntEqu IntSrlOut DataIn FrmClkDiv IntRstln_d DataOut

SRLC32E

Register COMPARE State Machine Register 5XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 17 ア ラ イ メ ン ト は、フ レーム ク ロ ッ ク をパ タ ーン ト レーニ ン グデー タ と し て使用 し て行われます。フ レー ム ク ロ ッ ク は ADC か ら のデー タ と 位相が揃い ます。 フ レーム ク ロ ッ ク が受信 さ れて フ レームパ タ ー ンが認識 さ れ る と き 、受信 し たデー タ はフ レーム信号 と 共にシ フ ト さ れ る ため、同様に位相が揃い ます。 デー タ 反転 と ビ ッ ト スワ ッ プのマルチ プ レ クサー 注目すべ き 点 こ の機能は、デザ イ ン内の フ レームキ ャ プチ ャ と 比較部分で利用で き 、 キ ャ プチ ャ し た フ レームパ タ ー ン を アプ リ ケーシ ョ ンへ示すために使用 し ます。

ADC か ら の DDR デー タ は、SDR モー ド の 2 つの ISERDESE2 で受信 さ れます。 こ の構成は、FPGA ロ ジ ッ ク (IBUFDS_DIFF_OUT) への差動出力 と 共に差動入力バ ッ フ ァ ーを使用す る 場合に可能です。 ISERDESE2 のシ リ アル-パ ラ レルレ ジ ス タ 内のデー タ は、CLK の立ち上が り エ ッ ジ と 立ち下が り エ ッ ジでキ ャ プチ ャ さ れます。 偶数ビ ッ ト (0、2、4、6、8、10、12、14) は CLK の立ち上が り エ ッ ジでキ ャ プチ ャ さ れ、 奇数ビ ッ ト は こ の ク ロ ッ ク の立ち下が り エ ッ ジでキ ャ プチ ャ さ れ る こ と を前提 と し ます。 差動入力バ ッ フ ァ ーの出力では、p 側に反転 し ないその ま ま の ビ ッ ト 値が現れ、n 側に反転 し た ビ ッ ト 値が現れます。 し たがっ て、n 側のキ ャ プチ ャデー タ は反転 し てい ます (図19)。 イ ンバー タ ーは、 すでに使用 さ れてい る ロ ジ ッ ク に入れ る こ と がで き ます。 X-Ref Target - Figure 18

図 18 : 基本デー タ イ ン タ ー フ ェ イ スのブ ロ ッ ク図

Bit and Byte Ordering, MSB and LSB Ordering, etc. MSB Register Register ISERDESE1 ISERDESE1 ISERDESE1 ISERDESE1 Register Multiplexer Register Register Multiplexer DataIn_1_p DataIn_1_n DataIn_0_n DataIn_0_p/n X524_18_040912 LSB Register MSB Register LSB Register CLKDIV LsbRegEna MsbRegEna CLKDIV CLK SwapMux BitSlip_n BitSlip_p Parameters [31:24] [15:0] [15:0] DataOut [31:0] [23:16] [15:8] [7:0]

偶数ビ ッ ト は ク ロ ッ ク の立ち上が り エ ッ ジでキ ャ プチ ャ さ れ、 奇数ビ ッ ト は立ち下が り エ ッ ジでキ ャ プ チ ャ さ れ る こ と を前提 と し ますが、こ れは保証 さ れてい ません。ク ロ ッ ク の立ち下が り エ ッ ジで偶数ビ ッ ト が p 側の ISERDESE2 へ入力 さ れた り 、 ク ロ ッ ク の立ち上が り エ ッ ジで奇数ビ ッ ト がキ ャ プチ ャ さ れ る 可能性があ り ます。図20に、 こ の よ う な状況を受けてマルチプ レ ク サーが こ れ ら の ビ ッ ト を並べ替 え る 様子を示 し ます。 ビ ッ ト ク ロ ッ ク ア ラ イ メ ン ト の ス テー ト マシ ンのエ ッ ジ検出レ ジ ス タ が、 マルチプ レ ク サーの入力選 択を制御 し ます。

X-Ref Target - Figure 19

図 19 : ISERDESE2 出力のイ ンバー タ ー X524_19_040612 I Data 1 1 1 0 1 0 0 1 1 1 1 0 1 0 0 1 0 0 0 1 0 1 1 0 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 IBUFDS_DIFF_OUT IB O OB CLK O OB O = Incoming Data

The dotted bits must be inverted to get 11101001 OB = Inverse of the Incoming Data

XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 19

リ フ ァ レ ン ス

デザイ ン

リ フ ァ レ ン スデザ イ ン フ ァ イ ルは、 次のサ イ ト か ら ダ ウ ン ロ ー ド で き ます。 https://secure.xilinx.com/webreg/clickthrough.do?cid=189141 表2に、 リ フ ァ レ ン ス デザ イ ンの詳細を示 し ます。 X-Ref Target - Figure 20図 20 : キ ャ プ チ ャデー タ と マルチ プ レ クサー機能 X524_20_040712 Data ISERDESE2_1 CLK CLKDIV Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q0 Q2 Q4 Q6 Q1 Q3 Q5 Q7 Q1 Q2 Q3 Q4 Q4 Q5 Q6 Q7 Q1 Q3 Q5 Q7 Q1 Q2 Q3 Q4 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 CLK D D CLKDIV ISERDESE2_2 1 1 1 0 1 0 0 1 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Multiplexer

When ISERDESE2_1 is clocked on the rising edge, the data appears as shown in this multiplexer.

When ISERDESE2_1 is clocked on the falling edge, the data appears at the ISERDES.Q bit swapped. A multiplexer

is needed to properly re-order them. Multiplexer 表 2 : リ フ ァ レ ン スデザイ ンの詳細 パラ メ ー タ ー 説明 全般 開発者 Marc Defossez タ ーゲ ッ ト デバ イ ス Kintex-7 FPGA XC7K325T-2FFG900 ソ ース コ ー ド の提供 あ り ソ ース コ ー ド の形式 VHDL 使用 し た IP な し シ ミ ュ レーシ ョ ン 機能シ ミ ュ レーシ ョ ンの実施 あ り タ イ ミ ン グシ ミ ュ レーシ ョ ンの実施 な し テ ス ト ベンチの形式 VDHL 使用 し たシ ミ ュ レー タ ソ フ ト ウ ェ アバージ ョ ン ISIM 13.3 ま たはそれ以降

SPICE/IBIS シ ミ ュ レーシ ョ ン な し イ ン プ リ メ ン テーシ ョ ン

合成ツール/バージ ョ ン XST 13.3 ま たはそれ以降

イ ンプ リ メ ン テーシ ョ ンツール/バージ ョ ン ISE® Design Suite 13.3 ま たはそれ以降 ス タ テ ィ ッ ク タ イ ミ ン グ解析の実施 あ り ハー ド ウ ェ ア検証 ハー ド ウ ェ ア検証の実施 あ り 検証に使用 し たハー ド ウ ェ アプ ラ ッ ト フ ォーム KC705 ボー ド 表 3 : デバイ ス使用率 パラ メ ー タ ー 仕様/詳細 最大周波数 (ス ピー ド グ レー ド ご と) Kintex-7 FPGA -1 600MHz -2 700MHz -3 700 デバ イ ス使用率 (テ ス ト ベンチな し) 2% デバ イ ス使用率 (テ ス ト ベンチあ り) (オプシ ョ ン) N/A QDR II SRAM 動作 な し バス幅 な し I/O 規格 HP バン ク:LVDS HR バン ク: LVDS_25 HDL 言語のサポー ト VHDL 検証用の タ ーゲ ッ ト メ モ リ デバ イ ス な し 表 4 : リ フ ァ レ ン スデザイ ンの使用率 ス ラ イ ス ロ ジ ッ クの使用率 使用済み 使用可能 使用 さ れている リ ソ ース数 (%) FF 数 302 407,600 1% 占有ス ラ イ ス の数 132 50,950 1% ロ ジ ッ ク と し て使用 さ れてい る 数 168 356,160 1% メ モ リ と し て使用 さ れてい る 数 64 64,000 1% シ フ ト レ ジ ス タ と し て使用 さ れて い る 数 0 ルー ト スルー と し て使用 さ れてい る 数 36 BUFG/BUFGCTRL 数 0 ISERDESE2 数 12 500 1% 表 2 : リ フ ァ レ ン スデザイ ンの詳細 (続き) パラ メ ー タ ー 説明

XAPP524 (v1.0) 2012 年 8 月 7 日 japan.xilinx.com 21

改訂履歴

次の表に、 こ の文書の改訂履歴を示 し ます。Notice of

Disclaimer

The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products.To the maximum extent permitted by applicable law:(1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications.You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent.Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx.Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:http://www.xilinx.com/warranty.htm#critapps. 本資料は英語版 (v1.0) を翻訳 し た も ので、 内容に相違が生 じ る 場合には原文を優先 し ます。 資料に よ っ ては英語版の更新に対応 し ていない も のがあ り ます。 日本語版は参考用 と し て ご使用の上、 最新情報につ き ま し ては、 必ず最新英語版を ご参照 く だ さ い。 こ の資料に関する フ ィ ー ド バ ッ ク および リ ン ク などの問題につき ま し ては、jpn_trans_feedback@xilinx.com までお知 らせ く だ さ い。 いただ き ま し たご意見を参考に早急に対応 させていただ き ます。 なお、 こ の メ ー ルア ド レ スへのお問い合わせは受け付けてお り ません。 あ ら か じ めご了承 く だ さ い。 IDELAYCTRL 数 18 18 5% MMCM_ADV 数 0 10 0% 表 4 : リ フ ァ レ ン スデザイ ンの使用率 (続き) ス ラ イ ス ロ ジ ッ クの使用率 使用済み 使用可能 使用 さ れている リ ソ ース数 (%) 日付 バージ ョ ン 内容 2012 年 8 月 7 日 1.0 初版 リ リ ース

![図 8 : サン プル エ ッ ジ を直接検出 (A 、 B 、 C 、 および D)DCLKC)BitClk_MonClk X524_08C_030212Sample on therising edgeStart1613-3 tapsFrom Q[8:1] stable at 0 toQ[8:1] unstable or stable at 1.Falling edge found](https://thumb-ap.123doks.com/thumbv2/123deta/5816931.539801/9.892.237.829.193.963/サンプルエッジ直接検出ABCおよびDDCLKCBitClkMonClkCSampletapsFromQ81stableattoQ.webp)

![図 12 : 基本的な フ レーム検出回路RqrdPatternFrameIn_pFrameIn_n [15:8][7:0]RegisterRegister](https://thumb-ap.123doks.com/thumbv2/123deta/5816931.539801/12.892.134.811.92.496/図12基本的なフレーム検出回路RqrdPatternFrameInpFrameInn1587RegisterRegister.webp)