リソグラフィ 1

第

2 編 リソグラフィ WG

第

1 章 はじめに

1-1 背景

ITRS ならびに STRJ のロードマップには、デバイスメーカ主体の観点で今後のデバイスの将 来像が描かれている。これはその将来のデバイスの実現のために、それぞれの技術研究開発 を集約し市場にデバイスが供給可能な体制をいつまでに整える必要があるかを明示してい る。図2-1-1 デバイス量産立ち上がりカーブ Figure 2-1-1 Production Ramp Curve

図2-1-1 には、ITRS のロードマップにおいて、デバイスの量産立ち上がり時期とテクノロジー のサイクルタイミングを明示している。このある微細化によるデバイスの量産が、少なくとも2つ のデバイスメーカによって最初に月産10,000 個以上の生産が開始される時期をその微細化の テクノロジーの生産導入時期とみなす。それまではそのテクノロジーの開発期間であり、その 時点の12 ヶ月前までに Production Tool つまり量産機が市場に投入されること、また 24 ヶ月 前にはβ機が、そしてその前にはα機が利用可能であることを必要とすることが示されている。 このリソグラフィ装置技術ロードマップでは、「デバイスメーカから要求されるリソグラフィ装置」と 「その装置を実現するために必要な技術開発、課題と解決策や候補、装置メーカからの提言」 を示す。またこのロードマップを「業界関係者間の技術情報の共有」に役立てたいと考えてい る。2012 年度版では、ITRS2011 に合わせた改訂と共に、章構成の見直し、新規露光技術の

リソグラフィ 2 体系付けの見直しなどの改訂を行った。

1-2 ロードマップの意義と期待する効果

この装置技術ロードマップは、一般のロードマップに当てはまるように次のような意義を持 つ。 1. ビジョンと目標の明確化と共有 2.実践プロセスの相互理解と役割の明確化 3.製品目標の発見と創生(仮説・論理・シナリオ) 4.コミュニケーションの促進(自律と協調) 5.鳥瞰的な全体理解(納得・確信) 6.競争と協調の調整(公開することによる共生) 7.資源の有効活用(重複投資回避) このリソグラフィ装置技術ロードマップでは、特に微細化を行う上で技術障壁が高くなって きている昨今において、SEAJ を中心とした半導体関連装置メーカやデバイスメーカ、材料メ ーカのみならず、国立研究機関、大学、また国レベルでの情報と知識の共有をすることによ ってお互いのビジョンを明確化することができる。またそれぞれの立場から相互の理解を促 進し、それぞれの役割を明確にすることをもたらし、そのためのコミュニケーションの促進を 図ることができるものと考える。今後の複雑で入り組んだ技術開発の過程を鳥瞰し、それぞ れのアクティビティの位置付けができる全体理解につなげ、ひいては重複投資を回避した 効率の良い開発の推進になる筈である。こうした情報を公開することにより競争と協調の調 整を図り、お互いの共生を実現するものである。 これによる期待効果としては (1) 基礎研究や技術開発を、効率良く分担できる。必要な要素開発をロードマップに記述す ることにより、例えば開発内容によって、 基礎研究の領域は: 国立研究所や大学で、 プリコンペティティブな開発領域は: コンソーシアム等で、 プリコンペティティブとコンペティティブの中間領域は: 装置メーカの共同開発で、 コンペティティブな開発領域は: 個別装置メーカで、 分担することができる。 特にプリコンペティティブな開発領域での各機関の協力と協調は、時間が限られている開 発期間内に効率よく開発を進める上で効果的である。 注: プリコンペティティブとは、量産化へ向けた解決策が示され、実用化が近いが、未だ業界 で競合状態にはなっていない状態を表す。 (2) リソグラフィ装置のコンポーネントメーカ、部品メーカ、材料メーカ、マスクおよびマスク関 連機器メーカ、レジストおよびレジスト関連機器メーカ等の皆様の開発計画策定に役立つもの と考えている。 (3) 将来露光技術として複数の方式が提案・検討されている。ここではそれらの方式、特徴、リソグラフィ 3 得意分野などについて解説を行うと共に、可能な限り現状及び今後の開発課題を明示した。 また参考文献等のリストも掲載しており、各方式理解と協調の一助になれば幸いである。

1-3 まとめと謝辞

昨今のようにデバイス、製造装置共に産業競争力が低下している状況では、技術情報の共 有による開発の効率化に有効利用できる装置技術ロードマップの作成とその浸透が急務であ る。本リソグラフィ装置技術ロードマップをご覧になった方々から多くのご意見ご指摘を賜り、ア ップデートしていきたい。 多くの皆様に有効活用されることを切に願う次第である。 謝辞: リソグラフィに関しては、ワーキンググループ委員以外多数の方々から原稿執筆のご協力を 頂きました。この場を借りて厚くお礼申し上げます。 また原稿作成に当たり多くのご助言、ご意見を賜りました。半導体技術ロードマップ委員会 (STRJ)の皆様、selete、EUVA,EIDEC を初めとするコンソーシアの皆様ならびに資料を提供下 さった各装置メーカ及び、リソグラフィ関係企業の皆様に感謝致します。第

2 章 技術概要

2-1 検討範囲

対象とするロードマップはITRS2011 をベースとし、原則として 2012 年 MPU/DRAM の 32nm および Flash の 20nm から 2018 年 MPU/DRAM の 15-16nm および Flash の 12nm ハーフピッチまでを対象範囲とした。また、表記方法として、年代とDRAM ハーフピッチ、 Flash ハーフピッチ、MPU は1層メタルのハーフピッチを採用しており、リソグラフィ装置で はより細かな時間軸区分が必要であるため、1年毎のロードマップとした。(図2-3-1 参照: DRAM ハーフピッチ 2012 年 32nm, 2015 年 23nm,2018 年 16nm とした。) リソグラフィ方式としては、現在、我が国で検討・開発されている技術を中心に記述し、ま た新規露光技術方として提案されてきている技術の紹介とそれぞれの方式と位置付けを明 確にした。また露光装置のみではなく関連技術である光源技術、マスク描画技術、 マスク 修正技術、コータデベロッパなどに関しても検討を行った。また露光技術に重要な役割を果 たすレジスト、データ変換についても最新の状況へのアップデートと今後の課題の記述を盛 り込んだ。32nm ハーフピッチ以細のソリューションとしてすでに量産技術として実用化され ているダブルパターニング(DP)ついては技術開発されている様々な方式に関し検討を加 えた。さらに微細化を進めるために必要なマルチプルパターニング(MP)に関してもダブル パターニングの説の中で一部解説を行った。

リソグラフィ

4

32nm ハーフピッチ以細のポテンシャルソリューションとして掲げられている EUV, インプ リント、ML2. Directed Self Assembly に関し、開発の現状と課題・展望に関し検討を行なっ た。これらの新規技術は、困難度が高く、実用化までに時間を必要とするため、最近では DFM( Design For Manufacturability)や Computational Lithography を駆使して、微細化技 術の延命を図る動きも目立つ様になって来た。DFM と Computational Lithography について も、解説を行なった。

2-2 検討項目・内容

各リソグラフィ技術の技術動向を把握し、ITRS2011 ロードマップの対応へむけての課題、 その解決策を検討した。その際、デバイスロードマップにおける顕著な傾向である下記の3 点は装置技術ロードマップ作成に多大な影響を与えるものであり、背景として考慮した。 (1) 三つのテクノロジードライバ ITRS2011 では ITRS2009 に引続き、次の3種類のデバイスに必要とされる最小線幅サイ ズを表記する方式が採用されている。その一つはDRAM ハーフピッチ でありこれまで通り 汎用デバイスの代表とされてきた汎用メモリである。その次にはFlash ハーフピッチであり近 年量産が顕著なフラッシュメモリはDRAM とのデバイス構造の違いから同一の世代のテクノ ロジーを用いるとDRAM よりも細かい微細化が可能であることから区別して表記されるよう になっている。ITRS2009 では DRAM よりも約 3 年早い微細化実用時期が示されていたが、 ITRS2011 では DRAM よりも約 4 年早い微細化実用時期が示されている。そして3つ目には MPU の 1 層メタルのハーフピッチである。MPU の大規模化と高速動作を実現するため Gate CD(Critical Dimension:線幅)の微細化が重要となっており、それに伴い 1 層メタルのハーフピッチの微細化が重要になっている。但し最近では微細化を計画通りに進めるのが 難しくなって来ており、実情に合わせ、ロードマップの微細化のスピードが緩和されており、 多方面のロードマップに大きな影響を及ぼすようになりつつある。 (2) 生産構造の変化と露光方式の多様化 現在、多くの国内デバイスメーカは、業界での生き残りを掛けて、選択と集中を強化し、 半導体生産の主力を主要製品に特化する傾向が見られるようになってきた。DRAM に特化 するメーカ、フラッシュメモリを中心に生産拡大を図るメーカ、先端プロセスの開発・量産を 行わずFoundry 企業に生産を委託する Fab Light 方式に方針を転換し、システム開発に重

点を置くSoC(System on Chip:システムオンチップ)メーカ、パワー半導体・LED・光センサ など特定製品を中心に事業展開を図るメーカなど様々なメーカが鎬を削っている。一方、海

外には汎用メモリやMPU を主力製品とし少品種・大量生産を中心とする半導体メーカ、半 導体の生産受託に特化したファンドリ、生産を外部に委託し設計・企画でビジネス拡大を目

指すファブレス、また設計から完成品の製造を手掛け販売会社に供給するODM (Original Design Manufacturing ), EMS(Electronics Manufacturing Service ) など様々

リソグラフィ 5 なビジネスモデルが立ち上がり、生産構造も大きく変化しつつある。装置メーカはこれらの すべての要求にこたえる必要がある。汎用メモリやMPU が「少品種大量生産」であるのに対 して、SoC をはじめとする多くの分野の製品群は、「多品種小中量生産」になると言われてい る。この生産構造の変化が、技術の選択として最適露光方式の多様化を産んだといえる。 (3) リソグラフィ技術の障壁の高さと複雑さ 今後リソグラフィ技術の発展には、従来よりも多くの内容、項目が開発課題として存在す ることが認識されており、その技術が確立されるためには主要な課題が全て解決されていな ければならない。つまりインフラストラクチャーの整備が必須となる。特に193nm(ArF)以降の リソグラフィでは、その障壁が高くなるばかりか課題も多く存在し、その克服のために一段と 装置の複雑さを必要としている。こうした背景があるなかで課題と解決策を明確にして取り 組むことが重要である。

第

3 章 技術要求・予測・課題

3-1 リソグラフィ方式の概説と全体ロードマップ

表2-3-1 に 16nm ハーフピッチ までに実用化される技術の候補を示す。 これまでは汎用メモリの量産に適した光リソグラフィが主流であったが、微細化の加速により将 来リソの候補として光方式以外にも様々な方式が提案されている。今後は解像度のみならず 生産規模や目的・用途に応じた使い分けがなされていく可能性が有る。 リソグラフィ方式は大別して光リソグラフィと電子ビーム(EB)リソグラフィと Imprint、DSA (Directed Self Assembly)などのその他の方式の3通りに分けられる。DSA は、単独では先端半 導体の加工には用いられず、他のリソグラフィ プラットフォームと組み合わせて使われる見通 しである。また16nm ハーフピッチ までの量産実用化が現時点では、不明の為、表には記載 していない。光リソグラフィとして実績のある光露光装置は微細化に対応して短波長化が進み、 現在は248nm、193nm といったエキシマレーザを光源とする露光装置が実用化され、その延 長として液浸技術の開発が進められている。さらに1桁以上短波長の光を用いたEUV リソグラ フィ方式は以前から実用化を目指した研究が取り組まれている。光リソグラフィの特徴はスル ープットが高く大量生産に適している事である。リソグラフィ 6 リソグラフィ名称 Lithography 方式 波長 Wave length マスク(倍率) Mask Mag. 248nm(KrF) 光 Optical 248nm(KrF) 4× 193nm(ArF) 193nm(ArF) 4× 193nm 液浸 (ArF Immersion) 134nm 等価波長(H2O ) 4× EUVL(Extreme Ultra Violet

Lithography) 13.5nm 4× ML2(Mask Less Lithography) EB ≦0.05nm *) 不要(not

required) Imprint Lithography 不要(not required) 1× *)電子のド・ヴロイ波長(解説 5-2.参照) EB 露光は微細加工能力を生かし、マスク製作手段への利用と共に先端デバイス R&D 用と して既に確立された技術である。近年、半導体製造に適した高スループット対応EB 露光方法 として、様々な方式が提案されて来たが、2011 年ITRSでは、ML2(Maskless Lithography)の みが23nm ハーフピッチ以細のポテンシャル・ソリューションとして提案されている。EB 露光は 解像度が高く、光露光が比較的苦手なCH(コンタクトホール)露光等で威力を発揮する。また ML2 はデバイス毎にマスクを製造する必要がないため、マスクの製造 TAT(Turn Around Time)が問題となるデバイス生産や次世代デバイスの開発・試作に適した方式である。 ここでは、デバイスの多様化に伴い、開発、生産、販売などの形態が変化する状況を考慮し、 現在提案されている露光方式の特徴から、各種適用の可能性を検討した。 (1) 少品種大量生産 従来からの主力であるDRAM、フラッシュメモリや MPU 等、少品種大量生産されるもの は、スループットの高い光露光装置が適している。現在実用化されている193nm リソグラフィ、

液浸技術、DP(Double Patterning)に続いて MP(Multiple Patterning),EUV(Extreme Ultraviolet)が候補として挙げられる。

(2) 多品種小中量生産

SoC など多品種小中量生産のデバイスはスループットに対する要求は前者ほど厳しくなく、 むしろカスタム性が高いため多品種への対応のしやすさ(主にマスクコスト低減、マスク製造リ ードタイム短縮)やメモリとロジックが混在する半導体チップへの対応が強く要求される。現状

リソグラフィ 7 のDUV(Deep Ultraviolet)光による光露光方式に代わる次世代技術として、高解像性が既に 実証済みでマスクを使用しないML2 といった EB リソグラフィ方式が提案されている。 (3) 試作・特殊デバイス(極小量生産) 次世代デバイスの試作開発、特殊な高速デバイス(携帯電話用の高周波デバイスや光ケ ーブル中継回路の発信器など)の生産、マイクロマシーンやナノテクノロジーの基礎研究分 野などは、生産量が非常に少なく高解像度を必要とするデバイスであり、デバイス毎にマス クを製造する必要がないという点でも、従来通りEBDW(EB Direct Writing)やその発展形 であるML2 方式が適している。Imprint Lithography も、一部のデバイスメーカで微細な寸法

のデバイスの試作や評価用にすでに実用化されている。また試作のみならず、デバイスの 量産化への対応も視野に入れた開発が進められている。

(4) Mix & Match

生産規模の観点による適性の他、デバイスのパターンによっても各方式の適性がある。 線幅均一性が要求されるゲートパターンや高解像力が要求されるCH に対しては EB 方式 が優れており、またEB 方式は DOF が大きい。こういった特徴に応じ、例えば特定レイヤー 用としての使われ方も考えられる。今後、解像度の厳しい特定レイヤー用としてEB 露光を 使い、高い解像度を必要としない他のレイヤーには光露光を使うという、光とEB との Mix & Match 方式の露光方法も検討されている。図 2-3-1 にリソグラフィロードマップを示す。 ITRS2011 に対応し、各リソグラフィのデバイス量産適応時期予測を示している。Directed Self Assembly に関しては、量産化時期が明確化されておらず、2018 年の実用化が微妙で ある為、表には記載しないこととした。

リソグラフィ 8

3-2 光リソグラフィ技術のポテンシャル

光リソグラフィにおける解像度は次に挙げるRayleigh の式により規定される。 R=k1(λ/NA) R :解像度 λ :露光光源波長 NA :レンズ開口数(Numerical Aperture)=n・sinθ θ :露光面への最大入射角 n :レンズとウェーハ間の媒体屈折率 k1 :プロセス定数;通常0.6~0.4 程度、理論限界 0.25 解像度を増大させる為には波長を短くし、NA を大きくし、k1ファクタを小さくする必要があ る。近年、検討が進められている液浸露光方式は、投影する光学系のウェーハ面に最も近 いレンズとウェーハの間を気体よりも屈折率の高い液体で満たすことによりNA をその液体 の屈折率倍にすることに注目した高NA 化の手法である。また、k1ファクタの低減のために 近年では変形照明*、位相シフト*、超解像技術が導入されている。これらの導入によりk1フ ァクタを通常の0.6 程度から 0.3 以下にまで低減することが可能となった。表 2-3-2 にリソグラ フィにおける解像度とNA, k1の関係を示す。 ITRS2007 に、リソグラフィの手法やデバイスによって量産で使われる k1 の目標値を決め て微細化の可能性を判断することになった。ITRS2011 では、EUV Single Exposure の k1の値と年度ごとのNA の値が Table に表記されたので、それらの値を表に取り込んだ。 ITRS2007 には Double Exposure/Double Patterning(DE/DP)においては、量産性を考慮し、

k1=0.20 以上と決められたが、最近では DE/DE の技術が進み DRAM/FLASH とも 20nm 1/2pitch での量産が見通せるか検討されるようになってきたため、この表 2-3-2 では、DE/DP の量産可能なk1 の値を 0.14 以上と決めた。Multiple Patterning では、Quadruple Patterning の可能性も視野に入れ、k1=0.09 以上 0.14 未満の領域を Multiple Patterning 可能な領域 に当てている。以上のk1 の目標値に基づいてカラーリングを行っている。MPU については、

1/2 pitch の値が DRAM に近く、量産性でk1の値が若干高めになるが、カラーリングも DRAM と大きな差が無いため DRAM の表を参考にして頂きたい。ArF のドライに関しては、 先端プロセスでのDE/DP もしくは Multiple Patterning がほとんど使われていないので、表に は記載しないこととした。技術の進展によっては、これらのカラーリングも変動する可能性が

リソグラフィ

9

表2-3-2 リソグラフィにおける解像度解像度と NA, k1の関係(Flash,DRAM)

Table 2-3-2 Relation in resolution, NA, k1 and wavelength in Optical Lithography

近年、パターンの微細化が進むにつれ、OPC(Optical Proximity Correction: 光学近接効果 補正)*の導入が避けられなくなってきている。これは補正パターンの解像度及びデータ量増 大の観点でマスク描画装置への負荷を増す要因となっている。

リソグラフィ

10

として、マスクのエラーファクタMEEF(Mask Error Enhancement Factor)*がある。図2-3-2 に示 す通り、MEEF は波長によらず k1ファクタの低下に伴い増加するため、マスク描画装置への負 荷は微細化スピード以上に厳しい要求となる。ただし、液浸からEUV の移行にあたっては、露 光波長が1 桁短波長化されるため、k1ファクタは一挙に緩くなり、MEEF も大幅に緩和される。 K1factor.vs.MEEF <6%att-PSM/Binary/Levenson: L/S> @B.F 0 1 2 3 4 5 6 0.25 0.3 0.35 0.4 0.45 0.5 K1-factor MEEF att-KrF 2/3Annular att-ArF 2/3Annular Bi-KrF 2/3Annular Lev-ArFσ0.3 図2-3-2 光リソグラフィにおける k 1 ファクタと MEEF の関係 Figure 2-3-2 Relation k1 and MEEF in Optical Lithography

用語説明

1) 変形照明(斜入射照明、Off axis illumination)

光軸の中心を外した位置に絞りを入れることによりレチクルに対し露光光束を斜めに

入射させる照明方法であり、解像度や

DOF が向上する。絞り形状により輪帯照明、四

(重)極照明などとも呼ばれる。

2) 位相シフト、PSM(Phase Shift Mask:位相シフトマスク)

位相シフトは

PSM を用いて光の位相を変化させることにより、解像度及び DOF

の向上を図る技術。

PSM には HT(ハーフトーン)マスク(Attenuate-PSM とも言う)やレ

ベンソンマスク(渋谷‐レベンソンマスクまたは

Alternative-PSM とも言う)などの種類が

ある。

3) OPC(Optical Proximity Correction:光学近接効果補正)

パターンの微細化に伴い、複数パターンの近接によって転写されたパターン形状が変

化してしまう近接効果が顕著になるため、レチクル上に微細な補正パターンをいれるこ

リソグラフィ

11

とによって転写パターン形状をコントロールする技術。

4) MEEF(Mask Error Enhancement Factor)レチクル上の誤差がウェーハ上で拡大される比率。

第

4 章 各リソグラフィ技術の動向、課題、解決策等

4-1 液浸露光技術

投影レンズとウェーハ間を液体で満たす露光方式である(図2-4-1)。原理的には露光波長 λを液体の屈折率n で除した等価波長λ/n による露光方式と理解でき、波長λ/n に相当する 解像力と焦点深度を得ることができる(表2-4-1)[1]。通常は波長λは変化せずに、NA が n 倍に増大したとして扱われる(NA は NA=n sinθで定義される(n は結像空間(液体)の屈折率、 θは結像光線の最大入射角))。液浸によってNA が1を超えることができるようになっている。

図2-4-1 液浸露光の基本構成 Figure 2-4-1 Principle of Immersion

表2-4-1 等価波長(λ/n)の比較 Table 2-4-1 Equivalent wavelength (λ/n) and Ratio

リソグラフィ 12 媒体 Media 屈折率 n Index 等価波長 λ/n Equivalent 等価波長比 Ratio 193nm dry Air 1.0 193nm 1.00 193nm Immersion Purified Water 1.44 134nm 0.69 193nm High Index

Immersion Organic Fluid ~1.65 ~117nm ~0.61

現在、実用化されているのは、媒体として純水(n=1.44)を用いた 193nm(ArF 波長)での露 光方式(λ/n = 134nm)である。2011 年現在、NA=1.35 の液浸露光装置を用いて、ハーフピッ チ40nm 程度までのデバイスの量産が行われるとともに、NAND フラッシュなど一部のデバイス 種においては側壁ダブルパターニング技術と組み合わせてハーフピッチ20nm 台の生産が行 われている[2, 3, 4, 5]。 図2-4-2 は、NA=1.30 の液浸露光装置で 39nm のパターンを露光したレジスト像の例である [2]。偏光照明とダイポール照明を組みあわせているため、比較的大きな焦点深度(800nm)を 得ている。NA=1.30 から 1.35 の露光装置において、生産に用いることができる解像限界として はハーフピッチで40nm 付近(k1=0.30)であると考えられており、それ以下のパターンを形成す るためには、ダブルパターニングの技法を液浸露光に組み合わせることが必要になる。 図 2-4-2 トップコート無しレジストを使った NA=1.30 193nm 液浸の 39nm L/S の解像例

リソグラフィ

13

Figure 2-4-2 Imaging of 39nm L/S by NA=1.30 193nm Immersion. Topcoat-less resist was used.

液浸露光においては、ディフェクトや気化熱による重ね合わせ誤差の発生が報告されてい たが、量産に問題ないレベルにまで改善されている。ダブルパターニングによる微細化に対応 するために、重ね合わせ精度を2nm 以下にする開発がなされ、2012 年現在、単一装置重ね では実現されている[6]。 純水による液浸の次の段階として、液体を純水から別の高屈折率液体に変更し、高NA を 得る試みが検討されていたが、多くの技術的な困難から2008 年の段階で実用開発には至ら ないことが判明した[5]。そのため純水をもちいた液浸のNA1.35 が当面の間、最高の NA とな る。 参考文献 [1] 大和 「液浸リソグラフィ」 応用物理 74巻 9号 p1192 (2005).

[2] J. Ishikawa, et al, “Latest results from the hyper-NA immersion scanners S609B and S610C”, Proc. SPIE 6520, 65201W (2007).

[3] H. Kubo, et al, “Immersion exposure tool for 45-nm HP mass production”, Proc. SPIE 6520, 65201X (2007).

[4] J. Klerk, et al, “Performance of a 1.35NA ArF immersion lithography system for 40-nm applications”, Proc. SPIE 6520, 65201Y (2007).

[5] S. Owa and H. Nagasaka “Immersion lithography: its history, current status, and future prospects”, Proc. SPIE 7140, 714015 (2008).

[6] Y. Uehara, et al., “Immersion and Dry ArF Scanners Enabling 22nm hp Production and Beyond”, Proc. SPIE 8326 (2012).

4.2 ダブルパターニング ダブルパターニング技術(以下 DP 技術と略す)は,現存の193液浸露光技術の限界解像 度を超える加工寸法を得るために考案された光露光の延命技術で,「自己整合タイプ」と「パ ターン分割タイプ」に大別さる。特に自己整合タイプの DP 技術は,微細化技術が先行する NAND Flash メモリで いち早く量産採用され,定着した技術でもある。さらに 1D レイアウトデ ザインの提案によりロジックデバイスへの展開も期待される。従来のプロセスを分割処理するこ とが前提である DP 技術では プロセスの複雑化やコストの上昇が懸念材料としてあり,エッチ ングや成膜技術を駆使しなければならない技術であることが リソ技術者には受け入れ難い手 法であることは事実である。しかし 大掛かりな設備投資をせずに,既存のプロセス装置を組み 合わせることで 微細パターンが得られることは 大きなメリットでもある。

リソグラフィ 14 4-2-1 自己整合タイプ スペーサ技術(SADP:Self-aligned DP)は,1 回のパターン露光で ピッチの 1/2 化が可能な 技術で DP 技術の中でも,最も簡便なプロセス工程で 193nm 液浸技術の解像限界を遥かに 超える高い解像性能を持つ(図 2-4‐3)[1] 。 図 2-4-3 レジストパターンをコアに用いた SADP フロー Figure 2-4-3 SADP Flow using resist pattern as a core

DP 技術は一様にプロセス処理工程数が多岐に渡り複雑化していることが懸念されているが, その解決策としては,レジストパターンをコアパターンに用いる手法が有望である。スペーサパ ターンとなる膜をレジストパターン上に直接 敷設する必要があるため レジストのガラス転移点 以下で成膜できる手法を用いるのが望ましい。レジストをコアパターンとし,低温で成膜が可能 なシリコン酸化膜を用いた実証例を図 2-4-4 に示す[2]。この手法では コアパターン形成用の 膜を,新たに追加する必要がなく,従来のシングル露光と同じレジスト積層構造で実現可能で あるため プロセスコストの低減にも寄与できる。 図 2-4-4 SADP の狭ピッチ化実証例 Figure2-4-4 Example of finner pitch using SADP

DP 技術は 成膜,エッチング技術を駆使する手法と見られる向きが強いが,リソグラフィの視 点でプロセス性能を認識・判断しなければならない。図 2-4-5 に示す様に,コアパターンの種 類によってプロセス余裕度に違いが現れる[3]。これはコアパターン形成時のエッチング工程で

焦点余裕度が著しく低下してしまっていることが所以であると推測できる。広いプロセス余裕度 を確保するためにもレジストをコアパターンとした手法を用いるのが良策であろう。

リソグラフィ

15

さらに 自己整合型 DP 技術は,20nm hp 以細の微細化に対する拡張性も有していることも 実証結果が報告されている。これは,SAQP(Self-Aligned Quadruple patterning)と呼ばれるも ので,端的にはピッチ分割を 2 度繰り返すものであるが,11nm hp までの解像性能を持つこと は秀逸な手法と言える。実証例では,レジストパターンを第一のコアとして ピッチを 1/2 化した パターンを下地の有機膜に転写し,さらに この有機膜を第 2 のコアとして用いている。従来の シングル露光工程と同様のレジスト積層構造で実現可能であることは プロセスコスト低減効果 として特筆すべき点である(図 2-4-6)[4]。 図 2-4-5 コア材別のプロセス余裕度比較

Figure2-4-5 Comparison of process margin between core materials

図 2-4-6 SAQP での11nm hp パターン解像結果

Figure2-4-6 Pattern imaging result of 11nm half pitch using SAQP

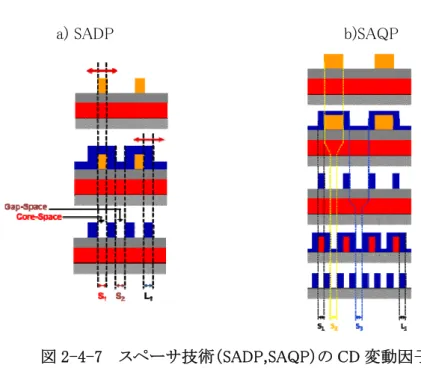

4-2-2 ダブルパターニングの CD 管理,LWR/LER 制御 SADP プロセスにおける CD 制御を語る上では,ライン CD より むしろ,スペース CD に注力 しなければならない。ここで,同じコアパターンを介して形成された 2 対のスペーサパターン間 をコアスペース,異なるコアパターンを介して形成された隣り合うスペーサをギャップスペースと 呼ぶ。SADP 処理後のライン CD は,ほぼスペーサ材の成膜制御性で決定されるが,コア・ギャ ップ 2 種類のスペース CD はコアパターンの CD,スペーサ材の膜厚,エッチング性能によって, 別個に変動する(図 2-4-7-a)。

リソグラフィ

16

a) SADP b)SAQP

図 2-4-7 スペーサ技術(SADP,SAQP)の CD 変動因子 Figure2-4-7 CD variation factors of

spacer technology (SADP,SAQP)

さらに SAQP では,ライン CD は第 2 のスペーサ CD で決定されるため寸法調整は容易であ るが,スペース CD は 3 種の変動因子からなるため,寸法制御に困難を来す(図 2-4-7-b)。ス ペース CD を調整する上で 最も厄介なノイズ成分はスペーサパターン上の LER であり,いか に LER を低減させるかが CD 安定性を確保する中核となる。LER の違いによるライン CD,スペ ース CD のウェハ面内均一性を比較した例を図 2-4-8,図 2-4-9 に示す[5,6]。LER を改善する ことにより,CD 均一性が劇的に改善されていることが分かり,さらにライン・スペース間の CD 差 も是正されている。

リソグラフィ

17

Figure 2-4-8 Figure2-4-9

Improvement of LEW/LWR by SAQP Improvement of CD Uniformity by SAQP

4-2-3 1D レイアウトと Complementary Lithography ロジックデバイスでは ゲート回路にランダムなレイアウトを用いることが通例であり,微細化に 伴い,高いパターン忠実度(Pattern Fidelity)の確保が求められてきた。現状の193液浸技術 では,このパターン忠実度を改善させる手法として SMO 技術が最たるものであろう。さらにパタ ーン忠実度やプロセスばらつき(Process Variability)を改善する手法として 1D レイアウトへの 移行が現実化している。これは 1 方向の方形パターンで構成されるレイアウトで,パターン形 成には,グリットライン形成とパターン切断の工程とに分割する手法が有力技術で,現在 この 相補的技術を Complementary Lithography と呼んでいる。前者のグリットライン形成には SADP が最適な手法であり,ライン切断には技術ノード世代ごとに要求されるパターン間隔によって, 露光技術が使い分けられる。Tela-Innovations 社デザインのレイアウトを用いた1D レイアウトの パターニング実証結果を 図 2-4-10 に示す[7]。193nm 液浸のシングル露光で 16nm ノード技 術世代まで適応できることが確認できている。この技術は Litho-Etch-Litho-Etch(LELE)プロ セスに代表される「パターン分割型」DP 技術に比べて露光時の重ね合わせ精度を大きく緩和 できることも特徴の一つである。 図 2-4-10 Complementary Lithography での1D パターン形成 Figure2-4-10 1D Patterning by Complementary Lithography

4-2-4 ダブルパターニングのホール適応

半導体デバイス種の中でも DRAM メモリのキャパシタ形成工程に最も微細なホールパター ンが必要とせれている。本項では 主に細密ホールに適応した DP 技術を紹介する。

・SADP

リソグラフィ 18 形成にも有用であることが分かっている。ピラーパターン上にスペーサ形成と同様の成膜を過 分に行うことで 4 本のピラー中心に窪みが生じる。引き続きスペーサ材をエッチバックすること で,ホールの狭ピッチ化が達成する。 シングル露光でホールのピッチ 1/2 化が可能な技術である。 ・DTD (デュアル・トーン・デベロップメント手法) DTD 技術は,レジストパターンの狭ピッチ化を目的として考案された技術であるが,原理的に はホールの狭ピッチ化にも有用な技術を推測できる。従来の露光~ポジ型現像にネガ型現像 を追加するだけで達成可能な技術で,リソクラスター(露光機,レジストトラック)内で全ての処 理が可能であることは,リソ技術者にとってはフレンドリな技術と言える(図 2-4-11)[8]。 図 2-4-11 DTD (デュアル・トーン・デベロップメント)法によるホールパターンの狭ピッチ化 Figure2-4-11 Finer pitch of hall pattern by DTD (Dual Tone Development)

・Cross-SADP SADP 技術を直行する形で多重処理することでラティス構造を形成し,最終的にホールを解 像させる技術である。解像性能は 20nmhp に達し,最も細密なホールを形成できる手法である (図 2-4-12)。露光の重ね合わせ精度が緩和できるのも特徴の一つ[9]。 図 2-4-12 Cross-SADP フロー Figure2-4-12 Flow of SADP

4-2-5 パターン分割タイプ

隣り合うパターンの処理工程を分離することで近接効果を低減させる手法で,リソ・エッチ・リ ソ・エッチ型と 処理工程短縮を意図したリソ・リソ・エッチ型とに分類される。露光時の重ね合 わせ精度に改善の余地があるため実用化が遅れていたが,NTD(ネガ・トーン・デベロップメン

リソグラフィ

19

ト)の登場で ロジックデバイスのメタル工程(トレンチ,ビアホール)で実用化されつつある。

参考文献

[1] W. Jung et. al., “Patterning with Spacer for Expanding the Resolution Limit of Current Lithography Tool”, Proc. SPIE6156 p.481 (2006)

[2] A.Hara et.al., “Advanced self-aligned DP process development for 22-nm node and beyond” Proc.of SPIE 7639-79 (2010)

[3] Y. Kuwahara et.al., “Advanced multi-patterning using resist core spacer process for22nm node and beyond” Proc.of SPIE 8325-79 (2012)

[4] H.Yegashi et.al., “Novel approaches to implement the self-aligned spacer double patterning process toward 11-nm node and beyond” Proc.of SPIE 7972-10 (2011) [5] K.Oyama et.al., ” CD error budget analysis for self-aligned multipatterning” Proc. of

SPIE 8325-43 (2012)

[6] K.Ohmori et.al., ” CD uniformity improvement on the self-aligned spacer double patterning process by resist material modification” Proc.of SPIE 8325-12 (2012)

[7] Michael C. Smayling et.al., “Sub-20nm logic lithography optimization with simple OPC and multiple pitch division” Proc.of SPIE 8326-39 (2012)

[8] S.Yamauchi et.al., “Applicability of double patterning process for fine hole pattern” Proc. of SPIE 8325-77 (2012)

[9] K.Oyama et.al., “The enhanced photoresist shrink process technique toward 22nm node” Proc.of SPIE 87972-98 (2011)

4-4 EUV

4-4-1 EUV リソグラフィ

波長13.5nm の EUV 光(Extreme Ultraviolet:極端紫外光)を用い、マスクパターンをウェー ハに1/4 に縮小転写する露光方式で、円弧状の領域をスキャン露光する。光を用いる縮小投 影スキャン露光方式であることから、193nm(ArF)リソグラフィの延長線上の技術と考えられ、光 リソグラフィの特長である量産性を持つ[1], [2], [3], [4]。使用波長が従来の1/10 以下であるため、 0.5 以上の k1 ファクタで DRAM ハーフピッチ 16nm あるいは 11nm まで対応可能である。ス ループットは100wph 以上(300mm wafer、10mJ/cm2、200W)が見込まれている。従来の光リソ グラフィとの最大の違いは、EUV 光を透過する材料が無いことから、露光光学系とマスクが全 て反射式(ミラー)になる点と、露光雰囲気が真空になる点である。EUV 光を反射するために、 重元素と軽元素を波長の約半分の周期で交互に数十層重ねた多層膜コートが用いられる。 EUV リソグラフィの使用波長が 13.5nm である理由は、最も安定で高い反射率を有する Mo/Si 多層膜の特性にあわせたためである。次世代EUV リソグラフィの基礎研究もすでに始まって

リソグラフィ

20

おり、La/B4C、LaN/B4 C、LaN/B などの多層膜を用いて波長 6.7nm に対して約 40%の反射率

が得られているが[5]、その波長半値幅は極めて狭く、実用化の目処は立っていない。 EUV リソグラフィ実現のための最大の課題は、光源技術、レジスト技術、およびマスク技術 である。波面収差や反射率などの各種計測には、信頼性があってクリーンな放射光源(SOR) が用いられるが、露光機に用いる光源としては光量が大きく不足する。レーザプラズマ光源や 放電プラズマ光源の開発が日米欧で盛んに行なわれている[6]。高出力で、照明ミラーの反射 率劣化の原因となるデブリ(高温プラズマや放電による飛沫物)の少ない光源の開発が急務で ある。光源出力は、発光点出力でなく、投影光学系で利用可能な集光点出力で議論される。 毎時100 枚以上のウェーハスループットを実現するためには、第一集光ミラー、デブリ低減機 構、波長選択フィルタなどを通過した後の集光点出力が115W 必要と試算され[7]、発光点出力 は300W を超えると考えられていた。しかしながら、この必要パワーの計算のベースとなってい たレジスト感度5mJ/cm2の実現は困難な状況にあり、光源パワーの要求値は180W、そして 200W へと上方修正された[8]。更なるスループット要求、投影系NA の拡大に伴うミラー枚数の 増加、レジストの高解像度化に伴う感度低下などが予想されており、光源パワー要求値は将 来的には500W を超える可能性もある。たとえそのような超高出力光源が実現できたとしても、 真空装置であるEUV 露光機には熱負荷の問題がある。高解像度や低 LER(ラインエッジラフ ネス)との両立は容易なことではないが、高感度化もきわめて重要な要素である。 EUV マスクの多層膜は、完全な欠陥修正が容易でないことから、多層膜成膜工程の無欠 陥化や成膜前の基板の無欠陥化が大きな課題である。加えて、ペリクルの使用が困難である ことから、後述のマスクキャリアを含めたマスクハンドリング技術も重要となる。基板、ブランクス、 マスクの欠陥低減には、欠陥検査機の開発が急務である。基板の欠陥検査には共焦点顕微 鏡の原理を応用した検査機が広く使われているが、実用感度は40nm 程度であり[9]、更なる高 感度化が必要である。多層膜検査は露光波長の光を用いた検査[10]が必要とされており、製品 化へ向けた開発が始まっている。マスクパターン検査についても、露光光パターン検査機や 露光光顕微鏡の開発が始まっている。 照明光学系の課題は、いかに少ない枚数で照度と照明σ の均一性を実現するかにある。 Mo/Si 多層膜の反射率はせいぜい 70%しかなく、ミラー枚数は少なければ少ないほど良い。 一方、CD 制御性(線幅均一性)の要求から、露光領域内における照度と σ の均一性が必要で あり、少ないミラー枚数でこれらを実現するためには、特殊形状をした多素子ミラー (Multi-facet Mirror)の作製が課題となる[11]。 投影光学系の課題は広範囲にわたる。非球面ミラー加工&計測、多層膜成膜、ミラー保持、 ミラー温度制御、波面計測等の技術にそれぞれブレークスルーが必要である。hp22nm 用の 投影光学系に対する波面精度要求は0.3nm rms と言われており、6 枚の非球面ミラーに求め られる形状精度は55 pm rms である。hp16nm から 11nm 用の投影光学系には波面精度 0.2nm rms が必要となり、8 枚の非球面ミラーに求められる形状精度は 35pm rms である。多層膜によ る反射光の位相変化は、EUV 光と可視光では全く異なるため、両波長による波面測定値の比

リソグラフィ 21 較評価が急務であった。これは2001 年度から 2005 年度まで NEDO の基盤技術研究促進事 業プロジェクトにおいて装置が開発され、2006 年度から 4 年間民間の自主研究が行なわれた [12]。ミラーの中間空間周波数帯の粗さ(MSFR)により、フレアが生じ、線幅(CD)制御性に影響 を与える。フレア量は波長の二乗の逆数に比例することから、EUV リソグラフィにおけるフレア は、従来の光リソグラフィのそれより多くなるため、フレア対策が重要となる。また、ミラー温度制 御技術は、光源の効率が低く光学系に莫大なエネルギーが投入されるEUV において、光学 系の精度維持に欠かせない開発項目である。発生した熱を効率よく排出する手段、及び、熱 の影響を受けにくいシステムの開発が要求される。マスクやウェーハでの発熱によるオーバレ イの劣化も懸念される。 多層膜コートされたミラーは、コンタミによってその反射率が低下する。例えば照明光学系、 マスク、及び投影光学系トータルで11 枚のミラーがあるとして、ミラー1面当たりの反射率が 70%から 69%にたった 1%低下したとして、光源からウェーハまでの伝送効率は約 15%も低下 する。コンタミには、ミラー表面に炭素がつくカーボンコンタミと、酸素と反応する酸化がある。 カーボンコンタミは防ぐ技術とクリーニングする技術が必要である。酸化は一度発生すると除 去が困難なため、防止技術[13]が必要であるが、水素ラジカルによる酸化還元方式によるクリー ニングも研究されており[14]、大きな期待が寄せられている。 EUV に使えるペリクルの開発が困難であることから、シッピング、保管、露光機内ハンドリン グ時のマスクへの異物付着防止技術が重要である。異物付着を防止するには、マスクへの接 触回数を極限まで減らす必要がある。シッピング、保管、露光機内ハンドリングを同一キャリア で行なう二重ポッドコンセプトが提案されている[15]。マスクを専用のエンクロージャで保護し、 露光機などの装置でエンドエフェクタがマスクに直接触れない工夫が施されている。二重ポッ ドコンセプトを採用したマスクキャリアは、Selete において性能評価が行なわれ、良好な評価結 果が得られている[16], [17], [18]。2009 年 7 月には SEMI 規格が成立、発行された[19]。 4-4-2 EUV 露光装置と EUV 要素開発 図2-4-13 に、EUV 露光装置の原理図を示す。 EUV リソグラフィ技術は、従来の光リソグラフィ技術の延長線上にあり、使用波長が 13.5nm と従来の1/10 以下であるため、比較的大きな k1 ファクタで hp22nm 世代から 11nm 世代まで 使用できることから、微細化対応と光リソグラフィの量産性を併せ持つ唯一の技術として期待さ れている。露光機のシステム技術に関しても、やはり従来の光リソ露光機システム技術の多く がそのまま利用できるが、EUV 露光機固有の技術も少なからず存在する。EUV 露光機固有 ではないが、対象が微小線幅ゆえの技術課題も存在する。EUV 露光機システム技術は、非球 面投影光学系開発技術、照明光学系開発技術、高精度反射光学系対応アライメント技術、真 空中高精度マスク及びウェーハステージ技術の各サブシステムから成る。加えて、これらのサ ブシステムを統合し、光源と組み合わせて真空容器内に構成する総合組み立て調整技術も 必要である。

リソグラフィ

22

Reticle Stage

Laser Produced Plasma Source or Discharge Source :13.5nm :1064nm Wafer Stage Illumination Optics Projection Optics Alignment Sensor Xe Nozzle Reticle YAG Laser Reticle Stage

Laser Produced Plasma Source or Discharge Source :13.5nm :1064nm Wafer Stage Illumination Optics Projection Optics Alignment Sensor Xe Nozzle Reticle YAG Laser

図2-4-13 EUV 露光機外観 Figure 2-4-13 EUV Exposrue System

193nm 液浸リソグラフィ&ダブルパターニングにより、すでに hp32nm の量産が始まっている。 EUV 露光機に期待されるのは、3 重以上のマルチプルパターニングが必要となる世代、具体 的にハーフピッチが20 nm を切るであろう 2015 年からの量産対応である。これまで、2007 年に は、フルフィールドのプロトタイプ露光機(α 機)による露光結果が得られた。2010 年から 2011 年に掛けて、プリプロダクション露光機(β 機)が 6 台出荷された。2012 年には準量産用露光機 が登場する予定である。プリプロダクション露光機に適用すべく、各要素開発が2010 年度末を めどに行なわれてきたが、まだ解決すべき多くの課題が残されており、2011 年度以降も継続 開発が行なわれている。

リソグラフィ

23 参考文献

[1] C. Gwyn et al.: “Extreme Ultraviolet Lithography White Paper 1998”, EUV LLC(1998). [2] C. Gwyn et al.: “Extreme Ultraviolet Lithography White Paper 1999”, EUV LLC(1999). [3] D. A. Tichenor et al.:”EUV Engineering Test Stand”, Emerging Lithographic

Technologies IV, Proc. of SPIE, 3997, 48(2000).

[4] EUV Lithography (SPIE Press Book), edited by Vivek Bakshi, SPIE Vol. No.: PM178 (2008).

[5] T. Tsarfati et al.: "Improved contrast and reflectivity of multilayer reflective optics for wavelengths beyond the Extreme UV", Alternative Lithographic Technologies, Proc. of SPIE Vol. 7271, 72713V-1 (2009).

[6] EUV Sources for Lithography (SPIE Press Book), edited by Vivek Bakshi, SPIE Vol. No.: PM149 (2006).

[7] K. Ota et al., "Join spec", EUV Source Workshop, Feb. 2003.

[8] K. Suzuki et al, "Joint Requirements for EUV Source", International Symposium on Extreme Ultraviolet Lithography、Oct. 2009.

[9] A. Ma et al., "Improvement of EUVL mask blank inspection capability at Intel",

Photomask and Next-Generation Lithography Mask Technology XVI. Proc. of SPIE Vol. 7379, 73790I (2009).

[10] T. Terasawa et al., "Development of actinic full-field EUV mask blank inspection tool at MIRAI-Selete", Alternative Lithographic Technologies, Proc. of SPIE Vol. 7271, 727122-1 (2009).

[11] H. Takino et al., "Fabrication of a fly-eye mirror for an extreme-ultraviolet lithography illumination system by arranging silicon mirror elements", Emerging Lithographic Technologies VI, Proc. of SPIE Vol. 4688, pp.648-655 (2002).

[12] K. Sugisaki et al., "EUV Wavefront Measurement of six-mirror optic using EWMS", Emerging Lithographic Technologies XII, Proc. of SPIE Vol. 6921, 69212U (2008). [13] S. Bajt: "Oxidation resistance of Ru-capped EUV multilayers", Emerging Lithographic

Technologies IX, Proc. of SPIE Vol. 5751, 118-127 (2005).

[14] I. Nishiyama, "Atomic Hydrogen Cleaning for EUV Optics Contamination", International Symposium on Extreme Ultraviolet Lithography, Oct. 2007.

[15] Y. Gomei et al. "EUVL mask dual pods to be used for mask shipping and handling in exposure tools”, Emerging Lithographic Technologies XI, Proc. of SPIE Vol. 6517, 65170W (2007).

[16] M. Amemiya et al., "Particle-Free Mask Handling Techniques and a Dual-Pod Carrier", Emerging Lithographic Technologies XII, Proc. of SPIE Vol. 6921, 69213T (2008). [17] M. Amemiya et al., " Experimental Study of Particle-free Mask Handling", Alternative

リソグラフィ

24

Lithographic Technologies, Proc. of SPIE Vol. 7271, 72713G (2009).

[18] K. Ota et al., "Selete EUV Reticle Shipping and Storage Test Results", Photomask and Next-Generation Lithography Mask Technology XV, Proc. SPIE, Vol. 7028, 70280I (2008).

[19] SEMI E152-0709, "Mechanical Specification of EUV Pod for 150 mm EUVL Reticles", (2009).

4-5 ML2 ( Maskless Lithography )

4-5-1 ML2(マスクレス・リソグラフィ)の全体状況 電子ビームを用いたウェーハ直接描画技術は、パターンデータをもとにウェーハに直接パタ ーンを描画する技術である。マスクを必要としないため、マスクレスリソグラフィと呼ばれ、リソグ ラフィ工程や工期を圧縮できる可能性がある。しかし、電子ビーム直接描画の処理能力が低 いため、これまでは、デバイスの開発・試作やASIC の QTAT(Quick Turn Around Time)製造 等の用途に限定して使用されてきた。電子ビームを用いたウェーハ直接描画の処理能力向上 のため、種々の描画方法が提案されている。ビームあるいはカラムをマルチ化することが、電 子ビーム直接描画を高スループット化するための基本的アイデアである。マルチカラムは、カ ラムの本数を複数にして、並列描画する方式である。マルチビームは、1カラム内のビーム本 数を複数にして、並列描画する方式である。 マルチビーム方式には、1つの電子銃から放射された電子をアパーチャアレイで多数のビ ームに分けた後、透過型ブランカーアレイで個別にオンオフして、パターンを描画する技術が ある。また、反射型パターンジェネレータでピクセル毎にビームをオンオフする描画技術がある。 現在、継続的に開発成果が報告されている透過型ブランカーアレイによるマルチビーム描画 装置にPML2 と MAPPER がある。また、反射型パターンジェネレータによるマルチビーム描画 装置にREBL がある。PML2、MAPPER、REBL の概要を図 2-4-14 に示した。リソグラフィ 25 図 2-4-14 PML2,MAPPER,REBL の概要 Fig 2-4-14 Outline of PML2, MAPPER,REBL PML2 は、IMS Nanofabrication が開発しているシングルカラム・マルチビーム方式の描画装 置である。[1],[2],[3],[4] MEMS 技術で製作したアパーチャプレートシステム(APS)を用いる。電子 ビームをアパーチャアレイにより、数 1000 本~1000 万本程度(最終目標)の多数本のビーム (ビームレット)に分ける。アパーチャアレイの各開口の下流に、個別にブランカー電極を設け て、ビームレットを個別に偏向する。偏向されたビームレットは最終絞りを通過できない。最終 絞りを通過したビームレットに対応して、アレイ開口の1/200 縮小像をウェーハに投影する。各 開口のウェーハ上における像サイズは約 15nm である。ステージ移動と同期して、ステージ移 動方向に並んだビームレットのオンオフ状態を制御することにより、ウェーハ上の各点を複数 回のビームレットで多重照射し、ウェーハにパターンを描画する。一つ一つの開口像サイズは 固定のため、多重照射の照射回数を制御するグレースケール(Gray Scale)制御により、描画 パターンの線幅を制御する。PML2 をウェーハ直接描画に適用する場合の目標スループット は5wph である。 PML2 と同様な描画方式を持つ電子ビームマスク描画装置 eMET 開発が行われている。 [5],[6],[7],[8] 加速電圧 50KeV、個別ビーム径約 20nm、総ビーム本数約 25 万本のマッシブパラレ

リソグラフィ

26

ル型電子ビーム描画装置である。先端フォトマスクを 10 時間以内で描画することを目標として いる。eMET カラムの原理検証(Proof-of-Concept; POC)結果が報告されている。線幅 20nm 程度のデバイステストパターンの描画結果や、Gray Scale 制御による線幅制御結果が得られ ている。これらの結果は、描画シミュレーションの結果とよく一致する。現在、原理検証段階を 終了し、量産機の試作が進められている。2012 年にシステムインテグレーションを行い、2013 年には描画時間を含むシステム評価結果を出すことを目標としている。

MAPPER は、MAPPER Lithography が開発するシングルカラム・マルチビームの描画方式で

ある。[9],[10] 低加速電圧 5keV の電子ビームを利用する。電子ビームをアパーチャアレイにより、 110 本(現在)~13000 本(最終目標)の多数本のビーム(ビームレット)に分ける。アパーチャア レイを配置した領域が非常に広い(26x26mm)のが特徴である。アパーチャアレイ全体を電子 ビームで均一に照射する。アパーチャアレイの各開口を通過したビーム(ビームレット)は全体 としてクロスオーバ像を結ぶことなく、静電レンズによりウェーハ上に結像する。静電レンズ下 部にあるデフレクターアレーが、各ビームレットをウェーハ上約 3um 幅で走査する。同時に、ブ ランカーアレイにより各ビームレットをオンオフ制御して、ウェーハ上にパターンを描画する。加 速電圧 5keV、有効な電子ビーム電流値の総計 150uA、アパーチャアレイ 26x26mm 範囲の均 一照射、の各条件をすべて満たせば、ウェーハ直接描画に適用する場合のスループット 10wph が可能である。また、10wph の MAPPER 装置を 10 台集めて(クラスタリング)、100wph スループットのシステムが提案されている。 現 在 、 110 本 ビ ー ム の MAPPER 社 の pre- α 機 を 使 っ て 評 価 が 行 わ れ て い る 。[11] 45nm1:1LS パターンを各ビームレットで個別に描画し、110 本ビーム間の線幅ばらつき約 3nm、 ウェーハ間の線幅再現性 3nm の描画結果が得られている。また、近接効果補正パラメータを 決定して、小規模なデバイスパターンを描画した結果も報告されている。描画に使えるトータ ルビーム電流値が目標の約 1/50 程度にとどまっていることが、Mapper の現状における最大課 題である。アパーチャアレイの開口数を約 50 倍増やすことが提案されている。[12] この場合、シ ステム規模が拡大し、複雑さも増すため、量産機の開発完了時期が延伸することが懸念され る。 REBL は、KLA-Tencor が開発するシングルカラム・マルチビームの描画方式である。[13] 加速 電圧 50keV の電子銃を用いる。50keV に加速された電子ビーム軌道を電磁界で曲げて、DPG (Digital Pattern Generator)と呼ばれるパターン発生部に導く。DPG 全体に電子銃の加速電圧 と同じ電圧 50kV を逆極性で印加する。電子ビームは DPG に達した時には減速し、電子銃カソ ードにおける熱電子発生直後と同程度の運動エネルギ(1eV 程度)になる。DPG には 4096× 248 個の電極(画素電極)を配置する。各画素電極に個別に+2V あるいは 0V の電圧を重畳する と、減速されてほとんど運動エネルギーを持たない電子のうち、+2V 電極近傍の電子だけが電 極に引き付けられる。これにより画素電極に印加した電圧パターンに相当したパターンを発生す る。カラムの下半分は、このパターンを 50kV で逆向きに再加速し、1/50 に縮小して試料面に転 写する光学系である。ウェーハ直接描画に適用する場合の目標スループットは、hp45nm におい

リソグラフィ 27 て、コンタクト Via 層で 45wph、ゲート層で 5wph、配線層で 2wph である。 REBL カラムを製作し、描画特性の検証結果が報告されている。DPG の構造がパターンの解 像性に大きく影響することが分かった。[14] 画素電極に個別にオンオフ電圧を印加したとき、電極 間で電界の干渉が発生する。これによりビームコントラストが低下し、描画パターンの解像性が 劣化する。これを避けるため新しいタイプの DPG が検討されている。MEMS で形成した深さ数 µm の分離壁で DPG 画素電極を相互に分離し、電極間電界の干渉を防止する。さらにこの分離 壁に多層の静電レンズ電極を形成し、電子ビームを電極面で収束させる方式が検討されている。 また、REBL カラムの小型化やカラム光学系構造の見直し、データパスの検討も進められている。 [15],[16] マルチカラム方式は、複数個の電子ビームカラムを試料ウェーハ上に設置する方式である。 電子銃(電子源)、レンズ、偏向器等をカラム個別に用意し、各カラムの電子ビームを独立に制 御することにより、ウェーハにパターンを描画する。適切に描画条件を設定すれば、マルチカラ ム方式の描画装置は、単一カラム(シングルカラム)の描画装置より、カラム本数分だけ描画時 間が早くなり、スループットも向上するものと考えられる。マルチカラムの製作方法には、ウェーハ 張り合わせ、貫通穴形成、断面加工などの半導体プロセス技術を用いて、複数本カラムを一度 に製作する方法がある。このような方法で製作したミニチュアサイズのマルチカラムの研究が行 われている。また、通常の電子ビームカラムの径を小さくし、それらを複数個集めてマルチカラム を製作する方法がある。代表例であるマルチカラム(MCC)方式の開発現状を、次節以降で紹 介する。 ML2 実用化のためには、数多く提案されている ML2 技術それぞれの将来性を見極め、見通 しのある方式に戦略的に開発資源を投入することが必要である。2015 年の 1Xnm ノードデバイス の試作に向けて ML2 の実用化が期待される。このために民間は勿論、官学とも連携し ML2 の開 発を加速することが求められる。 参考文献

[1] C. Klein, E. Platzgummer, J. Klikovits, W. Piller, H. Loeschner, T. Bejdak, P. Dolezel, V. Kolarik, W. Klingler, F. Letzkus, J. Butschke, M. Irmscher, M. Witt, W. Pilz, P. Jaschinsky, F. Thrum, C. Hohle, J. Kretz, J. T. Nogatch, and A. Zepka;“PML2: the maskless multibeam solution for the 22nm node and beyond”, Proc. SPIE Vol. 7271, 72710N (2009)

[2] Elmar Platzgummer, Christof Klein, Peter Joechl, Hans Loeschner, Martin Witt, Wolfgang Pilz, Joerg Butschke, Michael Jurisch, Florian Letzkus, Holger Sailer and Mathias Irmscher, "Charged particle multi-beam lithography evaluations for sub-16nm hp mask node fabrication and wafer direct write", Proc. SPIE 7488, 74881D (2009)

[3] C. Klein, E. Platzgummer, H. Loeschner, G. Gross, P. Dolezel, M. Tmej, V. Kolarik, W. Klingler, F. Letzkus, J. Butschke, M. Irmscher, M. Witt, and W. Pilz; “Projection maskless

リソグラフィ

28

lithography (PML2): proof-of-concept setup and first experimental results”, Proc. SPIE Vol. 6921, 69211O (2008)

[4] Elmar Platzgummer, Hans Loeschner, and Gerhard Gross;“Results obtained with the CHARPAN Engineering Tool and prospects of the ion Mask Exposure Tool (iMET)”, Proc. SPIE Vol. 7122, 71220L (2008)

[5] Christof Klein, Jan Klikovits, Hans Loeschner and Elmar Platzgummer, "eMET: 50 keV electron multibeam mask exposure tool", Proc. SPIE 7970, 79700C (2011)

[6] Elmar Platzgummer, Christof Klein and Hans Loeschner, "eMET POC: realization of a proof-of-concept 50 keV electron multibeam mask exposure tool", Proc. SPIE 8166, 816622 (2011)

[7] Elmar Platzgummer, Stefan Cernusca, Christof Klein, Samuel Kvasnica, Bernd Sonalkar and Hans Loeschner, "eMET: development of a 50 keV electron projection multibeam mask exposure tool for the 16nm hp technology node and below", Proc. SPIE 7748, 77480H (2010)

[8] Elmar Platzgummer, Stefan Cernusca, Christof Klein, Jan Klikovits, Samuel Kvasnica and Hans Loeschner, "eMET: 50 keV electron mask exposure tool development based on proven multi-beam projection technology", Proc. SPIE 7823, 782308 (2010)

[9] M. J. Wieland, G. de Boer, G. F. ten Berge, R. Jager, T. van de Peut, J. J. M. Peijster, E. Slot, S. W. H. K. Steenbrink, T. F. Teepen, A. H. V. van Veen, and B. J. Kampherbeek; “MAPPER: high-throughput maskless lithography”, Proc. SPIE Vol. 7271, 72710O (2009)

[10] E. Slot, M. J. Wieland, G. de Boer, P. Kruit, G. F. ten Berge, A. M. C. Houkes, R. Jager, T. van de Peut, J. J. M. Peijster, S. W. H. K. Steenbrink, T. F. Teepen, A. H. V. van Veen, and B. J. Kampherbeek; “MAPPER: high throughput maskless lithography”, Proc. SPIE Vol. 6921, 69211P (2008)

[11] L. Pain, B. Icard, M. Martin, C. Constancias, S. Tedesco, P. Wiedeman, A. Farah, B. J. Kampherbeek, C. Pieczulewski and H. Kandrashov, "IMAGINE: an open consortium to boost maskless lithography take off: first assessment results on MAPPER technology", Proc. SPIE 7970, 79700Y (2011)

[12] M. J. Wieland, H. Derks, H. Gupta, T. van de Peut, F. M. Postma, A. H. V. van Veen and Y. Zhang, "Throughput enhancement technique for MAPPER maskless lithography", Proc. SPIE 7637, 76371Z (2010)

[13] Paul Petric, Chris Bevis, Allen Carroll, Henry Percy, Marek Zywno, Keith Standiford, Alan Brodie, Noah Bareket, and Luca Grella; “REBL: A novel approach to high speed maskless electron beam direct write lithography”, J. Vac. Sci. Technol. B27, ( 2009 ) 161 [14] Regina Freed, Jeff Sun, Alan Brodie, Paul Petric, Mark McCord, Kurt Ronse, Luc

リソグラフィ

29

Haspeslagh and Bart Vereecke, "Demonstration of lithography patterns using reflective e-beam direct write", Proc. SPIE 7970, 79701T (2011)

[15] Paul Petric, Chris Bevis, Mark McCord, Allen Carroll, Alan Brodie, Upendra Ummethala, Luca Grella, Anthony Cheung and Regina Freed, "New advances with REBL for maskless high-throughput EBDW lithography", Proc. SPIE 7970, 797018 (2011)

[16] Faruk Krecinic, Shy-Jay Lin and Jack J. H. Chen, "Data path development for multiple electron beam maskless lithography", Proc. SPIE 7970, 797010 (2011)

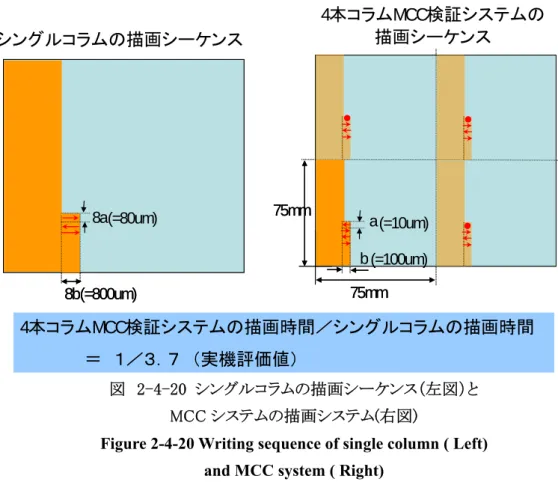

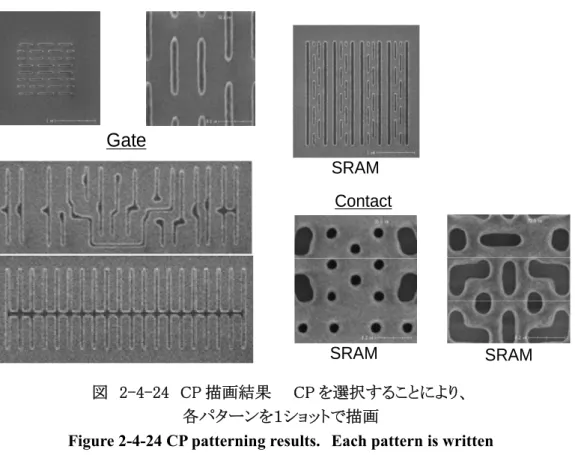

4-5-2 MCC(マルチカラムセル)描画方式の開発状況 可変矩形やCP 描画方式のシングルカラム描画装置が、デバイスの開発・試作に使用されて いる。技術的には確立したこれらの描画方式を活用しながら、描画スループットを向上するた めに、マルチカラム(MCC)方式の描画装置を製作した。電子ビーム描画のスループットを飛 躍的に向上するためには、カラムを複数本に分けて並べることが本質的に重要である。その理 由を以下に説明する。 12 インチウェーハを、加速電圧 50keV、レジスト感度 30µC/cm2、スループット5wph で描画す る場合を考える。パターンを形成するためウェーハに照射しなければならない総電荷量と描画 時間から、この条件で描画するためには、10µA 以上のビーム電流値が必要である。10µA の ビーム電流を通常の電子光学系をもつカラムに通した場合、クーロン相互作用により、例えば 1Xnm ノードパターンの解像性を得るのは非常に困難である。電流値 10µA を 10 本のカラム に分けるとすれば、1 カラム当たりの電流値は 1µA となる。この場合、クーロン相互作用の影響 は小さく、解像性とスループットの両立が可能となる。また、1 本のカラムでビーム電流値 10µA と解像性を両立するような電子光学系が可能であったとしても、スループット5wph を実現する ためには20MHz 以上のショットサイクルが必要である。加速電圧 50keV の電子ビームを一定 以上の範囲に偏向し、偏向位置でビームを静定させることが必要な偏向器で、この速いショッ トサイクルを実現することは技術的難易度が高い。また、解像性と両立するためにレジスト感度 が低下する傾向にあり、レジスト感度と電流密度の比から決まるショット時間を、このショットサイ クルに合わせることも技術的難易度が高い。10 本のカラムに分けて各カラムが個別独立に描 画可能とすると、各カラムの偏向器に要求されるショットサイクルは2MHz 程度となり、これは十 分に実現可能な値である。以上述べたように、電子線描画装置において、高解像性とスルー プットを両立するためにカラムを複数本に分けることは、本質的に必要である。

リソグラフィ

30

HOST

Stage control unit Gun HV Power Supply

Disk MCC Column Mask Substrate CC1 CC2 CC3 CC4 100um 100um 75mm 75 mm

LENS Power Supply

Pattern data Data Correctio n Analog Circuits HOST

Stage control unit Gun HV Power Supply

Disk MCC Column Mask Substrate CC1 CC2 CC3 CC4 100um 100um 75mm 75 mm

LENS Power Supply

Pattern data Data Correctio n Analog Circuits 図2-4-15 MCCの検証システムの概要(左図)と描画シーケンス(右図) Fig2-4-15 Schematic diagram of MCC verification system(Left)

and writing sequence(Right) カラム本数分スループットが向上し、かつ、解像性・精度が得られるという MCC 方式のコン セプトを検証するために、4 本カラムからなる検証システムを製作した。[1],[2],[3],[4] システムの概 要を図 2-4-15 に示した。4 本のカラムは、個別に電子銃、電磁レンズ、偏向器等を持ち、各カ ラムを独立に制御する。システムの主要部分を写した写真を図2-4-16 に示す。写真中心付近 に見える円筒形部分の中に4 本のカラムがある。円筒の両側に、4 本カラムの各偏向器を駆動 するアナログアンプを搭載する。カラム下部の真空チャンバ内には、試料ウェーハを搭載した ステージを設置する。各カラムのビーム電流条件は、従来のシングルカラムのビーム電流とほ ぼ同じである。つまり4 本カラム全体では従来カラムの約 4 倍のビーム電流を利用する。