2016 Microchip Technology Inc. DS00001900A_JP - p. 1

はじめに

Microchip 社は次世代型の Ethernet スイッチ、産業用 EtherCAT コントローラ、産業用 10/100 Ethernet MAC/PHY

コントローラをサポートするための設計ソリューションを提供しています。Ethernet スイッチ製品には、ホストバス

と

MII という 2 つのカテゴリがあります。ホストバス バージョンはスイッチ構造に備わるフル機能 Ethernet MAC を

サポートします。非ホストバス バージョンは、1 および 2 ポートの各種方式 (MII, RMII, Turbo MII) をサポートします。

以下の表に、各種製品を示します。

低コストを重視する、短距離の

PCB 接続を使う、極限環境条件 ( 温度等 ) で使う、このようなアプリケーションでは

トランスレス設計が有効です。2 つの既知の固定 Ethernet デバイスが既知の距離を隔てて通信する必要がある場合、

トランスレス設計にしておくと場所を問わずに適用できます。例えば、デバイス同士が同一

PCB 上で通信する場合ま

たは

VME 筐体のようにバックプレーン越しに通信する場合です。

本アプリケーション

ノートでは、トランスレスで 2 つの LAN9XXX Ethernet デバイスを接続するためのガイドライン

を示します。

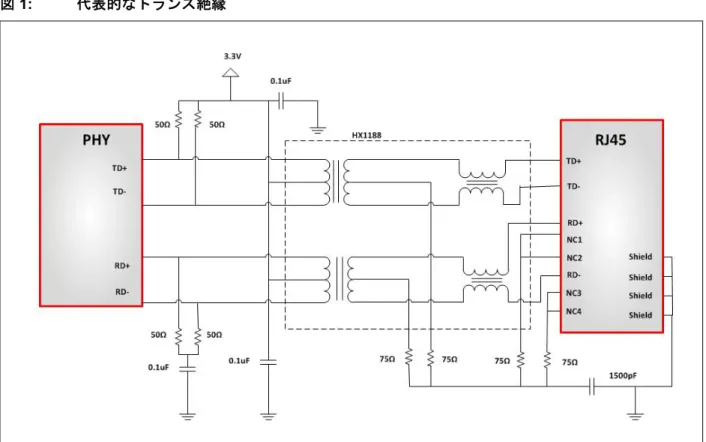

代表的なトランス絶縁

特殊なトランスレス

アプリケーション開発上の制約を認識するためには、物理ネットワーク サービスおよび信号伝達を

理解し、代表的な応用回路でトランスが担う機能を知る事が必要です。

代表的なネットワーク構成は、ケーブルを介した

2 つの物理層デバイス間の 2 点間接続からなります。

図

1

に、代表的

なトランス インターフェイス回路を示します。各ノードのトランスミッタとレシーバは、1:1 のトランスで直流的に

ネットワーク

ケーブルから絶縁されています。

トランスは、ケーブルからの直流絶縁機能と物理層デバイスにおける直流バイアス印加機能を持っています。絶縁は、

『

IEEE 802.3 AC and DC isolation specifications for cabled configurations』に準拠する必要があります。

製品番号

説明

LAN9250

産業用

10/100 Ethernet コントローラ & PHY

LAN9252

2/3 ポート EtherCAT スレーブ コントローラ ( 内蔵 Ethernet PHY)

LAN9352

10/100 2 ポートマネージド Ethernet スイッチ (16 ビット非 PCI CPU インターフェイス )

LAN9353

10/100 3 ポートマネージド Ethernet スイッチ ( シングル MII/Turbo MII またはデュアル RMII)

LAN9354

10/100 3 ポートマネージド Ethernet スイッチ ( シングル MII)

LAN9355

10/100 3 ポートマネージド Ethernet スイッチ ( デュアル MII/RMII/Turbo MII)

AN1900

Microchip 社 Ethernet コントローラ、スイッチ、

EtherCAT コントローラのトランスレス アプリケーション

Author:

Kansal Mariam Banu Shaick Ibrahim

Microchip Technology Inc.

注意: この日本語版文書は参考資料としてご利用ください。最新情報は必ずオリジ ナルの英語版をご参照願います。

AN1900

図

1:

代表的なトランス絶縁

2016 Microchip Technology Inc. DS00001900A_JP - p. 3

AN1900

トランスレス構成

特殊なトランスレス

ネットワーク アプリケーションの動作要件を満たすために、物理層コンポーネントの送受信の

分離とバイアス印加、

さらにはアプリケーション特有の安全要件を満たす高電圧直流絶縁を実装する必要があります。

代表的な構成ではトランスで実現している絶縁を、特殊なアプリケーションでは無極性コンデンサを使って実現でき

ます。

代表的なネットワーク構成は、自動ネゴシエーション、Auto-MDIX、10 Mbps 動作、100 Mbps 動作をサポートします。

トランスレス アプリケーションでは、リンクの両端をローカルが制御するため自動ネゴシエーションと Auto-MDIX は

無効化される場合があります

( 自動ネゴシエーションと Auto-MDIX が常に有効な LAN9252 を除く )。システム設計者は

両デバイスを特定の速度の二重通信方式に設定し、確実に通信させる事ができます。

Microchip 社ラボでのテストでは、2 つの PHY デバイスが Auto-MDIX と自動ネゴシエーションを両方とも有効にした

ままで正常にリンクを確立し通信しました。

しかしリセットからのリンクに数秒の遅延が生じました。

自動ネゴシエー

ションと

Auto-MDIX を無効にする事で、このシステム起動時の遅延を回避できます。

IEEE 802.3–2008 仕様では TX および RX 線路を差動モードで動作させる事を求めています。TXP および TXN 線路で

差動ペアを形成し、長距離の場合は

100 Ω の差動インピーダンスに、短距離の場合は 50 Ω の差動インピーダンスに

設計する必要があります。また、RXP および RXN 線路で差動ペアを形成し、適切な差動インピーダンスになるよう

に設計する必要があります。

図

3:

代表的なトランスレス絶縁

- 2 つの PHY を互いに接続

AN1900

自動ネゴシエーション

自動ネゴシエーション機能の目的は、リンク先の性能に基づいて、トランシーバを最適なリンク

パラメータを持つよ

うに自動的に設定する事です。自動ネゴシエーションとは、2 つのリンク パートナー間で設定情報を交換し、両者が

サポートするモードのうち最も高性能な動作モードを自動的に選択するための仕組みです。

LAN9XXX は、ハードウェアに関する以下のセクションに示す設定での自動ネゴシエーションのテストに成功してい

ます。

レジスタによる自動ネゴシエーションの無効化

( 自動ネゴシエーションが常に有効な LAN9252 は

非該当

)

自動ネゴシエーションは、PHY x 基本制御レジスタ (PHY_BASIC_CONTROL_x) の自動ネゴシエーション イネーブル

(PHY_AN) ビットをクリアする事で無効にできます。この場合、トランシーバは PHY x 基本制御レジスタ

(PHY_BASIC_CONTROL_x) の速度選択 LSB (PHY_SPEED_SEL_LSB) と二重通信方式モード (PHY_DUPLEX) の

情報を反映して動作速度を設定します。自動ネゴシエーション有効時、これらのビットは無視されます。

Note:

以下のセクションで、各

PHY レジスタ末尾に追加されている小文字の「x」は、PHY A または PHY B を

表す「A」または「B」に置き換えます。場合によって、「1」」または「2」が適切な場合があります

(LAN9250 は非該当 )。

PHY x 基本制御レジスタ (PHY_BASIC_CONTROL_x)

ビット

説明

タイプ

既定値

13 速度選択LSB (PHY_SPEED_SEL_LSB) 自動ネゴシエーション イネーブル (PHY_AN) ビットが クリアされている場合、このビットを使ってPHY の 速度を設定する。 0: 10 Mbps 1: 100 Mbps R/W LAN9252: 1’b1 LAN9250,LAN352,LAN9353,LAN9354,LAN9355: 100BASE-FX モードの場合 : 1’b1 autoneg_strap_x が「1」の場合 : 1’b1 上記以外の場合 : speed_strap_x の値 1 自動ネゴシエーション イネーブル (PHY_AN) このビットで自動ネゴシエーションの有効/ 無効を 切り換える。有効にした場合、速度選択LSB (PHY_SPEED_SEL_LSB) と二重通信方式モード (PHY_DUPLEX) はオーバーライドされる。 0: 自動ネゴシエーションを無効にする 1: 自動ネゴシエーションを有効にする R/W LAN9252: 100BASE-FX モードの場合 : 1’b0 上記以外の場合 : 1’b1 LAN9250,LAN9352,LAN9353,LAN9354,LAN9355: 100BASE-FX モードの場合 : 1’b0 上記以外の場合 : autoneg_strap_x の値 8 二重通信方式モード(PHY_DUPLEX) 自動ネゴシエーション イネーブル (PHY_AN) ビットが 無効の場合、このビットを使って二重通信方式を設定 する。 0: 半二重 1: 全二重 R/W LAN9252:1’b1 LAN9250,LAN9352,LAN9353,LAN9354,LAN9355: 100BASE-FX モードの場合 : duplex_strap_x の値 上記以外で autoneg_strap_x が「1」の場合 : 1’b0 上記以外の場合 : duplex_strap_x の値 2016 Microchip Technology Inc. DS00001900A_JP - p. 5

AN1900

ハードウェア

ストラップによる自動ネゴシエーションの無効化 (LAN9252 は非該当 )

下記のストラップは、LAN9252 に対しては無効です。

LAN9250 に対しては、autoneg_strap_2、duplex_strap_2、speed_strap_2 は無効です。

HP Auto-MDIX

HP Auto-MDIX を使うと、インターフェイス配線構成を考慮する事なく、CAT-3 (10BASE-T) または CAT-5 (100BASE-TX)

メディアの

UTP 接続ケーブルを使えます。ストレート ケーブルとクロスケーブルのどちらかをユーザが差し込むだ

けで、トランシーバは

TXPx/TXNx と RXPx/RXNx (LAN9250 は TXP/TXN、RXP/RXN 各 1 系統のみ ) のツイストペア

ピンを設定し、正常に動作できます。

デバイスの内部ロジックが、接続したデバイスの

TX および RX ピンを認識するためです。RX および TX 線路はペア

が入れ換わる可能性があるため、

Auto-MDIX 設計における磁気学的対称性と終端処理の対称性を確保するため PCB

設計上特別な考慮が必要です。

ストラップ名

説明

ピン

/ 既定値

autoneg_strap_1 PHY A 自動ネゴシエーション イネーブル ストラップ: 「0」 -- 自動ネゴシエーションを無効にする 「1」 -- 自動ネゴシエーションを有効にする LAN9250,LAN9352,LAN9354 : 1’b1 LAN9353,LAN9355 : P1_INTPHY ストラップ値 (Note: P1_INTPHY は、リセット時にラッチされるハード ストラップです。) autoneg_strap_2 PHY B 自動ネゴシエーション イネーブル ストラップ: 「0」 -- 自動ネゴシエーションを無効にする 「1」 -- 自動ネゴシエーションを有効にする 1’b1 duplex_strap_x PHY x 二重通信方式選択ストラップ : 「1」 -- 全二重 「0」 -- 半二重 1’b1 speed_strap_x PHY x 速度選択ストラップ : 「1」 -- 100 Mbps 「0」 -- 10 Mbps 1’b1Note:

以下のセクションで、各

PHY レジスタ末尾に追加されている小文字の「x」は、PHY A または PHY B を

表す「A」または「B」に置き換えます。場合によって、「1」」または「2」が適切な場合があります

(LAN9250 は非該当 )。

AN1900

レジスタによる

Auto-MDIX の無効化 (LAN9252 は非該当 )

Auto-MDIX 機能のソフトウェア ベースの制御は、PHY x 特殊制御 / ステータス表示レジスタ

(PHY_SPECIAL_CONTROL_STAT_IND_x) の Auto-MDIX 制御 (AMDIXCTRL) ビットで実行できます。AMDIXCTRL が

「1」にセットされている場合、Auto-MDIX の機能は PHY x 特殊制御 / ステータス表示レジスタ

(PHY_SPECIAL_CONTROL_STAT_IND_x) の Auto-MDIX イネーブル (AMDIXEN) ビットと Auto-MDIX ステート

(AMDIXSTATE) ビットで決まります。

ハードウェア

ストラップによる Auto-MDIX の無効化 (LAN9252 は非該当 )

MDIX ストラップの機能を下記に示します。

PHY x 特殊制御 / ステータス表示レジスタ (PHY_SPECIAL_CONTROL_STAT_IND_x)

ビット

説明

タイプ

既定値

15 Auto-MDIX 制御 (AMDIXCTRL) R/W 0 このビットでAuto-MDIX 制御のもとを決定する。 NASRセットした場合、Auto-MDIX 機能はこのレジスタの AMDIXEN および AMDIXSTATE ビットで制御する。 0: Port x の Auto-MDIX はストラップ入力で決まる 1: Port x の Auto-MDIX はビット 14 および 13 で決まる 14 Auto-MDIX イネーブル (AMDIXEN) R/W 0 このレジスタのAMDIXCTRL ビットがセットされている場合、AMDIXSTATE ビット

と組み合わせてこのビットを使いPort x の Auto-MDIX 機能を制御する。 NASR

13

Auto-MDIX ステート (AMDIXSTATE) R/W

0 このレジスタのAMDIXCTRL ビットがセットされている場合、AMDIXEN ビットと組

み合わせてこのビットを使いPort x の Auto-MDIX 機能を制御する。 NASR

Auto-MDIX イネーブル

Auto-MDIX ステート

モード

0 0 マニュアルモード、ストレート 0 1 マニュアルモード、クロス 1 0 Auto-MDIX モード 1 1 予約済み( 使用禁止 )auto_mdix_strap_x

manual_mdix_strap_x

モード

0 0 マニュアルモード、ストレート 0 1 マニュアルモード、クロス 1 X Auto-MDIX モード 2016 Microchip Technology Inc. DS00001900A_JP - p. 7

AN1900

物理接続

トランスミッタの出力はトランス内に電流を吸い込むように設計されています。トランスを用いない場合、

図

4

に示す

ように出力電圧を生じさせるため各デバイスに負荷抵抗を接続する必要があります。

Note:

Auto-MDIX 動作では、電源に接続した 50 Ω を RX ピンに配置します。TX ピンも同様です。Auto-MDIX

が無効で、かつ

RX ピンが受信モード専用の場合、ピン間の差動抵抗が 100 Ω である限り、外付け終端

をどのような方法で接続してもかまいません。

AN1900

距離の考慮

2 つの Ethernet デバイスをトランスを使わずに接続するシステムを設計する場合、必要とされるハードウェアはデバ

イス間の距離によって影響を受けます。

2 つのデバイスを短距離で接続する場合

一般的なガイドラインとして、およそ

1 メートル未満の距離を短距離とし、1 メートル以上の距離を長距離とします。

短距離の場合、

50 Ω の抵抗を並列に組み合わせて

図

5

に示すような

25 Ω の抵抗で構成する事ができます。

図

5:

短距離用の負荷抵抗

2016 Microchip Technology Inc. DS00001900A_JP - p. 9

AN1900

2 つのデバイスを長距離で接続する場合

長距離の場合、両

Ethernet デバイスの各アナログピンに終端抵抗を接続する事を推奨します。長距離の構成例は、

バックプレーンで接続したデバイス、長いケーブルで接続したネットワーク

カード等です。

図

6

に示す構成を使った

抵抗配置を最適化するには、実験で適切に妥当性を確認する必要があります。

高電圧を誘起する恐れ、またはノイズの影響を受ける恐れがあるため、トランスを使わずに非常に長い距離をケーブル

接続する事は推奨しません。

図

6:

長距離用の両端に配置する抵抗

AN1900

LAN9XXX では、RX ピンの直流除去コンデンサは不要です。別の Ethernet デバイスと接続する場合、コンデンサを

接続する必要がある事もあります。

図

7

に、LAN9115 との接続例を示します。

まとめ

LAN9XXX は特殊なトランスレス ネットワーク アプリケーションでも使え、問題なく送受信できます。ネットワーク

ケーブルとの直流絶縁として、個別のアプリケーションに適した最低限の直流絶縁定格を備える無極性コンデンサを

使う事を推奨します。

図

7:

直流除去コンデンサを必要とするデバイスとの接続

LAN9XXX

3.3V TXP TXN RXP RXNLAN9115

RXP RXN TXP TXN 3.3V 50? 50? 50? 50? 0.1uF 0.1uF 100? 0.1uF 0.1uF 50? 50? 2016 Microchip Technology Inc. DS00001900A_JP - p. 11

AN1900

補遺

A:

アプリケーション

ノートの改訂履歴

表

A-1:

改訂履歴

リビジョンレベル

/ 日付

セクション

/ 図 / 項目

改訂内容

DS00001900A_JP

(2015 年 2 月 26 日 )

本書は初版です。

本書に記載されているデバイス アプリケーション等に関する 情報は、ユーザの便宜のためにのみ提供されているものであ り、更新によって無効とされる事があります。お客様のアプ リケーションが仕様を満たす事を保証する責任は、お客様に あります。Microchip 社は、明示的、暗黙的、書面、口頭、法 定のいずれであるかを問わず、本書に記載されている情報に 関して、状態、品質、性能、商品性、特定目的への適合性を は じ め と す る、い か な る 類 の 表 明 も 保 証 も 行 い ま せ ん。 Microchip 社は、本書の情報およびその使用に起因する一切の 責任を否認します。生命維持装置あるいは生命安全用途に Microchip 社の製品を使用する事は全て購入者のリスクとし、 また購入者はこれによって発生したあらゆる損害、クレーム、 訴訟、費用に関して、Microchip 社は擁護され、免責され、損 害を受けない事に同意するものとします。暗黙的あるいは明 示的を問わず、Microchip 社が知的財産権を保有しているライ センスは一切譲渡されません。 商標

Microchip 社の名称とロゴ、Microchip ロゴ、dsPIC、FlashFlex、 KEELOQ、KEELOQロゴ、MPLAB、PIC、PICmicro、PICSTART、 PIC32ロゴ、rfPIC、SST、SST ロゴ、SuperFlash、UNI/O は、米 国およびその他の国におけるMicrochip Technology Incorporated の登録商標です。

FilterLab、Hampshire、HI-TECH C、Linear Active Thermistor、 MTP、SEEVAL、Embedded Control Solutions Company は、 米国におけるMicrochip Technology Incorporated の登録商標 です。

Silicon Storage Technology は、他の国における Microchip Technology Inc. の登録商標です。

Analog-for-the-Digital Age、Application Maestro、BodyCom、 chipKIT、chipKIT ロゴ、CodeGuard、dsPICDEM、dsPICDEM.net、 dsPICworks、dsSPEAK、ECAN、ECONOMONITOR、 FanSense、HI-TIDE、In-Circuit Serial Programming、ICSP、 Mindi、MiWi、MPASM、MPF、MPLAB Certified ロゴ、MPLIB、 MPLINK、mTouch、Omniscient Code Generation、PICC、 PICC-18、PICDEM、PICDEM.net、PICkit、PICtail、REAL ICE、 rfLAB、Select Mode、SQl、Serial Quad I/O、Total Endurance、 TSHARC、UniWinDriver、WiperLock、ZENA および Z-Scale は、米国およびその他のMicrochip Technology Incorporated の商標です。

SQTP は、米国における Microchip Technology Incorporated のサービスマークです。

GestIC および ULPP は、Microchip Technology Inc. の子会社 であるMicrochip Technology Germany II GmbH & Co. & KG 社 の他の国における登録商標です。

その他本書に記載されている商標は各社に帰属します。 © 2016, Microchip Technology Incorporated, All Rights Reserved. Microchip 社製デバイスのコード保護機能に関して以下の点にご注意ください。 • Microchip 社製品は、該当する Microchip 社データシートに記載の仕様を満たしています。 • Microchip 社では、通常の条件ならびに仕様に従って使用した場合、Microchip 社製品のセキュリティ レベルは、現在市場に 流通している同種製品の中でも最も高度であると考えています。 • しかし、コード保護機能を解除するための不正かつ違法な方法が存在する事もまた事実です。弊社の理解では、こうした手法 はMicrochip 社データシートにある動作仕様書以外の方法で Microchip 社製品を使用する事になります。このような行為は知 的所有権の侵害に該当する可能性が非常に高いと言えます。 • Microchip 社は、コードの保全性に懸念を抱いているお客様と連携し、対応策に取り組んでいきます。 • Microchip 社を含む全ての半導体メーカーで、自社のコードのセキュリティを完全に保証できる企業はありません。コード保 護機能とは、Microchip 社が製品を「解読不能」として保証するものではありません。 コード保護機能は常に進歩しています。Microchip 社では、常に製品のコード保護機能の改善に取り組んでいます。Microchip 社の コード保護機能の侵害は、デジタル ミレニアム著作権法に違反します。そのような行為によってソフトウェアまたはその他の著作 物に不正なアクセスを受けた場合、デジタル ミレニアム著作権法の定めるところにより損害賠償訴訟を起こす権利があります。

DS00001900A_JP - p.13 2016 Microchip Technology Inc.